Pertemuan6 Rangkaian Sekuensial RANGKAIAN LOGIKA SEKUENSIAL SINKRON A

- Slides: 35

Pertemuan-6 Rangkaian Sekuensial

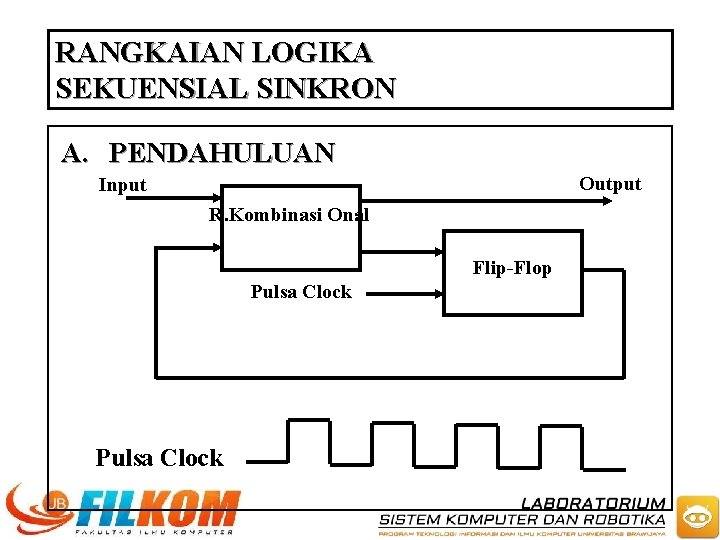

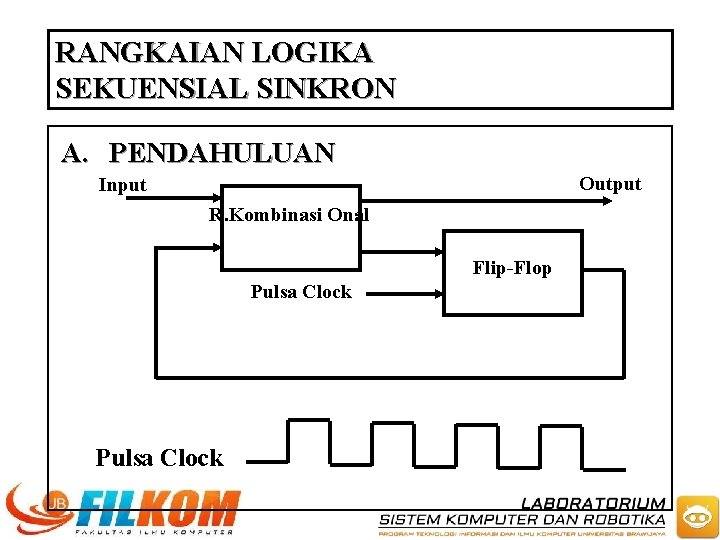

RANGKAIAN LOGIKA SEKUENSIAL SINKRON A. PENDAHULUAN Output Input R. Kombinasi Onal Flip-Flop Pulsa Clock

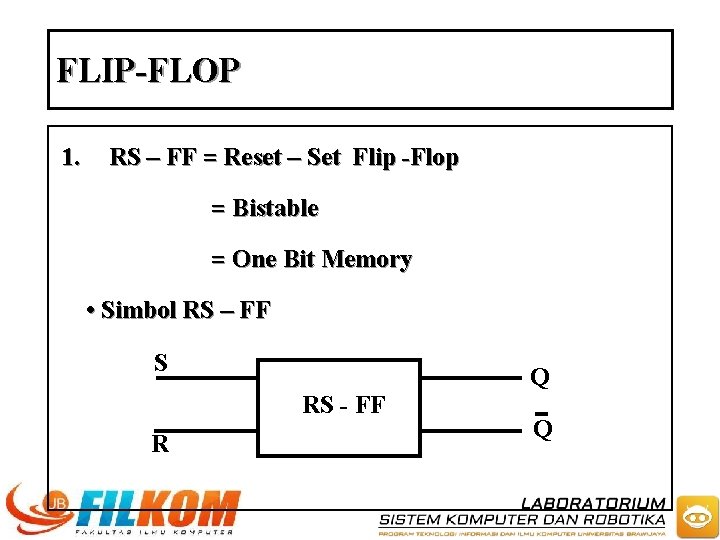

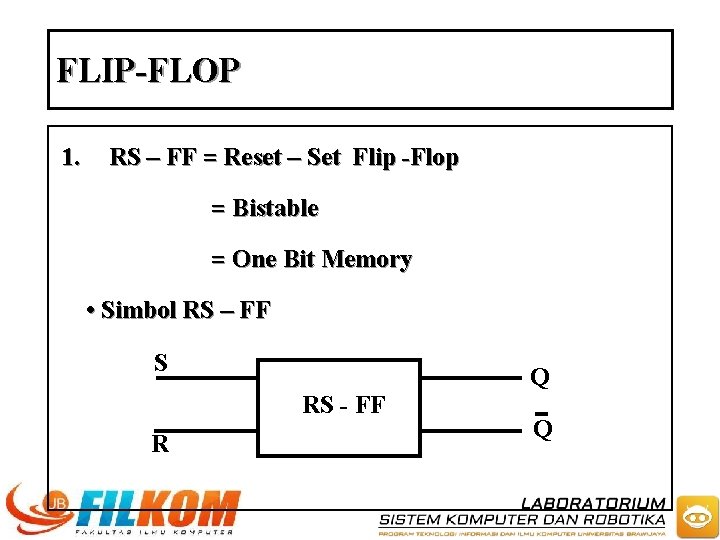

FLIP-FLOP 1. RS – FF = Reset – Set Flip -Flop = Bistable = One Bit Memory • Simbol RS – FF S Q RS - FF R Q

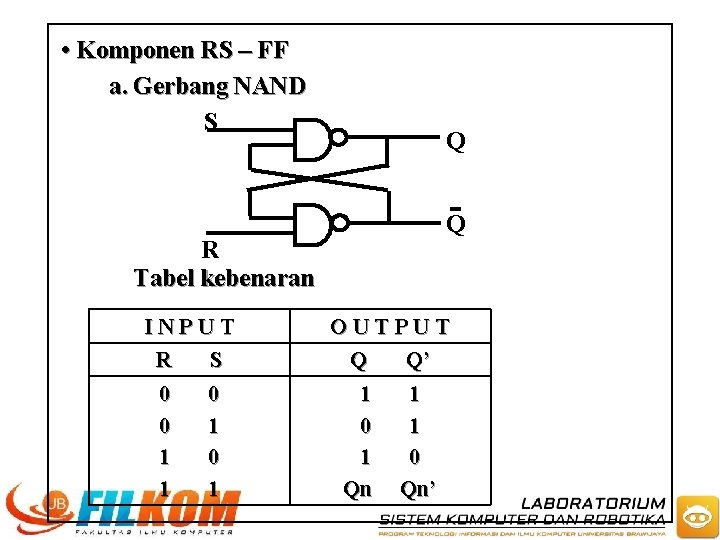

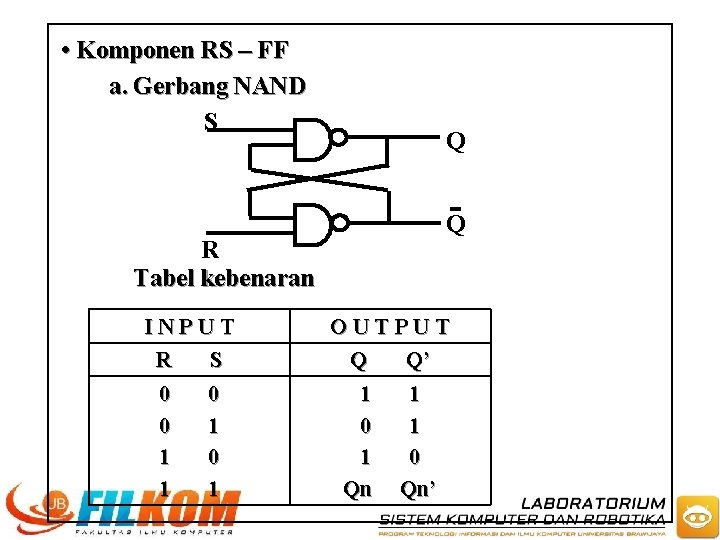

• Komponen RS – FF a. Gerbang NAND S Q Q R Tabel kebenaran INPUT R S 0 0 1 1 0 1 OUTPUT Q Q’ 1 0 1 Qn 1 1 0 Qn’

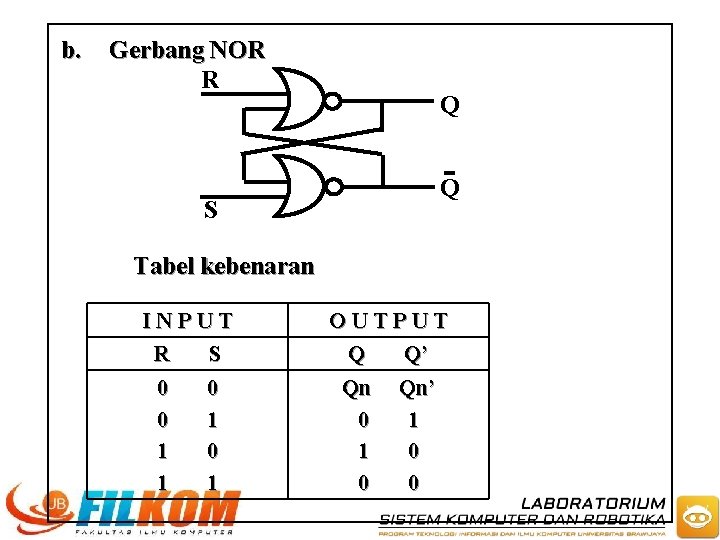

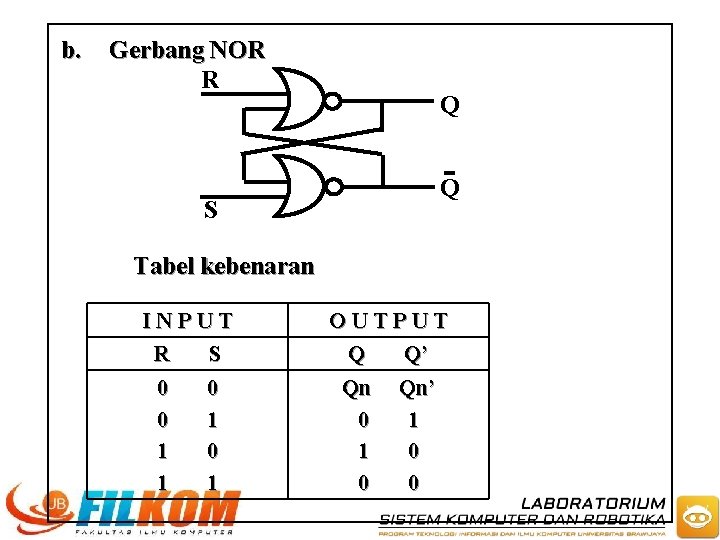

b. Gerbang NOR R Q Q S Tabel kebenaran INPUT R S 0 0 1 1 0 1 OUTPUT Q Q’ Qn 0 1 0 Qn’ 1 0 0

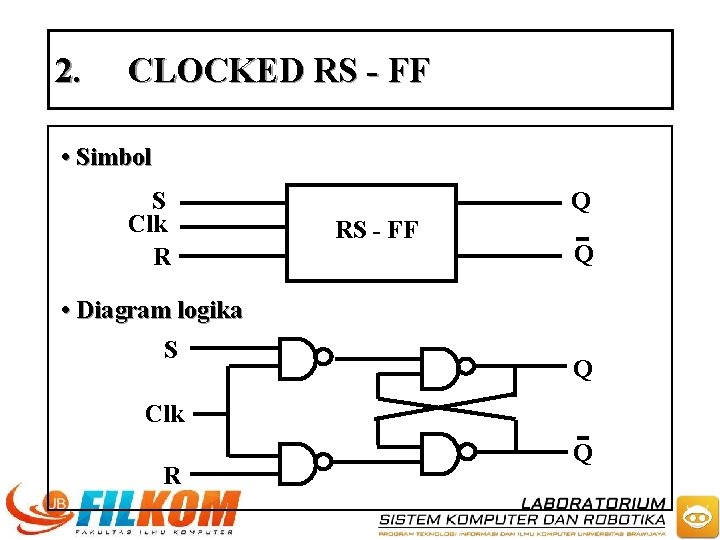

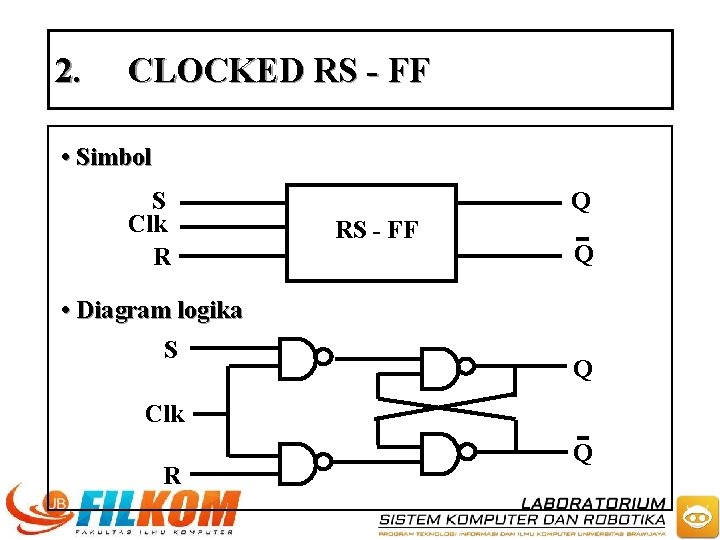

2. CLOCKED RS - FF • Simbol S Clk R Q RS - FF Q • Diagram logika S Q Clk R Q

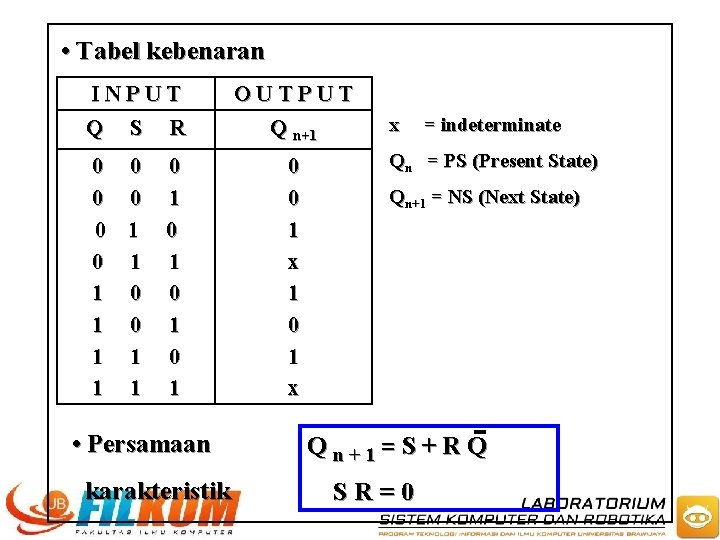

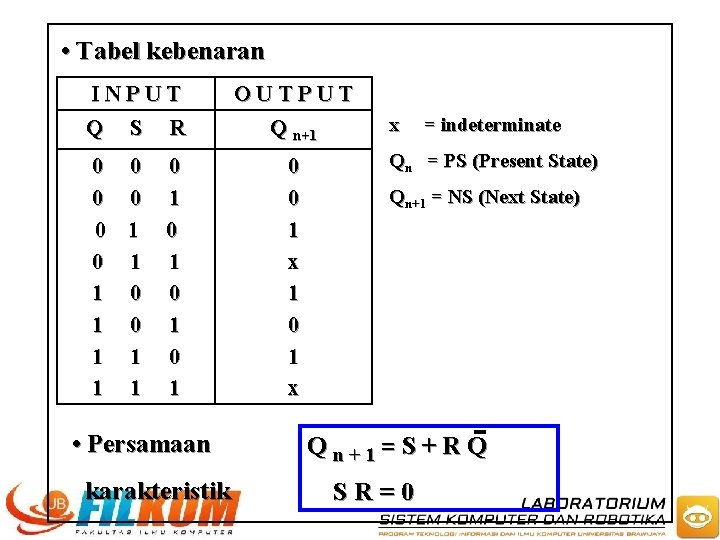

• Tabel kebenaran INPUT Q S R 0 0 0 1 0 1 1 1 1 0 1 0 1 • Persamaan karakteristik OUTPUT Q n+1 0 0 1 x 1 0 1 x x = indeterminate Qn = PS (Present State) Qn+1 = NS (Next State) Qn+1=S+RQ SR=0

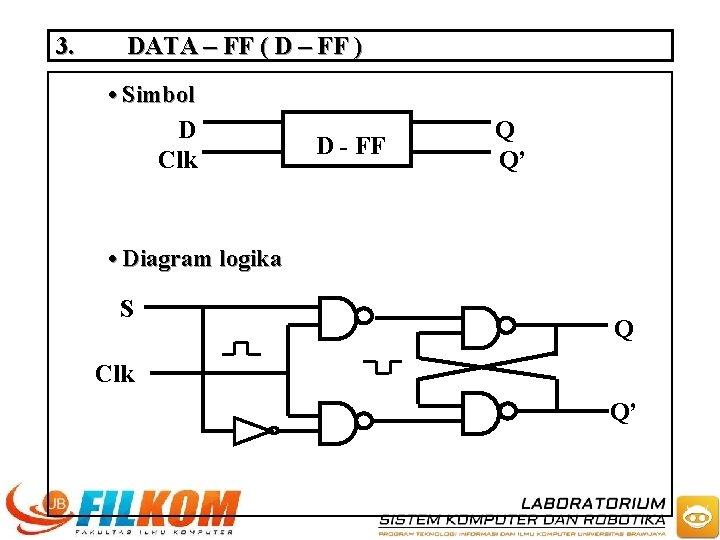

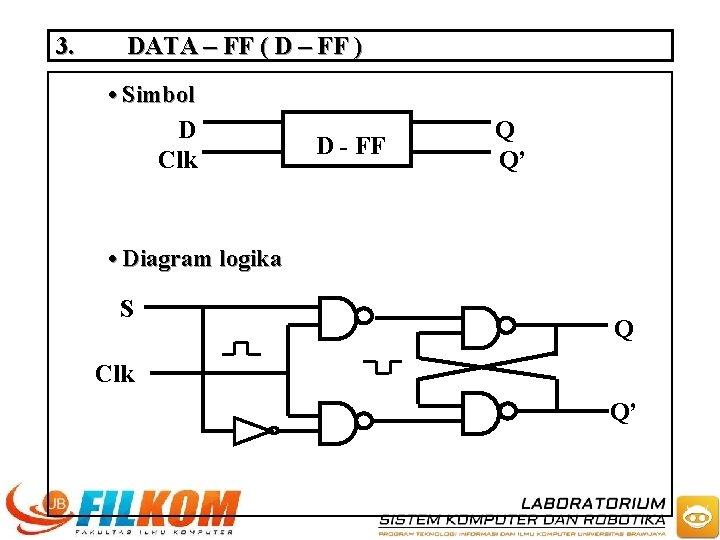

3. DATA – FF ( D – FF ) • Simbol D Clk D - FF Q Q’ • Diagram logika S Q Clk Q’

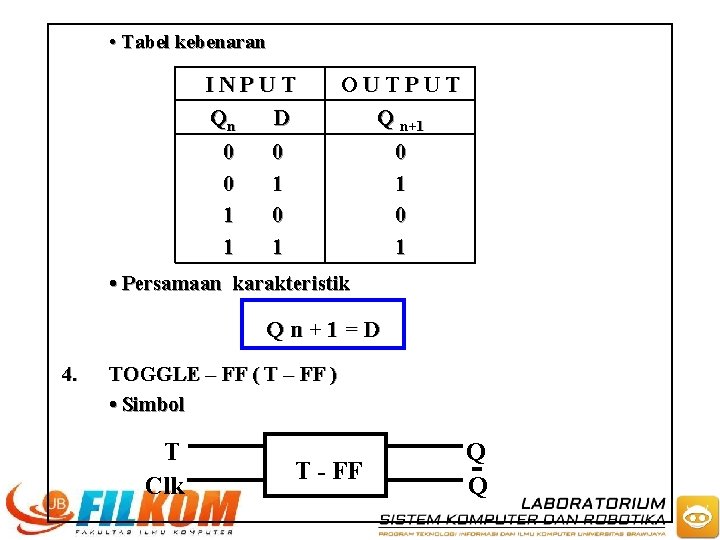

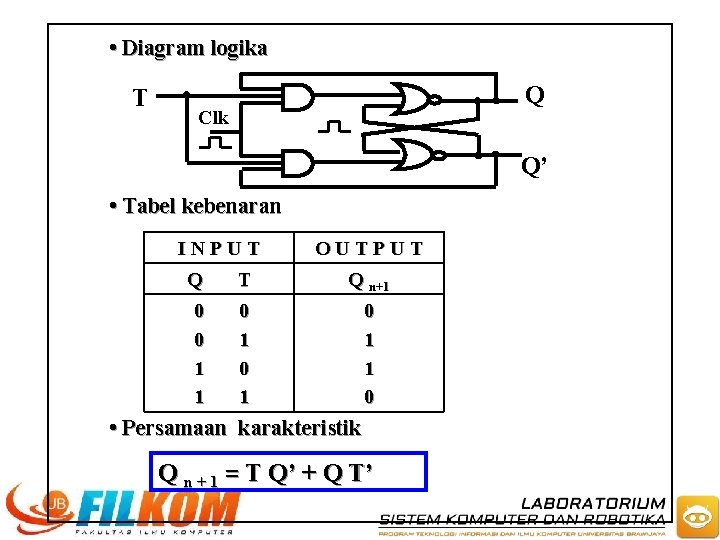

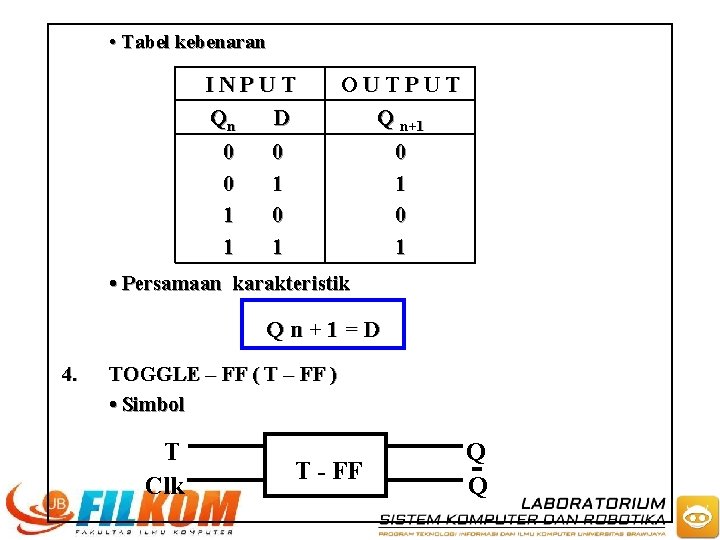

• Tabel kebenaran INPUT Qn D 0 0 1 1 OUTPUT Q n+1 0 1 0 1 • Persamaan karakteristik Qn+1=D 4. TOGGLE – FF ( T – FF ) • Simbol T Clk T - FF Q Q

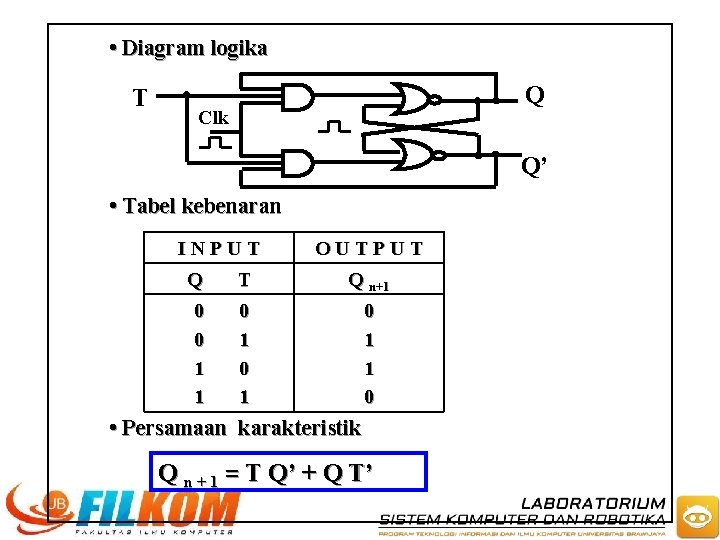

• Diagram logika T Q Clk Q’ • Tabel kebenaran INPUT OUTPUT Q n+1 0 0 1 1 0 1 0 1 1 0 • Persamaan karakteristik Q n + 1 = T Q’ + Q T’

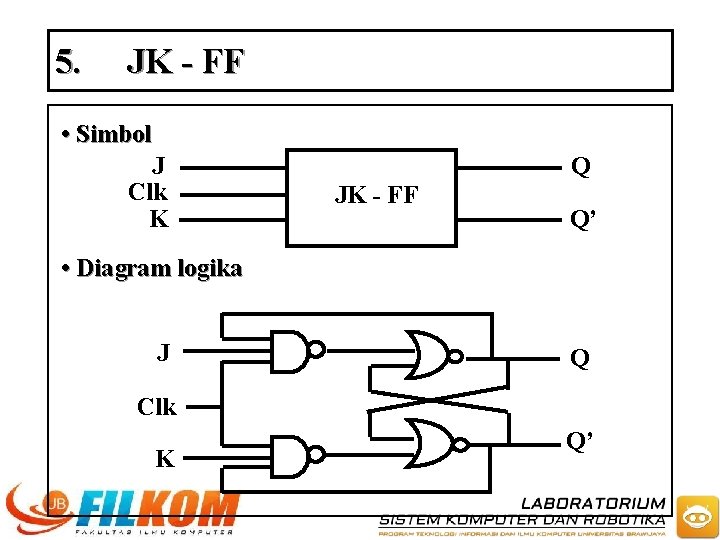

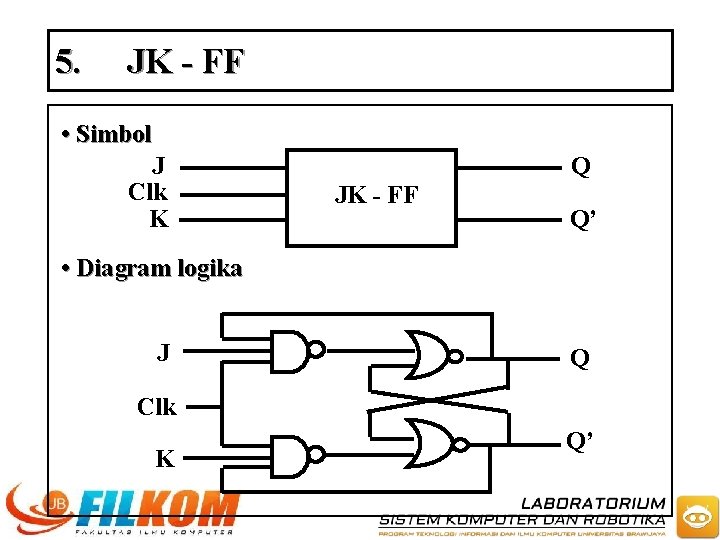

5. JK - FF • Simbol J Clk K Q JK - FF Q’ • Diagram logika J Q Clk K Q’

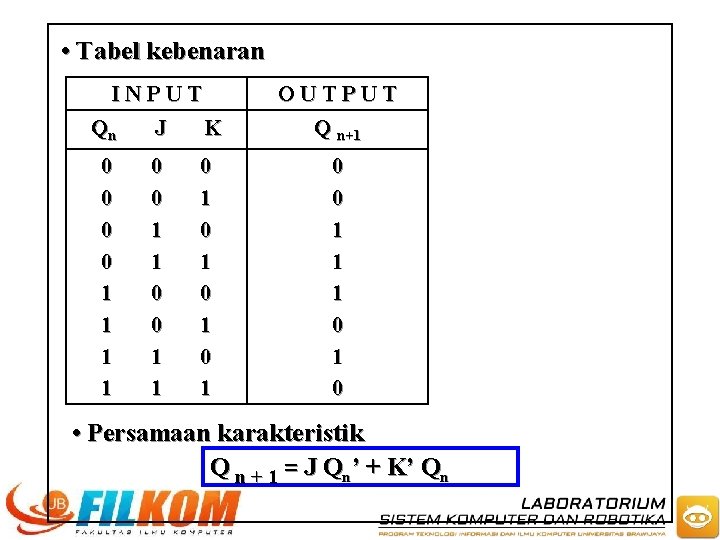

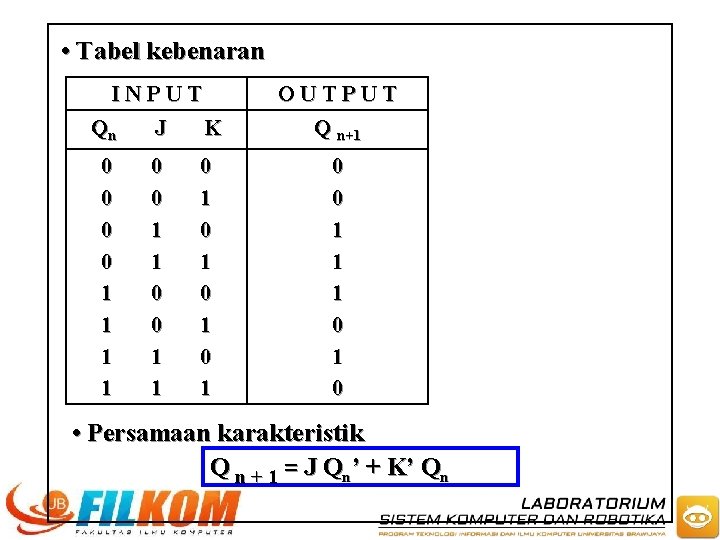

• Tabel kebenaran INPUT Qn J K 0 0 1 1 0 1 0 1 OUTPUT Q n+1 0 0 1 1 1 0 • Persamaan karakteristik Q n + 1 = J Qn’ + K’ Qn

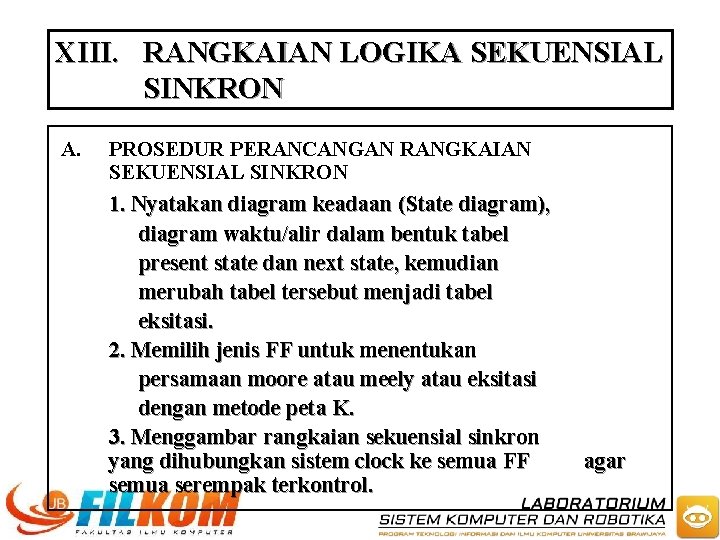

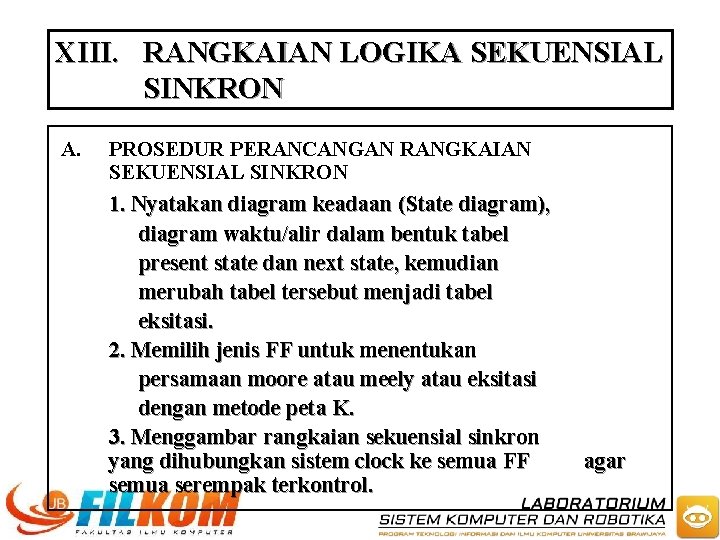

XIII. RANGKAIAN LOGIKA SEKUENSIAL SINKRON A. PROSEDUR PERANCANGAN RANGKAIAN SEKUENSIAL SINKRON 1. Nyatakan diagram keadaan (State diagram), diagram waktu/alir dalam bentuk tabel present state dan next state, kemudian merubah tabel tersebut menjadi tabel eksitasi. 2. Memilih jenis FF untuk menentukan persamaan moore atau meely atau eksitasi dengan metode peta K. 3. Menggambar rangkaian sekuensial sinkron yang dihubungkan sistem clock ke semua FF semua serempak terkontrol. agar

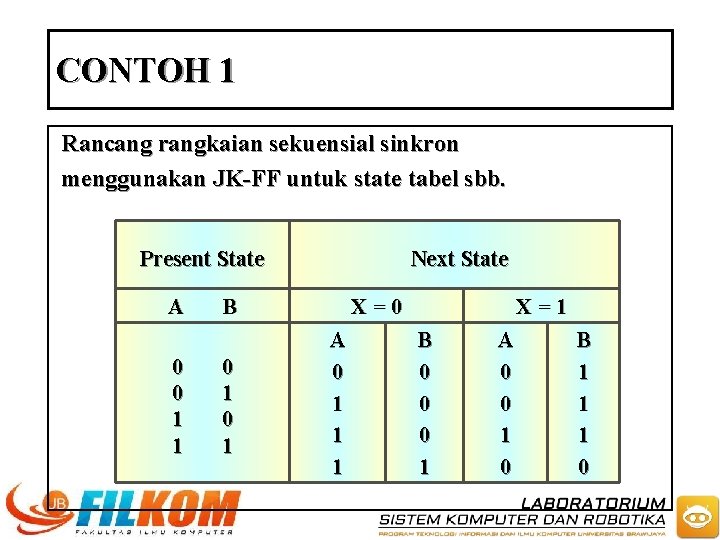

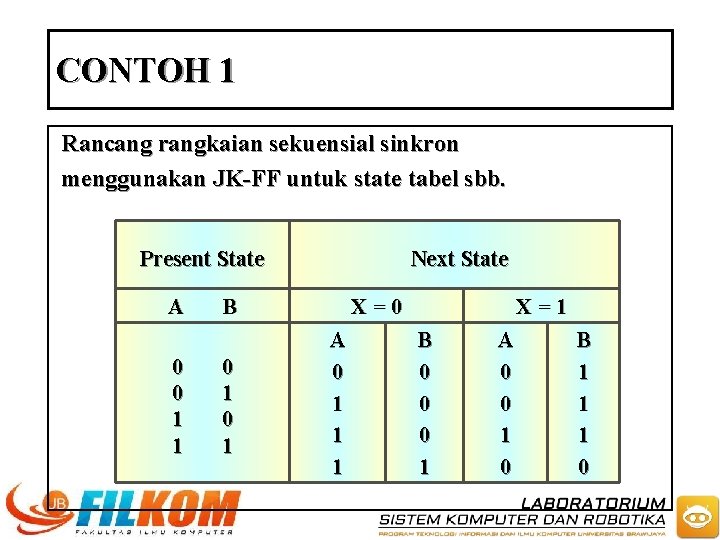

CONTOH 1 Rancang rangkaian sekuensial sinkron menggunakan JK-FF untuk state tabel sbb. Present State A 0 0 1 1 Next State B 0 1 X=0 A 0 1 1 1 X=1 B 0 0 0 1 A 0 0 1 0 B 1 1 1 0

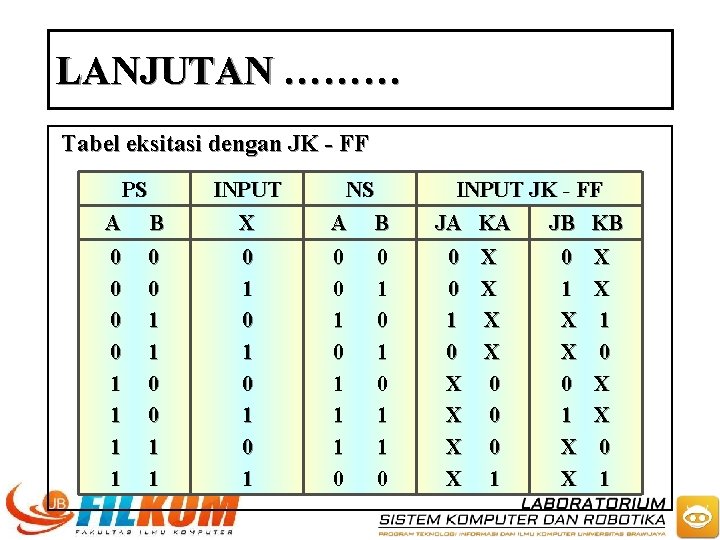

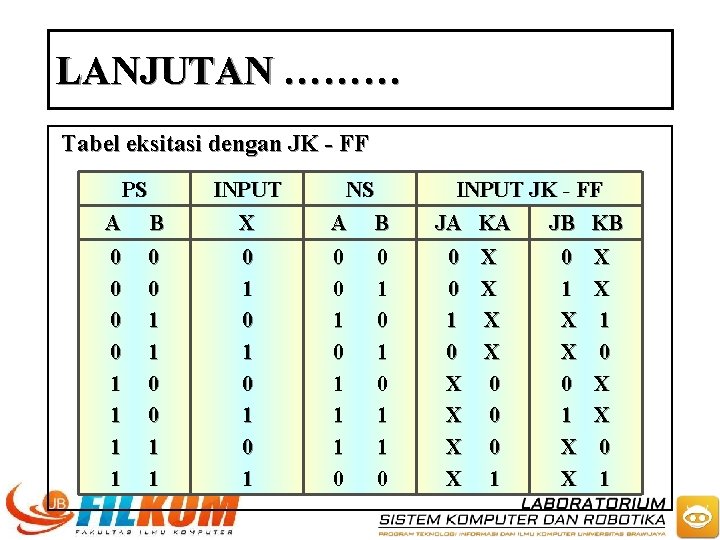

LANJUTAN ……… Tabel eksitasi dengan JK - FF PS A 0 0 1 1 B 0 0 1 1 INPUT X 0 1 0 1 NS A B 0 0 1 1 1 0 0 1 0 1 1 0 INPUT JK - FF JA KA JB KB 0 0 1 0 X X X X 0 0 0 1 X X 1 0 X X 0 1

Lanjutan ……. . Persamaan karakteristik JA = BX’ JB = X KA = BX KB = A’X’ + AX = A xnor X Gambar rangkaian logika B’ A A’ B Q K A Q J Q K B Q J CLK X

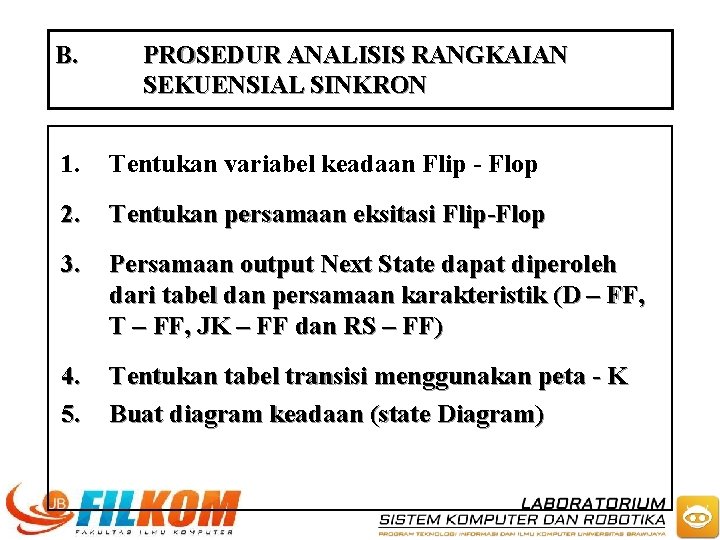

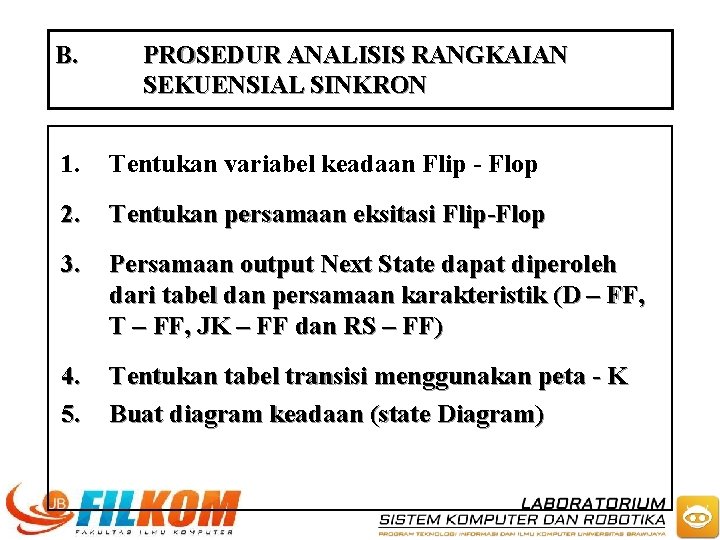

B. PROSEDUR ANALISIS RANGKAIAN SEKUENSIAL SINKRON 1. Tentukan variabel keadaan Flip - Flop 2. Tentukan persamaan eksitasi Flip-Flop 3. Persamaan output Next State dapat diperoleh dari tabel dan persamaan karakteristik (D – FF, T – FF, JK – FF dan RS – FF) 4. 5. Tentukan tabel transisi menggunakan peta - K Buat diagram keadaan (state Diagram)

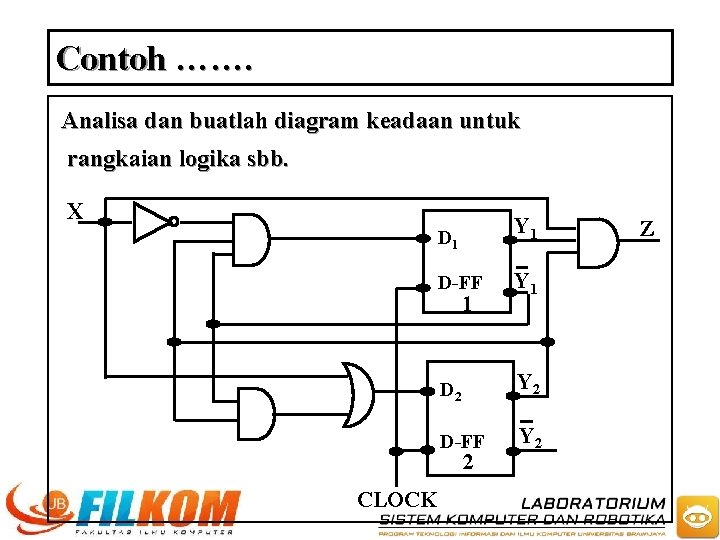

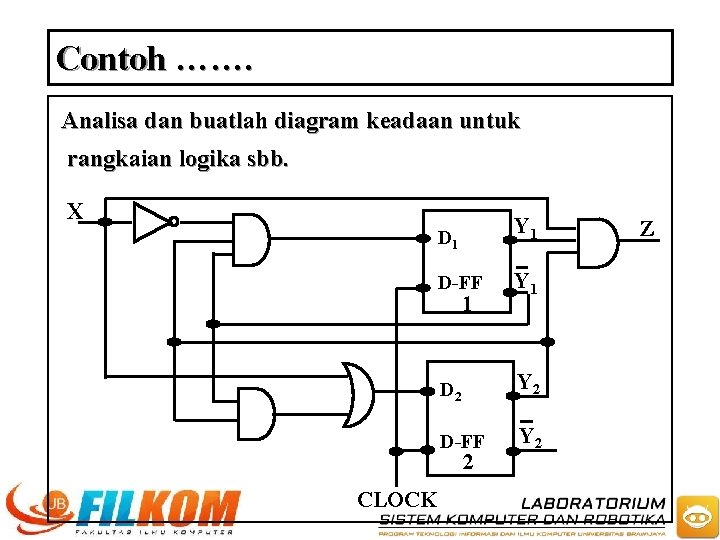

Contoh ……. Analisa dan buatlah diagram keadaan untuk rangkaian logika sbb. X D 1 Y 1 D-FF Y 1 D 2 Y 2 D-FF Y 2 1 2 CLOCK Z

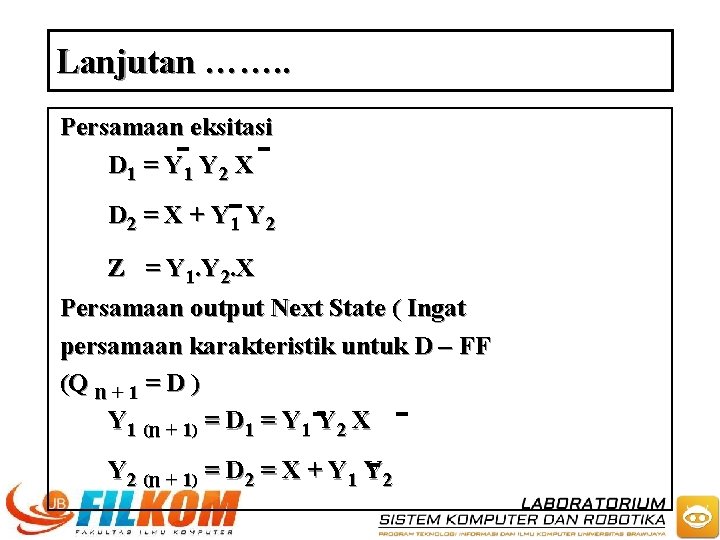

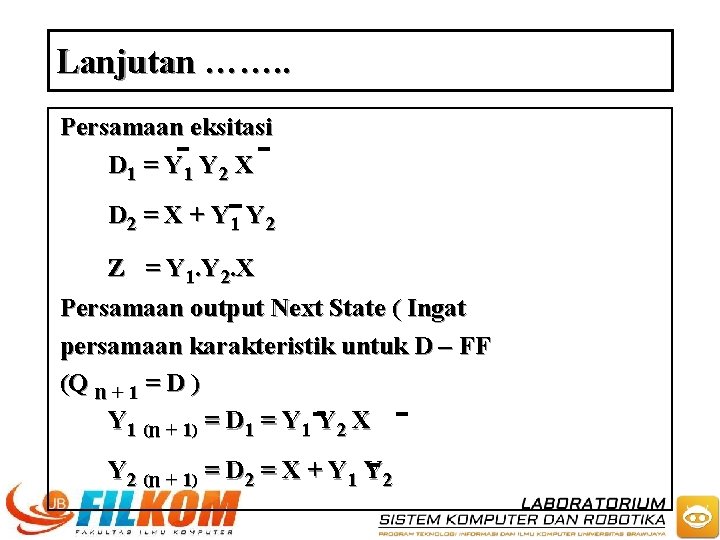

Lanjutan ……. . Persamaan eksitasi D 1 = Y 1 Y 2 X D 2 = X + Y 1 Y 2 Z = Y 1. Y 2. X Persamaan output Next State ( Ingat persamaan karakteristik untuk D – FF (Q n + 1 = D ) Y 1 (n + 1 ) = D 1 = Y 1 Y 2 X Y 2 (n + 1 ) = D 2 = X + Y 1 Y 2

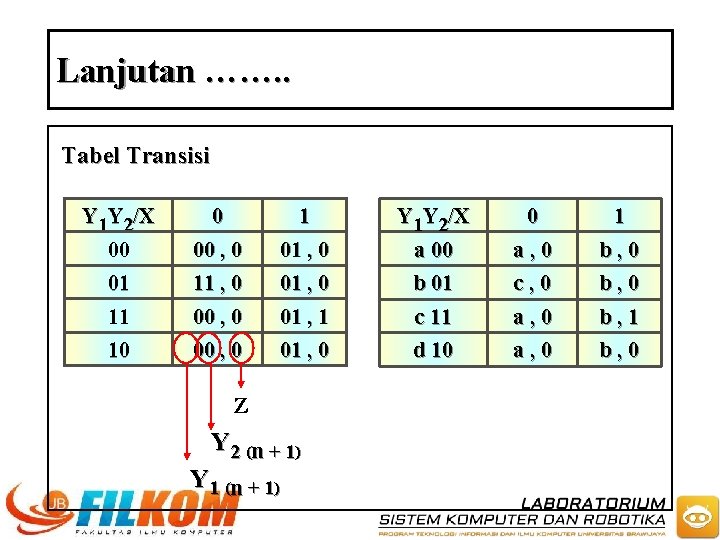

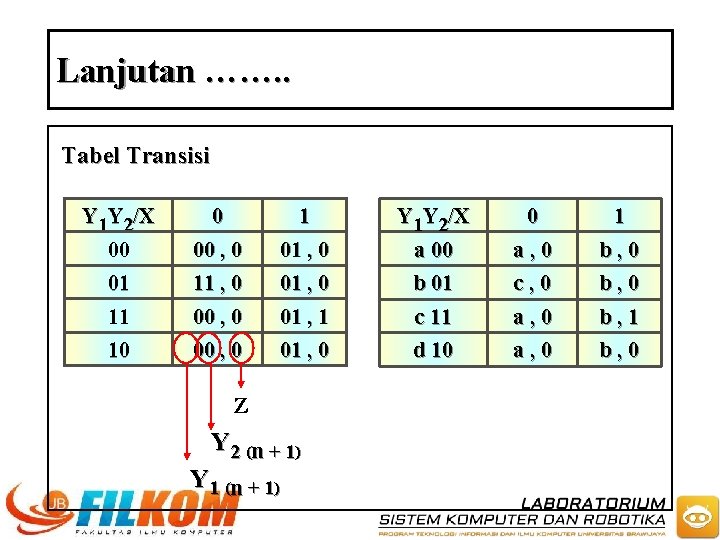

Lanjutan ……. . Tabel Transisi Y 1 Y 2/X 00 0 00 , 0 1 01 , 0 Y 1 Y 2/X a 00 0 a, 0 1 b, 0 01 11 11 , 0 00 , 0 01 , 1 b 01 c 11 c, 0 a, 0 b, 1 10 00 , 0 01 , 0 d 10 a, 0 b, 0 Z Y 2 (n + 1 ) Y 1 (n + 1 )

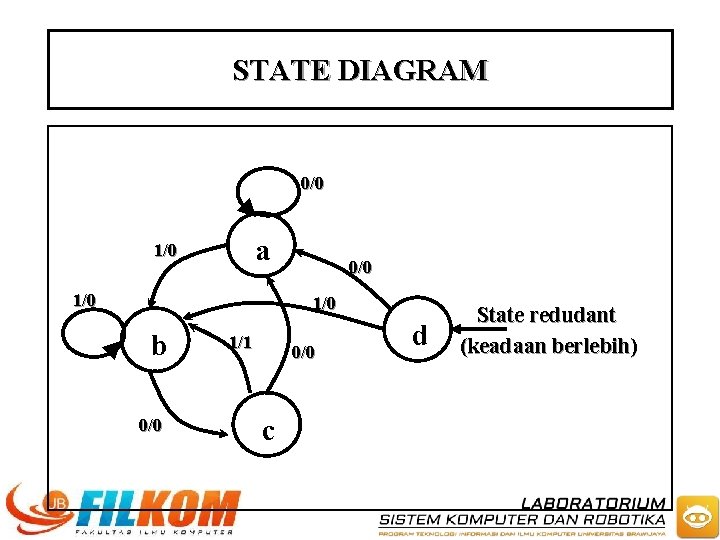

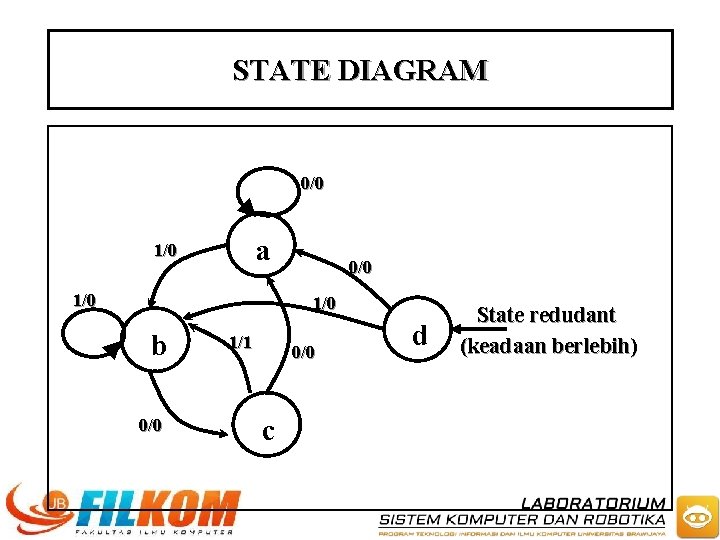

STATE DIAGRAM 0/0 a 1/0 0/0 1/0 b 0/0 1/1 0/0 c d State redudant (keadaan berlebih)

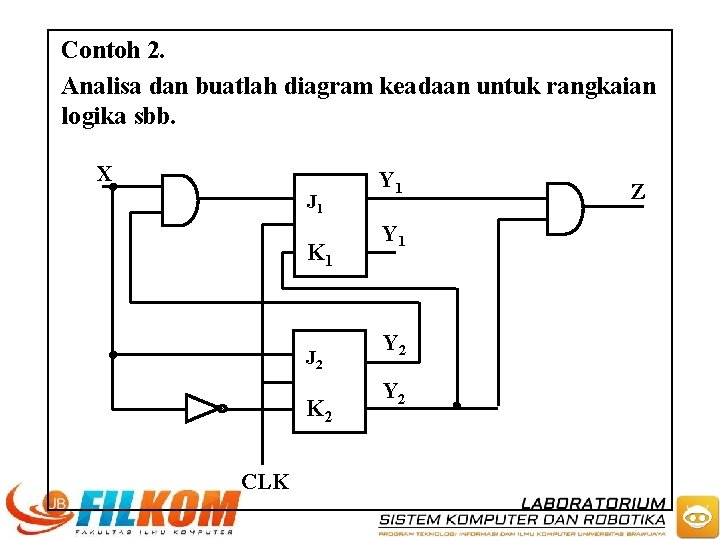

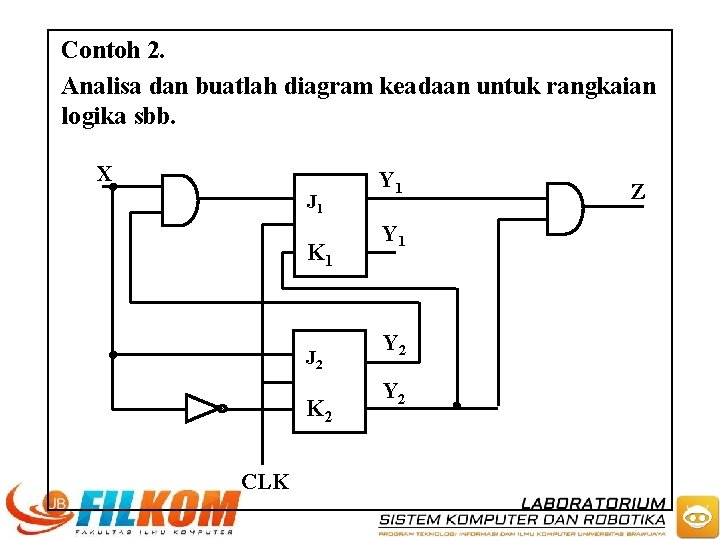

Contoh 2. Analisa dan buatlah diagram keadaan untuk rangkaian logika sbb. X J 1 K 1 J 2 K 2 CLK Y 1 Y 2 Z

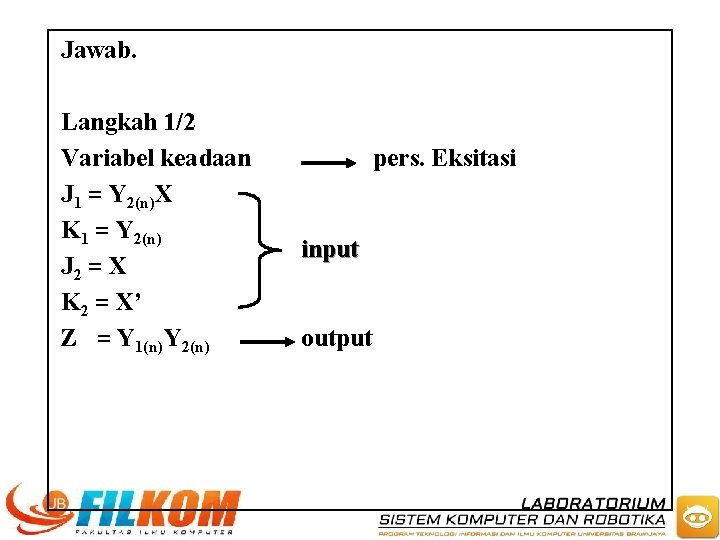

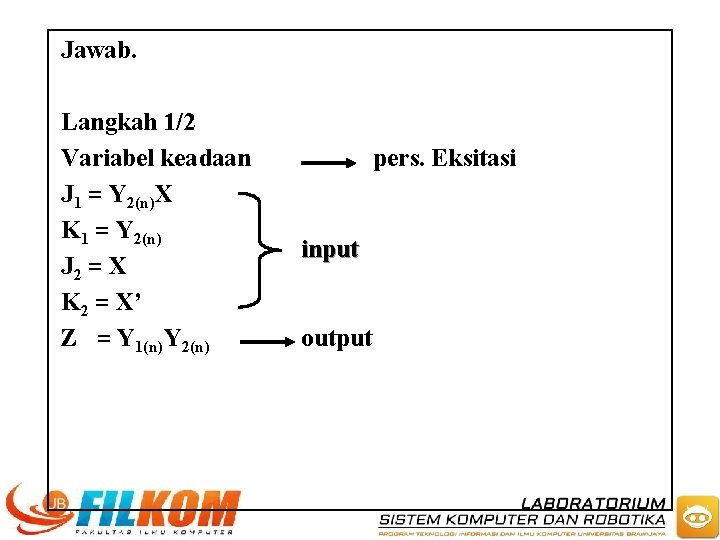

Jawab. Langkah 1/2 Variabel keadaan J 1 = Y 2(n)X K 1 = Y 2(n) J 2 = X K 2 = X’ Z = Y 1(n)Y 2(n) pers. Eksitasi input output

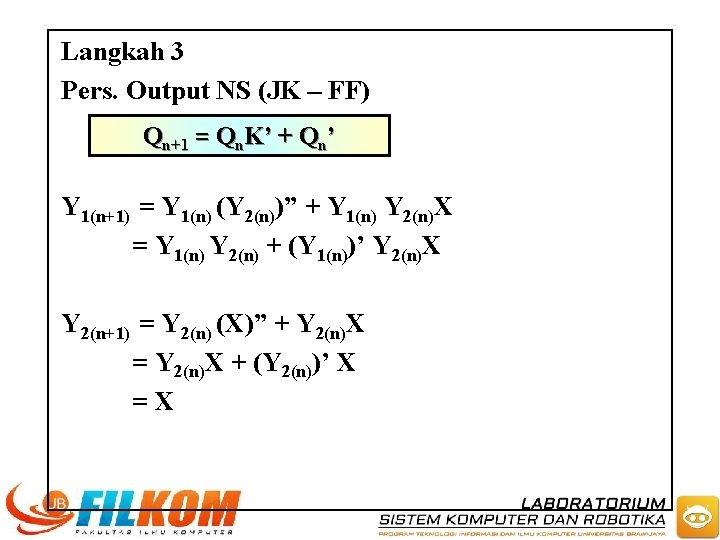

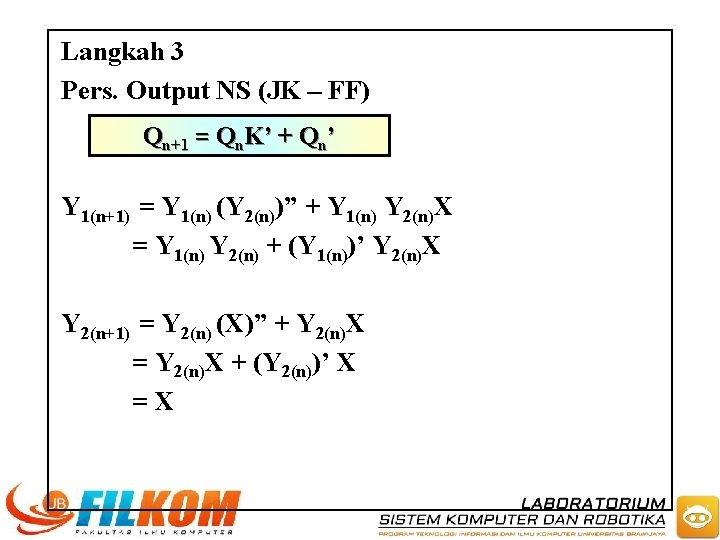

Langkah 3 Pers. Output NS (JK – FF) Qn+1 = Qn. K’ + Qn’ Y 1(n+1) = Y 1(n) (Y 2(n))” + Y 1(n) Y 2(n)X = Y 1(n) Y 2(n) + (Y 1(n))’ Y 2(n)X Y 2(n+1) = Y 2(n) (X)” + Y 2(n)X = Y 2(n)X + (Y 2(n))’ X =X

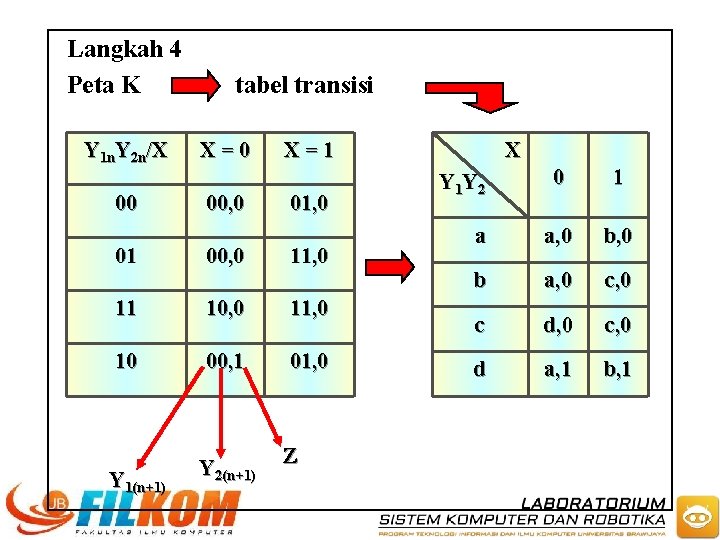

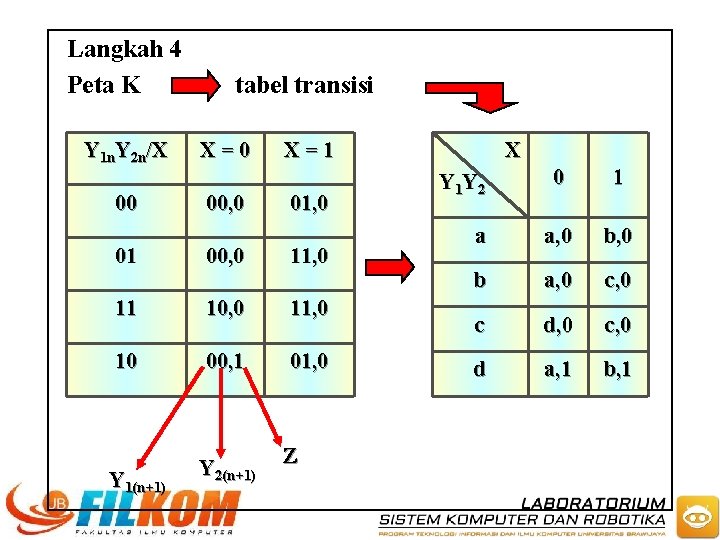

Langkah 4 Peta K Y 1 n. Y 2 n/X 00 tabel transisi X=0 00, 0 X=1 01, 0 01 00, 0 11 10, 0 11, 0 10 00, 1 01, 0 Y 1(n+1) Y 2(n+1) Z X 0 1 a a, 0 b a, 0 c d, 0 c, 0 d a, 1 b, 1 Y 1 Y 2

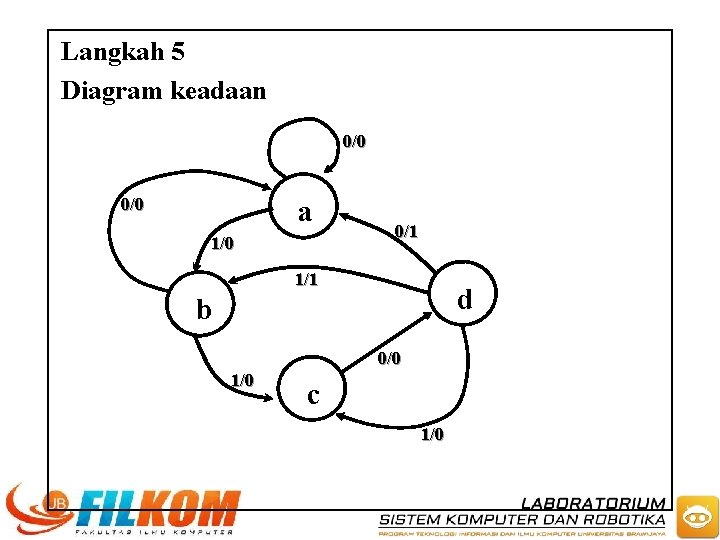

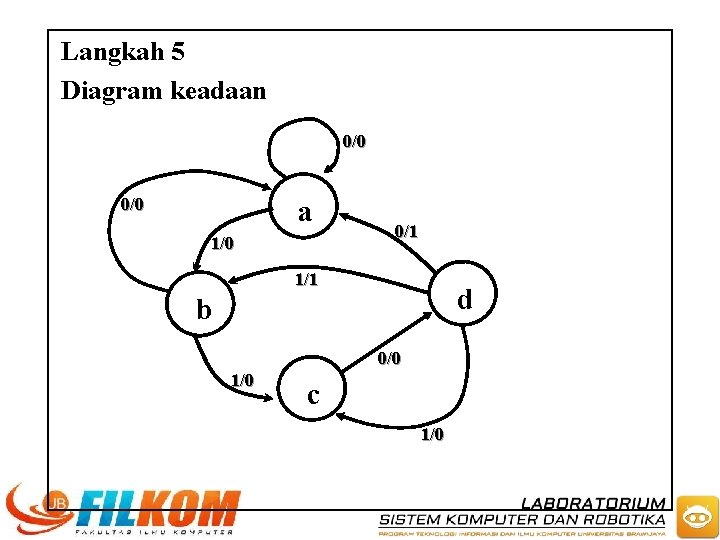

Langkah 5 Diagram keadaan 0/0 a 1/0 0/1 1/1 d b 0/0 1/0 c 1/0

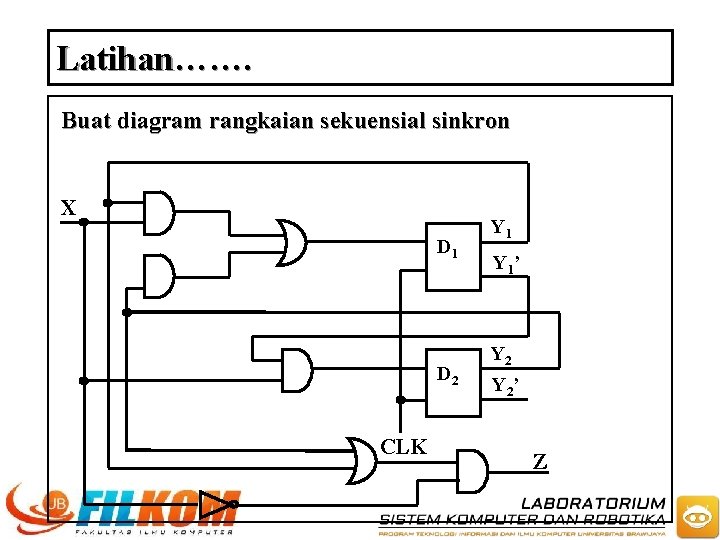

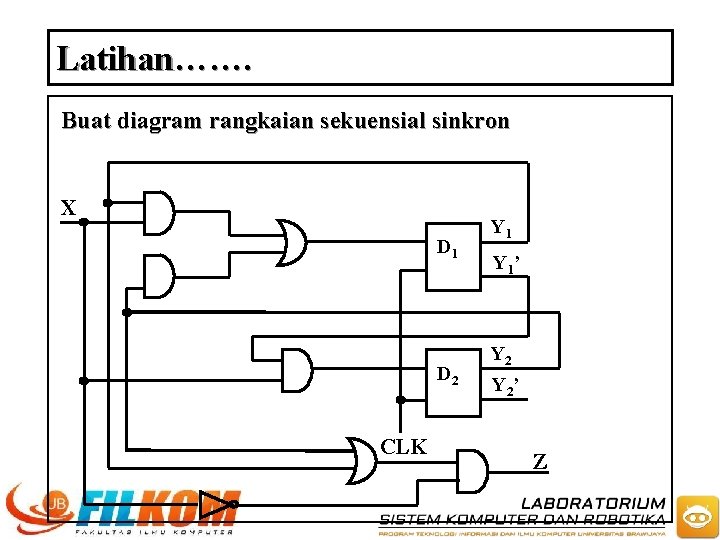

Latihan……. Buat diagram rangkaian sekuensial sinkron X D 1 D 2 CLK Y 1 ’ Y 2 ’ Z

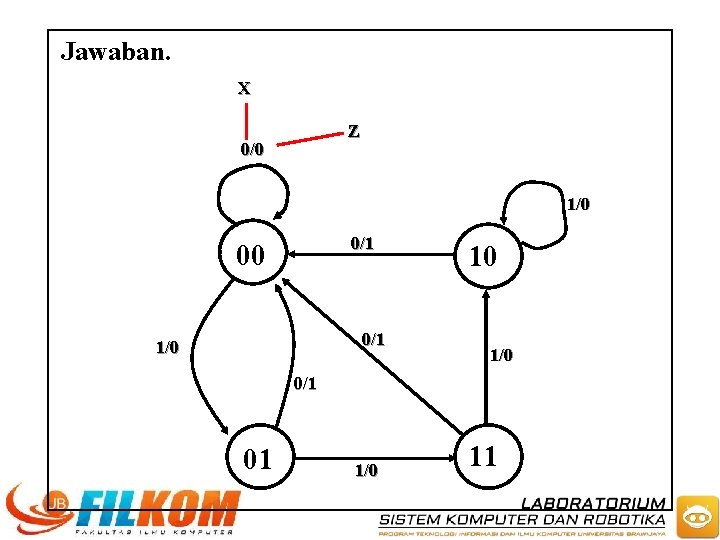

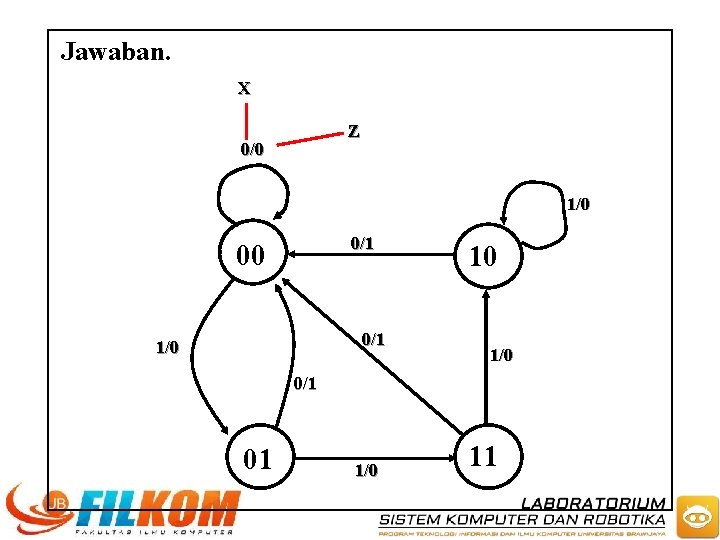

Jawaban. X Z 0/0 1/0 0/1 00 0/1 1/0 10 1/0 0/1 01 1/0 11

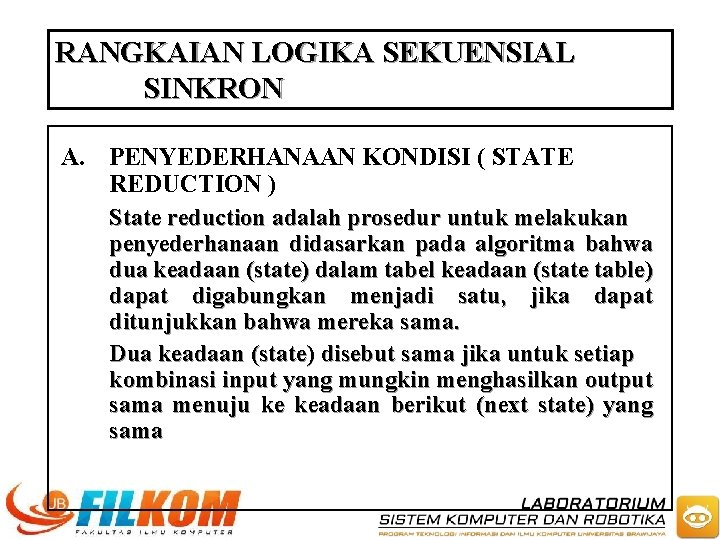

RANGKAIAN LOGIKA SEKUENSIAL SINKRON A. PENYEDERHANAAN KONDISI ( STATE REDUCTION ) State reduction adalah prosedur untuk melakukan penyederhanaan didasarkan pada algoritma bahwa dua keadaan (state) dalam tabel keadaan (state table) dapat digabungkan menjadi satu, jika dapat ditunjukkan bahwa mereka sama. Dua keadaan (state) disebut sama jika untuk setiap kombinasi input yang mungkin menghasilkan output sama menuju ke keadaan berikut (next state) yang sama

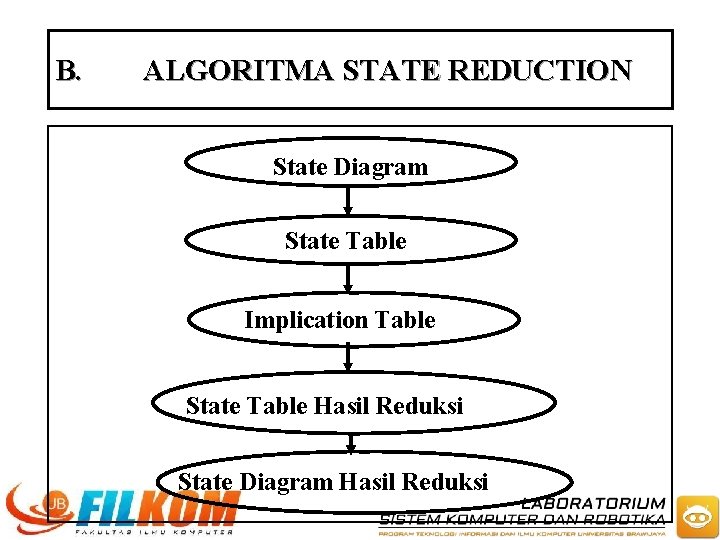

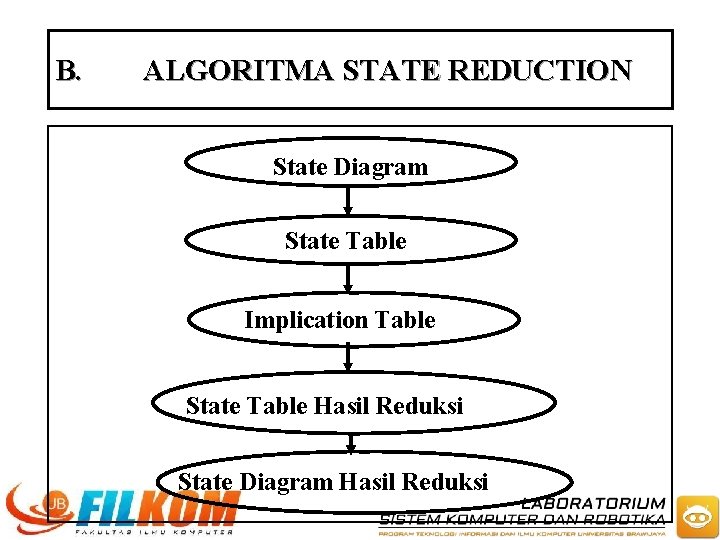

B. ALGORITMA STATE REDUCTION State Diagram State Table Implication Table State Table Hasil Reduksi State Diagram Hasil Reduksi

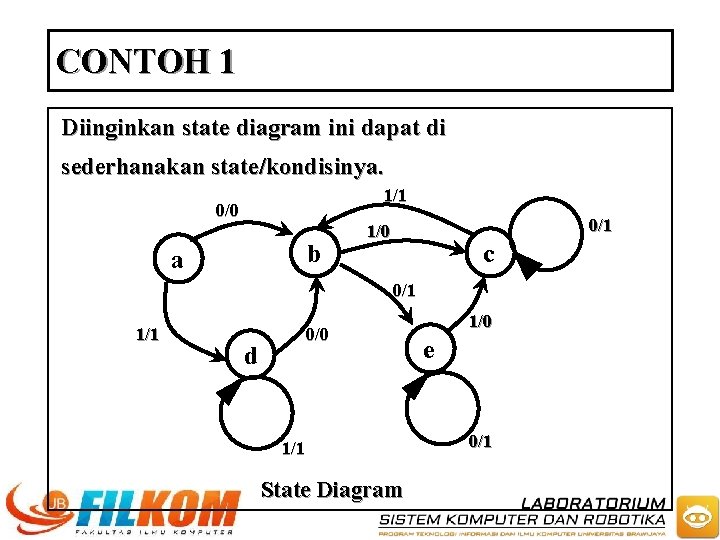

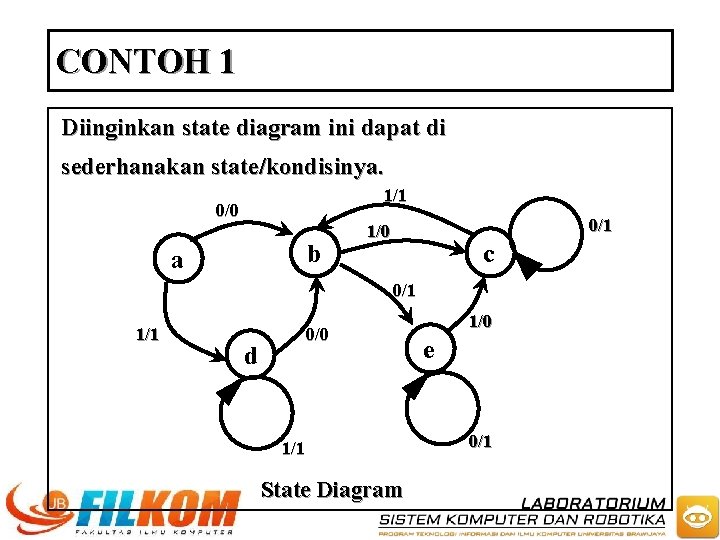

CONTOH 1 Diinginkan state diagram ini dapat di sederhanakan state/kondisinya. 1/1 0/0 b a 0/1 1/0 c 0/1 1/1 0/0 d 1/1 State Diagram 1/0 e 0/1

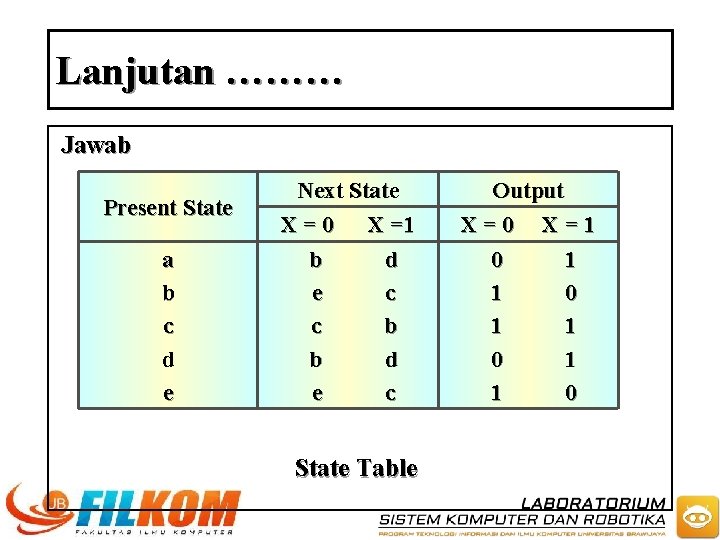

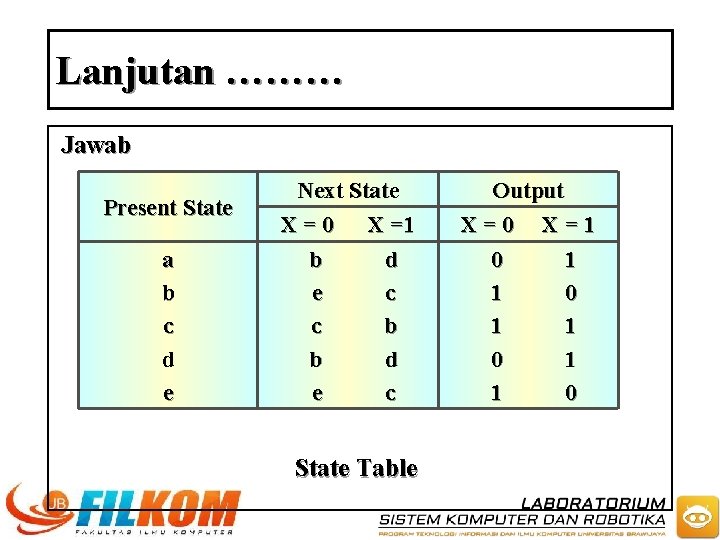

Lanjutan ……… Jawab Present State a b c d e Next State X=0 X =1 b e c b e d c b d c State Table Output X=0 X=1 0 1 1 0

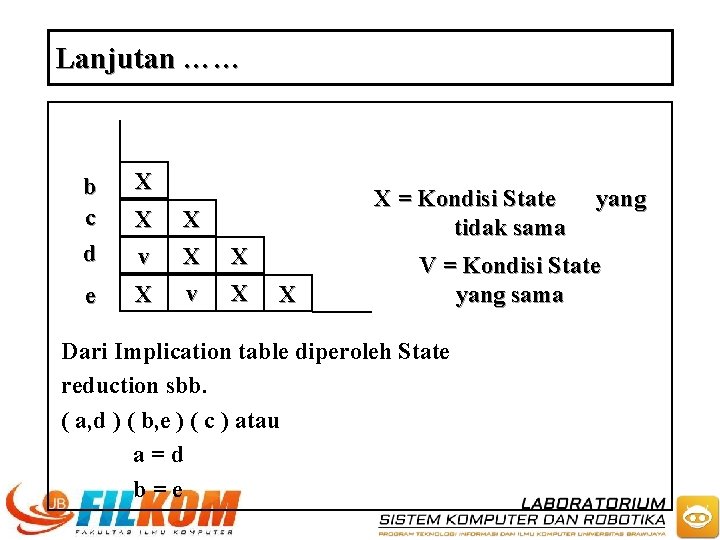

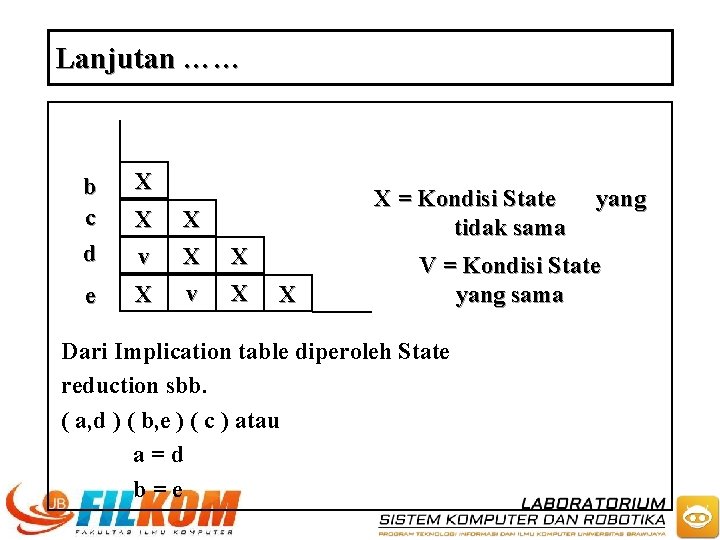

Lanjutan …… b c d X e X = Kondisi State tidak sama X X v X X yang V = Kondisi State yang sama Dari Implication table diperoleh State reduction sbb. ( a, d ) ( b, e ) ( c ) atau a=d b=e

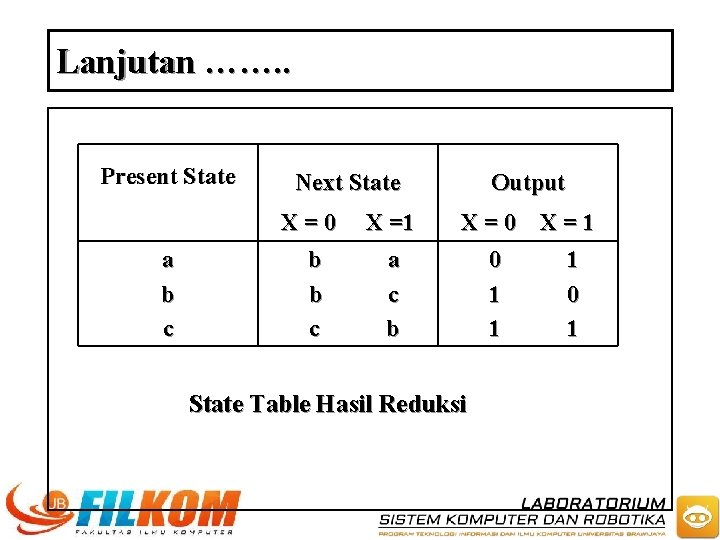

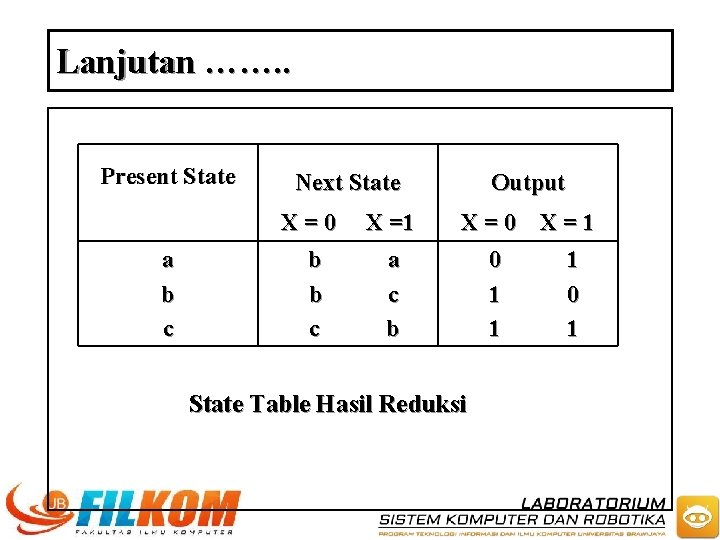

Lanjutan ……. . Present State a b c Next State X=0 X =1 b b c a c b Output X=0 X=1 State Table Hasil Reduksi 0 1 1 1 0 1

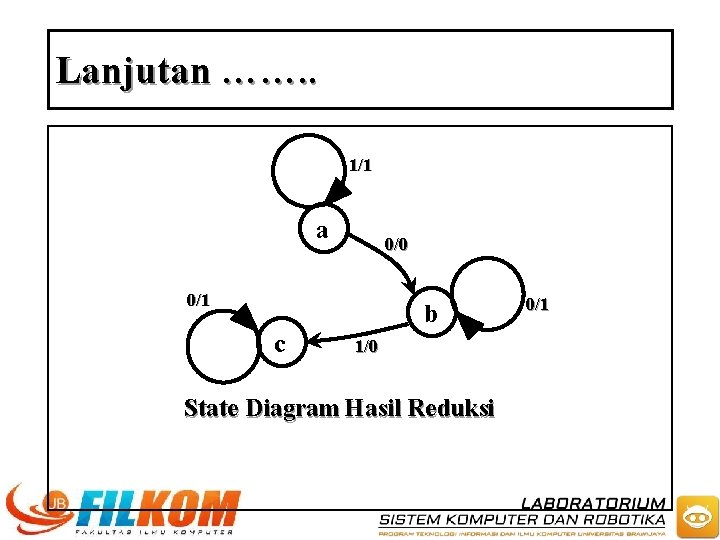

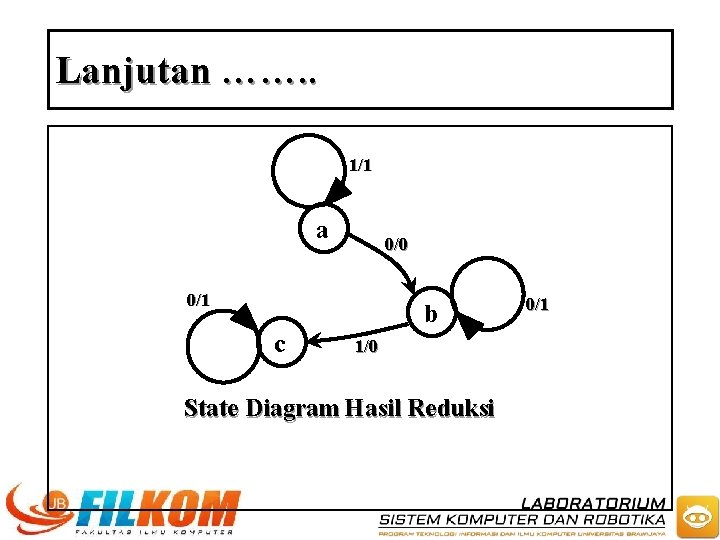

Lanjutan ……. . 1/1 a 0/0 0/1 b c 1/0 State Diagram Hasil Reduksi 0/1