Self Repairing and Self Calibration A DesignTest Strategy

Self Repairing and Self Calibration: A Design/Test Strategy for Nano scale CMOS Kaushik Roy S. Mukhopadhyay, H. Mahmoodi, A. Raychowdhury, Chris Kim, S. Ghosh, K. Kang School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN

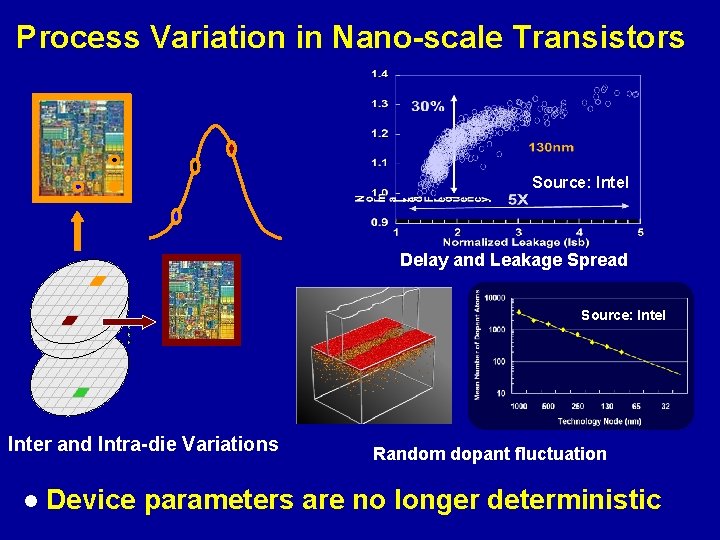

Process Variation in Nano-scale Transistors Source: Intel Delay and Leakage Spread Source: Intel Inter and Intra-die Variations l Random dopant fluctuation Device parameters are no longer deterministic

Process Variations: Failures, Test, Self Calibration, and Self Repair • Memories (Caches and Register Files) – Failure analysis – Updated March Test for process induced failures – Process/Defect tolerant caches – Self Repairing SRAM’s – Leakage and delay sensors for self repair • Logic – Failure analysis in pipelines and robust pipeline design – Delay sensor to measure critical path delays and integrated test generation for robust segment delay coverage • Updated scan chain logic – FLH and FLS (First level hold and scan flip flops) for low power (dynamic and leakage) and efficient delay testing • Temperature control to prevent thermal runaway during burn in

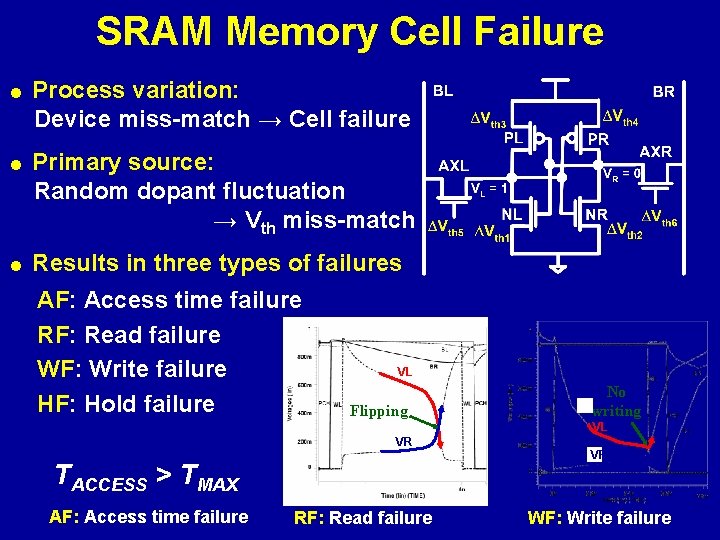

SRAM Memory Cell Failure = Process variation: Device miss-match → Cell failure = Primary source: Random dopant fluctuation → Vth miss-match = Results in three types of failures AF: Access time failure RF: Read failure WF: Write failure HF: Hold failure VL Flipping No writing VL VR VR TACCESS > TMAX AF: Access time failure RF: Read failure WF: Write failure

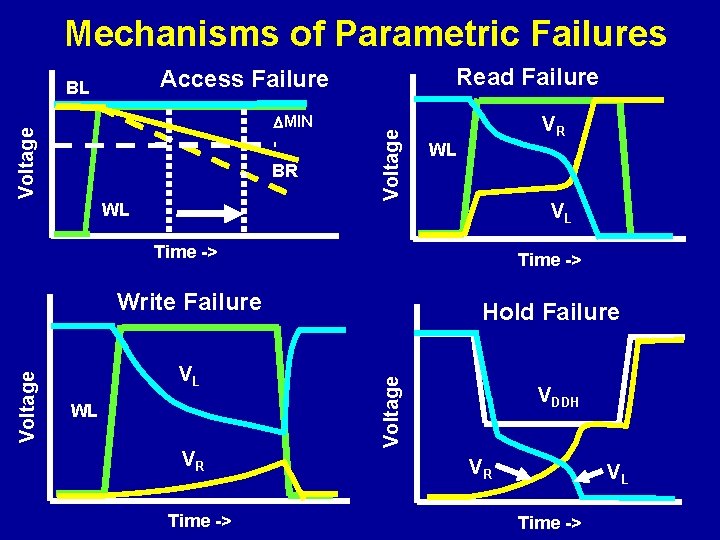

Mechanisms of Parametric Failures BR WL Voltage MIN Voltage Read Failure Access Failure BL VR WL VL Time -> VL WL VR Time -> Hold Failure Voltage Write Failure VDDH VR VL Time ->

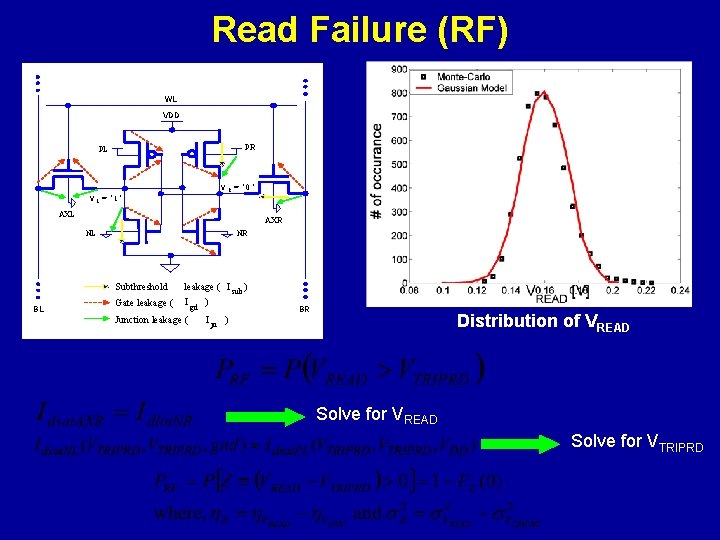

Read Failure (RF) WL VDD PR PL V R = ‘ 0 ’ V L = ‘ 1 ’ AXL AXR NL BL NR Subthreshold leakage ( I sub ) Gate leakage ( I gd ) Junction leakage ( BR Distribution of VREAD I jn ) Solve for VREAD Solve for VTRIPRD

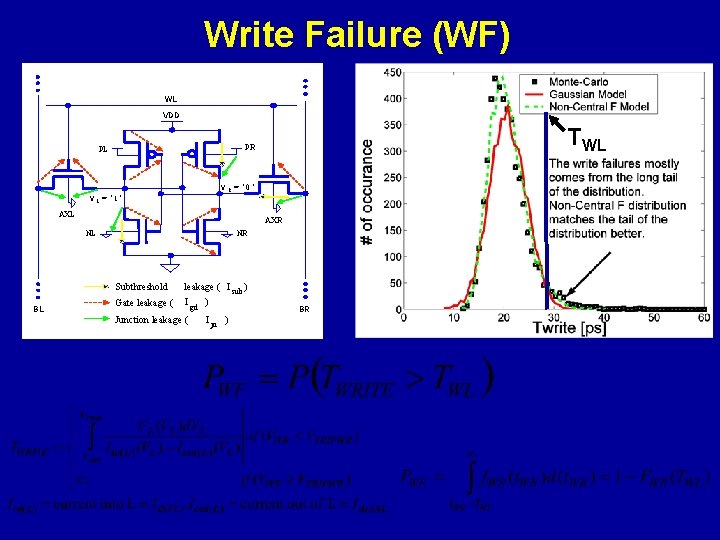

Write Failure (WF) WL VDD TWL PR PL V R = ‘ 0 ’ V L = ‘ 1 ’ AXL AXR NL BL NR Subthreshold leakage ( I sub ) Gate leakage ( I gd ) Junction leakage ( I jn ) BR

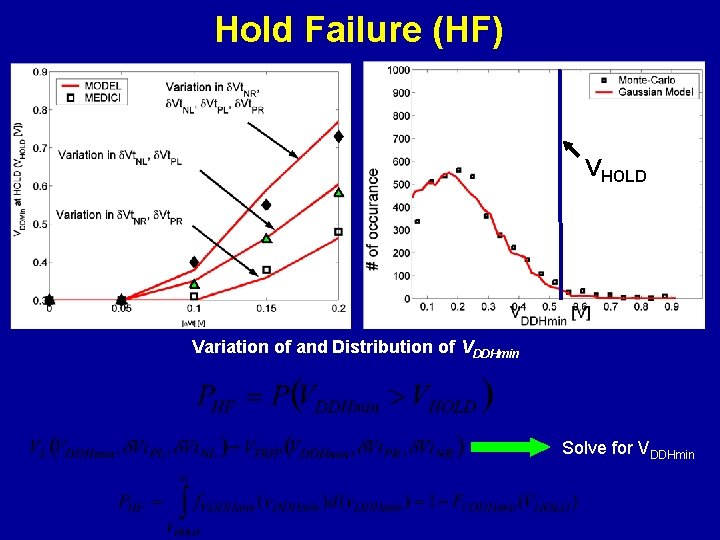

Hold Failure (HF) VHOLD Variation of and Distribution of VDDHmin Solve for VDDHmin

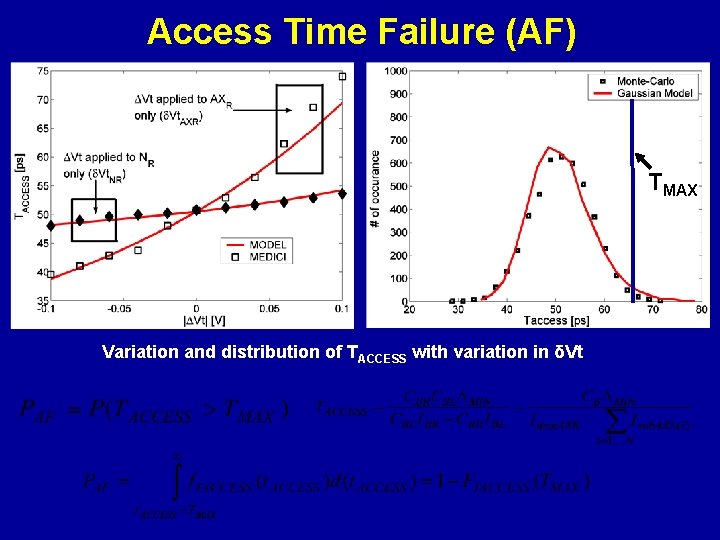

Access Time Failure (AF) Distribution of TACCESS Variation and distribution of TACCESS with variation in δVt TMAX

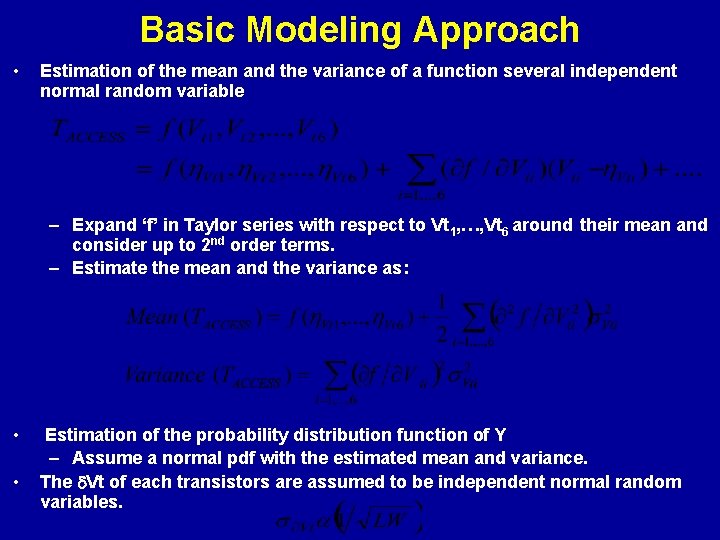

Basic Modeling Approach • Estimation of the mean and the variance of a function several independent normal random variable – Expand ‘f’ in Taylor series with respect to Vt 1, …, Vt 6 around their mean and consider up to 2 nd order terms. – Estimate the mean and the variance as: • • Estimation of the probability distribution function of Y – Assume a normal pdf with the estimated mean and variance. The Vt of each transistors are assumed to be independent normal random variables.

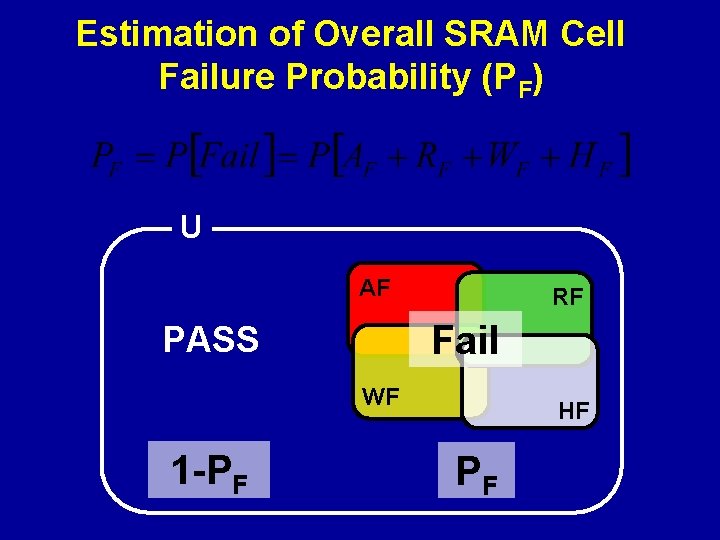

Estimation of Overall SRAM Cell Failure Probability (PF) U AF RF Fail PASS WF 1 -PF HF PF

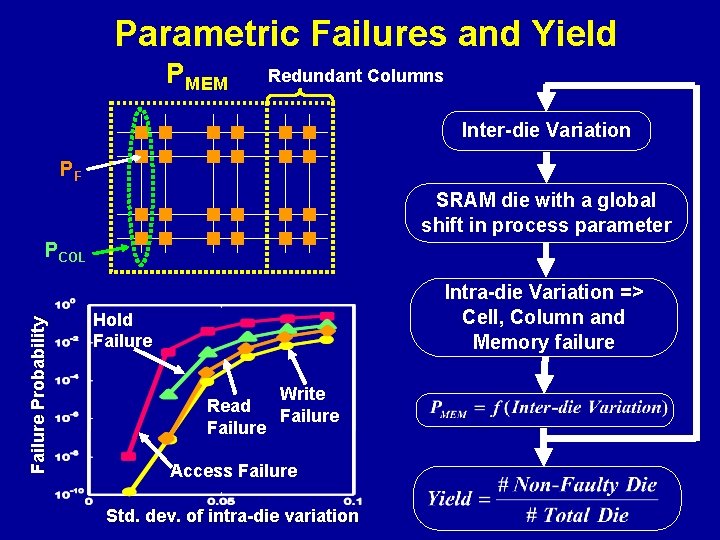

Estimation of Memory Failure Probability (PMEM) • PCOL: Probability that any of the cells in a column fails • PMEM: Probability that more than NRC (# of redundant columns) fail PMEM PF PCOL Redundant Columns

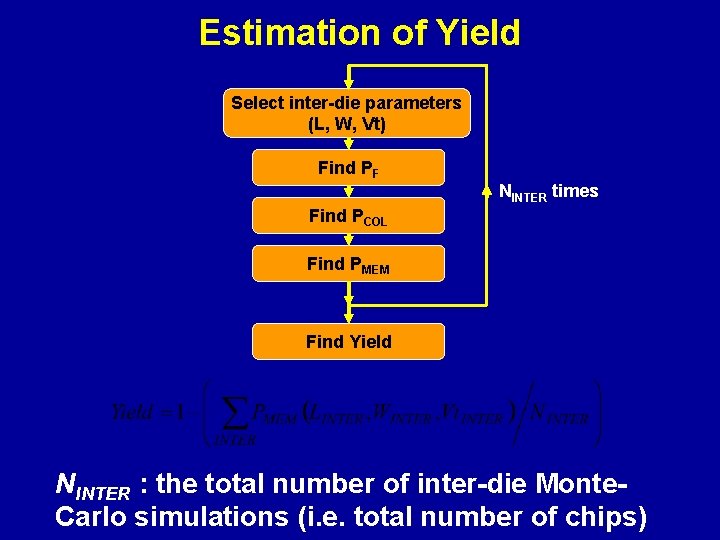

Estimation of Yield Select inter-die parameters (L, W, Vt) Find PF NINTER times Find PCOL Find PMEM Find Yield NINTER : the total number of inter-die Monte. Carlo simulations (i. e. total number of chips)

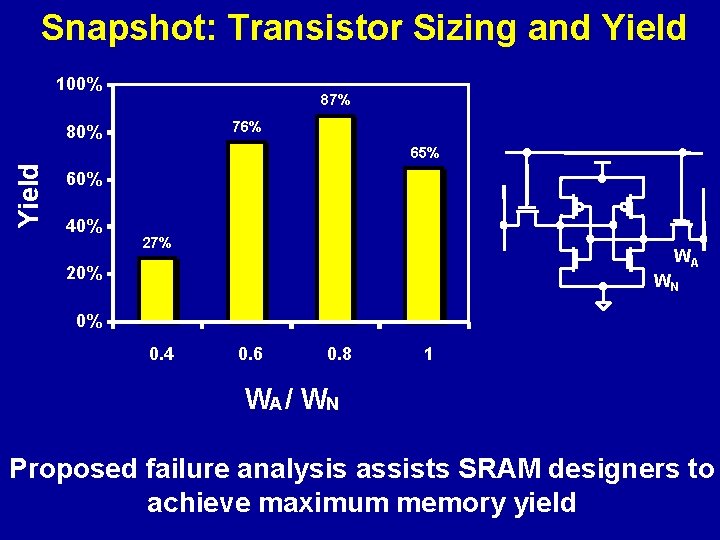

Snapshot: Transistor Sizing and Yield 100% 87% 76% 80% Yield 65% 60% 40% 27% WA 20% WN 0% 0. 4 0. 6 0. 8 1 WA / WN Proposed failure analysis assists SRAM designers to achieve maximum memory yield

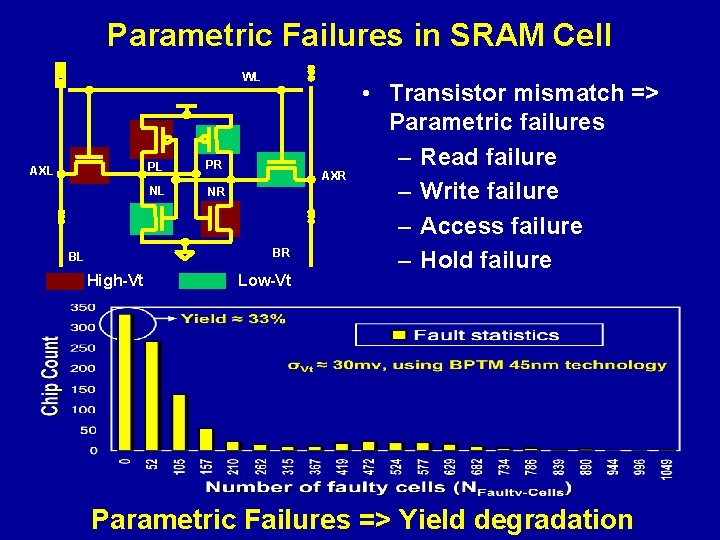

Parametric Failures in SRAM Cell WL AXL PL PR NL NR AXR BR BL High-Vt Low-Vt • Transistor mismatch => Parametric failures – Read failure – Write failure – Access failure – Hold failure Parametric Failures => Yield degradation

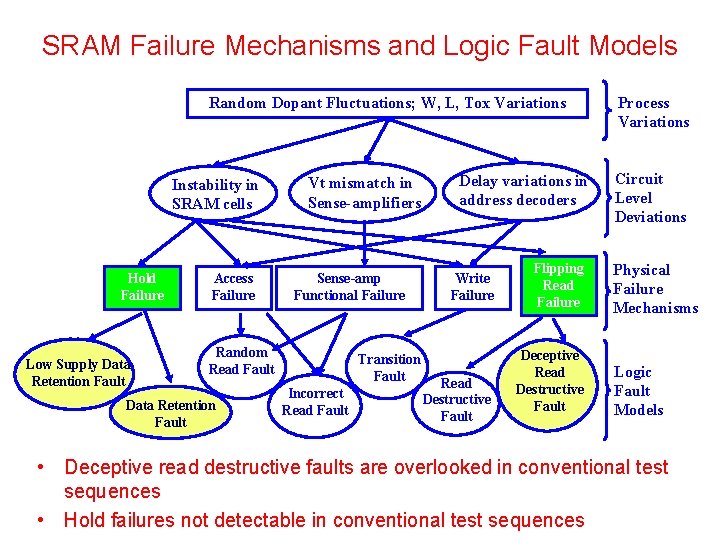

SRAM Failure Mechanisms and Logic Fault Models Random Dopant Fluctuations; W, L, Tox Variations Instability in SRAM cells Hold Failure Low Supply Data Retention Fault Access Failure Vt mismatch in Sense-amplifiers Sense-amp Functional Failure Random Read Fault Data Retention Fault Transition Fault Incorrect Read Fault Delay variations in address decoders Write Failure Read Destructive Fault Flipping Read Failure Deceptive Read Destructive Fault Process Variations Circuit Level Deviations Physical Failure Mechanisms Logic Fault Models • Deceptive read destructive faults are overlooked in conventional test sequences • Hold failures not detectable in conventional test sequences

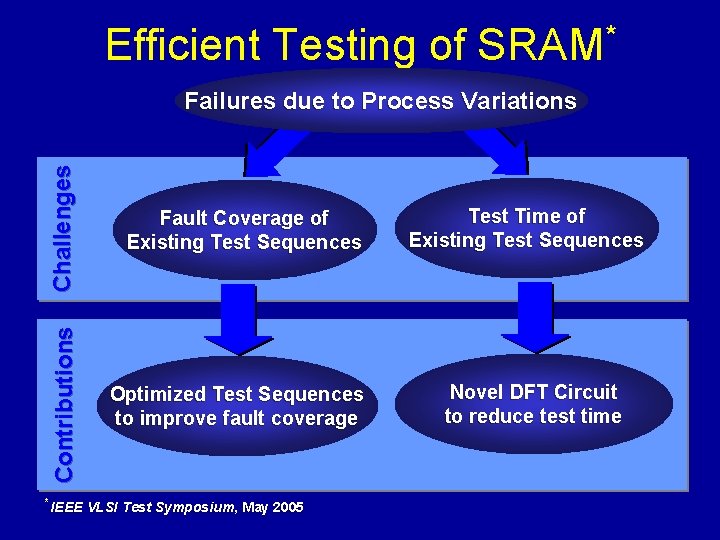

Efficient Testing of SRAM* Challenges Fault Coverage of Existing Test Sequences Contributions Failures due to Process Variations Optimized Test Sequences to improve fault coverage * IEEE VLSI Test Symposium, May 2005 Test Time of Existing Test Sequences Novel DFT Circuit to reduce test time

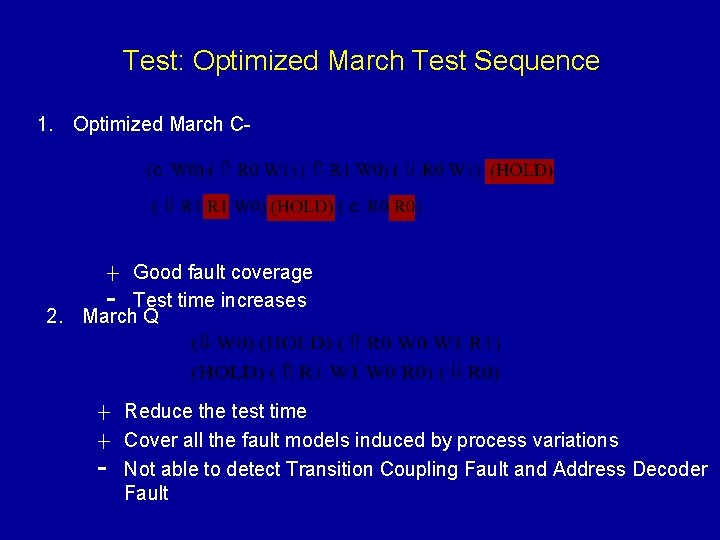

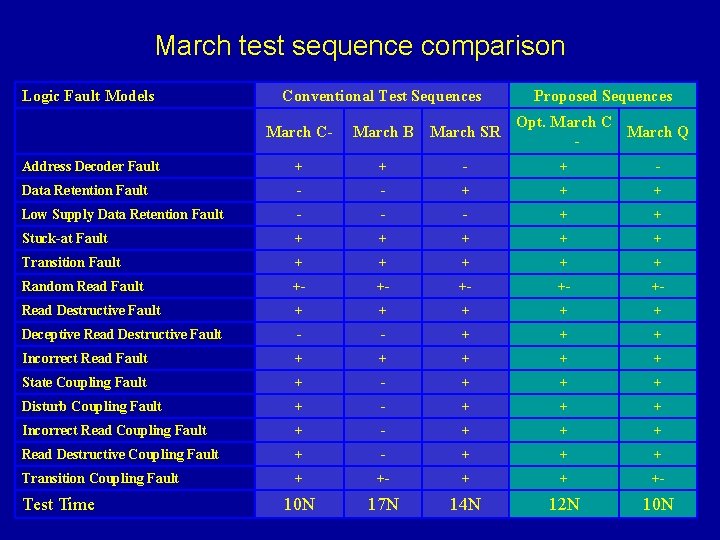

Test: Optimized March Test Sequence 1. Optimized March C + Good fault coverage Test time increases 2. March Q + + Reduce the test time Cover all the fault models induced by process variations Not able to detect Transition Coupling Fault and Address Decoder Fault

March test sequence comparison Logic Fault Models Conventional Test Sequences Proposed Sequences Opt. March C March Q - March C- March B March SR Address Decoder Fault + + - Data Retention Fault - - + + + Low Supply Data Retention Fault - - - + + Stuck-at Fault + + + Transition Fault + + + Random Read Fault +- +- +- Read Destructive Fault + + + Deceptive Read Destructive Fault - - + + + Incorrect Read Fault + + + State Coupling Fault + - + + + Disturb Coupling Fault + - + + + Incorrect Read Coupling Fault + - + + + Read Destructive Coupling Fault + - + + + Transition Coupling Fault + +- + + +- 10 N 17 N 14 N 12 N 10 N Test Time

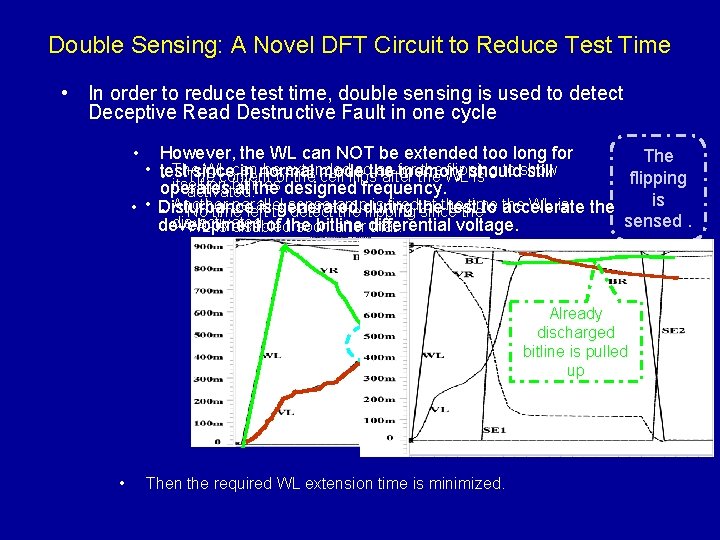

Double Sensing: A Novel DFT Circuit to Reduce Test Time • In order to reduce test time, double sensing is used to detect Deceptive Read Destructive Fault in one cycle • However, the WL can NOT be extended too long for The • test The WL can be extended so as for the flipping to show since in normal memory still • The content of the mode cell flipsthe after the WL should is flipping itself on bitlines operates at the designed frequency. activated. is • Another parallel sense amp is firedthe at the time the WL is the • Disturbance istogenerated test to accelerate • No time left detect the during flipping since the sensed. dis activated. development of the bitline voltage. WL is disabled soon after differential that. WL Already extended discharged bitline is pulled up • Then the required WL extension time is minimized.

Parametric Failures and Yield PMEM Redundant Columns Inter-die Variation PF SRAM die with a global shift in process parameter Failure Probability PCOL Intra-die Variation => Cell, Column and Memory failure Hold Failure Read Failure Write Failure Access Failure Std. dev. of intra-die variation

What is the effect of Inter-die variation on Parametric Failures?

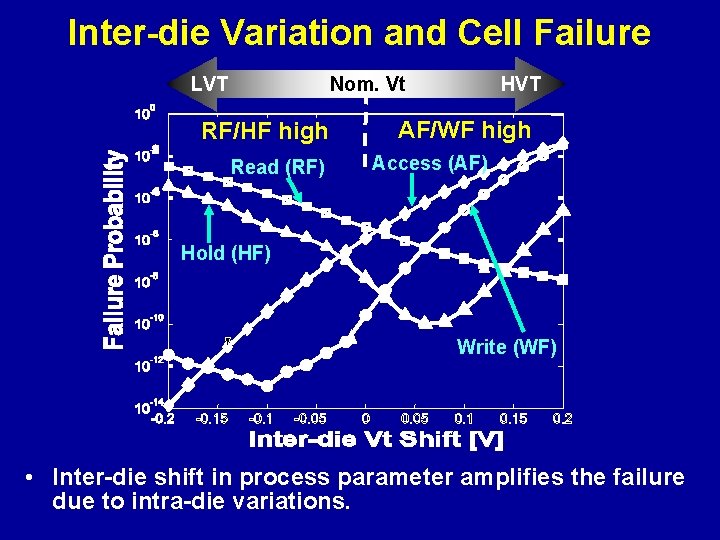

Inter-die Variation and Cell Failure LVT Nom. Vt RF/HF high Read (RF) HVT AF/WF high Access (AF) Hold (HF) Write (WF) • Inter-die shift in process parameter amplifies the failure due to intra-die variations.

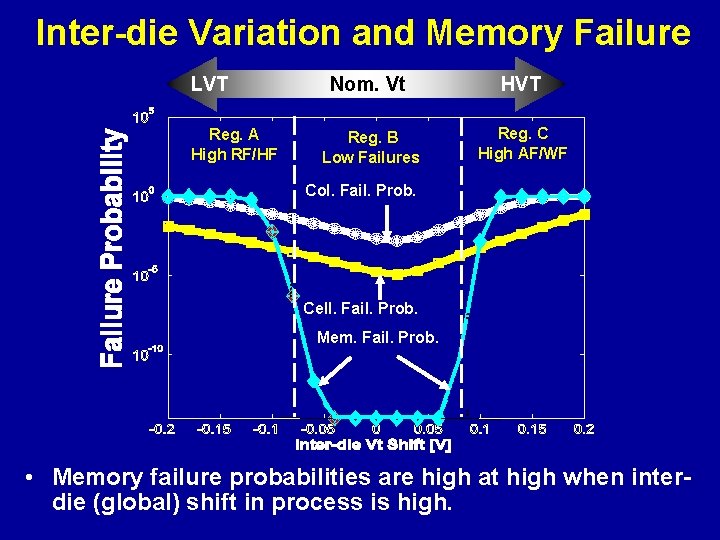

Inter-die Variation and Memory Failure LVT Reg. A High RF/HF Nom. Vt HVT Reg. B Low Failures Reg. C High AF/WF Col. Fail. Prob. Cell. Fail. Prob. Mem. Fail. Prob. • Memory failure probabilities are high at high when interdie (global) shift in process is high.

How can we improve yield considering both inter-die and intra-die variations?

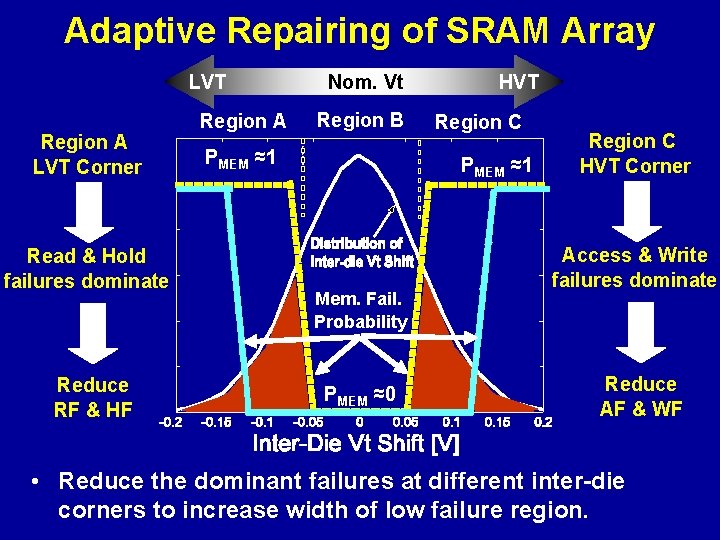

Adaptive Repairing of SRAM Array LVT Region A LVT Corner Read & Hold failures dominate Reduce RF & HF Region A Nom. Vt Region B PMEM ≈1 HVT Region C PMEM ≈1 Mem. Fail. Probability PMEM ≈0 Region C HVT Corner Access & Write failures dominate Reduce AF & WF • Reduce the dominant failures at different inter-die corners to increase width of low failure region.

How can we reduce the dominant failures at different inter-die corners?

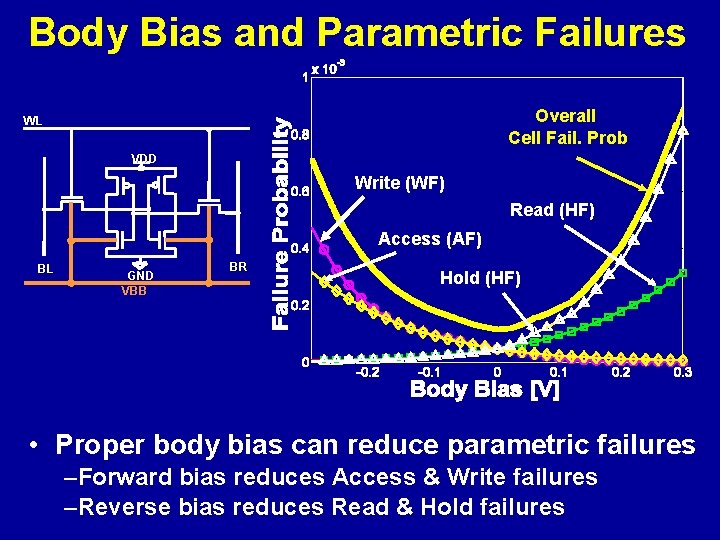

Body Bias and Parametric Failures Overall Cell Fail. Prob WL VDD Write (WF) Read (HF) Access (AF) BL GND VBB BR Hold (HF) • Proper body bias can reduce parametric failures –Forward bias reduces Access & Write failures –Reverse bias reduces Read & Hold failures

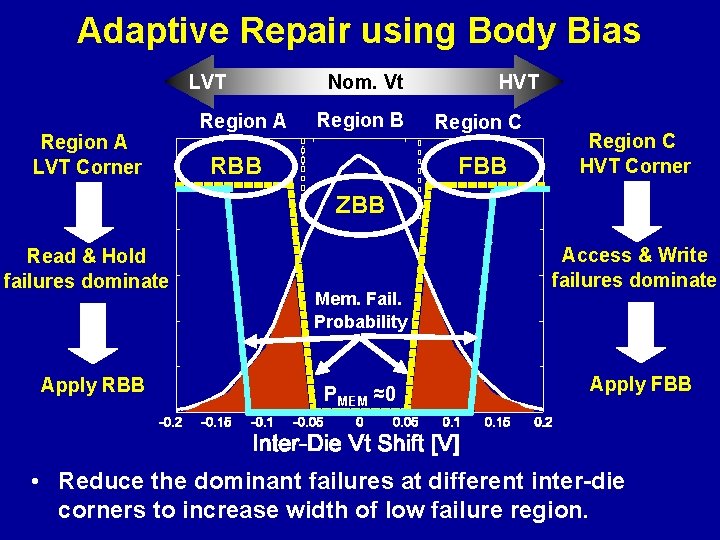

Adaptive Repair using Body Bias LVT Region A LVT Corner Region A Nom. Vt Region B RBB HVT Region C FBB Region C HVT Corner ZBB Read & Hold failures dominate Apply RBB Mem. Fail. Probability PMEM ≈0 Access & Write failures dominate Apply FBB • Reduce the dominant failures at different inter-die corners to increase width of low failure region.

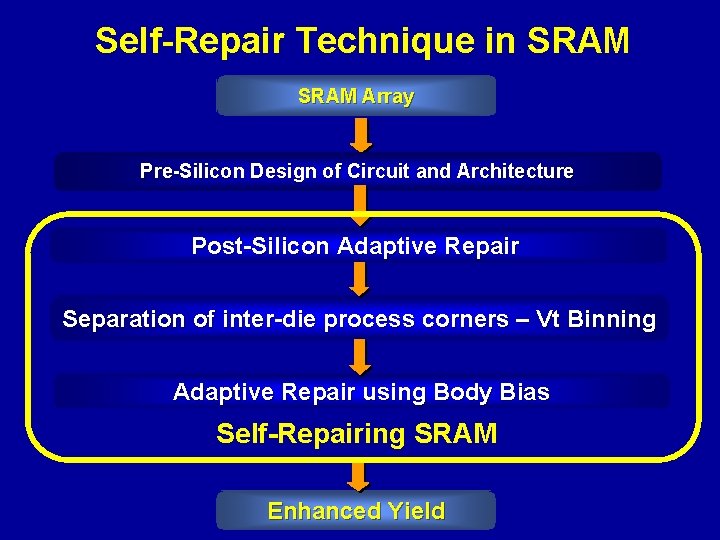

Self-Repair Technique in SRAM Array Pre-Silicon Design of Circuit and Architecture Post-Silicon Adaptive Repair Separation of inter-die process corners – Vt Binning Adaptive Repair using Body Bias Self-Repairing SRAM Enhanced Yield

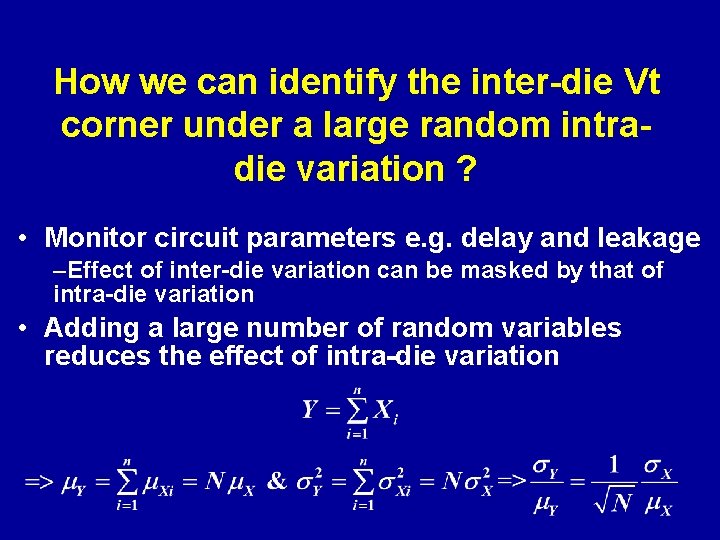

How we can identify the inter-die Vt corner under a large random intradie variation ? • Monitor circuit parameters e. g. delay and leakage –Effect of inter-die variation can be masked by that of intra-die variation • Adding a large number of random variables reduces the effect of intra-die variation

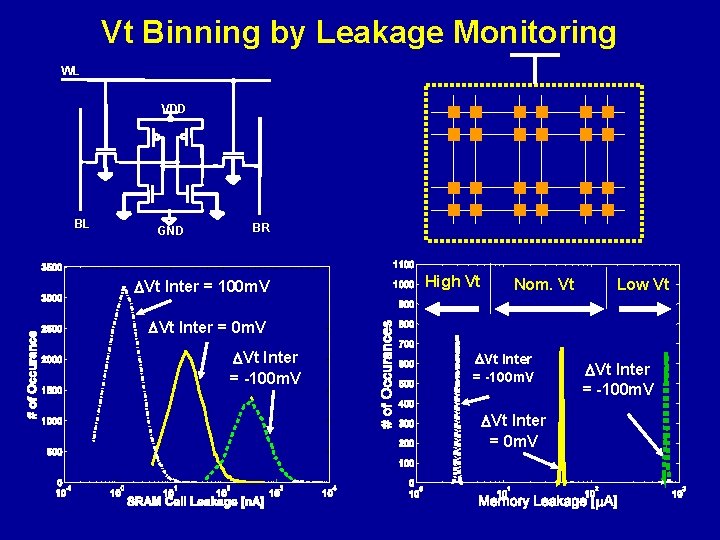

Vt Binning by Leakage Monitoring WL VDD BL GND BR Vt Inter = 100 m. V High Vt Nom. Vt Low Vt Inter = 0 m. V Vt Inter = -100 m. V Vt Inter = -100 m. V

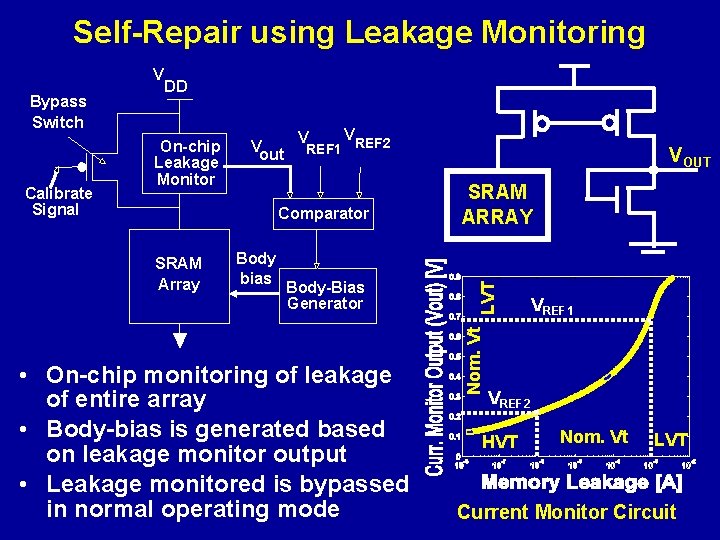

Self-Repair using Leakage Monitoring Calibrate Signal DD On-chip Leakage Monitor V out V V REF 1 REF 2 Comparator SRAM Array Body bias Body-Bias Generator • On-chip monitoring of leakage of entire array • Body-bias is generated based on leakage monitor output • Leakage monitored is bypassed in normal operating mode VOUT SRAM ARRAY LVT Bypass Switch Nom. Vt V VREF 1 VREF 2 HVT Nom. Vt LVT Current Monitor Circuit

Yield Enhancement using Self-Repair 265 KB Self-Repairing SRAM 265 KB SRAM with No Body-Bias • Self-Repairing SRAM using body-bias can significantly improve design yield.

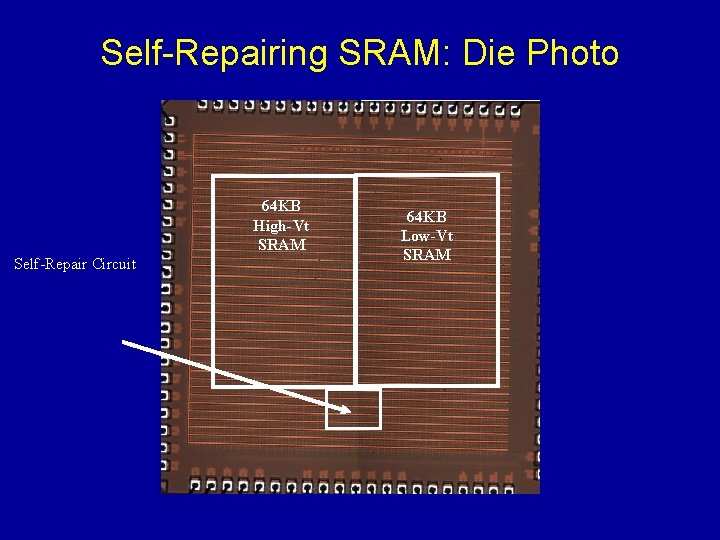

Self Repairing SRAM: Die Photo 64 KB High-Vt SRAM Self-Repair Circuit 64 KB Low-Vt SRAM

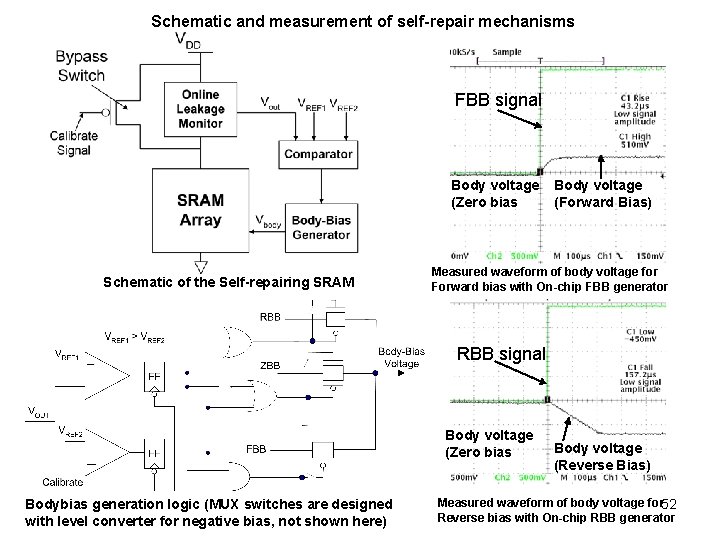

Schematic and measurement of self-repair mechanisms FBB signal Body voltage (Zero bias Schematic of the Self-repairing SRAM Body voltage (Forward Bias) Measured waveform of body voltage for Forward bias with On-chip FBB generator RBB signal Body voltage (Zero bias Bodybias generation logic (MUX switches are designed with level converter for negative bias, not shown here) Body voltage (Reverse Bias) Measured waveform of body voltage for 52 Reverse bias with On-chip RBB generator

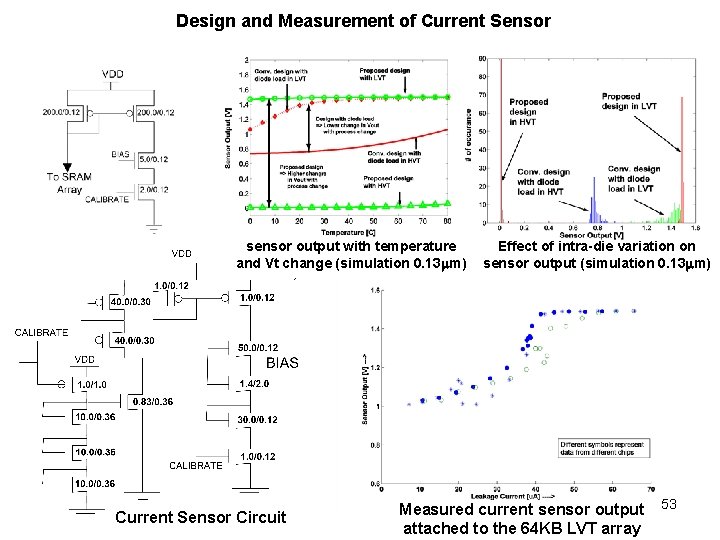

Design and Measurement of Current Sensor sensor output with temperature and Vt change (simulation 0. 13 m) Current Sensor Circuit Effect of intra-die variation on sensor output (simulation 0. 13 m) Measured current sensor output attached to the 64 KB LVT array 53

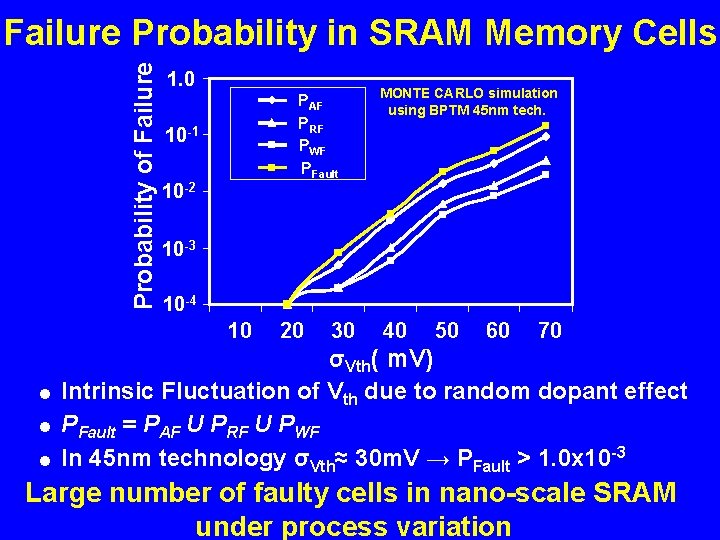

Probability of Failure Probability in SRAM Memory Cells 1. 0 PAF PRF PWF PFault 10 -1 10 -2 MONTE CARLO simulation using BPTM 45 nm tech. 10 -3 10 -4 10 20 30 40 50 60 70 σVth( m. V) = Intrinsic Fluctuation of Vth due to random dopant effect = PFault = PAF U PRF U PWF = In 45 nm technology σVth≈ 30 m. V → PFault > 1. 0 x 10 -3 Large number of faulty cells in nano-scale SRAM under process variation

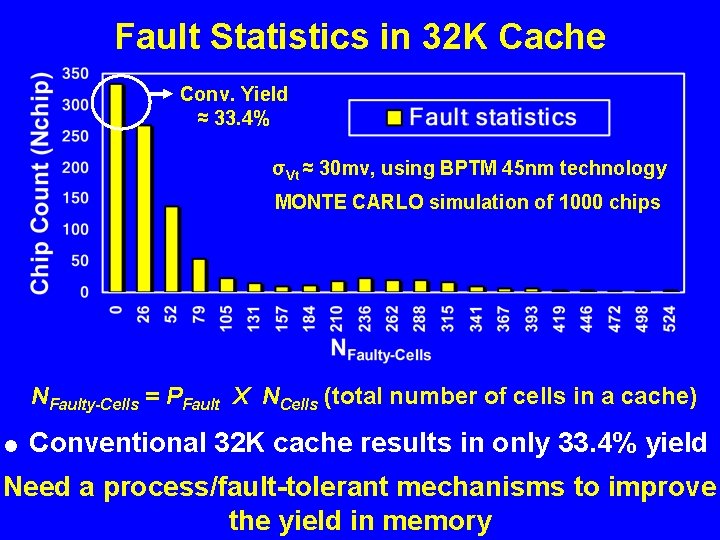

Fault Statistics in 32 K Cache Conv. Yield ≈ 33. 4% σVt ≈ 30 mv, using BPTM 45 nm technology MONTE CARLO simulation of 1000 chips NFaulty-Cells = PFault X NCells (total number of cells in a cache) = Conventional 32 K cache results in only 33. 4% yield Need a process/fault-tolerant mechanisms to improve the yield in memory

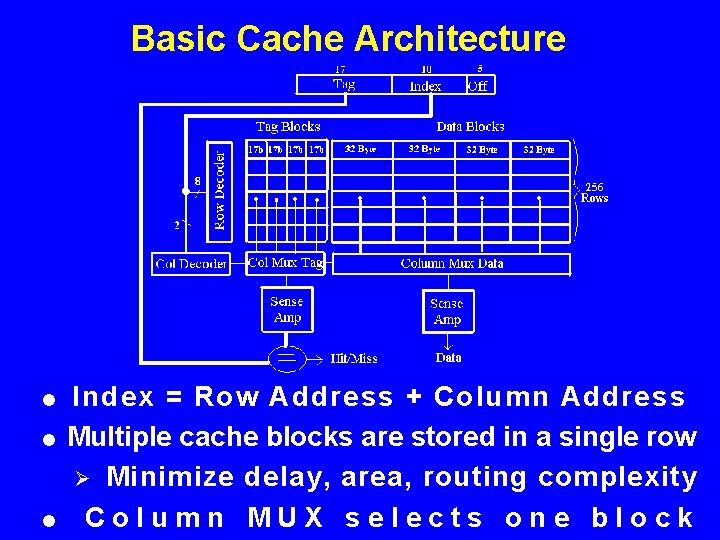

Basic Cache Architecture Index = Row Address + Column Address = Multiple cache blocks are stored in a single row Ø Minimize delay, area, routing complexity = Column MUX selects one block =

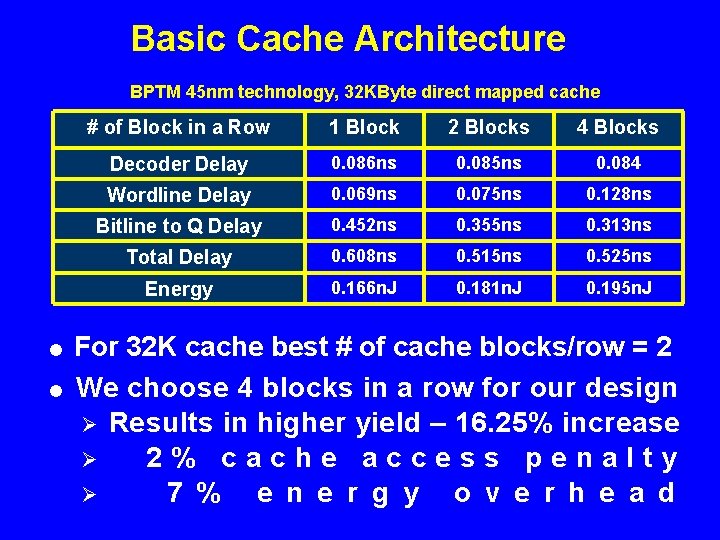

Basic Cache Architecture BPTM 45 nm technology, 32 KByte direct mapped cache # of Block in a Row 1 Block 2 Blocks 4 Blocks Decoder Delay 0. 086 ns 0. 085 ns 0. 084 Wordline Delay 0. 069 ns 0. 075 ns 0. 128 ns Bitline to Q Delay 0. 452 ns 0. 355 ns 0. 313 ns Total Delay 0. 608 ns 0. 515 ns 0. 525 ns Energy 0. 166 n. J 0. 181 n. J 0. 195 n. J For 32 K cache best # of cache blocks/row = 2 = We choose 4 blocks in a row for our design Ø Results in higher yield – 16. 25% increase Ø 2% cache access penalty Ø 7 % e n e r g y o v e r h e a d =

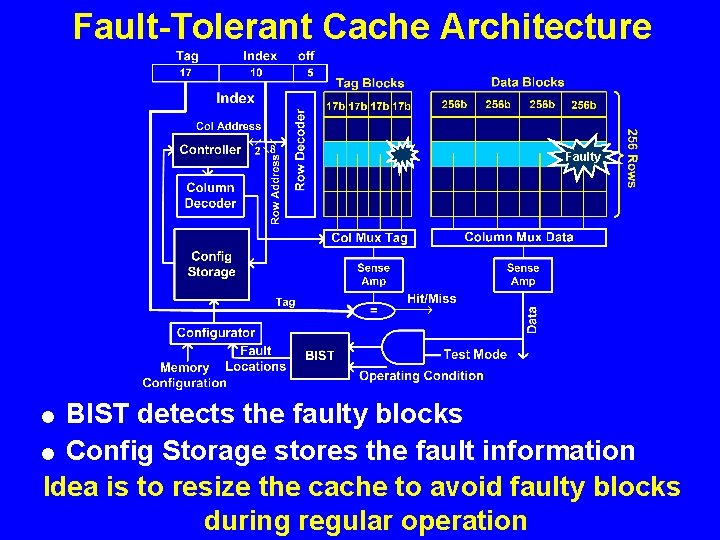

Fault-Tolerant Cache Architecture Faulty BIST detects the faulty blocks = Config Storage stores the fault information Idea is to resize the cache to avoid faulty blocks during regular operation =

Resizing the Cache Config Storage is accessed in parallel with cache “ 00” Feeds the fault information to controller Controller alters the column address Force the column MUX to select a non-faulty block in the same row if the accessed block is faulty Handle large number of faults without significantly reducing the cache size

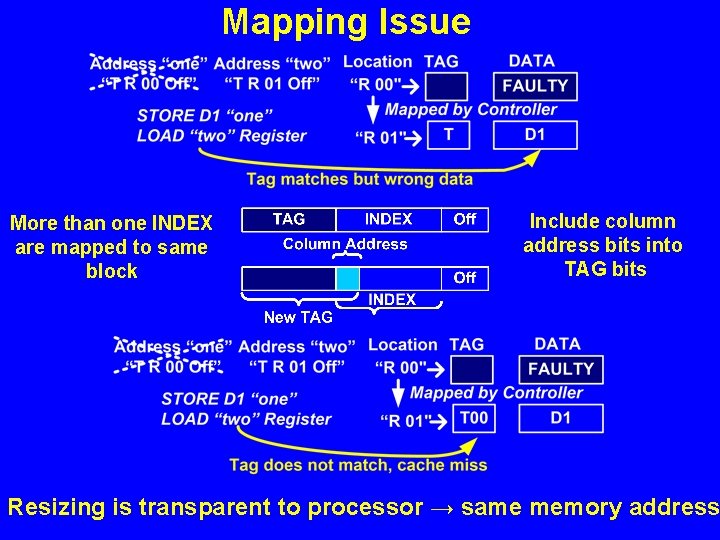

Mapping Issue More than one INDEX are mapped to same block Include column address bits into TAG bits Resizing is transparent to processor → same memory address

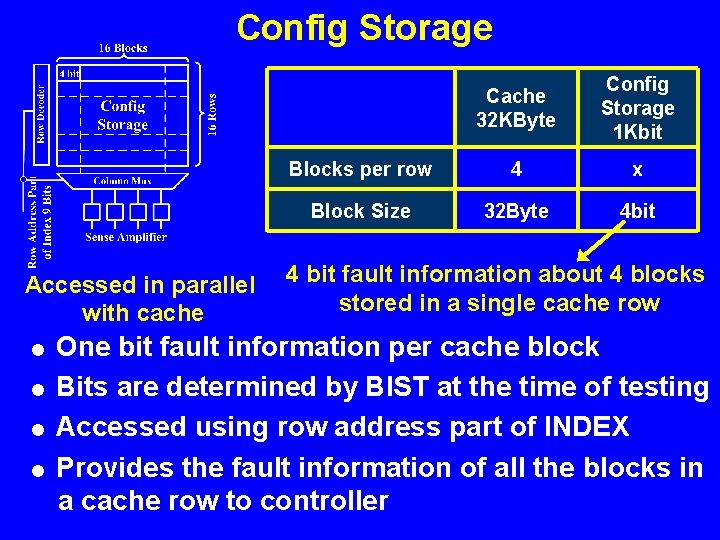

Config Storage Accessed in parallel with cache Cache 32 KByte Config Storage 1 Kbit Blocks per row 4 x Block Size 32 Byte 4 bit 4 bit fault information about 4 blocks stored in a single cache row One bit fault information per cache block = Bits are determined by BIST at the time of testing = Accessed using row address part of INDEX = Provides the fault information of all the blocks in a cache row to controller =

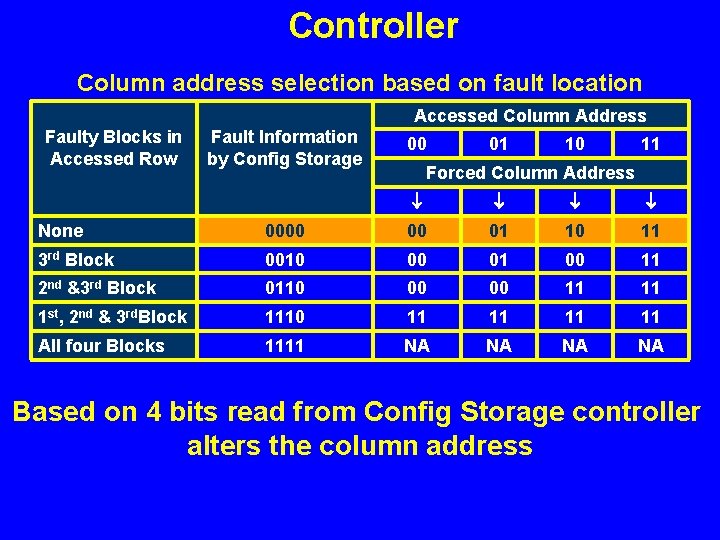

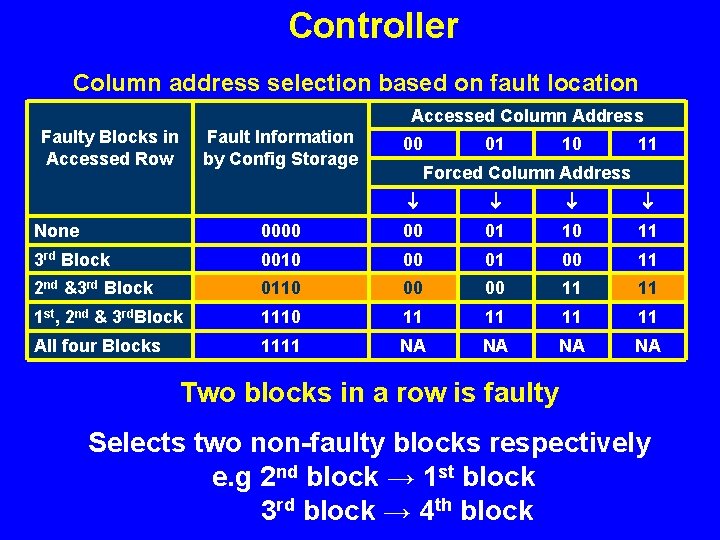

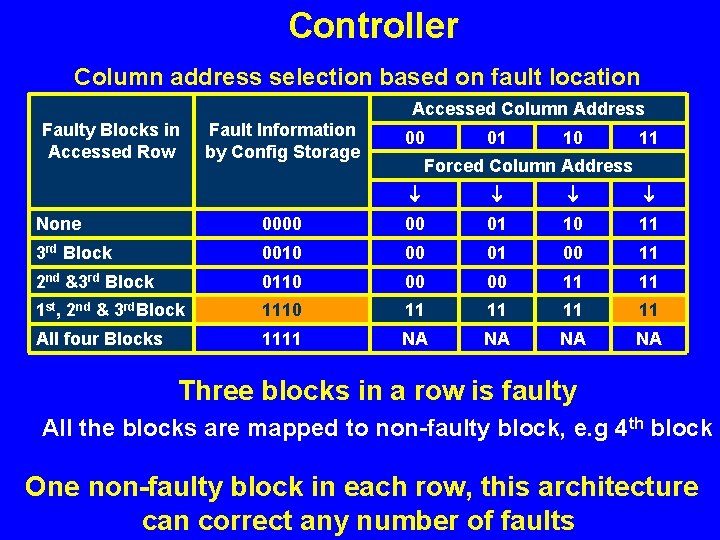

Controller Column address selection based on fault location Accessed Column Address Faulty Blocks in Accessed Row Fault Information by Config Storage 00 01 10 11 Forced Column Address None 0000 00 01 10 11 3 rd Block 0010 00 01 00 11 2 nd &3 rd Block 0110 00 00 11 11 1 st, 2 nd & 3 rd. Block 1110 11 11 All four Blocks 1111 NA NA Based on 4 bits read from Config Storage controller alters the column address

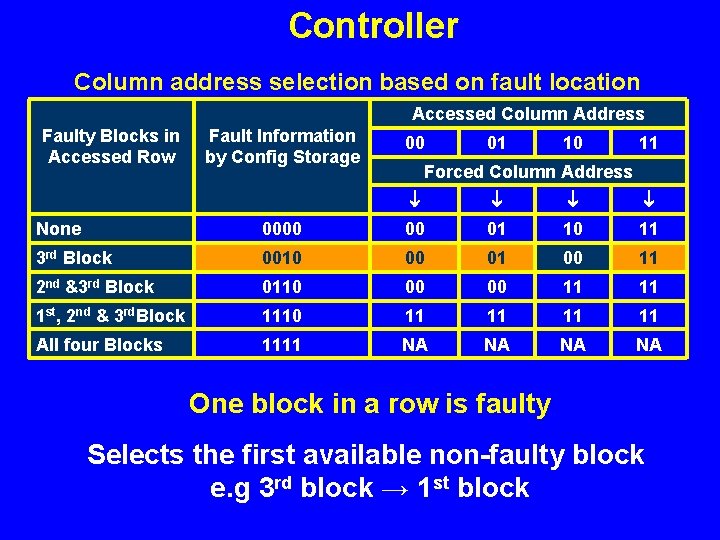

Controller Column address selection based on fault location Accessed Column Address Faulty Blocks in Accessed Row Fault Information by Config Storage 00 01 10 11 Forced Column Address None 0000 00 01 10 11 3 rd Block 0010 00 01 00 11 2 nd &3 rd Block 0110 00 00 11 11 1 st, 2 nd & 3 rd. Block 1110 11 11 All four Blocks 1111 NA NA One block in a row is faulty Selects the first available non-faulty block e. g 3 rd block → 1 st block

Controller Column address selection based on fault location Accessed Column Address Faulty Blocks in Accessed Row Fault Information by Config Storage 00 01 10 11 Forced Column Address None 0000 00 01 10 11 3 rd Block 0010 00 01 00 11 2 nd &3 rd Block 0110 00 00 11 11 1 st, 2 nd & 3 rd. Block 1110 11 11 All four Blocks 1111 NA NA Two blocks in a row is faulty Selects two non-faulty blocks respectively e. g 2 nd block → 1 st block 3 rd block → 4 th block

Controller Column address selection based on fault location Accessed Column Address Faulty Blocks in Accessed Row Fault Information by Config Storage 00 01 10 11 Forced Column Address None 0000 00 01 10 11 3 rd Block 0010 00 01 00 11 2 nd &3 rd Block 0110 00 00 11 11 1 st, 2 nd & 3 rd. Block 1110 11 11 All four Blocks 1111 NA NA Three blocks in a row is faulty All the blocks are mapped to non-faulty block, e. g 4 th block One non-faulty block in each row, this architecture can correct any number of faults

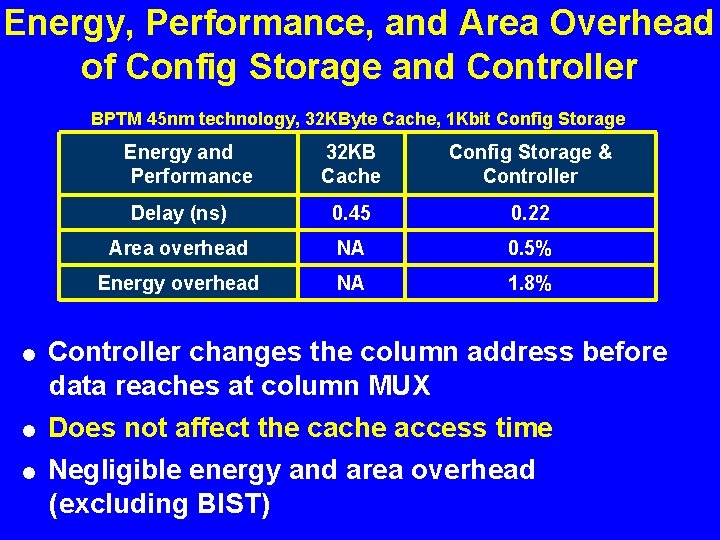

Energy, Performance, and Area Overhead of Config Storage and Controller BPTM 45 nm technology, 32 KByte Cache, 1 Kbit Config Storage Energy and Performance = 32 KB Cache Config Storage & Controller Delay (ns) 0. 45 0. 22 Area overhead NA 0. 5% Energy overhead NA 1. 8% Controller changes the column address before data reaches at column MUX Does not affect the cache access time = Negligible energy and area overhead (excluding BIST) =

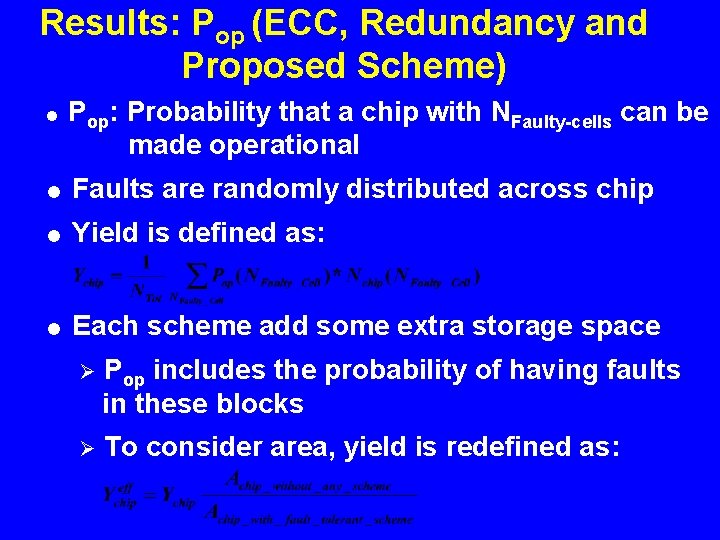

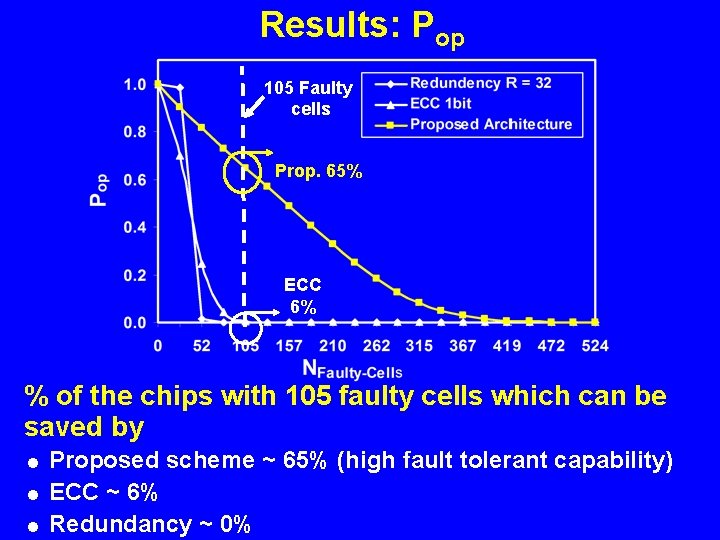

Results: Pop (ECC, Redundancy and Proposed Scheme) = Pop: Probability that a chip with NFaulty-cells can be made operational = Faults are randomly distributed across chip = Yield is defined as: = Each scheme add some extra storage space Ø Pop includes the probability of having faults in these blocks Ø To consider area, yield is redefined as:

Results: Pop 105 Faulty cells Prop. 65% ECC 6% % of the chips with 105 faulty cells which can be saved by Proposed scheme ~ 65% (high fault tolerant capability) = ECC ~ 6% = Redundancy ~ 0% =

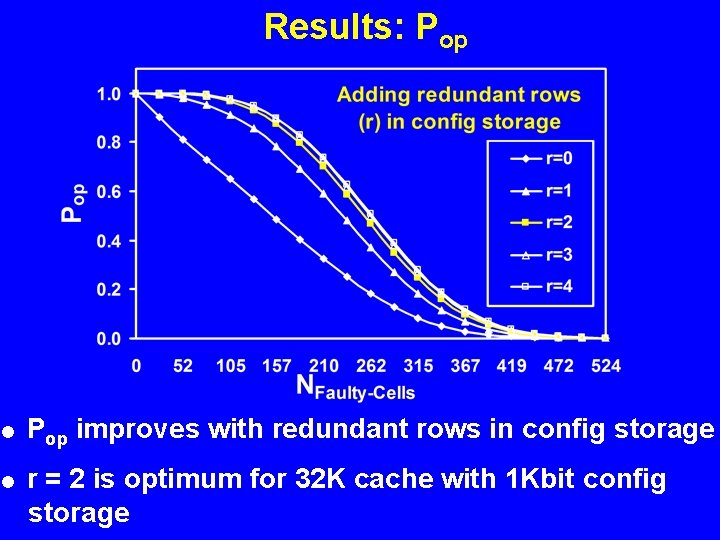

Results: Pop = Pop improves with redundant rows in config storage = r = 2 is optimum for 32 K cache with 1 Kbit config storage

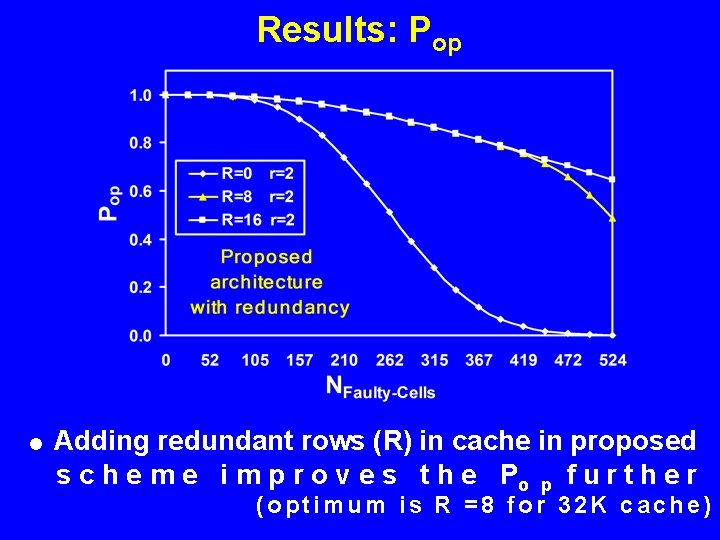

Results: Pop = Adding redundant rows (R) in cache in proposed s c h e m e i m p r o v e s t h e Po p f u r t h e r (optimum is R =8 for 32 K cache)

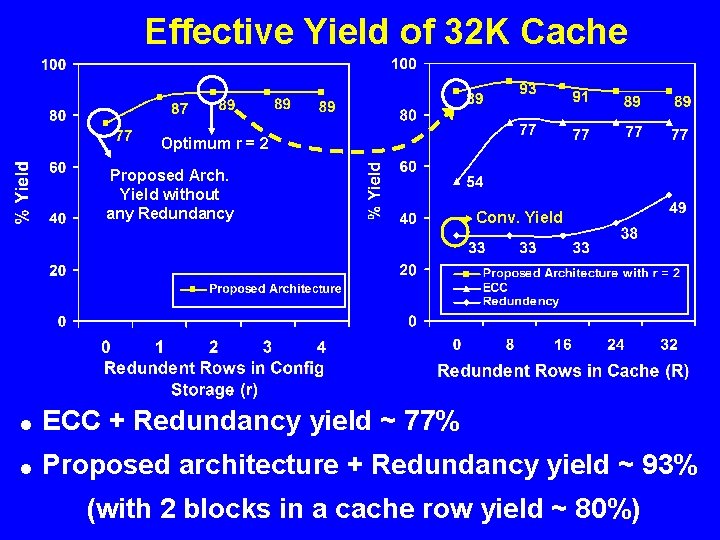

Effective Yield of 32 K Cache Optimum r = 2 Proposed Arch. Yield without any Redundancy Conv. Yield = ECC + Redundancy yield ~ 77% = Proposed architecture + Redundancy yield ~ 93% (with 2 blocks in a cache row yield ~ 80%)

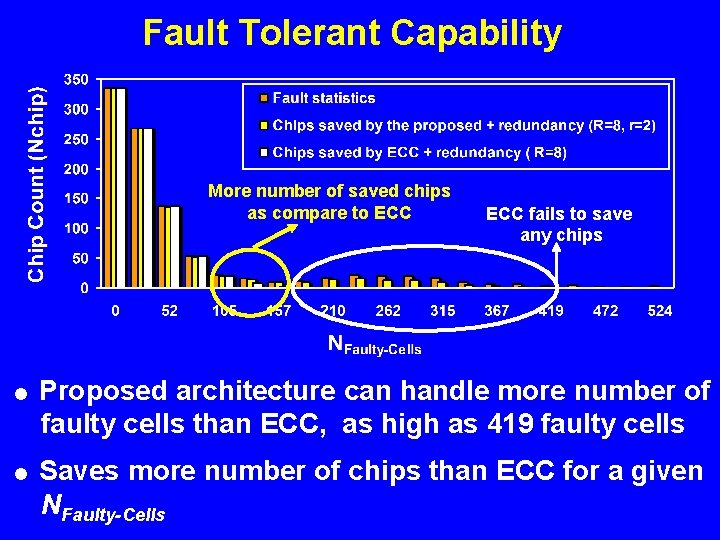

Fault Tolerant Capability More number of saved chips as compare to ECC fails to save any chips = Proposed architecture can handle more number of faulty cells than ECC, as high as 419 faulty cells = Saves more number of chips than ECC for a given NFaulty-Cells

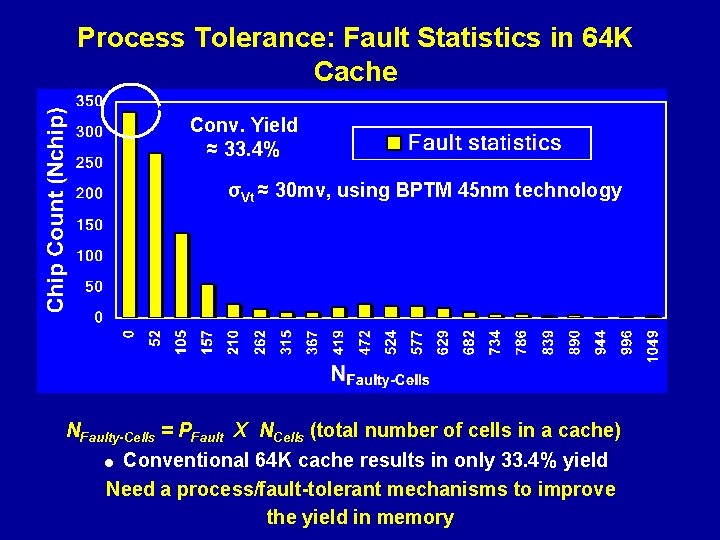

Process Tolerance: Fault Statistics in 64 K Cache Conv. Yield ≈ 33. 4% σVt ≈ 30 mv, using BPTM 45 nm technology NFaulty-Cells = PFault X NCells (total number of cells in a cache) = Conventional 64 K cache results in only 33. 4% yield Need a process/fault-tolerant mechanisms to improve the yield in memory

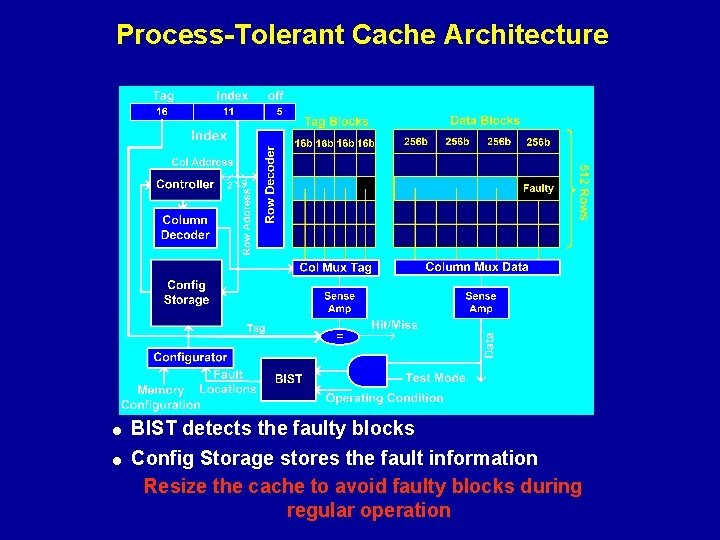

Process-Tolerant Cache Architecture = BIST detects the faulty blocks = Config Storage stores the fault information Resize the cache to avoid faulty blocks during regular operation

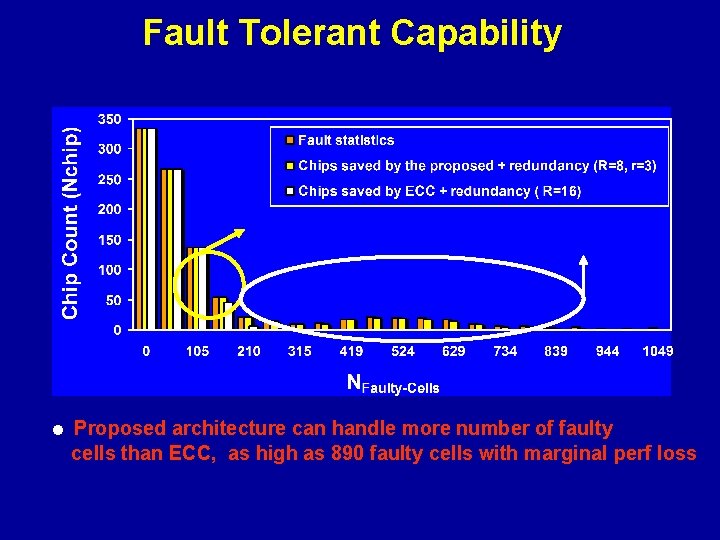

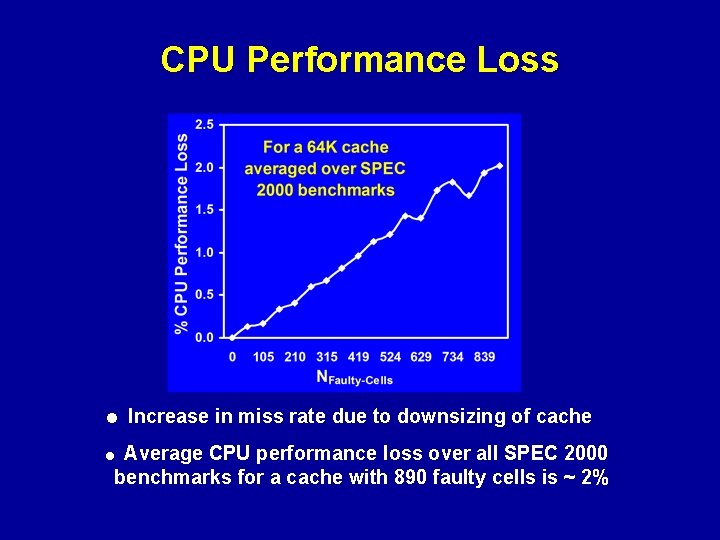

Fault Tolerant Capability More number of saved chips as compare to ECC fails to save any chips = Proposed architecture can handle more number of faulty cells than ECC, as high as 890 faulty cells with marginal perf loss

CPU Performance Loss = Increase in miss rate due to downsizing of cache Average CPU performance loss over all SPEC 2000 benchmarks for a cache with 890 faulty cells is ~ 2% =

Register File: Self Calibration using Leakage Sensing C. Kim, R. Krishnamurthy, & K. Roy

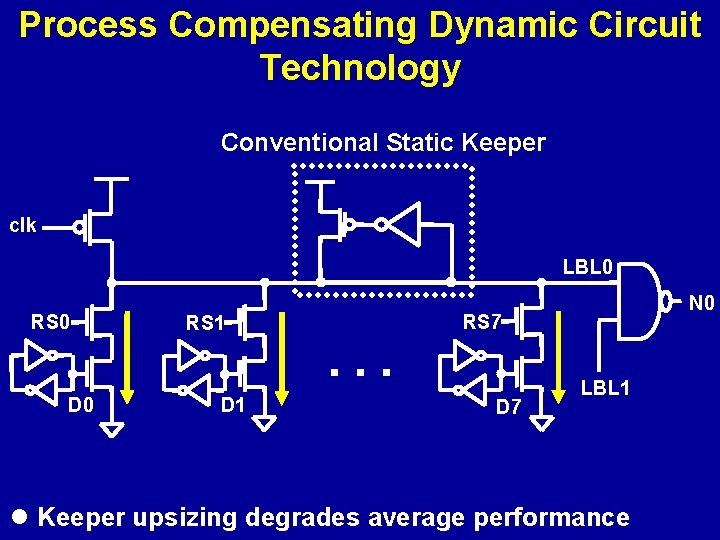

Process Compensating Dynamic Circuit Technology Conventional Static Keeper clk LBL 0 RS 0 D 0 RS 1 D 1 . . . N 0 RS 7 D 7 LBL 1 l Keeper upsizing degrades average performance

![Process Compensating Dynamic Circuit Technology 3 -bit programmable keeper b[2: 0] W clk s Process Compensating Dynamic Circuit Technology 3 -bit programmable keeper b[2: 0] W clk s](http://slidetodoc.com/presentation_image_h/95400c5f1559fe1f5ad91e522d5ad065/image-63.jpg)

Process Compensating Dynamic Circuit Technology 3 -bit programmable keeper b[2: 0] W clk s 2 W s 4 W s LBL 0 RS 0 D 0 RS 1 D 1 . . . N 0 RS 7 D 7 LBL 1 C. Kim et al. , VLSI Circuits Symp. ‘ 03 l Opportunistic speedup via keeper downsizing

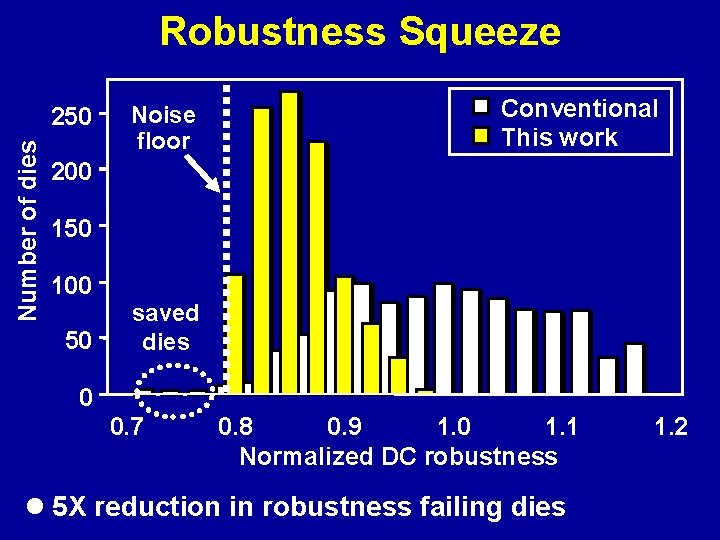

Robustness Squeeze Number of dies 250 Noise floor Conventional This work 200 150 100 50 saved dies 0 0. 7 0. 8 0. 9 1. 0 1. 1 Normalized DC robustness l 5 X reduction in robustness failing dies 1. 2

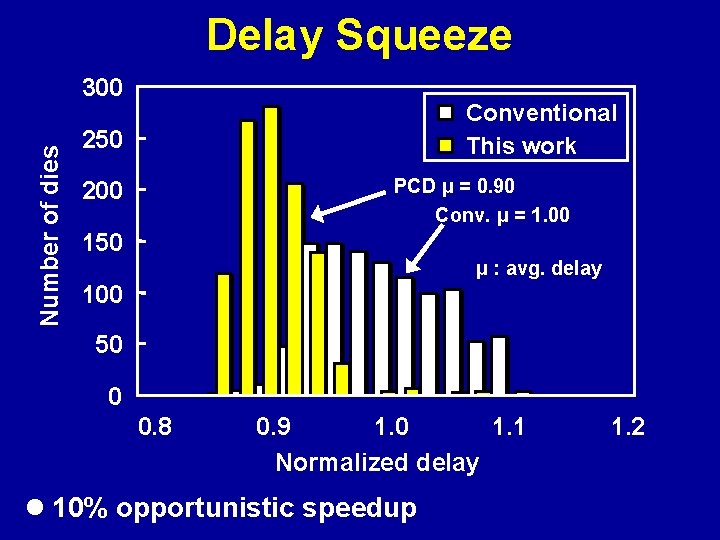

Delay Squeeze Number of dies 300 Conventional This work 250 PCD μ = 0. 90 Conv. μ = 1. 00 200 150 μ : avg. delay 100 50 0 0. 8 0. 9 1. 0 1. 1 Normalized delay l 10% opportunistic speedup 1. 2

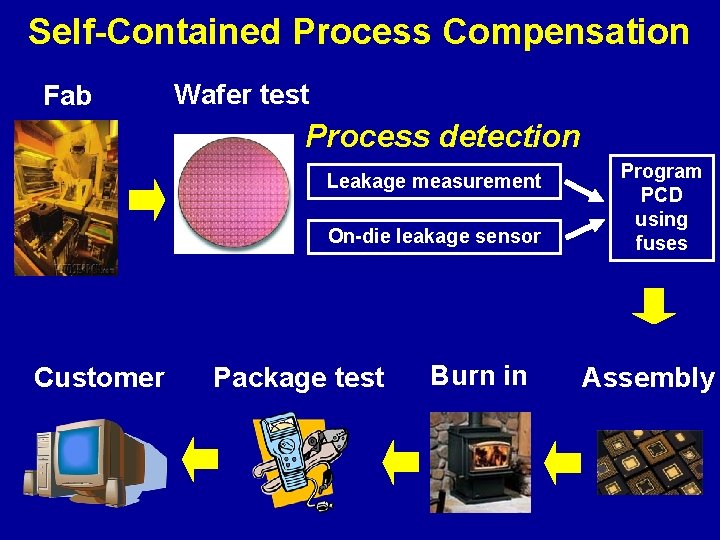

Self-Contained Process Compensation Fab Wafer test Process detection Leakage measurement On-die leakage sensor Customer Package test Burn in Program PCD using fuses Assembly

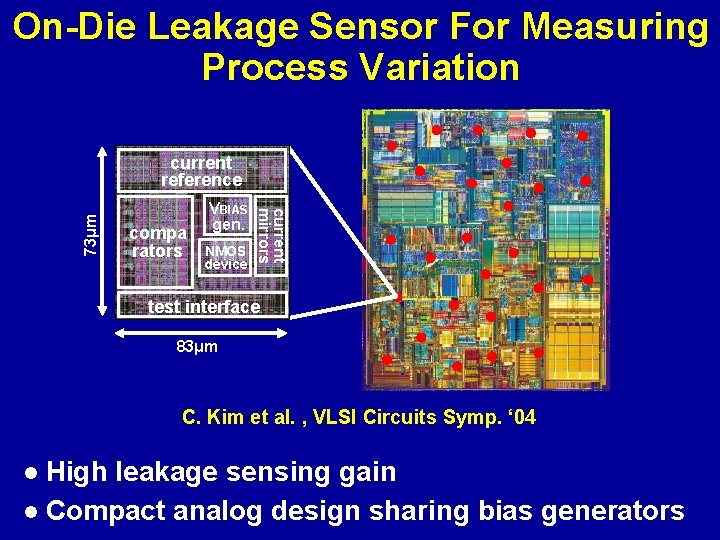

On-Die Leakage Sensor For Measuring Process Variation compa rators VBIAS gen. NMOS device current mirrors 73μm current reference test interface 83μm C. Kim et al. , VLSI Circuits Symp. ‘ 04 High leakage sensing gain l Compact analog design sharing bias generators l

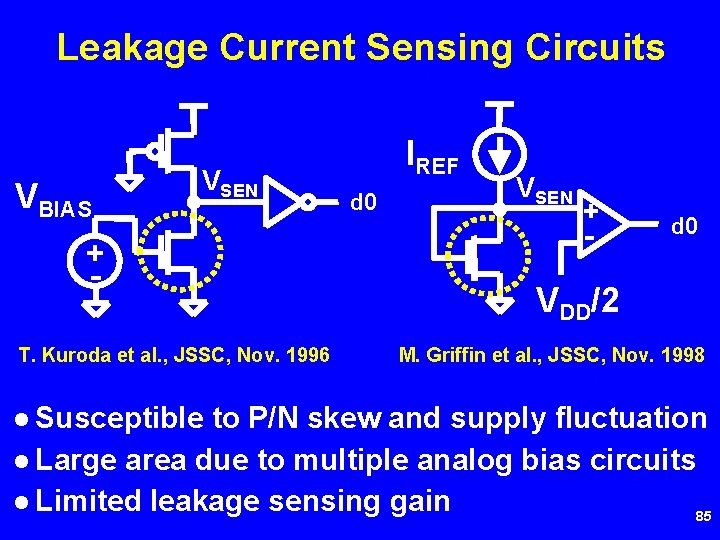

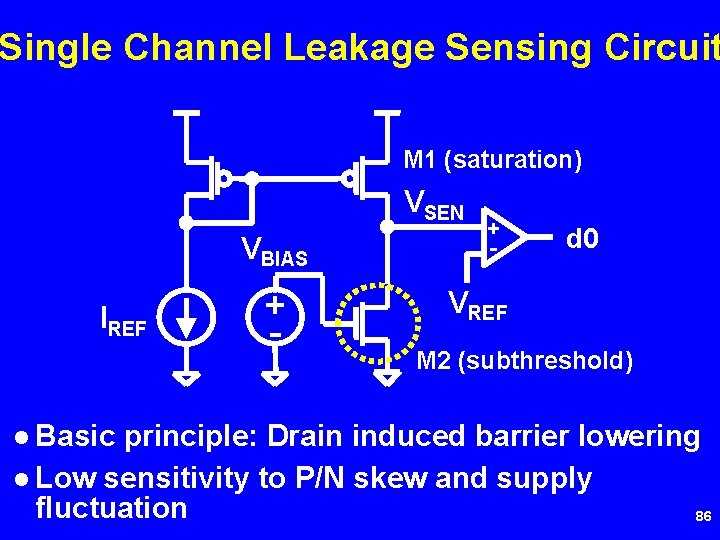

Leakage Current Sensing Circuits VBIAS VSEN + T. Kuroda et al. , JSSC, Nov. 1996 l Susceptible IREF d 0 VSEN + - d 0 VDD/2 M. Griffin et al. , JSSC, Nov. 1998 to P/N skew and supply fluctuation l Large area due to multiple analog bias circuits l Limited leakage sensing gain 85

Single Channel Leakage Sensing Circuit M 1 (saturation) VSEN VBIAS IREF l Basic + - d 0 VREF M 2 (subthreshold) principle: Drain induced barrier lowering l Low sensitivity to P/N skew and supply fluctuation 86

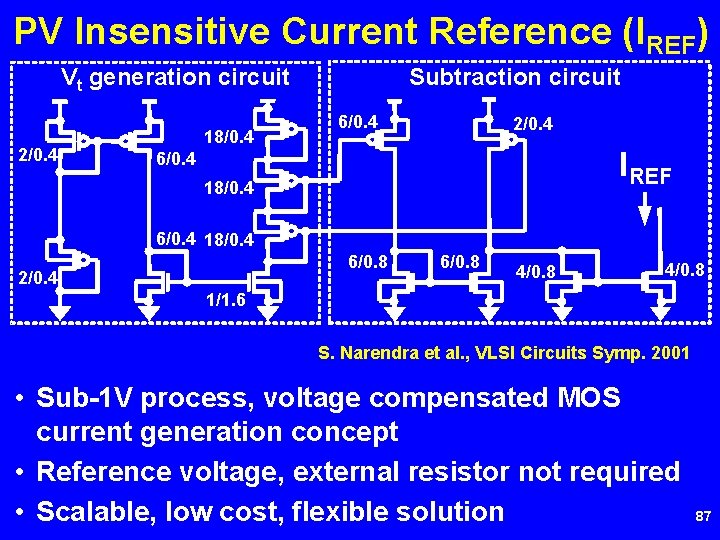

PV Insensitive Current Reference (IREF) Vt generation circuit 2/0. 4 18/0. 4 Subtraction circuit 6/0. 4 2/0. 4 IREF 6/0. 4 18/0. 4 6/0. 8 2/0. 4 6/0. 8 4/0. 8 1/1. 6 S. Narendra et al. , VLSI Circuits Symp. 2001 • Sub-1 V process, voltage compensated MOS current generation concept • Reference voltage, external resistor not required • Scalable, low cost, flexible solution 87

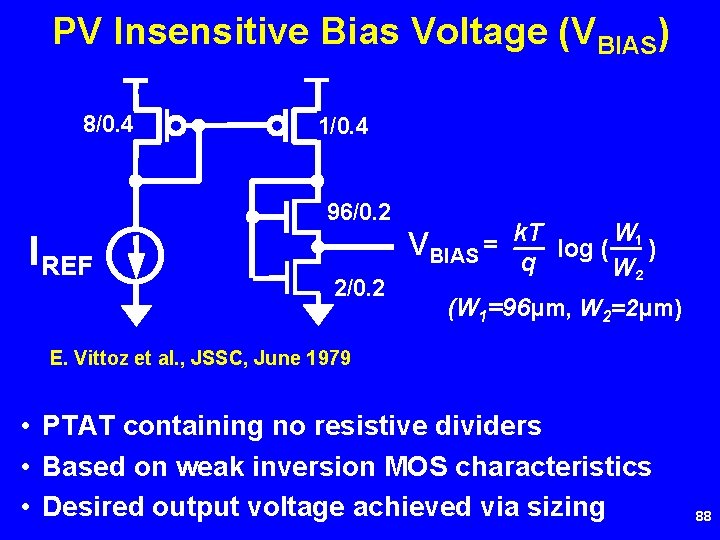

PV Insensitive Bias Voltage (VBIAS) 8/0. 4 1/0. 4 96/0. 2 IREF VBIAS = 2/0. 2 W 1 k. T log ( ) q W 2 (W 1=96μm, W 2=2μm) E. Vittoz et al. , JSSC, June 1979 • PTAT containing no resistive dividers • Based on weak inversion MOS characteristics • Desired output voltage achieved via sizing 88

Comparator + = - Subtraction circuit IREF (-) (+) 4/0. 4 8/0. 4 output 4/0. 4 • 2 -stage differential amplifier • Already designed IREF is used for bias current 4/0. 4 89

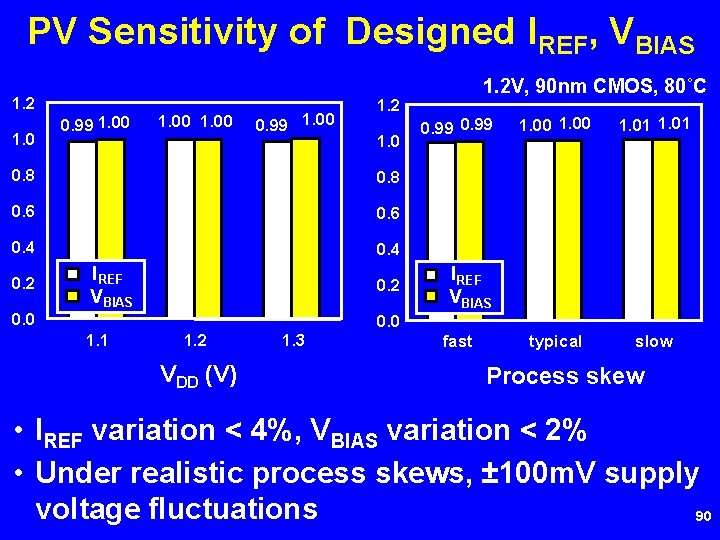

PV Sensitivity of Designed IREF, VBIAS 1. 2 1. 0 0. 99 1. 00 0. 99 1. 00 1. 2 1. 0 0. 8 0. 6 0. 4 0. 2 0. 0 IREF VBIAS 0. 2 1. 2 V, 90 nm CMOS, 80˚C 0. 99 1. 00 1. 01 typical slow IREF VBIAS 0. 0 1. 1 1. 2 VDD (V) 1. 3 fast Process skew • IREF variation < 4%, VBIAS variation < 2% • Under realistic process skews, ± 100 m. V supply voltage fluctuations 90

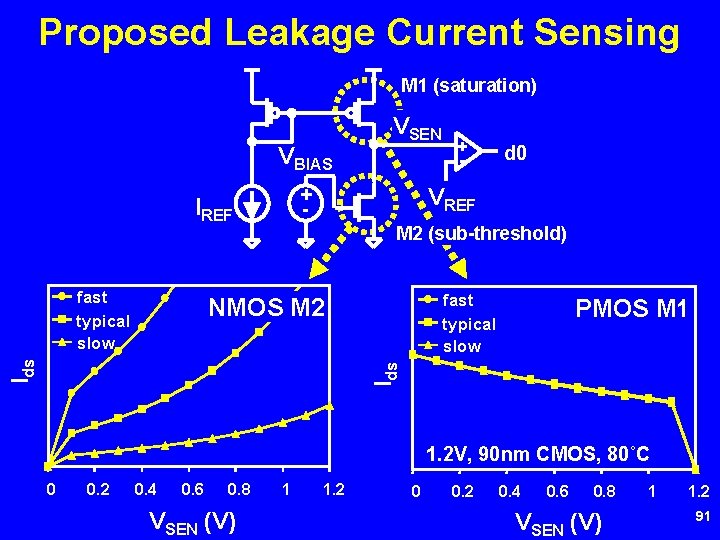

Proposed Leakage Current Sensing M 1 (saturation) VBIAS + - d 0 VREF + - IREF fast typical slow VSEN M 2 (sub-threshold) fast typical slow PMOS M 1 Ids NMOS M 2 1. 2 V, 90 nm CMOS, 80˚C 0 0. 2 0. 4 0. 6 0. 8 VSEN (V) 1 1. 2 91

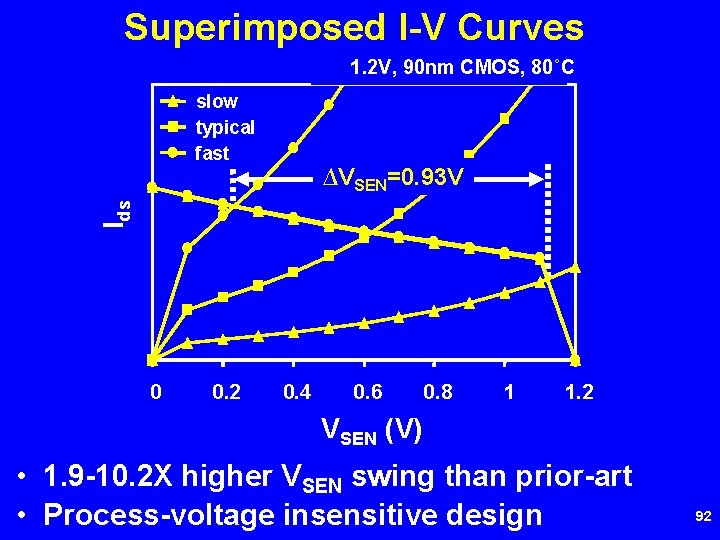

Superimposed I-V Curves 1. 2 V, 90 nm CMOS, 80˚C slow typical fast Ids ∆VSEN=0. 93 V 0 0. 2 0. 4 0. 6 0. 8 1 1. 2 VSEN (V) • 1. 9 -10. 2 X higher VSEN swing than prior-art • Process-voltage insensitive design 92

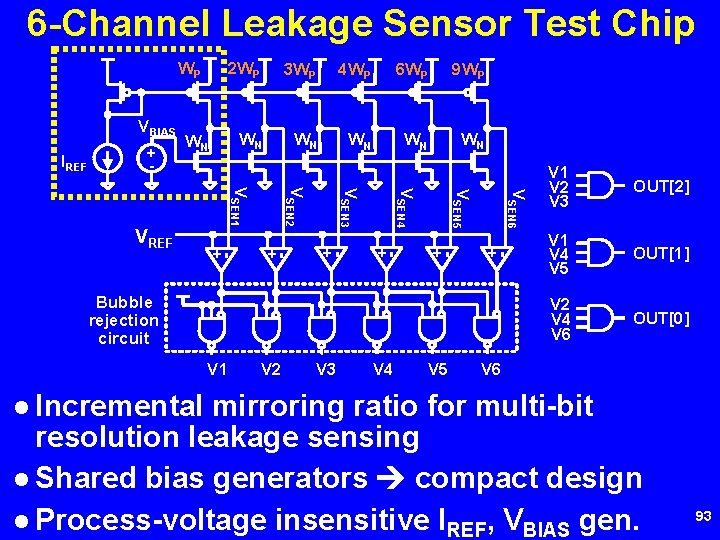

6 -Channel Leakage Sensor Test Chip WP VBIAS IREF + - 2 WP 3 WP 4 WP 6 WP 9 WP WN WN WN VSEN 6 VSEN 5 VSEN 4 VSEN 3 VSEN 2 VSEN 1 - + - + - + VREF Bubble rejection circuit V 1 V 2 V 3 V 4 V 5 V 1 V 2 V 3 OUT[2] V 1 V 4 V 5 OUT[1] V 2 V 4 V 6 OUT[0] V 6 l Incremental mirroring ratio for multi-bit resolution leakage sensing l Shared bias generators compact design l Process-voltage insensitive IREF, VBIAS gen. 93

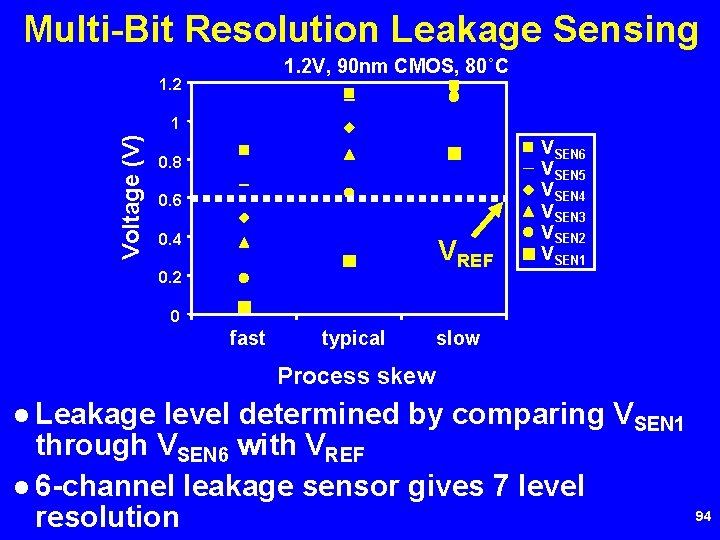

Multi-Bit Resolution Leakage Sensing 1. 2 V, 90 nm CMOS, 80˚C 1. 2 Voltage (V) 1 0. 8 0. 6 0. 4 VREF 0. 2 VSEN 6 VSEN 5 VSEN 4 VSEN 3 VSEN 2 VSEN 1 0 fast typical slow Process skew l Leakage level determined by comparing VSEN 1 through VSEN 6 with VREF l 6 -channel leakage sensor gives 7 level resolution 94

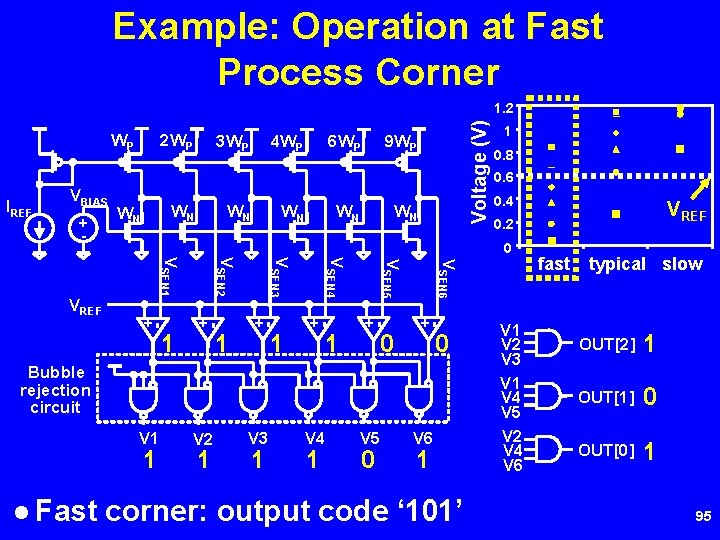

Example: Operation at Fast Process Corner WP IREF VBIAS + - 2 WP 3 WP WN WN 4 WP WN 6 WP WN Voltage (V) 1. 2 9 WP WN WN 0. 8 0. 6 0. 4 - + - 1 VSEN 6 VSEN 5 1 + - + - 1 VSEN 4 VSEN 3 VSEN 2 VSEN 1 + 1 0 0 Bubble rejection circuit V 1 1 V 2 1 V 3 1 V 4 1 V 5 0 V 6 1 corner: output code ‘ 101’ VREF 0. 2 0 VREF l Fast 1 V 2 V 3 V 1 V 4 V 5 V 2 V 4 V 6 fast typical slow OUT[2] 1 OUT[1] 0 OUT[0] 1 95

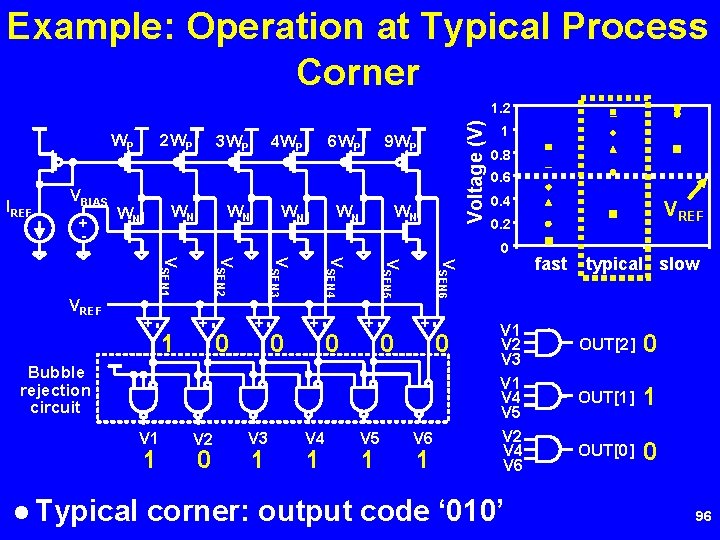

Example: Operation at Typical Process Corner WP IREF VBIAS + - 2 WP 3 WP WN WN 4 WP WN 6 WP WN Voltage (V) 1. 2 9 WP WN WN 0. 8 0. 6 0. 4 - + - 0 VSEN 6 VSEN 5 0 + - + - 0 VSEN 4 VSEN 3 VSEN 2 VSEN 1 + 1 0 0 Bubble rejection circuit V 1 1 V 2 0 V 3 1 V 4 1 V 5 1 V 6 1 VREF 0. 2 0 VREF l Typical 1 V 2 V 3 V 1 V 4 V 5 V 2 V 4 V 6 corner: output code ‘ 010’ fast typical slow OUT[2] 0 OUT[1] 1 OUT[0] 0 96

On-Die Leakage Sensor Test Chip current reference NMOS devices current mirrors compar ators VBIAS gen. test interface Technology 90 nm dual Vt CMOS VDD 1. 2 V Resolution 7 levels Power consumption 0. 66 m. W @80 Cº Dimensions 83 X 73 μm 2

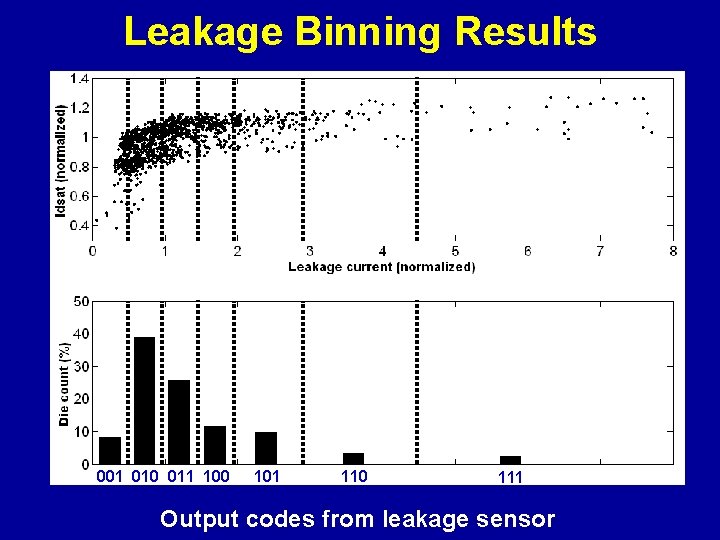

Leakage Binning Results 001 010 011 100 101 110 111 Output codes from leakage sensor

Conclusion l Statistical Failure Analysis Helps Enhance Yield l Post Silicon Tuning/Calibration is Becoming Promising for Si Nano systems l Built-In Leakage/Delay Sensors Provide Information on Intra-Die Process Variations

- Slides: 82