Hardware Description Language Logic Design using Verilog TsungChu

- Slides: 21

Hardware Description Language -- Logic Design using Verilog Tsung-Chu Huang Dept. of Electronic Eng. National Changhua University of Ed. Email: tch@cc. ncue. edu. tw 2015/09/10 HDL T. -C. Huang / NCUE Fall 2015 1

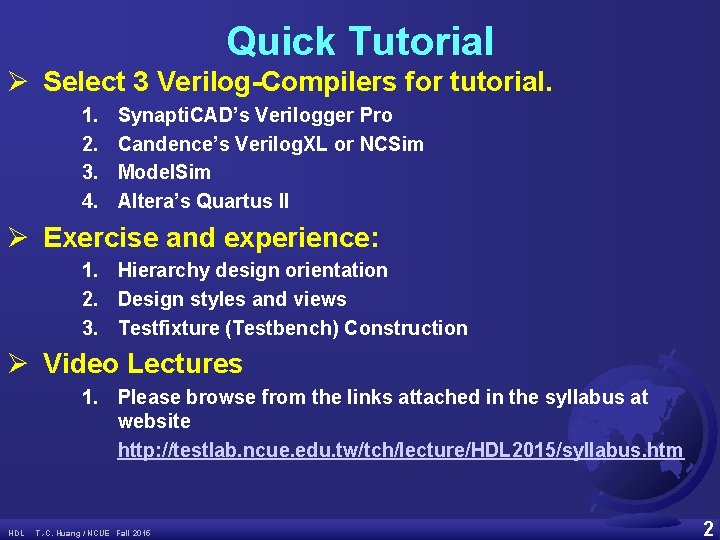

Quick Tutorial Ø Select 3 Verilog-Compilers for tutorial. 1. 2. 3. 4. Synapti. CAD’s Verilogger Pro Candence’s Verilog. XL or NCSim Model. Sim Altera’s Quartus II Ø Exercise and experience: 1. Hierarchy design orientation 2. Design styles and views 3. Testfixture (Testbench) Construction Ø Video Lectures 1. Please browse from the links attached in the syllabus at website http: //testlab. ncue. edu. tw/tch/lecture/HDL 2015/syllabus. htm HDL T. -C. Huang / NCUE Fall 2015 2

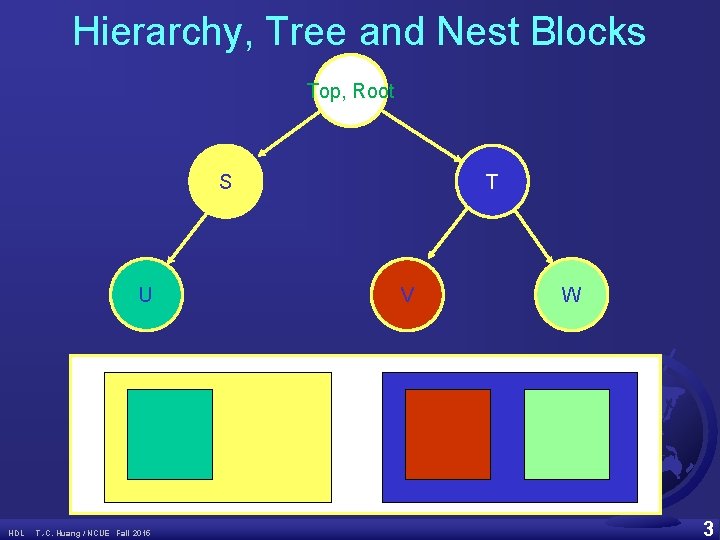

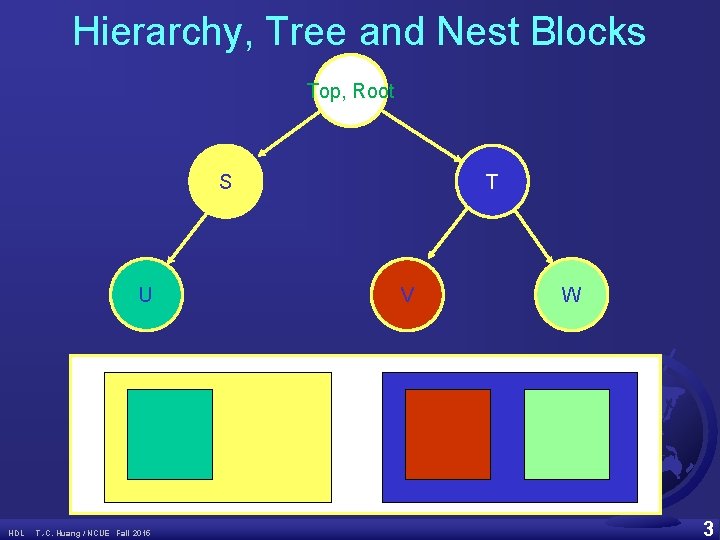

Hierarchy, Tree and Nest Blocks Top, Root S U HDL T. -C. Huang / NCUE Fall 2015 T V W 3

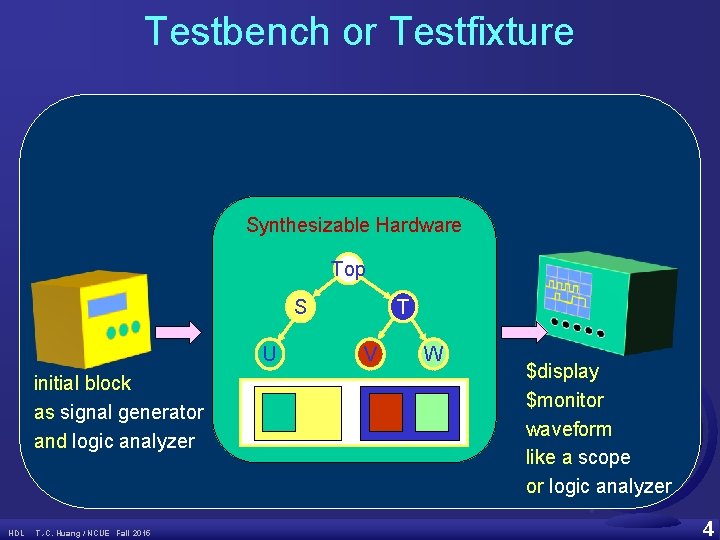

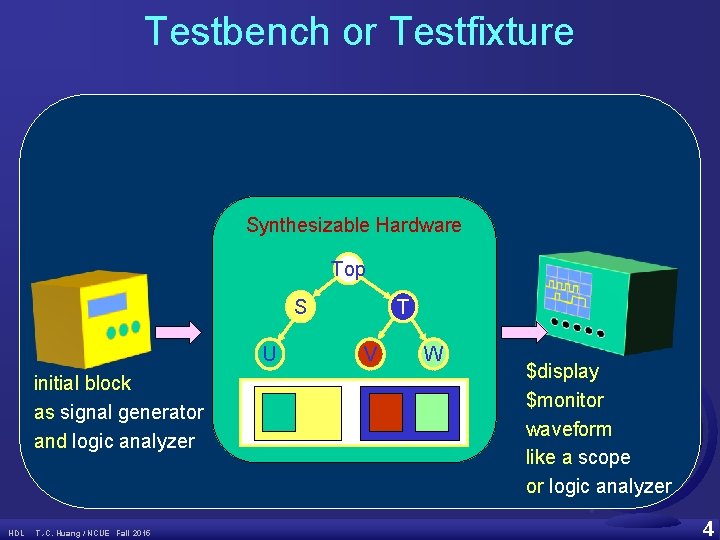

Testbench or Testfixture Synthesizable Hardware Top S U initial block as signal generator and logic analyzer HDL T. -C. Huang / NCUE Fall 2015 T V W $display $monitor waveform like a scope or logic analyzer 4

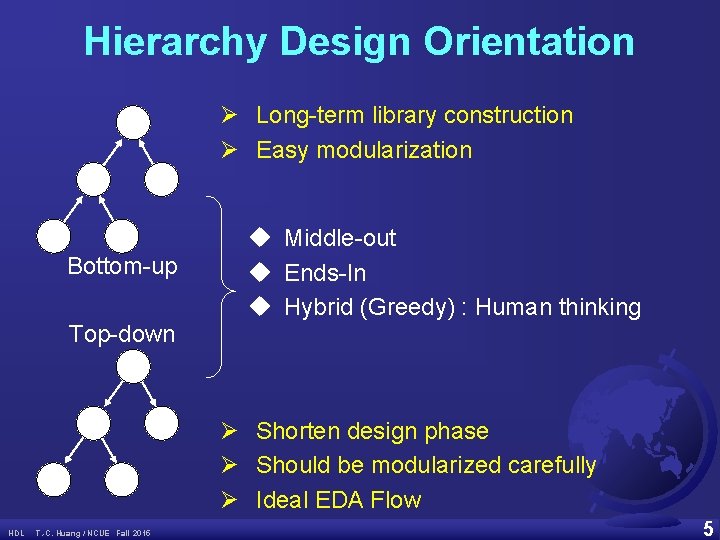

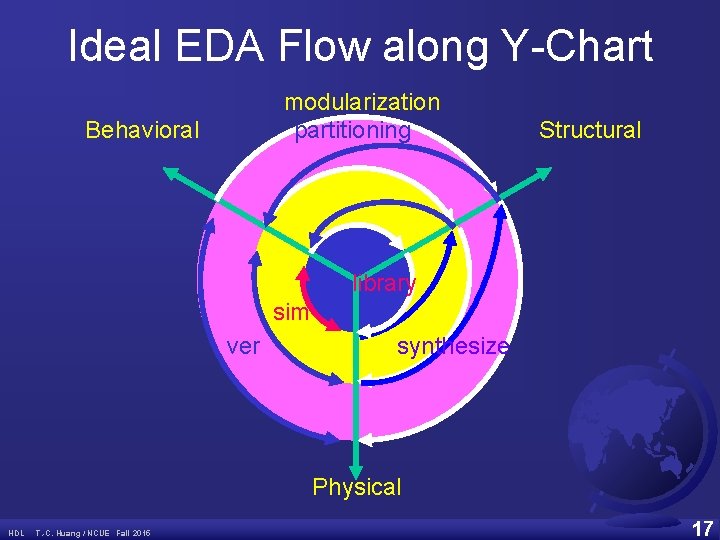

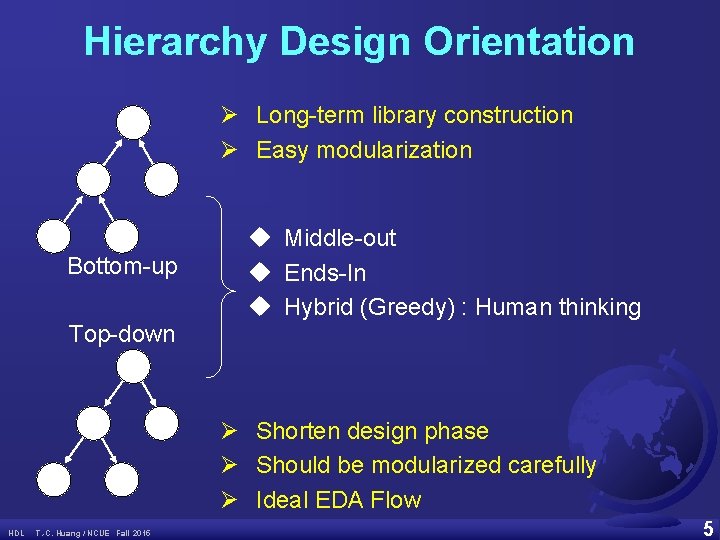

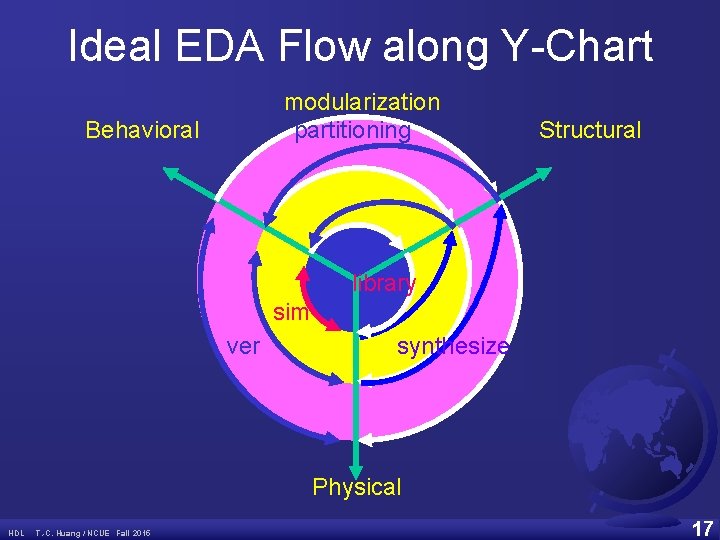

Hierarchy Design Orientation Ø Long-term library construction Ø Easy modularization Bottom-up u Middle-out u Ends-In u Hybrid (Greedy) : Human thinking Top-down Ø Shorten design phase Ø Should be modularized carefully Ø Ideal EDA Flow HDL T. -C. Huang / NCUE Fall 2015 5

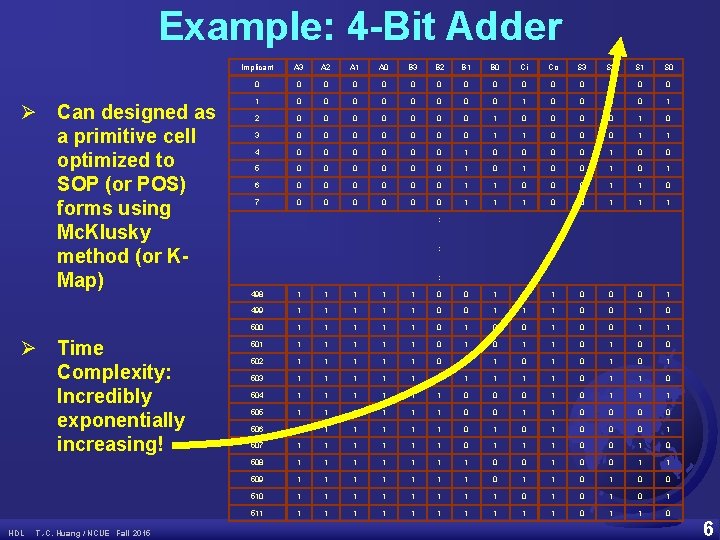

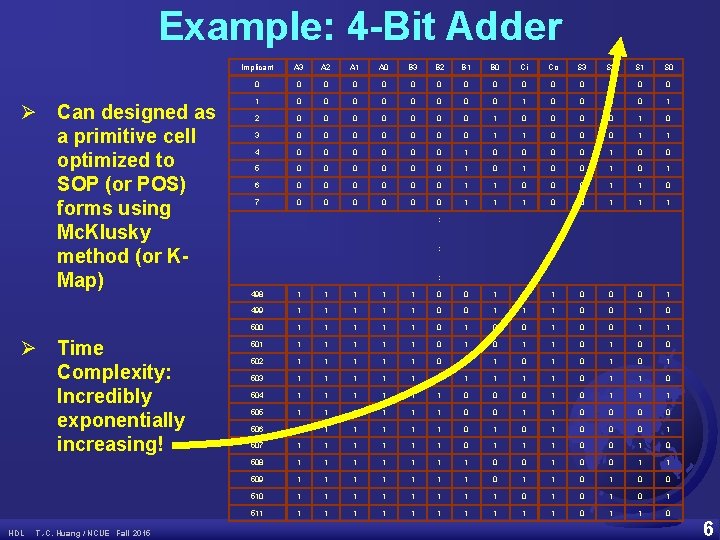

Example: 4 -Bit Adder Ø Can designed as a primitive cell optimized to SOP (or POS) forms using Mc. Klusky method (or KMap) Ø Time Complexity: Incredibly exponentially increasing! HDL T. -C. Huang / NCUE Fall 2015 Implicant A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 Ci Co S 3 S 2 S 1 S 0 0 0 0 1 0 0 0 0 1 2 0 0 0 0 1 0 3 0 0 0 0 1 1 4 0 0 0 1 0 0 5 0 0 0 1 6 0 0 0 1 1 0 7 0 0 0 1 1 1 : 498 1 1 1 0 0 0 1 499 1 1 1 0 0 1 0 500 1 1 1 0 0 1 1 501 1 1 0 0 502 1 1 1 0 1 0 1 503 1 1 1 0 1 1 0 504 1 1 1 0 0 0 1 1 1 505 1 1 1 0 0 506 1 1 1 0 1 0 0 0 1 507 1 1 1 0 0 1 0 508 1 1 1 1 0 0 1 1 509 1 1 1 1 0 1 0 0 510 1 1 1 1 0 1 0 1 511 1 1 0 1 1 0 6

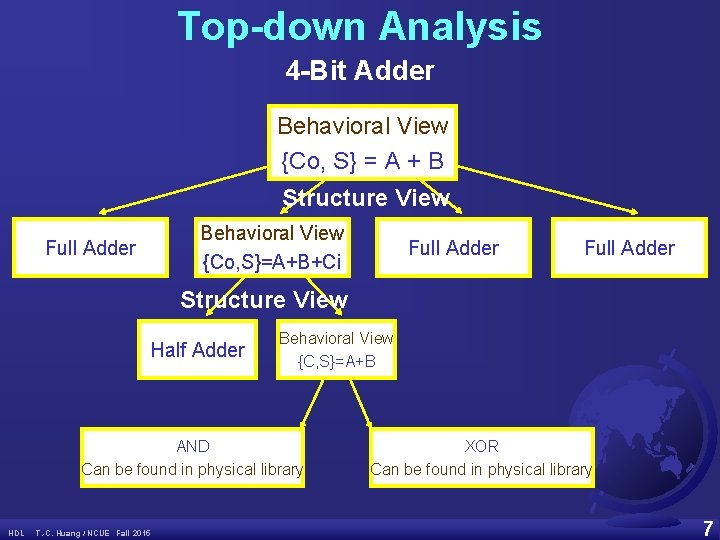

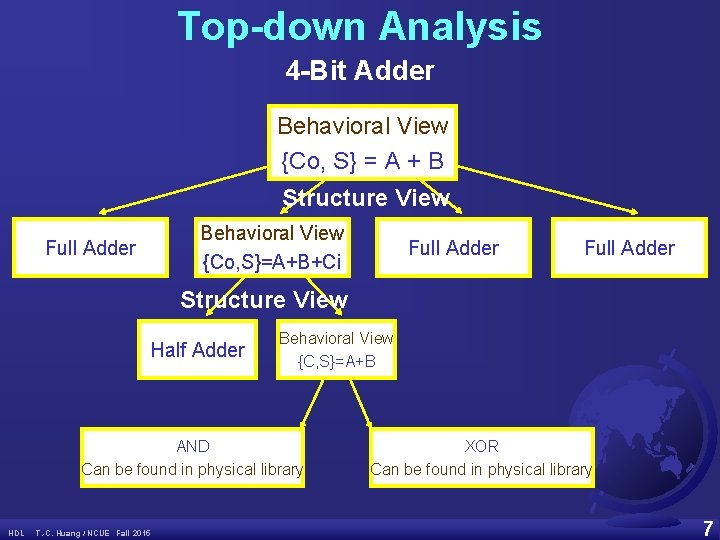

Top-down Analysis 4 -Bit Adder Behavioral View {Co, S} = A + B Structure View Behavioral View Full Adder {Co, S}=A+B+Ci Full Adder Structure View Half Adder Behavioral View Half Adder {C, S}=A+B AND Can be found in physical library HDL T. -C. Huang / NCUE Fall 2015 XOR Can be found in physical library 7

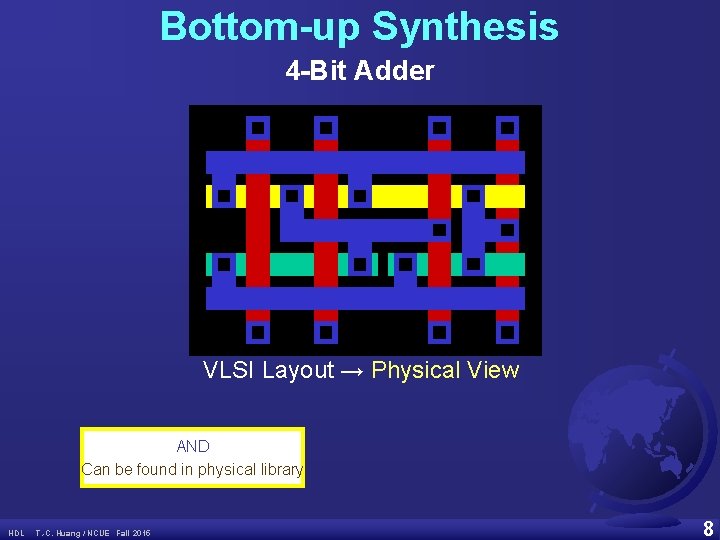

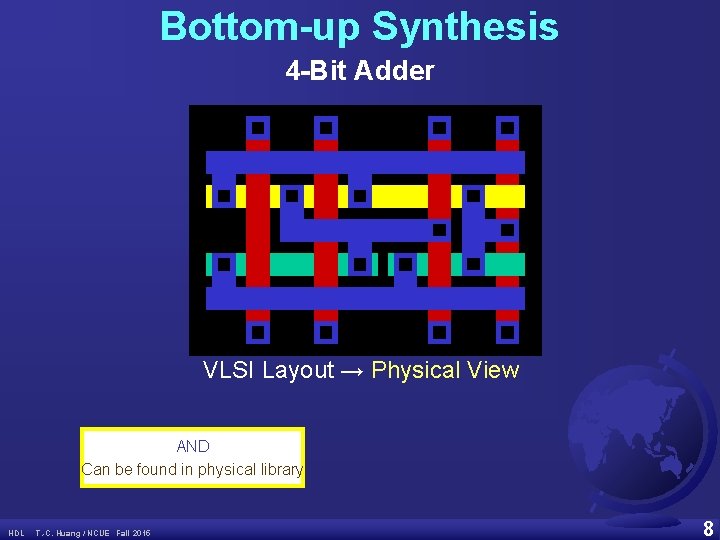

Bottom-up Synthesis 4 -Bit Adder VLSI Layout → Physical View AND Can be found in physical library HDL T. -C. Huang / NCUE Fall 2015 8

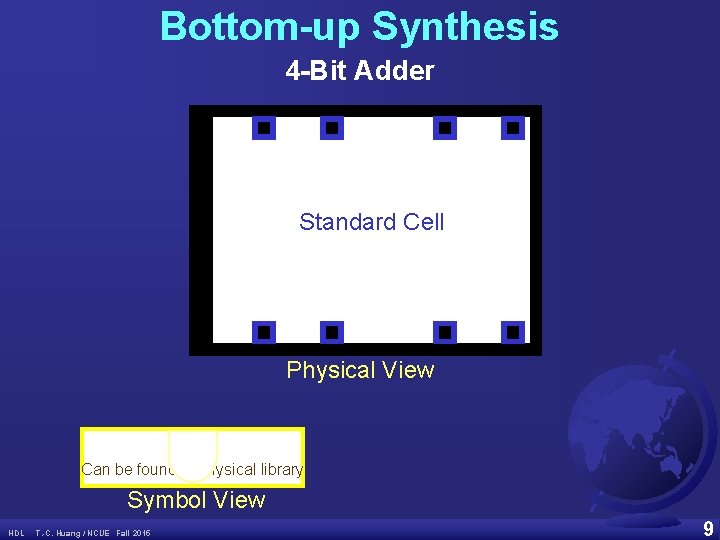

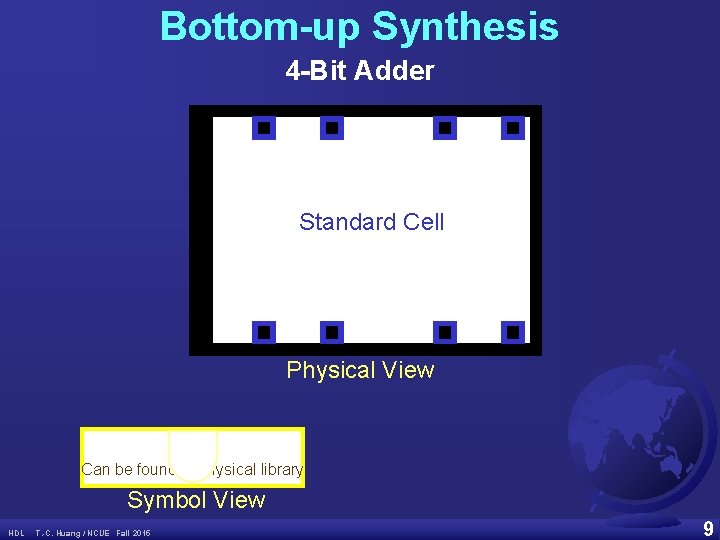

Bottom-up Synthesis 4 -Bit Adder Standard Cell Physical View AND Can be found in physical library Symbol View HDL T. -C. Huang / NCUE Fall 2015 9

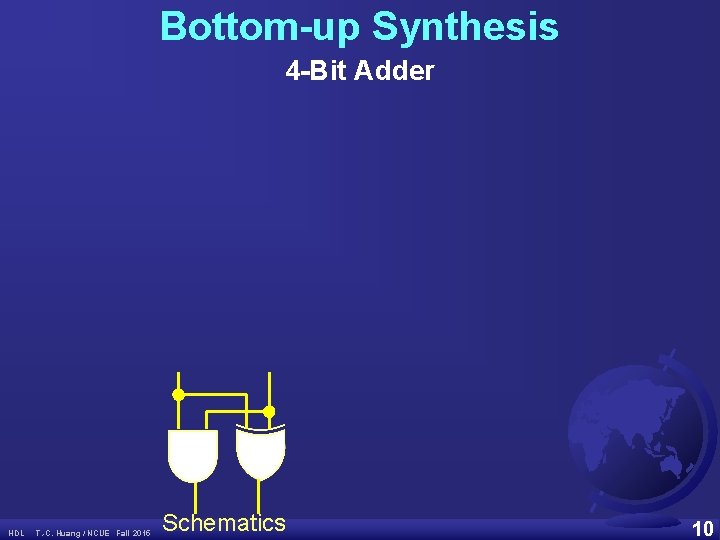

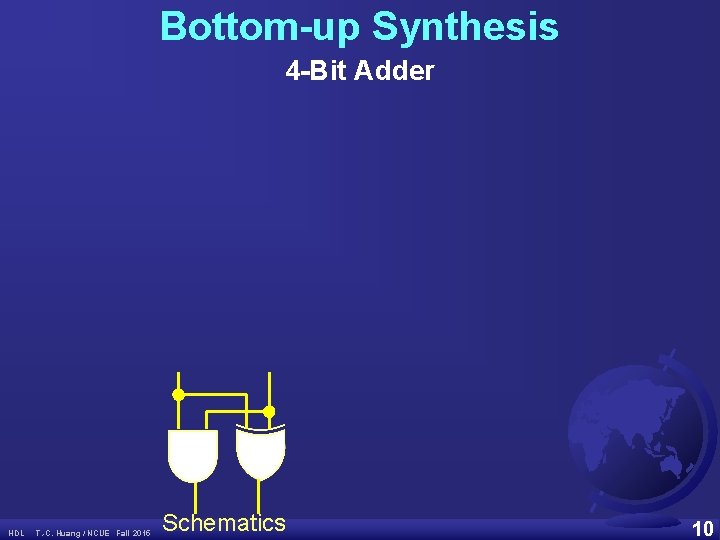

Bottom-up Synthesis 4 -Bit Adder HDL T. -C. Huang / NCUE Fall 2015 Schematics 10

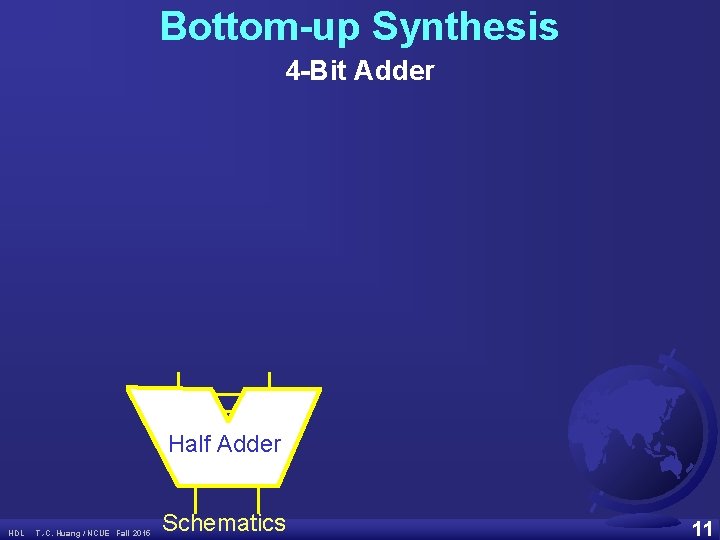

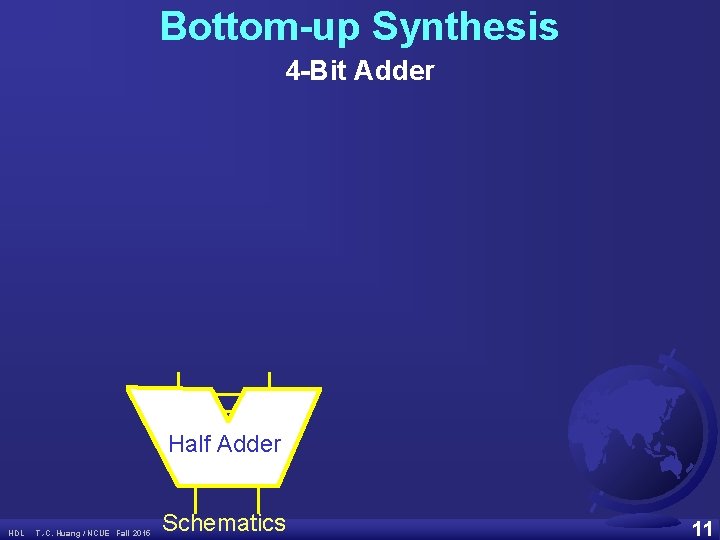

Bottom-up Synthesis 4 -Bit Adder Half Adder HDL T. -C. Huang / NCUE Fall 2015 Schematics 11

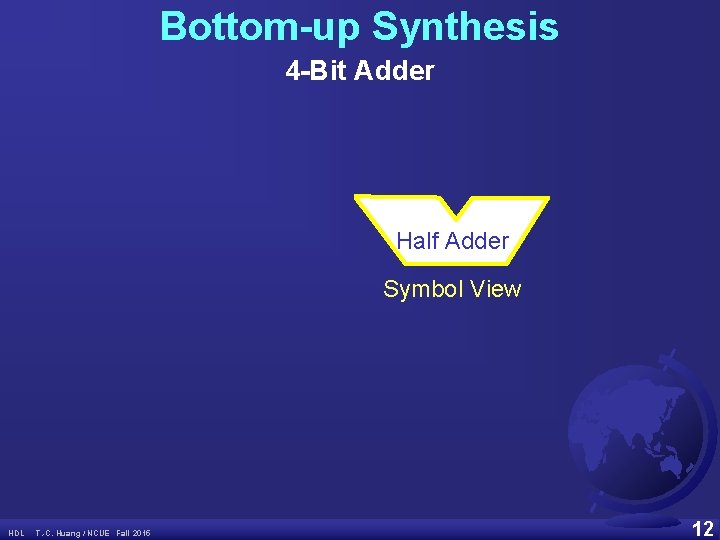

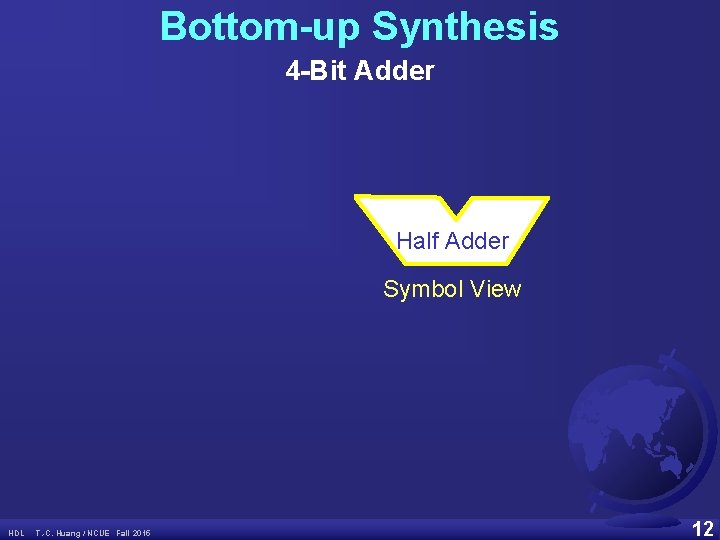

Bottom-up Synthesis 4 -Bit Adder Half Adder Symbol View HDL T. -C. Huang / NCUE Fall 2015 12

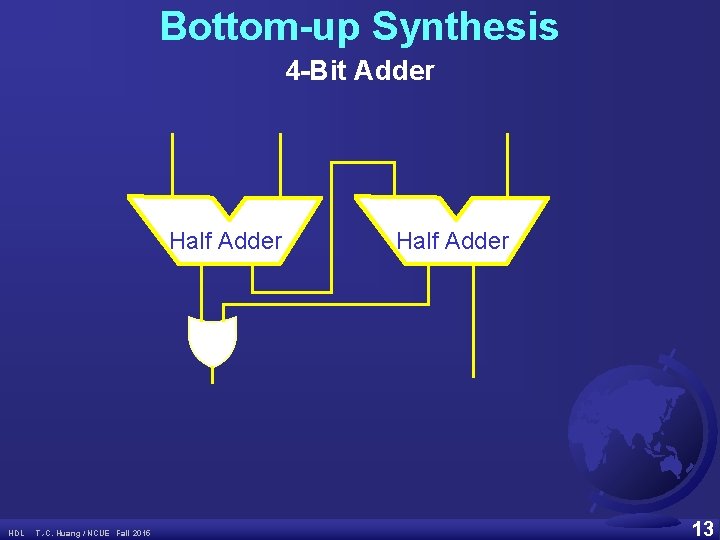

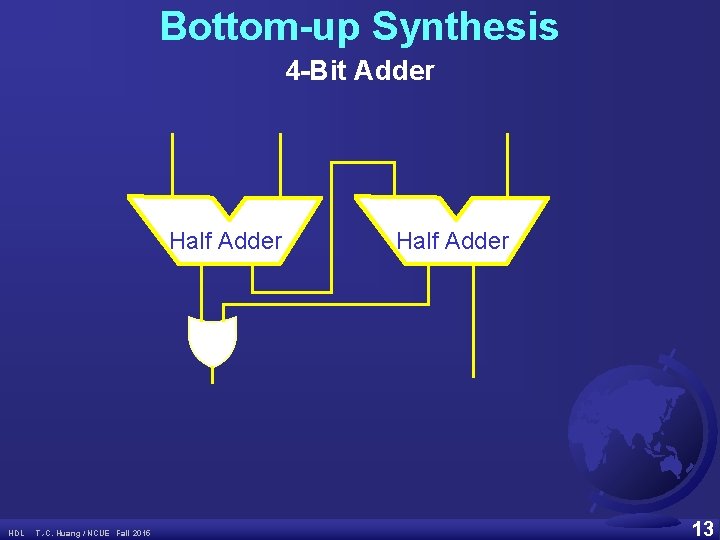

Bottom-up Synthesis 4 -Bit Adder Half Adder HDL T. -C. Huang / NCUE Fall 2015 Half Adder 13

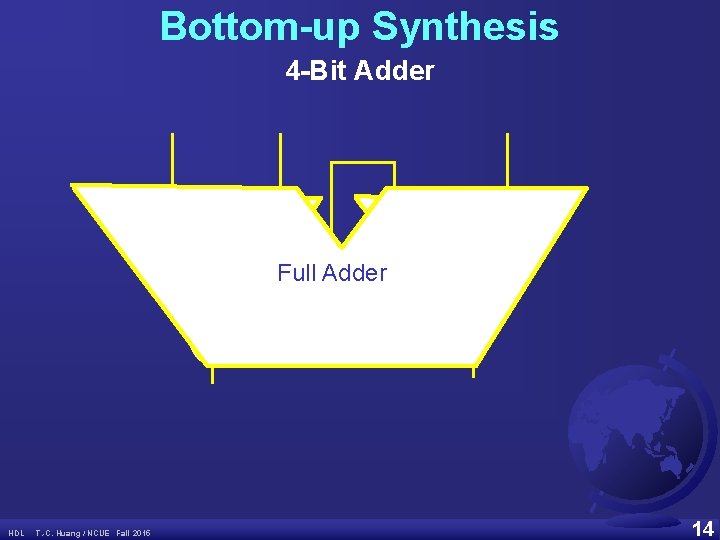

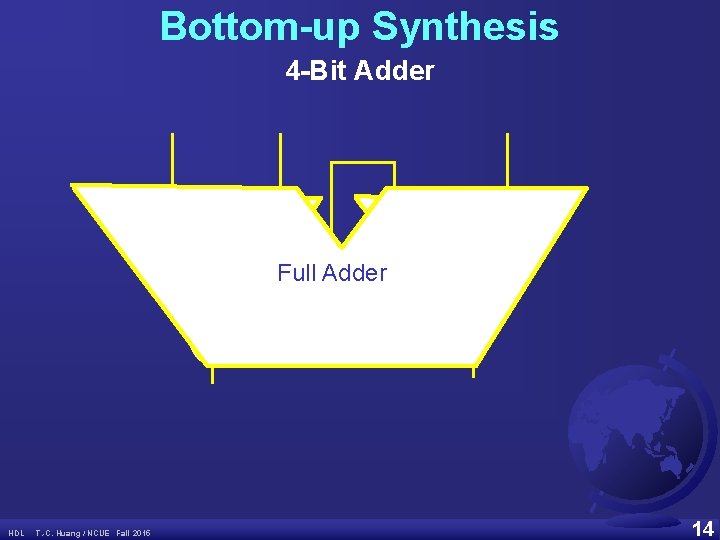

Bottom-up Synthesis 4 -Bit Adder Half Adder Full Adder HDL T. -C. Huang / NCUE Fall 2015 14

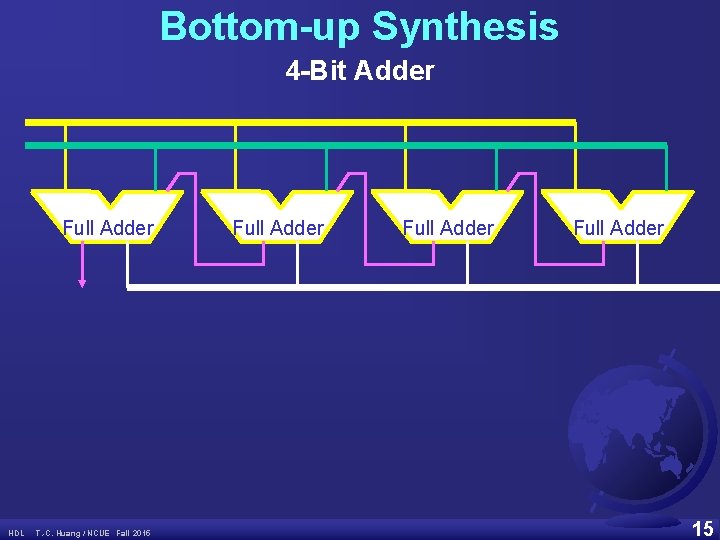

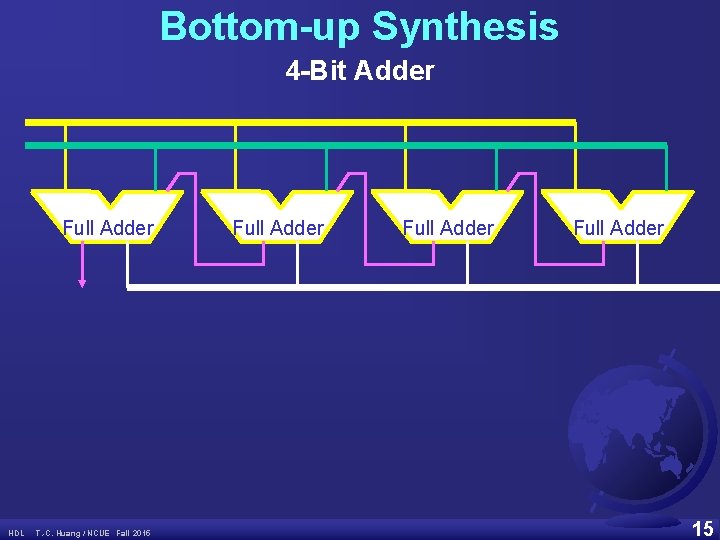

Bottom-up Synthesis 4 -Bit Adder Full Adder HDL T. -C. Huang / NCUE Fall 2015 Full Adder 15

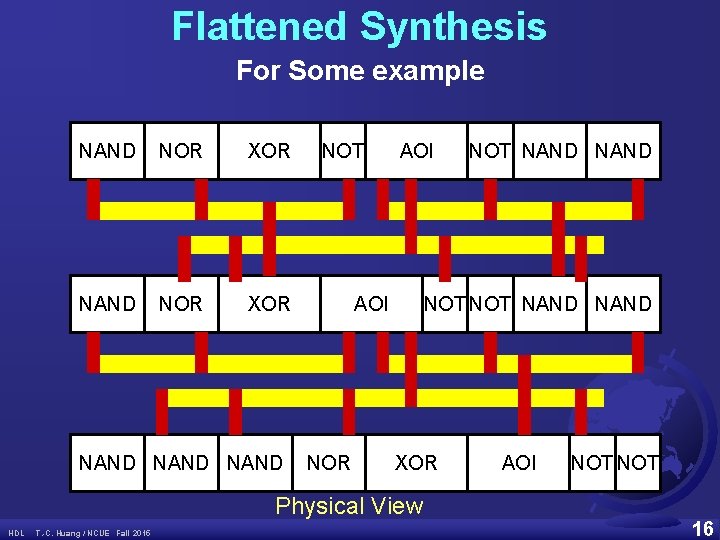

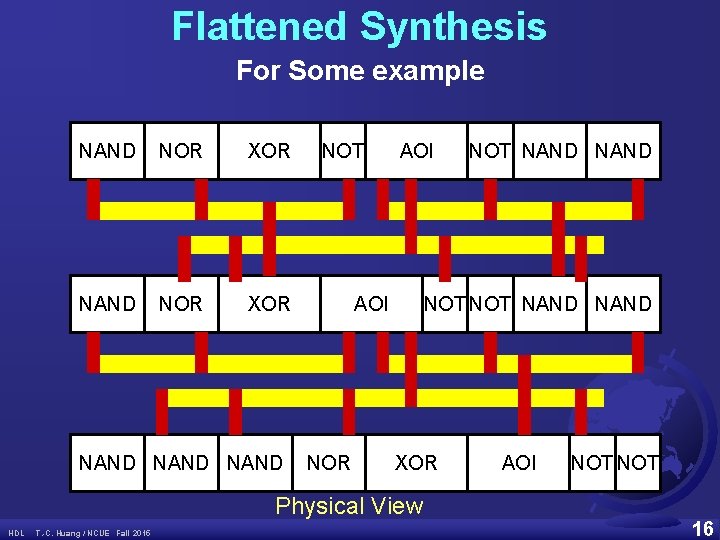

Flattened Synthesis For Some example NAND NOR XOR NAND NOT AOI NOR NOT NAND XOR Physical View HDL T. -C. Huang / NCUE Fall 2015 NOT NAND AOI NOT 16

Ideal EDA Flow along Y-Chart modularization partitioning Behavioral Structural library sim ver synthesize Physical HDL T. -C. Huang / NCUE Fall 2015 17

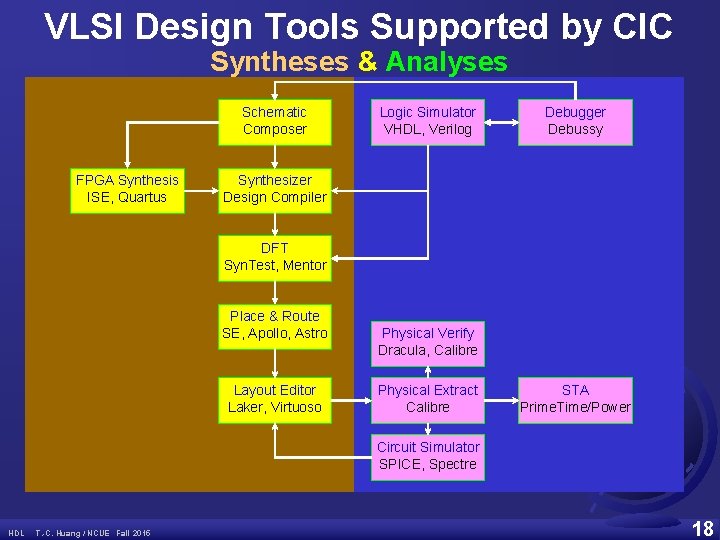

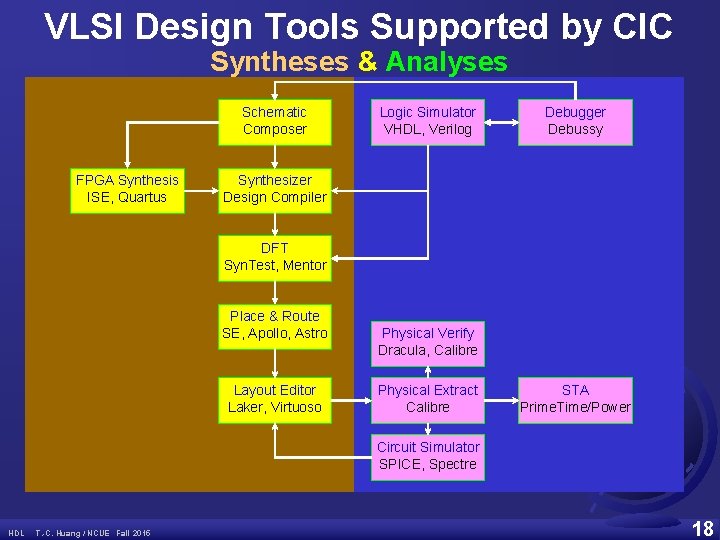

VLSI Design Tools Supported by CIC Syntheses & Analyses Schematic Composer FPGA Synthesis ISE, Quartus Logic Simulator VHDL, Verilog Debugger Debussy Synthesizer Design Compiler DFT Syn. Test, Mentor Place & Route SE, Apollo, Astro Layout Editor Laker, Virtuoso Physical Verify Dracula, Calibre Physical Extract Calibre STA Prime. Time/Power Circuit Simulator SPICE, Spectre HDL T. -C. Huang / NCUE Fall 2015 18

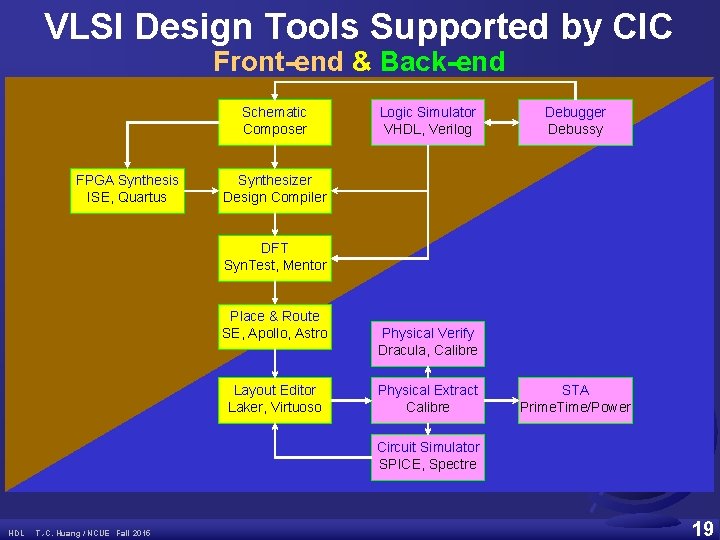

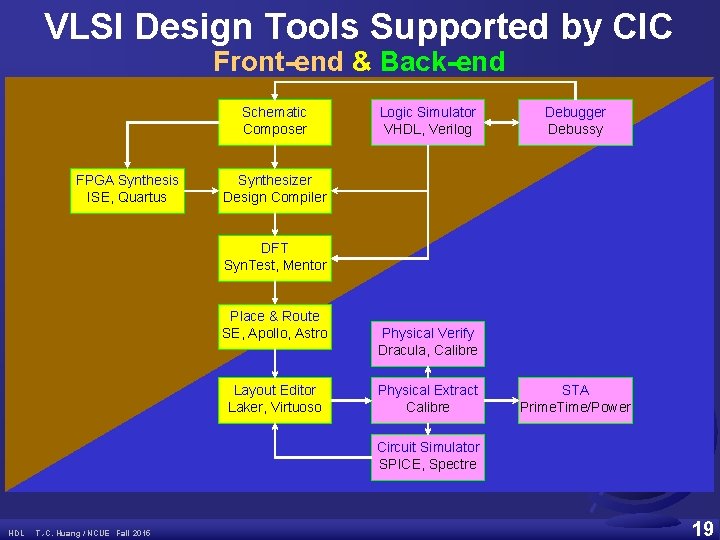

VLSI Design Tools Supported by CIC Front-end & Back-end Schematic Composer FPGA Synthesis ISE, Quartus Logic Simulator VHDL, Verilog Debugger Debussy Synthesizer Design Compiler DFT Syn. Test, Mentor Place & Route SE, Apollo, Astro Layout Editor Laker, Virtuoso Physical Verify Dracula, Calibre Physical Extract Calibre STA Prime. Time/Power Circuit Simulator SPICE, Spectre HDL T. -C. Huang / NCUE Fall 2015 19

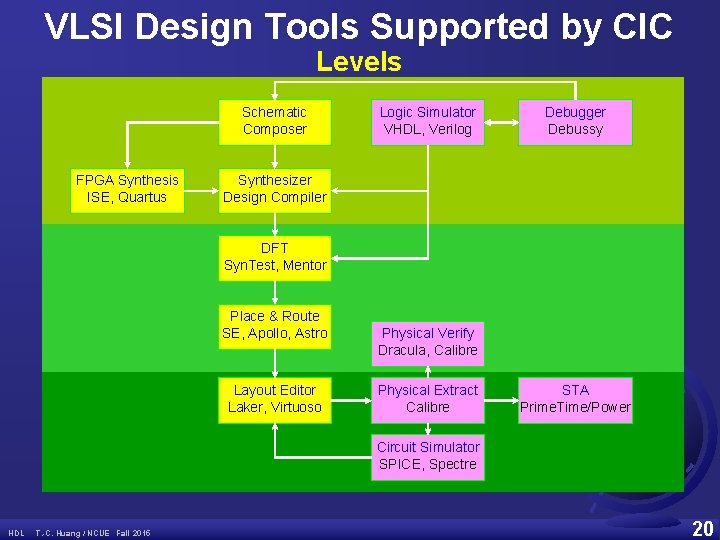

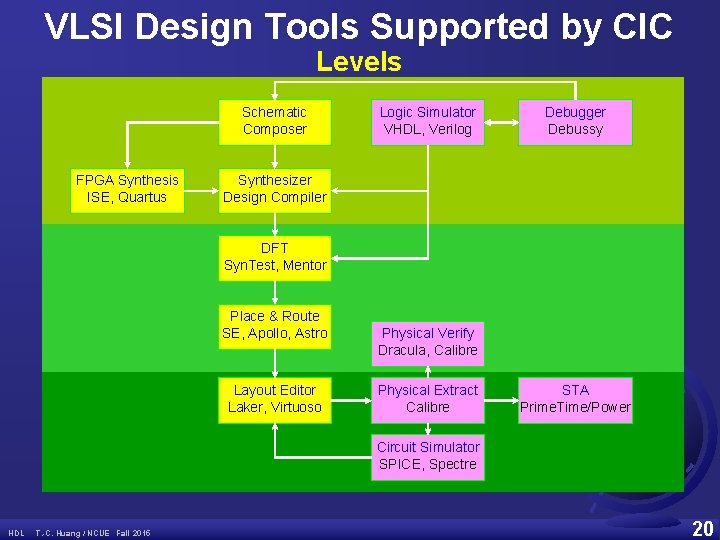

VLSI Design Tools Supported by CIC Levels Schematic Composer FPGA Synthesis ISE, Quartus Logic Simulator VHDL, Verilog Debugger Debussy Synthesizer Design Compiler DFT Syn. Test, Mentor Place & Route SE, Apollo, Astro Layout Editor Laker, Virtuoso Physical Verify Dracula, Calibre Physical Extract Calibre STA Prime. Time/Power Circuit Simulator SPICE, Spectre HDL T. -C. Huang / NCUE Fall 2015 20

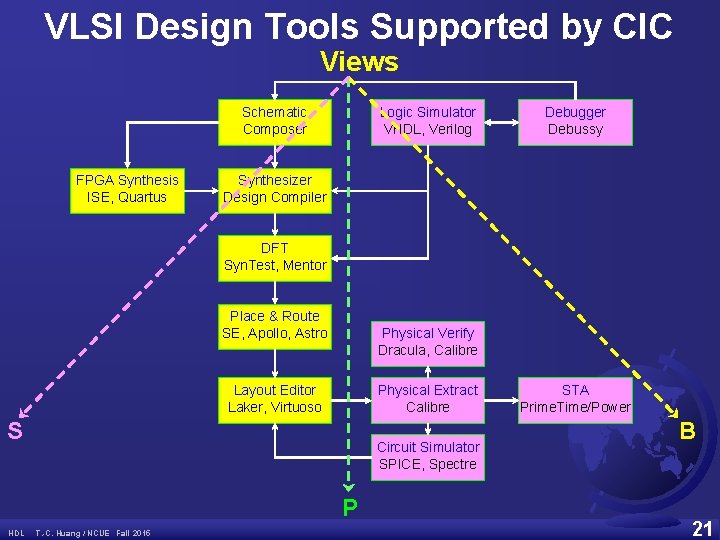

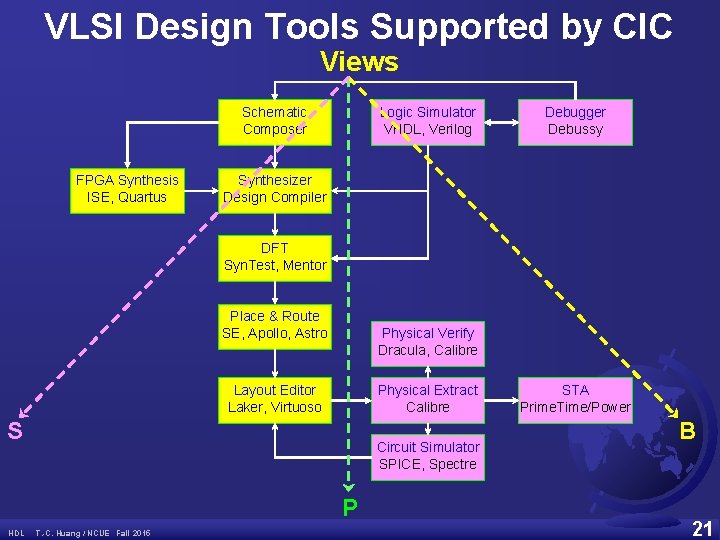

VLSI Design Tools Supported by CIC Views Schematic Composer FPGA Synthesis ISE, Quartus Logic Simulator VHDL, Verilog Debugger Debussy Synthesizer Design Compiler DFT Syn. Test, Mentor Place & Route SE, Apollo, Astro Physical Verify Dracula, Calibre Layout Editor Laker, Virtuoso Physical Extract Calibre S Circuit Simulator SPICE, Spectre P HDL T. -C. Huang / NCUE Fall 2015 STA Prime. Time/Power B 21