Hardware Description Language Logic Design using Verilog TsungChu

- Slides: 12

Hardware Description Language -- Logic Design using Verilog Tsung-Chu Huang Dept. of Electronic Eng. National Changhua University of Ed. Email: tch@cc. ncue. edu. tw 2014/10/30 HDL T. -C. Huang / NCUE Fall 2005 1

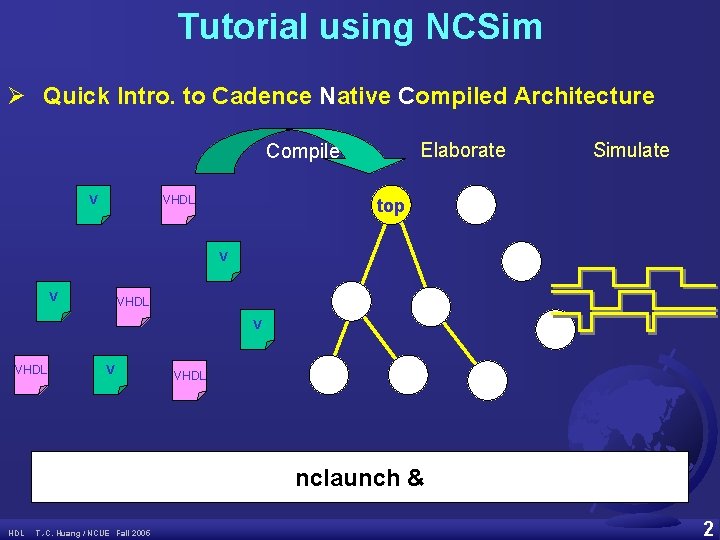

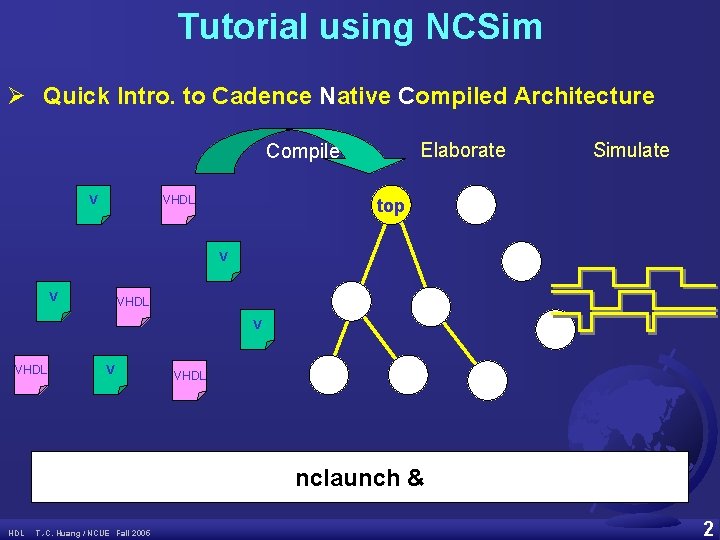

Tutorial using NCSim Ø Quick Intro. to Cadence Native Compiled Architecture Elaborate Compile V VHDL Simulate top V V VHDL nclaunch & HDL T. -C. Huang / NCUE Fall 2005 2

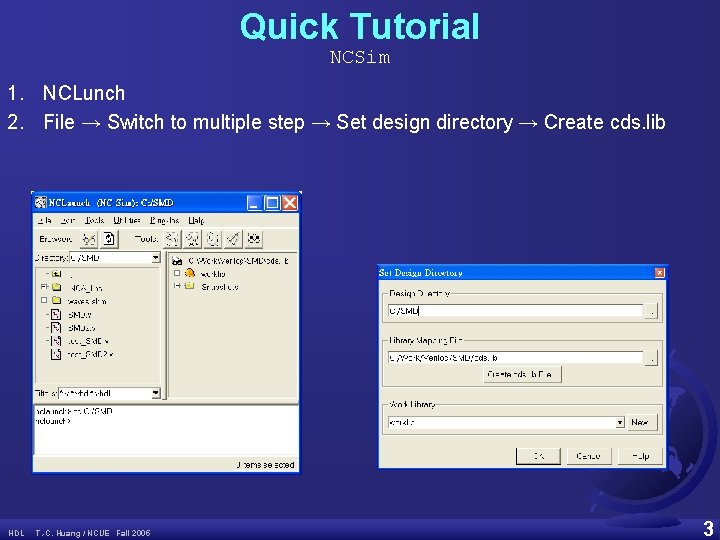

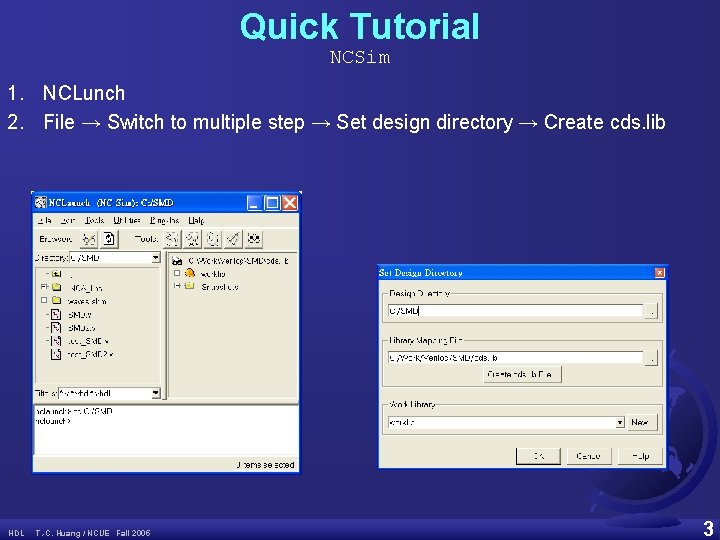

Quick Tutorial NCSim 1. NCLunch 2. File → Switch to multiple step → Set design directory → Create cds. lib HDL T. -C. Huang / NCUE Fall 2005 3

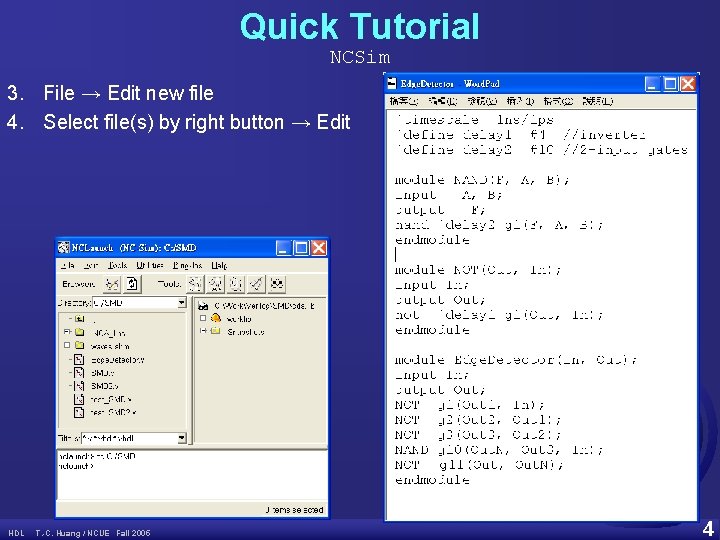

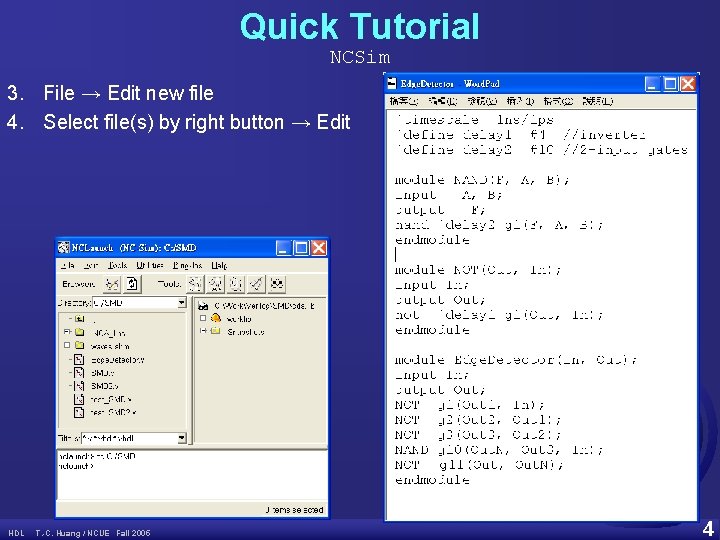

Quick Tutorial NCSim 3. File → Edit new file 4. Select file(s) by right button → Edit HDL T. -C. Huang / NCUE Fall 2005 4

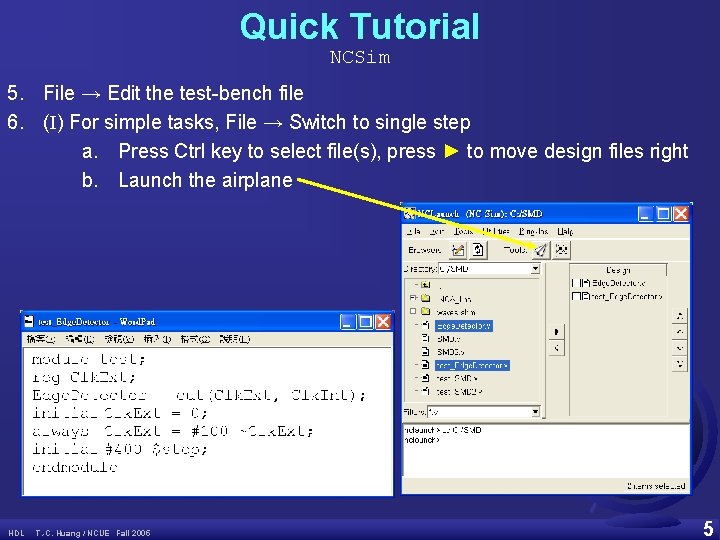

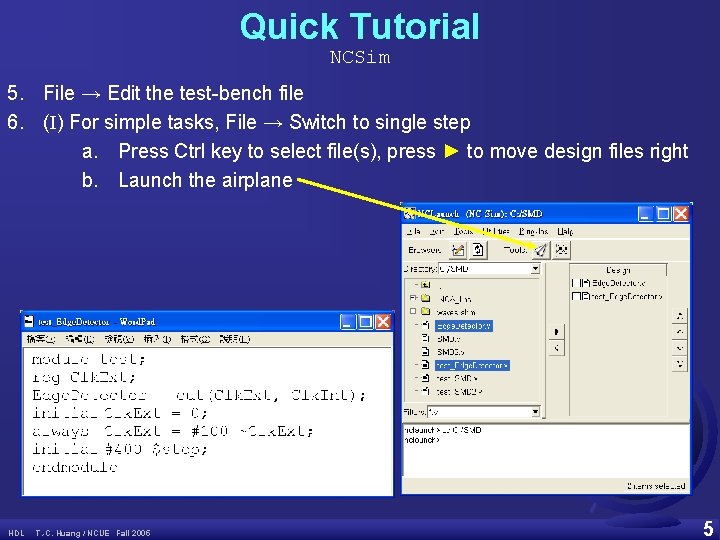

Quick Tutorial NCSim 5. File → Edit the test-bench file 6. (I) For simple tasks, File → Switch to single step a. Press Ctrl key to select file(s), press ► to move design files right b. Launch the airplane HDL T. -C. Huang / NCUE Fall 2005 5

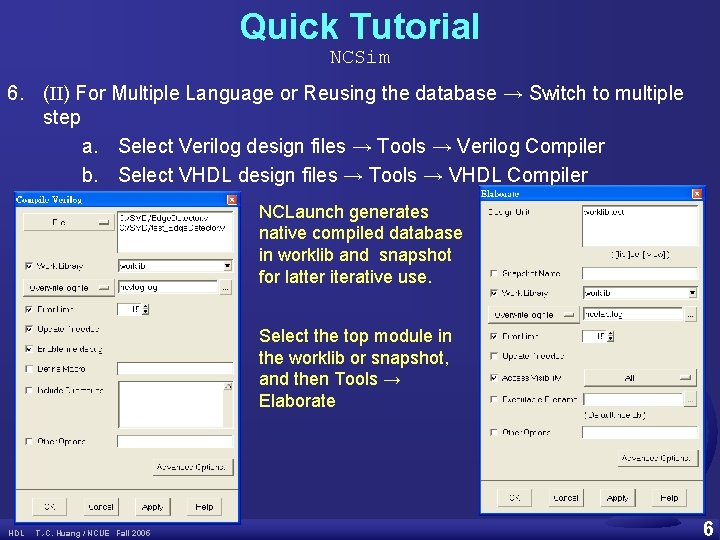

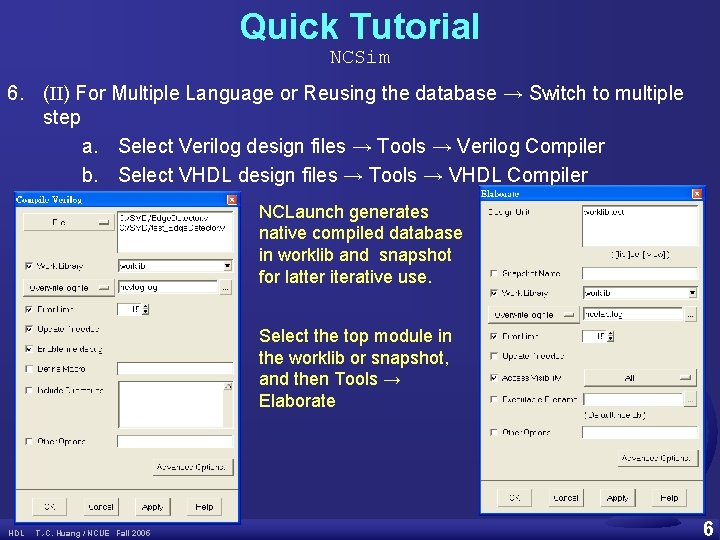

Quick Tutorial NCSim 6. (II) For Multiple Language or Reusing the database → Switch to multiple step a. Select Verilog design files → Tools → Verilog Compiler b. Select VHDL design files → Tools → VHDL Compiler NCLaunch generates native compiled database in worklib and snapshot for latter iterative use. Select the top module in the worklib or snapshot, and then Tools → Elaborate HDL T. -C. Huang / NCUE Fall 2005 6

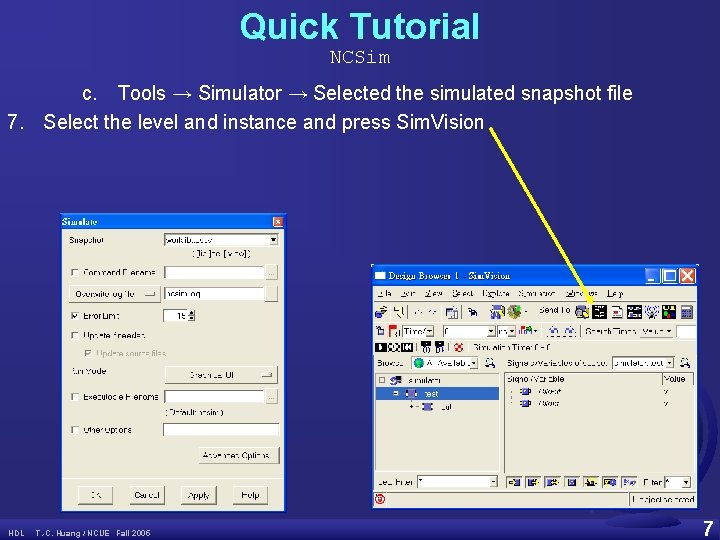

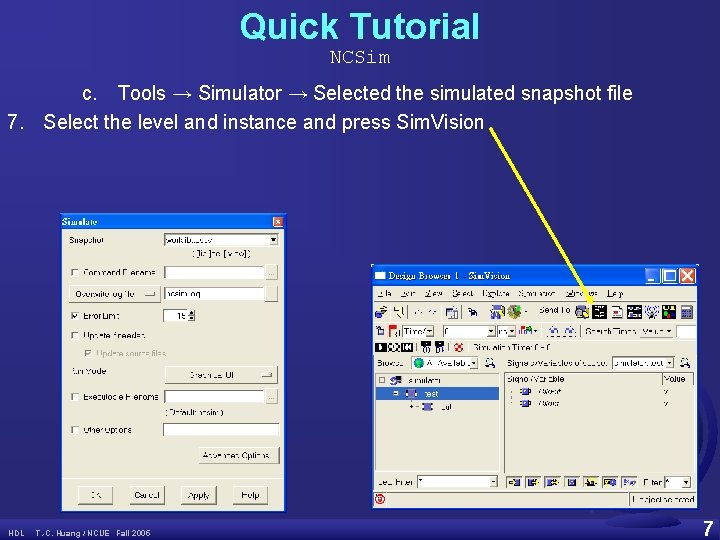

Quick Tutorial NCSim c. Tools → Simulator → Selected the simulated snapshot file 7. Select the level and instance and press Sim. Vision HDL T. -C. Huang / NCUE Fall 2005 7

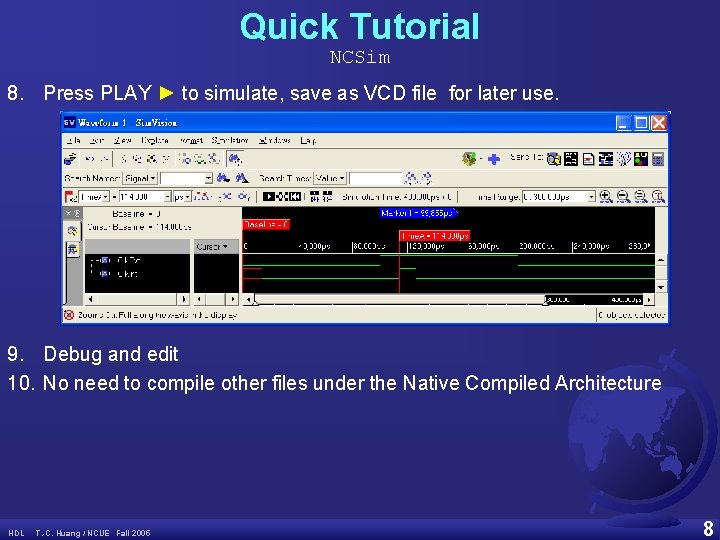

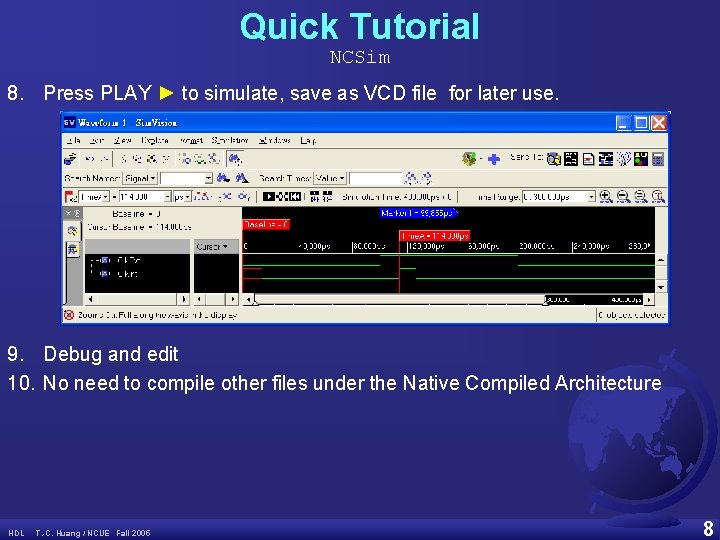

Quick Tutorial NCSim 8. Press PLAY ► to simulate, save as VCD file for later use. 9. Debug and edit 10. No need to compile other files under the Native Compiled Architecture HDL T. -C. Huang / NCUE Fall 2005 8

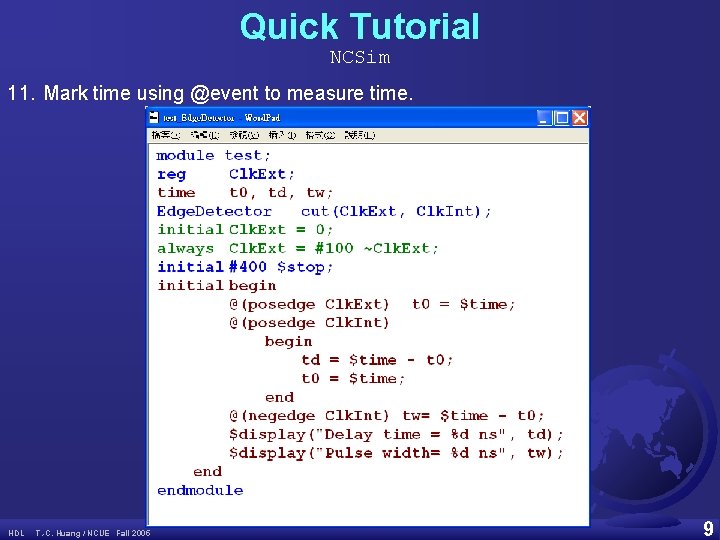

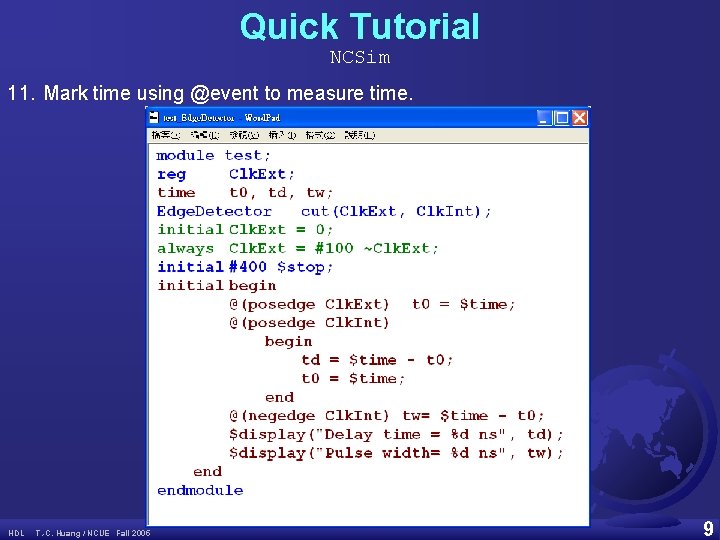

Quick Tutorial NCSim 11. Mark time using @event to measure time. HDL T. -C. Huang / NCUE Fall 2005 9

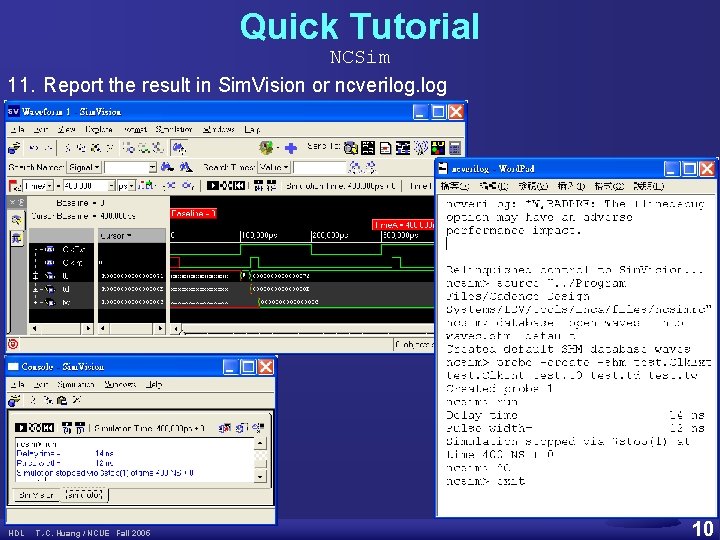

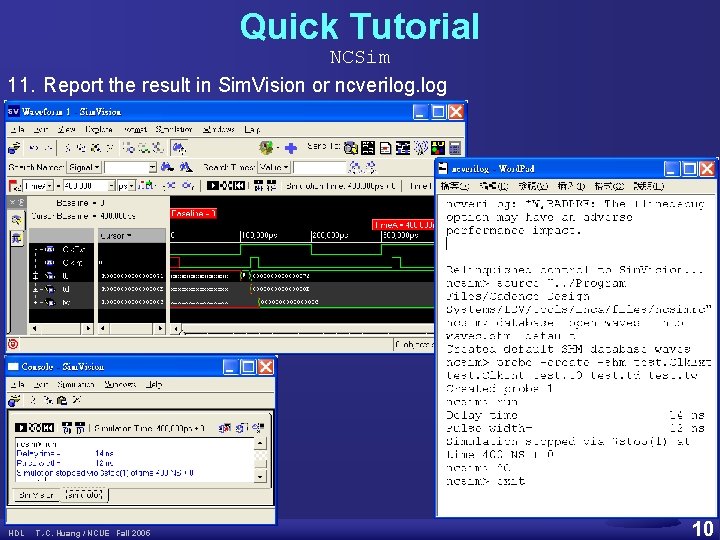

Quick Tutorial NCSim 11. Report the result in Sim. Vision or ncverilog. log HDL T. -C. Huang / NCUE Fall 2005 10

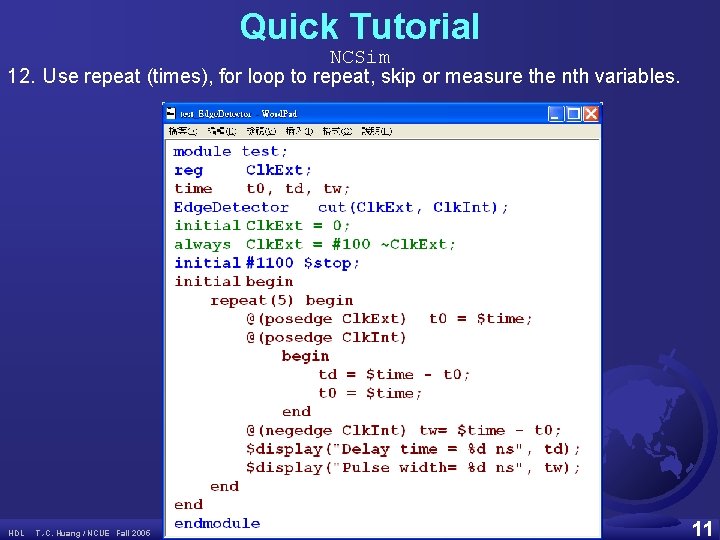

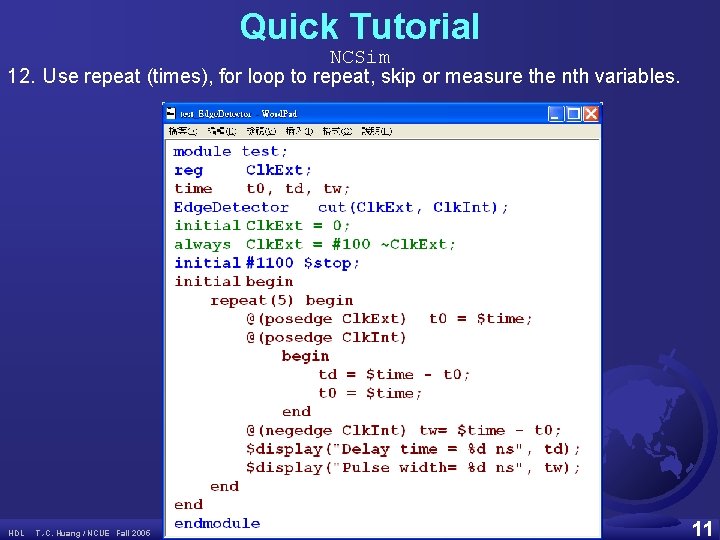

Quick Tutorial NCSim 12. Use repeat (times), for loop to repeat, skip or measure the nth variables. HDL T. -C. Huang / NCUE Fall 2005 11

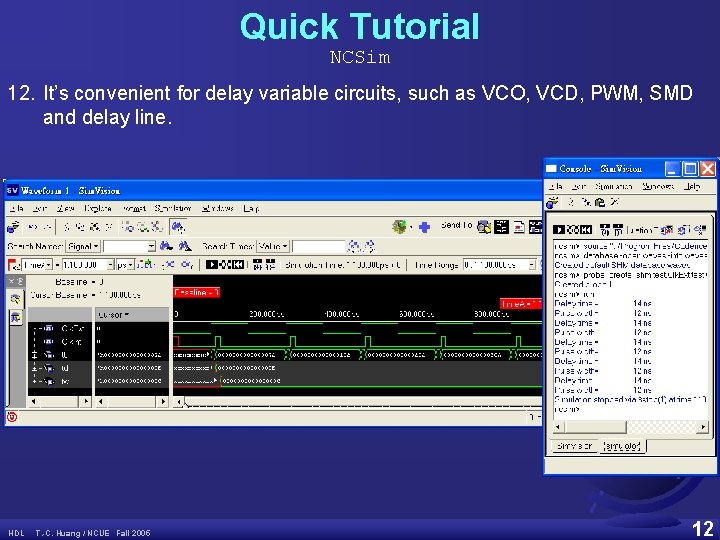

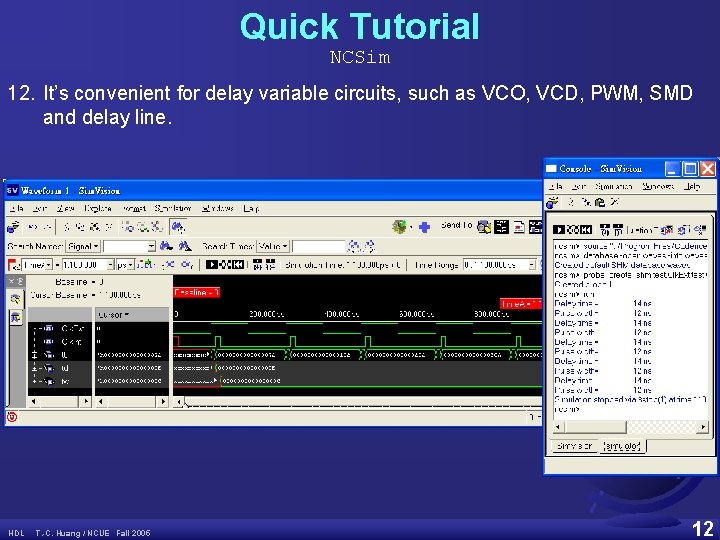

Quick Tutorial NCSim 12. It’s convenient for delay variable circuits, such as VCO, VCD, PWM, SMD and delay line. HDL T. -C. Huang / NCUE Fall 2005 12