Hardware Description Language Logic Design using Verilog TsungChu

![Instruction Cycle IR←M[AD] T. -C. Huang / NCUE Fall 2005 e c e D Instruction Cycle IR←M[AD] T. -C. Huang / NCUE Fall 2005 e c e D](https://slidetodoc.com/presentation_image/01588a18fef1766065a38955aa3eecc3/image-7.jpg)

- Slides: 16

Hardware Description Language -- Logic Design using Verilog Tsung-Chu Huang Dept. of Electronic Eng. National Changhua University of Ed. Email: tch@cc. ncue. edu. tw 2011/12/01 HDL T. -C. Huang / NCUE Fall 2005 1

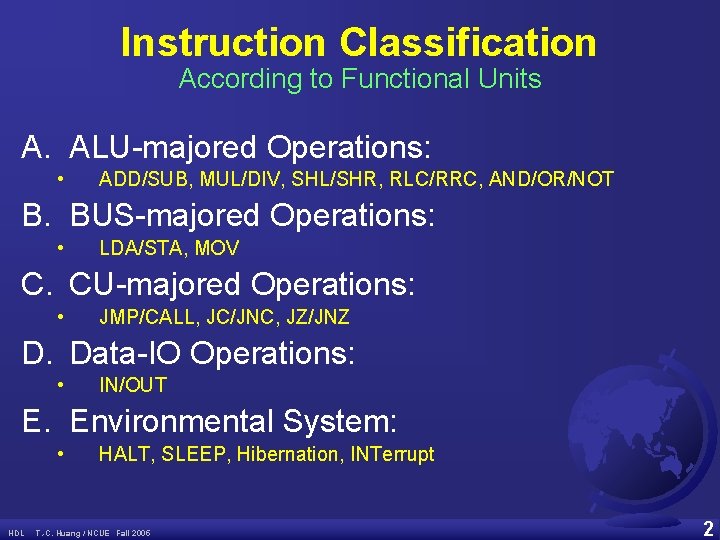

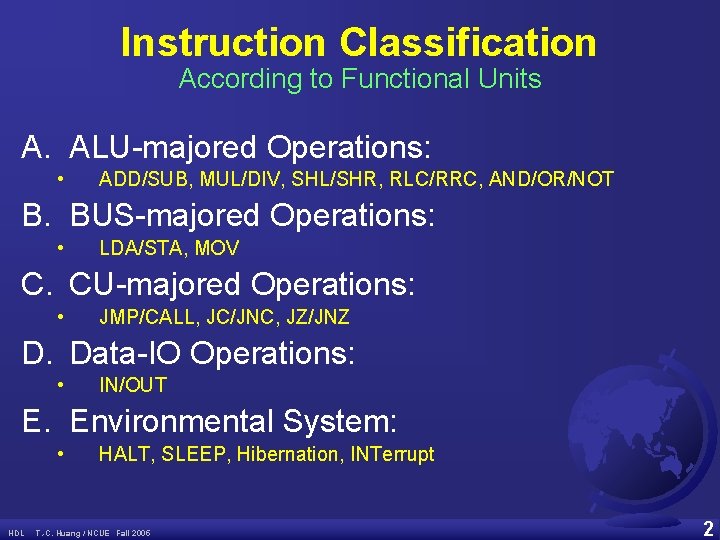

Instruction Classification According to Functional Units A. ALU-majored Operations: • ADD/SUB, MUL/DIV, SHL/SHR, RLC/RRC, AND/OR/NOT B. BUS-majored Operations: • LDA/STA, MOV C. CU-majored Operations: • JMP/CALL, JC/JNC, JZ/JNZ D. Data-IO Operations: • IN/OUT E. Environmental System: • HDL HALT, SLEEP, Hibernation, INTerrupt T. -C. Huang / NCUE Fall 2005 2

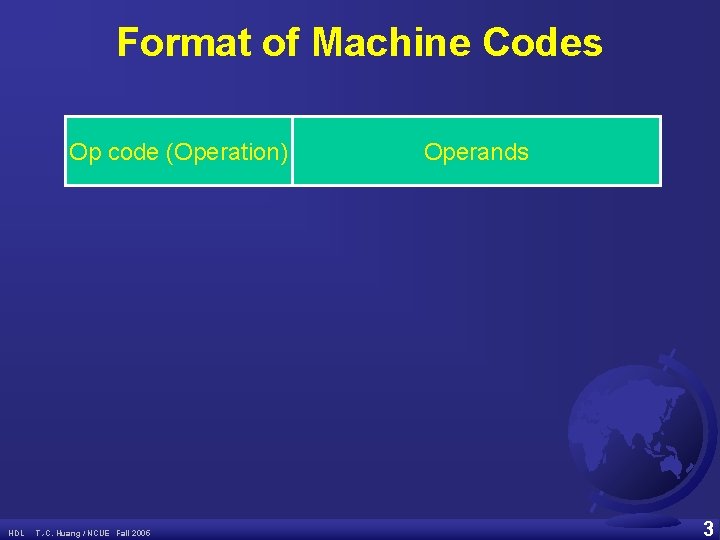

Format of Machine Codes Op code (Operation) HDL T. -C. Huang / NCUE Fall 2005 Operands 3

Instruction Classification According to Operand Count A. No Operand or Implied-1 -Operand • NOT, HLT, CLR, NOP B. One Operand • LDA/STA, JMP C. Two Operands • ADD/SUB D. More-than-2 Operands • HDL ADD Destination, R 1, R 2 T. -C. Huang / NCUE Fall 2005 4

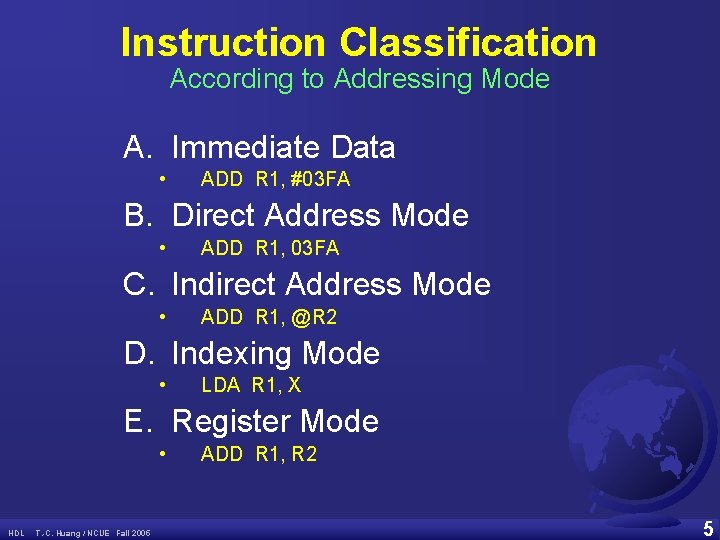

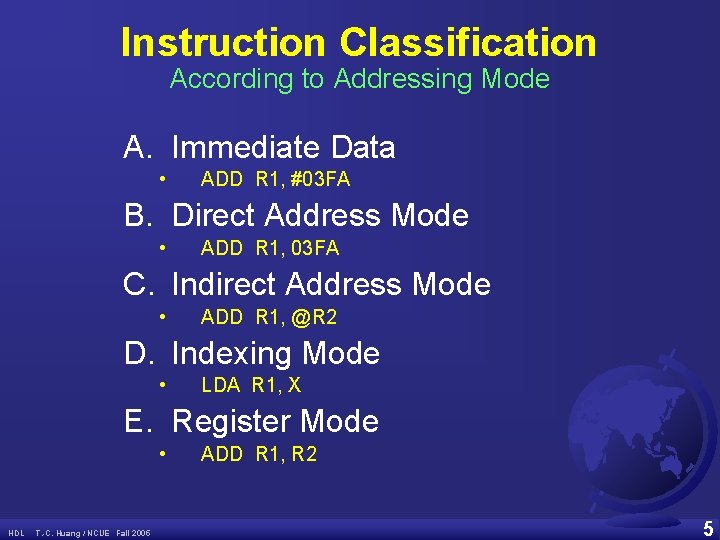

Instruction Classification According to Addressing Mode A. Immediate Data • ADD R 1, #03 FA B. Direct Address Mode • ADD R 1, 03 FA C. Indirect Address Mode • ADD R 1, @R 2 D. Indexing Mode • LDA R 1, X E. Register Mode • HDL T. -C. Huang / NCUE Fall 2005 ADD R 1, R 2 5

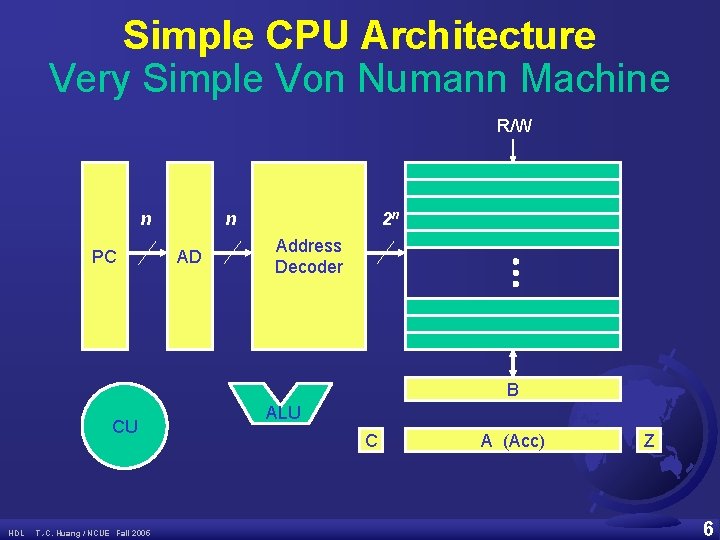

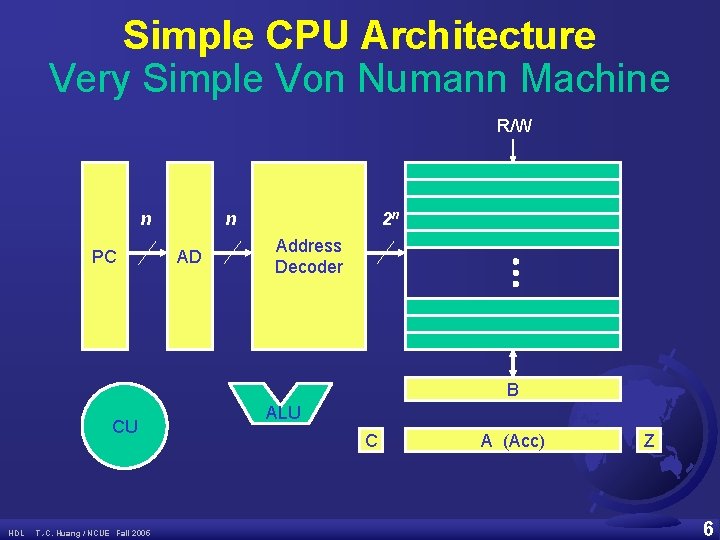

Simple CPU Architecture Very Simple Von Numann Machine R/W n PC n AD 2 n Address Decoder B CU HDL T. -C. Huang / NCUE Fall 2005 ALU C A (Acc) Z 6

![Instruction Cycle IRMAD T C Huang NCUE Fall 2005 e c e D Instruction Cycle IR←M[AD] T. -C. Huang / NCUE Fall 2005 e c e D](https://slidetodoc.com/presentation_image/01588a18fef1766065a38955aa3eecc3/image-7.jpg)

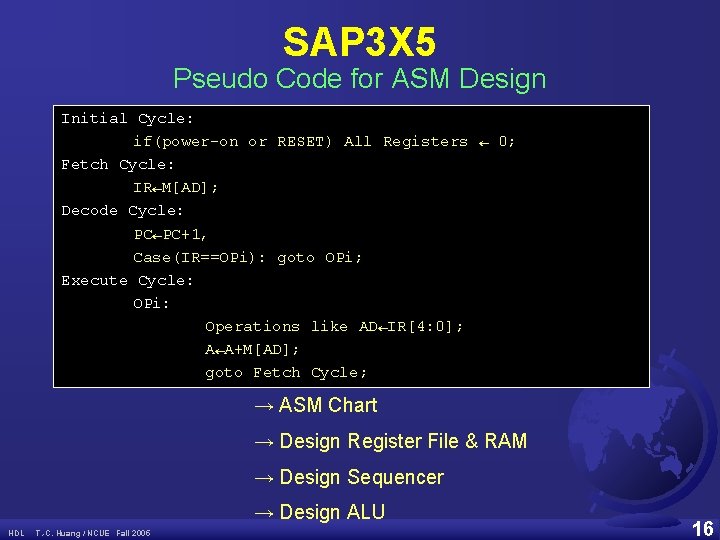

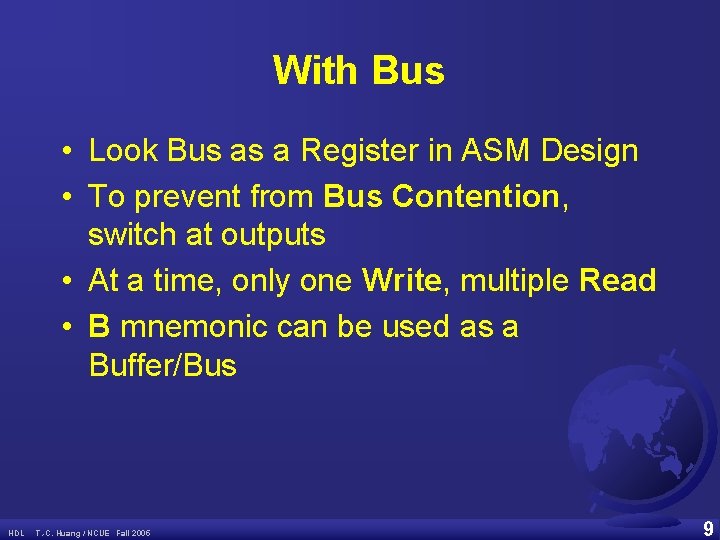

Instruction Cycle IR←M[AD] T. -C. Huang / NCUE Fall 2005 e c e D e d o C e HDL l c Cy E x e i cu t on yc l case(IR) PC←PC+1 Fetch Cycle AD←PC R 1←R 2□R 3 7

No Bus -- Glue • Each register may have (n-1) multiplexed inputs and (n-1) fanouts • The `Glue Bus’ will be NXn. X(n-1) wires HDL T. -C. Huang / NCUE Fall 2005 8

With Bus • Look Bus as a Register in ASM Design • To prevent from Bus Contention, switch at outputs • At a time, only one Write, multiple Read • B mnemonic can be used as a Buffer/Bus HDL T. -C. Huang / NCUE Fall 2005 9

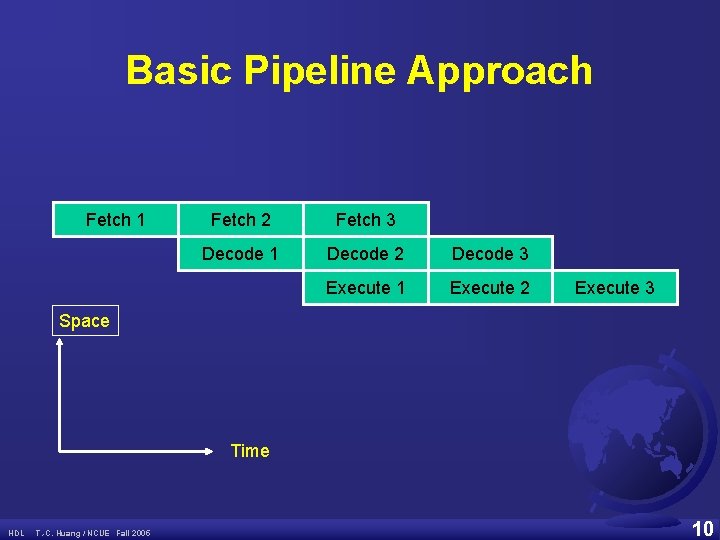

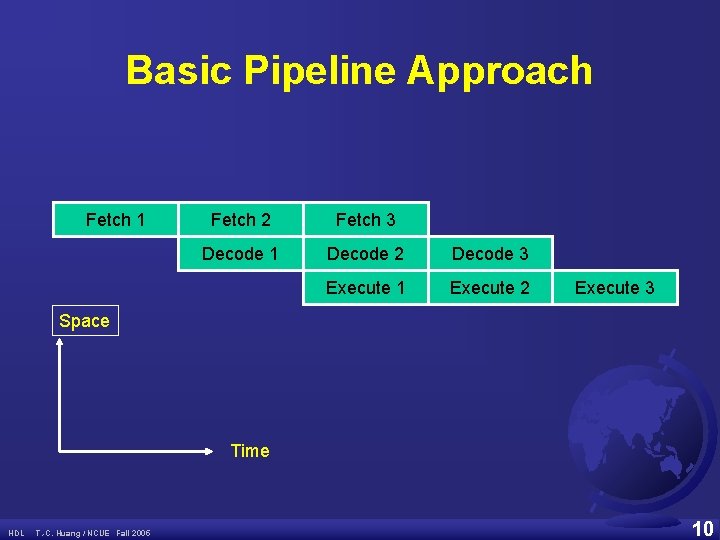

Basic Pipeline Approach Fetch 1 Fetch 2 Fetch 3 Decode 1 Decode 2 Decode 3 Execute 1 Execute 2 Execute 3 Space Time HDL T. -C. Huang / NCUE Fall 2005 10

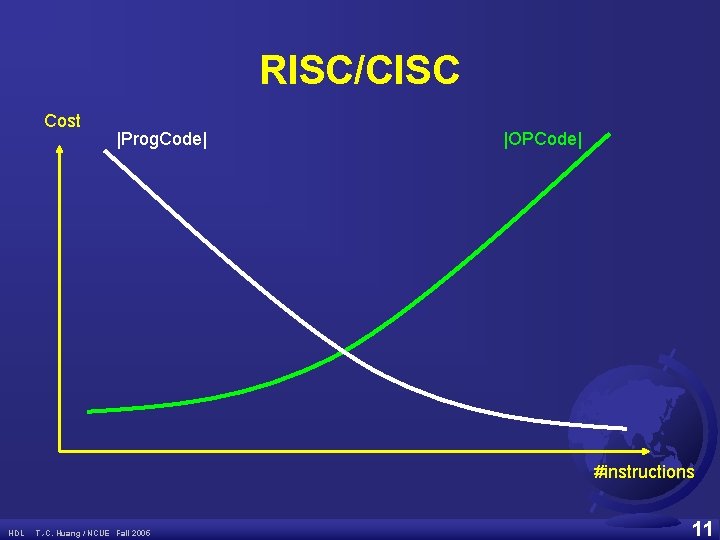

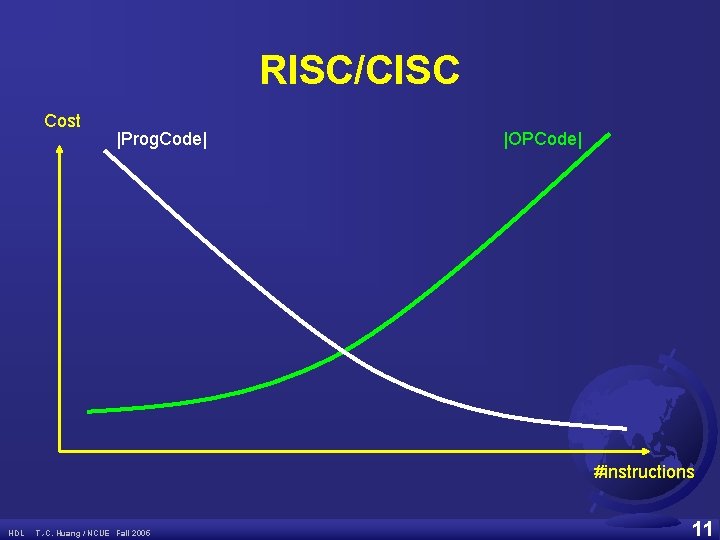

RISC/CISC Cost |Prog. Code| |OPCode| #instructions HDL T. -C. Huang / NCUE Fall 2005 11

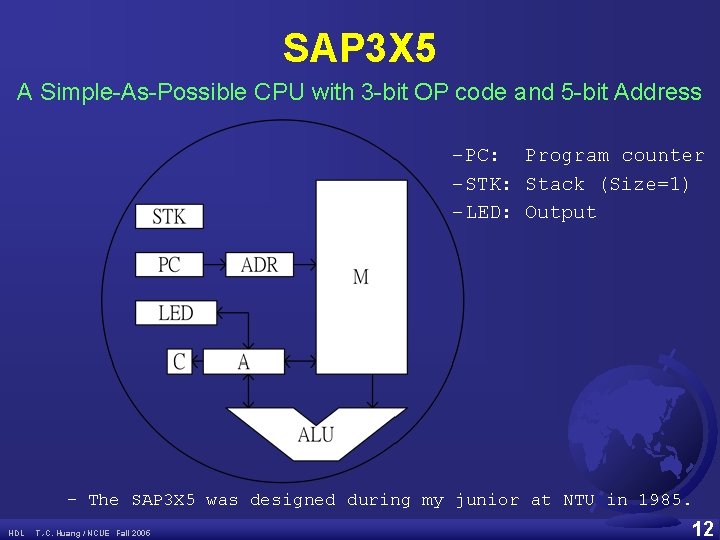

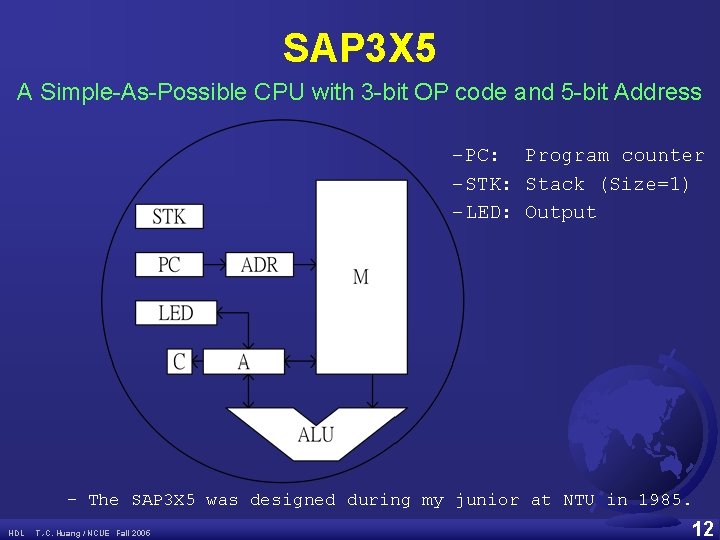

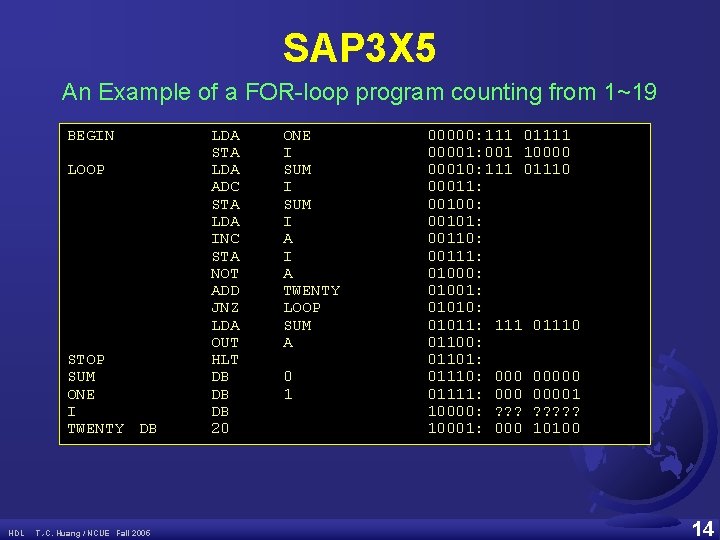

SAP 3 X 5 A Simple-As-Possible CPU with 3 -bit OP code and 5 -bit Address –PC: Program counter –STK: Stack (Size=1) –LED: Output – The SAP 3 X 5 was designed during my junior at NTU in 1985. HDL T. -C. Huang / NCUE Fall 2005 12

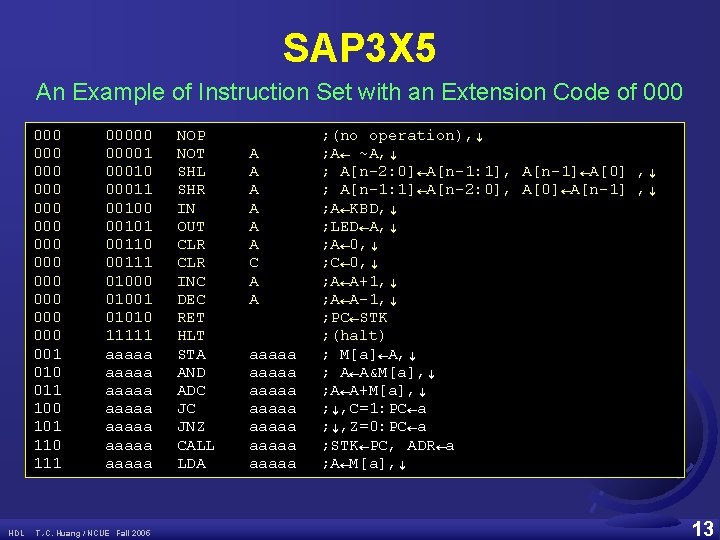

SAP 3 X 5 An Example of Instruction Set with an Extension Code of 000 000 000 000 001 010 011 100 101 110 111 HDL 000001 00010 00011 00100 00101 00110 00111 01000 01001 01010 11111 aaaaa aaaaa T. -C. Huang / NCUE Fall 2005 NOP NOT SHL SHR IN OUT CLR INC DEC RET HLT STA AND ADC JC JNZ CALL LDA A A A C A A aaaaa aaaaa ; (no operation), ↓ ; A← ~A, ↓ ; A[n-2: 0]←A[n-1: 1], A[n-1]←A[0] , ↓ ; A[n-1: 1]←A[n-2: 0], A[0]←A[n-1] , ↓ ; A←KBD, ↓ ; LED←A, ↓ ; A← 0, ↓ ; C← 0, ↓ ; A←A+1, ↓ ; A←A-1, ↓ ; PC←STK ; (halt) ; M[a]←A, ↓ ; A←A&M[a], ↓ ; A←A+M[a], ↓ ; ↓, C=1: PC←a ; ↓, Z=0: PC←a ; STK←PC, ADR←a ; A←M[a], ↓ 13

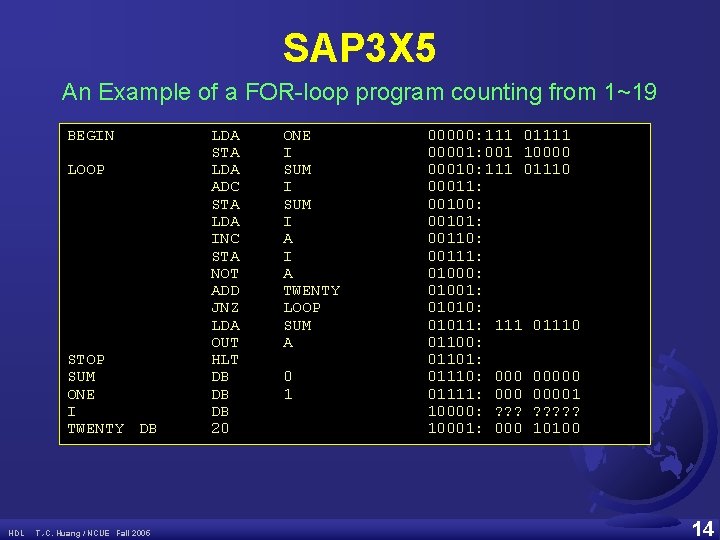

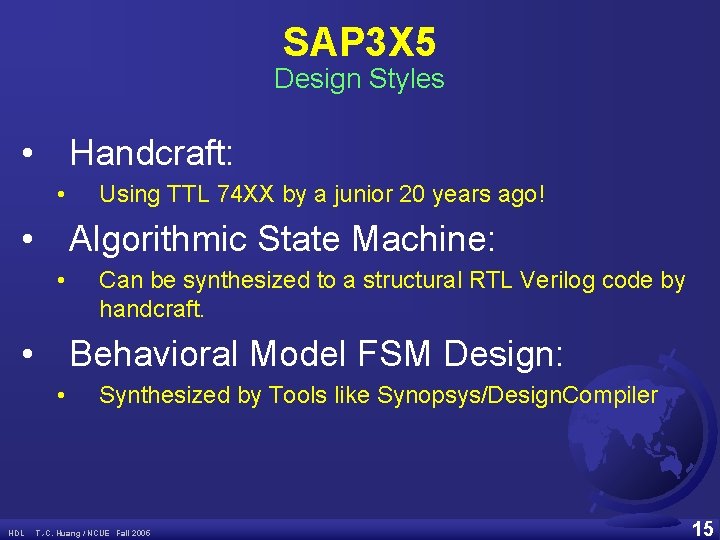

SAP 3 X 5 An Example of a FOR-loop program counting from 1~19 BEGIN LOOP STOP SUM ONE I TWENTY DB HDL T. -C. Huang / NCUE Fall 2005 LDA STA LDA ADC STA LDA INC STA NOT ADD JNZ LDA OUT HLT DB DB DB 20 ONE I SUM I A TWENTY LOOP SUM A 0 1 00000: 111 01111 00001: 001 10000 00010: 111 01110 00011: 00100: 00101: 00110: 00111: 01000: 01001: 01010: 01011: 111 01110 01100: 01101: 01110: 00000 01111: 00001 10000: ? ? ? ? 10001: 000 10100 14

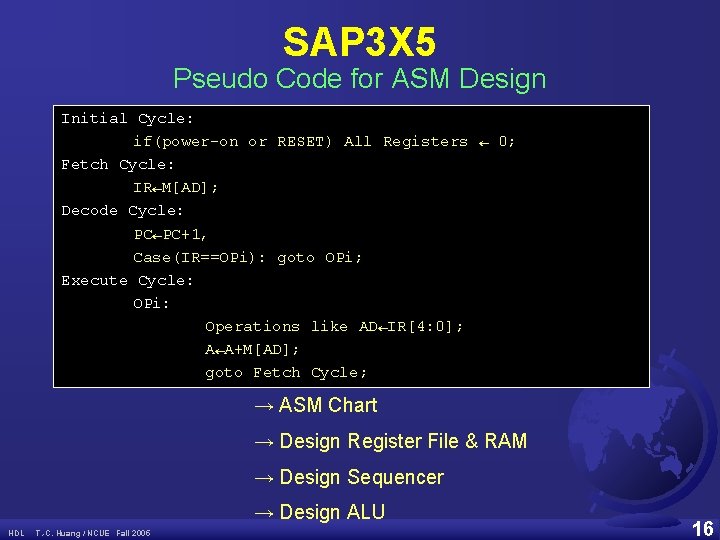

SAP 3 X 5 Design Styles • Handcraft: • Using TTL 74 XX by a junior 20 years ago! • Algorithmic State Machine: • Can be synthesized to a structural RTL Verilog code by handcraft. • Behavioral Model FSM Design: • HDL Synthesized by Tools like Synopsys/Design. Compiler T. -C. Huang / NCUE Fall 2005 15

SAP 3 X 5 Pseudo Code for ASM Design Initial Cycle: if(power-on or RESET) All Registers ← 0; Fetch Cycle: IR←M[AD]; Decode Cycle: PC←PC+1, Case(IR==OPi): goto OPi; Execute Cycle: OPi: Operations like AD←IR[4: 0]; A←A+M[AD]; goto Fetch Cycle; → ASM Chart → Design Register File & RAM → Design Sequencer → Design ALU HDL T. -C. Huang / NCUE Fall 2005 16