Hardware Description Language Logic Design using Verilog TsungChu

![Bus Splitting and Concatenating A[3: 0] B[3: 0] assign A=C[7: 4]; B=C[3: 0]; D=C[7: Bus Splitting and Concatenating A[3: 0] B[3: 0] assign A=C[7: 4]; B=C[3: 0]; D=C[7:](https://slidetodoc.com/presentation_image_h2/00e799464d365cf33cf8ca8c51eff409/image-15.jpg)

![Example: Counters Ø Basic Down-Counting Counter: Module CNT(Clk, Q); input Clk; output [7: 0] Example: Counters Ø Basic Down-Counting Counter: Module CNT(Clk, Q); input Clk; output [7: 0]](https://slidetodoc.com/presentation_image_h2/00e799464d365cf33cf8ca8c51eff409/image-26.jpg)

- Slides: 26

Hardware Description Language -- Logic Design using Verilog Tsung-Chu Huang Dept. of Electronic Eng. National Changhua University of Ed. Email: tch@cc. ncue. edu. tw 2015/09/24 HDL T. -C. Huang / NCUE Fall 2015 1

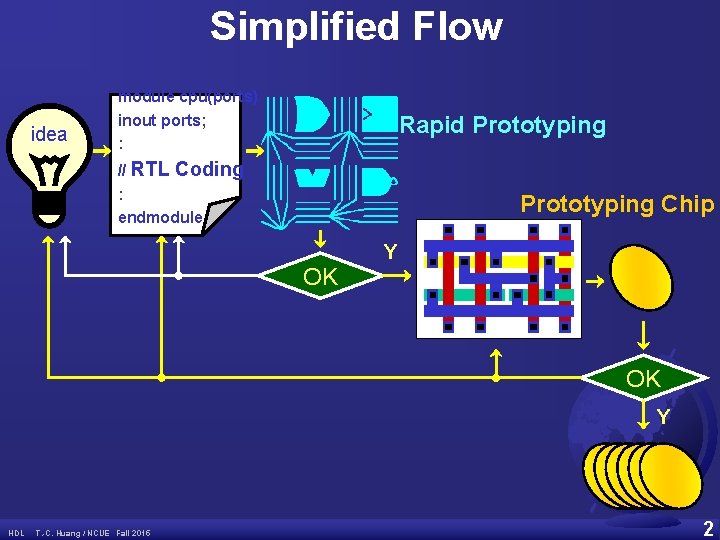

Simplified Flow idea module cpu(ports) inout ports; : Rapid Prototyping // RTL Coding : endmodule Prototyping Chip OK Y HDL T. -C. Huang / NCUE Fall 2015 2

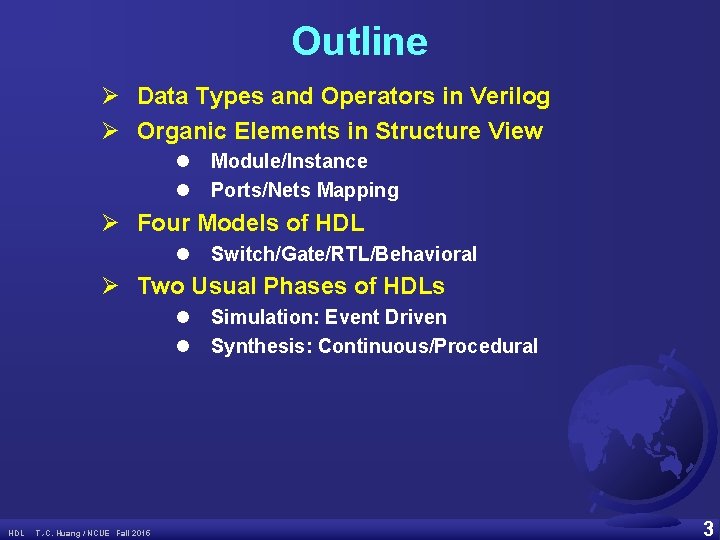

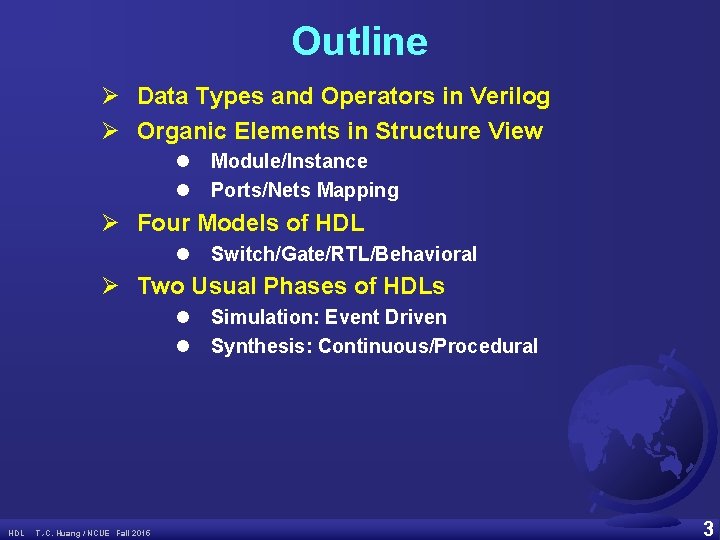

Outline Ø Data Types and Operators in Verilog Ø Organic Elements in Structure View l l Module/Instance Ports/Nets Mapping Ø Four Models of HDL l Switch/Gate/RTL/Behavioral Ø Two Usual Phases of HDLs l l HDL T. -C. Huang / NCUE Fall 2015 Simulation: Event Driven Synthesis: Continuous/Procedural 3

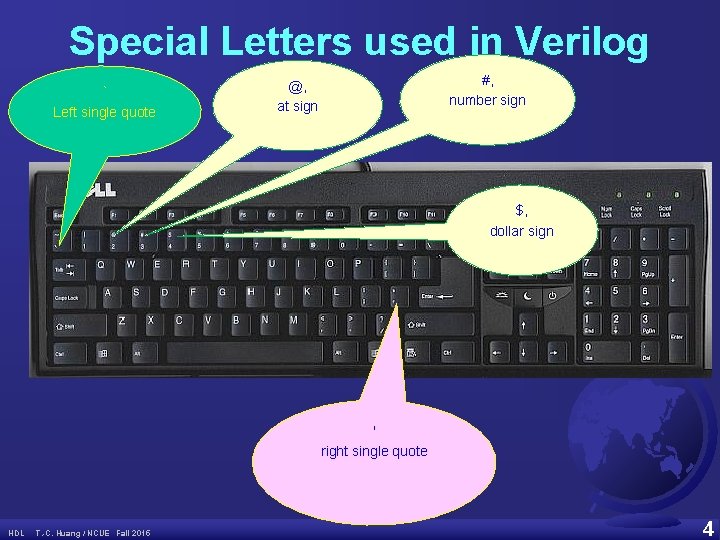

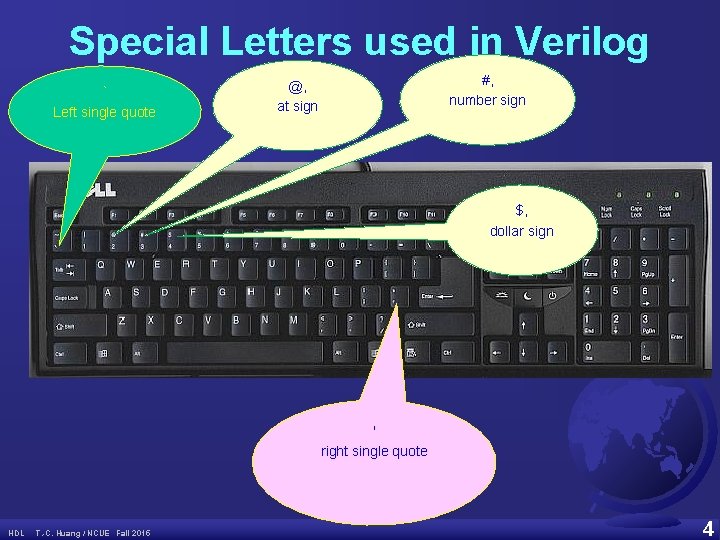

Special Letters used in Verilog ` Left single quote #, number sign @, at sign $, dollar sign ' right single quote HDL T. -C. Huang / NCUE Fall 2015 4

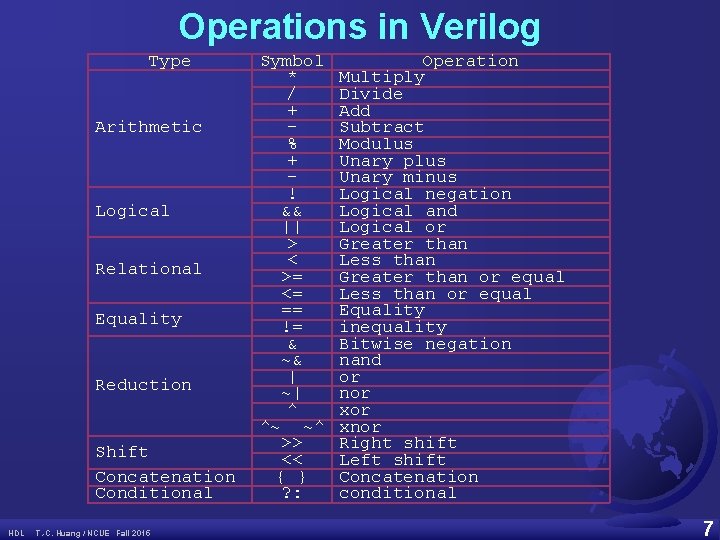

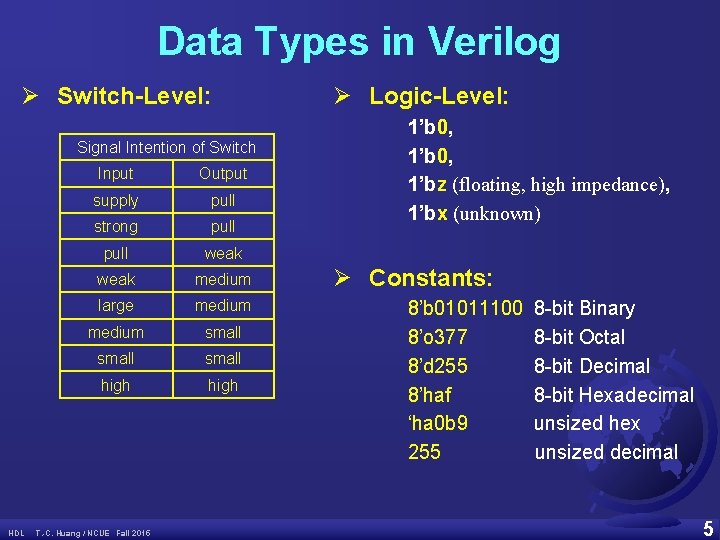

Data Types in Verilog Ø Switch-Level: Signal Intention of Switch HDL Input Output supply pull strong pull weak medium large medium small high T. -C. Huang / NCUE Fall 2015 Ø Logic-Level: 1’b 0, 1’bz (floating, high impedance), 1’bx (unknown) Ø Constants: 8’b 01011100 8’o 377 8’d 255 8’haf ‘ha 0 b 9 255 8 -bit Binary 8 -bit Octal 8 -bit Decimal 8 -bit Hexadecimal unsized hex unsized decimal 5

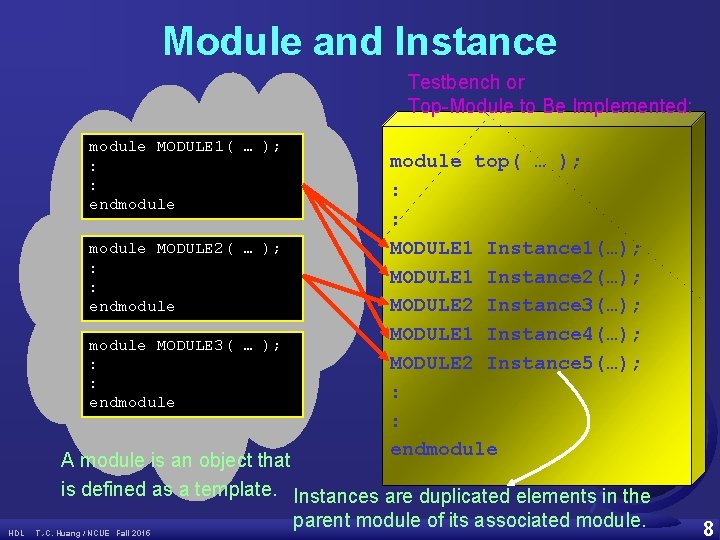

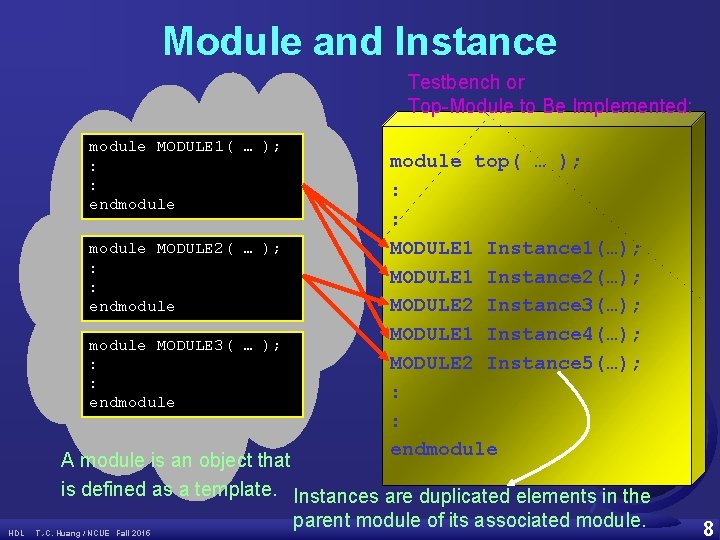

Operations in Verilog Ø Similar to C Language 1. Unary: assign a = ~b; // bitwise not 2. Binary: assign a = b & c; // bitwise and such as: +, -, *, /, |, ^, <<, >>, 3. Ternary: assign d = c ? a : b; // if 1, d=a; else d=b Ø Synthesizable Operators: Ø Most ALU and logic operation designs are developed in library. Ø In RTL model, the designs are “assigned” according to data flow. Ø Unsynthesizable Statements and Operators: Ø Ø HDL Statements dependent to time or times, e. g. , initial, repeat Switch-level Operators used in compiling/simulation only, e. g. , === Operators with no design/method in current library, e. g. , / % (in some tool) T. -C. Huang / NCUE Fall 2015 6

Operations in Verilog Type Arithmetic Logical Relational Equality Reduction Shift Concatenation Conditional HDL T. -C. Huang / NCUE Fall 2015 Symbol * / + % + ! && || > < >= <= == != & ~& | ~| ^ ^~ ~^ >> << { } ? : Operation Multiply Divide Add Subtract Modulus Unary plus Unary minus Logical negation Logical and Logical or Greater than Less than Greater than or equal Less than or equal Equality inequality Bitwise negation nand or nor xnor Right shift Left shift Concatenation conditional 7

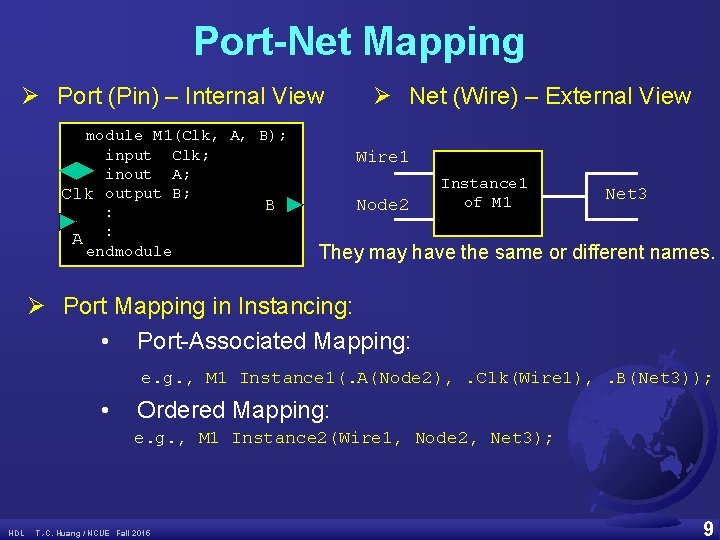

Module and Instance Testbench or Top-Module to Be Implemented: module MODULE 1( … ); : : endmodule MODULE 2( … ); : : endmodule MODULE 3( … ); : : endmodule top( … ); : : MODULE 1 Instance 1(…); MODULE 1 Instance 2(…); MODULE 2 Instance 3(…); MODULE 1 Instance 4(…); MODULE 2 Instance 5(…); : : endmodule A module is an object that is defined as a template. Instances are duplicated elements in the HDL T. -C. Huang / NCUE Fall 2015 parent module of its associated module. 8

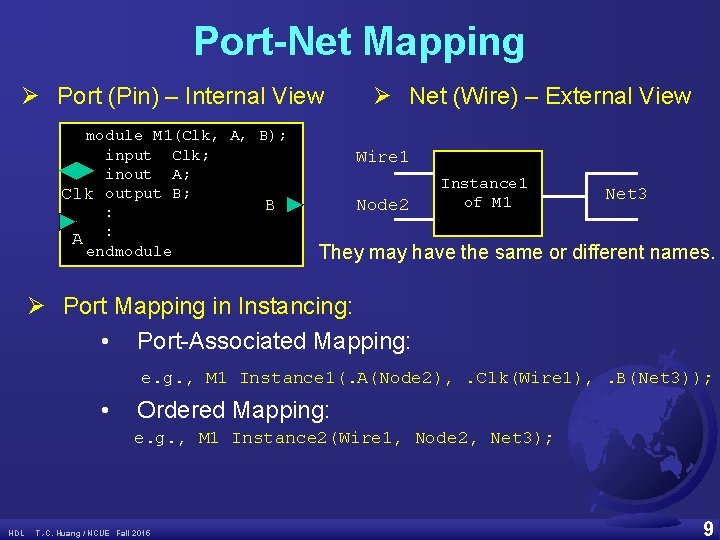

Port-Net Mapping Ø Port (Pin) – Internal View module M 1(Clk, A, B); input Clk; inout A; Clk output B; B : A : endmodule Ø Net (Wire) – External View Wire 1 Node 2 Instance 1 of M 1 Net 3 They may have the same or different names. Ø Port Mapping in Instancing: • Port-Associated Mapping: e. g. , M 1 Instance 1(. A(Node 2), . Clk(Wire 1), . B(Net 3)); • Ordered Mapping: e. g. , M 1 Instance 2(Wire 1, Node 2, Net 3); HDL T. -C. Huang / NCUE Fall 2015 9

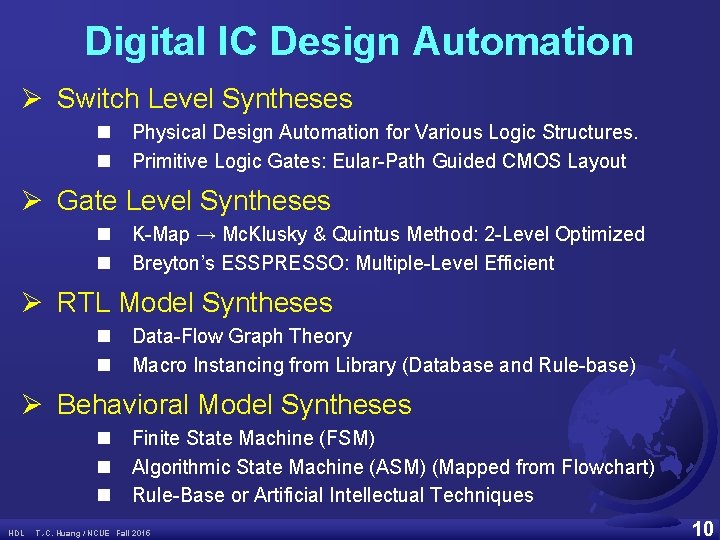

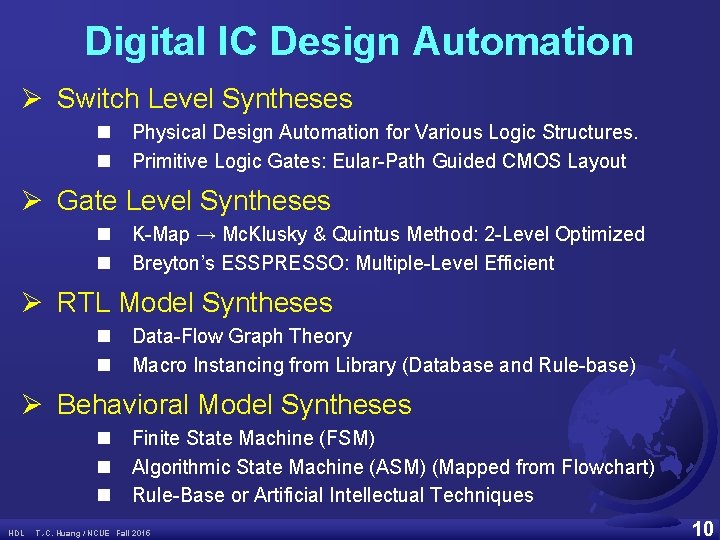

Digital IC Design Automation Ø Switch Level Syntheses n n Physical Design Automation for Various Logic Structures. Primitive Logic Gates: Eular-Path Guided CMOS Layout Ø Gate Level Syntheses n n K-Map → Mc. Klusky & Quintus Method: 2 -Level Optimized Breyton’s ESSPRESSO: Multiple-Level Efficient Ø RTL Model Syntheses n n Data-Flow Graph Theory Macro Instancing from Library (Database and Rule-base) Ø Behavioral Model Syntheses n n n HDL Finite State Machine (FSM) Algorithmic State Machine (ASM) (Mapped from Flowchart) Rule-Base or Artificial Intellectual Techniques T. -C. Huang / NCUE Fall 2015 10

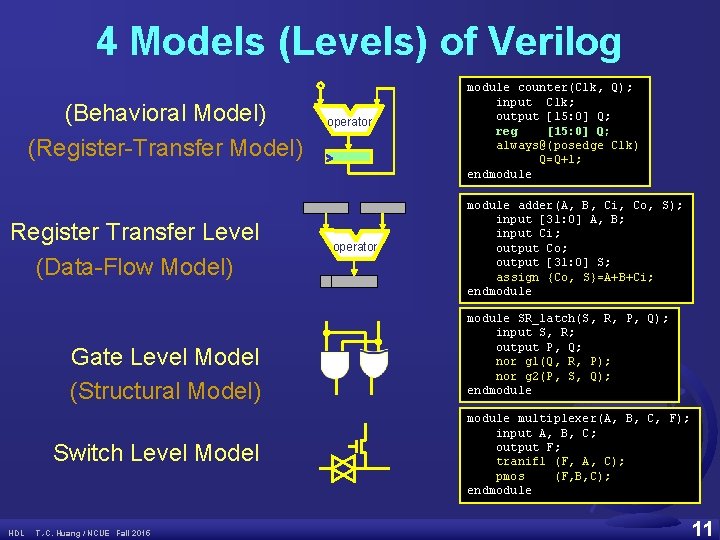

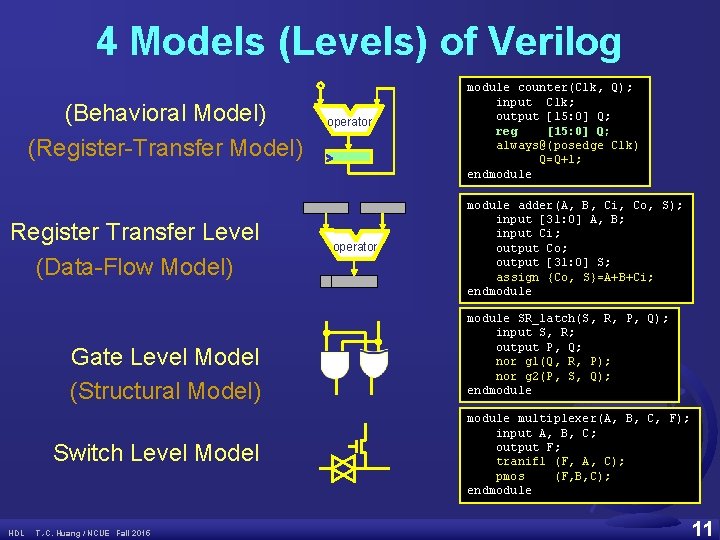

4 Models (Levels) of Verilog (Behavioral Model) (Register-Transfer Model) Register Transfer Level (Data-Flow Model) Gate Level Model (Structural Model) Switch Level Model HDL T. -C. Huang / NCUE Fall 2015 operator module counter(Clk, Q); input Clk; output [15: 0] Q; reg [15: 0] Q; always@(posedge Clk) Q=Q+1; endmodule adder(A, B, Ci, Co, S); input [31: 0] A, B; input Ci; output Co; output [31: 0] S; assign {Co, S}=A+B+Ci; endmodule SR_latch(S, R, P, Q); input S, R; output P, Q; nor g 1(Q, R, P); nor g 2(P, S, Q); endmodule multiplexer(A, B, C, F); input A, B, C; output F; tranif 1 (F, A, C); pmos (F, B, C); endmodule 11

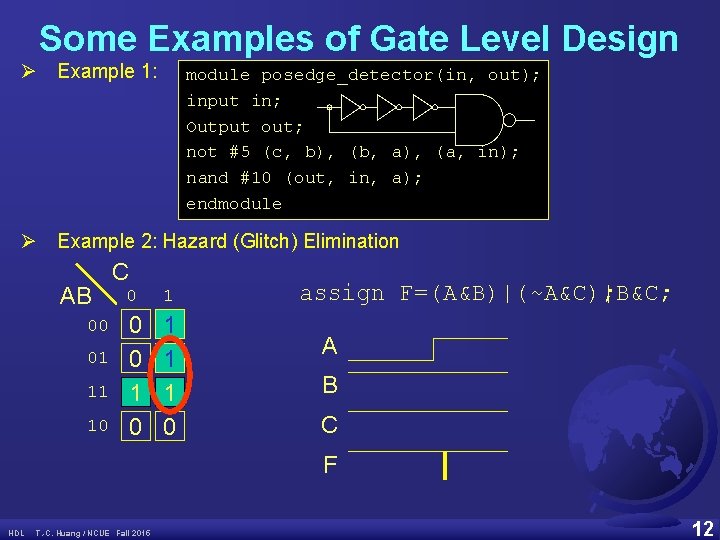

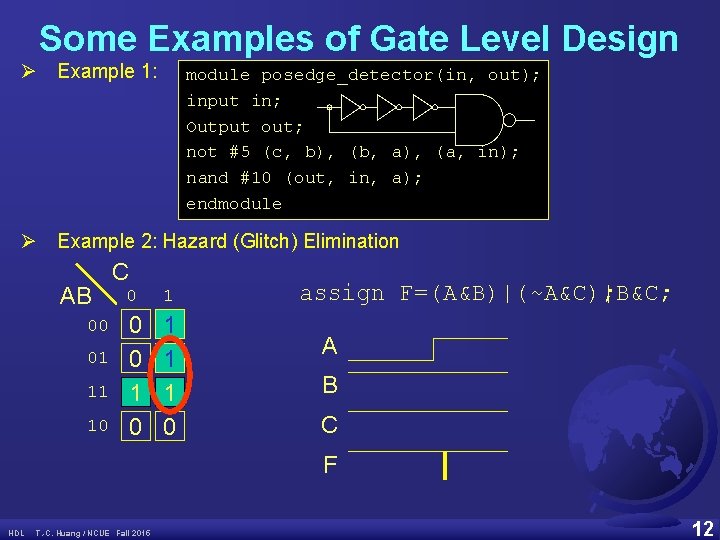

Some Examples of Gate Level Design Ø Example 1: module posedge_detector(in, out); input in; Output out; not #5 (c, b), (b, a), (a, in); nand #10 (out, in, a); endmodule Ø Example 2: Hazard (Glitch) Elimination AB 00 01 11 10 C 0 1 0 1 1 1 0 assign F=(A&B)|(~A&C)|B&C; F=(A&B)|(~A&C); A B C F HDL T. -C. Huang / NCUE Fall 2015 12

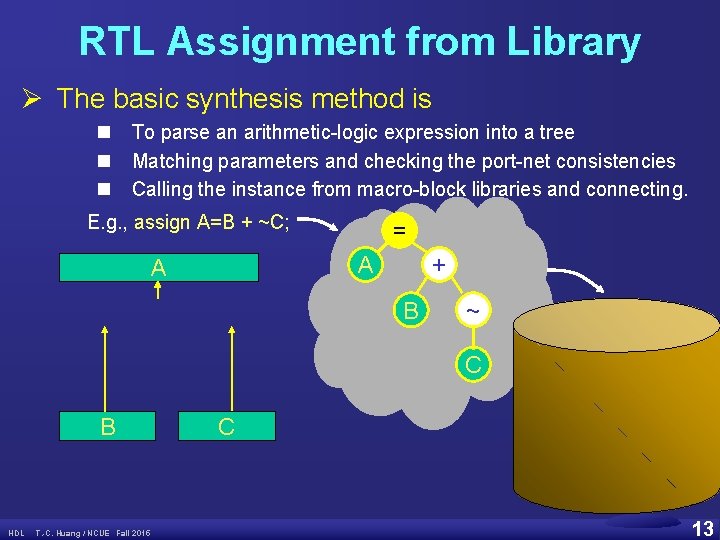

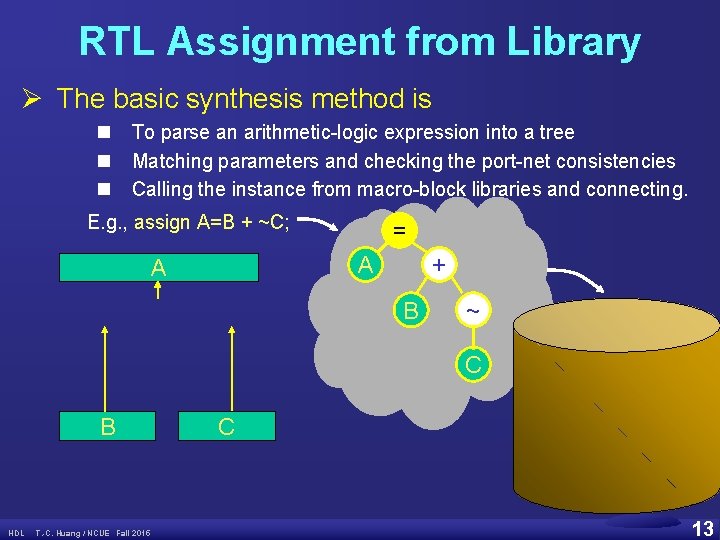

RTL Assignment from Library Ø The basic synthesis method is n n n To parse an arithmetic-logic expression into a tree Matching parameters and checking the port-net consistencies Calling the instance from macro-block libraries and connecting. E. g. , assign A=B + ~C; = A A + B ~ C B HDL T. -C. Huang / NCUE Fall 2015 C 13

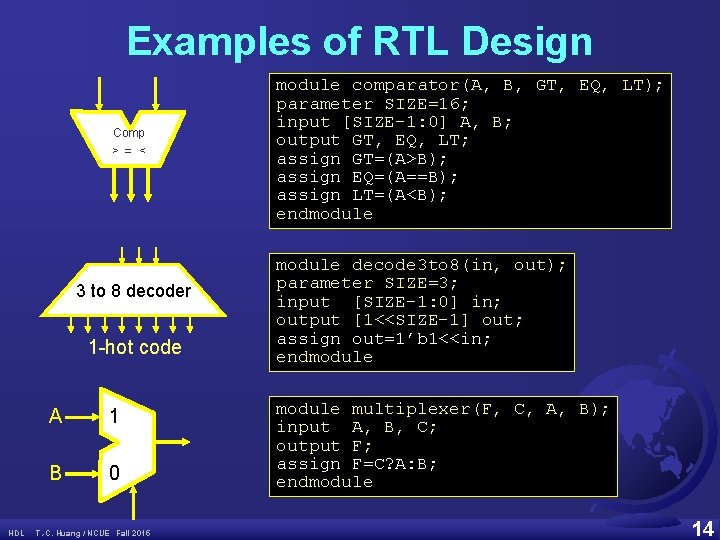

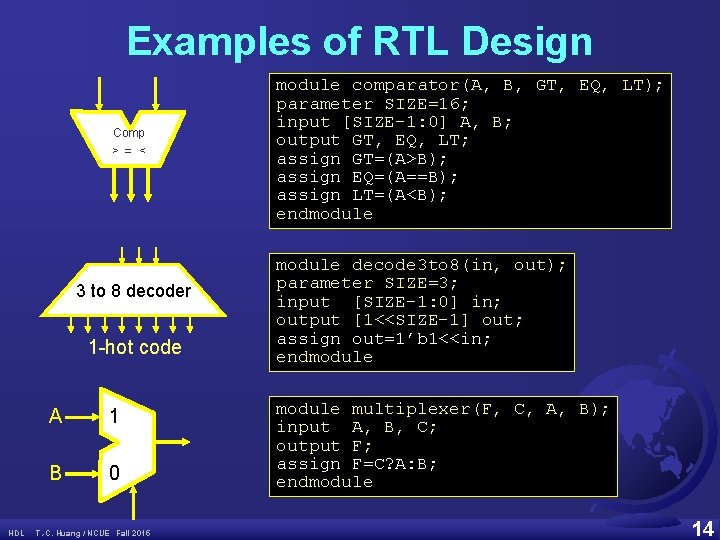

Examples of RTL Design Comp > = < 3 to 8 decoder 1 -hot code HDL A 1 B 0 T. -C. Huang / NCUE Fall 2015 module comparator(A, B, GT, EQ, LT); parameter SIZE=16; input [SIZE-1: 0] A, B; output GT, EQ, LT; assign GT=(A>B); assign EQ=(A==B); assign LT=(A<B); endmodule decode 3 to 8(in, out); parameter SIZE=3; input [SIZE-1: 0] in; output [1<<SIZE-1] out; assign out=1’b 1<<in; endmodule multiplexer(F, C, A, B); input A, B, C; output F; assign F=C? A: B; endmodule 14

![Bus Splitting and Concatenating A3 0 B3 0 assign AC7 4 BC3 0 DC7 Bus Splitting and Concatenating A[3: 0] B[3: 0] assign A=C[7: 4]; B=C[3: 0]; D=C[7:](https://slidetodoc.com/presentation_image_h2/00e799464d365cf33cf8ca8c51eff409/image-15.jpg)

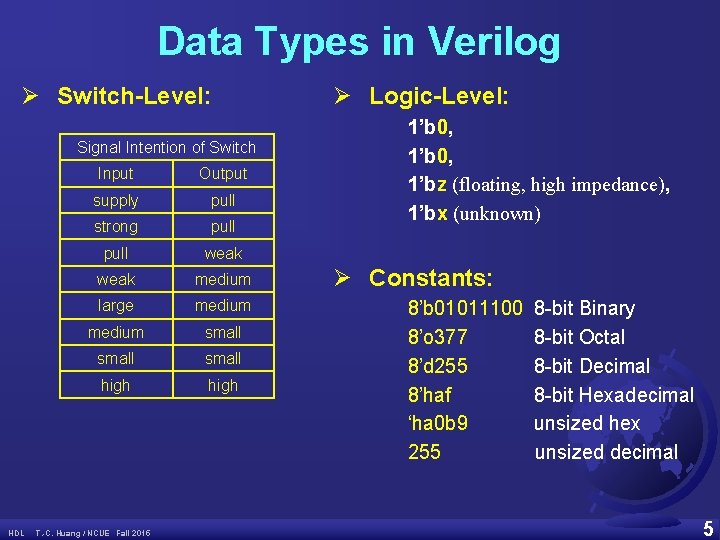

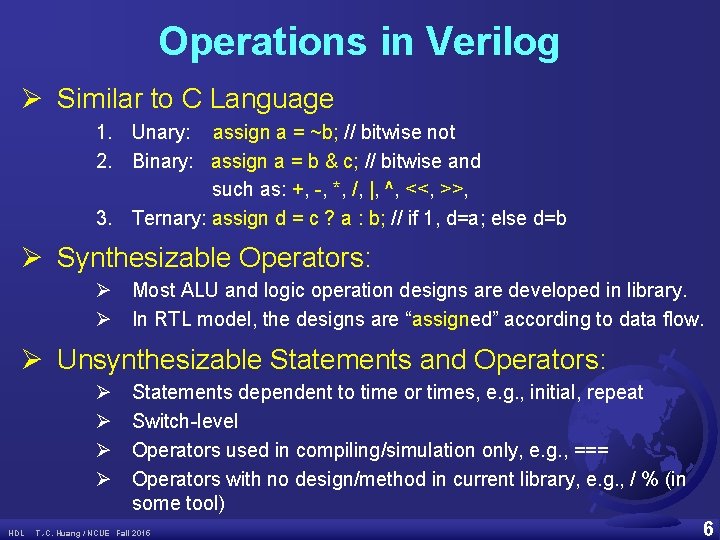

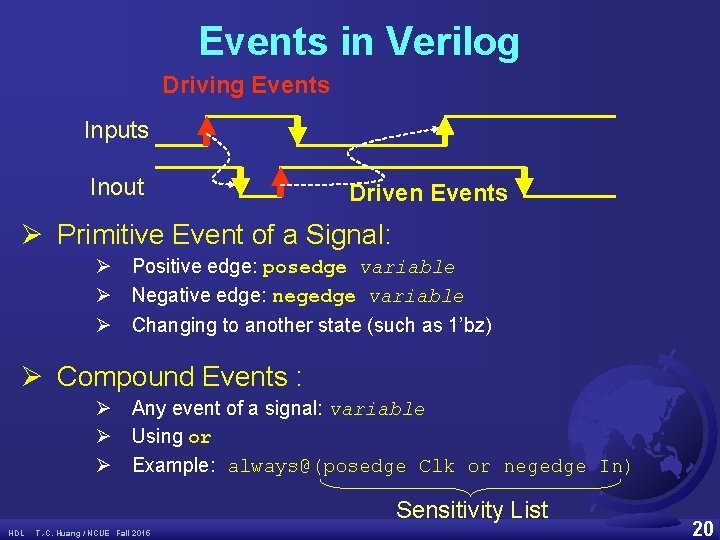

Bus Splitting and Concatenating A[3: 0] B[3: 0] assign A=C[7: 4]; B=C[3: 0]; D=C[7: 6]; E=C[5: 0]; C[7: 0] assign C={A, B}; assign {D, E}=C; D[1: 0] HDL T. -C. Huang / NCUE Fall 2015 E[5: 0] 15

What’s Behavior Event! Another Event! HDL T. -C. Huang / NCUE Fall 2015 16

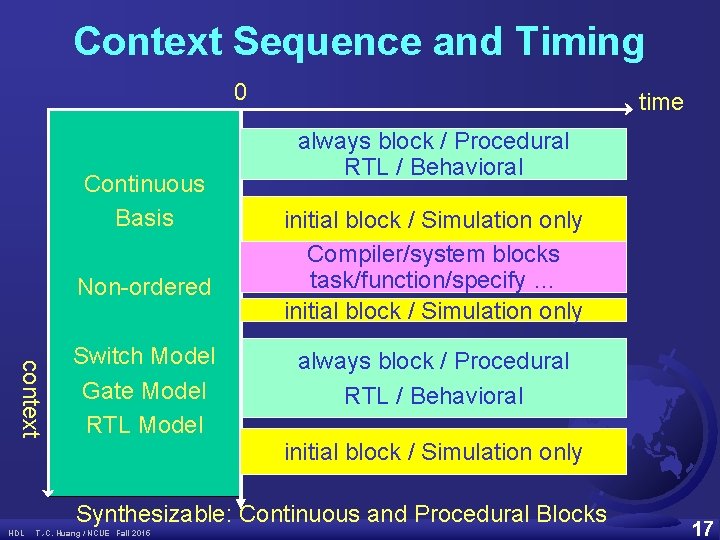

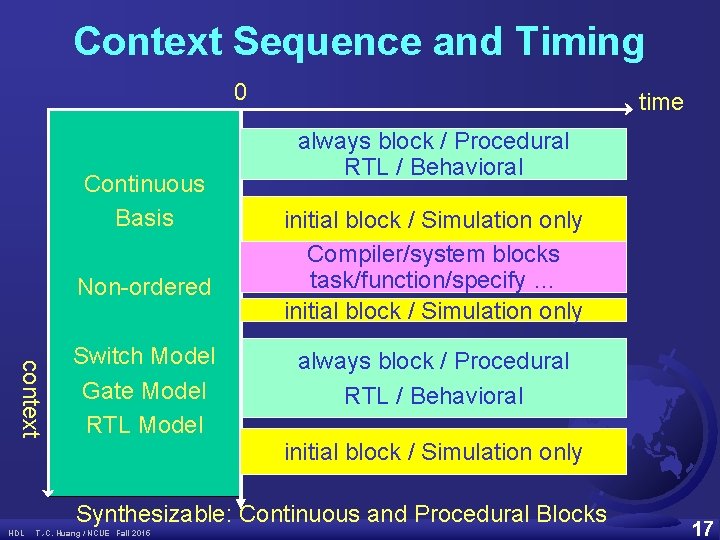

Context Sequence and Timing 0 Continuous Basis Non-ordered context Switch Model Gate Model RTL Model time always block / Procedural RTL / Behavioral initial block / Simulation only Compiler/system blocks task/function/specify … initial block / Simulation only always block / Procedural RTL / Behavioral initial block / Simulation only Synthesizable: Continuous and Procedural Blocks HDL T. -C. Huang / NCUE Fall 2015 17

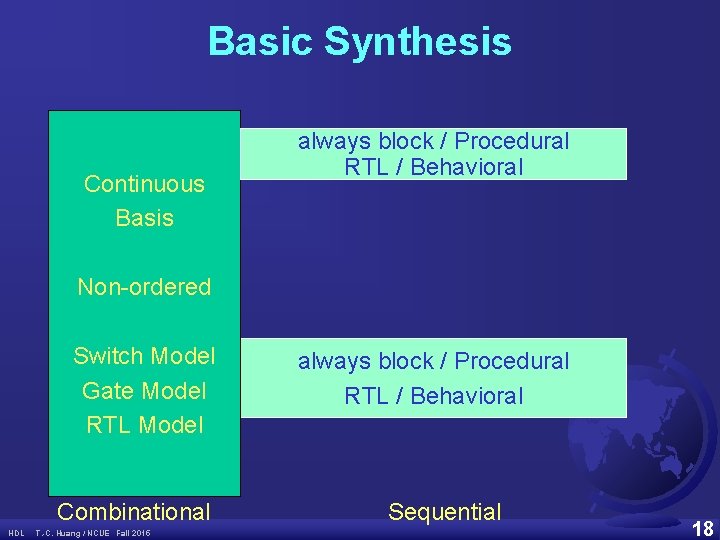

Basic Synthesis Continuous Basis always block / Procedural RTL / Behavioral Non-ordered Switch Model Gate Model RTL Model Combinational HDL T. -C. Huang / NCUE Fall 2015 always block / Procedural RTL / Behavioral Sequential 18

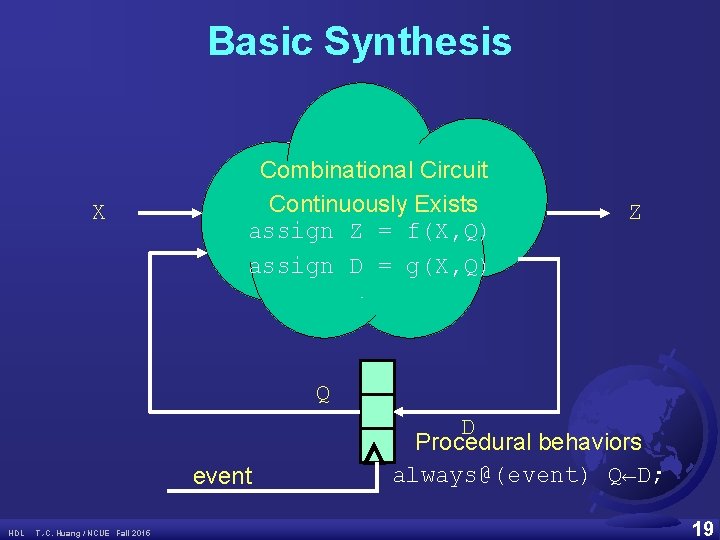

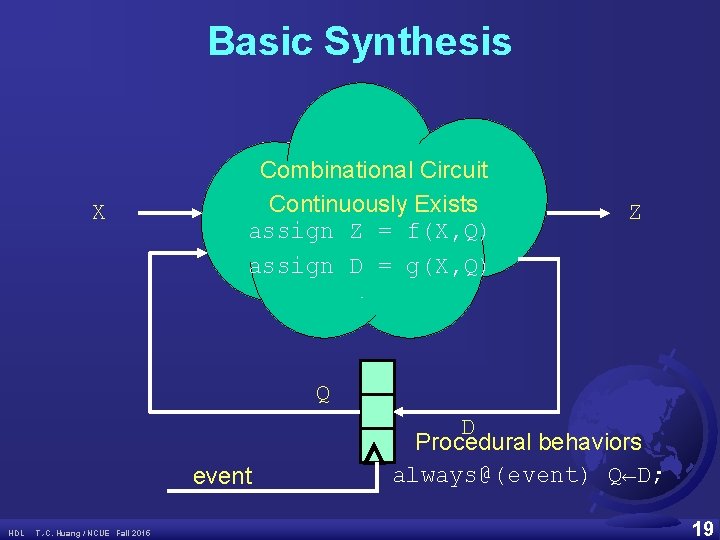

Basic Synthesis X Combinational Circuit Continuously Exists assign Z = f(X, Q) assign D = g(X, Q) Z Q event HDL T. -C. Huang / NCUE Fall 2015 D Procedural behaviors always@(event) Q←D; 19

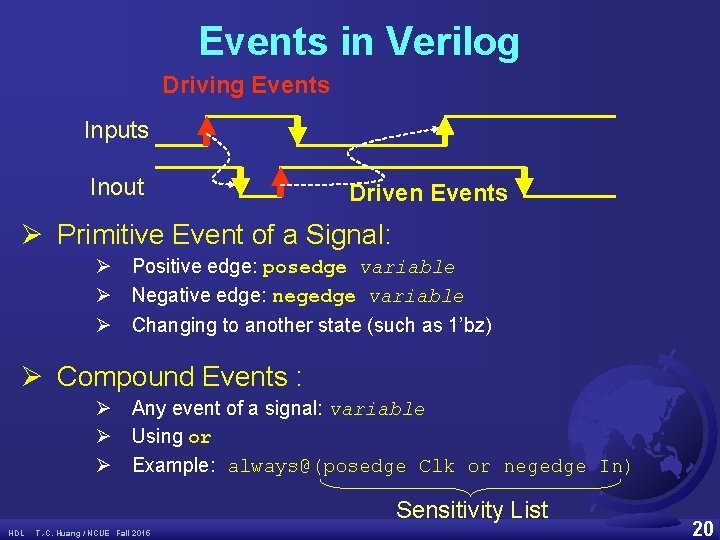

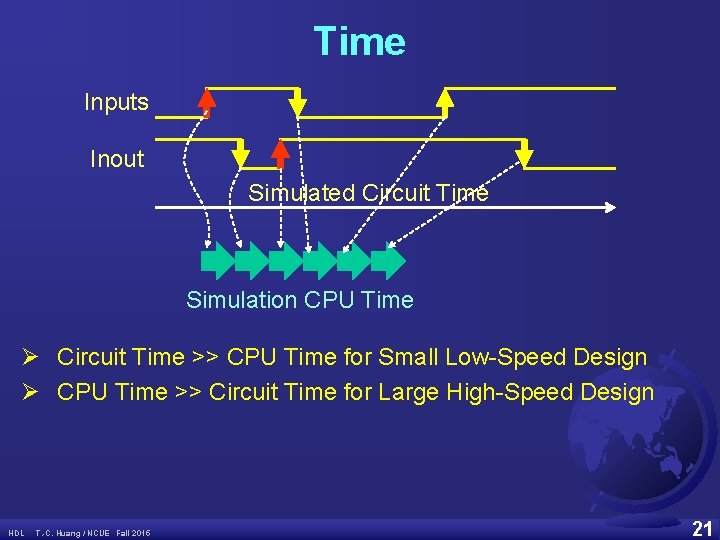

Events in Verilog Driving Events Inputs Inout Driven Events Ø Primitive Event of a Signal: Ø Positive edge: posedge variable Ø Negative edge: negedge variable Ø Changing to another state (such as 1’bz) Ø Compound Events : Ø Any event of a signal: variable Ø Using or Ø Example: always@(posedge Clk or negedge In) Sensitivity List HDL T. -C. Huang / NCUE Fall 2015 20

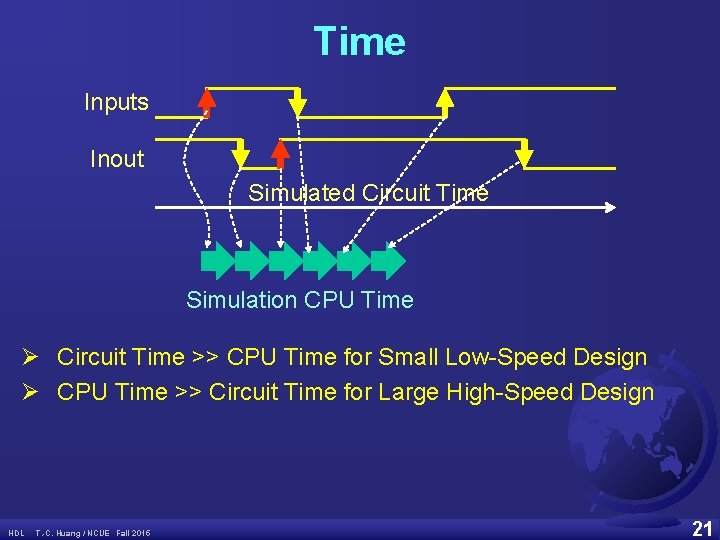

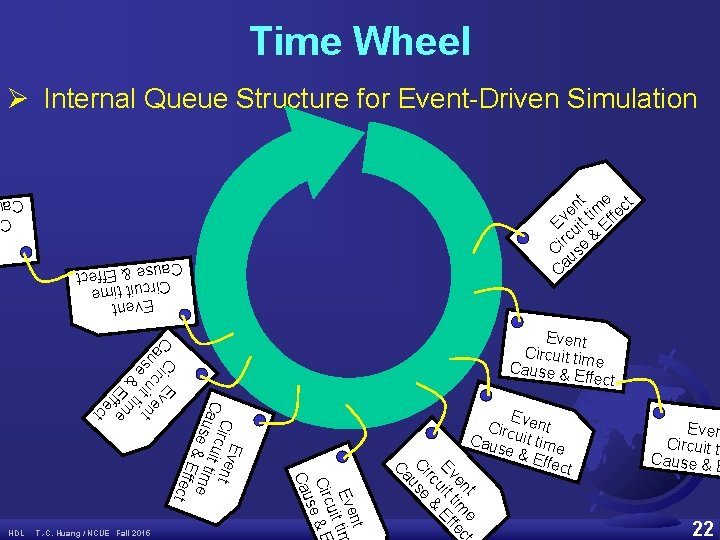

Time Inputs Inout Simulated Circuit Time Simulation CPU Time Ø Circuit Time >> CPU Time for Small Low-Speed Design Ø CPU Time >> Circuit Time for Large High-Speed Design HDL T. -C. Huang / NCUE Fall 2015 21

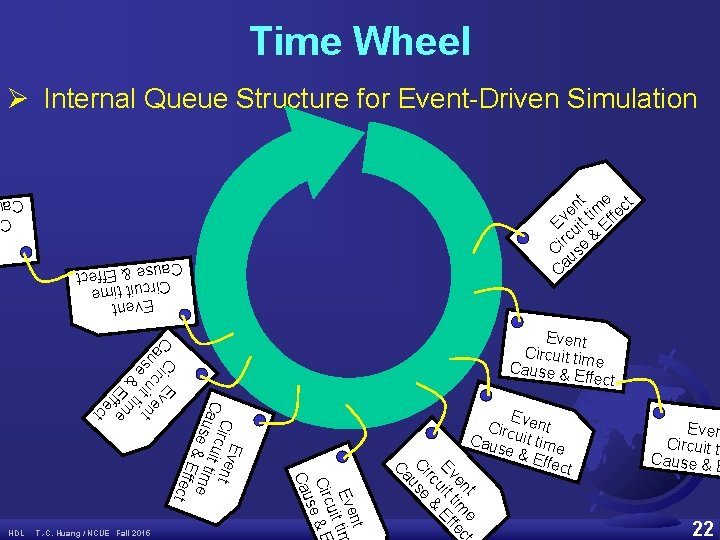

Time Wheel Ø Internal Queue Structure for Event-Driven Simulation nt ime ect e t f Ev uit Ef irc & C use a C Ca Event Circuit time t ec Cause & Eff T. -C. Huang / NCUE Fall 2015 E Circ vent Cau uit tim e se & Effe ct t e en tim fec Ev uit Ef irc & C use a C t HDL nt Eve t tim ui Circ e & E s Cau E C ven C ircui t a u se &t time E ffec Ca Cir Ev c e u s uit nt e & tim Ef e ct Event Circuit tim e Cause & Effect Even Circuit ti Cause & E 22

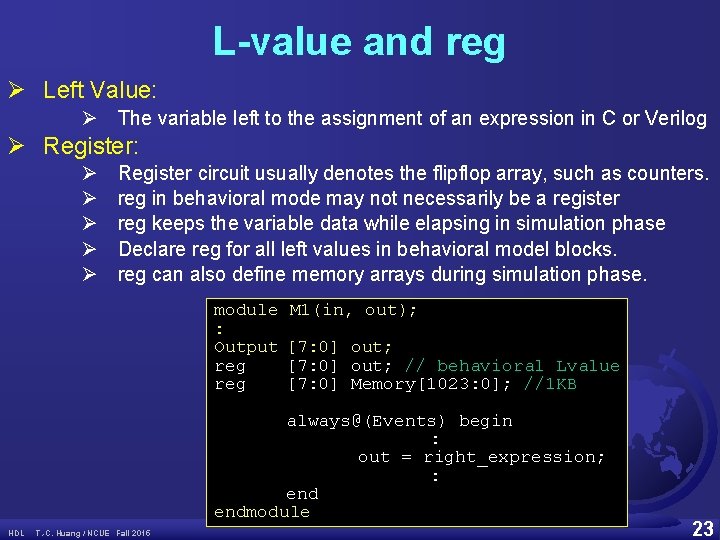

L-value and reg Ø Left Value: Ø The variable left to the assignment of an expression in C or Verilog Ø Register: Ø Ø Ø Register circuit usually denotes the flipflop array, such as counters. reg in behavioral mode may not necessarily be a register reg keeps the variable data while elapsing in simulation phase Declare reg for all left values in behavioral model blocks. reg can also define memory arrays during simulation phase. module : Output reg M 1(in, out); [7: 0] out; // behavioral Lvalue [7: 0] Memory[1023: 0]; //1 KB always@(Events) begin : out = right_expression; : endmodule HDL T. -C. Huang / NCUE Fall 2015 23

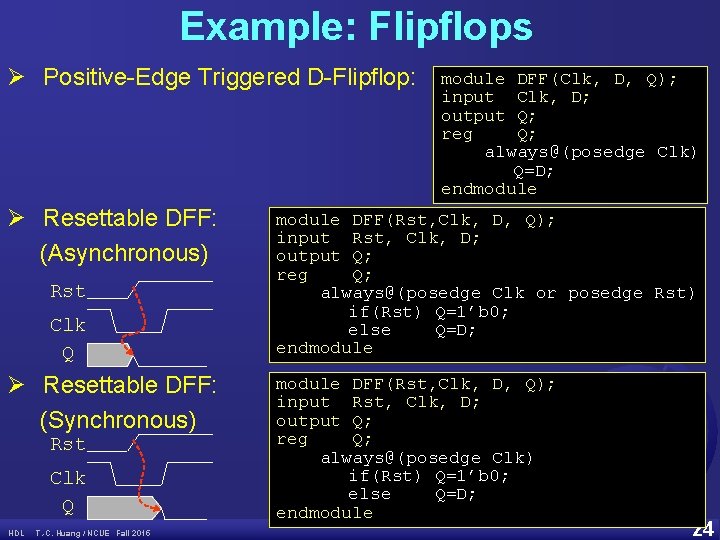

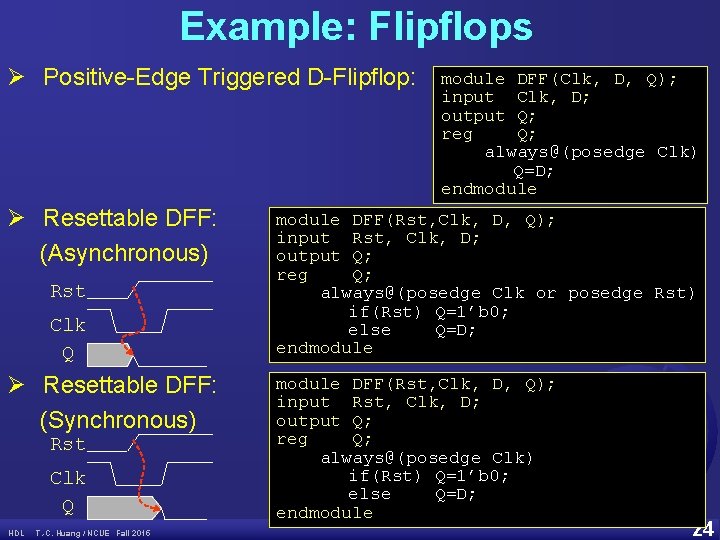

Example: Flipflops Ø Positive-Edge Triggered D-Flipflop: Ø Resettable DFF: (Asynchronous) Rst Clk Q Ø Resettable DFF: (Synchronous) Rst Clk Q HDL T. -C. Huang / NCUE Fall 2015 module DFF(Clk, D, Q); input Clk, D; output Q; reg Q; always@(posedge Clk) Q=D; endmodule DFF(Rst, Clk, D, Q); input Rst, Clk, D; output Q; reg Q; always@(posedge Clk or posedge Rst) if(Rst) Q=1’b 0; else Q=D; endmodule DFF(Rst, Clk, D, Q); input Rst, Clk, D; output Q; reg Q; always@(posedge Clk) if(Rst) Q=1’b 0; else Q=D; endmodule 24

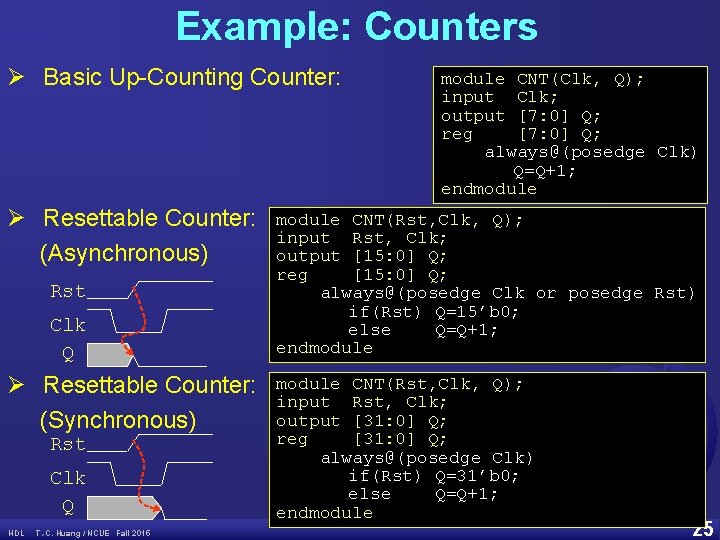

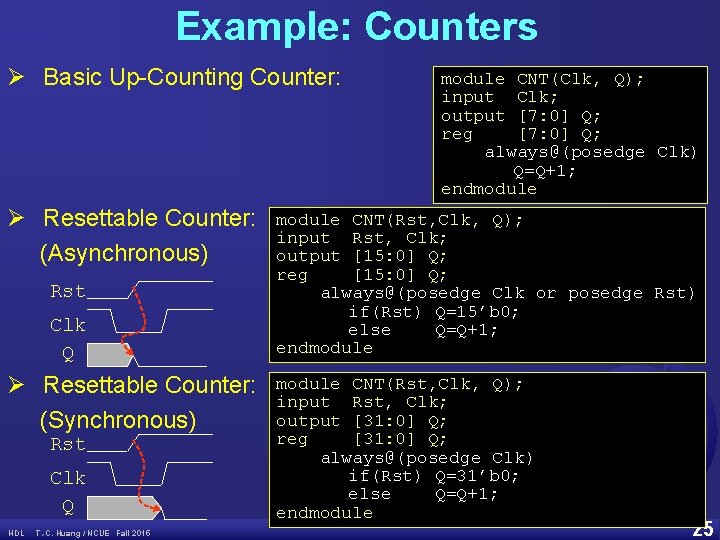

Example: Counters Ø Basic Up-Counting Counter: Ø Resettable Counter: (Asynchronous) Rst Clk Q Ø Resettable Counter: (Synchronous) Rst Clk Q HDL T. -C. Huang / NCUE Fall 2015 module CNT(Clk, Q); input Clk; output [7: 0] Q; reg [7: 0] Q; always@(posedge Clk) Q=Q+1; endmodule CNT(Rst, Clk, Q); input Rst, Clk; output [15: 0] Q; reg [15: 0] Q; always@(posedge Clk or posedge Rst) if(Rst) Q=15’b 0; else Q=Q+1; endmodule CNT(Rst, Clk, Q); input Rst, Clk; output [31: 0] Q; reg [31: 0] Q; always@(posedge Clk) if(Rst) Q=31’b 0; else Q=Q+1; endmodule 25

![Example Counters Ø Basic DownCounting Counter Module CNTClk Q input Clk output 7 0 Example: Counters Ø Basic Down-Counting Counter: Module CNT(Clk, Q); input Clk; output [7: 0]](https://slidetodoc.com/presentation_image_h2/00e799464d365cf33cf8ca8c51eff409/image-26.jpg)

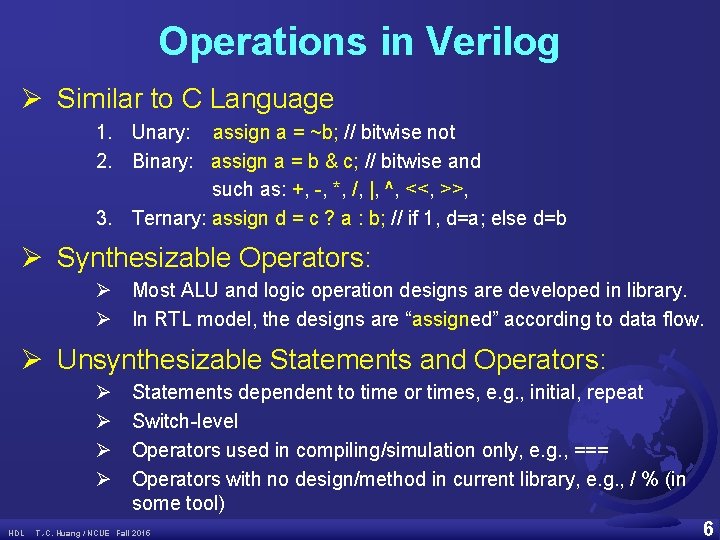

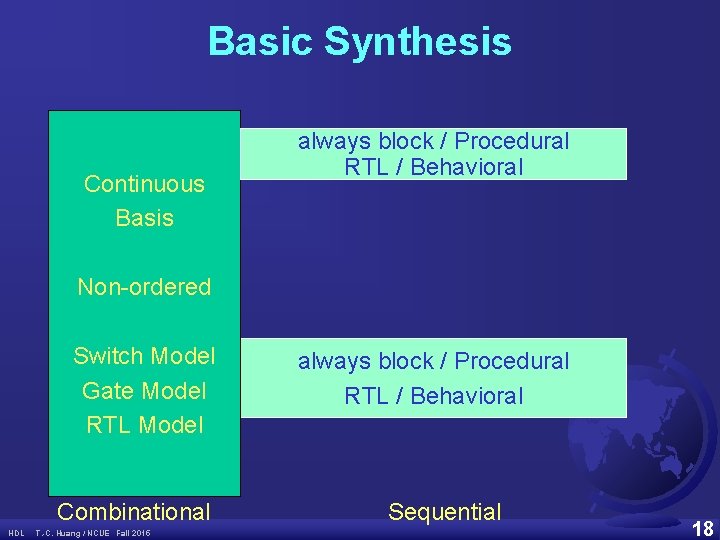

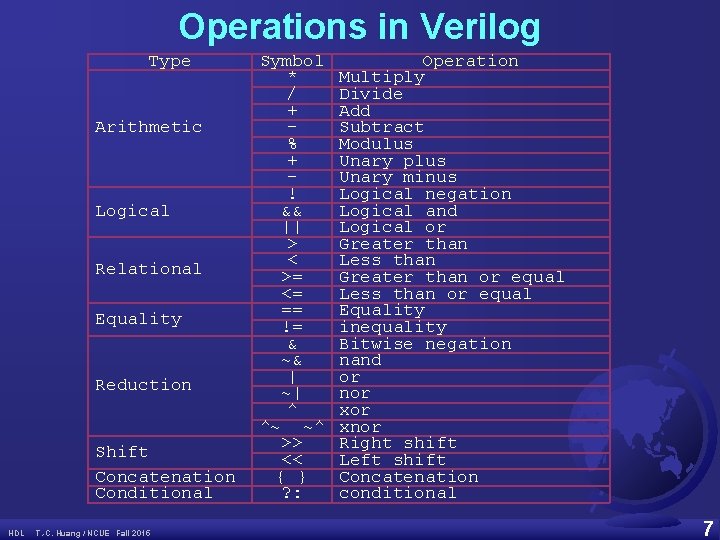

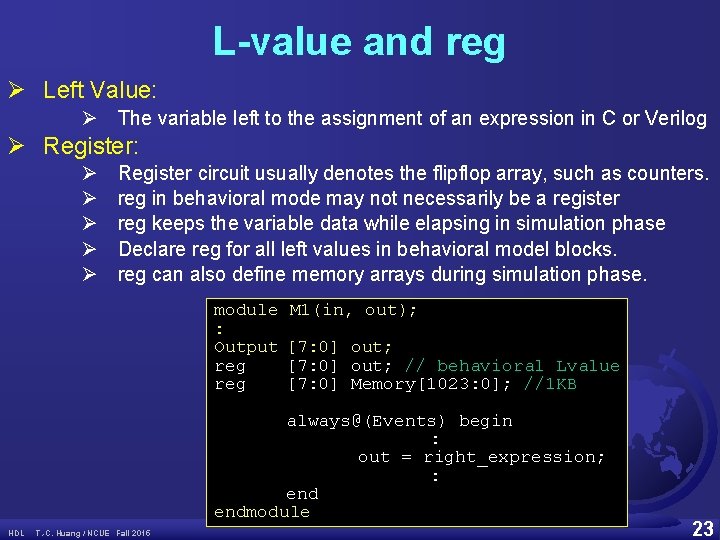

Example: Counters Ø Basic Down-Counting Counter: Module CNT(Clk, Q); input Clk; output [7: 0] Q; reg [7: 0] Q; always@(posedge Clk) Q=Q-1; endmodule Ø Loadable Counter: module CNT(Load, Clk, D, Q); input Load, Clk, D; output [15: 0] Q; reg [15: 0] Q; always@(posedge Clk) if(Load) Q=D; else Q=Q+1; endmodule Ø Modulo Counter: module CNT(Rst, Clk, Q); input Rst, Clk; output [7: 0] Q; reg [7: 0] Q; always@(posedge Clk) if(Rst) Q=7’b 0; else if(Q==99) Q=7’b 0; //%100 else Q=Q+1; endmodule 26 HDL T. -C. Huang / NCUE Fall 2015