ECE 448 Lecture 15 FPro Video Subsystem VGA

ECE 448 Lecture 15 FPro Video Subsystem: VGA Display & On-Screen Display Core ECE 448 – FPGA and ASIC Design with VHDL George Mason University

Required Reading P. Chu, FPGA Prototyping by VHDL Examples Chapter 20. 1, Introduction to a Video Display Chapter 21. 1, Organization of the Video Subsystem Chapter 21. 2, FPro video IP core Chapter 23, On-Screen Display Core ECE 448 – FPGA and ASIC Design with VHDL 2

Source Code Companion Website of FPGA Prototyping by VHDL Examples 2 nd edition https: //academic. csuohio. edu/chu_p/rtl/fpga_mcs_vhdl. html § Source code read_me file: readme_source_code. pdf source file: fpga_mcs_vhdl_src. zip (last updated 11/10/2017) fpga_mcs_vhdl_src/hdl/video fpga_mcs_vhdl_src/hdl/sys/subsys/video_sys_daisy*. vhd fpga_mcs_vhdl_src/cpp/drv/vga_core [. h, . cpp] fpga_mcs_vhdl_src/cpp/app/main_video_test. cpp ECE 448 – FPGA and ASIC Design with VHDL 3

Basics ECE 448 – FPGA and ASIC Design with VHDL 4

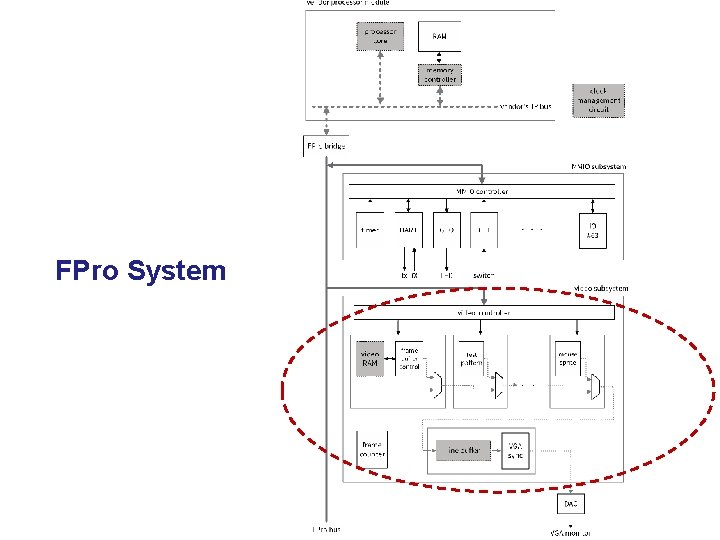

FPro System

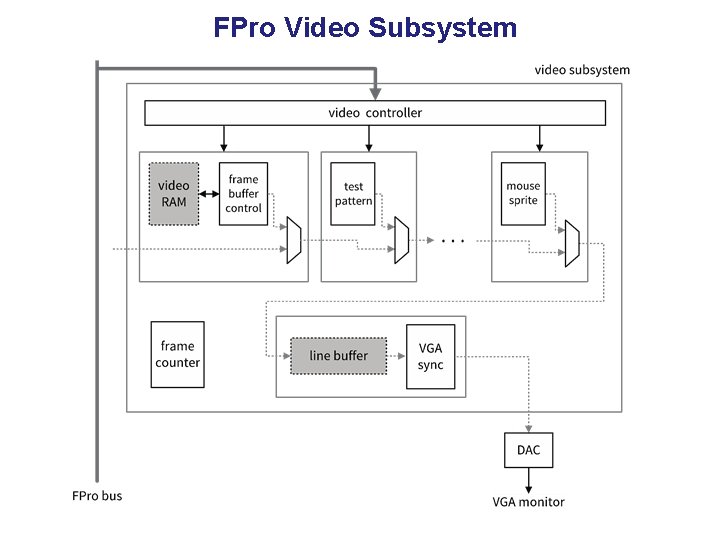

FPro Video Subsystem

VGA – Video Graphics Array • Video display standard introduced in the late 1980’s • Widely supported by PC graphics hardware and monitors • Used initially with the CRT (cathode ray tube) monitors • Later adopted for LCD (liquid-crystal display) monitors as well ECE 448 – FPGA and ASIC Design with VHDL 7

VGA – Characteristic Features • • Resolution: 640 x 480 Typical Refresh Rate: 60 Hz (frames / second) RGB: Red, Green and Blue analog signals Color depth: number of bits used to encode a color of each pixel § True color mode: 24 bits § Basic color mode: 3 bits § Monochrome: 1 bit ECE 448 – FPGA and ASIC Design with VHDL 8

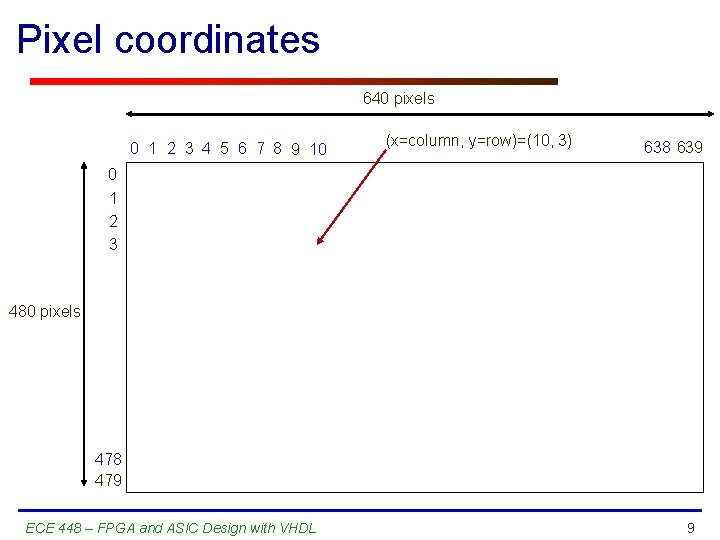

Pixel coordinates 640 pixels 0 1 2 3 4 5 6 7 8 9 10 (x=column, y=row)=(10, 3) 638 639 0 1 2 3 480 pixels 478 479 ECE 448 – FPGA and ASIC Design with VHDL 9

Three-bit VGA Color Combinations Red (R) Green (G) Blue (B) Resulting Color 0 0 0 black 0 0 1 blue 0 1 0 green 0 1 1 cyan 1 0 0 red 1 0 1 magenta 1 1 0 yellow 1 1 1 white ECE 448 – FPGA and ASIC Design with VHDL 10

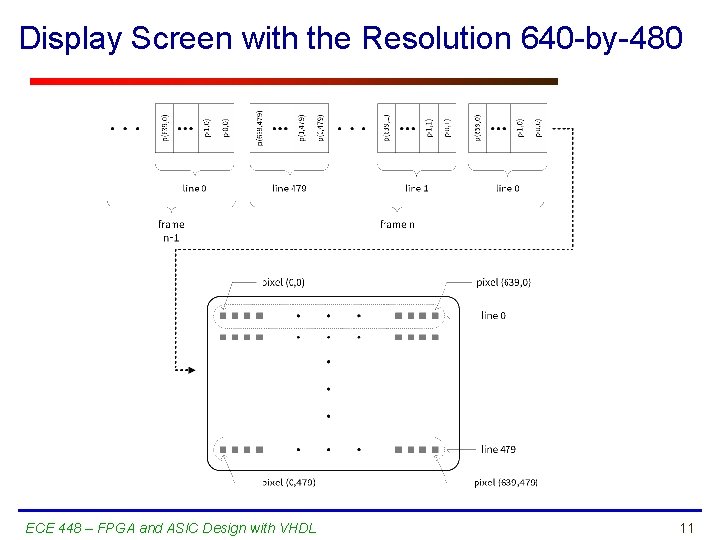

Display Screen with the Resolution 640 -by-480 ECE 448 – FPGA and ASIC Design with VHDL 11

FPro Video Subsystem

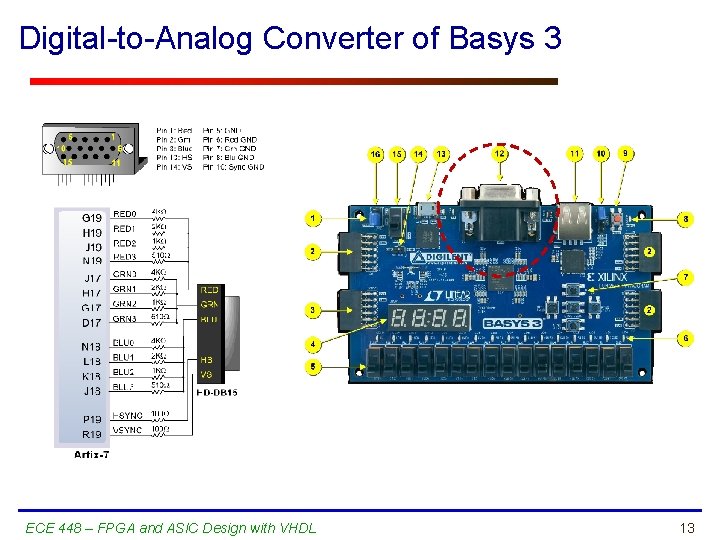

Digital-to-Analog Converter of Basys 3 ECE 448 – FPGA and ASIC Design with VHDL 13

FPro Video Subsystem

Frame Buffer • A special memory module that hold the bitmap of a complete frame • Each pixel can be independently retrieved and updated • Read pipe: a data retrieving circuit that reads memory continuously at the pixel rate • Write port connected to the processor that generates or updates the content of the frame ECE 448 – FPGA and ASIC Design with VHDL 15

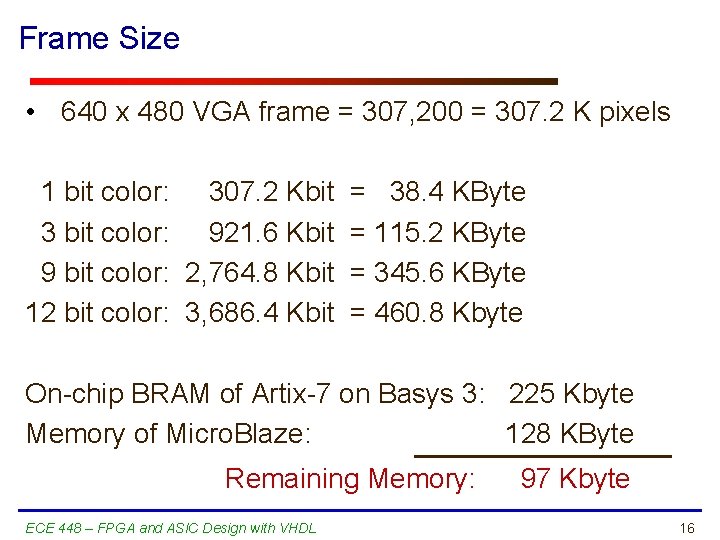

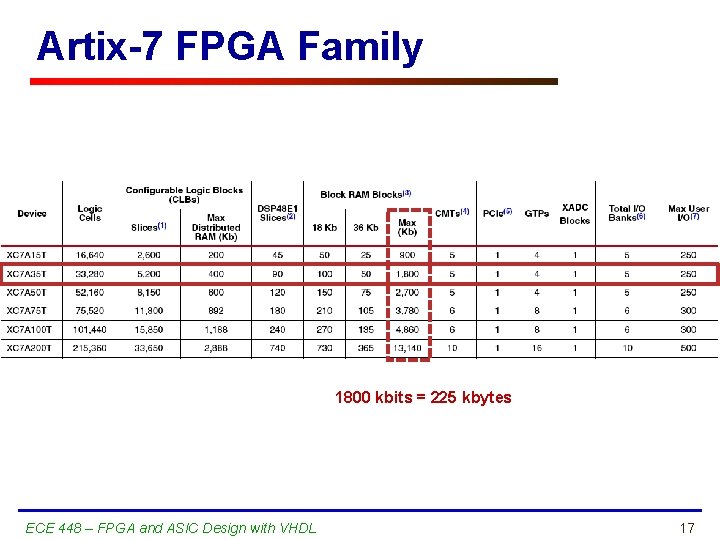

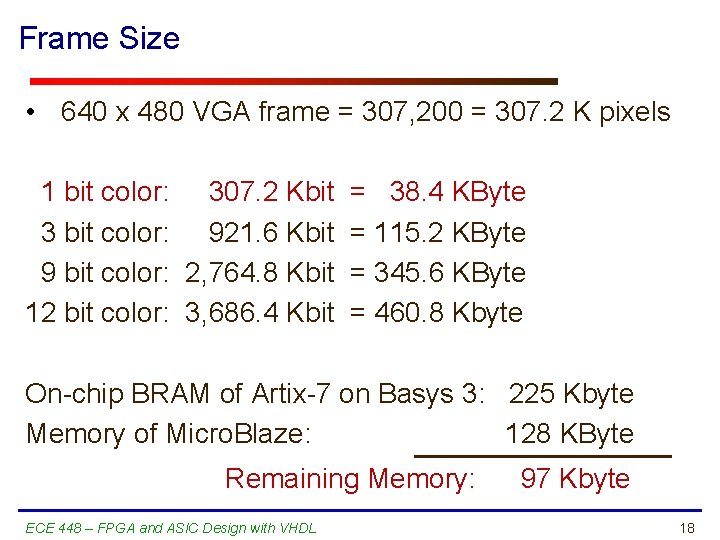

Frame Size • 640 x 480 VGA frame = 307, 200 = 307. 2 K pixels 1 bit color: 307. 2 Kbit 3 bit color: 921. 6 Kbit 9 bit color: 2, 764. 8 Kbit 12 bit color: 3, 686. 4 Kbit = 38. 4 KByte = 115. 2 KByte = 345. 6 KByte = 460. 8 Kbyte On-chip BRAM of Artix-7 on Basys 3: 225 Kbyte Memory of Micro. Blaze: 128 KByte Remaining Memory: ECE 448 – FPGA and ASIC Design with VHDL 97 Kbyte 16

Artix-7 FPGA Family 1800 kbits = 225 kbytes ECE 448 – FPGA and ASIC Design with VHDL 17

Frame Size • 640 x 480 VGA frame = 307, 200 = 307. 2 K pixels 1 bit color: 307. 2 Kbit 3 bit color: 921. 6 Kbit 9 bit color: 2, 764. 8 Kbit 12 bit color: 3, 686. 4 Kbit = 38. 4 KByte = 115. 2 KByte = 345. 6 KByte = 460. 8 Kbyte On-chip BRAM of Artix-7 on Basys 3: 225 Kbyte Memory of Micro. Blaze: 128 KByte Remaining Memory: ECE 448 – FPGA and ASIC Design with VHDL 97 Kbyte 18

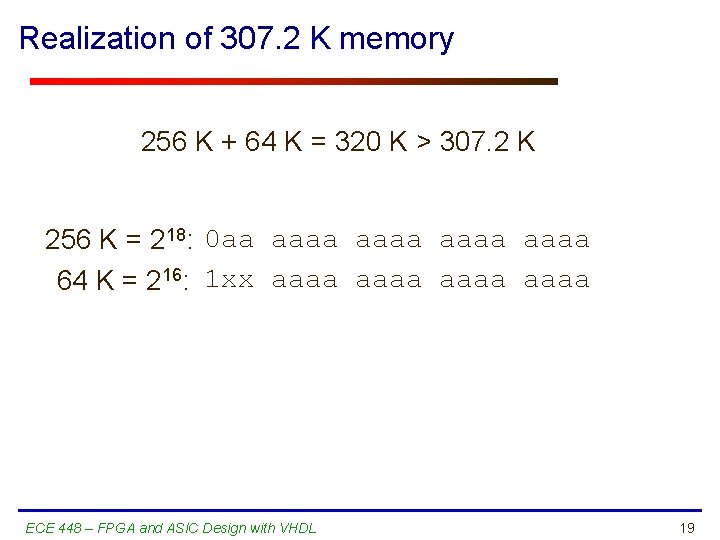

Realization of 307. 2 K memory 256 K + 64 K = 320 K > 307. 2 K 256 K = 218: 0 aa aaaa 64 K = 216: 1 xx aaaa ECE 448 – FPGA and ASIC Design with VHDL 19

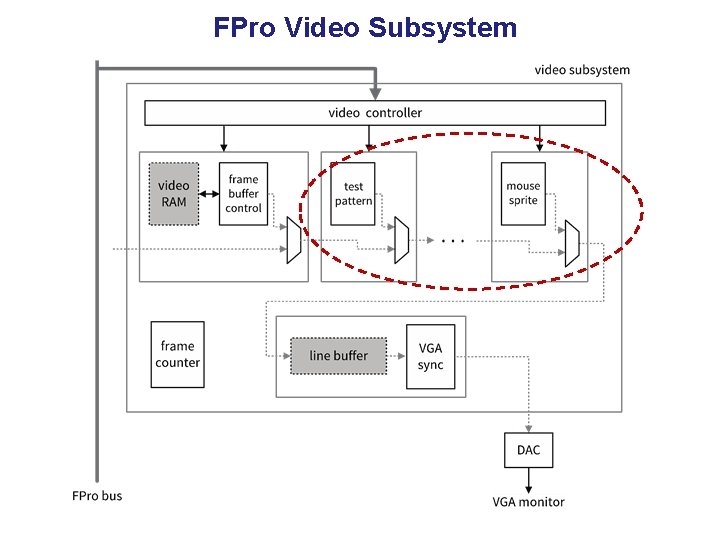

FPro Video Subsystem

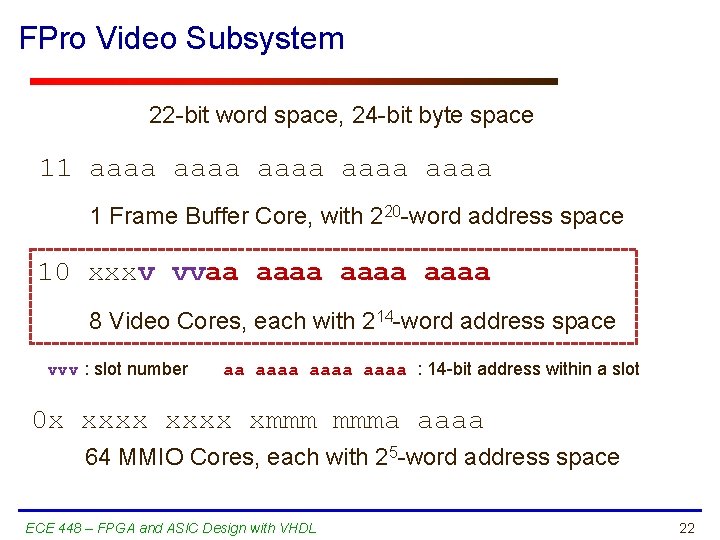

FPro Video Subsystem 22 -bit word space, 24 -bit byte space 11 aaaa aaaa 1 Frame Buffer Core, with 220 -word address space 10 xxxv vvaa aaaa 8 Video Cores, each with 214 -word address space vvv : slot number aa aaaa : 14 -bit address within a slot ECE 448 – FPGA and ASIC Design with VHDL 21

FPro Video Subsystem 22 -bit word space, 24 -bit byte space 11 aaaa aaaa 1 Frame Buffer Core, with 220 -word address space 10 xxxv vvaa aaaa 8 Video Cores, each with 214 -word address space vvv : slot number aa aaaa : 14 -bit address within a slot 0 x xxxx xmmm mmma aaaa 64 MMIO Cores, each with 25 -word address space ECE 448 – FPGA and ASIC Design with VHDL 22

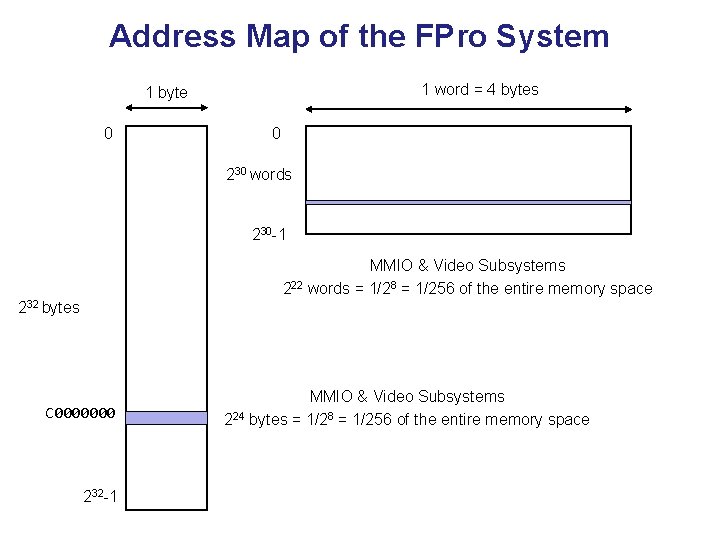

Address Map of the FPro System 1 word = 4 bytes 1 byte 0 0 230 words 230 -1 MMIO & Video Subsystems 222 words = 1/28 = 1/256 of the entire memory space 232 bytes C 0000000 232 -1 MMIO & Video Subsystems 224 bytes = 1/28 = 1/256 of the entire memory space

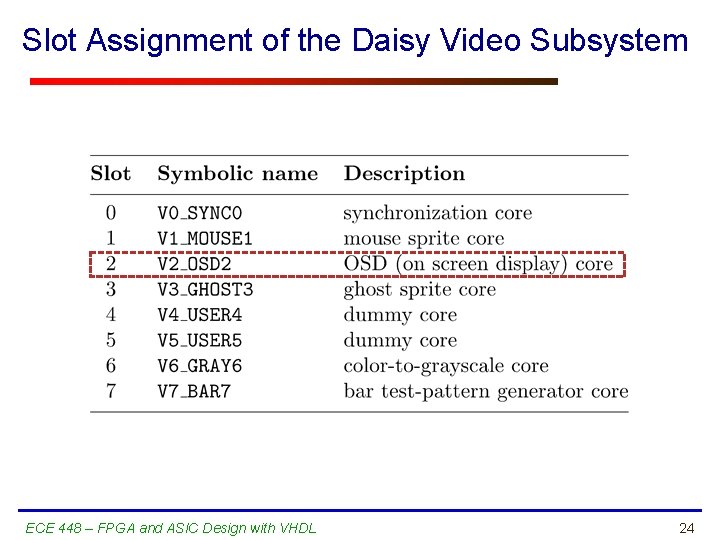

Slot Assignment of the Daisy Video Subsystem ECE 448 – FPGA and ASIC Design with VHDL 24

Two Types of FPro Video Cores e. g. . color-to-grayscale conversion ECE 448 – FPGA and ASIC Design with VHDL 25

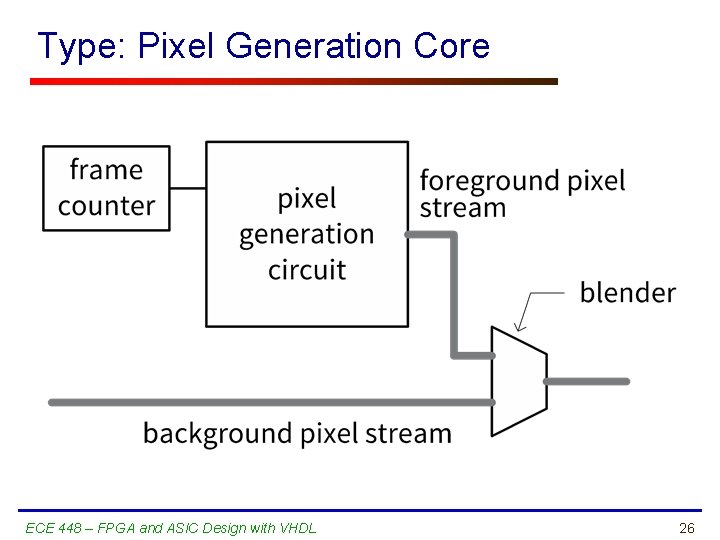

Type: Pixel Generation Core ECE 448 – FPGA and ASIC Design with VHDL 26

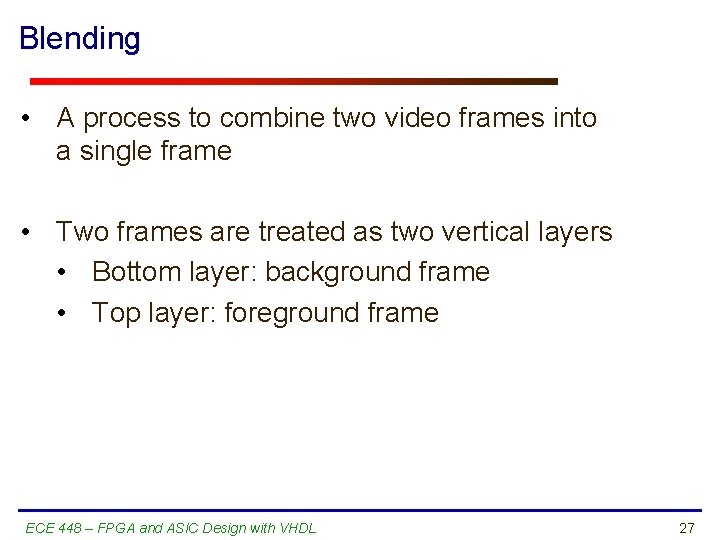

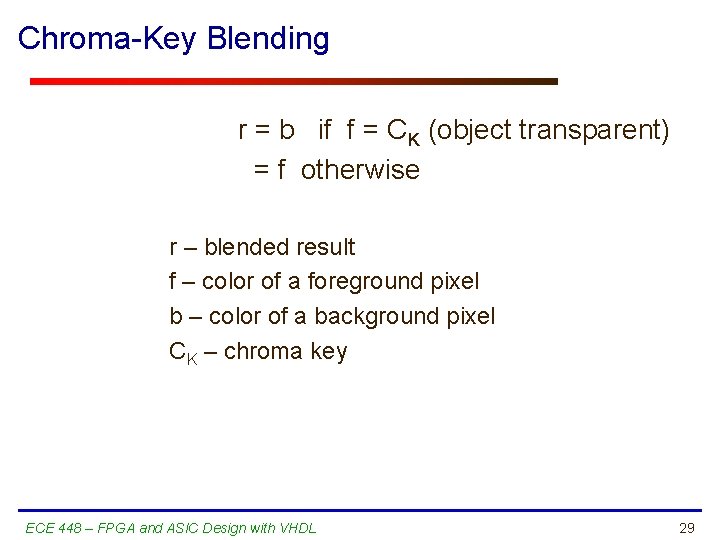

Blending • A process to combine two video frames into a single frame • Two frames are treated as two vertical layers • Bottom layer: background frame • Top layer: foreground frame ECE 448 – FPGA and ASIC Design with VHDL 27

Chroma-Key Blending Background Frame ECE 448 – FPGA and ASIC Design with VHDL Foreground Frame 28

Chroma-Key Blending r = b if f = CK (object transparent) = f otherwise r – blended result f – color of a foreground pixel b – color of a background pixel CK – chroma key ECE 448 – FPGA and ASIC Design with VHDL 29

Tile-Based Text & Symbol Generation ECE 448 – FPGA and ASIC Design with VHDL 30

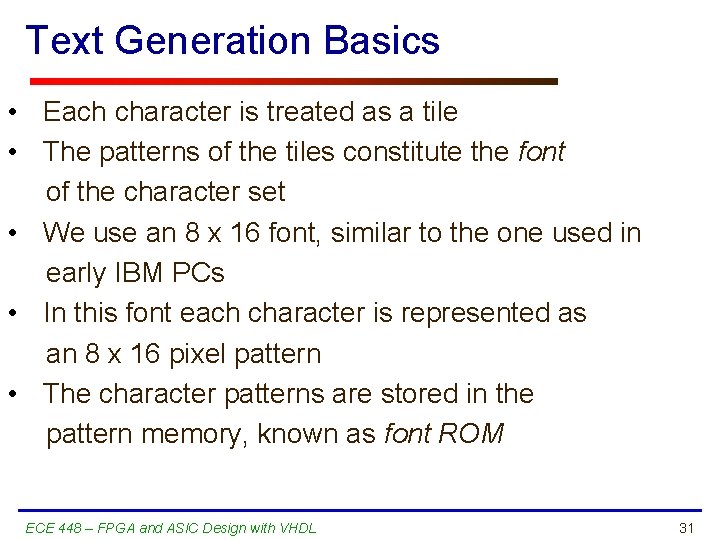

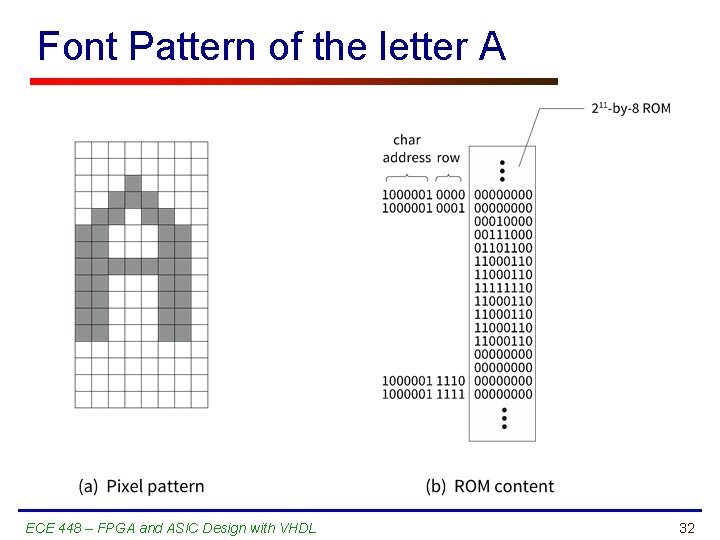

Text Generation Basics • Each character is treated as a tile • The patterns of the tiles constitute the font of the character set • We use an 8 x 16 font, similar to the one used in early IBM PCs • In this font each character is represented as an 8 x 16 pixel pattern • The character patterns are stored in the pattern memory, known as font ROM ECE 448 – FPGA and ASIC Design with VHDL 31

Font Pattern of the letter A ECE 448 – FPGA and ASIC Design with VHDL 32

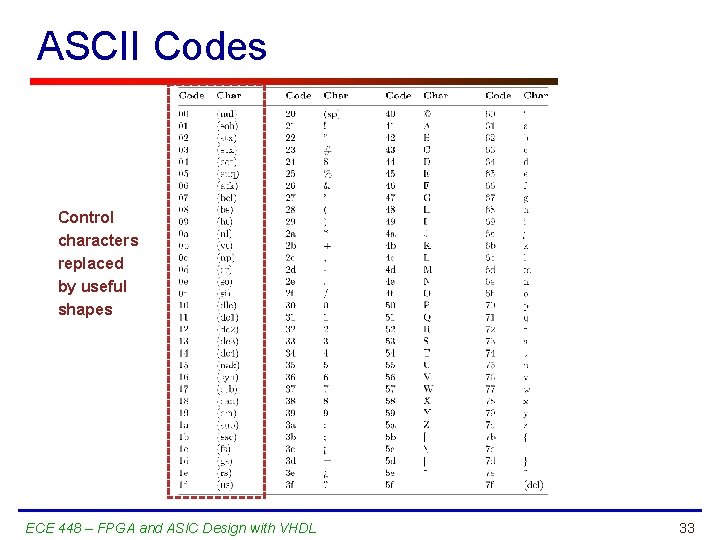

ASCII Codes Control characters replaced by useful shapes ECE 448 – FPGA and ASIC Design with VHDL 33

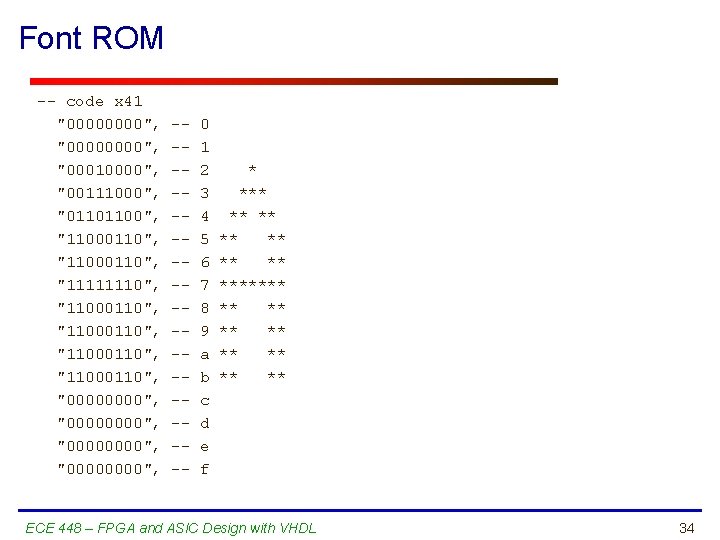

Font ROM -- code x 41 "00000000", "00010000", "00111000", "01101100", "11000110", "11111110", "11000110", "00000000", --------- 0 1 2 3 4 5 6 7 8 9 a b c d e f * ** ******* ** ** ECE 448 – FPGA and ASIC Design with VHDL 34

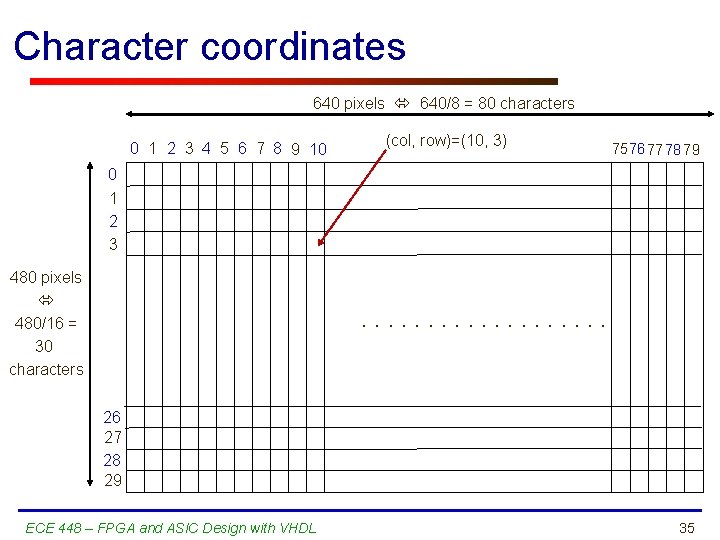

Character coordinates 640 pixels 640/8 = 80 characters 0 1 2 3 4 5 6 7 8 9 10 (col, row)=(10, 3) 7576 77 78 79 0 1 2 3 480 pixels 480/16 = 30 characters . . 26 27 28 29 ECE 448 – FPGA and ASIC Design with VHDL 35

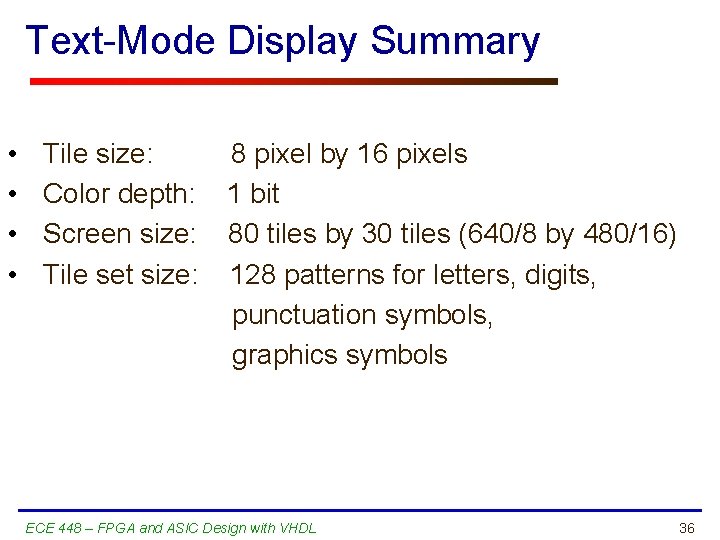

Text-Mode Display Summary • • Tile size: Color depth: Screen size: Tile set size: 8 pixel by 16 pixels 1 bit 80 tiles by 30 tiles (640/8 by 480/16) 128 patterns for letters, digits, punctuation symbols, graphics symbols ECE 448 – FPGA and ASIC Design with VHDL 36

An OSD Pixel Generation Circuit we_a ECE 448 – FPGA and ASIC Design with VHDL 37

An OSD Pixel Generation Circuit we_a 211 x 8 bit = 2 k x 8 bit = = 16 kbit = 2 kbyte ECE 448 – FPGA and ASIC Design with VHDL 38

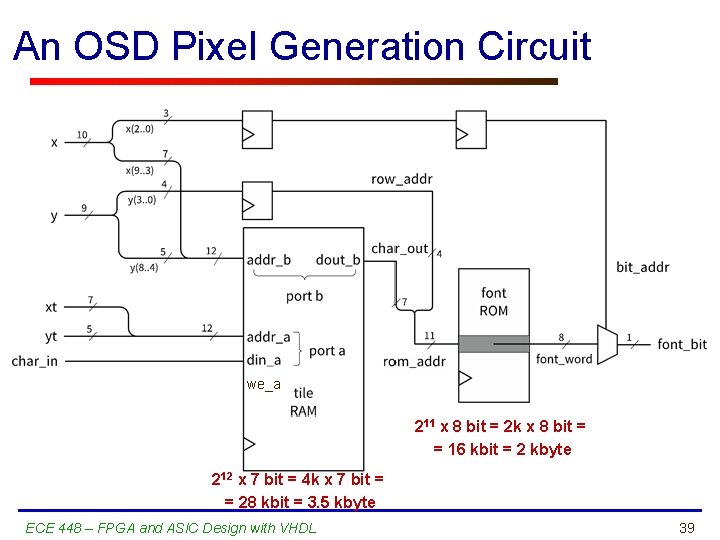

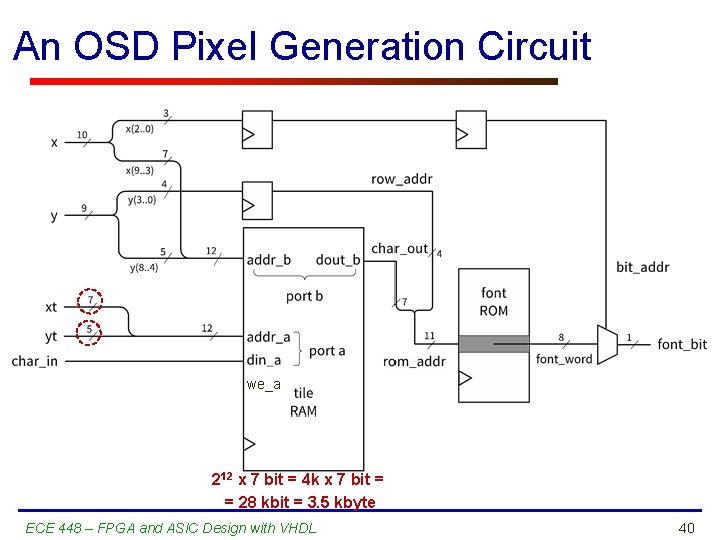

An OSD Pixel Generation Circuit we_a 211 x 8 bit = 2 k x 8 bit = = 16 kbit = 2 kbyte 212 x 7 bit = 4 k x 7 bit = = 28 kbit = 3. 5 kbyte ECE 448 – FPGA and ASIC Design with VHDL 39

An OSD Pixel Generation Circuit we_a 212 x 7 bit = 4 k x 7 bit = = 28 kbit = 3. 5 kbyte ECE 448 – FPGA and ASIC Design with VHDL 40

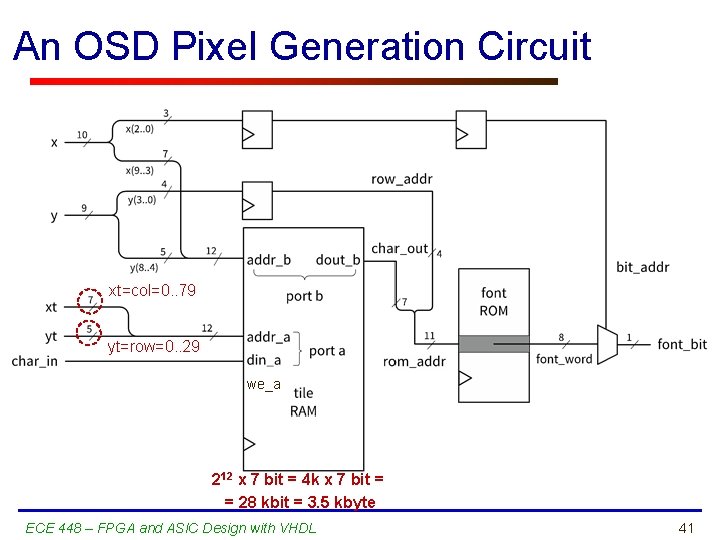

An OSD Pixel Generation Circuit xt=col=0. . 79 yt=row=0. . 29 we_a 212 x 7 bit = 4 k x 7 bit = = 28 kbit = 3. 5 kbyte ECE 448 – FPGA and ASIC Design with VHDL 41

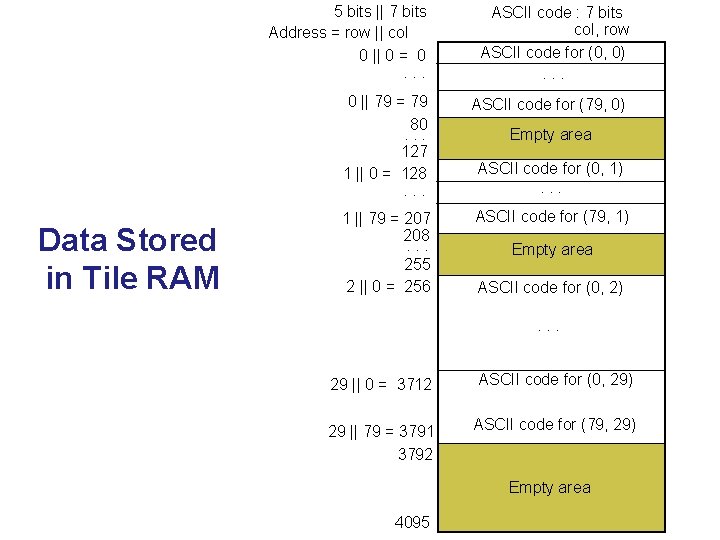

Data Stored in Tile RAM 5 bits || 7 bits Address = row || col 0 || 0 = 0. . . ASCII code : 7 bits col, row ASCII code for (0, 0). . . 0 || 79 = 79 80. . . 127 1 || 0 = 128. . . ASCII code for (79, 0) 1 || 79 = 207 208. . . 255 2 || 0 = 256 ASCII code for (79, 1) Empty area ASCII code for (0, 1). . . Empty area ASCII code for (0, 2). . . 29 || 0 = 3712 ASCII code for (0, 29) 29 || 79 = 3791 3792 ASCII code for (79, 29) Empty area 4095

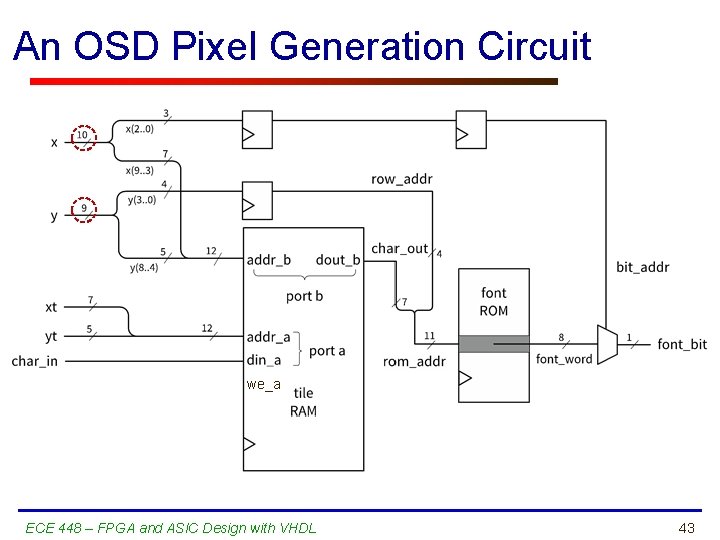

An OSD Pixel Generation Circuit we_a ECE 448 – FPGA and ASIC Design with VHDL 43

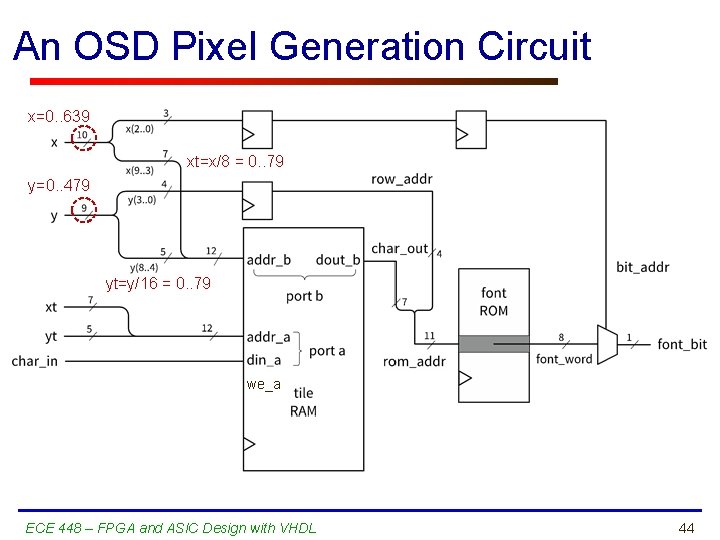

An OSD Pixel Generation Circuit x=0. . 639 xt=x/8 = 0. . 79 y=0. . 479 yt=y/16 = 0. . 79 we_a ECE 448 – FPGA and ASIC Design with VHDL 44

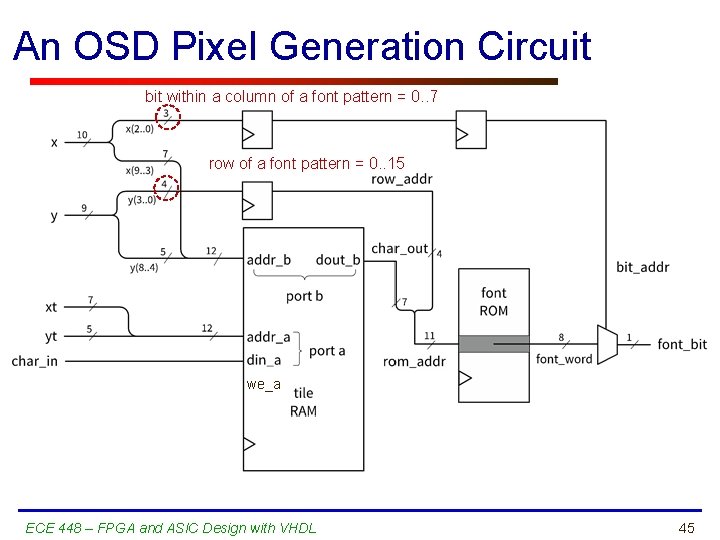

An OSD Pixel Generation Circuit bit within a column of a font pattern = 0. . 7 row of a font pattern = 0. . 15 we_a ECE 448 – FPGA and ASIC Design with VHDL 45

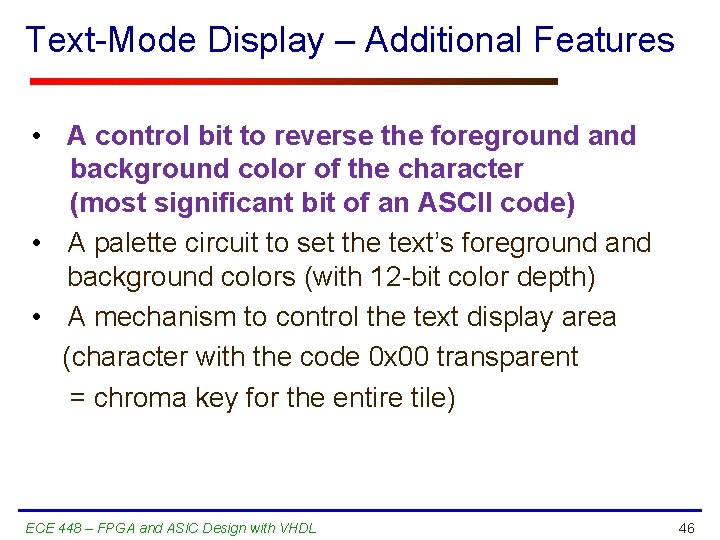

Text-Mode Display – Additional Features • A control bit to reverse the foreground and background color of the character (most significant bit of an ASCII code) • A palette circuit to set the text’s foreground and background colors (with 12 -bit color depth) • A mechanism to control the text display area (character with the code 0 x 00 transparent = chroma key for the entire tile) ECE 448 – FPGA and ASIC Design with VHDL 46

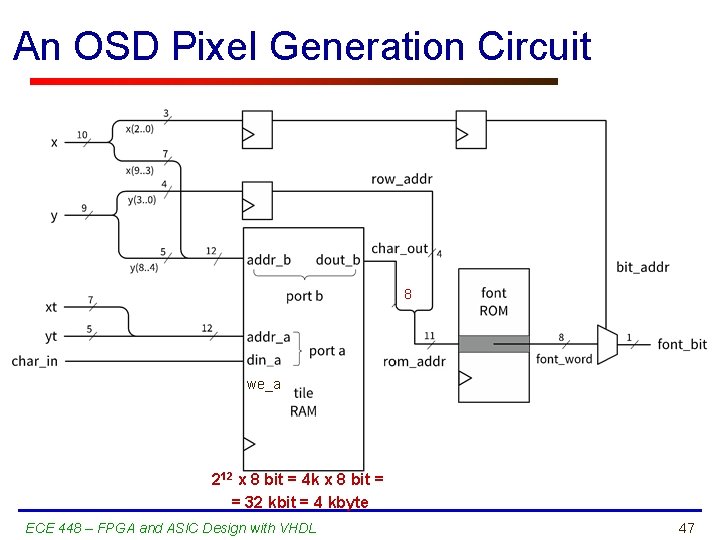

An OSD Pixel Generation Circuit 8 we_a 212 x 8 bit = 4 k x 8 bit = = 32 kbit = 4 kbyte ECE 448 – FPGA and ASIC Design with VHDL 47

Text-Mode Display – Additional Features • A control bit to reverse the foreground and background color of the character (most significant bit of an ASCII code) • A palette circuit to set the text’s foreground and background colors (with 12 -bit color depth) • A mechanism to control the text display area (character with the code 0 x 00 transparent = chroma key for the entire tile) ECE 448 – FPGA and ASIC Design with VHDL 48

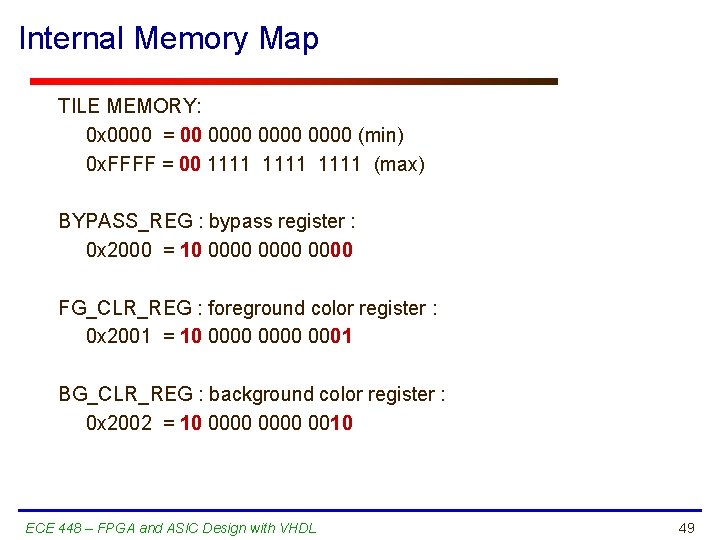

Internal Memory Map TILE MEMORY: 0 x 0000 = 00 0000 (min) 0 x. FFFF = 00 1111 (max) BYPASS_REG : bypass register : 0 x 2000 = 10 0000 FG_CLR_REG : foreground color register : 0 x 2001 = 10 0000 0001 BG_CLR_REG : background color register : 0 x 2002 = 10 0000 0010 ECE 448 – FPGA and ASIC Design with VHDL 49

Driver Code ECE 448 – FPGA and ASIC Design with VHDL 50

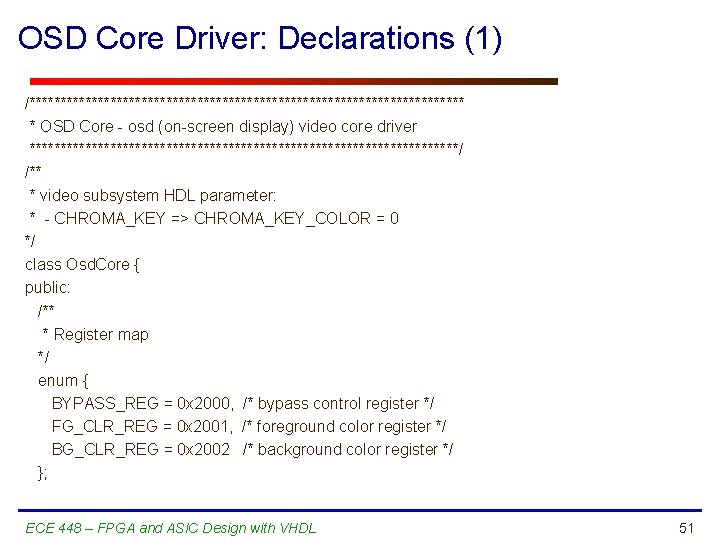

OSD Core Driver: Declarations (1) /*********************************** * OSD Core - osd (on-screen display) video core driver ***********************************/ /** * video subsystem HDL parameter: * - CHROMA_KEY => CHROMA_KEY_COLOR = 0 */ class Osd. Core { public: /** * Register map */ enum { BYPASS_REG = 0 x 2000, /* bypass control register */ FG_CLR_REG = 0 x 2001, /* foreground color register */ BG_CLR_REG = 0 x 2002 /* background color register */ }; ECE 448 – FPGA and ASIC Design with VHDL 51

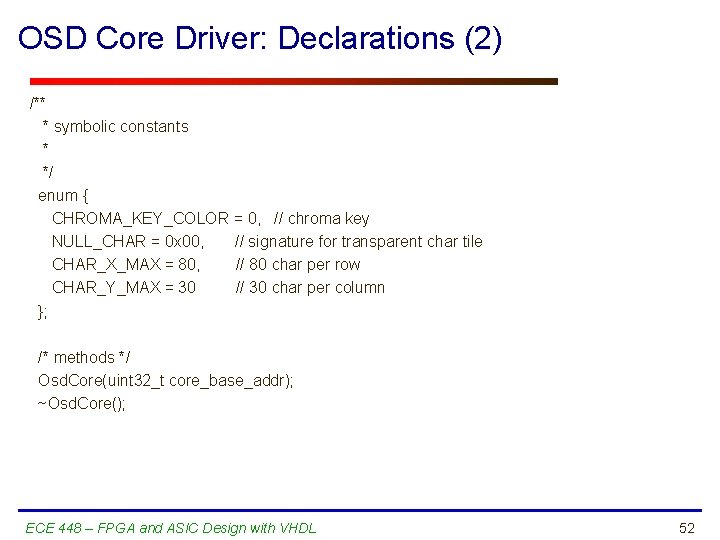

OSD Core Driver: Declarations (2) /** * symbolic constants * */ enum { CHROMA_KEY_COLOR = 0, // chroma key NULL_CHAR = 0 x 00, // signature for transparent char tile CHAR_X_MAX = 80, // 80 char per row CHAR_Y_MAX = 30 // 30 char per column }; /* methods */ Osd. Core(uint 32_t core_base_addr); ~Osd. Core(); ECE 448 – FPGA and ASIC Design with VHDL 52

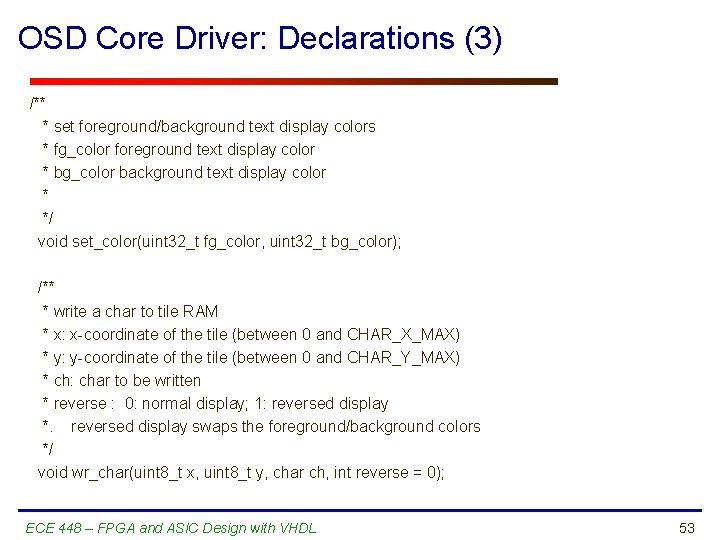

OSD Core Driver: Declarations (3) /** * set foreground/background text display colors * fg_color foreground text display color * bg_color background text display color * */ void set_color(uint 32_t fg_color, uint 32_t bg_color); /** * write a char to tile RAM * x: x-coordinate of the tile (between 0 and CHAR_X_MAX) * y: y-coordinate of the tile (between 0 and CHAR_Y_MAX) * ch: char to be written * reverse : 0: normal display; 1: reversed display *. reversed display swaps the foreground/background colors */ void wr_char(uint 8_t x, uint 8_t y, char ch, int reverse = 0); ECE 448 – FPGA and ASIC Design with VHDL 53

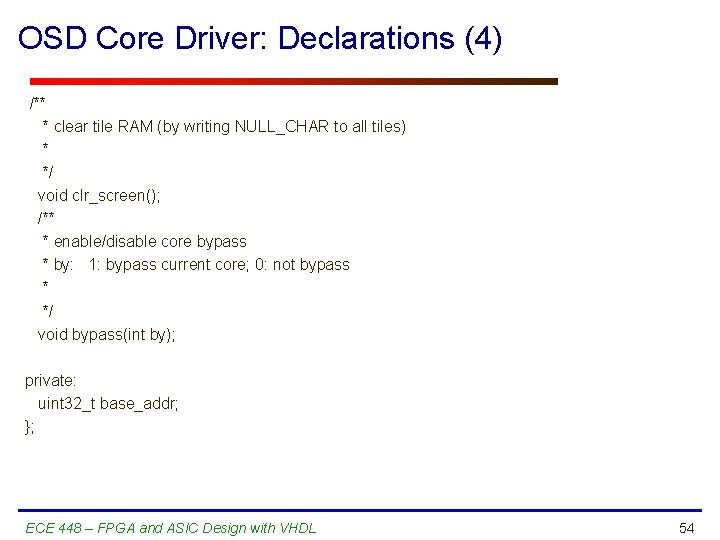

OSD Core Driver: Declarations (4) /** * clear tile RAM (by writing NULL_CHAR to all tiles) * */ void clr_screen(); /** * enable/disable core bypass * by: 1: bypass current core; 0: not bypass * */ void bypass(int by); private: uint 32_t base_addr; }; ECE 448 – FPGA and ASIC Design with VHDL 54

OSD Driver Functions ECE 448 – FPGA and ASIC Design with VHDL 55

Internal Memory Map TILE MEMORY: 0 x 0000 = 0 0000 (min) 0 x. FFFF = 0 1111 (max) BYPASS_REG : bypass register : 0 x 2000 = 1 0000 FG_CLR_REG : foreground color register : 0 x 2001 = 1 0000 0001 BG_CLR_REG : background color register : 0 x 2002 = 1 0000 0010 ECE 448 – FPGA and ASIC Design with VHDL 56

OSD Core Driver: Functions (1) Osd. Core: : Osd. Core(uint 32_t core_base_addr) { base_addr = core_base_addr; set_color(0 x 0 f 0, CHROMA_KEY_COLOR); // green on black } Osd. Core: : ~Osd. Core() { } void Osd. Core: : bypass(int by) { io_write(base_addr, BYPASS_REG, (uint 32_t ) by); } ECE 448 – FPGA and ASIC Design with VHDL 57

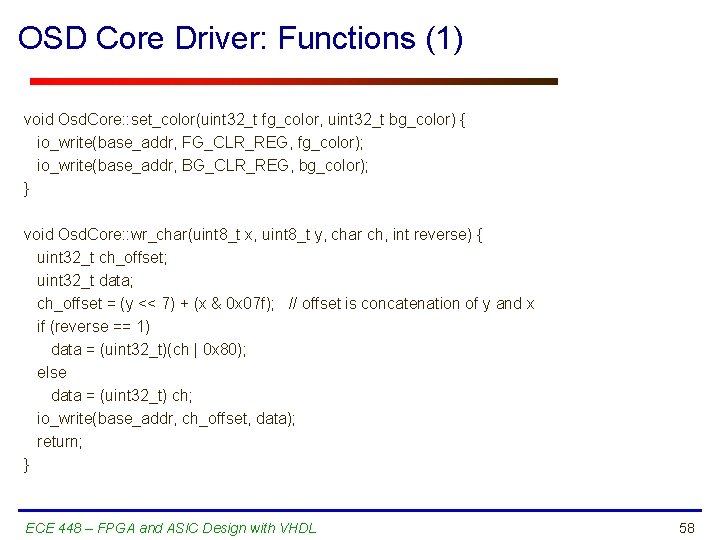

OSD Core Driver: Functions (1) void Osd. Core: : set_color(uint 32_t fg_color, uint 32_t bg_color) { io_write(base_addr, FG_CLR_REG, fg_color); io_write(base_addr, BG_CLR_REG, bg_color); } void Osd. Core: : wr_char(uint 8_t x, uint 8_t y, char ch, int reverse) { uint 32_t ch_offset; uint 32_t data; ch_offset = (y << 7) + (x & 0 x 07 f); // offset is concatenation of y and x if (reverse == 1) data = (uint 32_t)(ch | 0 x 80); else data = (uint 32_t) ch; io_write(base_addr, ch_offset, data); return; } ECE 448 – FPGA and ASIC Design with VHDL 58

OSD Core Driver: Functions (2) void Osd. Core: : clr_screen() { int x, y; for (x = 0; x < CHAR_X_MAX; x++) for (y = 0; y < CHAR_Y_MAX; y++) { wr_char(x, y, NULL_CHAR); } return; } ECE 448 – FPGA and ASIC Design with VHDL 59

OSD Driver Test ECE 448 – FPGA and ASIC Design with VHDL 60

OSD Core Test #include "chu_init. h" #include "gpio_cores. h" #include "vga_core. h” Osd. Core osd(get_sprite_addr(BRIDGE_BASE, V 2_OSD)); main() { osd. set_color(0 x 0 f 0, 0 x 001); // dark gray/green osd. bypass(0); osd. clr_screen(); for (int i = 0; i < 64; i++) { osd. wr_char(8 + i, 20, i); osd. wr_char(8 + i, 21, 64 + i, 1); sleep_ms(100); } sleep_ms(3000); } ECE 448 – FPGA and ASIC Design with VHDL 61

- Slides: 61