ECE 448 Lecture 20 Video Cores ECE 448

- Slides: 64

ECE 448 Lecture 20 Video Cores ECE 448 – FPGA and ASIC Design with VHDL George Mason University

Required Reading • P. Chu, FPGA Prototyping by VHDL Examples Chapter 21. 3, Example Video Cores ECE 448 – FPGA and ASIC Design with VHDL 2

Source Code Companion Website of FPGA Prototyping by VHDL Examples 2 nd edition https: //academic. csuohio. edu/chu_p/rtl/fpga_mcs_vhdl. html § Source code read_me file: readme_source_code. pdf source file: fpga_mcs_vhdl_src. zip (last updated 11/10/2017) fpga_mcs_vhdl_src/hdl/video/bar fpga_mcs_vhdl_src/hdl/sys/subsys/video_sys_daisy*. vhd fpga_mcs_vhdl_src/cpp/drv/vga_core [. h, . cpp] fpga_mcs_vhdl_src/cpp/app/main_video_test. cpp ECE 448 – FPGA and ASIC Design with VHDL 3

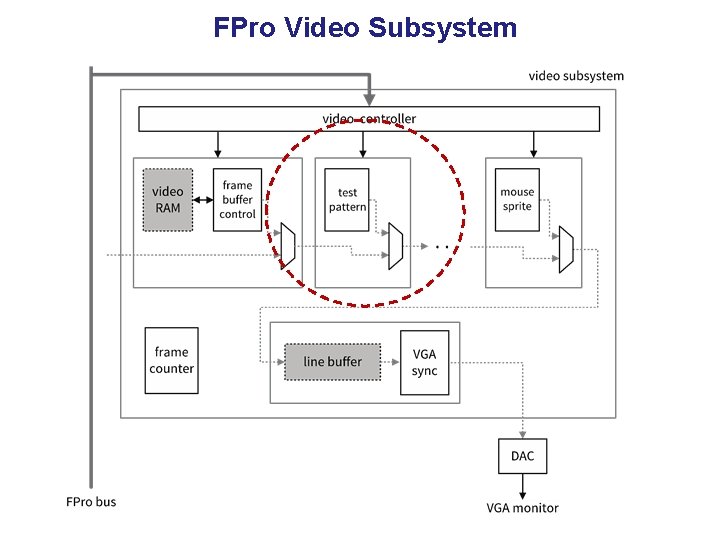

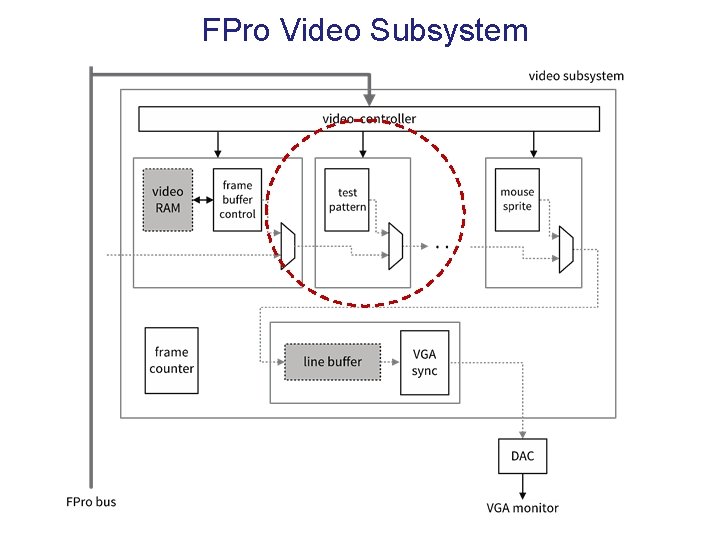

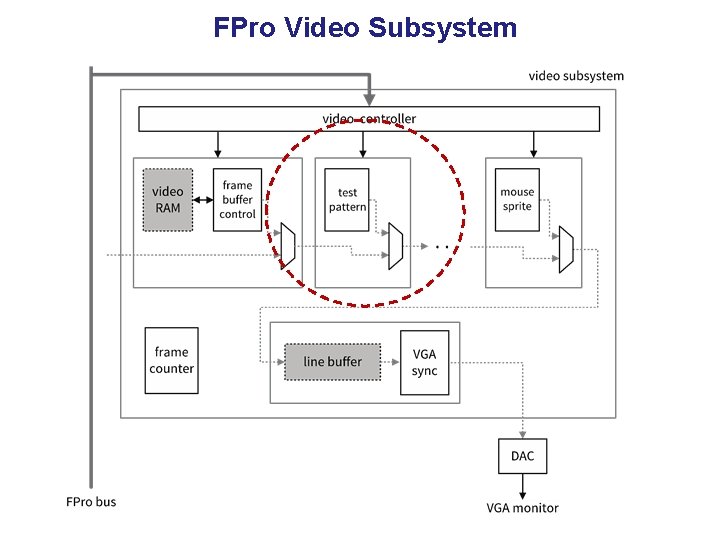

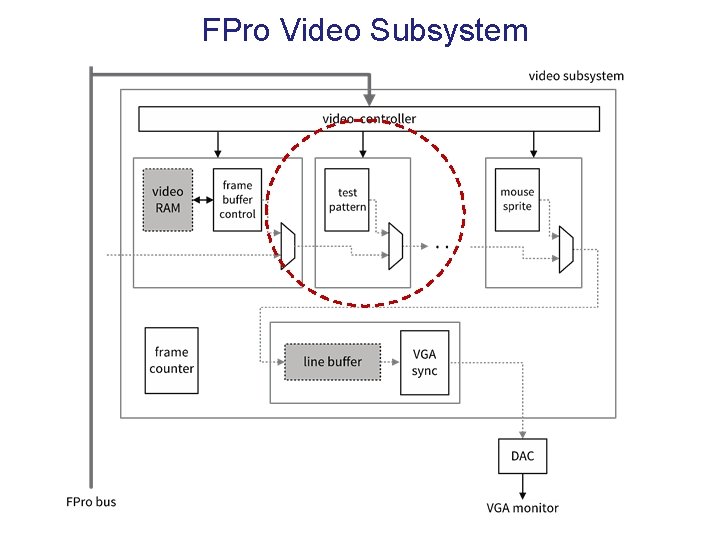

FPro Video Subsystem

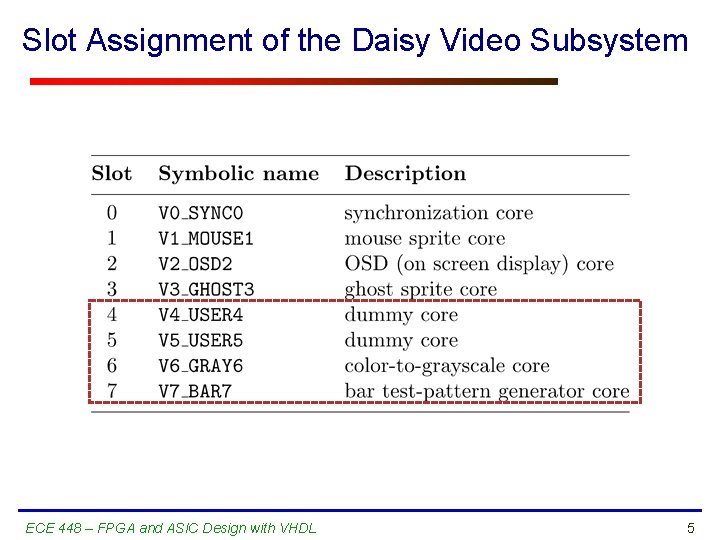

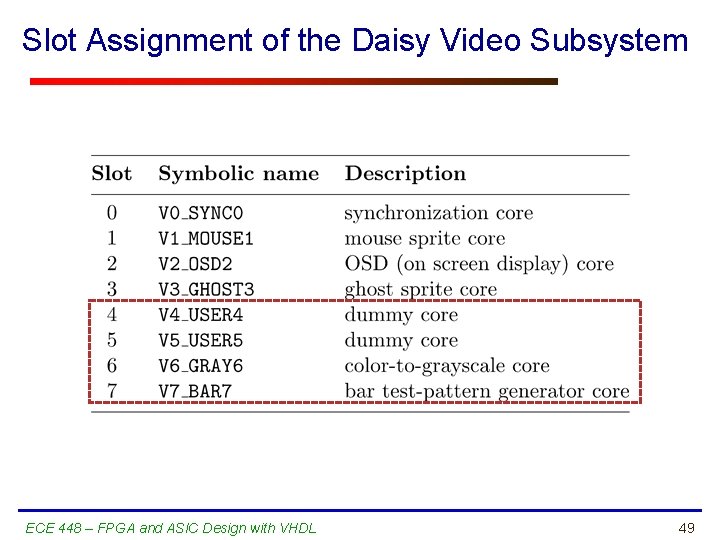

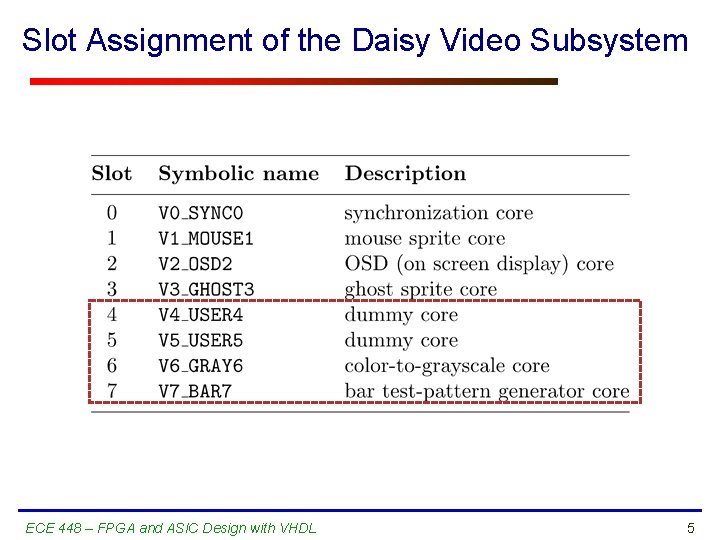

Slot Assignment of the Daisy Video Subsystem ECE 448 – FPGA and ASIC Design with VHDL 5

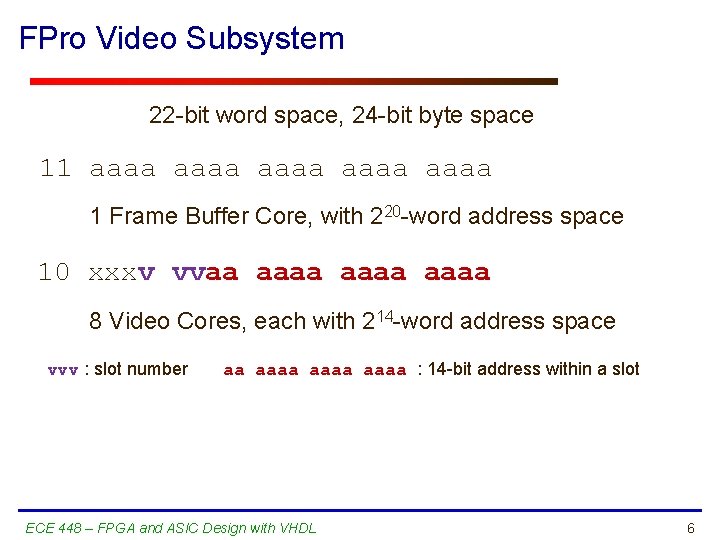

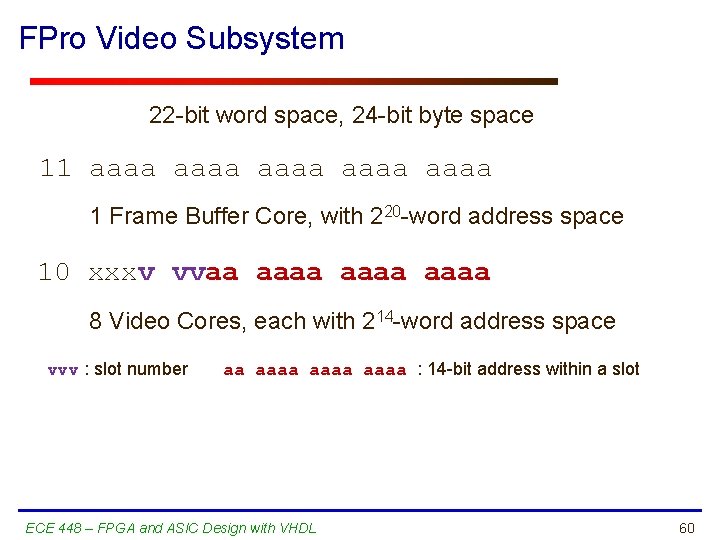

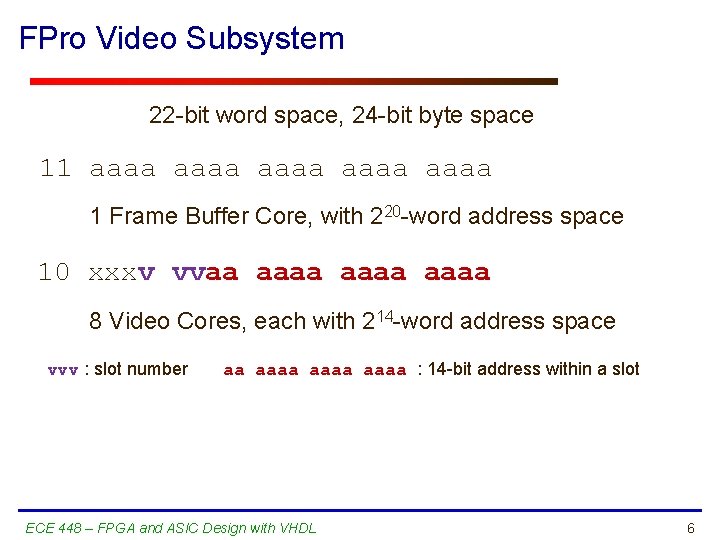

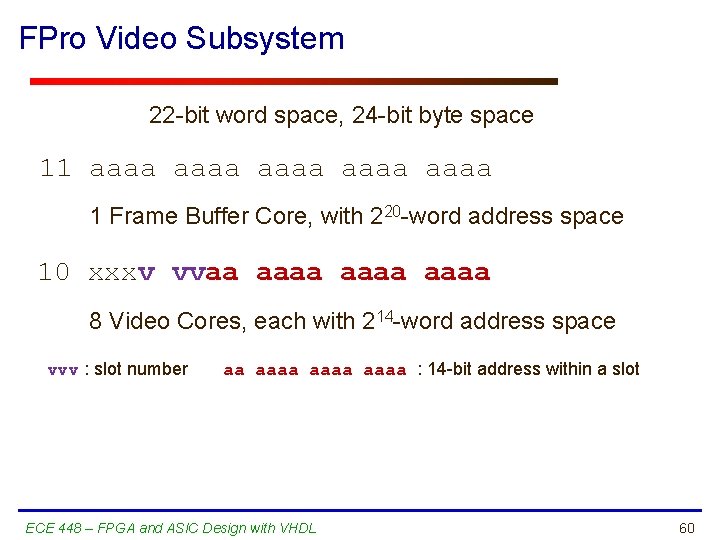

FPro Video Subsystem 22 -bit word space, 24 -bit byte space 11 aaaa aaaa 1 Frame Buffer Core, with 220 -word address space 10 xxxv vvaa aaaa 8 Video Cores, each with 214 -word address space vvv : slot number aa aaaa : 14 -bit address within a slot ECE 448 – FPGA and ASIC Design with VHDL 6

Motivation Labs 5 & 6 ECE 448 – FPGA and ASIC Design with VHDL 7

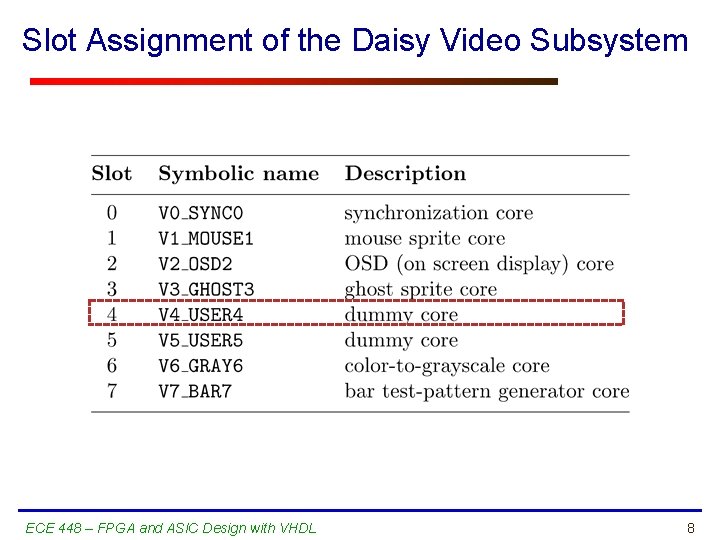

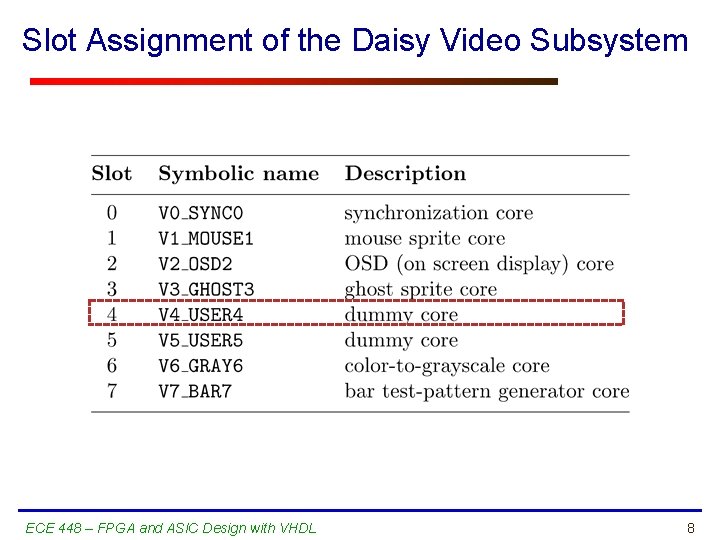

Slot Assignment of the Daisy Video Subsystem ECE 448 – FPGA and ASIC Design with VHDL 8

Lab 5 Video Core ECE 448 – FPGA and ASIC Design with VHDL

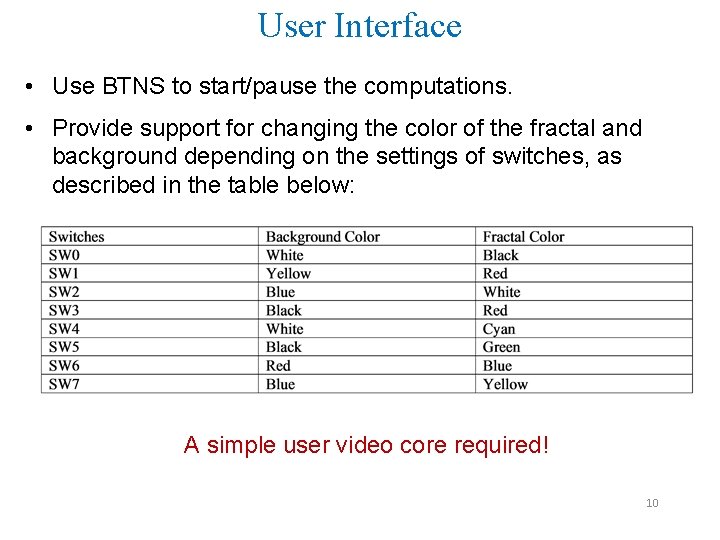

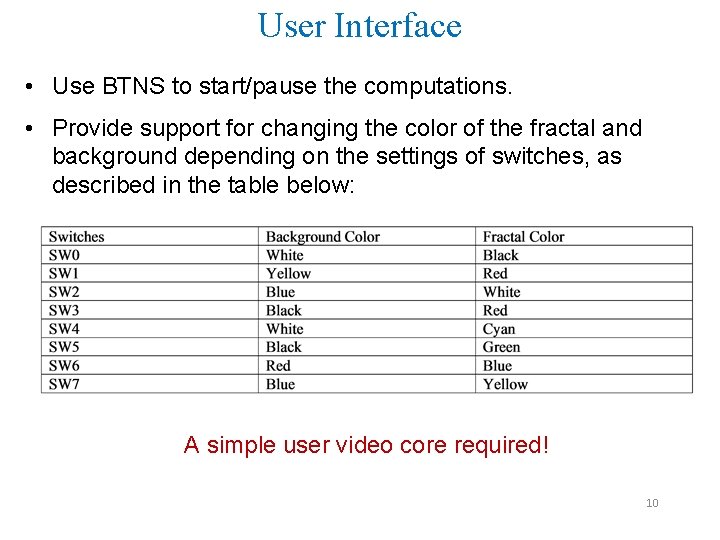

User Interface • Use BTNS to start/pause the computations. • Provide support for changing the color of the fractal and background depending on the settings of switches, as described in the table below: A simple user video core required! 10

Lab 6 Video Core ECE 448 – FPGA and ASIC Design with VHDL 11

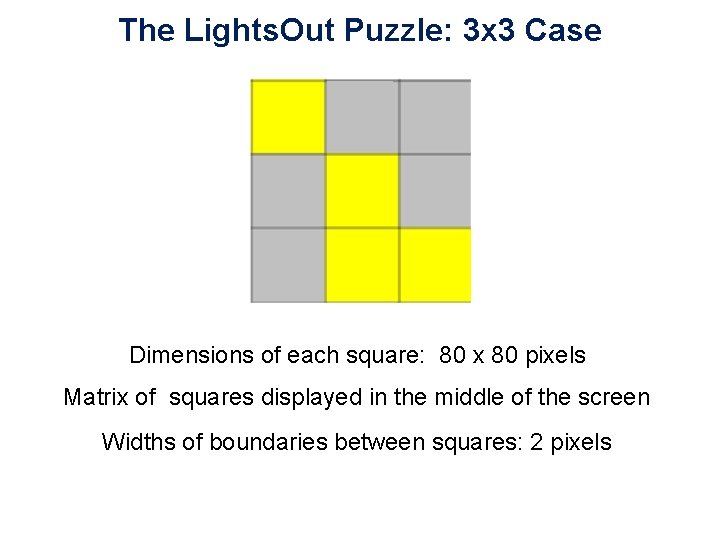

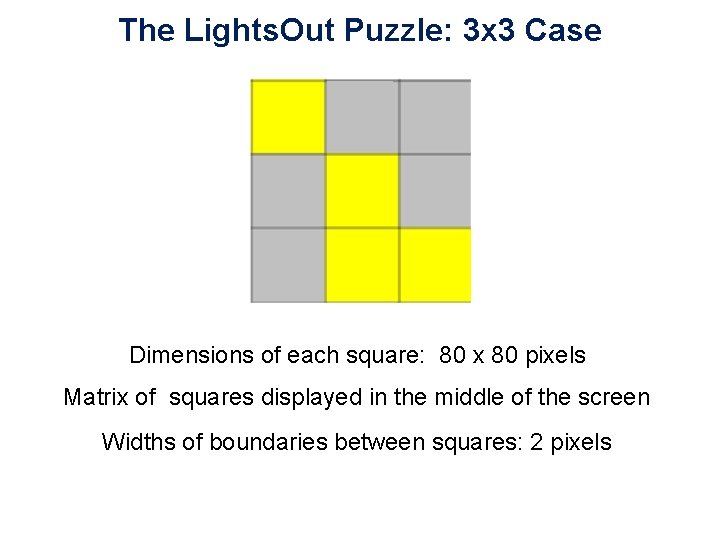

The Lights. Out Puzzle: 3 x 3 Case Dimensions of each square: 80 x 80 pixels Matrix of squares displayed in the middle of the screen Widths of boundaries between squares: 2 pixels

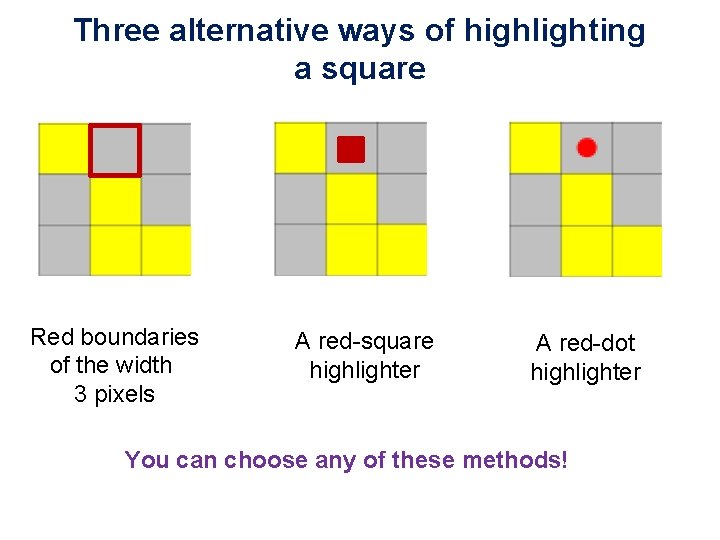

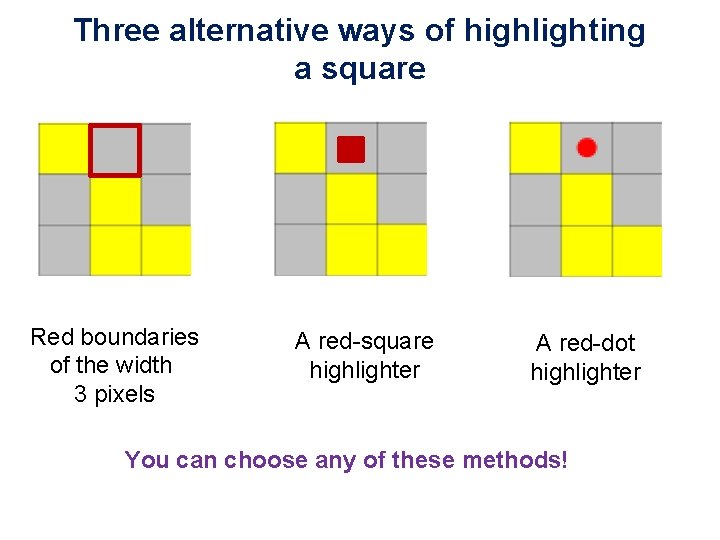

Three alternative ways of highlighting a square Red boundaries of the width 3 pixels A red-square highlighter A red-dot highlighter You can choose any of these methods!

Bar Test-Pattern Generator Core ECE 448 – FPGA and ASIC Design with VHDL

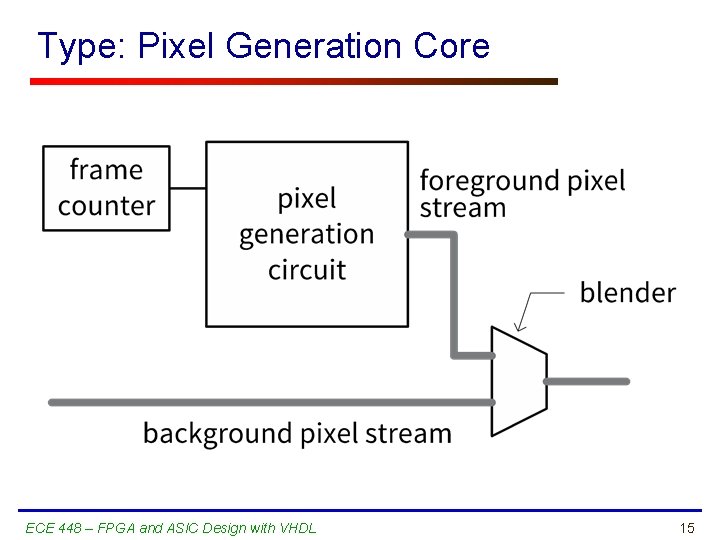

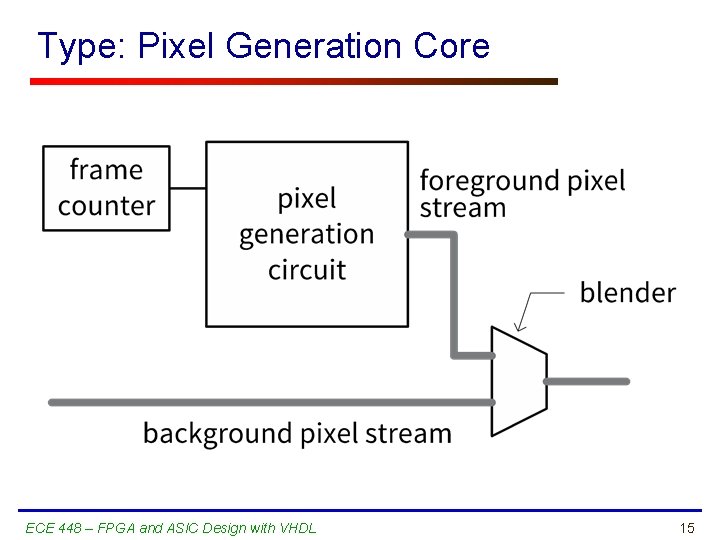

Type: Pixel Generation Core ECE 448 – FPGA and ASIC Design with VHDL 15

FPro Video Subsystem

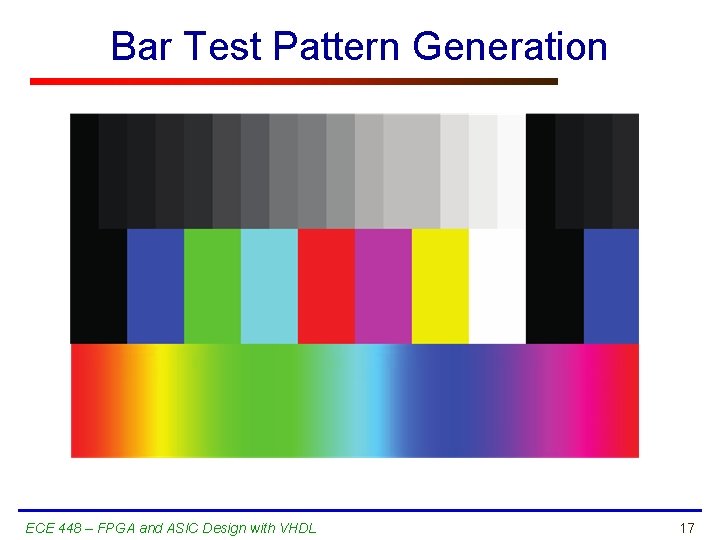

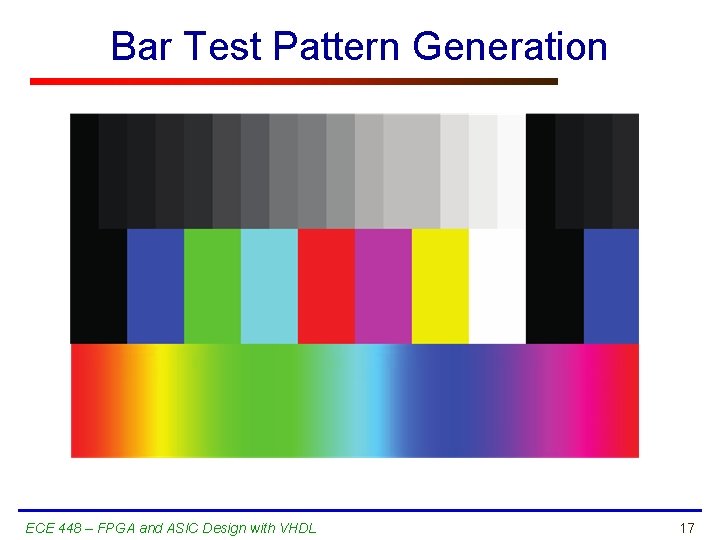

Bar Test Pattern Generation ECE 448 – FPGA and ASIC Design with VHDL 17

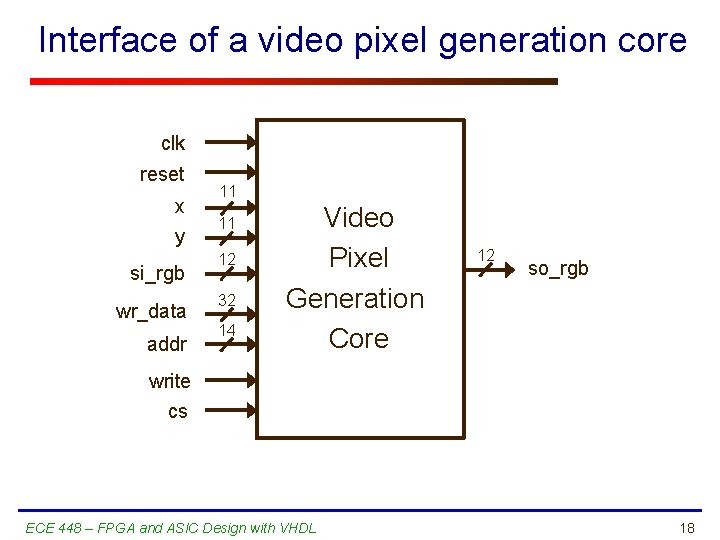

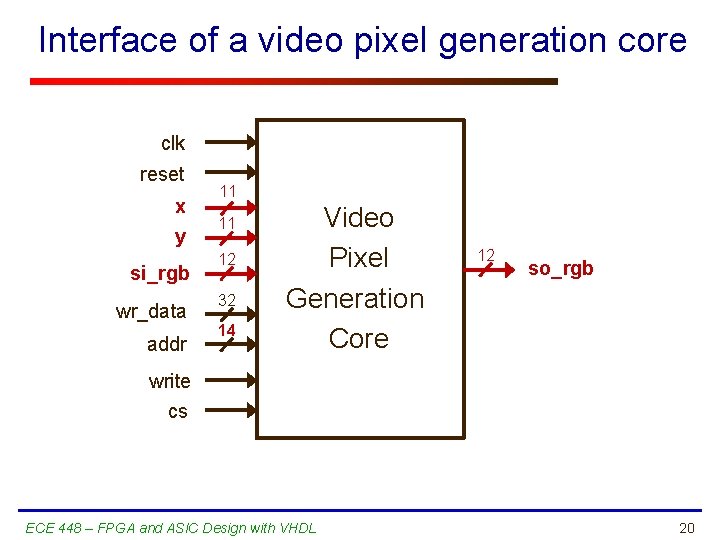

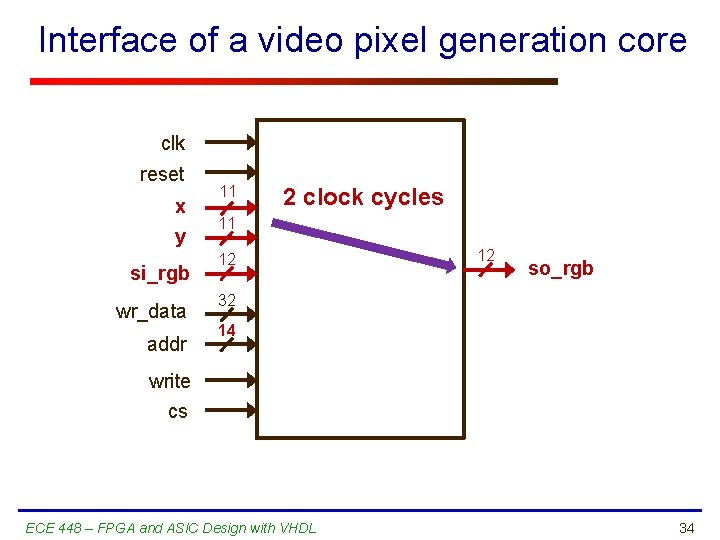

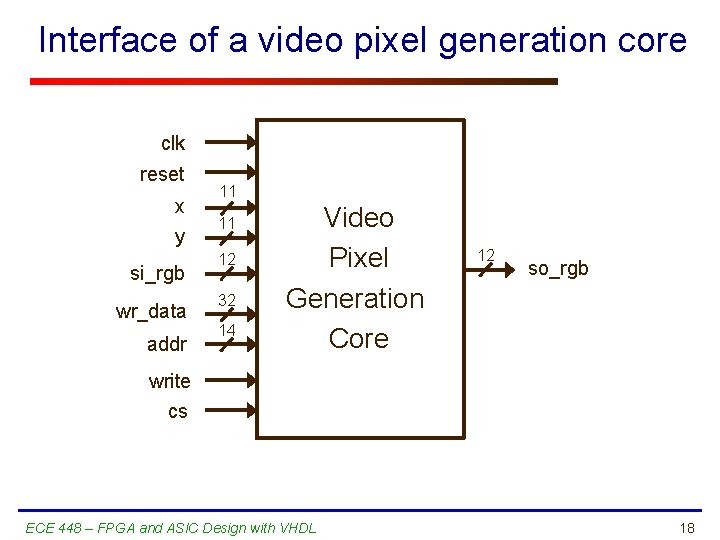

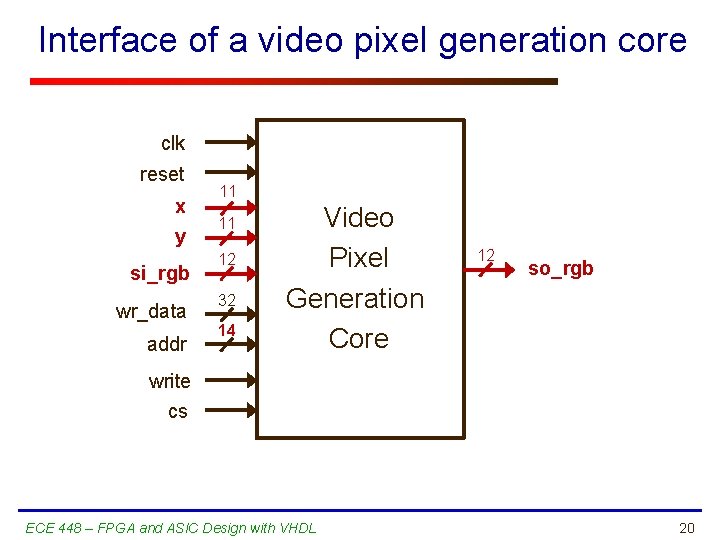

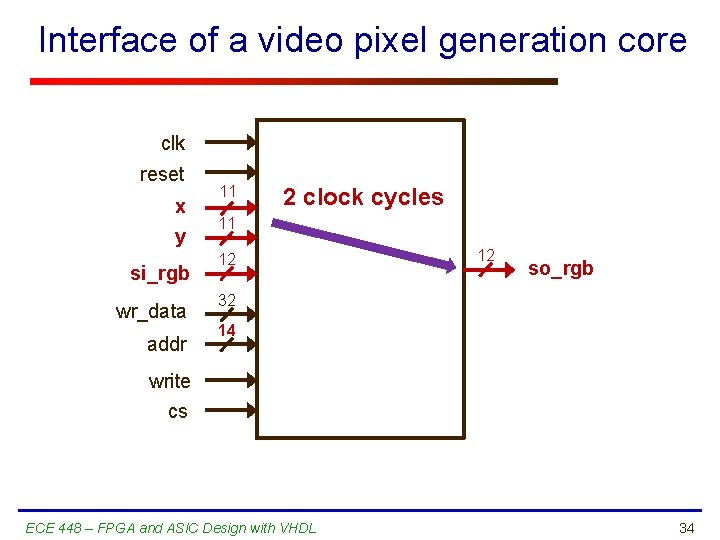

Interface of a video pixel generation core clk reset x y si_rgb wr_data addr 11 11 12 32 14 Video Pixel Generation Core 12 so_rgb write cs ECE 448 – FPGA and ASIC Design with VHDL 18

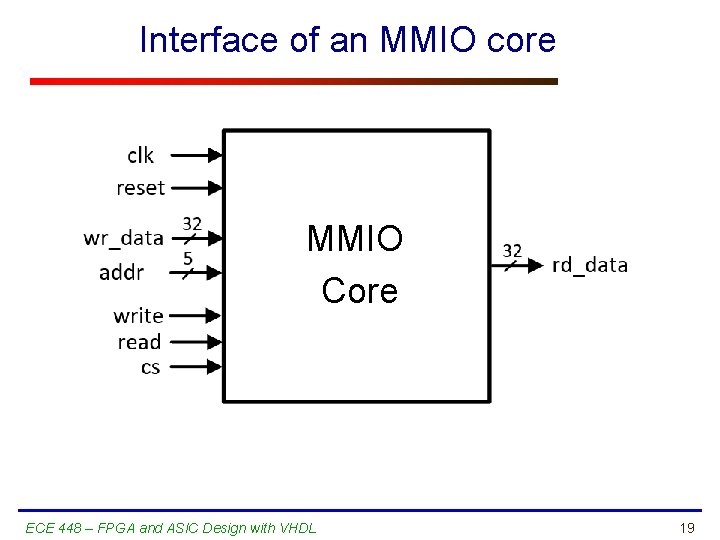

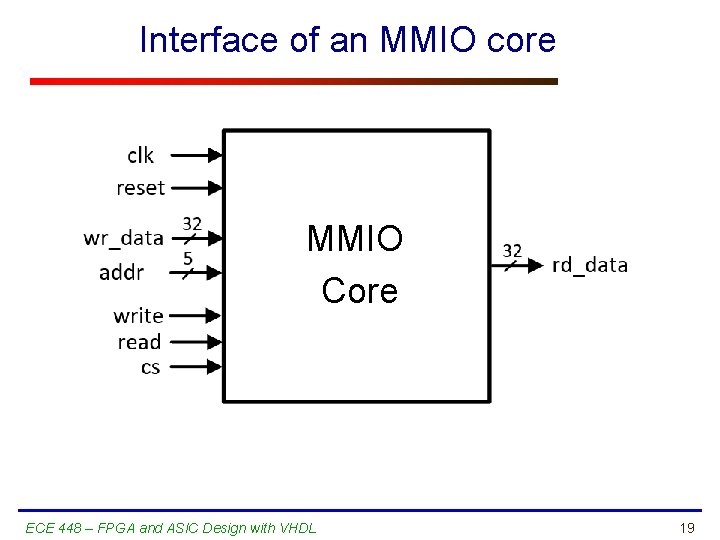

Interface of an MMIO core MMIO Core ECE 448 – FPGA and ASIC Design with VHDL 19

Interface of a video pixel generation core clk reset x y si_rgb wr_data addr 11 11 12 32 14 Video Pixel Generation Core 12 so_rgb write cs ECE 448 – FPGA and ASIC Design with VHDL 20

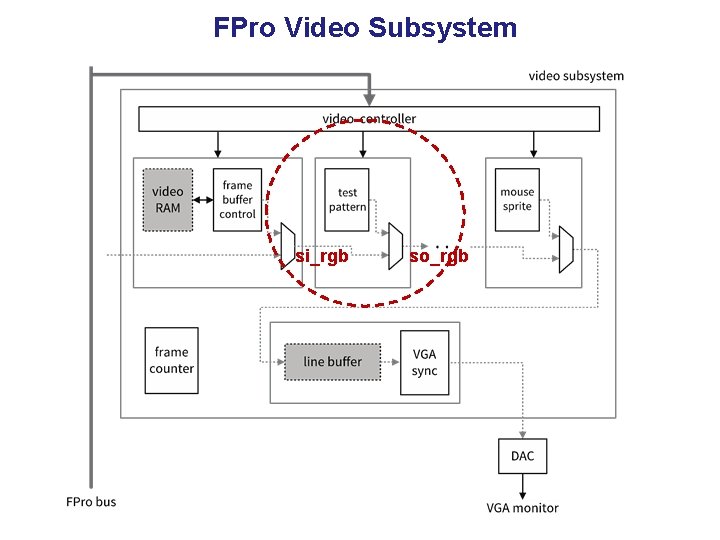

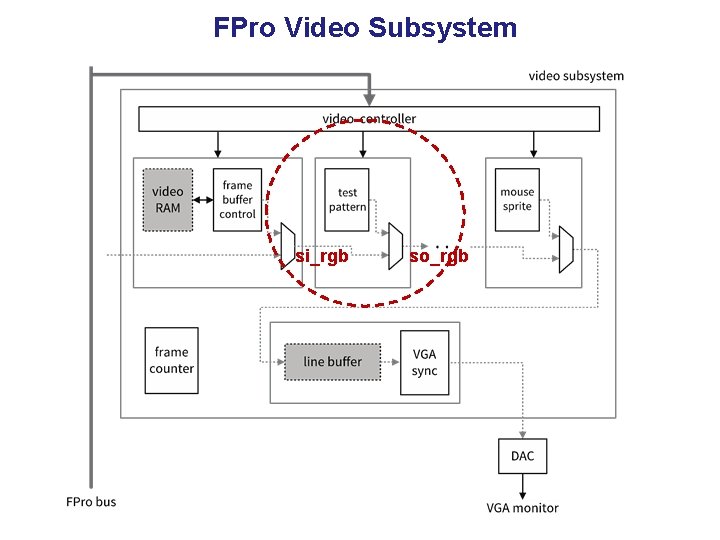

FPro Video Subsystem si_rgb so_rgb

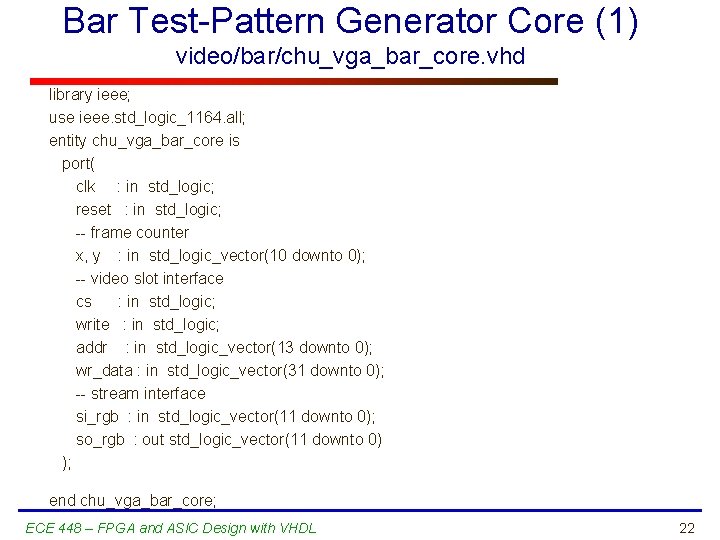

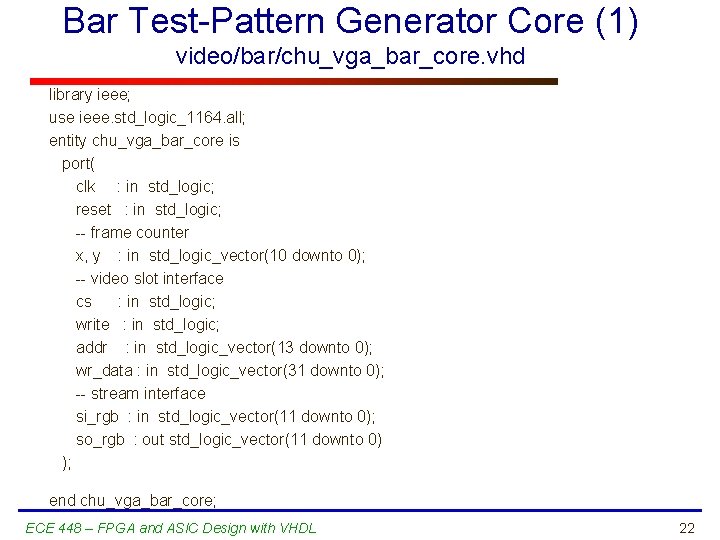

Bar Test-Pattern Generator Core (1) video/bar/chu_vga_bar_core. vhd library ieee; use ieee. std_logic_1164. all; entity chu_vga_bar_core is port( clk : in std_logic; reset : in std_logic; -- frame counter x, y : in std_logic_vector(10 downto 0); -- video slot interface cs : in std_logic; write : in std_logic; addr : in std_logic_vector(13 downto 0); wr_data : in std_logic_vector(31 downto 0); -- stream interface si_rgb : in std_logic_vector(11 downto 0); so_rgb : out std_logic_vector(11 downto 0) ); end chu_vga_bar_core; ECE 448 – FPGA and ASIC Design with VHDL 22

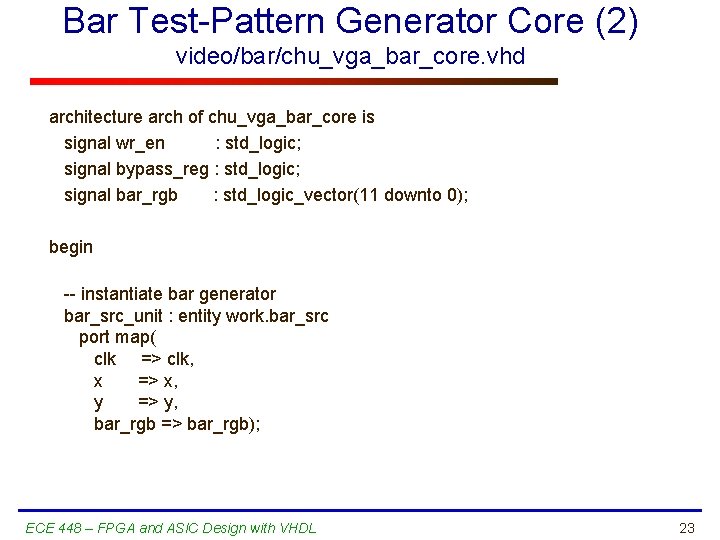

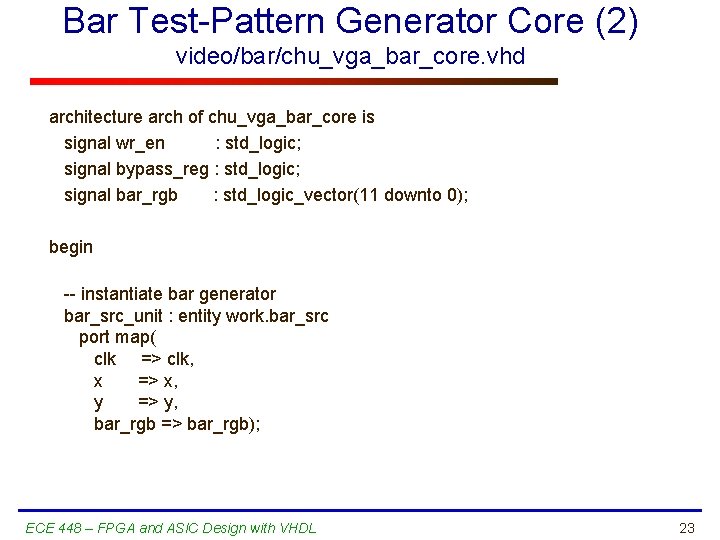

Bar Test-Pattern Generator Core (2) video/bar/chu_vga_bar_core. vhd architecture arch of chu_vga_bar_core is signal wr_en : std_logic; signal bypass_reg : std_logic; signal bar_rgb : std_logic_vector(11 downto 0); begin -- instantiate bar generator bar_src_unit : entity work. bar_src port map( clk => clk, x => x, y => y, bar_rgb => bar_rgb); ECE 448 – FPGA and ASIC Design with VHDL 23

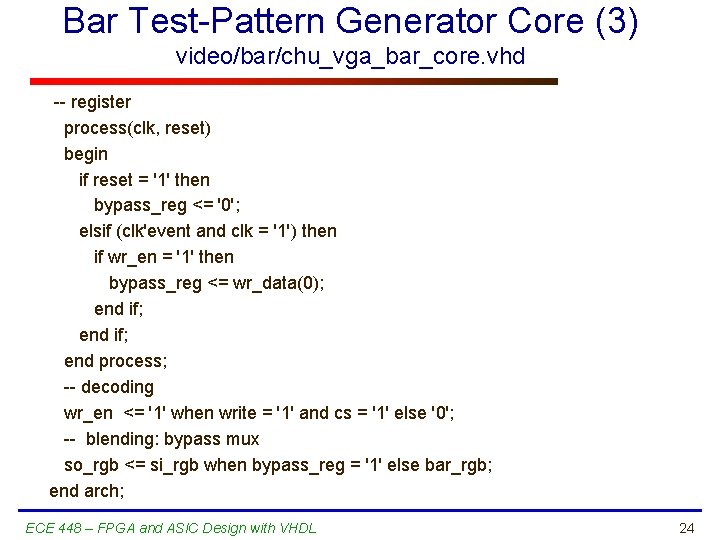

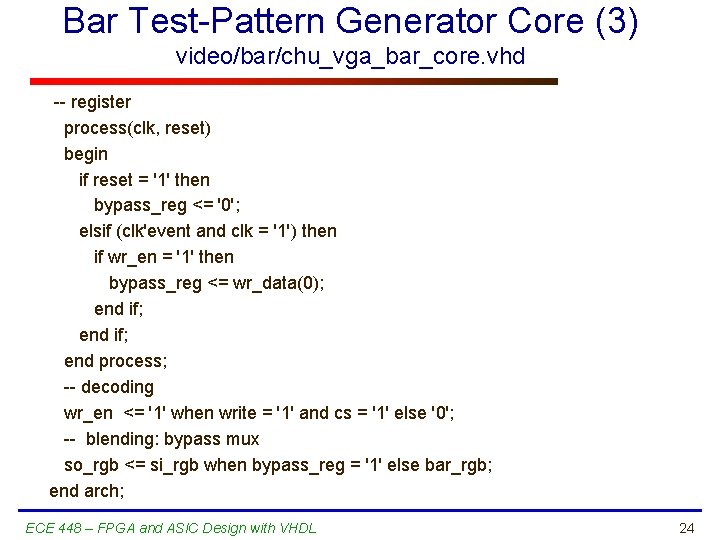

Bar Test-Pattern Generator Core (3) video/bar/chu_vga_bar_core. vhd -- register process(clk, reset) begin if reset = '1' then bypass_reg <= '0'; elsif (clk'event and clk = '1') then if wr_en = '1' then bypass_reg <= wr_data(0); end if; end process; -- decoding wr_en <= '1' when write = '1' and cs = '1' else '0'; -- blending: bypass mux so_rgb <= si_rgb when bypass_reg = '1' else bar_rgb; end arch; ECE 448 – FPGA and ASIC Design with VHDL 24

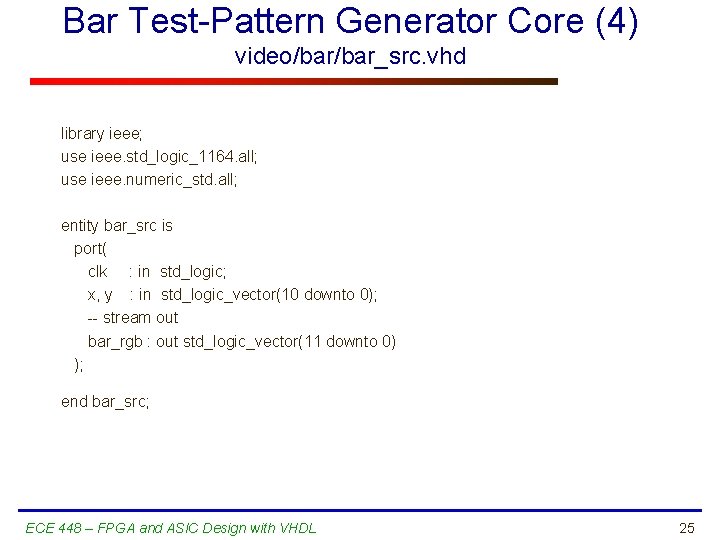

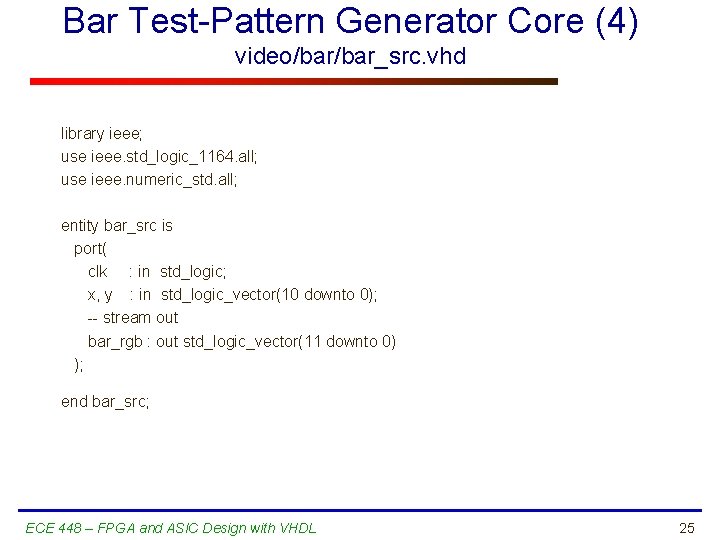

Bar Test-Pattern Generator Core (4) video/bar_src. vhd library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity bar_src is port( clk : in std_logic; x, y : in std_logic_vector(10 downto 0); -- stream out bar_rgb : out std_logic_vector(11 downto 0) ); end bar_src; ECE 448 – FPGA and ASIC Design with VHDL 25

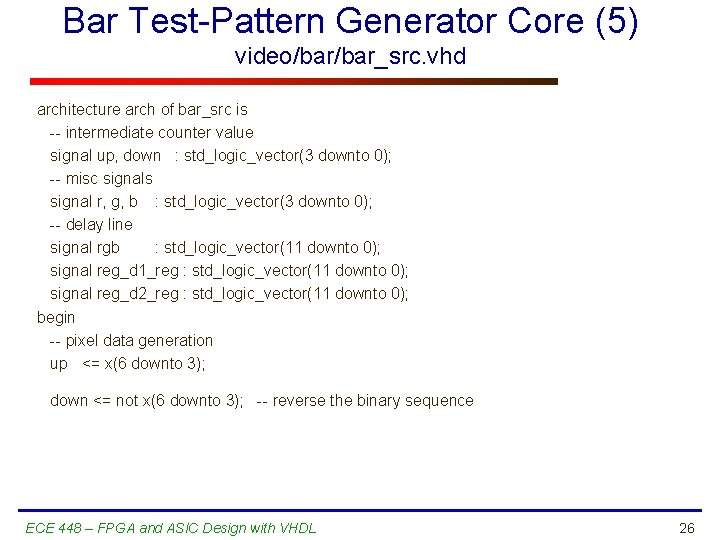

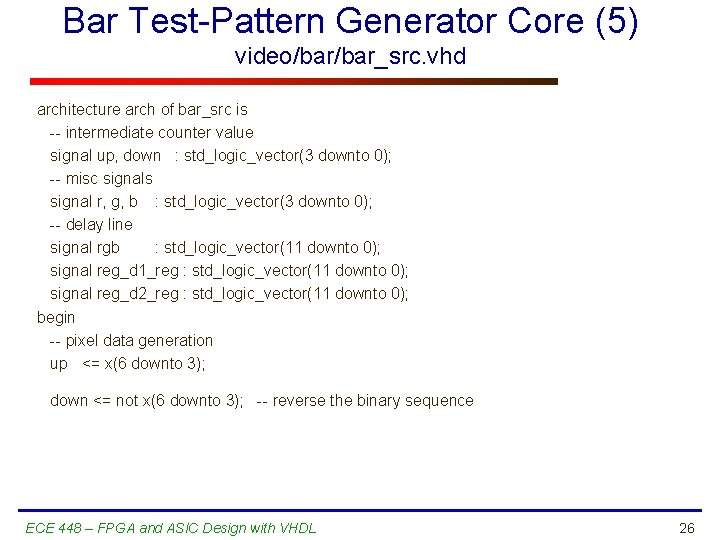

Bar Test-Pattern Generator Core (5) video/bar_src. vhd architecture arch of bar_src is -- intermediate counter value signal up, down : std_logic_vector(3 downto 0); -- misc signals signal r, g, b : std_logic_vector(3 downto 0); -- delay line signal rgb : std_logic_vector(11 downto 0); signal reg_d 1_reg : std_logic_vector(11 downto 0); signal reg_d 2_reg : std_logic_vector(11 downto 0); begin -- pixel data generation up <= x(6 downto 3); down <= not x(6 downto 3); -- reverse the binary sequence ECE 448 – FPGA and ASIC Design with VHDL 26

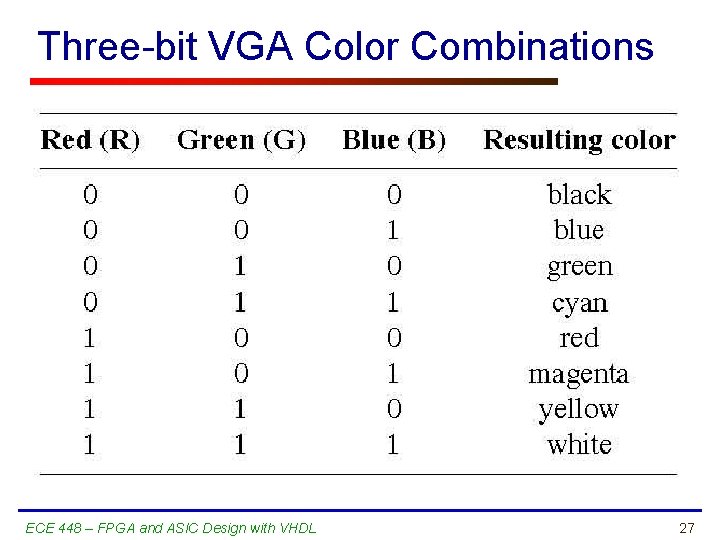

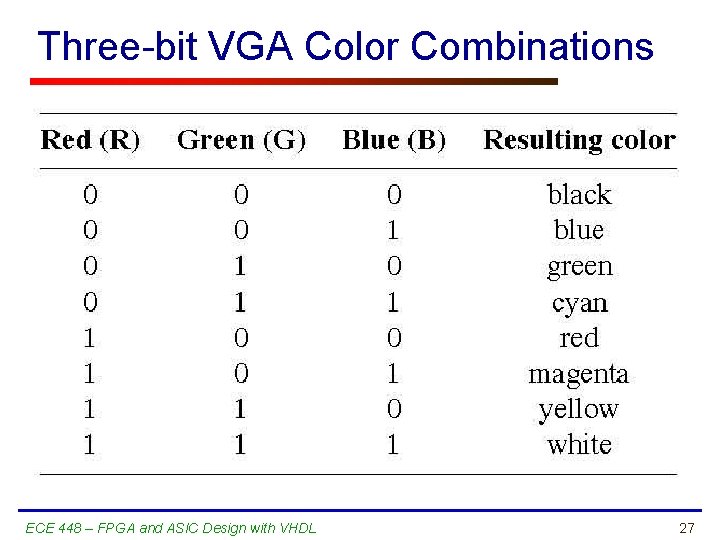

Three-bit VGA Color Combinations ECE 448 – FPGA and ASIC Design with VHDL 27

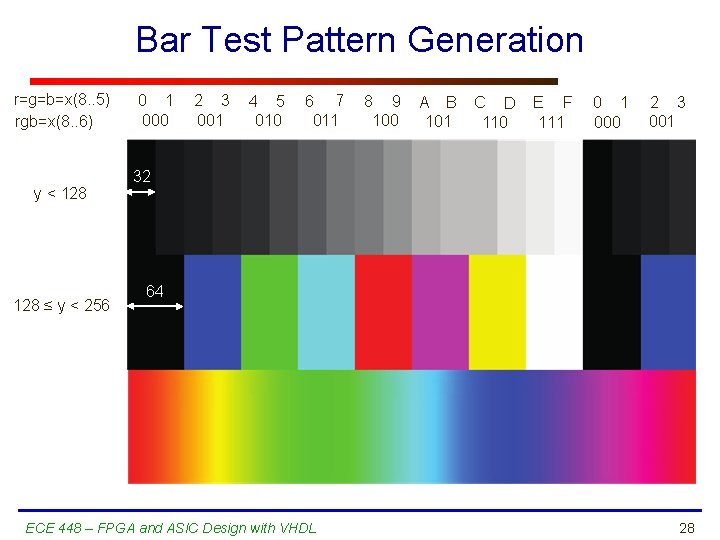

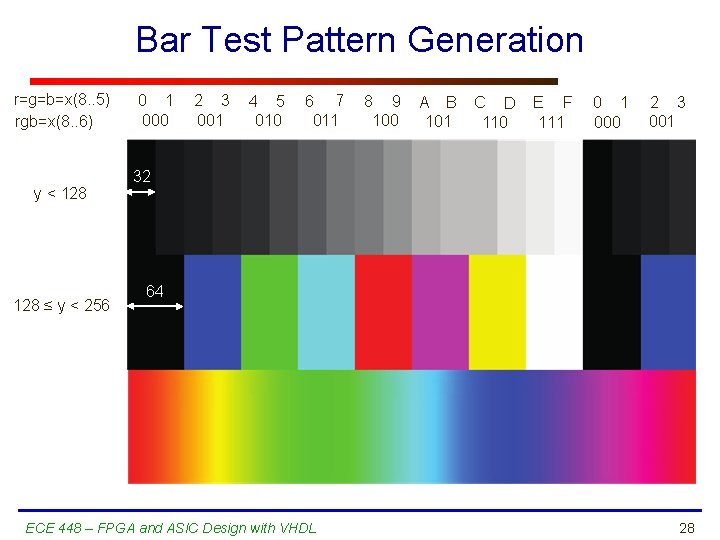

Bar Test Pattern Generation r=g=b=x(8. . 5) rgb=x(8. . 6) y < 128 ≤ y < 256 0 1 000 2 3 001 4 5 010 6 7 011 8 9 100 A B 101 C D 110 E F 111 0 1 000 2 3 001 32 64 ECE 448 – FPGA and ASIC Design with VHDL 28

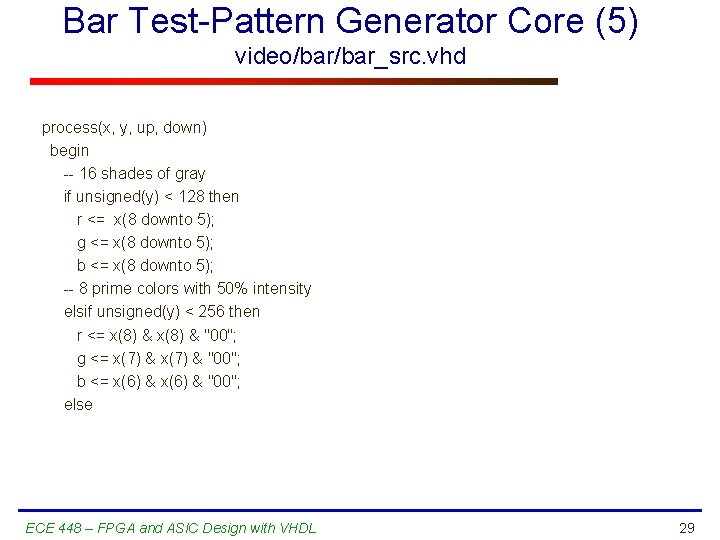

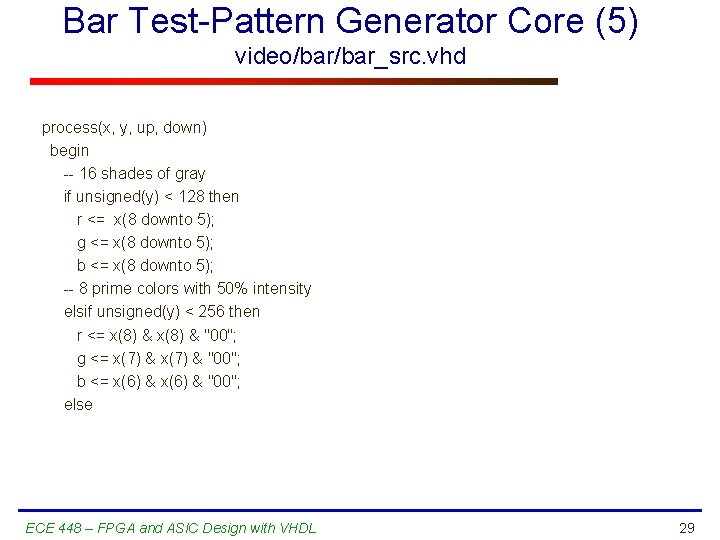

Bar Test-Pattern Generator Core (5) video/bar_src. vhd process(x, y, up, down) begin -- 16 shades of gray if unsigned(y) < 128 then r <= x(8 downto 5); g <= x(8 downto 5); b <= x(8 downto 5); -- 8 prime colors with 50% intensity elsif unsigned(y) < 256 then r <= x(8) & "00"; g <= x(7) & "00"; b <= x(6) & "00"; else ECE 448 – FPGA and ASIC Design with VHDL 29

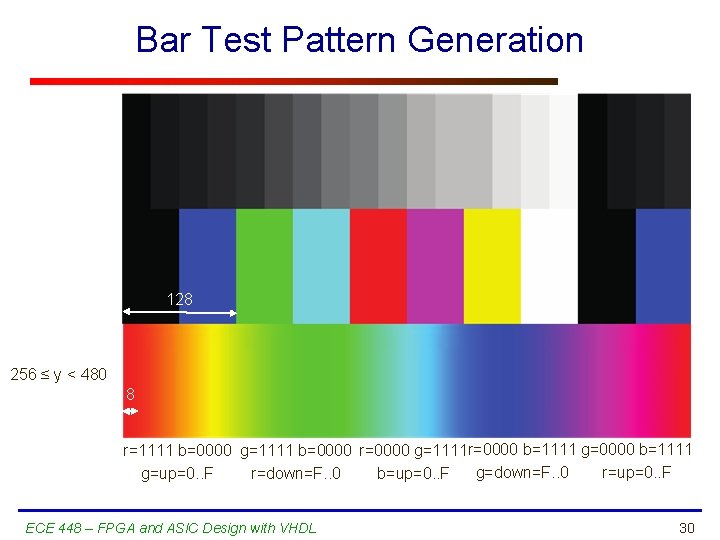

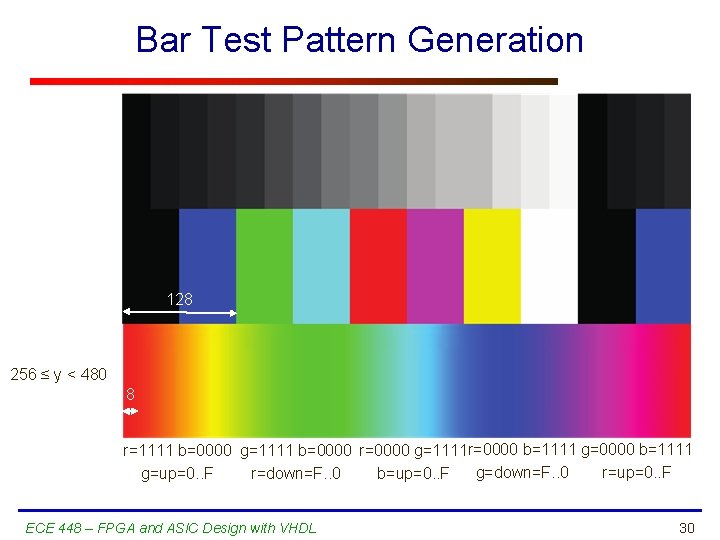

Bar Test Pattern Generation 128 256 ≤ y < 480 8 r=1111 b=0000 g=1111 b=0000 r=0000 g=1111 r=0000 b=1111 g=down=F. . 0 r=up=0. . F g=up=0. . F r=down=F. . 0 b=up=0. . F ECE 448 – FPGA and ASIC Design with VHDL 30

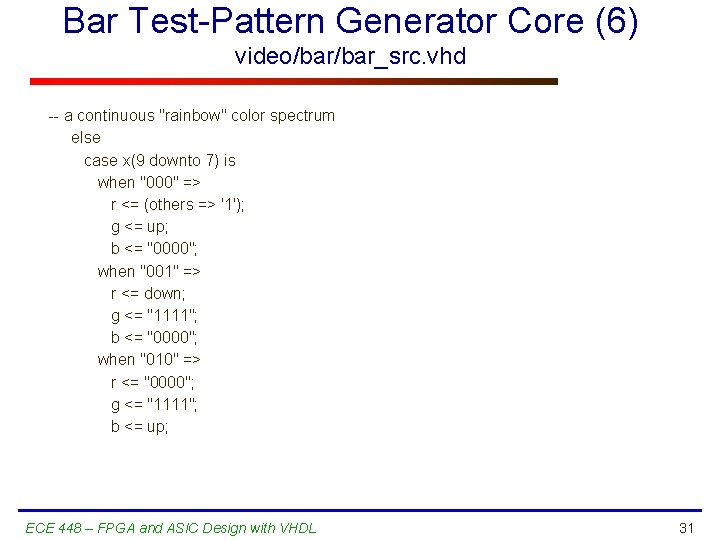

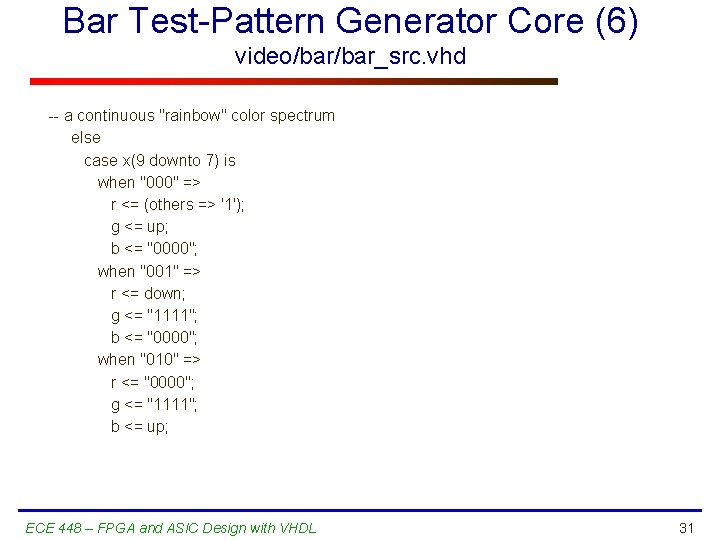

Bar Test-Pattern Generator Core (6) video/bar_src. vhd -- a continuous "rainbow" color spectrum else case x(9 downto 7) is when "000" => r <= (others => '1'); g <= up; b <= "0000"; when "001" => r <= down; g <= "1111"; b <= "0000"; when "010" => r <= "0000"; g <= "1111"; b <= up; ECE 448 – FPGA and ASIC Design with VHDL 31

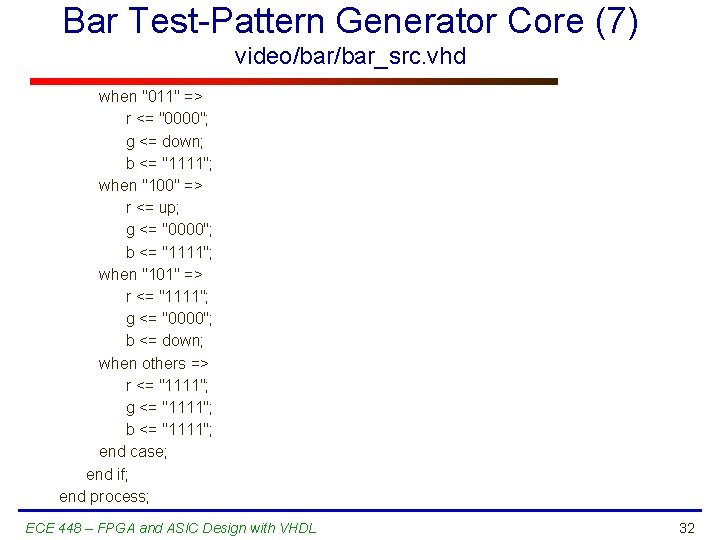

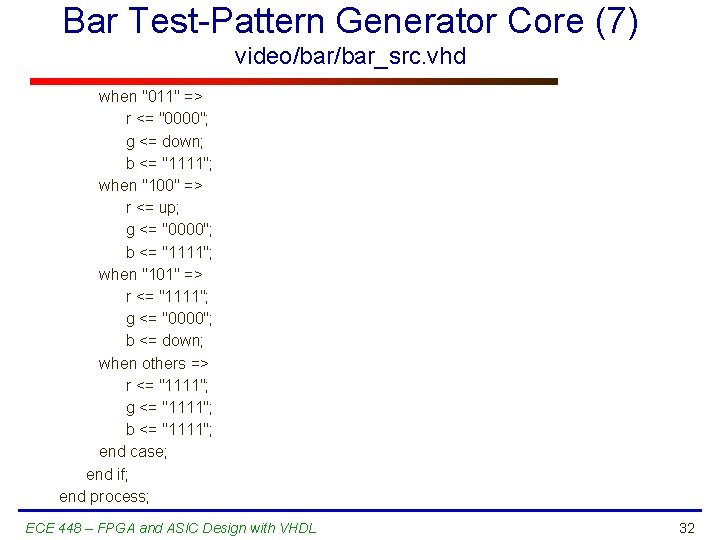

Bar Test-Pattern Generator Core (7) video/bar_src. vhd when "011" => r <= "0000"; g <= down; b <= "1111"; when "100" => r <= up; g <= "0000"; b <= "1111"; when "101" => r <= "1111"; g <= "0000"; b <= down; when others => r <= "1111"; g <= "1111"; b <= "1111"; end case; end if; end process; ECE 448 – FPGA and ASIC Design with VHDL 32

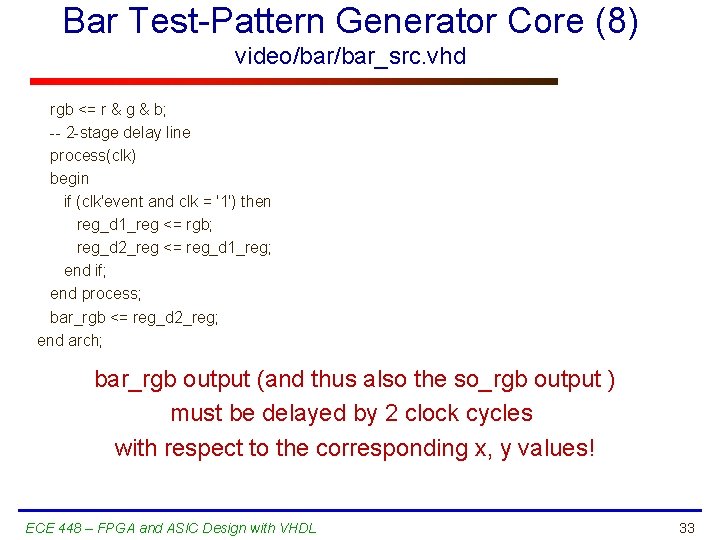

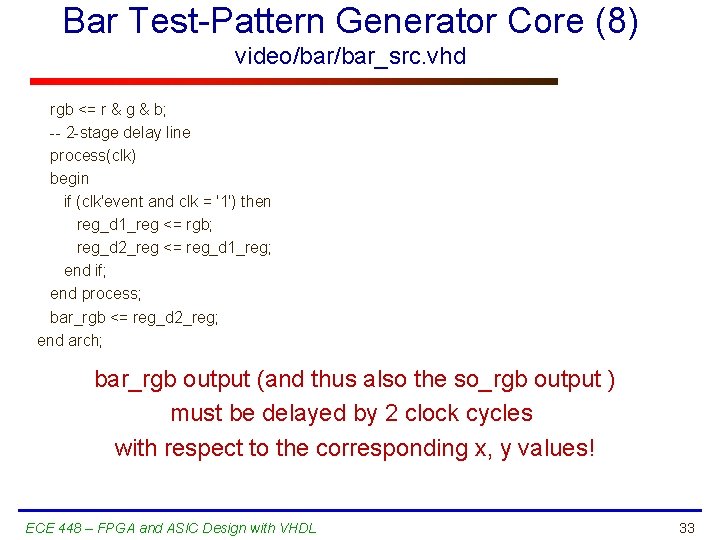

Bar Test-Pattern Generator Core (8) video/bar_src. vhd rgb <= r & g & b; -- 2 -stage delay line process(clk) begin if (clk'event and clk = '1') then reg_d 1_reg <= rgb; reg_d 2_reg <= reg_d 1_reg; end if; end process; bar_rgb <= reg_d 2_reg; end arch; bar_rgb output (and thus also the so_rgb output ) must be delayed by 2 clock cycles with respect to the corresponding x, y values! ECE 448 – FPGA and ASIC Design with VHDL 33

Interface of a video pixel generation core clk reset x y si_rgb wr_data addr 11 2 clock cycles 11 12 12 so_rgb 32 14 write cs ECE 448 – FPGA and ASIC Design with VHDL 34

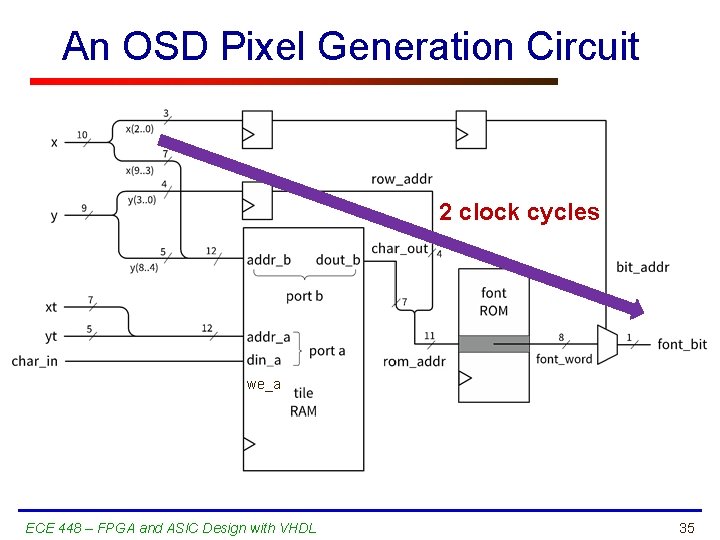

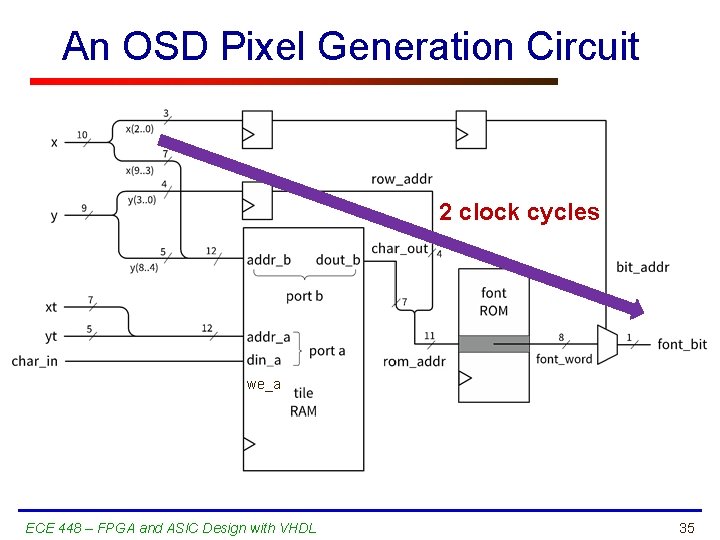

An OSD Pixel Generation Circuit 2 clock cycles we_a ECE 448 – FPGA and ASIC Design with VHDL 35

Color-to-Grayscale Conversion Core ECE 448 – FPGA and ASIC Design with VHDL 36

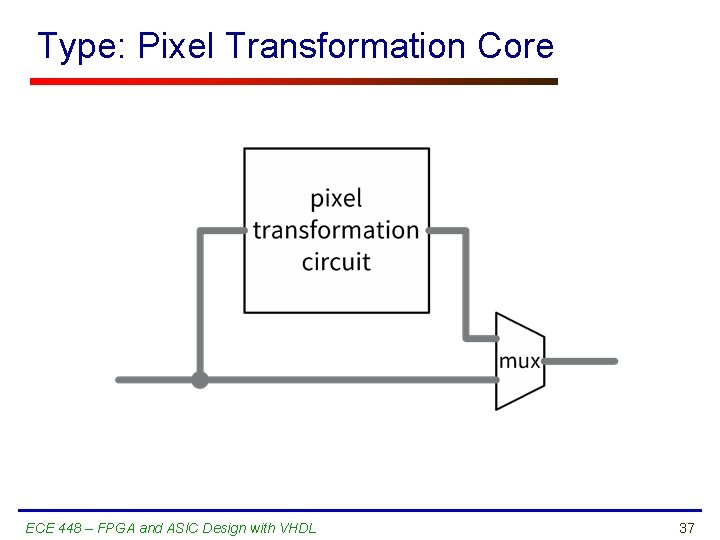

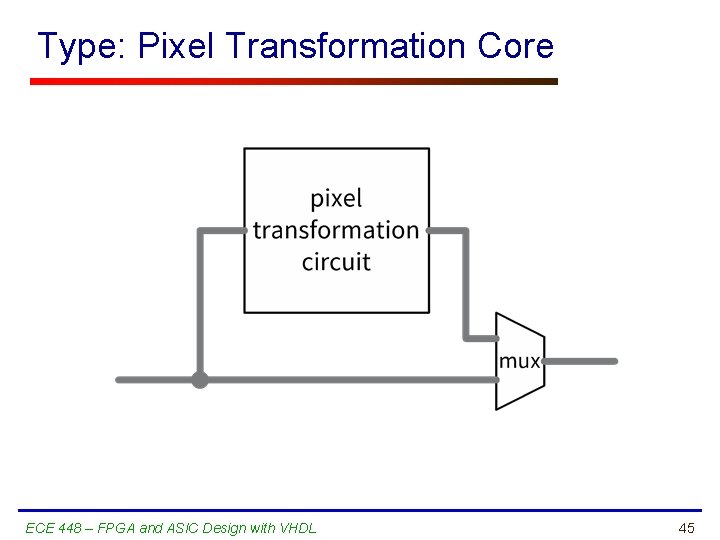

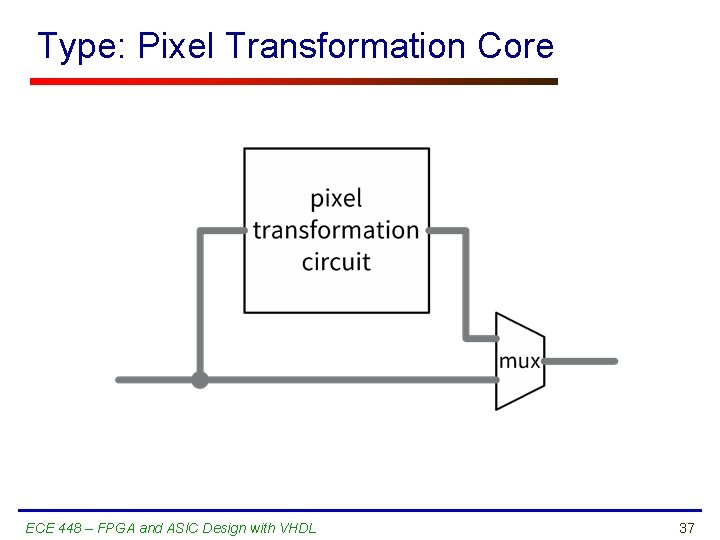

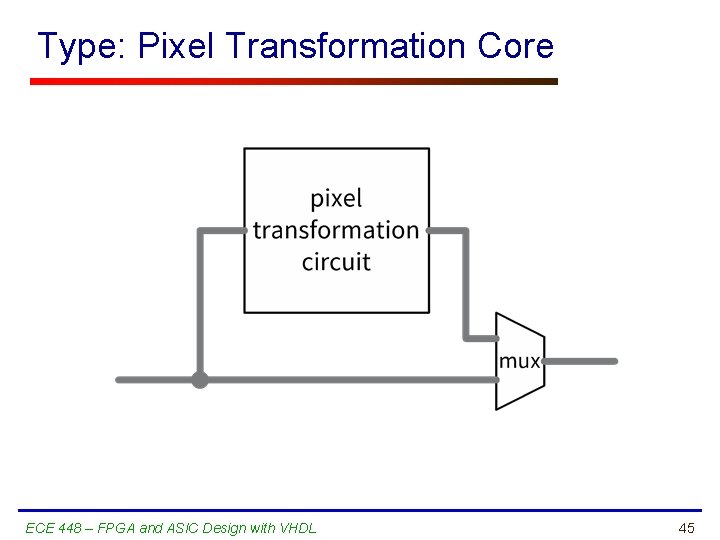

Type: Pixel Transformation Core ECE 448 – FPGA and ASIC Design with VHDL 37

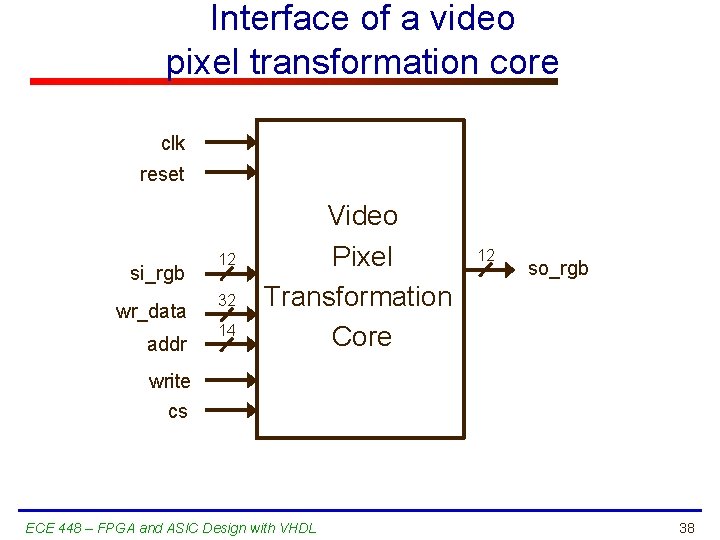

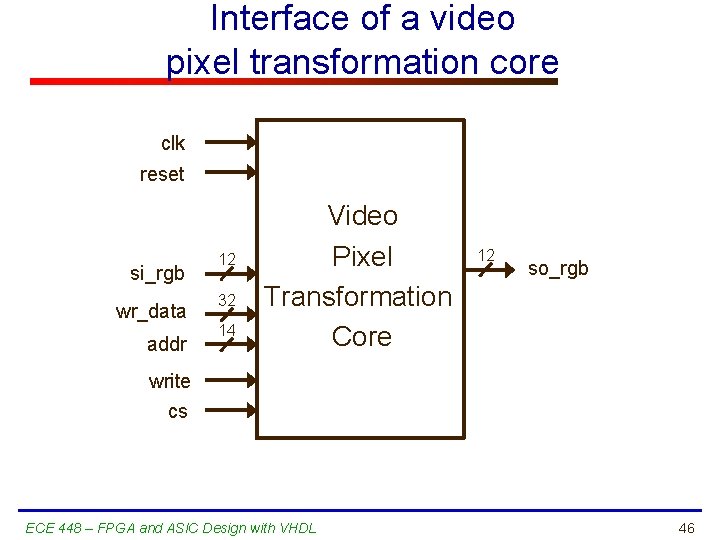

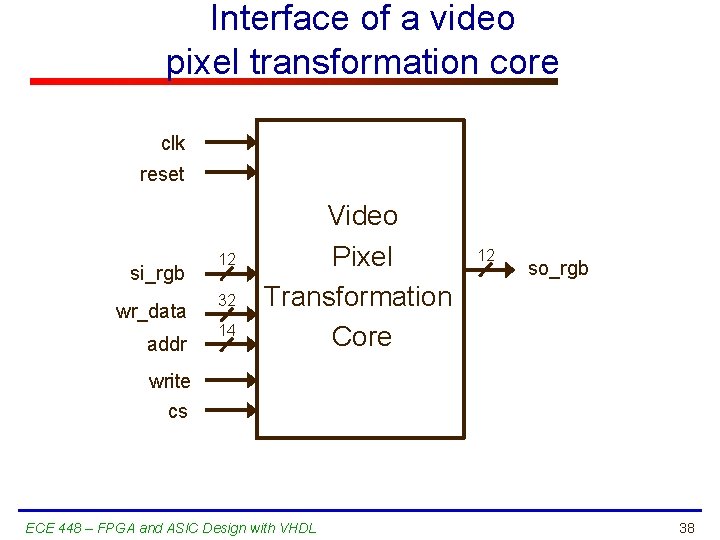

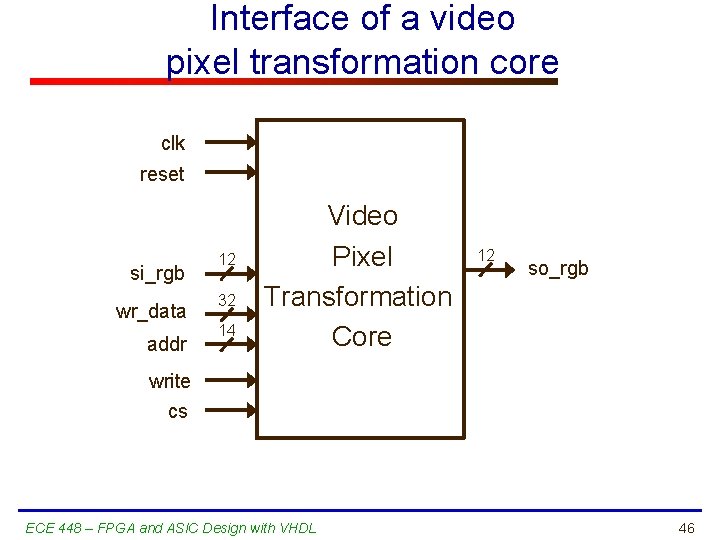

Interface of a video pixel transformation core clk reset si_rgb wr_data addr 12 32 14 Video Pixel Transformation Core 12 so_rgb write cs ECE 448 – FPGA and ASIC Design with VHDL 38

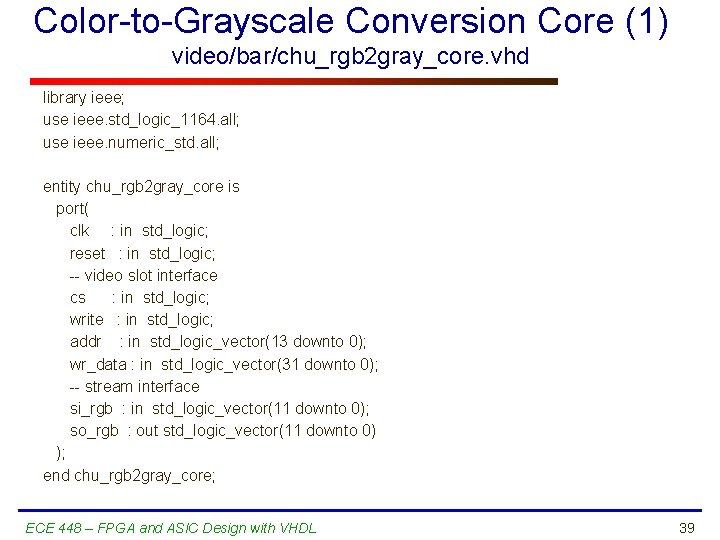

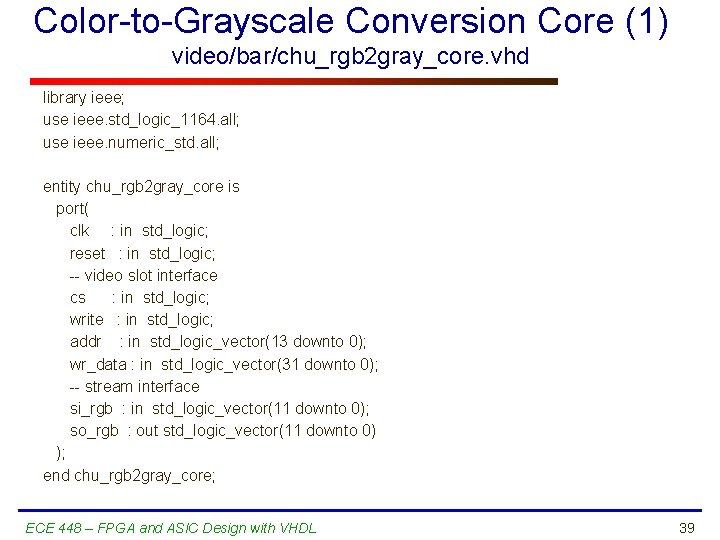

Color-to-Grayscale Conversion Core (1) video/bar/chu_rgb 2 gray_core. vhd library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity chu_rgb 2 gray_core is port( clk : in std_logic; reset : in std_logic; -- video slot interface cs : in std_logic; write : in std_logic; addr : in std_logic_vector(13 downto 0); wr_data : in std_logic_vector(31 downto 0); -- stream interface si_rgb : in std_logic_vector(11 downto 0); so_rgb : out std_logic_vector(11 downto 0) ); end chu_rgb 2 gray_core; ECE 448 – FPGA and ASIC Design with VHDL 39

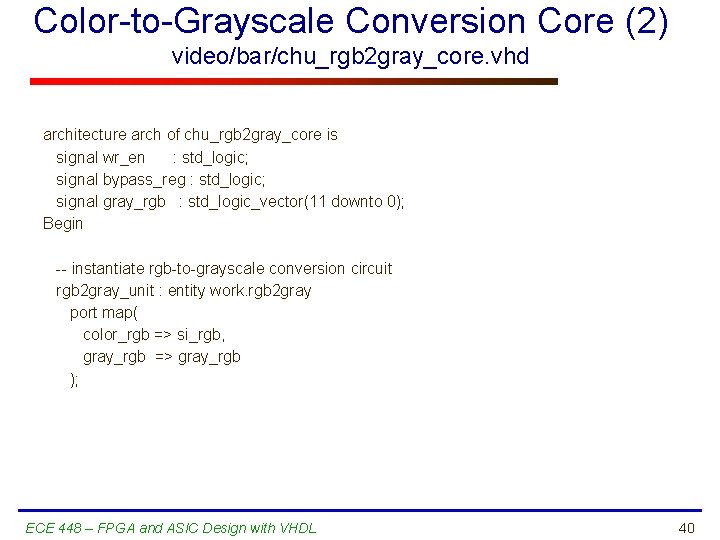

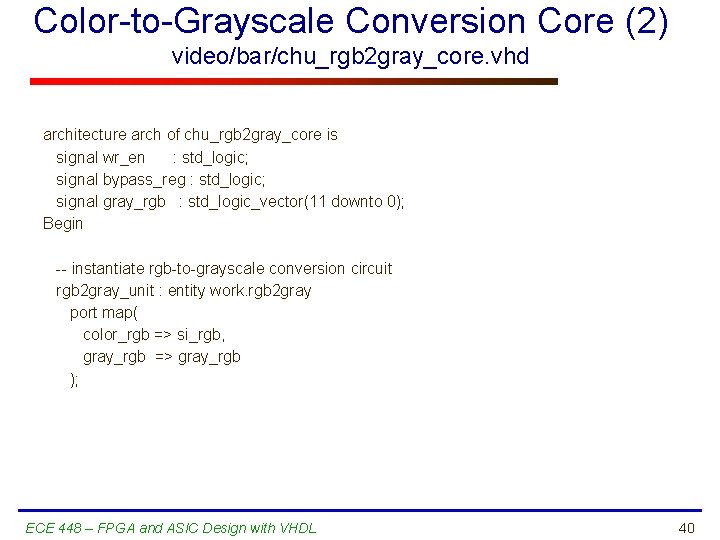

Color-to-Grayscale Conversion Core (2) video/bar/chu_rgb 2 gray_core. vhd architecture arch of chu_rgb 2 gray_core is signal wr_en : std_logic; signal bypass_reg : std_logic; signal gray_rgb : std_logic_vector(11 downto 0); Begin -- instantiate rgb-to-grayscale conversion circuit rgb 2 gray_unit : entity work. rgb 2 gray port map( color_rgb => si_rgb, gray_rgb => gray_rgb ); ECE 448 – FPGA and ASIC Design with VHDL 40

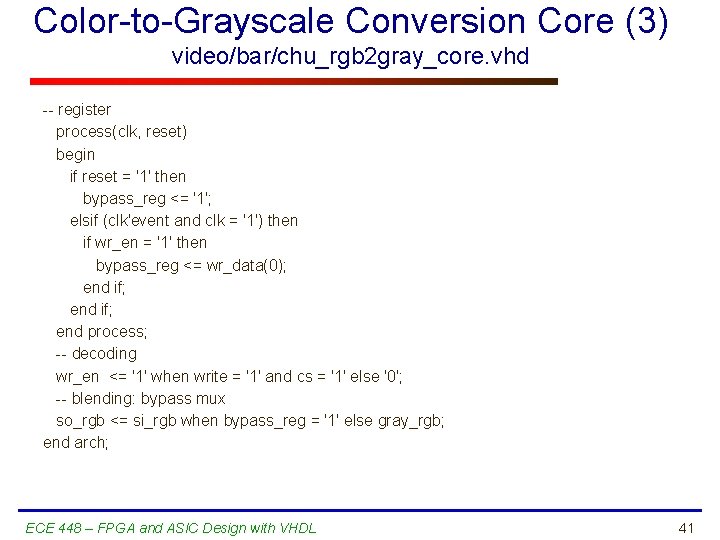

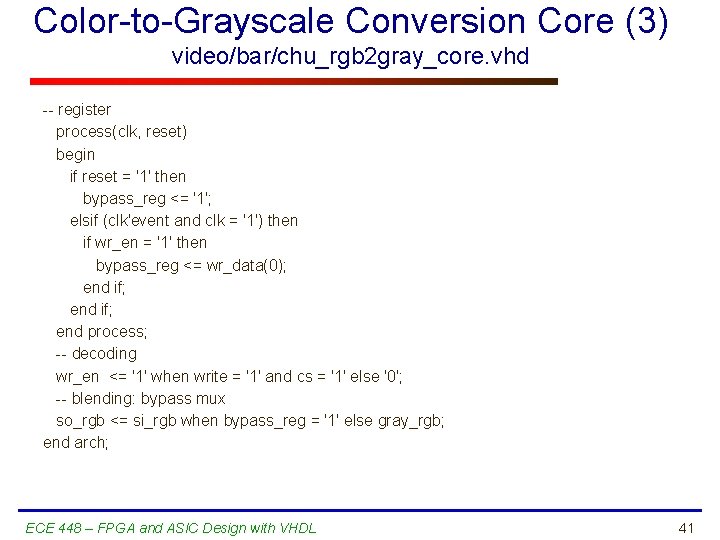

Color-to-Grayscale Conversion Core (3) video/bar/chu_rgb 2 gray_core. vhd -- register process(clk, reset) begin if reset = '1' then bypass_reg <= '1'; elsif (clk'event and clk = '1') then if wr_en = '1' then bypass_reg <= wr_data(0); end if; end process; -- decoding wr_en <= '1' when write = '1' and cs = '1' else '0'; -- blending: bypass mux so_rgb <= si_rgb when bypass_reg = '1' else gray_rgb; end arch; ECE 448 – FPGA and ASIC Design with VHDL 41

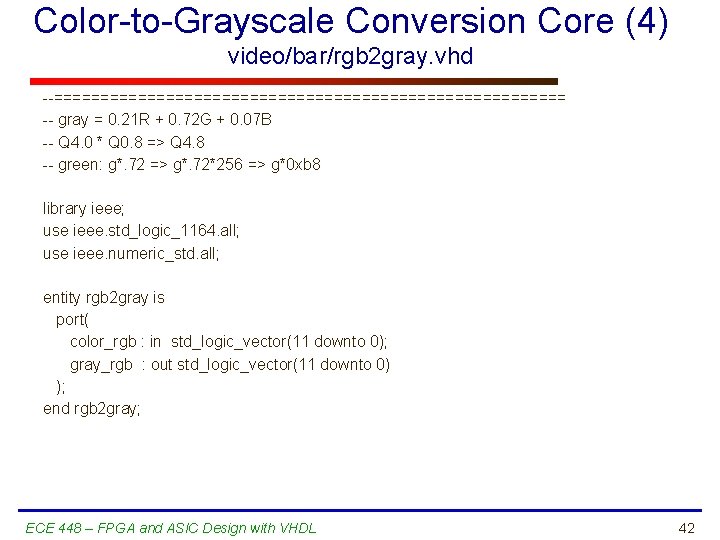

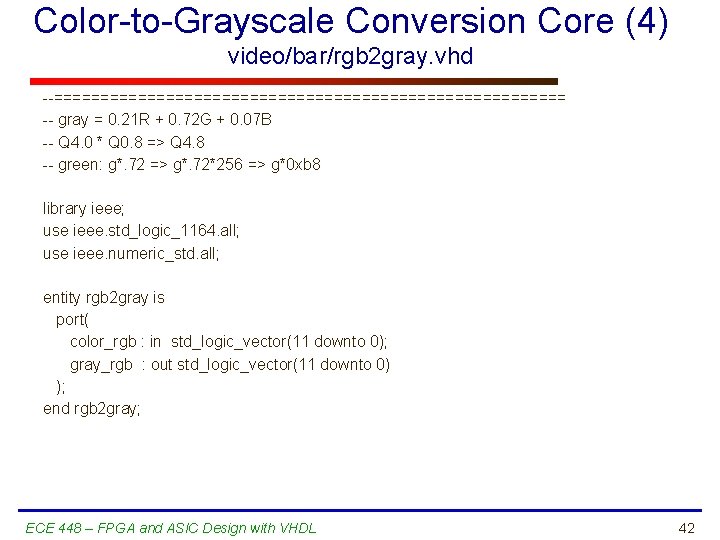

Color-to-Grayscale Conversion Core (4) video/bar/rgb 2 gray. vhd --============================ -- gray = 0. 21 R + 0. 72 G + 0. 07 B -- Q 4. 0 * Q 0. 8 => Q 4. 8 -- green: g*. 72 => g*. 72*256 => g*0 xb 8 library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity rgb 2 gray is port( color_rgb : in std_logic_vector(11 downto 0); gray_rgb : out std_logic_vector(11 downto 0) ); end rgb 2 gray; ECE 448 – FPGA and ASIC Design with VHDL 42

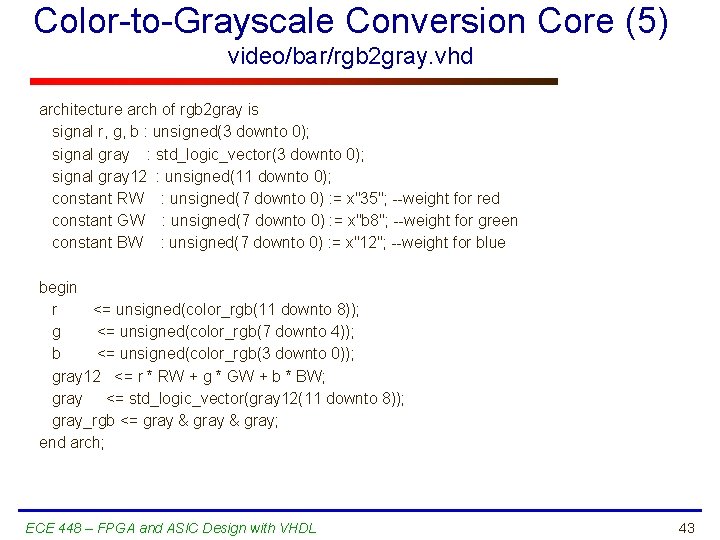

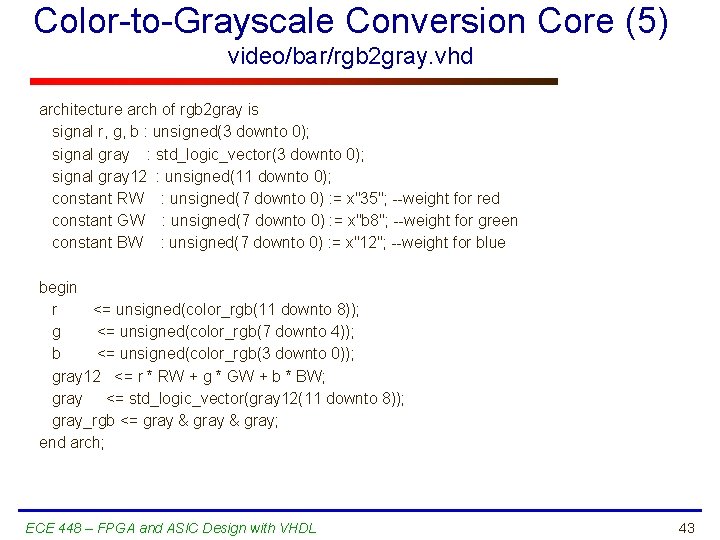

Color-to-Grayscale Conversion Core (5) video/bar/rgb 2 gray. vhd architecture arch of rgb 2 gray is signal r, g, b : unsigned(3 downto 0); signal gray : std_logic_vector(3 downto 0); signal gray 12 : unsigned(11 downto 0); constant RW : unsigned(7 downto 0) : = x"35"; --weight for red constant GW : unsigned(7 downto 0) : = x"b 8"; --weight for green constant BW : unsigned(7 downto 0) : = x"12"; --weight for blue begin r <= unsigned(color_rgb(11 downto 8)); g <= unsigned(color_rgb(7 downto 4)); b <= unsigned(color_rgb(3 downto 0)); gray 12 <= r * RW + g * GW + b * BW; gray <= std_logic_vector(gray 12(11 downto 8)); gray_rgb <= gray & gray; end arch; ECE 448 – FPGA and ASIC Design with VHDL 43

Dummy Core ECE 448 – FPGA and ASIC Design with VHDL 44

Type: Pixel Transformation Core ECE 448 – FPGA and ASIC Design with VHDL 45

Interface of a video pixel transformation core clk reset si_rgb wr_data addr 12 32 14 Video Pixel Transformation Core 12 so_rgb write cs ECE 448 – FPGA and ASIC Design with VHDL 46

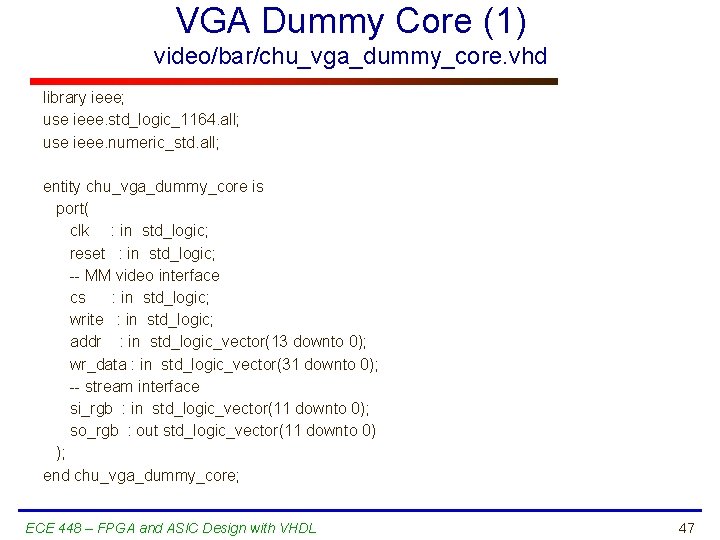

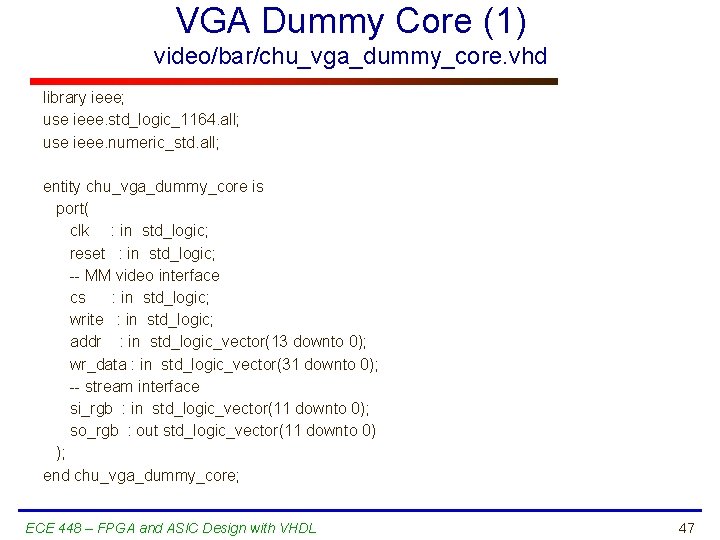

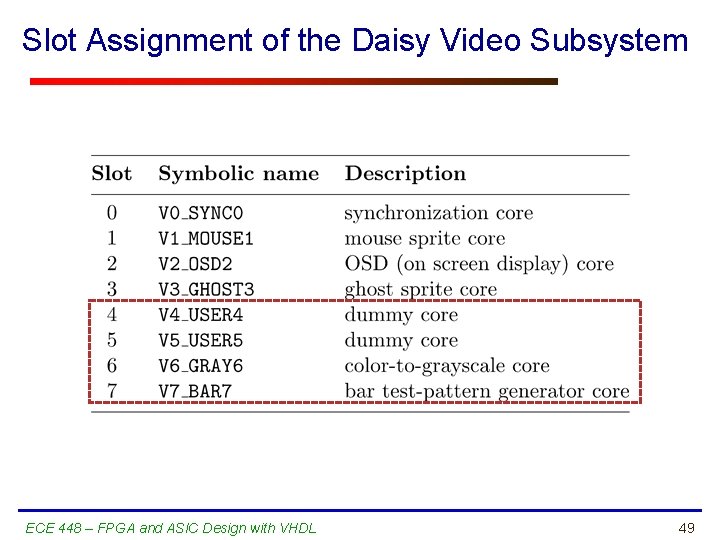

VGA Dummy Core (1) video/bar/chu_vga_dummy_core. vhd library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity chu_vga_dummy_core is port( clk : in std_logic; reset : in std_logic; -- MM video interface cs : in std_logic; write : in std_logic; addr : in std_logic_vector(13 downto 0); wr_data : in std_logic_vector(31 downto 0); -- stream interface si_rgb : in std_logic_vector(11 downto 0); so_rgb : out std_logic_vector(11 downto 0) ); end chu_vga_dummy_core; ECE 448 – FPGA and ASIC Design with VHDL 47

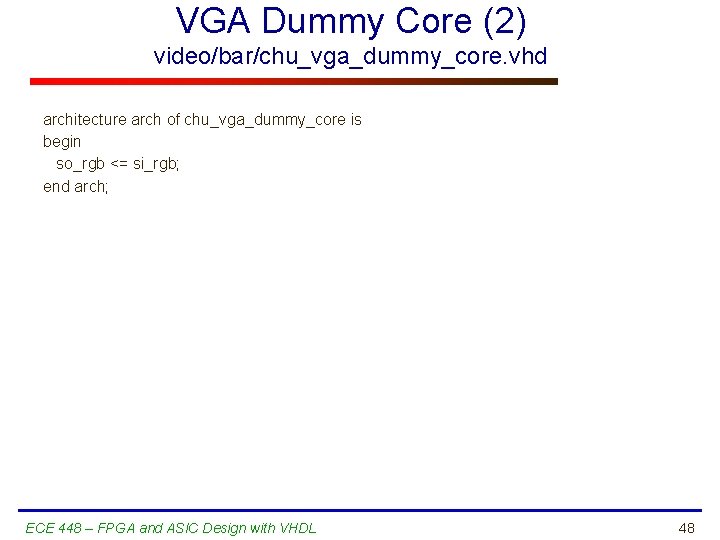

VGA Dummy Core (2) video/bar/chu_vga_dummy_core. vhd architecture arch of chu_vga_dummy_core is begin so_rgb <= si_rgb; end arch; ECE 448 – FPGA and ASIC Design with VHDL 48

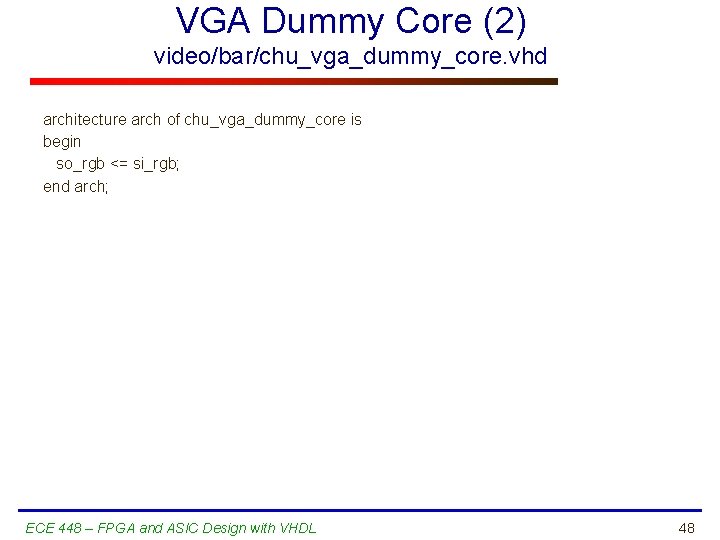

Slot Assignment of the Daisy Video Subsystem ECE 448 – FPGA and ASIC Design with VHDL 49

Instantiation of Video Cores ECE 448 – FPGA and ASIC Design with VHDL 50

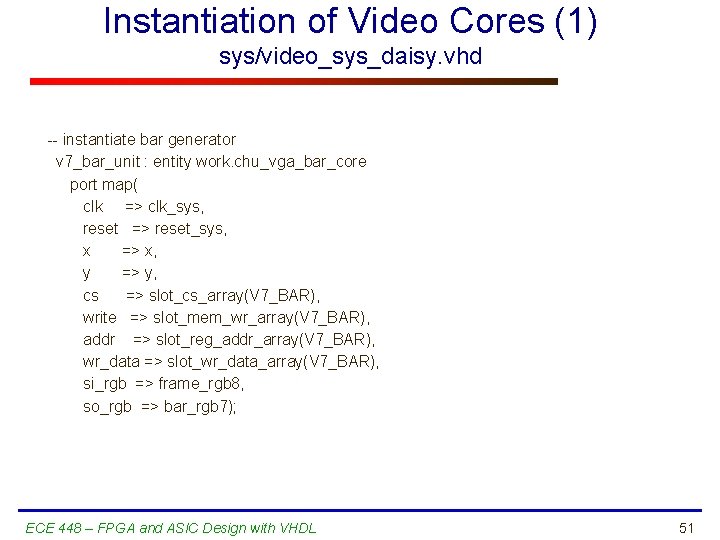

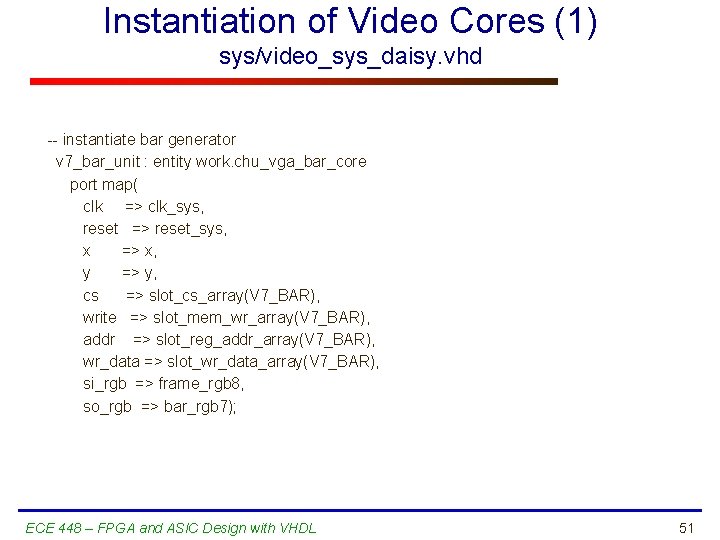

Instantiation of Video Cores (1) sys/video_sys_daisy. vhd -- instantiate bar generator v 7_bar_unit : entity work. chu_vga_bar_core port map( clk => clk_sys, reset => reset_sys, x => x, y => y, cs => slot_cs_array(V 7_BAR), write => slot_mem_wr_array(V 7_BAR), addr => slot_reg_addr_array(V 7_BAR), wr_data => slot_wr_data_array(V 7_BAR), si_rgb => frame_rgb 8, so_rgb => bar_rgb 7); ECE 448 – FPGA and ASIC Design with VHDL 51

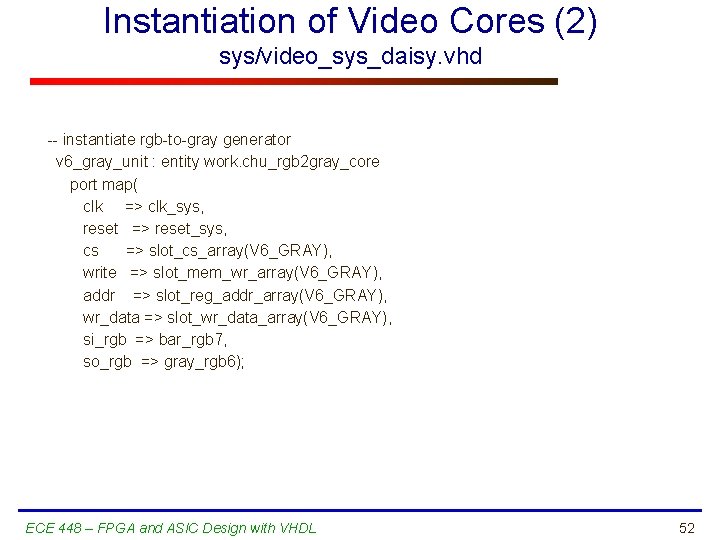

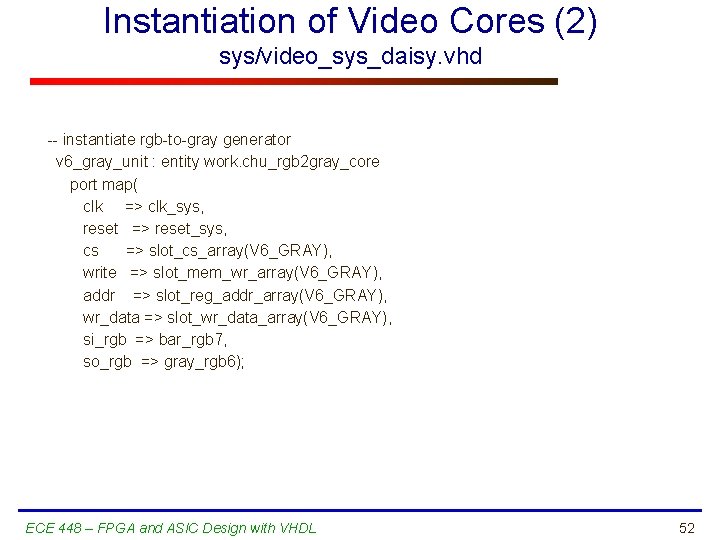

Instantiation of Video Cores (2) sys/video_sys_daisy. vhd -- instantiate rgb-to-gray generator v 6_gray_unit : entity work. chu_rgb 2 gray_core port map( clk => clk_sys, reset => reset_sys, cs => slot_cs_array(V 6_GRAY), write => slot_mem_wr_array(V 6_GRAY), addr => slot_reg_addr_array(V 6_GRAY), wr_data => slot_wr_data_array(V 6_GRAY), si_rgb => bar_rgb 7, so_rgb => gray_rgb 6); ECE 448 – FPGA and ASIC Design with VHDL 52

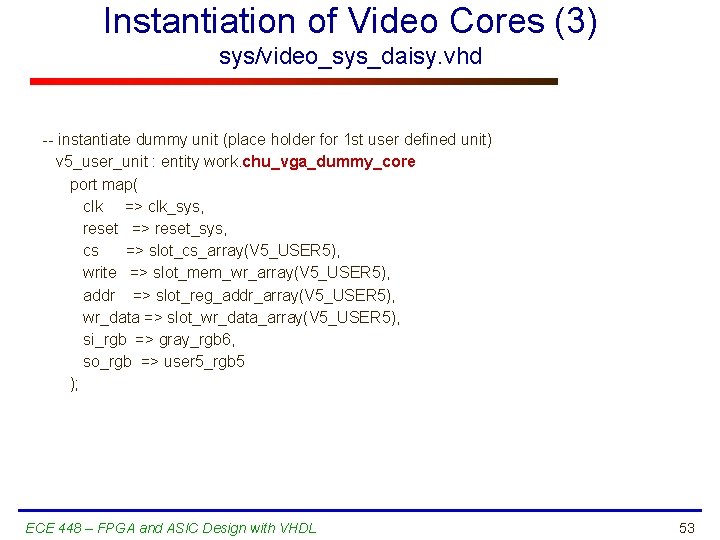

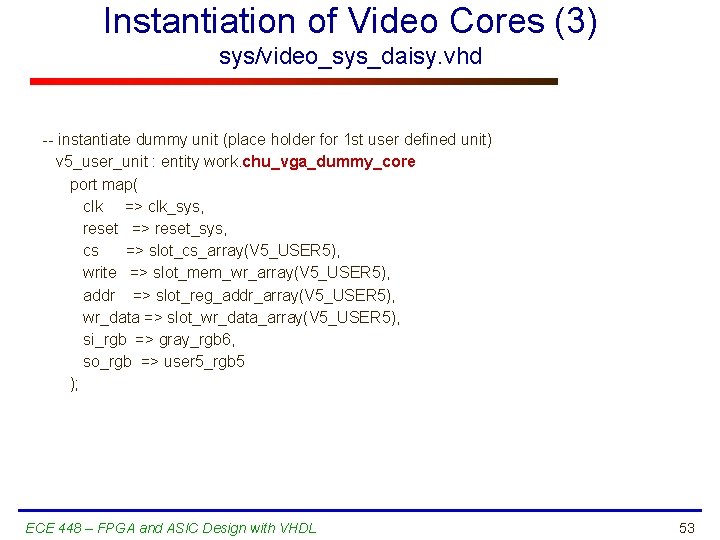

Instantiation of Video Cores (3) sys/video_sys_daisy. vhd -- instantiate dummy unit (place holder for 1 st user defined unit) v 5_user_unit : entity work. chu_vga_dummy_core port map( clk => clk_sys, reset => reset_sys, cs => slot_cs_array(V 5_USER 5), write => slot_mem_wr_array(V 5_USER 5), addr => slot_reg_addr_array(V 5_USER 5), wr_data => slot_wr_data_array(V 5_USER 5), si_rgb => gray_rgb 6, so_rgb => user 5_rgb 5 ); ECE 448 – FPGA and ASIC Design with VHDL 53

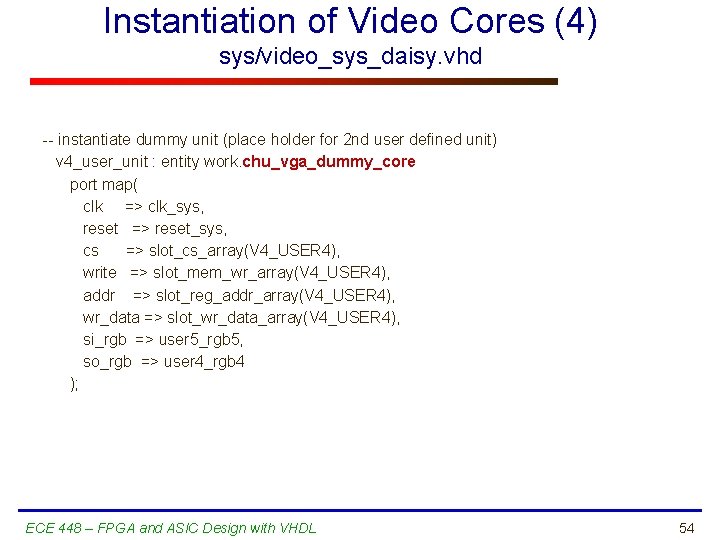

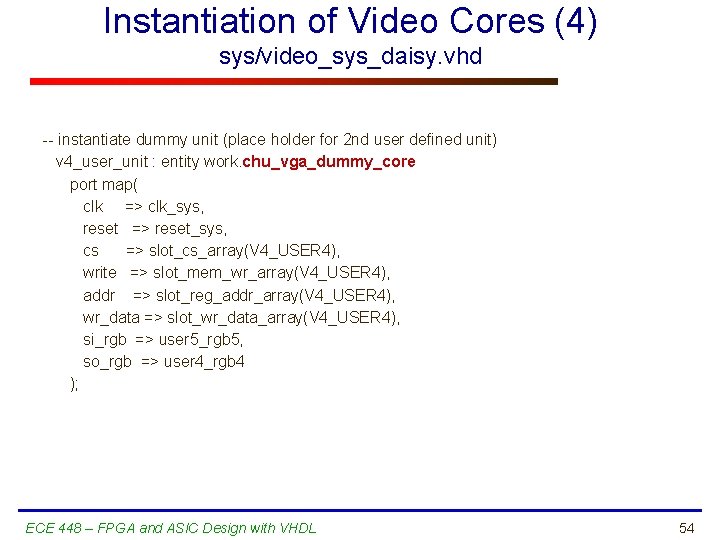

Instantiation of Video Cores (4) sys/video_sys_daisy. vhd -- instantiate dummy unit (place holder for 2 nd user defined unit) v 4_user_unit : entity work. chu_vga_dummy_core port map( clk => clk_sys, reset => reset_sys, cs => slot_cs_array(V 4_USER 4), write => slot_mem_wr_array(V 4_USER 4), addr => slot_reg_addr_array(V 4_USER 4), wr_data => slot_wr_data_array(V 4_USER 4), si_rgb => user 5_rgb 5, so_rgb => user 4_rgb 4 ); ECE 448 – FPGA and ASIC Design with VHDL 54

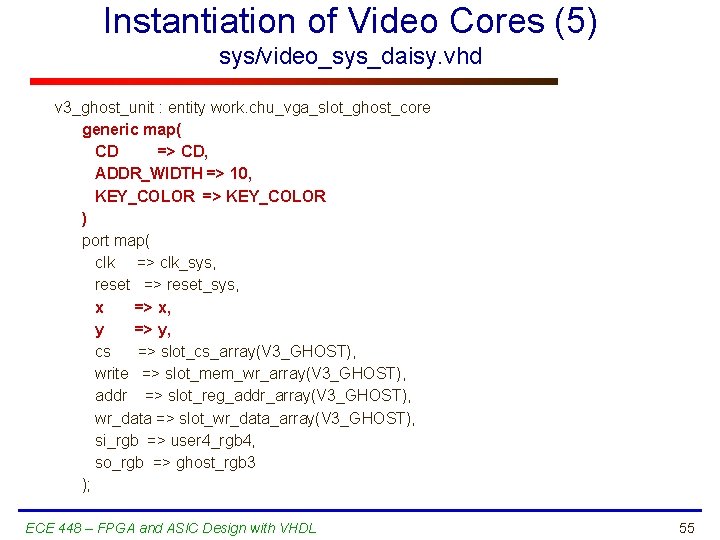

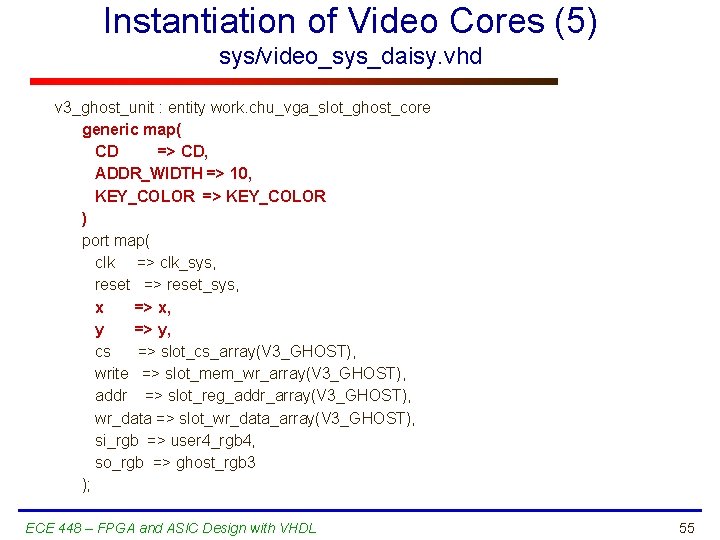

Instantiation of Video Cores (5) sys/video_sys_daisy. vhd v 3_ghost_unit : entity work. chu_vga_slot_ghost_core generic map( CD => CD, ADDR_WIDTH => 10, KEY_COLOR => KEY_COLOR ) port map( clk => clk_sys, reset => reset_sys, x => x, y => y, cs => slot_cs_array(V 3_GHOST), write => slot_mem_wr_array(V 3_GHOST), addr => slot_reg_addr_array(V 3_GHOST), wr_data => slot_wr_data_array(V 3_GHOST), si_rgb => user 4_rgb 4, so_rgb => ghost_rgb 3 ); ECE 448 – FPGA and ASIC Design with VHDL 55

General-Purpose Video Core Driver ECE 448 – FPGA and ASIC Design with VHDL 56

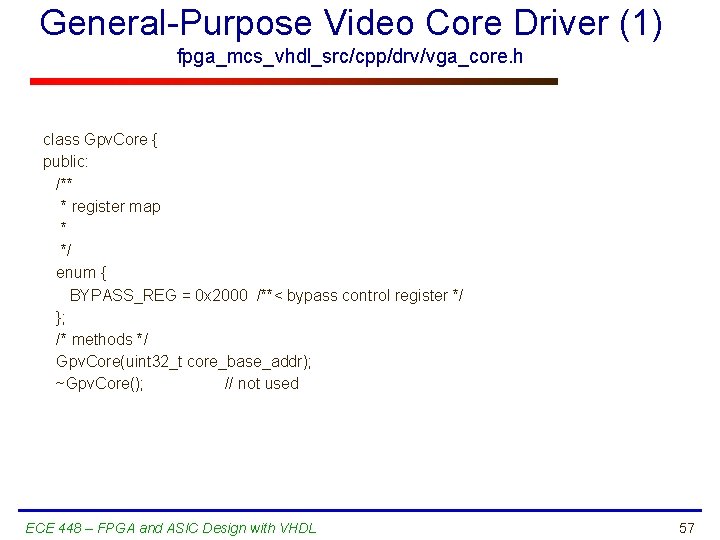

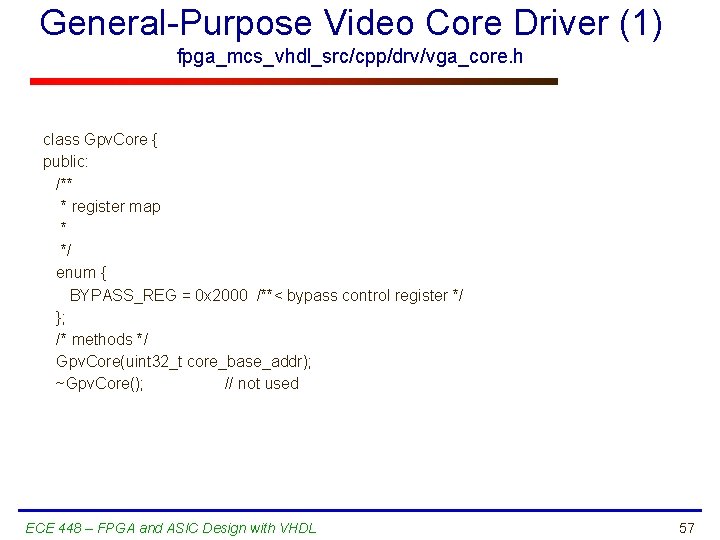

General-Purpose Video Core Driver (1) fpga_mcs_vhdl_src/cpp/drv/vga_core. h class Gpv. Core { public: /** * register map * */ enum { BYPASS_REG = 0 x 2000 /**< bypass control register */ }; /* methods */ Gpv. Core(uint 32_t core_base_addr); ~Gpv. Core(); // not used ECE 448 – FPGA and ASIC Design with VHDL 57

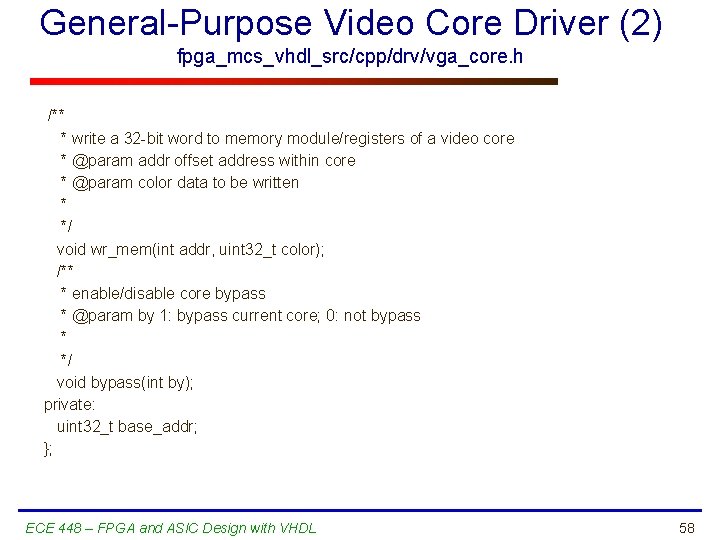

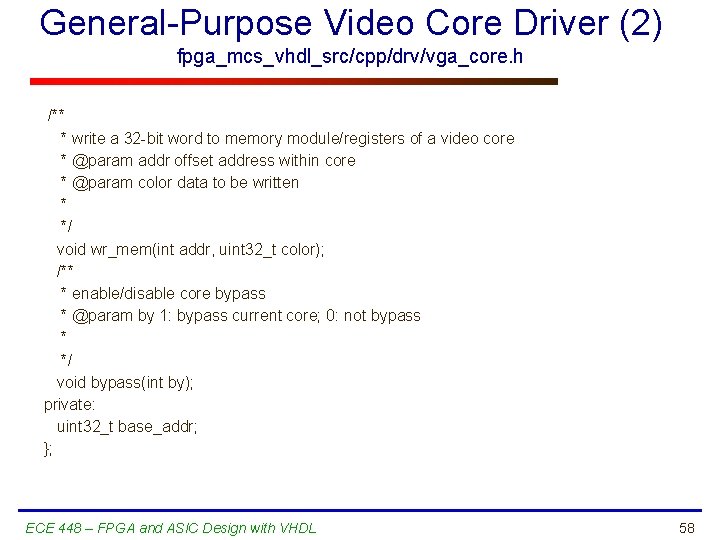

General-Purpose Video Core Driver (2) fpga_mcs_vhdl_src/cpp/drv/vga_core. h /** * write a 32 -bit word to memory module/registers of a video core * @param addr offset address within core * @param color data to be written * */ void wr_mem(int addr, uint 32_t color); /** * enable/disable core bypass * @param by 1: bypass current core; 0: not bypass * */ void bypass(int by); private: uint 32_t base_addr; }; ECE 448 – FPGA and ASIC Design with VHDL 58

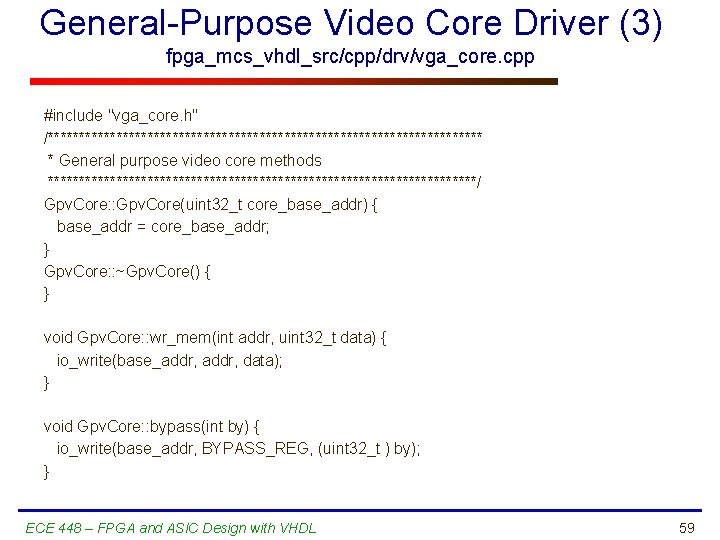

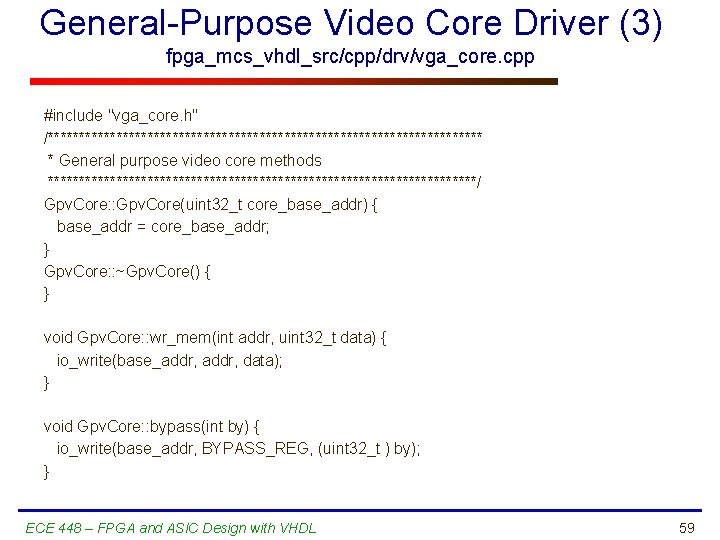

General-Purpose Video Core Driver (3) fpga_mcs_vhdl_src/cpp/drv/vga_core. cpp #include "vga_core. h" /*********************************** * General purpose video core methods ***********************************/ Gpv. Core: : Gpv. Core(uint 32_t core_base_addr) { base_addr = core_base_addr; } Gpv. Core: : ~Gpv. Core() { } void Gpv. Core: : wr_mem(int addr, uint 32_t data) { io_write(base_addr, data); } void Gpv. Core: : bypass(int by) { io_write(base_addr, BYPASS_REG, (uint 32_t ) by); } ECE 448 – FPGA and ASIC Design with VHDL 59

FPro Video Subsystem 22 -bit word space, 24 -bit byte space 11 aaaa aaaa 1 Frame Buffer Core, with 220 -word address space 10 xxxv vvaa aaaa 8 Video Cores, each with 214 -word address space vvv : slot number aa aaaa : 14 -bit address within a slot ECE 448 – FPGA and ASIC Design with VHDL 60

Calling Driver Functions in a Test Application ECE 448 – FPGA and ASIC Design with VHDL 61

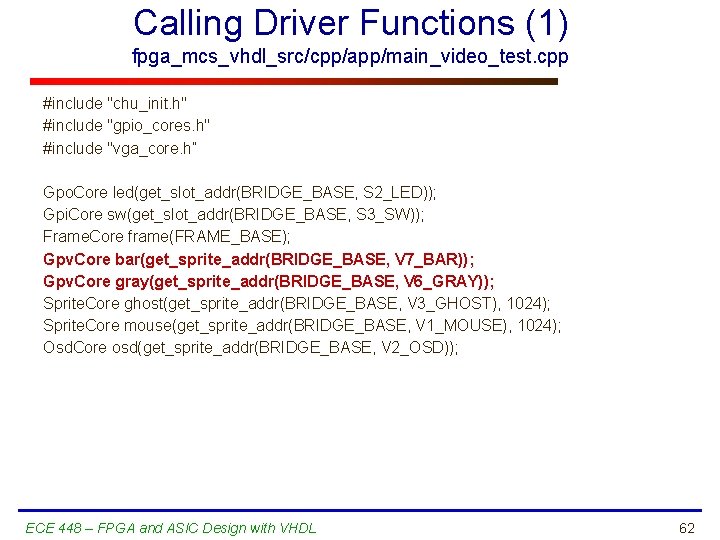

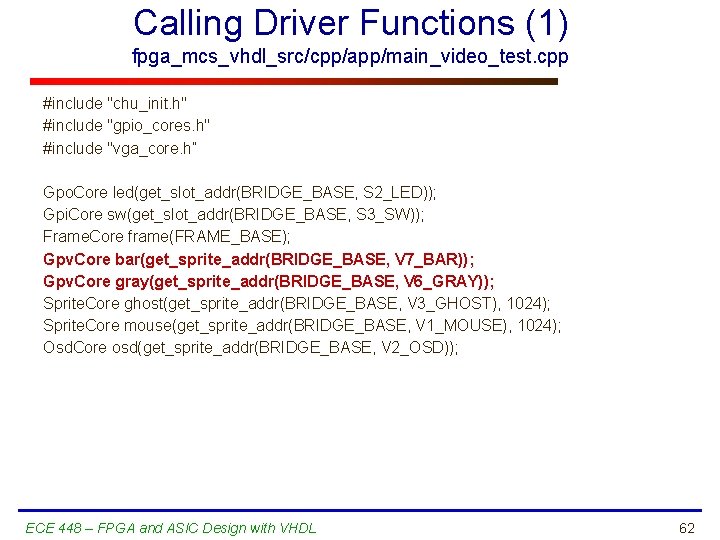

Calling Driver Functions (1) fpga_mcs_vhdl_src/cpp/app/main_video_test. cpp #include "chu_init. h" #include "gpio_cores. h" #include "vga_core. h” Gpo. Core led(get_slot_addr(BRIDGE_BASE, S 2_LED)); Gpi. Core sw(get_slot_addr(BRIDGE_BASE, S 3_SW)); Frame. Core frame(FRAME_BASE); Gpv. Core bar(get_sprite_addr(BRIDGE_BASE, V 7_BAR)); Gpv. Core gray(get_sprite_addr(BRIDGE_BASE, V 6_GRAY)); Sprite. Core ghost(get_sprite_addr(BRIDGE_BASE, V 3_GHOST), 1024); Sprite. Core mouse(get_sprite_addr(BRIDGE_BASE, V 1_MOUSE), 1024); Osd. Core osd(get_sprite_addr(BRIDGE_BASE, V 2_OSD)); ECE 448 – FPGA and ASIC Design with VHDL 62

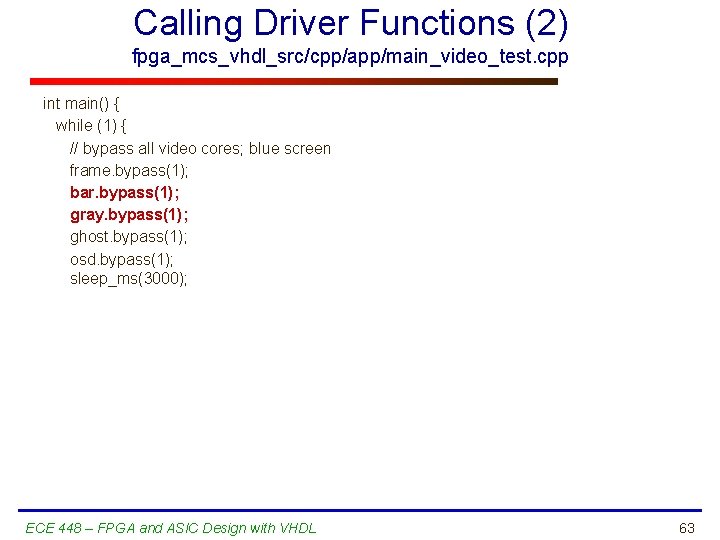

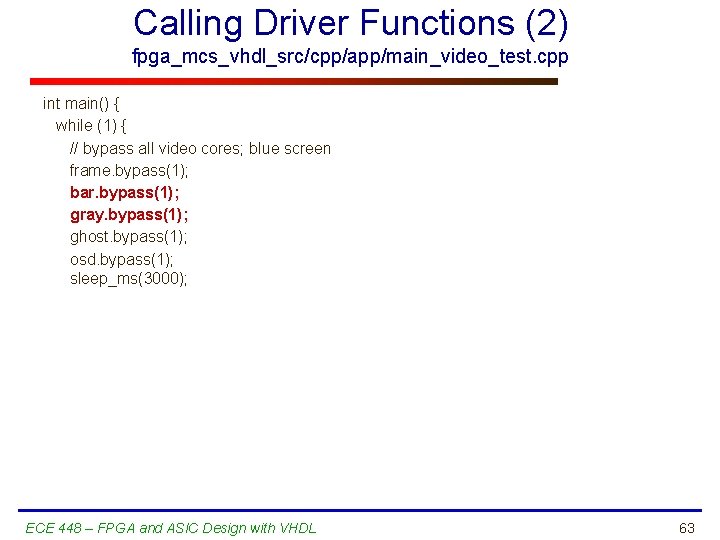

Calling Driver Functions (2) fpga_mcs_vhdl_src/cpp/app/main_video_test. cpp int main() { while (1) { // bypass all video cores; blue screen frame. bypass(1); bar. bypass(1); gray. bypass(1); ghost. bypass(1); osd. bypass(1); sleep_ms(3000); ECE 448 – FPGA and ASIC Design with VHDL 63

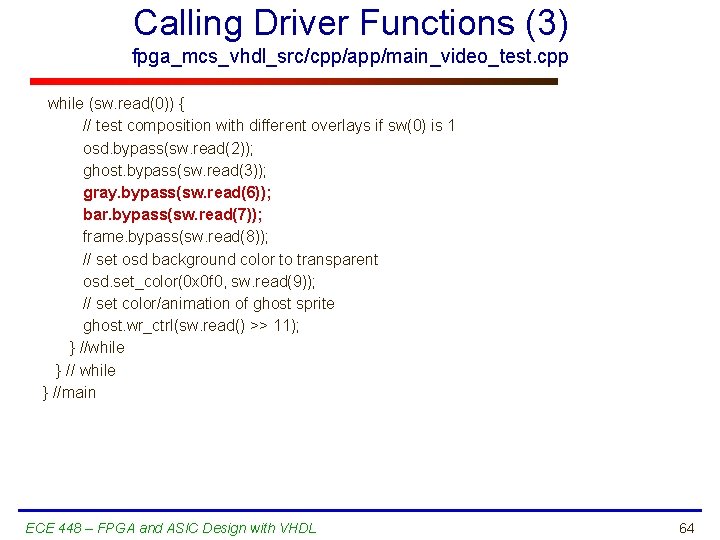

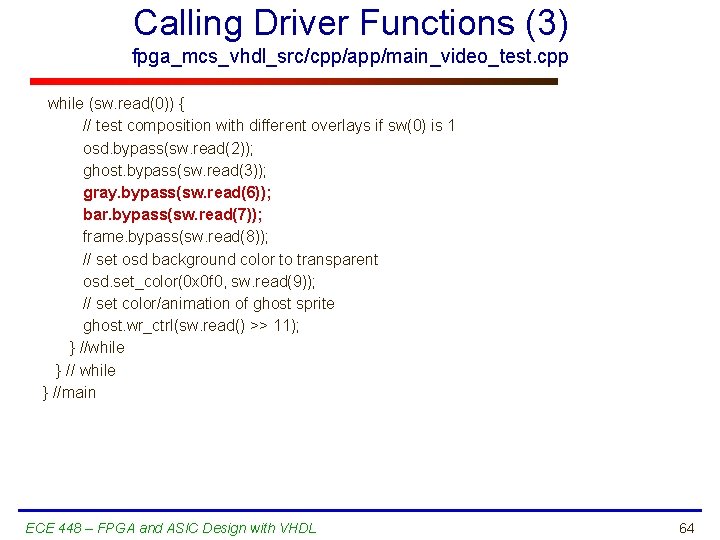

Calling Driver Functions (3) fpga_mcs_vhdl_src/cpp/app/main_video_test. cpp while (sw. read(0)) { // test composition with different overlays if sw(0) is 1 osd. bypass(sw. read(2)); ghost. bypass(sw. read(3)); gray. bypass(sw. read(6)); bar. bypass(sw. read(7)); frame. bypass(sw. read(8)); // set osd background color to transparent osd. set_color(0 x 0 f 0, sw. read(9)); // set color/animation of ghost sprite ghost. wr_ctrl(sw. read() >> 11); } //while } //main ECE 448 – FPGA and ASIC Design with VHDL 64