ECE 448 Lecture 13 VGA Display Part 4

![Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. . Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. .](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-16.jpg)

![Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. . Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. .](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-19.jpg)

![Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. . Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. .](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-27.jpg)

![Text Generation Circuit with Tile Memory [0. . 15] [0. . 29] & [0. Text Generation Circuit with Tile Memory [0. . 15] [0. . 29] & [0.](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-31.jpg)

![Text Generation Circuit with Tile Memory [0. . 15] [0. . 29] & [0. Text Generation Circuit with Tile Memory [0. . 15] [0. . 29] & [0.](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-38.jpg)

- Slides: 42

ECE 448 Lecture 13 VGA Display Part 4 Text Generation ECE 448 – FPGA and ASIC Design with VHDL George Mason University

Required Reading • P. Chu, FPGA Prototyping by VHDL Examples Chapter 13, VGA Controller II: Text • Source Codes of Examples http: //academic. csuohio. edu/chu_p/rtl/fpga_vhdl. html • Basys 3 FPGA Board Reference Manual 7. VGA Port ECE 448 – FPGA and ASIC Design with VHDL 2

Text Generation ECE 448 – FPGA and ASIC Design with VHDL 3

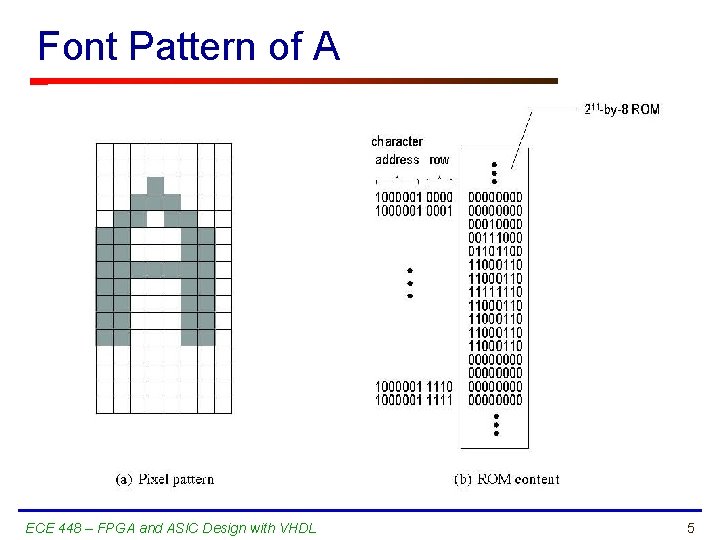

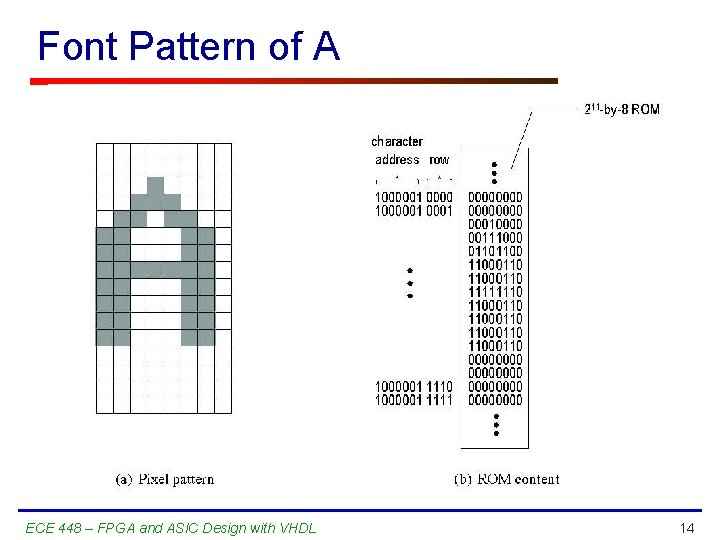

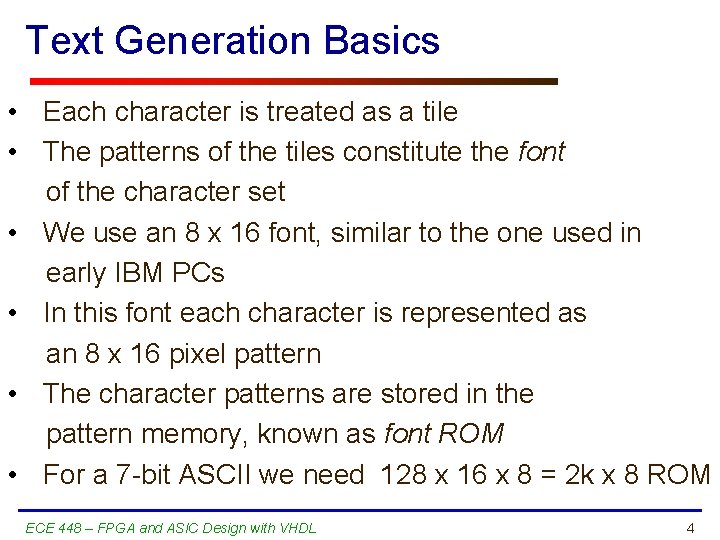

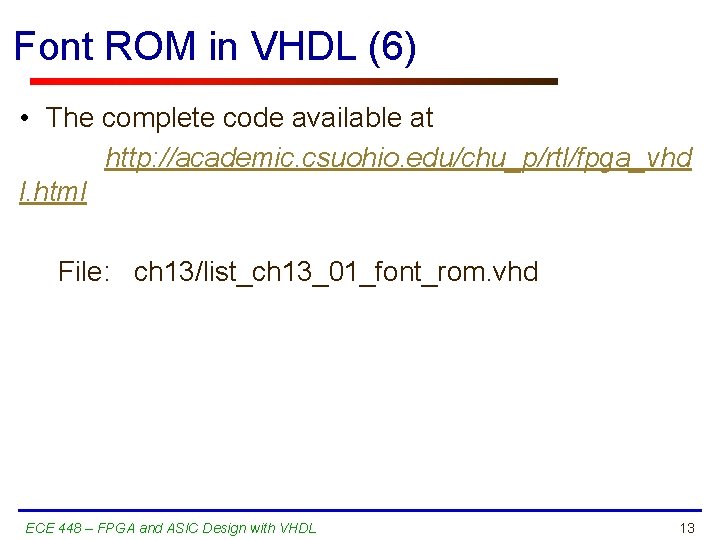

Text Generation Basics • Each character is treated as a tile • The patterns of the tiles constitute the font of the character set • We use an 8 x 16 font, similar to the one used in early IBM PCs • In this font each character is represented as an 8 x 16 pixel pattern • The character patterns are stored in the pattern memory, known as font ROM • For a 7 -bit ASCII we need 128 x 16 x 8 = 2 k x 8 ROM ECE 448 – FPGA and ASIC Design with VHDL 4

Font Pattern of A ECE 448 – FPGA and ASIC Design with VHDL 5

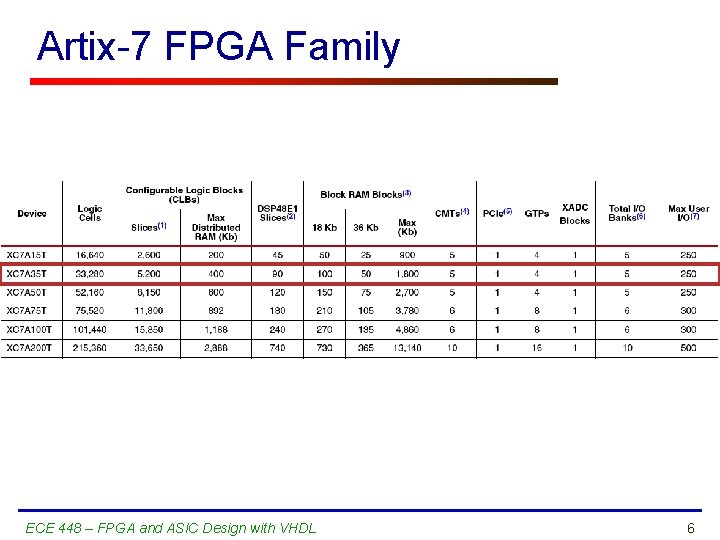

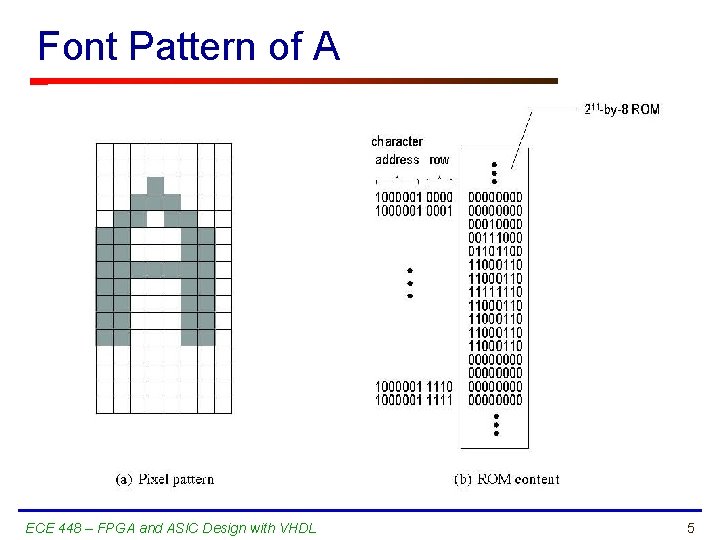

Artix-7 FPGA Family ECE 448 – FPGA and ASIC Design with VHDL 6

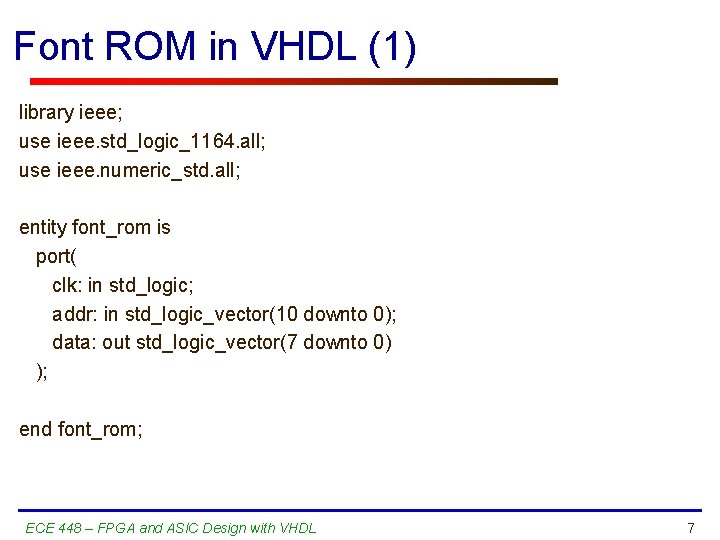

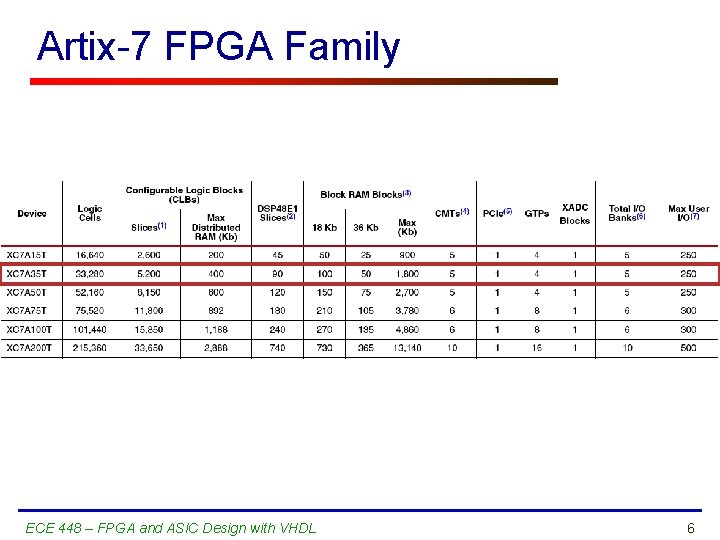

Font ROM in VHDL (1) library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity font_rom is port( clk: in std_logic; addr: in std_logic_vector(10 downto 0); data: out std_logic_vector(7 downto 0) ); end font_rom; ECE 448 – FPGA and ASIC Design with VHDL 7

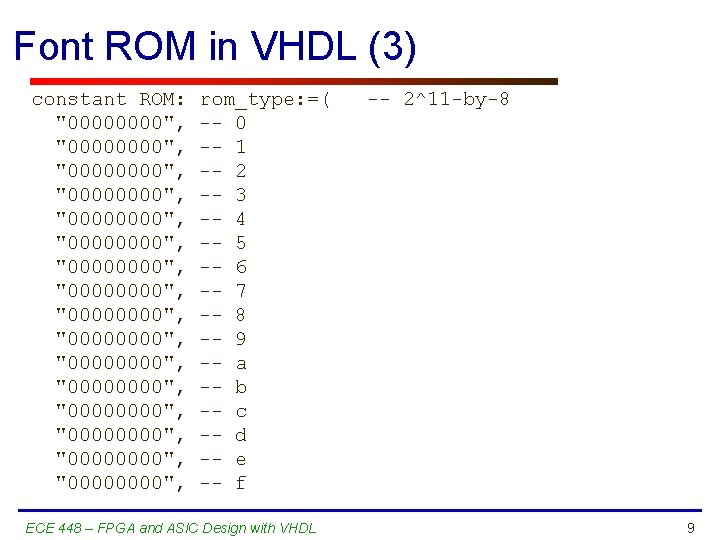

Font ROM in VHDL (2) architecture arch of font_rom is constant ADDR_WIDTH: integer: =11; constant DATA_WIDTH: integer: =8; signal addr_reg: std_logic_vector(ADDR_WIDTH-1 downto 0); type rom_type is array (0 to 2**ADDR_WIDTH-1) of std_logic_vector(DATA_WIDTH-1 downto 0); ECE 448 – FPGA and ASIC Design with VHDL 8

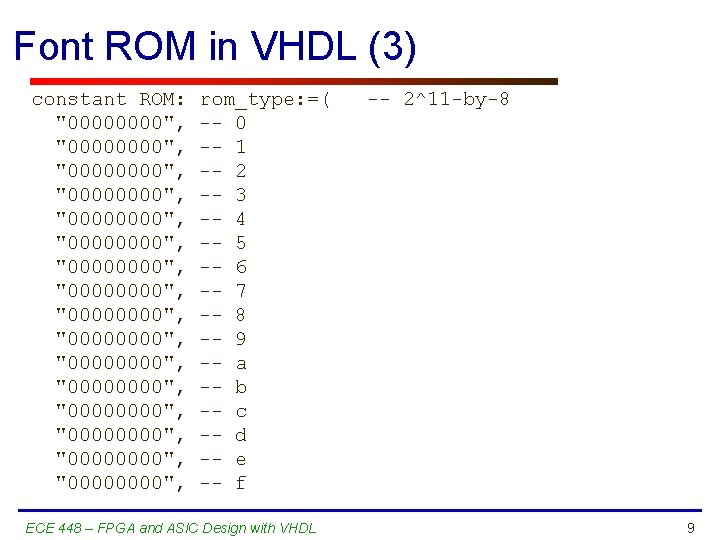

Font ROM in VHDL (3) constant ROM: "00000000", "00000000", "00000000", "00000000", rom_type: =( -- 0 -- 1 -- 2 -- 3 -- 4 -- 5 -- 6 -- 7 -- 8 -- 9 -- a -- b -- c -- d -- e -- f ECE 448 – FPGA and ASIC Design with VHDL -- 2^11 -by-8 9

Font ROM in VHDL (4) -- code x 01 (smiley face) "0000", -- 0 "0000", -- 1 "01111110", -- 2 ****** "10000001", -- 3 * * "10100101", -- 4 * * "10000001", -- 5 * * "10000001", -- 6 * * "10111101", -- 7 * **** * "1001", -- 8 * ** * "10000001", -- 9 * * "10000001", -- a * * "01111110", -- b ****** "0000", -- c "0000", -- d "0000", -- e "0000", -- f ECE 448 – FPGA and ASIC Design with VHDL 10

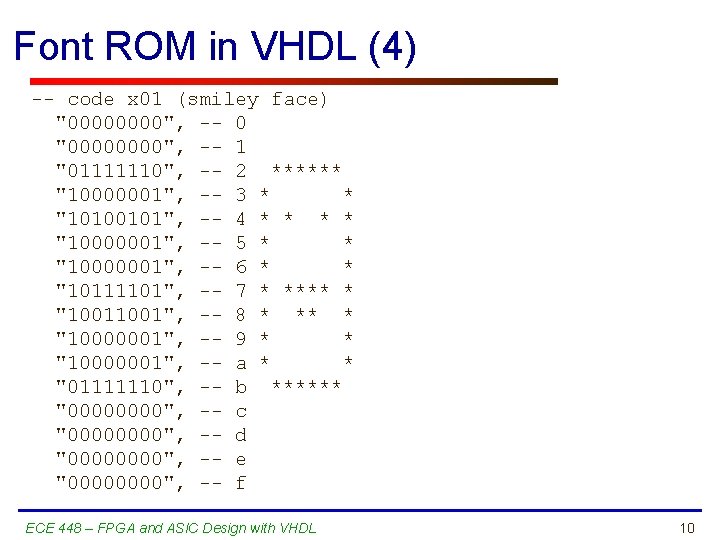

Font ROM in VHDL (5) – version 1 ………………… "0000" -- f ); begin data_next <= ROM(to_integer(unsigned(addr))); -- addr register to infer block RAM process (clk) begin if (clk'event and clk = '1') then data <= data_next; end if; end process; end arch; ECE 448 – FPGA and ASIC Design with VHDL 11

Font ROM in VHDL (5) – version 2 ………………… "0000" -- f ); begin -- addr register to infer block RAM process (clk) begin if (clk'event and clk = '1') then addr_reg <= addr; end if; end process; data <= ROM(to_integer(unsigned(addr_reg))); end arch; ECE 448 – FPGA and ASIC Design with VHDL 12

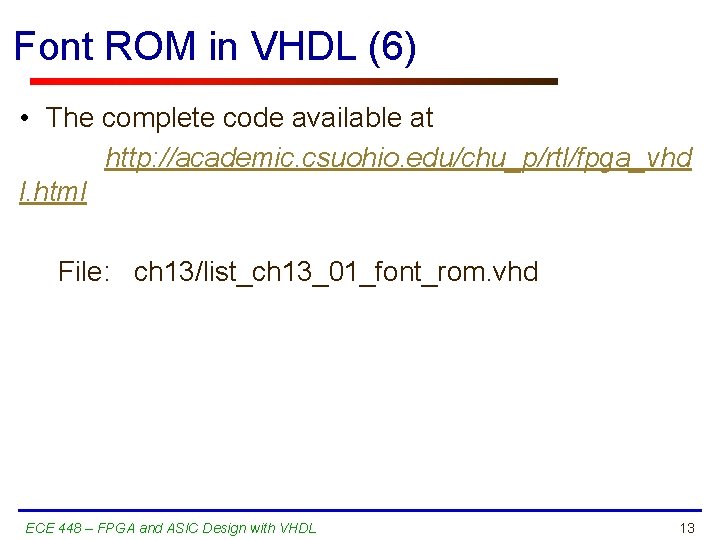

Font ROM in VHDL (6) • The complete code available at http: //academic. csuohio. edu/chu_p/rtl/fpga_vhd l. html File: ch 13/list_ch 13_01_font_rom. vhd ECE 448 – FPGA and ASIC Design with VHDL 13

Font Pattern of A ECE 448 – FPGA and ASIC Design with VHDL 14

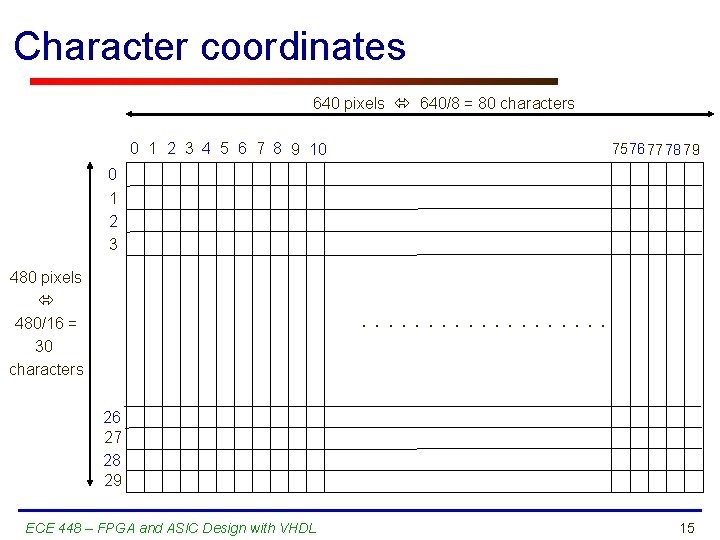

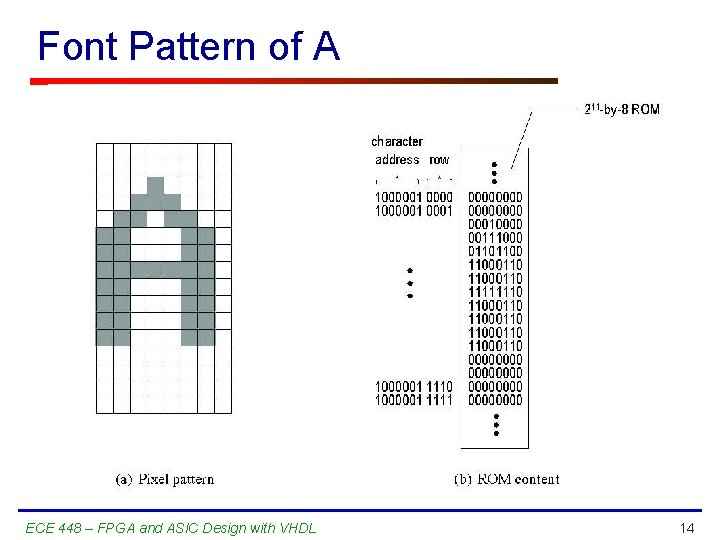

Character coordinates 640 pixels 640/8 = 80 characters 0 1 2 3 4 5 6 7 8 9 10 7576 77 78 79 0 1 2 3 480 pixels 480/16 = 30 characters . . 26 27 28 29 ECE 448 – FPGA and ASIC Design with VHDL 15

![Text Generation Circuit 0 15 0 29 0 127 0 Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. .](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-16.jpg)

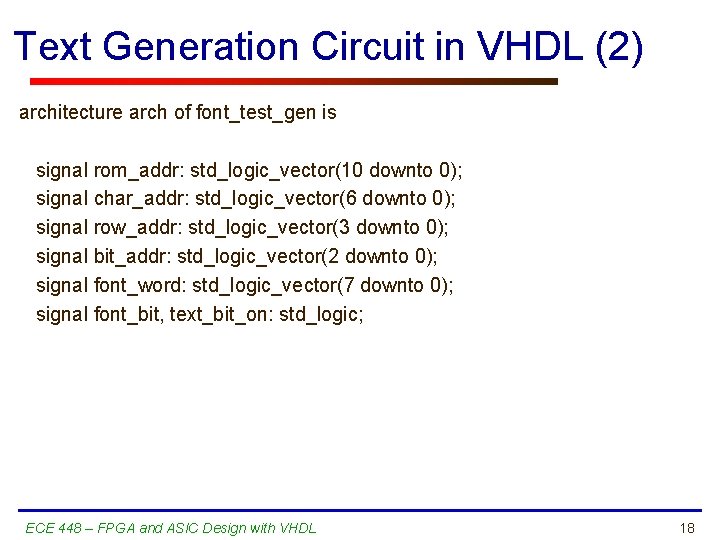

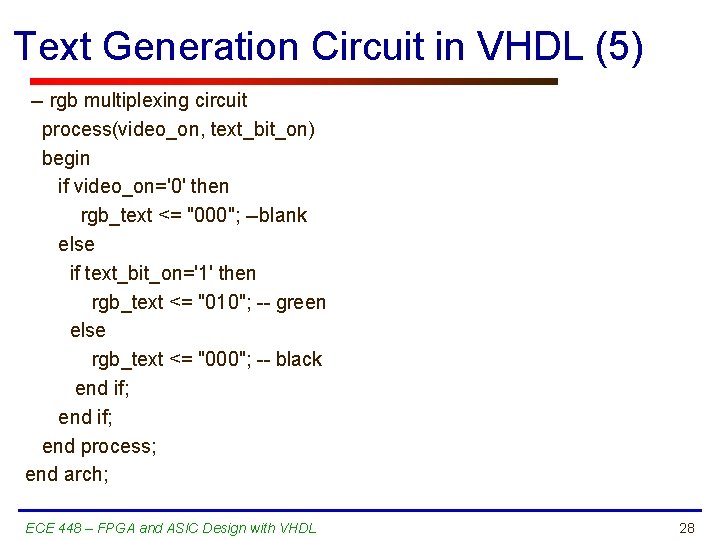

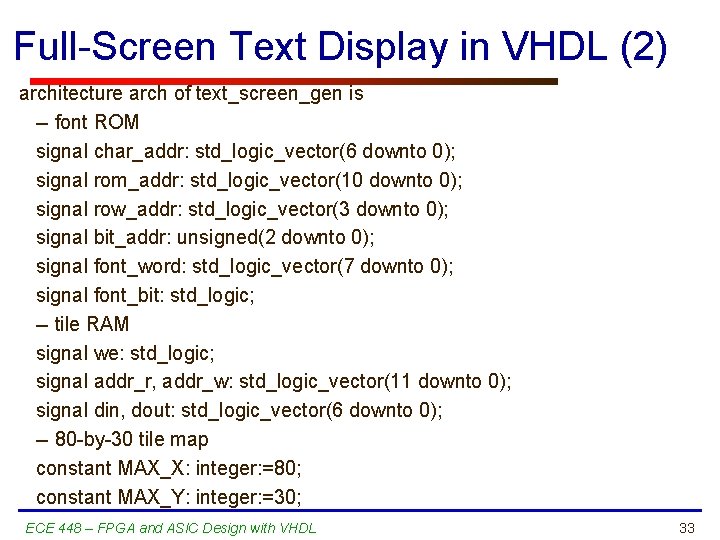

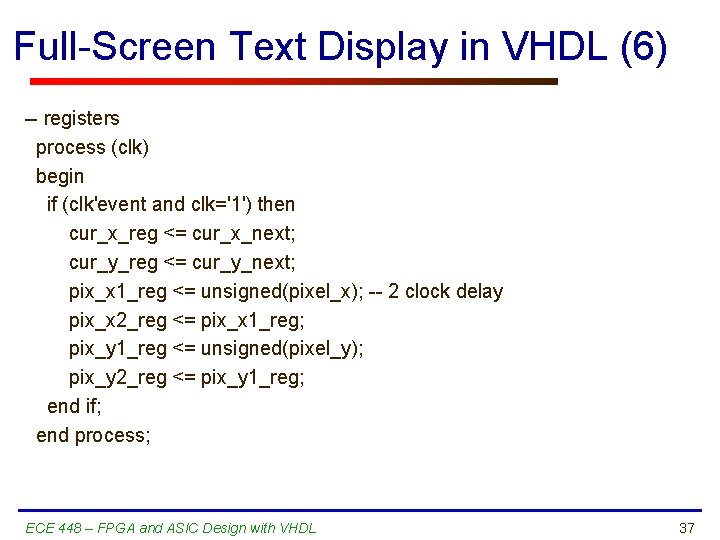

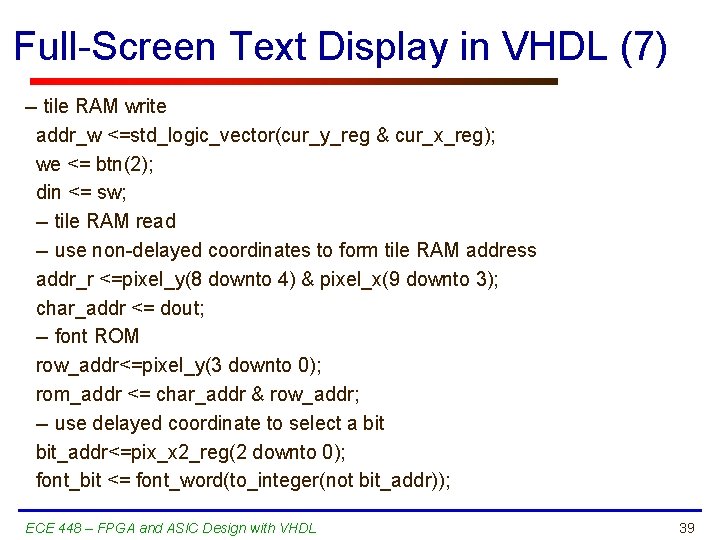

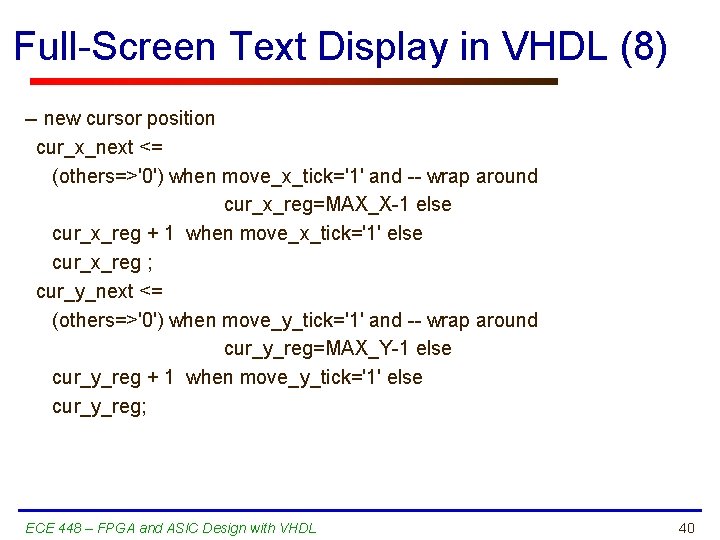

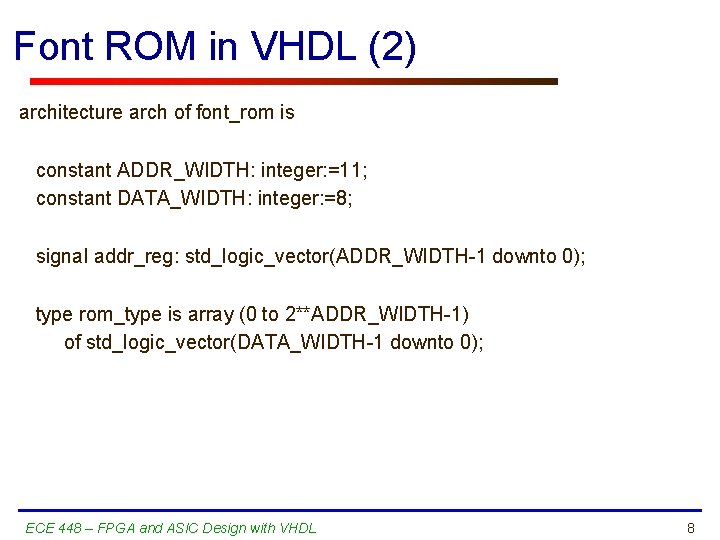

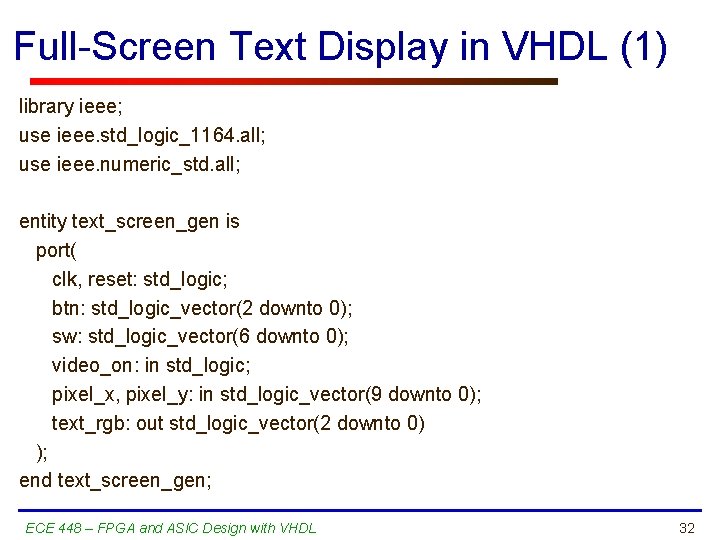

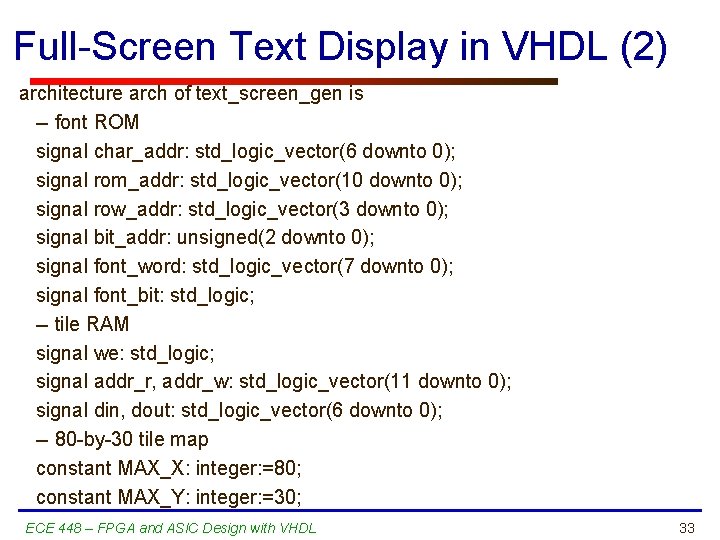

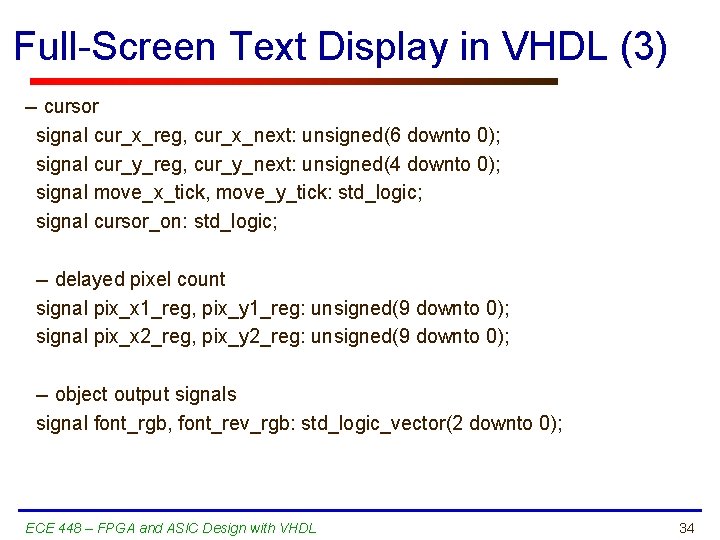

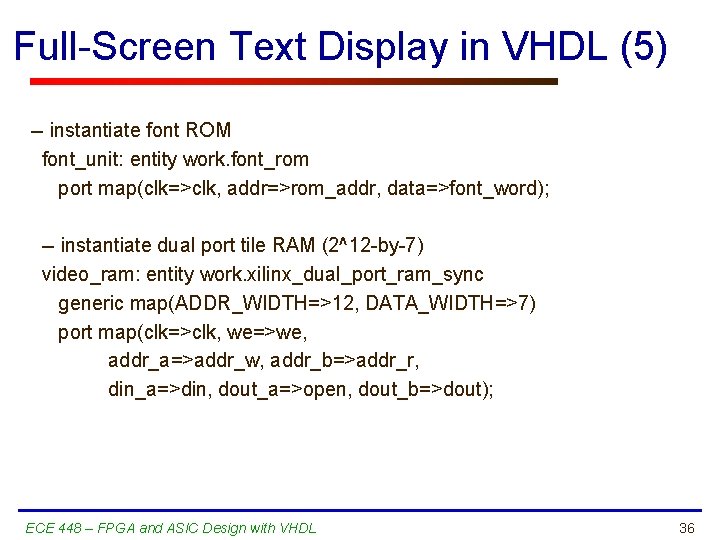

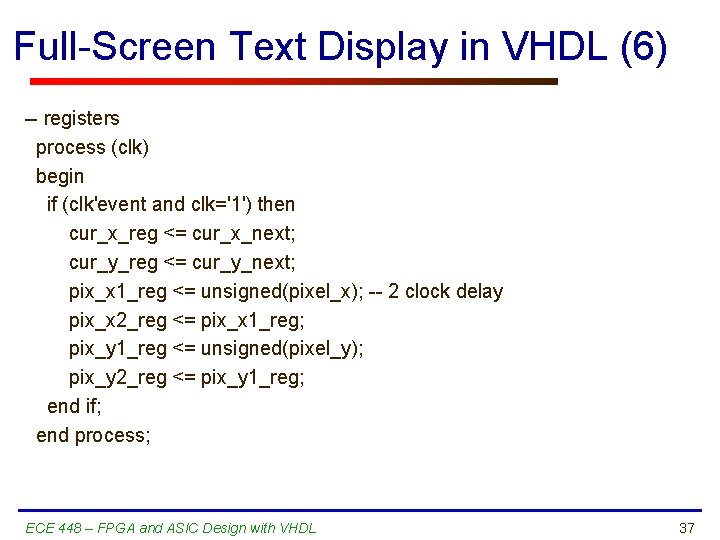

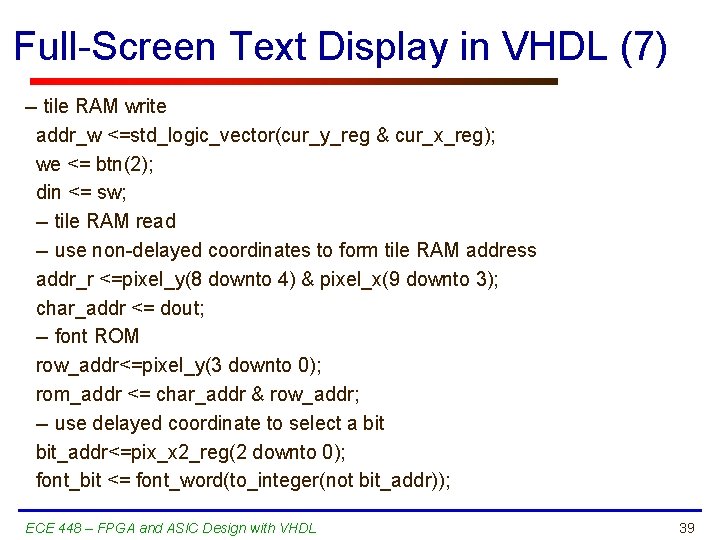

Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. . 2047] [0. . 79] [0. . 7] ECE 448 – FPGA and ASIC Design with VHDL 16

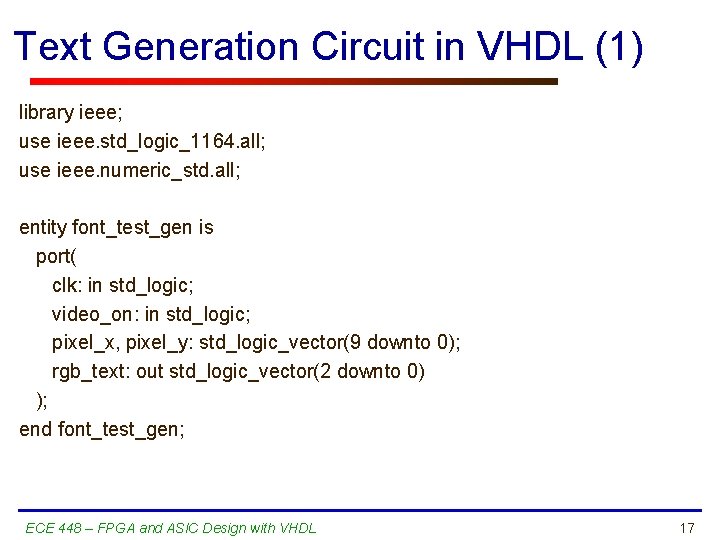

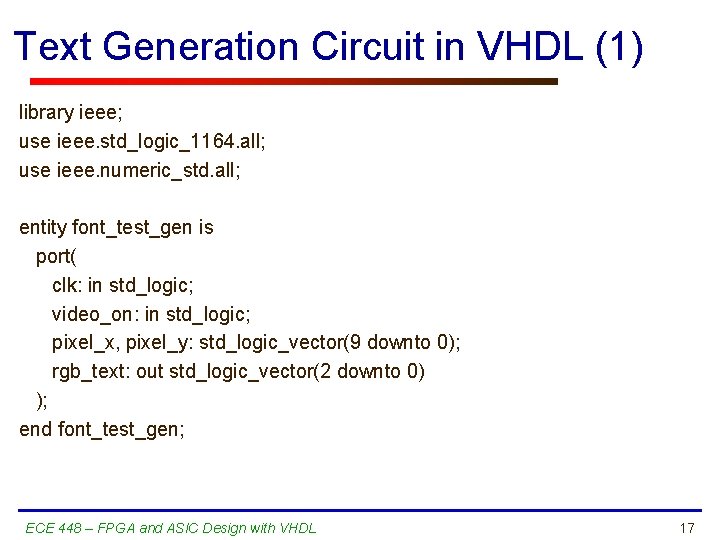

Text Generation Circuit in VHDL (1) library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity font_test_gen is port( clk: in std_logic; video_on: in std_logic; pixel_x, pixel_y: std_logic_vector(9 downto 0); rgb_text: out std_logic_vector(2 downto 0) ); end font_test_gen; ECE 448 – FPGA and ASIC Design with VHDL 17

Text Generation Circuit in VHDL (2) architecture arch of font_test_gen is signal rom_addr: std_logic_vector(10 downto 0); signal char_addr: std_logic_vector(6 downto 0); signal row_addr: std_logic_vector(3 downto 0); signal bit_addr: std_logic_vector(2 downto 0); signal font_word: std_logic_vector(7 downto 0); signal font_bit, text_bit_on: std_logic; ECE 448 – FPGA and ASIC Design with VHDL 18

![Text Generation Circuit 0 15 0 29 0 127 0 Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. .](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-19.jpg)

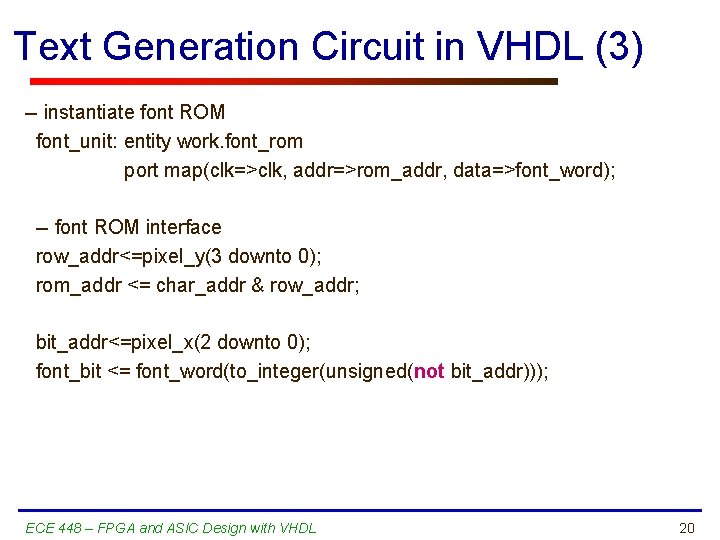

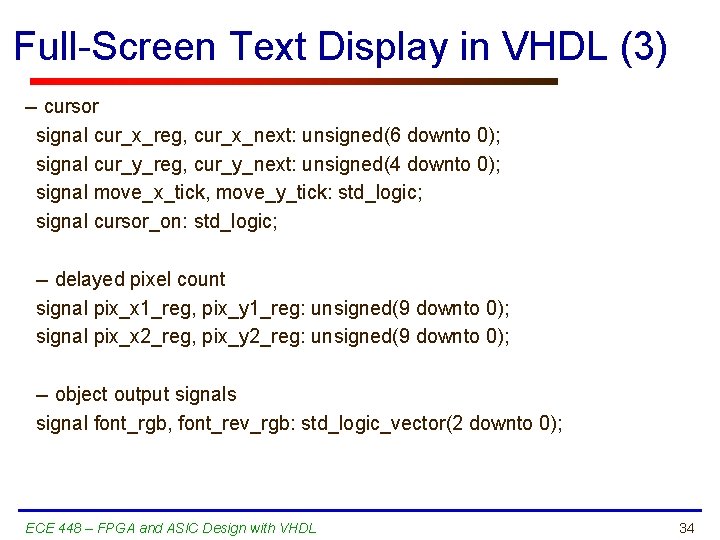

Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. . 2047] [0. . 79] [0. . 7] ECE 448 – FPGA and ASIC Design with VHDL 19

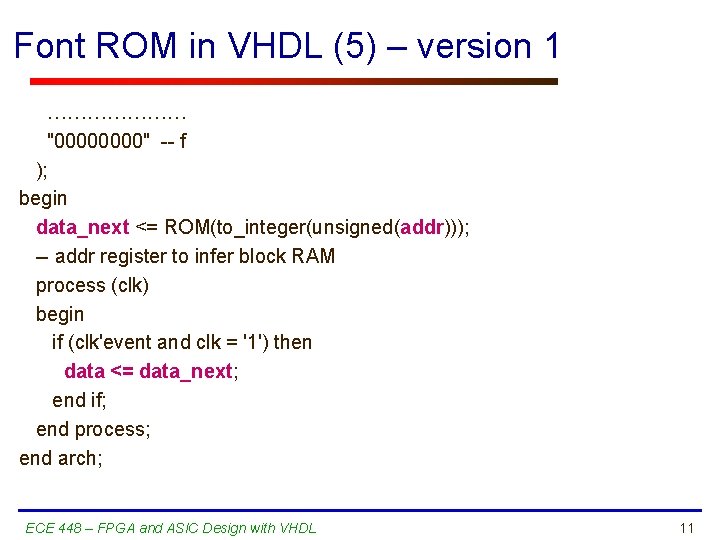

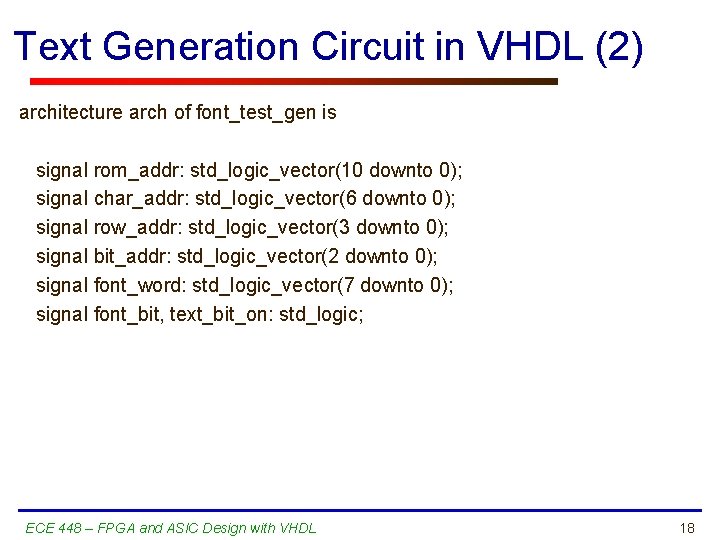

Text Generation Circuit in VHDL (3) -- instantiate font ROM font_unit: entity work. font_rom port map(clk=>clk, addr=>rom_addr, data=>font_word); -- font ROM interface row_addr<=pixel_y(3 downto 0); rom_addr <= char_addr & row_addr; bit_addr<=pixel_x(2 downto 0); font_bit <= font_word(to_integer(unsigned(not bit_addr))); ECE 448 – FPGA and ASIC Design with VHDL 20

not bit_addr= 0 1 2 3 4 5 6 7 f(bit_addr)= 7 6 5 4 3 2 1 0 f(bit_addr) = 7 – bit_addr = bit_addr Example: 2 = 0102 5 = 1012 = 7 -2 = 2 ECE 448 – FPGA and ASIC Design with VHDL 21

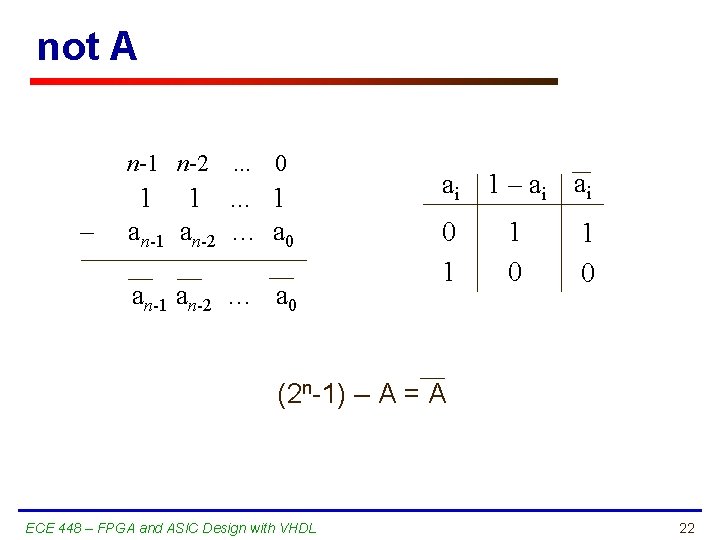

not A n-1 n-2 – . . . 0 1 1. . . 1 an-2 … a 0 an-1 an-2 … a 0 ai 1 – ai ai 0 1 1 0 (2 n-1) – A = A ECE 448 – FPGA and ASIC Design with VHDL 22

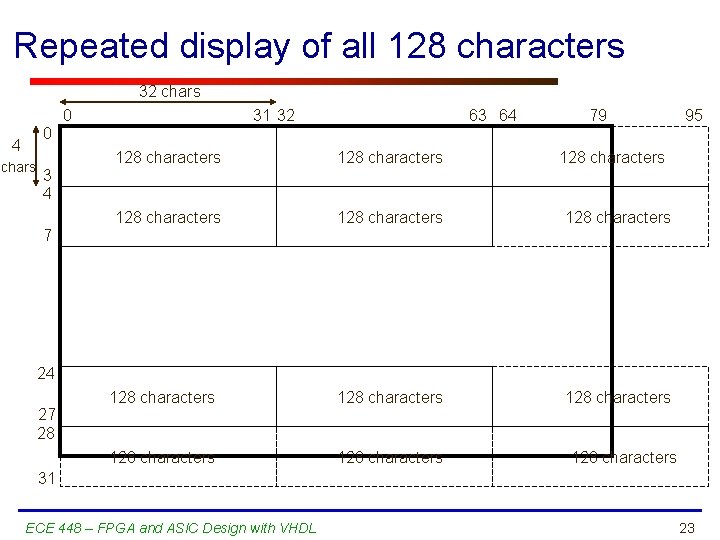

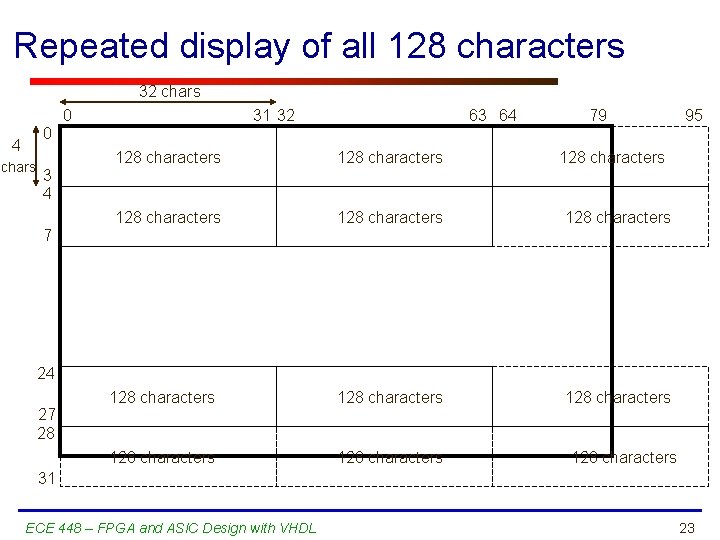

Repeated display of all 128 characters 32 chars 0 31 32 63 64 79 95 0 4 chars 128 characters 128 characters 128 characters 3 4 7 24 27 28 128 characters 31 ECE 448 – FPGA and ASIC Design with VHDL 23

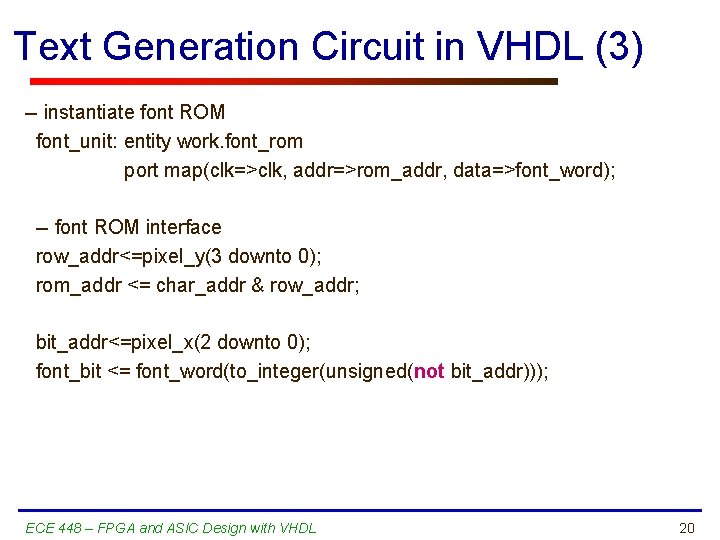

Text Generation Circuit in VHDL (4) char_addr <=pixel_y(5 downto 4) & pixel_x(7 downto 3); -- 32 consecutive characters displayed in 4 rows -- This 32 x 4 region displayed repetitively on the screen ECE 448 – FPGA and ASIC Design with VHDL 24

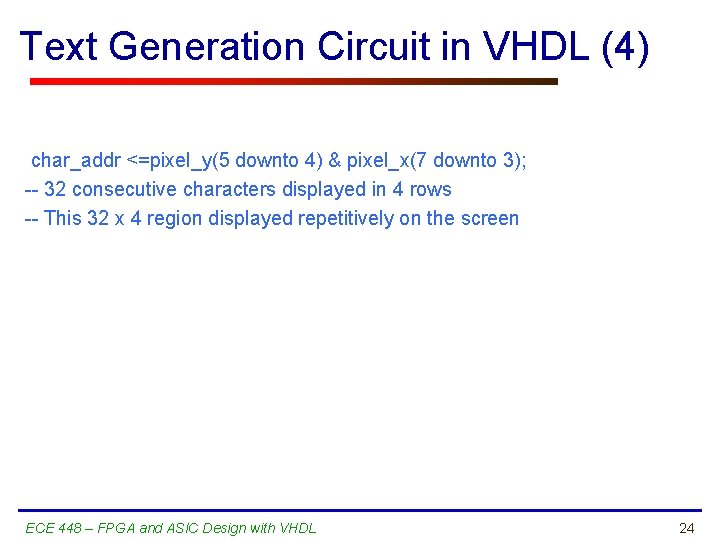

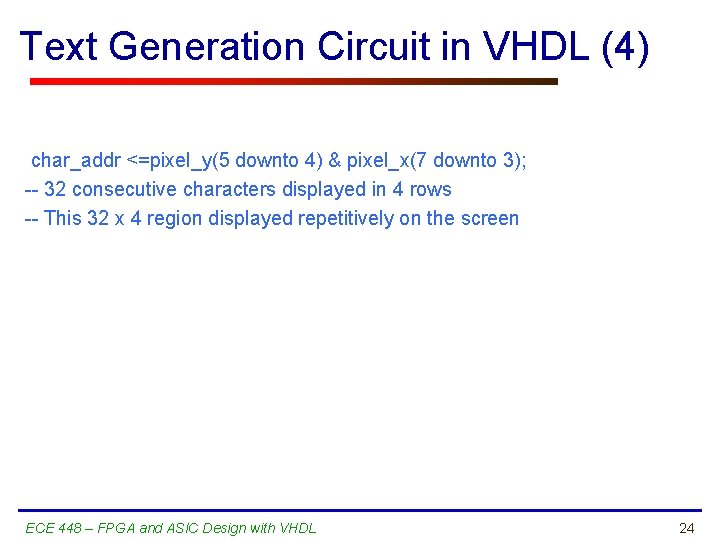

Repeated display of all 128 characters 32 chars 4 chars 0 31 0 0 255 79 128 characters 3 63 29 ECE 448 – FPGA and ASIC Design with VHDL 25

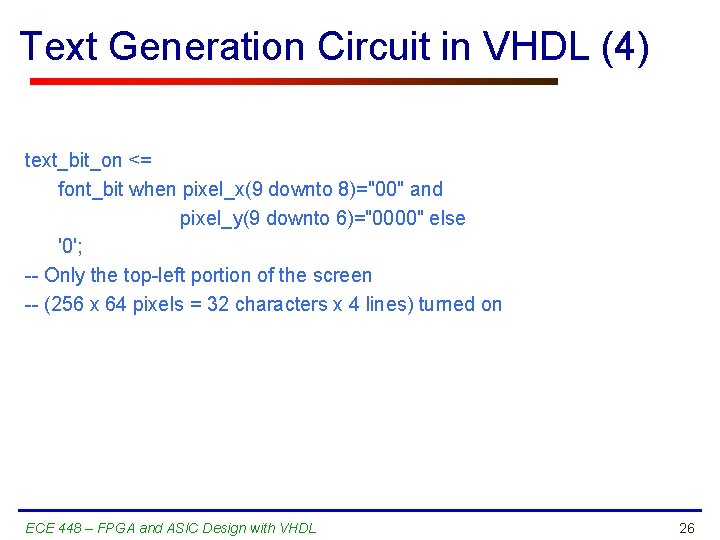

Text Generation Circuit in VHDL (4) text_bit_on <= font_bit when pixel_x(9 downto 8)="00" and pixel_y(9 downto 6)="0000" else '0'; -- Only the top-left portion of the screen -- (256 x 64 pixels = 32 characters x 4 lines) turned on ECE 448 – FPGA and ASIC Design with VHDL 26

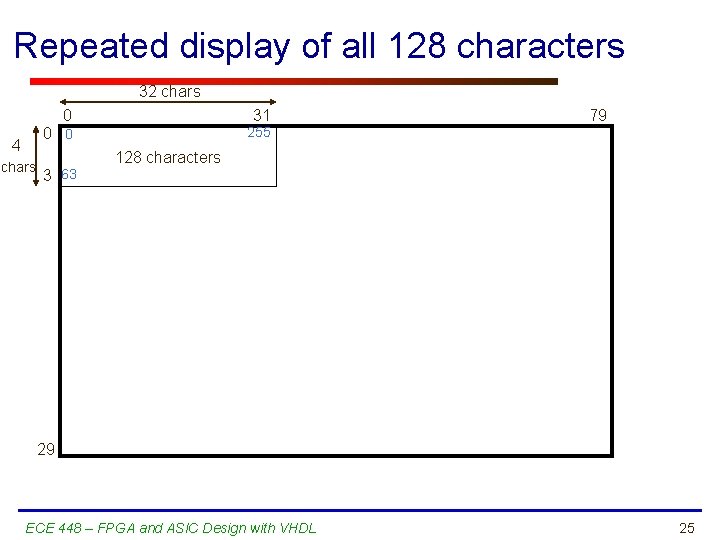

![Text Generation Circuit 0 15 0 29 0 127 0 Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. .](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-27.jpg)

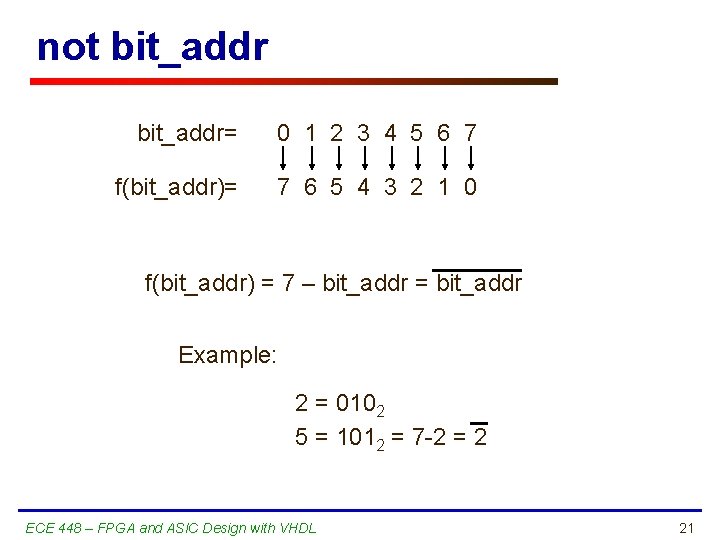

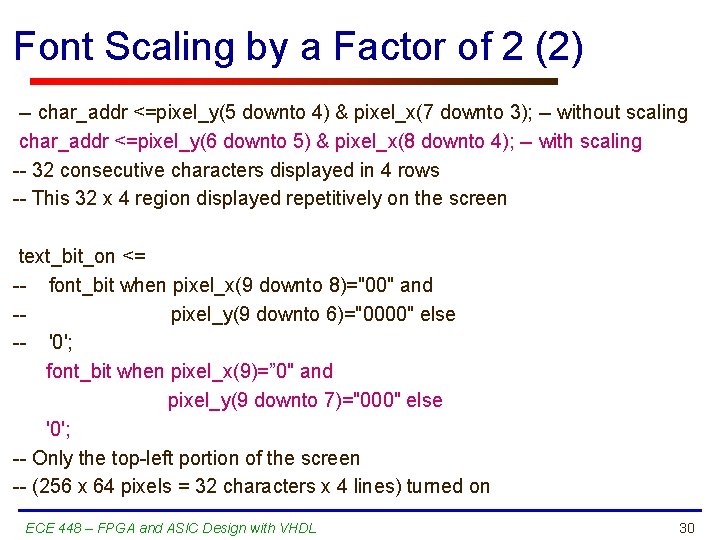

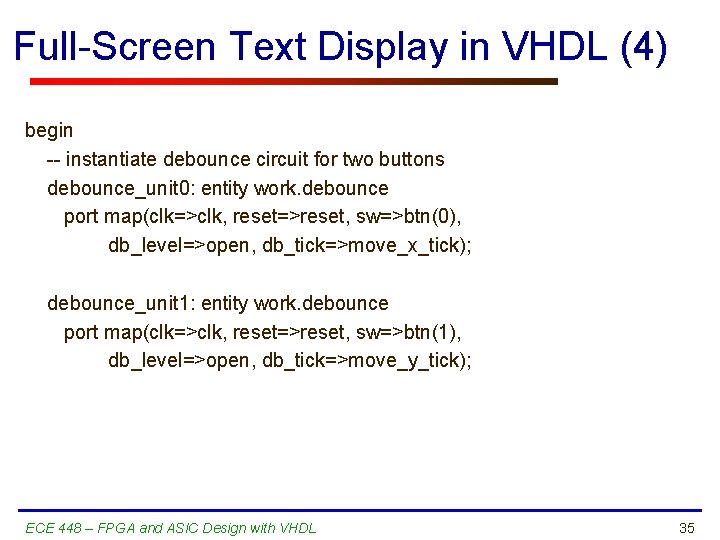

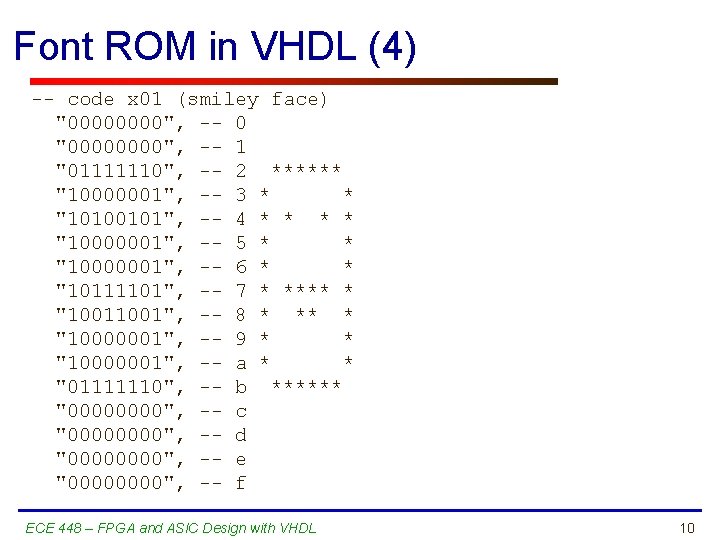

Text Generation Circuit [0. . 15] [0. . 29] [0. . 127] [0. . 2047] [0. . 79] [0. . 7] ECE 448 – FPGA and ASIC Design with VHDL 27

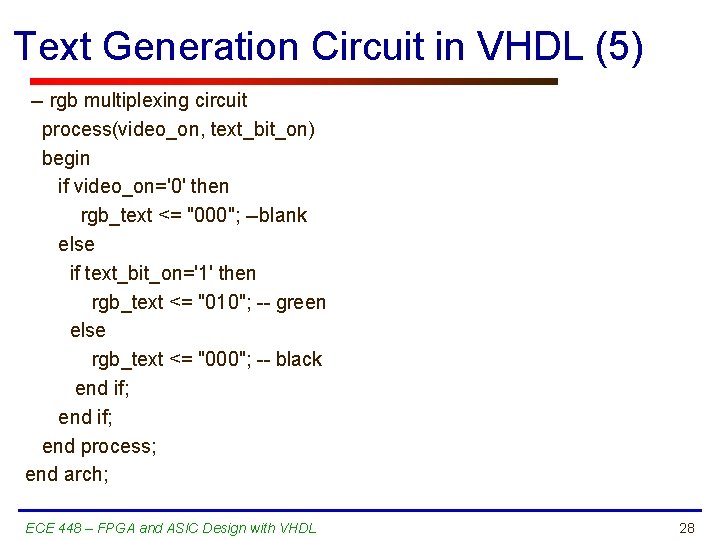

Text Generation Circuit in VHDL (5) -- rgb multiplexing circuit process(video_on, text_bit_on) begin if video_on='0' then rgb_text <= "000"; --blank else if text_bit_on='1' then rgb_text <= "010"; -- green else rgb_text <= "000"; -- black end if; end process; end arch; ECE 448 – FPGA and ASIC Design with VHDL 28

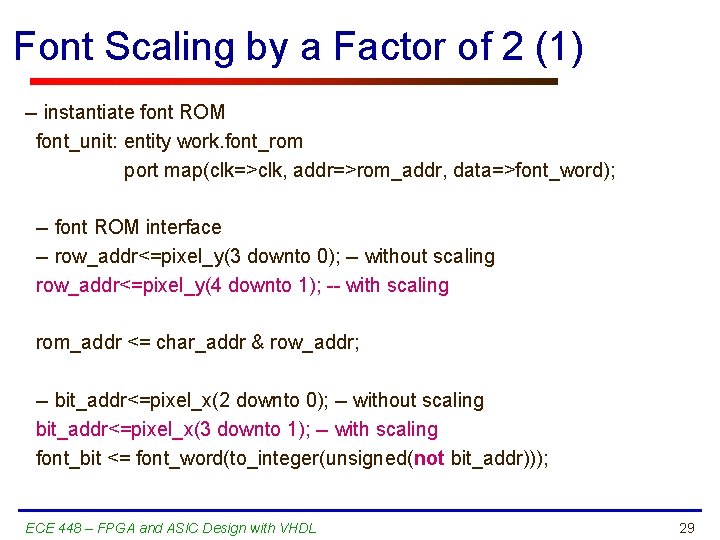

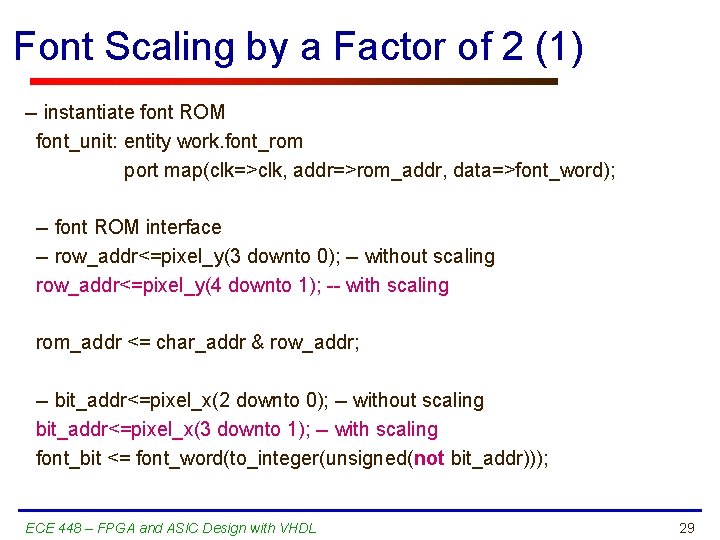

Font Scaling by a Factor of 2 (1) -- instantiate font ROM font_unit: entity work. font_rom port map(clk=>clk, addr=>rom_addr, data=>font_word); -- font ROM interface -- row_addr<=pixel_y(3 downto 0); -- without scaling row_addr<=pixel_y(4 downto 1); -- with scaling rom_addr <= char_addr & row_addr; -- bit_addr<=pixel_x(2 downto 0); -- without scaling bit_addr<=pixel_x(3 downto 1); -- with scaling font_bit <= font_word(to_integer(unsigned(not bit_addr))); ECE 448 – FPGA and ASIC Design with VHDL 29

Font Scaling by a Factor of 2 (2) -- char_addr <=pixel_y(5 downto 4) & pixel_x(7 downto 3); -- without scaling char_addr <=pixel_y(6 downto 5) & pixel_x(8 downto 4); -- with scaling -- 32 consecutive characters displayed in 4 rows -- This 32 x 4 region displayed repetitively on the screen text_bit_on <= -- font_bit when pixel_x(9 downto 8)="00" and -pixel_y(9 downto 6)="0000" else -- '0'; font_bit when pixel_x(9)=” 0" and pixel_y(9 downto 7)="000" else '0'; -- Only the top-left portion of the screen -- (256 x 64 pixels = 32 characters x 4 lines) turned on ECE 448 – FPGA and ASIC Design with VHDL 30

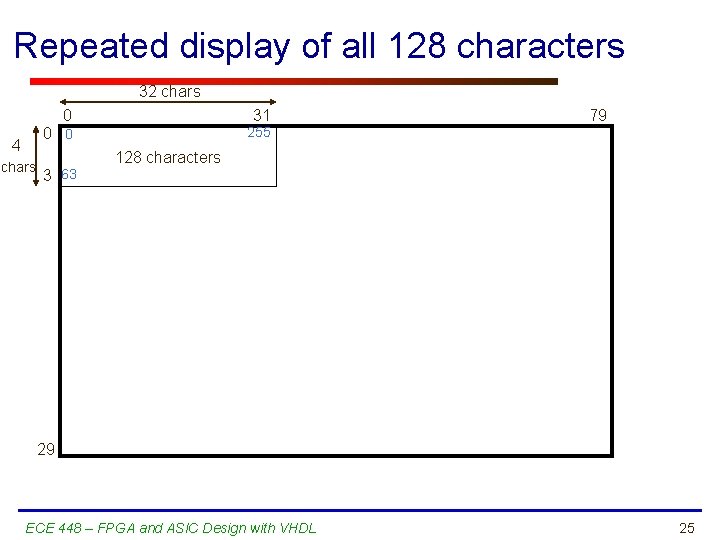

![Text Generation Circuit with Tile Memory 0 15 0 29 0 Text Generation Circuit with Tile Memory [0. . 15] [0. . 29] & [0.](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-31.jpg)

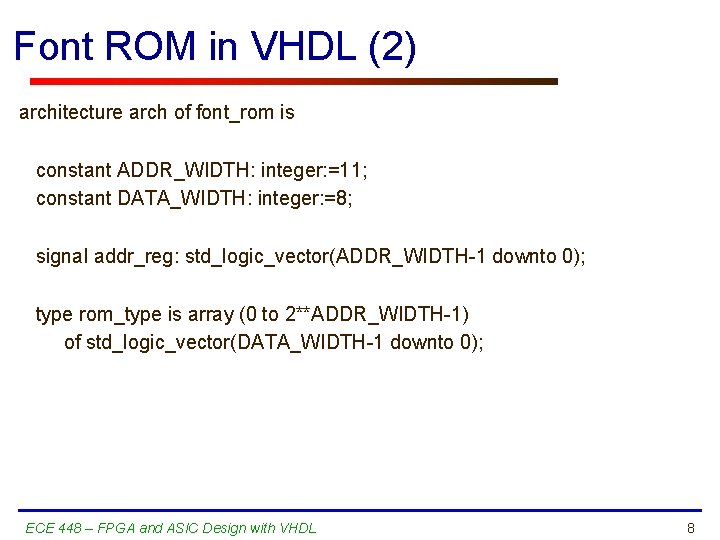

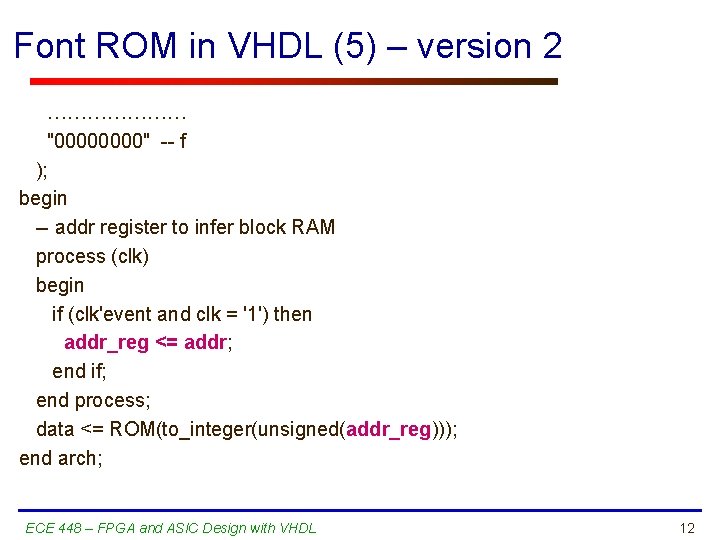

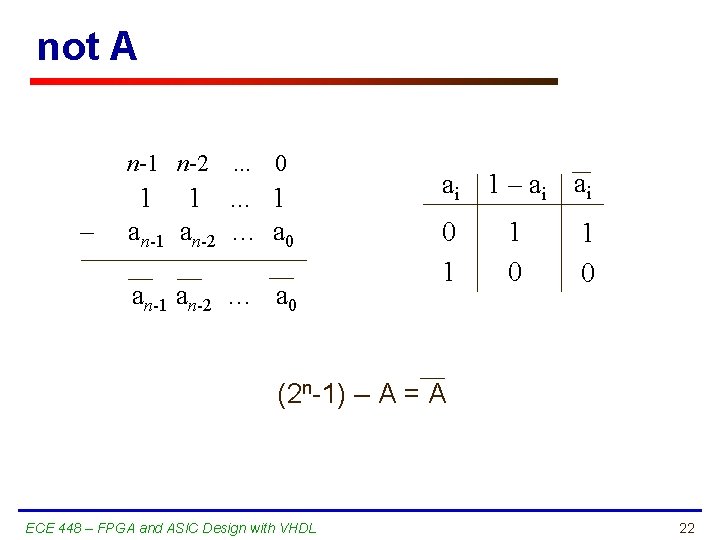

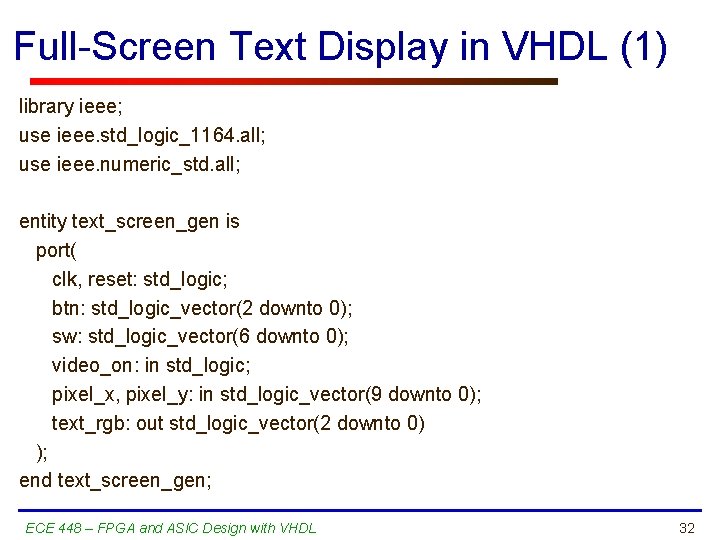

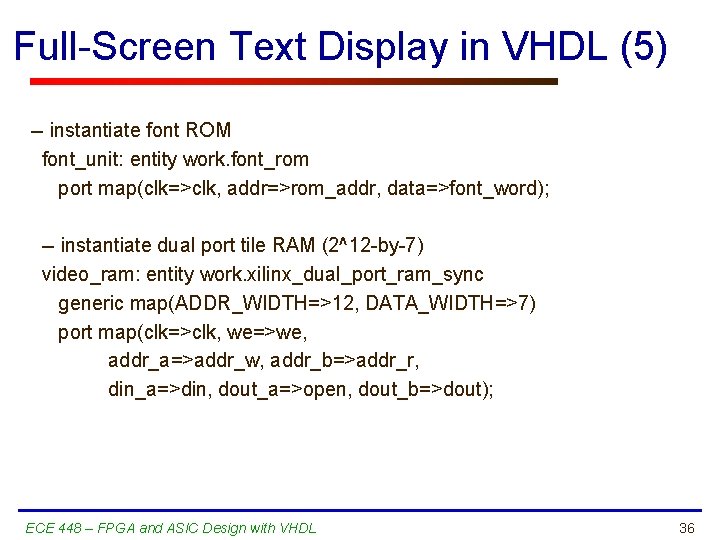

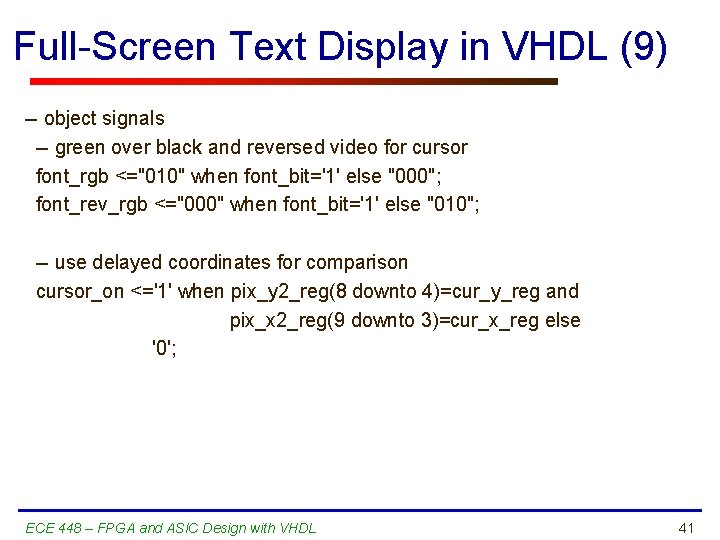

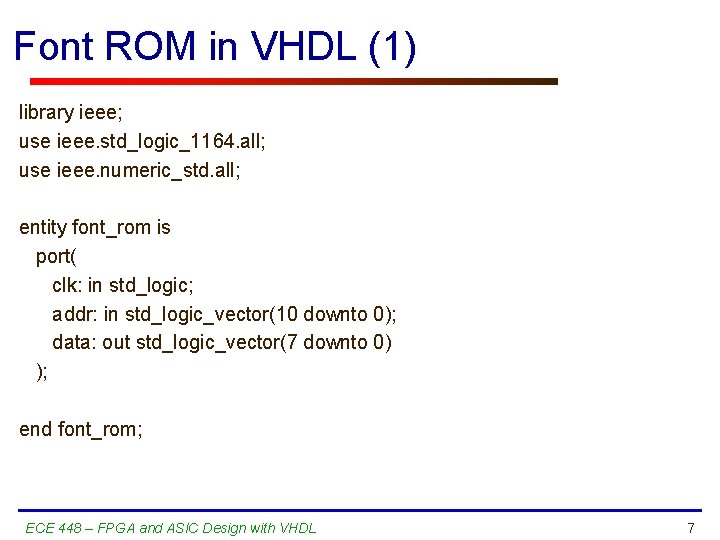

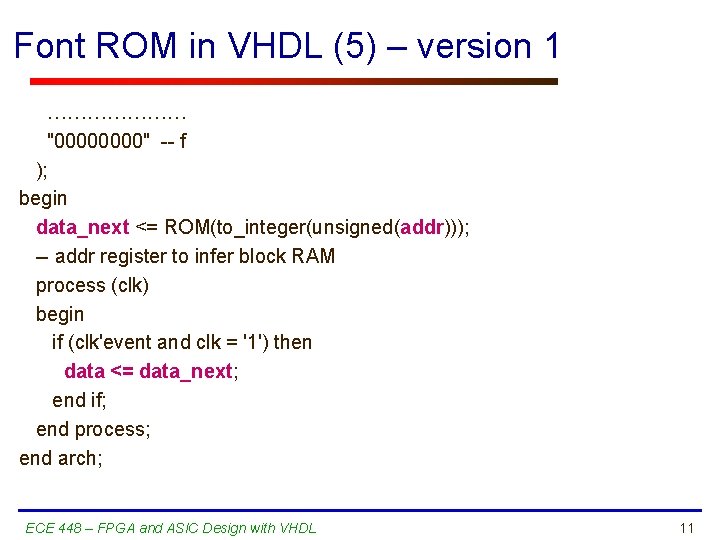

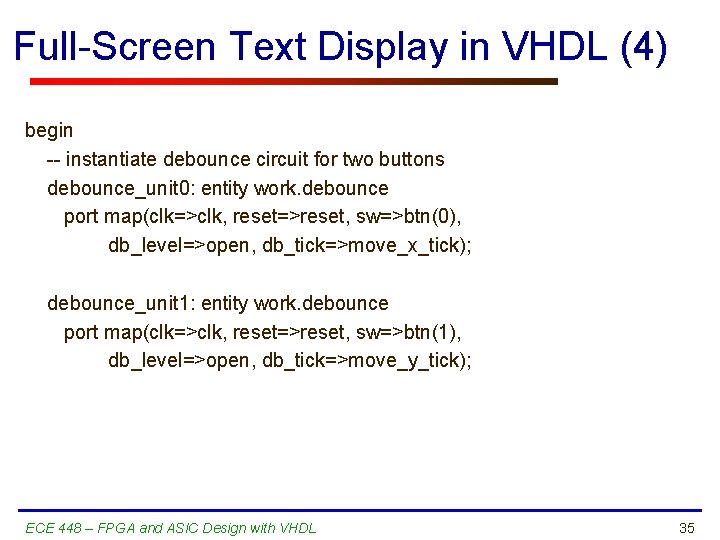

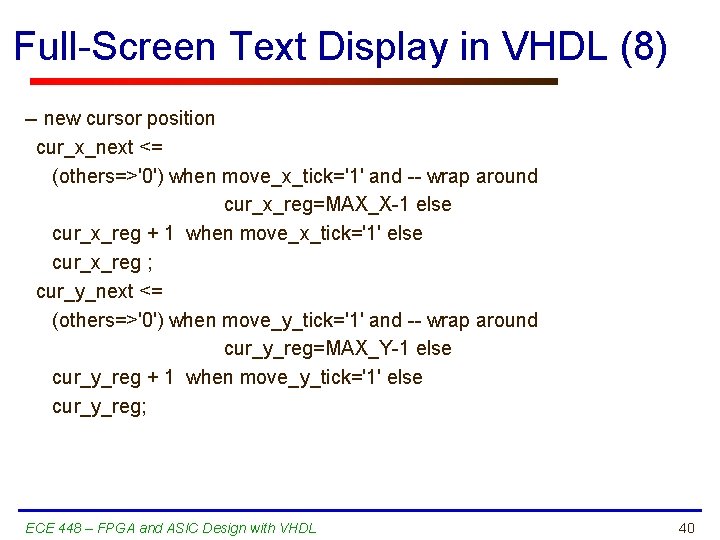

Text Generation Circuit with Tile Memory [0. . 15] [0. . 29] & [0. . 79] [7. . 0] [0. . 29] [0. . 79] [0. . 2047] [0. . 7] ECE 448 – FPGA and ASIC Design with VHDL 31

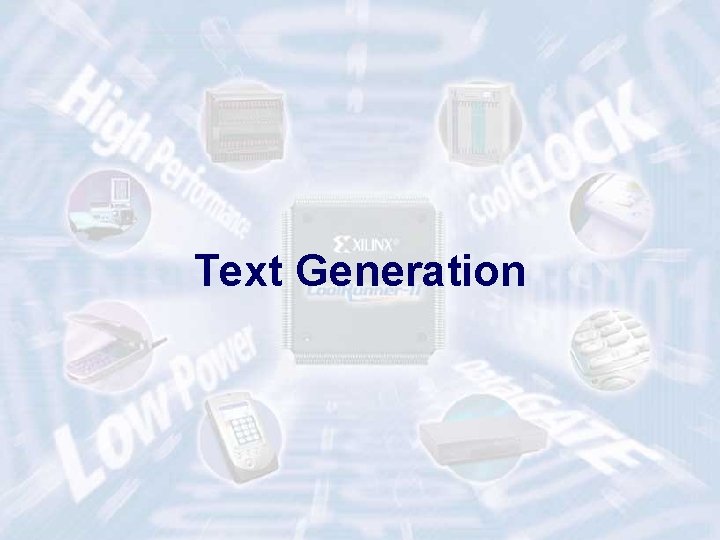

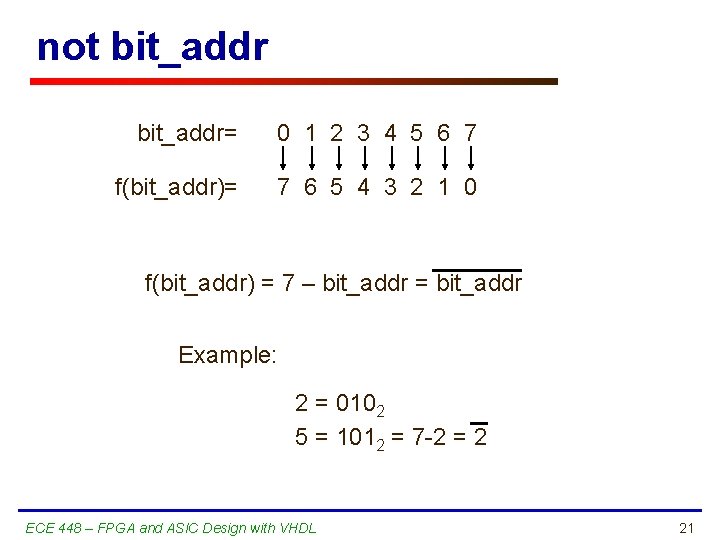

Full-Screen Text Display in VHDL (1) library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity text_screen_gen is port( clk, reset: std_logic; btn: std_logic_vector(2 downto 0); sw: std_logic_vector(6 downto 0); video_on: in std_logic; pixel_x, pixel_y: in std_logic_vector(9 downto 0); text_rgb: out std_logic_vector(2 downto 0) ); end text_screen_gen; ECE 448 – FPGA and ASIC Design with VHDL 32

Full-Screen Text Display in VHDL (2) architecture arch of text_screen_gen is -- font ROM signal char_addr: std_logic_vector(6 downto 0); signal rom_addr: std_logic_vector(10 downto 0); signal row_addr: std_logic_vector(3 downto 0); signal bit_addr: unsigned(2 downto 0); signal font_word: std_logic_vector(7 downto 0); signal font_bit: std_logic; -- tile RAM signal we: std_logic; signal addr_r, addr_w: std_logic_vector(11 downto 0); signal din, dout: std_logic_vector(6 downto 0); -- 80 -by-30 tile map constant MAX_X: integer: =80; constant MAX_Y: integer: =30; ECE 448 – FPGA and ASIC Design with VHDL 33

Full-Screen Text Display in VHDL (3) -- cursor signal cur_x_reg, cur_x_next: unsigned(6 downto 0); signal cur_y_reg, cur_y_next: unsigned(4 downto 0); signal move_x_tick, move_y_tick: std_logic; signal cursor_on: std_logic; -- delayed pixel count signal pix_x 1_reg, pix_y 1_reg: unsigned(9 downto 0); signal pix_x 2_reg, pix_y 2_reg: unsigned(9 downto 0); -- object output signals signal font_rgb, font_rev_rgb: std_logic_vector(2 downto 0); ECE 448 – FPGA and ASIC Design with VHDL 34

Full-Screen Text Display in VHDL (4) begin -- instantiate debounce circuit for two buttons debounce_unit 0: entity work. debounce port map(clk=>clk, reset=>reset, sw=>btn(0), db_level=>open, db_tick=>move_x_tick); debounce_unit 1: entity work. debounce port map(clk=>clk, reset=>reset, sw=>btn(1), db_level=>open, db_tick=>move_y_tick); ECE 448 – FPGA and ASIC Design with VHDL 35

Full-Screen Text Display in VHDL (5) -- instantiate font ROM font_unit: entity work. font_rom port map(clk=>clk, addr=>rom_addr, data=>font_word); -- instantiate dual port tile RAM (2^12 -by-7) video_ram: entity work. xilinx_dual_port_ram_sync generic map(ADDR_WIDTH=>12, DATA_WIDTH=>7) port map(clk=>clk, we=>we, addr_a=>addr_w, addr_b=>addr_r, din_a=>din, dout_a=>open, dout_b=>dout); ECE 448 – FPGA and ASIC Design with VHDL 36

Full-Screen Text Display in VHDL (6) -- registers process (clk) begin if (clk'event and clk='1') then cur_x_reg <= cur_x_next; cur_y_reg <= cur_y_next; pix_x 1_reg <= unsigned(pixel_x); -- 2 clock delay pix_x 2_reg <= pix_x 1_reg; pix_y 1_reg <= unsigned(pixel_y); pix_y 2_reg <= pix_y 1_reg; end if; end process; ECE 448 – FPGA and ASIC Design with VHDL 37

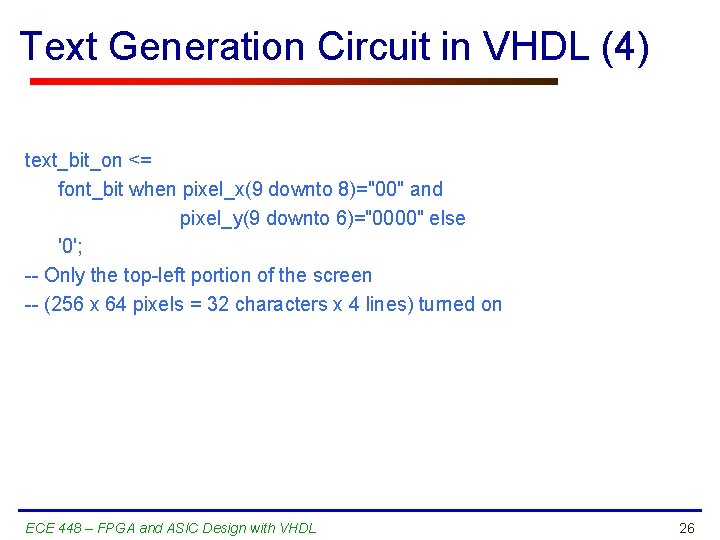

![Text Generation Circuit with Tile Memory 0 15 0 29 0 Text Generation Circuit with Tile Memory [0. . 15] [0. . 29] & [0.](https://slidetodoc.com/presentation_image_h/214c6d64dad074d3d371ef99bf1de019/image-38.jpg)

Text Generation Circuit with Tile Memory [0. . 15] [0. . 29] & [0. . 79] [7. . 0] [0. . 29] [0. . 79] [0. . 2047] [0. . 7] ECE 448 – FPGA and ASIC Design with VHDL 38

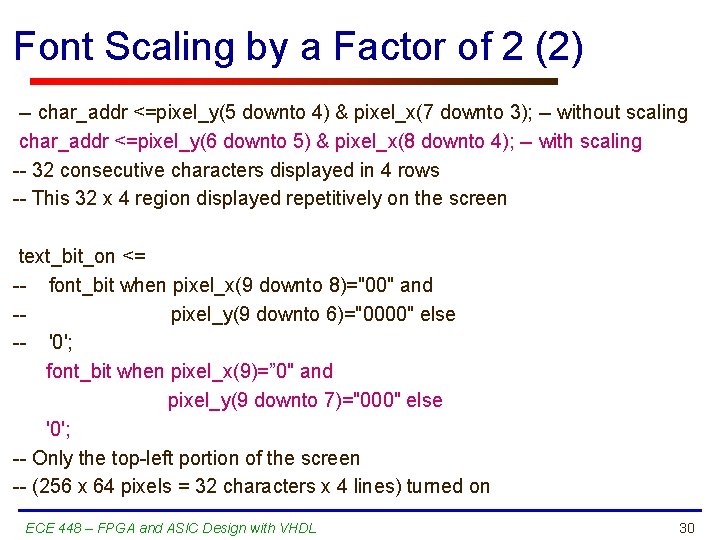

Full-Screen Text Display in VHDL (7) -- tile RAM write addr_w <=std_logic_vector(cur_y_reg & cur_x_reg); we <= btn(2); din <= sw; -- tile RAM read -- use non-delayed coordinates to form tile RAM address addr_r <=pixel_y(8 downto 4) & pixel_x(9 downto 3); char_addr <= dout; -- font ROM row_addr<=pixel_y(3 downto 0); rom_addr <= char_addr & row_addr; -- use delayed coordinate to select a bit_addr<=pix_x 2_reg(2 downto 0); font_bit <= font_word(to_integer(not bit_addr)); ECE 448 – FPGA and ASIC Design with VHDL 39

Full-Screen Text Display in VHDL (8) -- new cursor position cur_x_next <= (others=>'0') when move_x_tick='1' and -- wrap around cur_x_reg=MAX_X-1 else cur_x_reg + 1 when move_x_tick='1' else cur_x_reg ; cur_y_next <= (others=>'0') when move_y_tick='1' and -- wrap around cur_y_reg=MAX_Y-1 else cur_y_reg + 1 when move_y_tick='1' else cur_y_reg; ECE 448 – FPGA and ASIC Design with VHDL 40

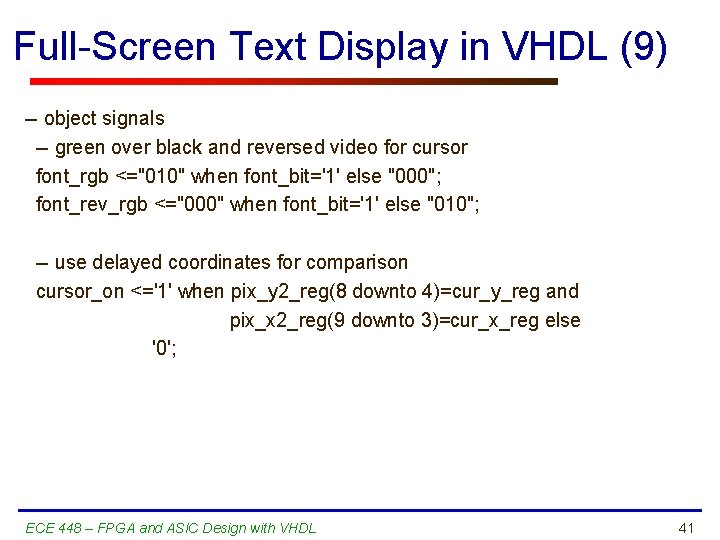

Full-Screen Text Display in VHDL (9) -- object signals -- green over black and reversed video for cursor font_rgb <="010" when font_bit='1' else "000"; font_rev_rgb <="000" when font_bit='1' else "010"; -- use delayed coordinates for comparison cursor_on <='1' when pix_y 2_reg(8 downto 4)=cur_y_reg and pix_x 2_reg(9 downto 3)=cur_x_reg else '0'; ECE 448 – FPGA and ASIC Design with VHDL 41

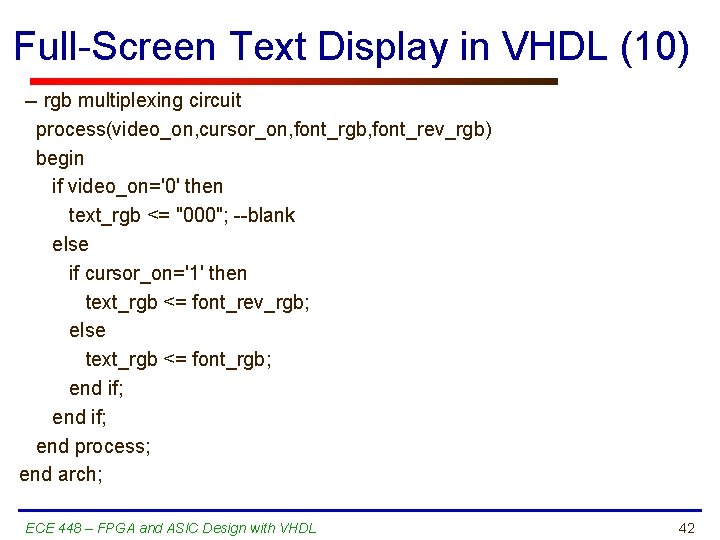

Full-Screen Text Display in VHDL (10) -- rgb multiplexing circuit process(video_on, cursor_on, font_rgb, font_rev_rgb) begin if video_on='0' then text_rgb <= "000"; --blank else if cursor_on='1' then text_rgb <= font_rev_rgb; else text_rgb <= font_rgb; end if; end process; end arch; ECE 448 – FPGA and ASIC Design with VHDL 42