ECE 448 Lab 4 Developing an FPro So

ECE 448: Lab 4 Developing an FPro So. C with standard & custom hardware IP cores

Agenda for today Part 1: Solution to the Lab Midterm Exam Part 2: Introduction to the FPro platform & FPro device drivers Part 3: Introduction to Lab 4 Assignment Part 4 : Hands-on session on developing an example design with an FPro System Part 5: Lab 4 Exercise 1

Part 1 Solution to the Lab Midterm Exam ECE 448 – FPGA and ASIC Design with VHDL

Part 2 Introduction to the FPro platform & FPro device drivers ECE 448 – FPGA and ASIC Design with VHDL

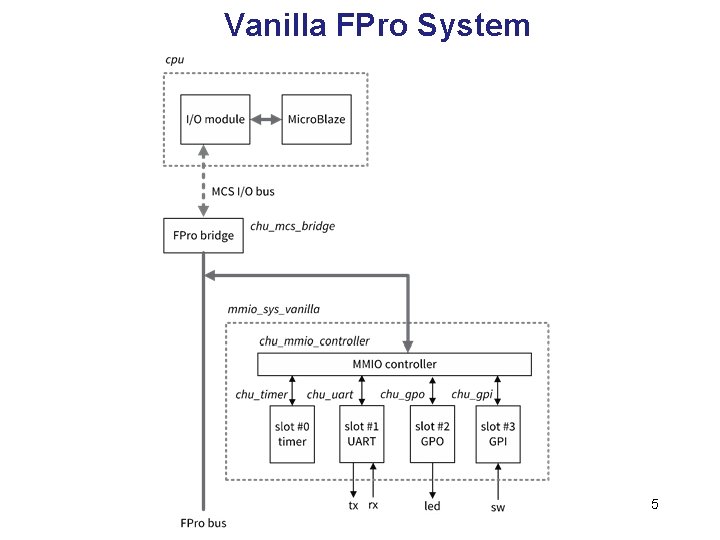

Vanilla FPro System 5

MMIO Cores of the Vanilla FPro System • Timer (for time measurements) • UART: Universal Asynchronous Receiver and Transmitter (for communication with a terminal emulator program on a PC, including displaying debug messages) • GPO: General-Purpose Output (for driving LEDs) • GPI: General-Purpose Input (for reading values of switches) 6

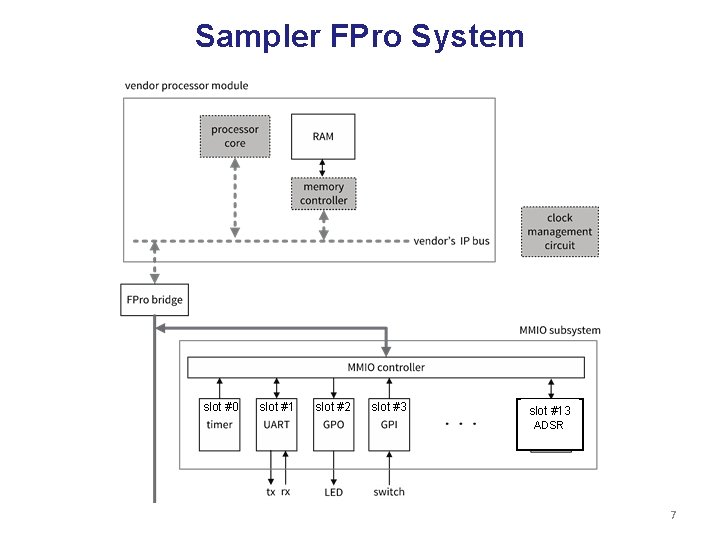

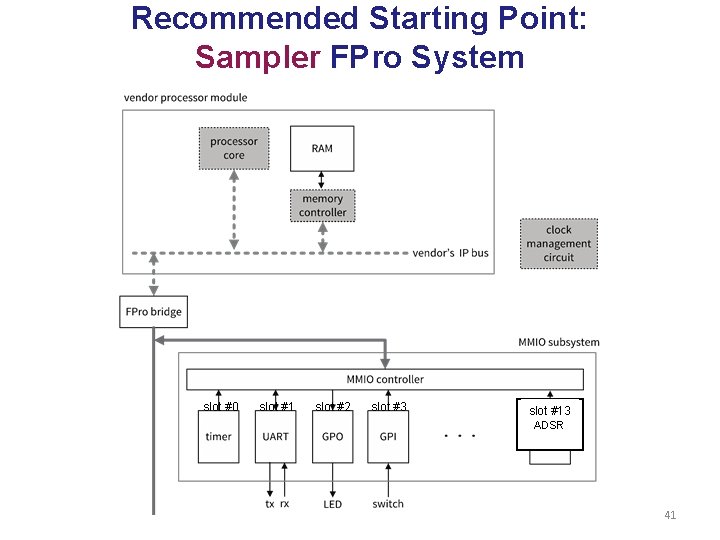

Sampler FPro System slot #0 slot #1 slot #2 slot #3 slot #13 ADSR 7

MMIO Cores of the Sampler FPro System used in Lab 4 • Timer (for time measurements) • UART: Universal Asynchronous Receiver and Transmitter (for communication with a terminal emulator program on a PC, including displaying debug messages) • GPO: General-Purpose Output (for driving LEDs) • GPI: General-Purpose Input (for reading values of switches) • Debouncing (for sensing buttons) • LED-MUX (for driving seven-segment displays) 8

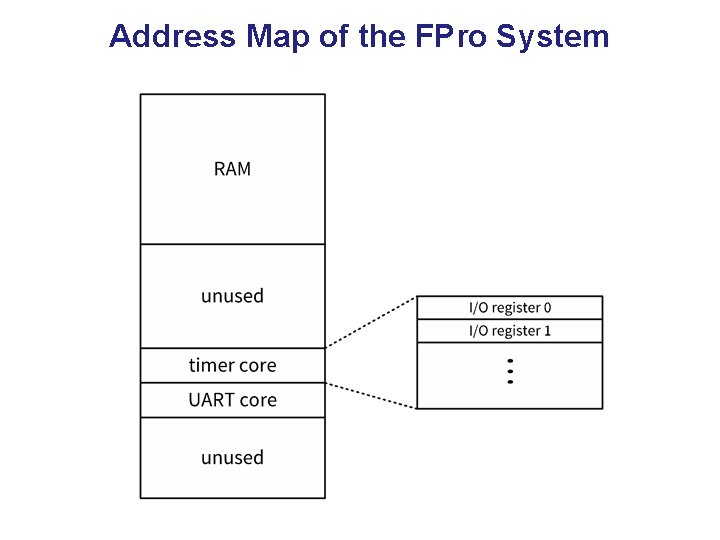

Address Map of the FPro System

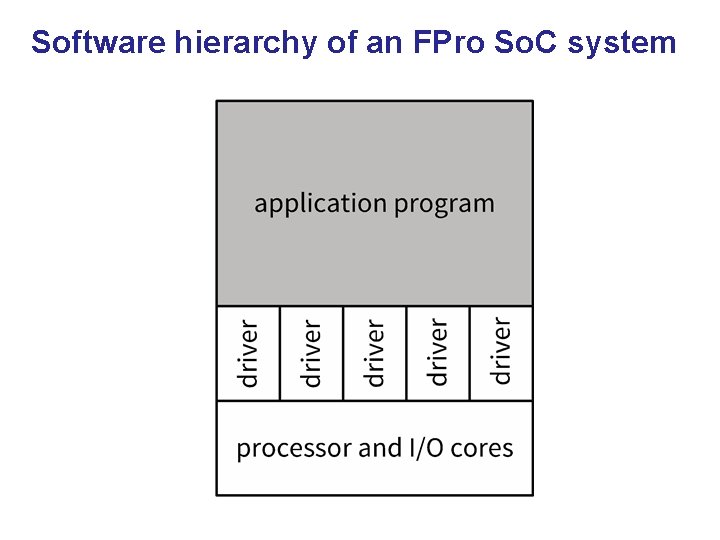

Software hierarchy of an FPro So. C system

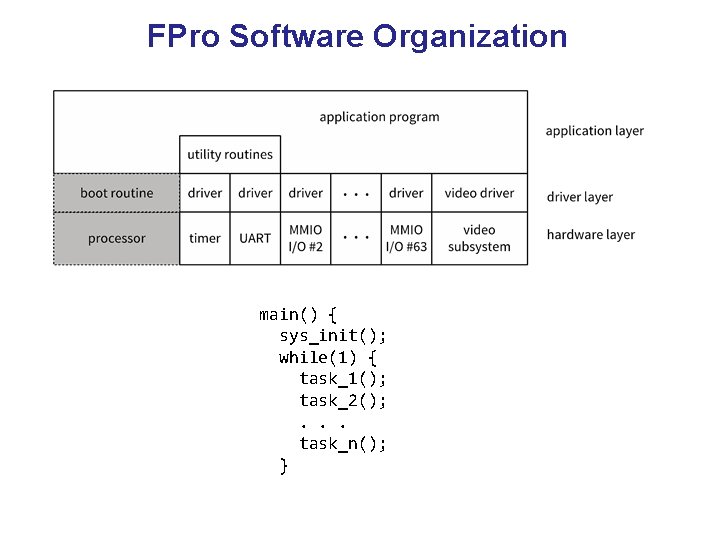

FPro Software Organization main() { sys_init(); while(1) { task_1(); task_2(); . . . task_n(); }

Platform Software Organization • A simple bare metal software scheme - No operating system • The processor boots directly into an infinite main loop • Software hierarchy of an FPro system contains § application layer § driver layer § hardware layer • A boot routine is associated with the processor. It performs the basic initialization process, such as § clearing the caches, § configuring the stack and heap segments § initializing the interrupt, and then transfers control to the main program. • The timer core and UART maintain a system time and assist displaying debug messages on the console.

Source Code of Drivers and Test Applications Companion Website of FPGA Prototyping by VHDL Examples 2 nd edition https: //academic. csuohio. edu/chu_p/rtl/fpga_mcs_vhdl. html § Source codes read_me file: readme_source_code. pdf source file: fpga_mcs_vhdl_src. zip (last updated 11/10/2017) Go to the folder: fpga_mcs_vhdl_src/cpp 13

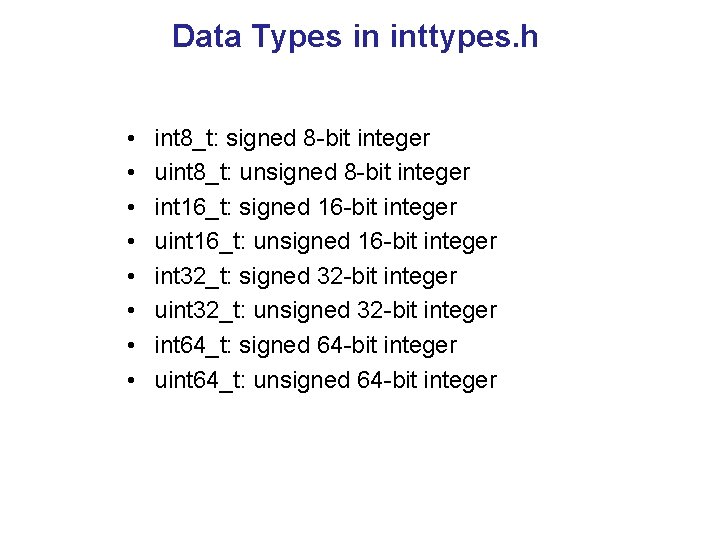

Data Types in inttypes. h • • int 8_t: signed 8 -bit integer uint 8_t: unsigned 8 -bit integer int 16_t: signed 16 -bit integer uint 16_t: unsigned 16 -bit integer int 32_t: signed 32 -bit integer uint 32_t: unsigned 32 -bit integer int 64_t: signed 64 -bit integer uint 64_t: unsigned 64 -bit integer

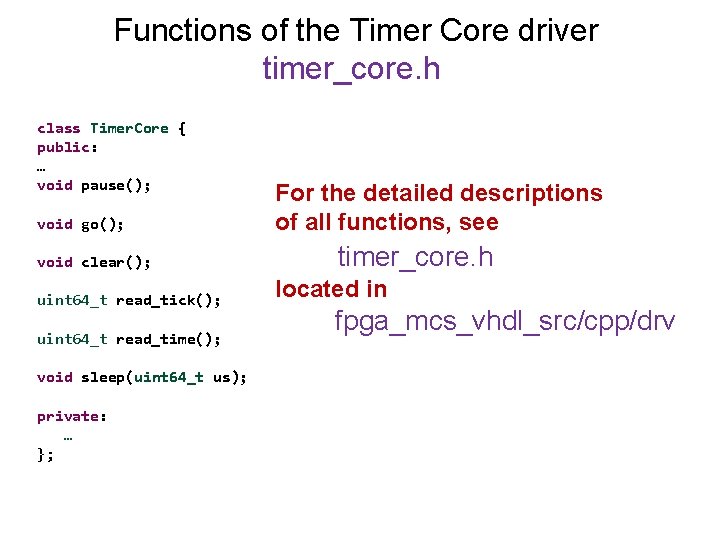

Functions of the Timer Core driver timer_core. h class Timer. Core { public: … void pause(); void go(); void clear(); uint 64_t read_tick(); uint 64_t read_time(); void sleep(uint 64_t us); private: … }; For the detailed descriptions of all functions, see timer_core. h located in fpga_mcs_vhdl_src/cpp/drv

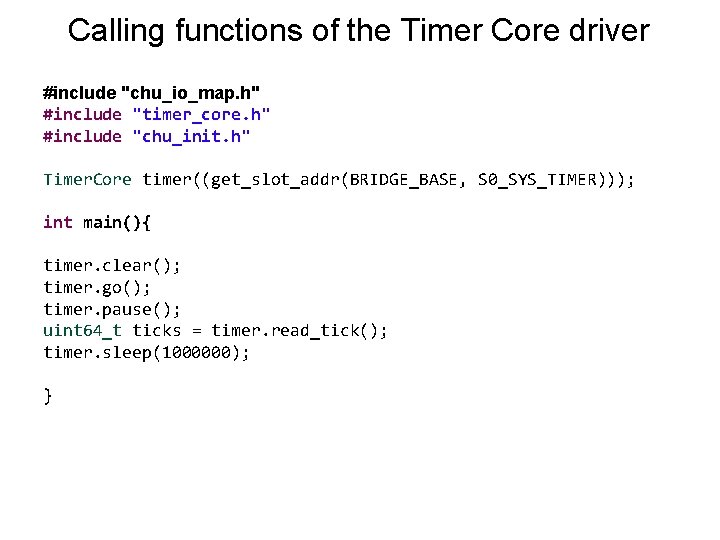

Calling functions of the Timer Core driver #include "chu_io_map. h" #include "timer_core. h" #include "chu_init. h" Timer. Core timer((get_slot_addr(BRIDGE_BASE, S 0_SYS_TIMER))); int main(){ timer. clear(); timer. go(); timer. pause(); uint 64_t ticks = timer. read_tick(); timer. sleep(1000000); }

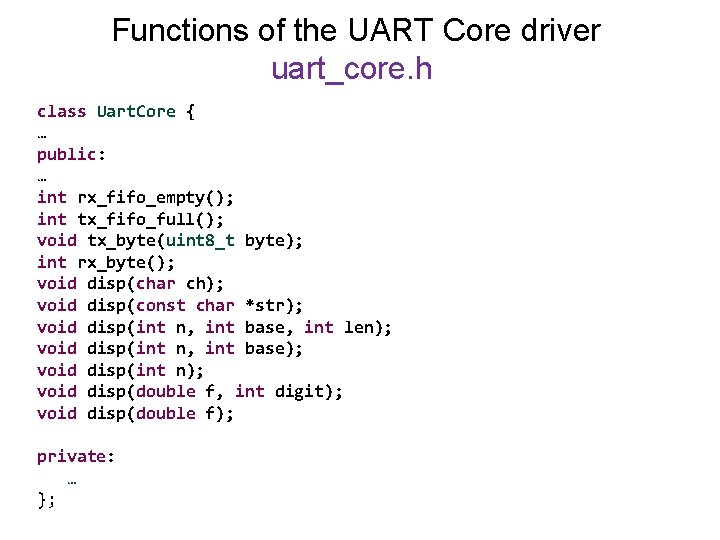

Functions of the UART Core driver uart_core. h class Uart. Core { … public: … int rx_fifo_empty(); int tx_fifo_full(); void tx_byte(uint 8_t byte); int rx_byte(); void disp(char ch); void disp(const char *str); void disp(int n, int base, int len); void disp(int n, int base); void disp(int n); void disp(double f, int digit); void disp(double f); private: … };

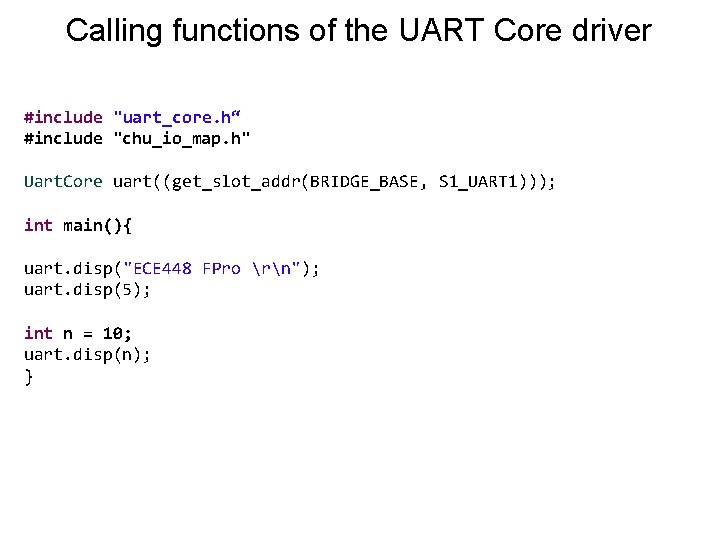

Calling functions of the UART Core driver #include "uart_core. h“ #include "chu_io_map. h" Uart. Core uart((get_slot_addr(BRIDGE_BASE, S 1_UART 1))); int main(){ uart. disp("ECE 448 FPro rn"); uart. disp(5); int n = 10; uart. disp(n); }

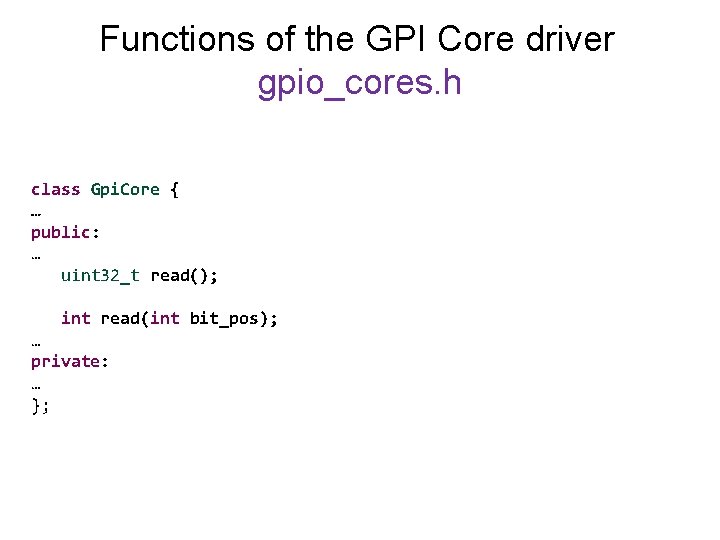

Functions of the GPI Core driver gpio_cores. h class Gpi. Core { … public: … uint 32_t read(); int read(int bit_pos); … private: … };

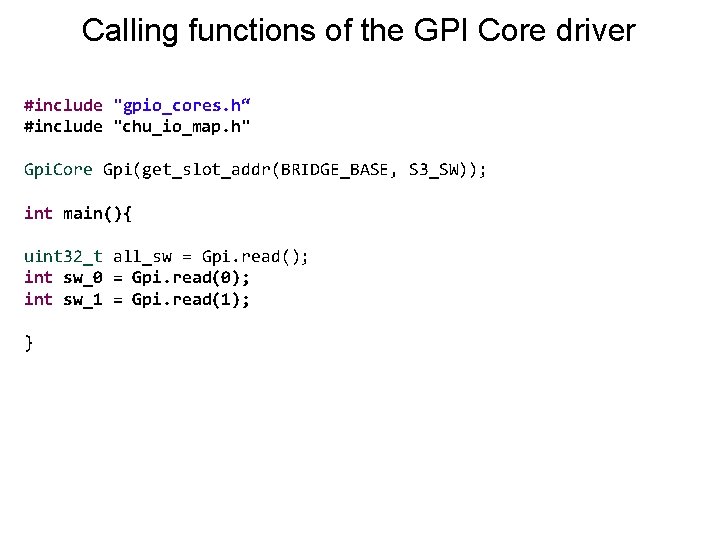

Calling functions of the GPI Core driver #include "gpio_cores. h“ #include "chu_io_map. h" Gpi. Core Gpi(get_slot_addr(BRIDGE_BASE, S 3_SW)); int main(){ uint 32_t all_sw = Gpi. read(); int sw_0 = Gpi. read(0); int sw_1 = Gpi. read(1); }

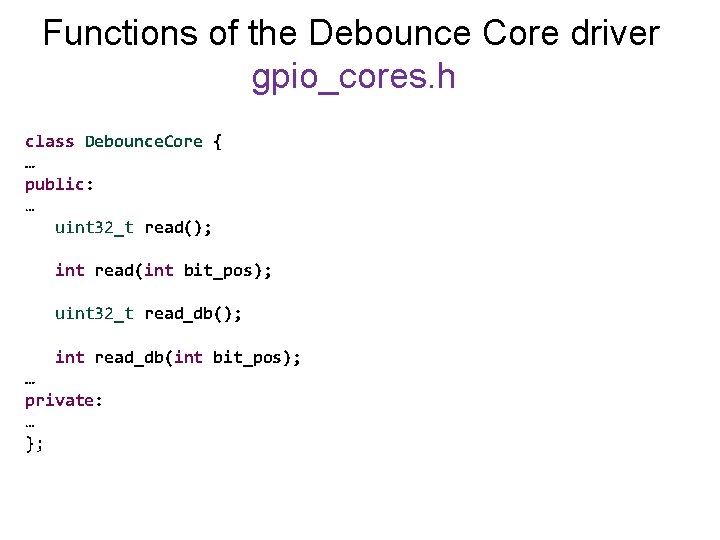

Functions of the Debounce Core driver gpio_cores. h class Debounce. Core { … public: … uint 32_t read(); int read(int bit_pos); uint 32_t read_db(); int read_db(int bit_pos); … private: … };

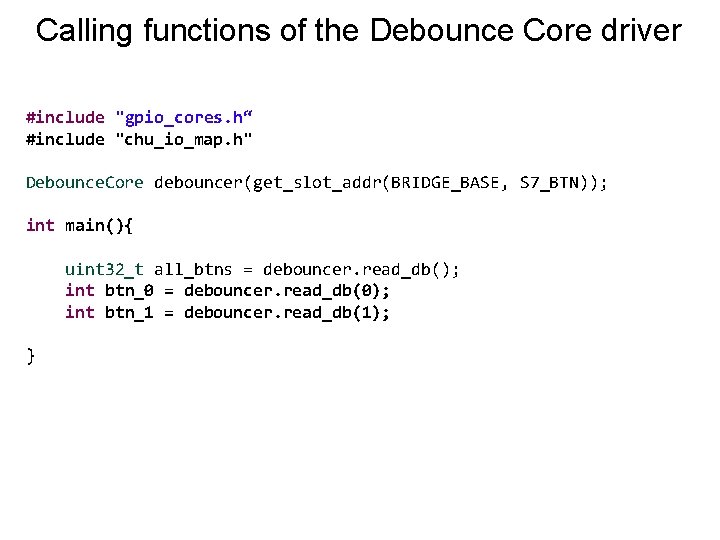

Calling functions of the Debounce Core driver #include "gpio_cores. h“ #include "chu_io_map. h" Debounce. Core debouncer(get_slot_addr(BRIDGE_BASE, S 7_BTN)); int main(){ uint 32_t all_btns = debouncer. read_db(); int btn_0 = debouncer. read_db(0); int btn_1 = debouncer. read_db(1); }

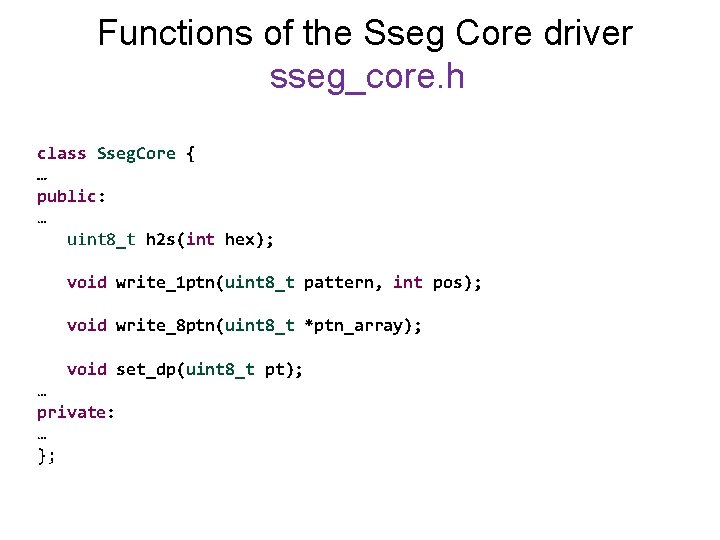

Functions of the Sseg Core driver sseg_core. h class Sseg. Core { … public: … uint 8_t h 2 s(int hex); void write_1 ptn(uint 8_t pattern, int pos); void write_8 ptn(uint 8_t *ptn_array); void set_dp(uint 8_t pt); … private: … };

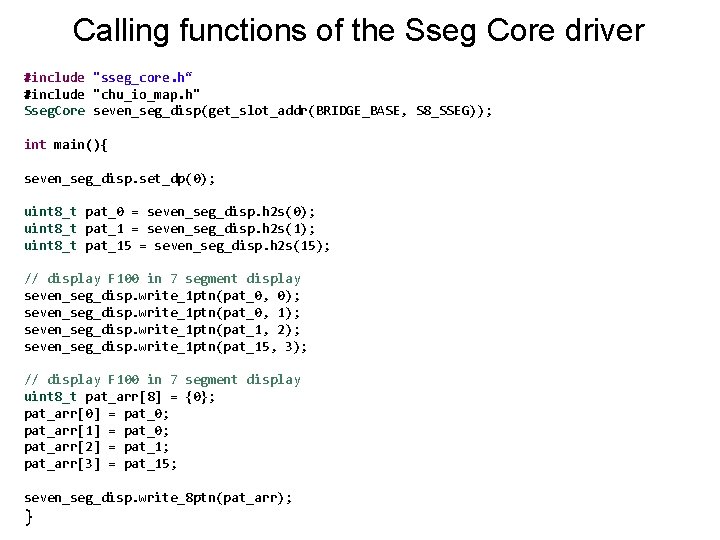

Calling functions of the Sseg Core driver #include "sseg_core. h“ #include "chu_io_map. h" Sseg. Core seven_seg_disp(get_slot_addr(BRIDGE_BASE, S 8_SSEG)); int main(){ seven_seg_disp. set_dp(0); uint 8_t pat_0 = seven_seg_disp. h 2 s(0); uint 8_t pat_1 = seven_seg_disp. h 2 s(1); uint 8_t pat_15 = seven_seg_disp. h 2 s(15); // display F 100 in 7 segment display seven_seg_disp. write_1 ptn(pat_0, 0); seven_seg_disp. write_1 ptn(pat_0, 1); seven_seg_disp. write_1 ptn(pat_1, 2); seven_seg_disp. write_1 ptn(pat_15, 3); // display F 100 in 7 segment display uint 8_t pat_arr[8] = {0}; pat_arr[0] = pat_0; pat_arr[1] = pat_0; pat_arr[2] = pat_1; pat_arr[3] = pat_15; seven_seg_disp. write_8 ptn(pat_arr); }

Part 3 Introduction to Lab 4 Assignment ECE 448 – FPGA and ASIC Design with VHDL

General Description 1. Sorting in software (C/C++) using Micro. Blaze 2. Sorting using a hardware accelerator written in RTL VHDL 3. Comparison of the execution times for different number of elements to sort from 29 to 214 (powers of two only) 26

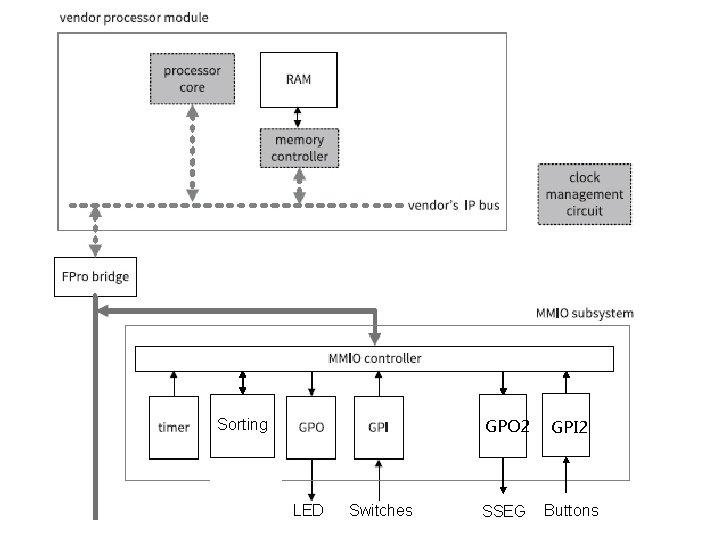

Sorting LED Switches GPO 2 GPI 2 SSEG Buttons

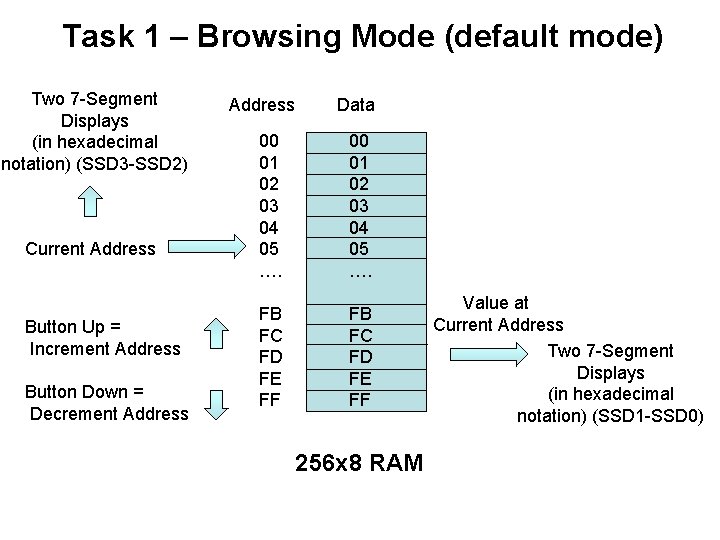

Task 1 – Browsing Mode (default mode) Two 7 -Segment Displays (in hexadecimal notation) (SSD 3 -SSD 2) Current Address Button Up = Increment Address Button Down = Decrement Address Data 00 01 02 03 04 05 …. FB FC FD FE FF 256 x 8 RAM Value at Current Address Two 7 -Segment Displays (in hexadecimal notation) (SSD 1 -SSD 0)

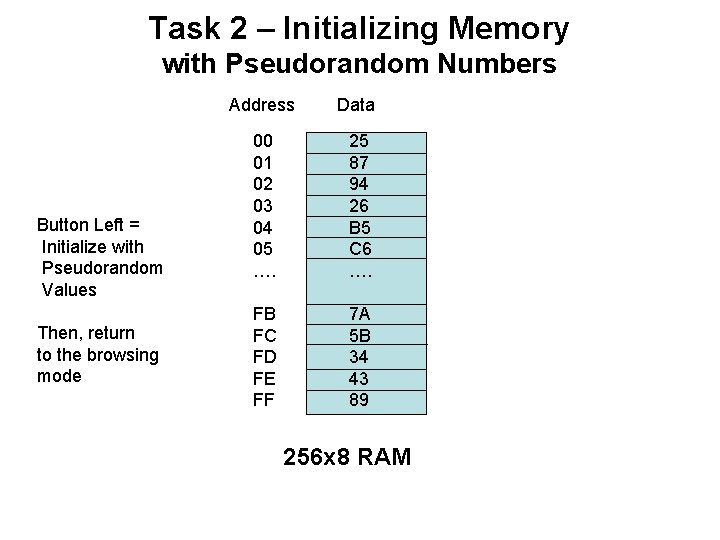

Task 2 – Initializing Memory with Pseudorandom Numbers Button Left = Initialize with Pseudorandom Values Then, return to the browsing mode Address Data 00 01 02 03 04 05 …. 25 87 94 26 B 5 C 6 …. FB FC FD FE FF 7 A 5 B 34 43 89 256 x 8 RAM

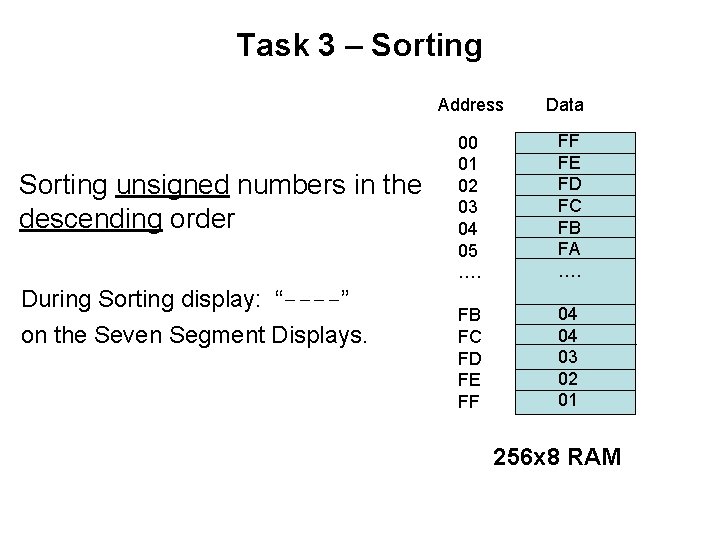

Task 3 – Sorting unsigned numbers in the descending order During Sorting display: “----” on the Seven Segment Displays. Address Data 00 01 02 03 04 05 …. FF FE FD FC FB FA …. FB FC FD FE FF 04 04 03 02 01 256 x 8 RAM

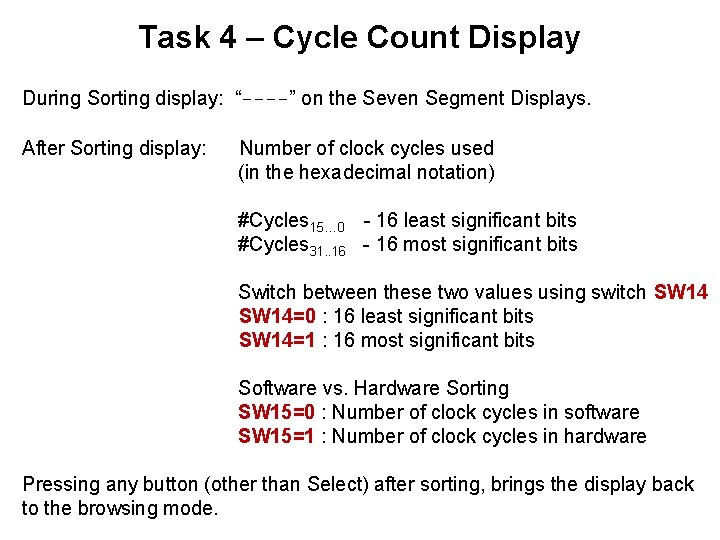

Task 4 – Cycle Count Display During Sorting display: “----” on the Seven Segment Displays. After Sorting display: Number of clock cycles used (in the hexadecimal notation) #Cycles 15… 0 - 16 least significant bits #Cycles 31. . 16 - 16 most significant bits Switch between these two values using switch SW 14=0 : 16 least significant bits SW 14=1 : 16 most significant bits Software vs. Hardware Sorting SW 15=0 : Number of clock cycles in software SW 15=1 : Number of clock cycles in hardware Pressing any button (other than Select) after sorting, brings the display back to the browsing mode.

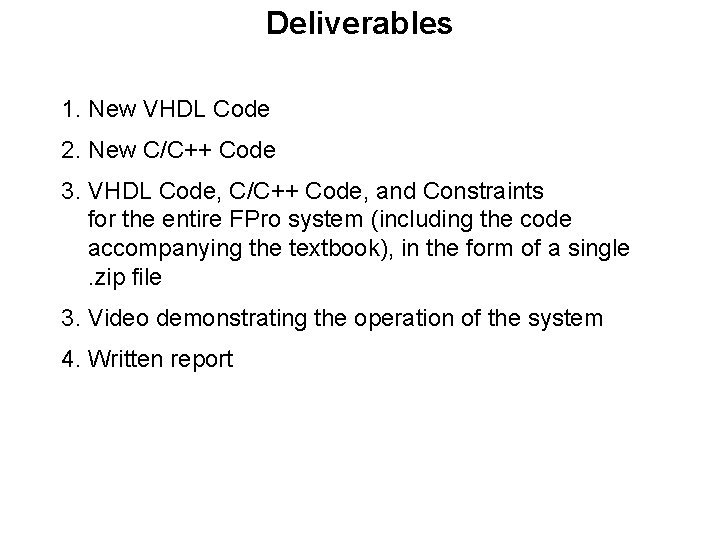

Deliverables 1. New VHDL Code 2. New C/C++ Code 3. VHDL Code, C/C++ Code, and Constraints for the entire FPro system (including the code accompanying the textbook), in the form of a single. zip file 3. Video demonstrating the operation of the system 4. Written report

Report File 1. List of fully completed tasks 2. List of partially completed tasks, including the description of any incorrect functionality 3. Tables and graphs showing for each number of memory elements between 29 and 214 (powers of 2 only) • Execution time in software (clock cycles & ms) • Execution time in hardware (clock cycles & ms) • Ratio of the execution time in software vs. hardware • Resource utilization (#Slices, #LUTs, #FFs, #BRAMs) 4. Conclusions

Contest for the Fastest Implementation of Sorting Bonus points will be awarded to students who perform sorting (correctly) using the smallest number of clock cycles in hardware and/or software Possible optimizations: • Faster sorting algorithms in software • Efficient C implementation • Faster sorting algorithms in hardware • Efficient VHDL implementation

Part 4 Hands-on session on developing an example design with an FPro System ECE 448 – FPGA and ASIC Design with VHDL

Known Problems None of the paths used by Xilinx SDK is allowed to contain spaces In particular, the workspace folder has to be selected in such a way that its path does not contain spaces.

Part 5 Lab 4 Exercise 1 ECE 448 – FPGA and ASIC Design with VHDL

16 -bit Binary Up-Down Counter Design, implement, verify, and test using the FPro So. C on Basys 3 board a 16 -bit Binary Up/Down Counter in C/C++ Your code should make use of : • Timer core for timing • GPI core for reading switches • Debouncer core for reading buttons • Sseg core to control seven-segment displays • UART core to send debug information to host computer.

Functions of Buttons • BTNC – toggling between addition and subtraction • BTNU – adding/subtracting 1 • BTND – adding/subtracting 5 • BTNL – adding/subtracting 10 • BTNR – adding/subtracting 20. After reset, the counter should be set to “ 0000”, and the mode to addition. SW 0 should be used to reset counter value to 0.

Double Display After any of the buttons representing an addition/subtraction amount (i. e. , BTNU, BTND, BTNL, or BTNR) is pressed, the corresponding amount, represented in the hexadecimal notation, (i. e. , 0001, 0005, 000 A, 0014) should be displayed for 1 second, and then, the seven segment displays should show an updated value of the counter.

Recommended Starting Point: Sampler FPro System slot #0 slot #1 slot #2 slot #3 slot #13 ADSR 41

Major Tasks 1. Synthesize and implement the FPro So. C system using Xilinx Vivado. 2. Generate the bitstream. 3. Write C/C++ code for the FPro system to implement the 16 -bit Binary Up/Down Counter. 4. Generate the. elf file and program the FPGA. 5. Verify experimentally the correct operation of your circuit.

Deliverables 1. File main. cpp containing any new functions written in C/C++, including main(). 2. A short video demonstrating the required functionality realized using Basys 3.

- Slides: 43