ECE 448 Lab 1 Developing Effective Testbenches ECE

ECE 448 Lab 1 Developing Effective Testbenches ECE 448 – FPGA and ASIC Design with VHDL George Mason University

Agenda for today Part 1: Lab Rules Part 2: Installation and Setup of Tools Part 3: Refresher on Testbenches Part 4: Introduction to Lab 1 Assignment Part 5: Lab 1 Exercise Part 6: Hands-on Session: Vivado Simulator 2

Part 1 Lab Rules ECE 448 – FPGA and ASIC Design with VHDL 3

Lab Rules https: //ece. gmu. edu/coursewebpages/ECE 448/S 20/#Rules ECE 448 – FPGA and ASIC Design with VHDL 4

Part 2 Installation and Setup of Tools ECE 448 – FPGA and ASIC Design with VHDL 5

Installation and Setup of Tools https: //ece. gmu. edu/tutorials-and-lab-manuals • Xilinx Vivado Installation Instructions • Model. Sim-Intel FPGA Installation and Integration with Vivado Guide ECE 448 – FPGA and ASIC Design with VHDL 6

Part 3 Refresher on VHDL Testbenches ECE 448 – FPGA and ASIC Design with VHDL 7

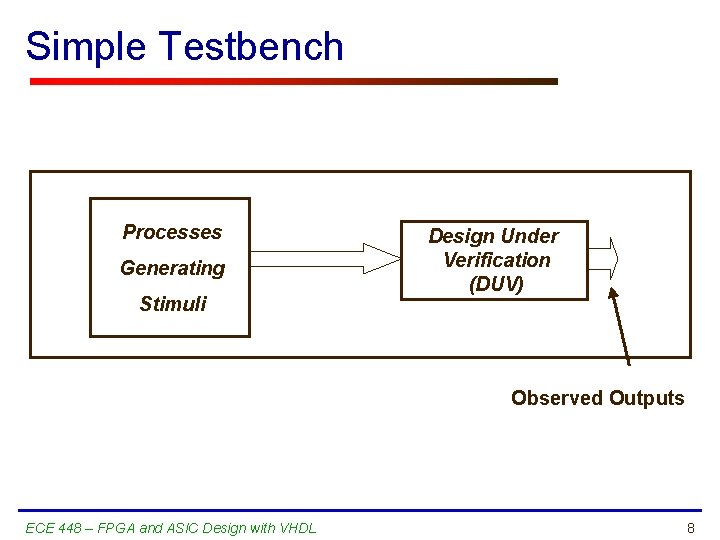

Simple Testbench Processes Generating Stimuli Design Under Verification (DUV) Observed Outputs ECE 448 – FPGA and ASIC Design with VHDL 8

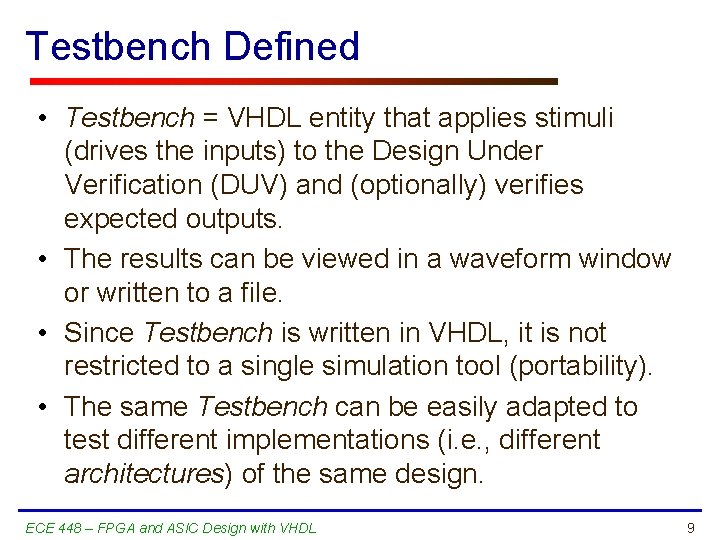

Testbench Defined • Testbench = VHDL entity that applies stimuli (drives the inputs) to the Design Under Verification (DUV) and (optionally) verifies expected outputs. • The results can be viewed in a waveform window or written to a file. • Since Testbench is written in VHDL, it is not restricted to a single simulation tool (portability). • The same Testbench can be easily adapted to test different implementations (i. e. , different architectures) of the same design. ECE 448 – FPGA and ASIC Design with VHDL 9

Possible sources of expected results used for comparison Testbench VHDL Design actual results = ? Representative Manual Calculations Inputs or expected results Reference Software Implementation (C, Java, Matlab ) ECE 448 – FPGA and ASIC Design with VHDL 10

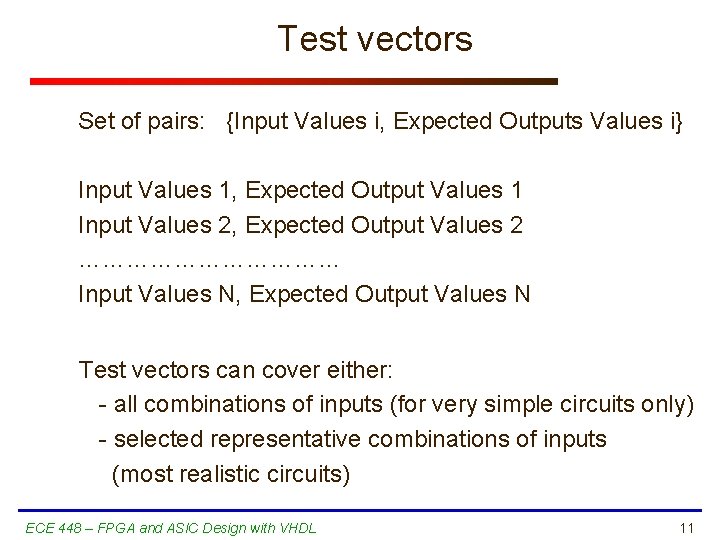

Test vectors Set of pairs: {Input Values i, Expected Outputs Values i} Input Values 1, Expected Output Values 1 Input Values 2, Expected Output Values 2 ……………… Input Values N, Expected Output Values N Test vectors can cover either: - all combinations of inputs (for very simple circuits only) - selected representative combinations of inputs (most realistic circuits) ECE 448 – FPGA and ASIC Design with VHDL 11

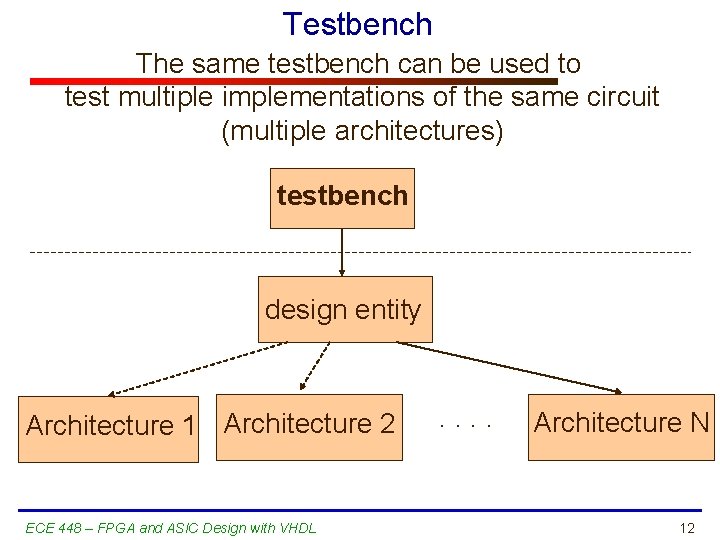

Testbench The same testbench can be used to test multiple implementations of the same circuit (multiple architectures) testbench design entity Architecture 1 Architecture 2 ECE 448 – FPGA and ASIC Design with VHDL . . Architecture N 12

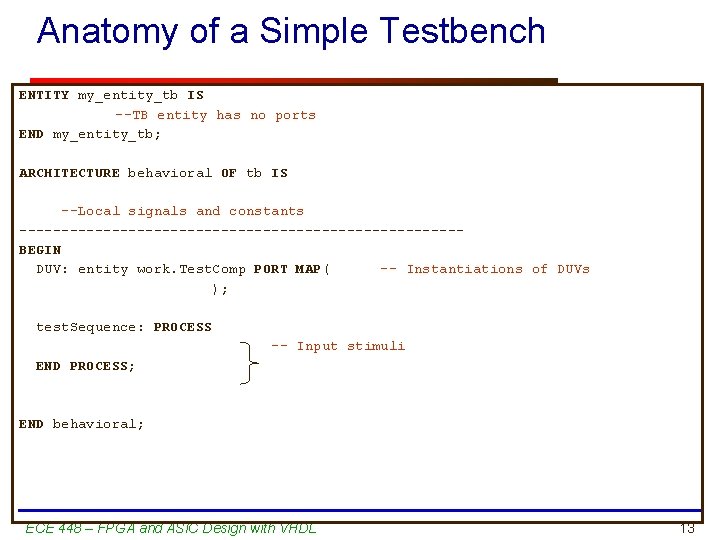

Anatomy of a Simple Testbench ENTITY my_entity_tb IS --TB entity has no ports END my_entity_tb; ARCHITECTURE behavioral OF tb IS --Local signals and constants --------------------------BEGIN DUV: entity work. Test. Comp PORT MAP( -- Instantiations of DUVs ); test. Sequence: PROCESS -- Input stimuli END PROCESS; END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 13

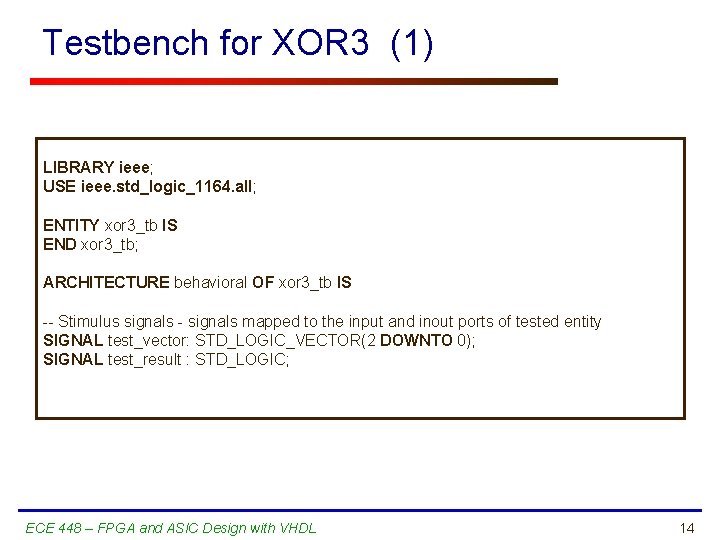

Testbench for XOR 3 (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY xor 3_tb IS END xor 3_tb; ARCHITECTURE behavioral OF xor 3_tb IS -- Stimulus signals - signals mapped to the input and inout ports of tested entity SIGNAL test_vector: STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL test_result : STD_LOGIC; ECE 448 – FPGA and ASIC Design with VHDL 14

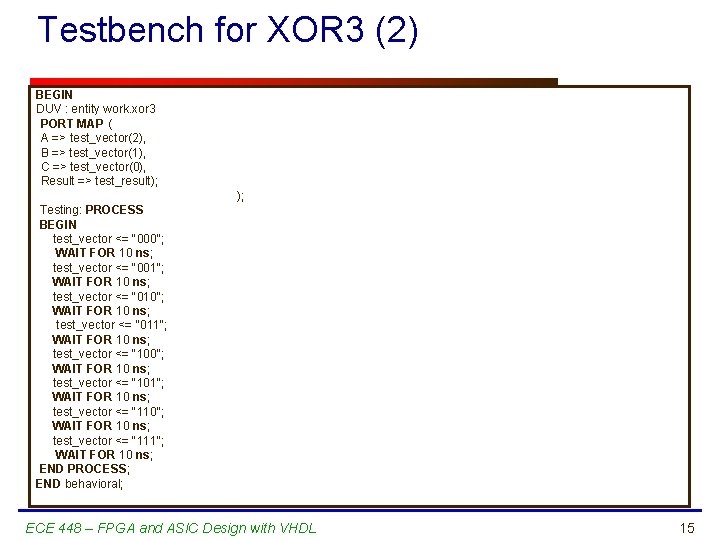

Testbench for XOR 3 (2) BEGIN DUV : entity work. xor 3 PORT MAP ( A => test_vector(2), B => test_vector(1), C => test_vector(0), Result => test_result); ); Testing: PROCESS BEGIN test_vector <= "000"; WAIT FOR 10 ns; test_vector <= "001"; WAIT FOR 10 ns; test_vector <= "010"; WAIT FOR 10 ns; test_vector <= "011"; WAIT FOR 10 ns; test_vector <= "100"; WAIT FOR 10 ns; test_vector <= "101"; WAIT FOR 10 ns; test_vector <= "110"; WAIT FOR 10 ns; test_vector <= "111"; WAIT FOR 10 ns; END PROCESS; END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 15

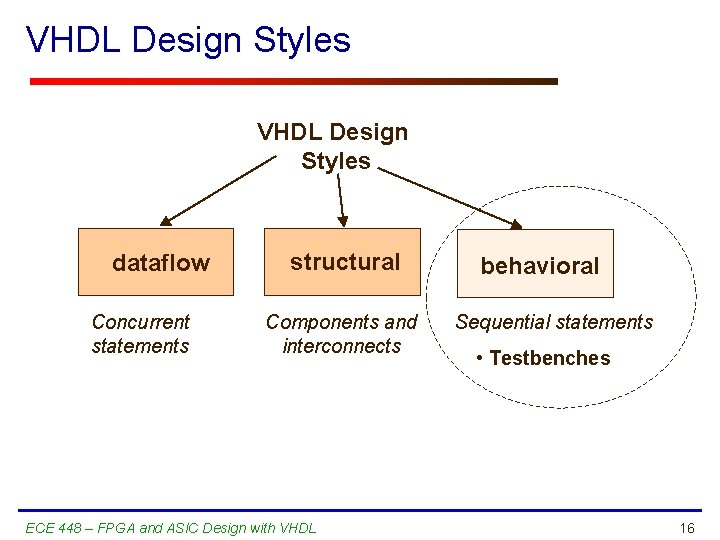

VHDL Design Styles dataflow Concurrent statements structural Components and interconnects ECE 448 – FPGA and ASIC Design with VHDL behavioral Sequential statements • Testbenches 16

Process without Sensitivity List and its use in Testbenches ECE 448 – FPGA and ASIC Design with VHDL 17

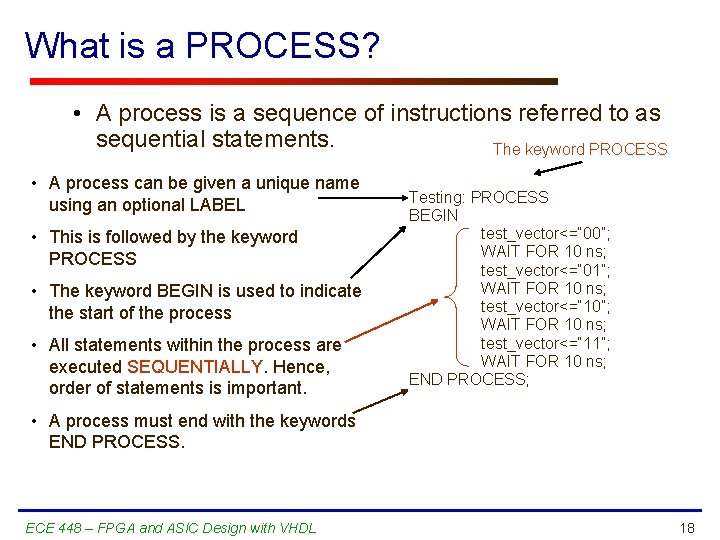

What is a PROCESS? • A process is a sequence of instructions referred to as sequential statements. The keyword PROCESS • A process can be given a unique name using an optional LABEL • This is followed by the keyword PROCESS • The keyword BEGIN is used to indicate the start of the process • All statements within the process are executed SEQUENTIALLY. Hence, order of statements is important. Testing: PROCESS BEGIN test_vector<=“ 00”; WAIT FOR 10 ns; test_vector<=“ 01”; WAIT FOR 10 ns; test_vector<=“ 10”; WAIT FOR 10 ns; test_vector<=“ 11”; WAIT FOR 10 ns; END PROCESS; • A process must end with the keywords END PROCESS. ECE 448 – FPGA and ASIC Design with VHDL 18

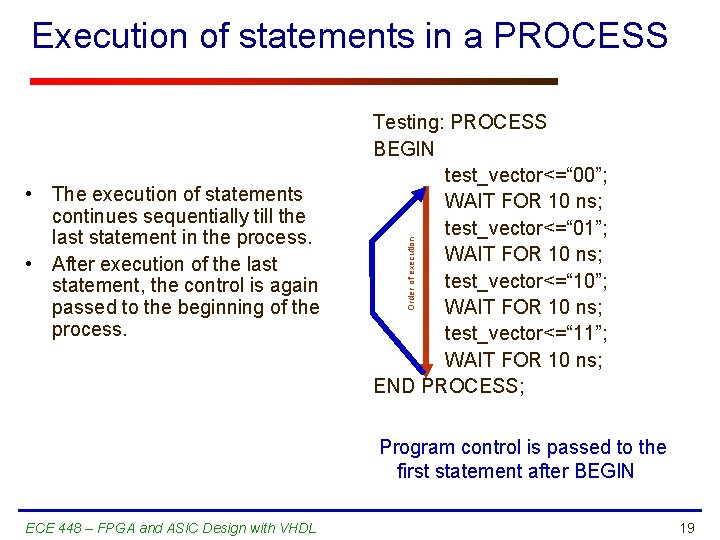

Execution of statements in a PROCESS Order of execution • The execution of statements continues sequentially till the last statement in the process. • After execution of the last statement, the control is again passed to the beginning of the process. Testing: PROCESS BEGIN test_vector<=“ 00”; WAIT FOR 10 ns; test_vector<=“ 01”; WAIT FOR 10 ns; test_vector<=“ 10”; WAIT FOR 10 ns; test_vector<=“ 11”; WAIT FOR 10 ns; END PROCESS; Program control is passed to the first statement after BEGIN ECE 448 – FPGA and ASIC Design with VHDL 19

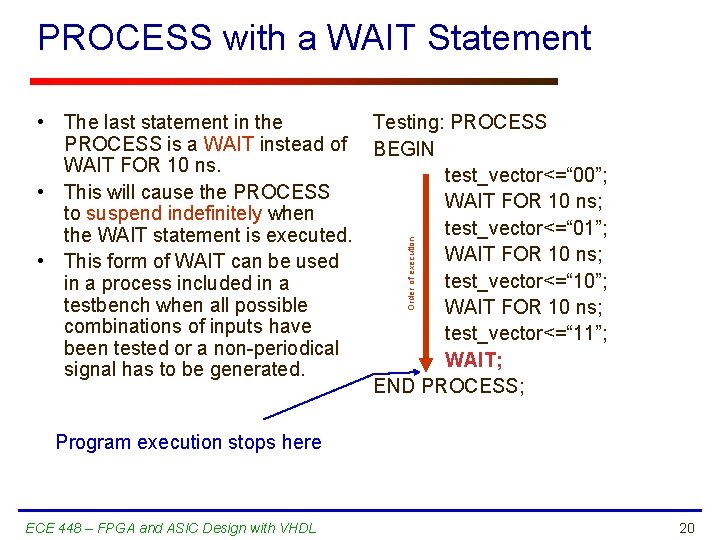

PROCESS with a WAIT Statement Order of execution • The last statement in the Testing: PROCESS is a WAIT instead of BEGIN WAIT FOR 10 ns. test_vector<=“ 00”; • This will cause the PROCESS WAIT FOR 10 ns; to suspend indefinitely when test_vector<=“ 01”; the WAIT statement is executed. WAIT FOR 10 ns; • This form of WAIT can be used test_vector<=“ 10”; in a process included in a testbench when all possible WAIT FOR 10 ns; combinations of inputs have test_vector<=“ 11”; been tested or a non-periodical WAIT; signal has to be generated. END PROCESS; Program execution stops here ECE 448 – FPGA and ASIC Design with VHDL 20

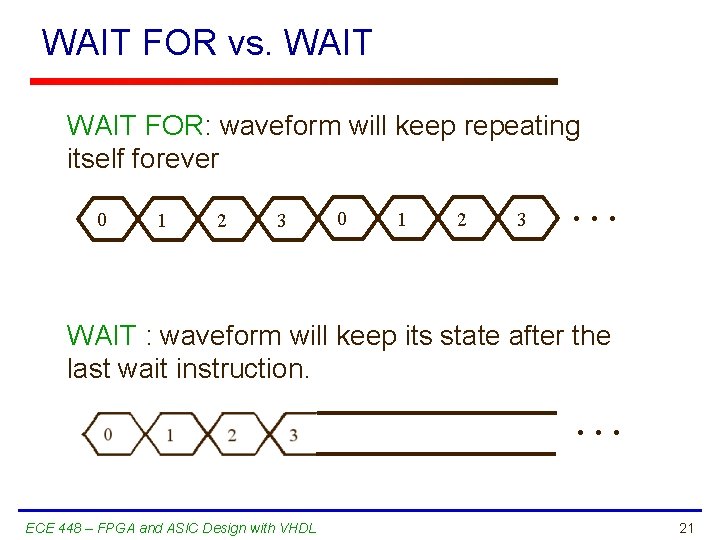

WAIT FOR vs. WAIT FOR: waveform will keep repeating itself forever 0 1 2 3 … WAIT : waveform will keep its state after the last wait instruction. … ECE 448 – FPGA and ASIC Design with VHDL 21

Specifying time in VHDL ECE 448 – FPGA and ASIC Design with VHDL 22

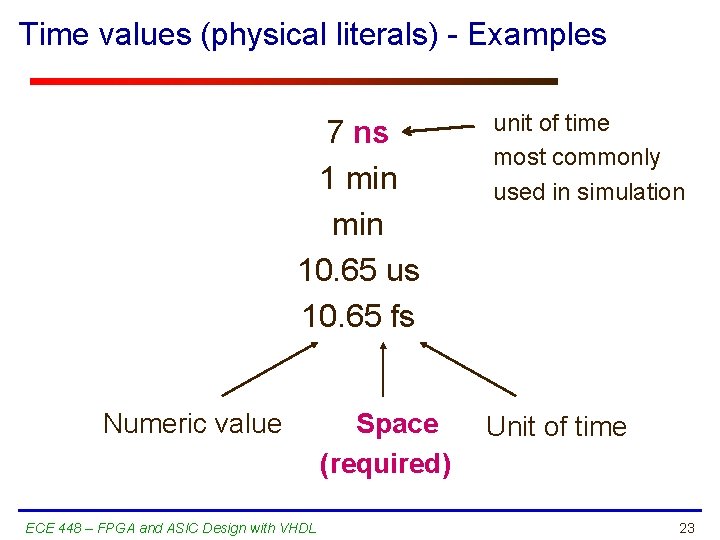

Time values (physical literals) - Examples 7 ns 1 min 10. 65 us 10. 65 fs Numeric value ECE 448 – FPGA and ASIC Design with VHDL Space (required) unit of time most commonly used in simulation Unit of time 23

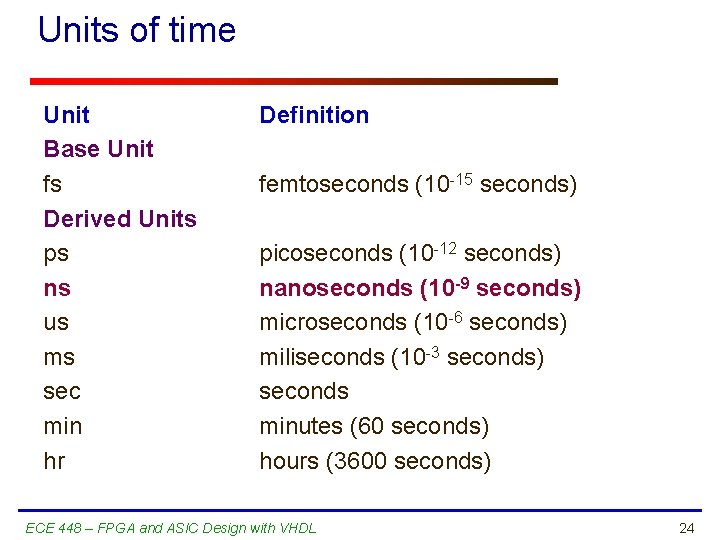

Units of time Unit Base Unit fs Derived Units ps ns us ms sec min hr Definition femtoseconds (10 -15 seconds) picoseconds (10 -12 seconds) nanoseconds (10 -9 seconds) microseconds (10 -6 seconds) miliseconds (10 -3 seconds) seconds minutes (60 seconds) hours (3600 seconds) ECE 448 – FPGA and ASIC Design with VHDL 24

Simple Testbenches ECE 448 – FPGA and ASIC Design with VHDL 25

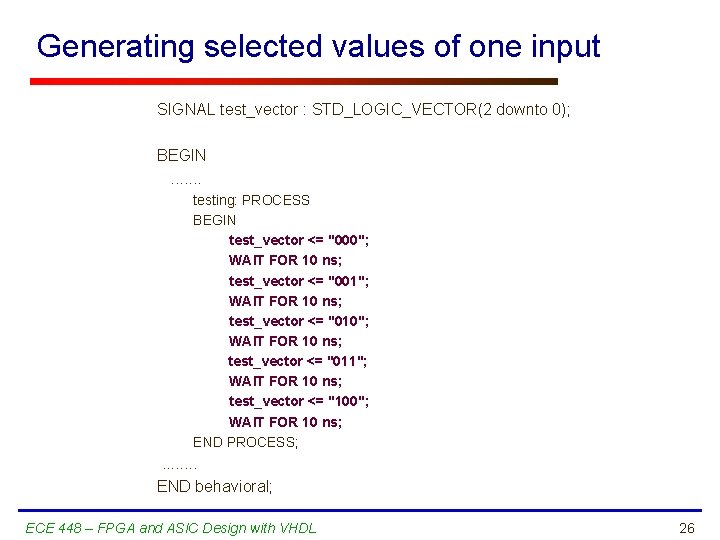

Generating selected values of one input SIGNAL test_vector : STD_LOGIC_VECTOR(2 downto 0); BEGIN. . . . testing: PROCESS BEGIN test_vector <= "000"; WAIT FOR 10 ns; test_vector <= "001"; WAIT FOR 10 ns; test_vector <= "010"; WAIT FOR 10 ns; test_vector <= "011"; WAIT FOR 10 ns; test_vector <= "100"; WAIT FOR 10 ns; END PROCESS; . . . . END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 26

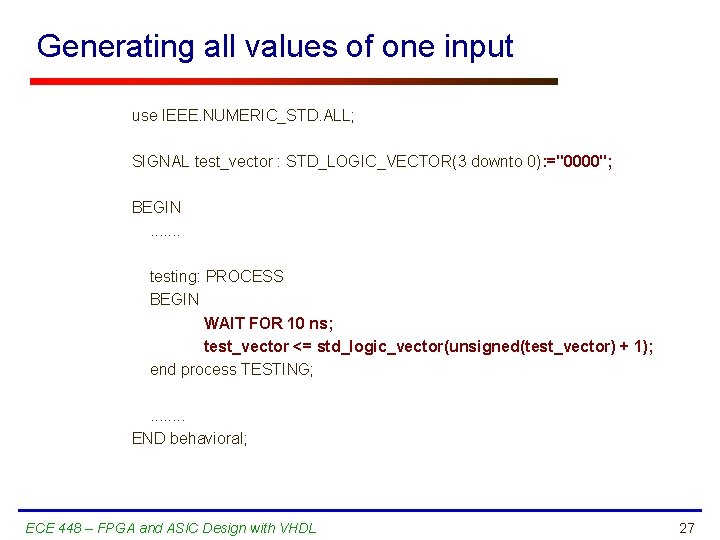

Generating all values of one input use IEEE. NUMERIC_STD. ALL; SIGNAL test_vector : STD_LOGIC_VECTOR(3 downto 0): ="0000"; BEGIN. . . . testing: PROCESS BEGIN WAIT FOR 10 ns; test_vector <= std_logic_vector(unsigned(test_vector) + 1); end process TESTING; . . . . END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 27

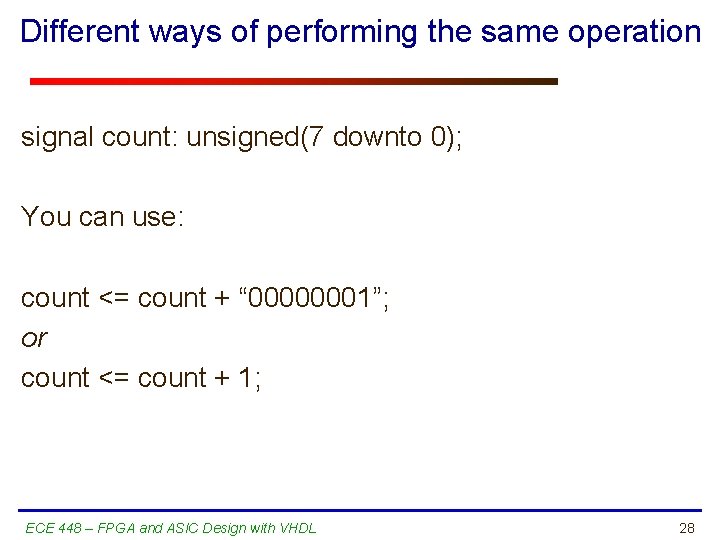

Different ways of performing the same operation signal count: unsigned(7 downto 0); You can use: count <= count + “ 00000001”; or count <= count + 1; ECE 448 – FPGA and ASIC Design with VHDL 28

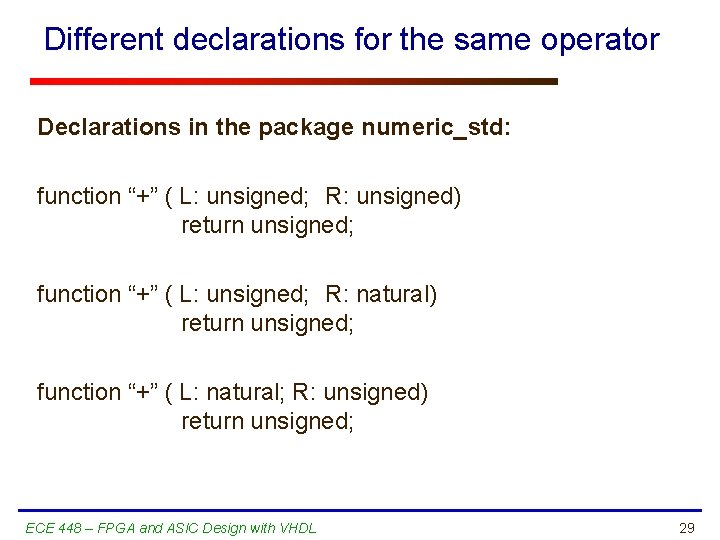

Different declarations for the same operator Declarations in the package numeric_std: function “+” ( L: unsigned; R: unsigned) return unsigned; function “+” ( L: unsigned; R: natural) return unsigned; function “+” ( L: natural; R: unsigned) return unsigned; ECE 448 – FPGA and ASIC Design with VHDL 29

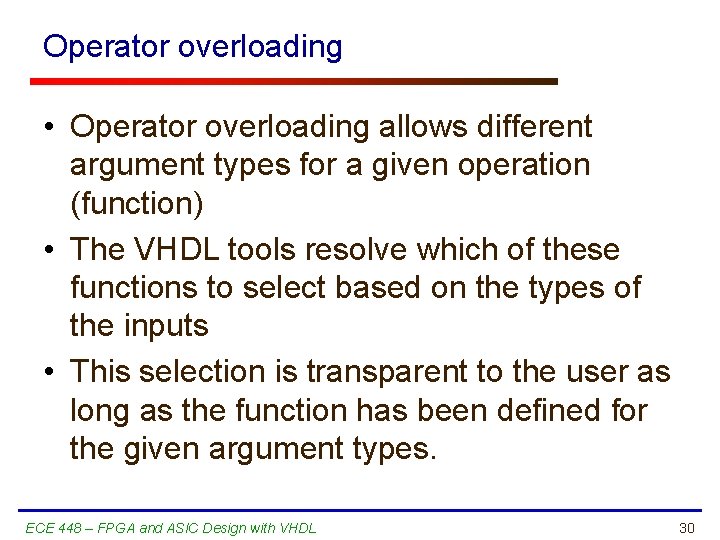

Operator overloading • Operator overloading allows different argument types for a given operation (function) • The VHDL tools resolve which of these functions to select based on the types of the inputs • This selection is transparent to the user as long as the function has been defined for the given argument types. ECE 448 – FPGA and ASIC Design with VHDL 30

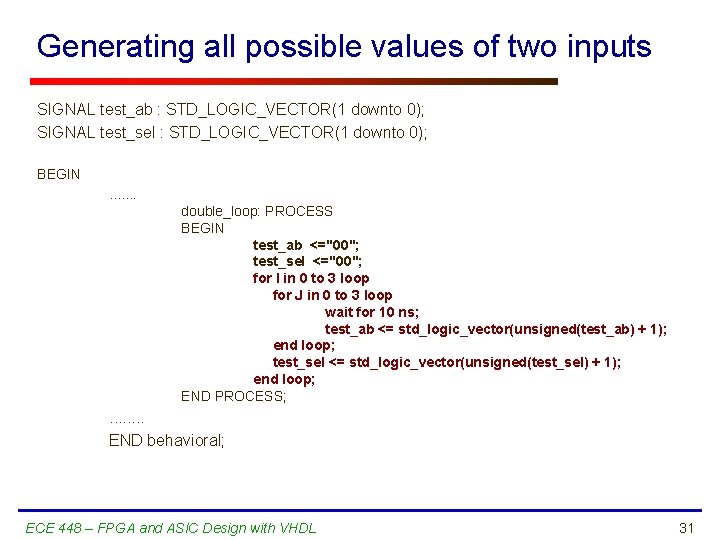

Generating all possible values of two inputs SIGNAL test_ab : STD_LOGIC_VECTOR(1 downto 0); SIGNAL test_sel : STD_LOGIC_VECTOR(1 downto 0); BEGIN. . . . double_loop: PROCESS BEGIN test_ab <="00"; test_sel <="00"; for I in 0 to 3 loop for J in 0 to 3 loop wait for 10 ns; test_ab <= std_logic_vector(unsigned(test_ab) + 1); end loop; test_sel <= std_logic_vector(unsigned(test_sel) + 1); end loop; END PROCESS; . . . . END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 31

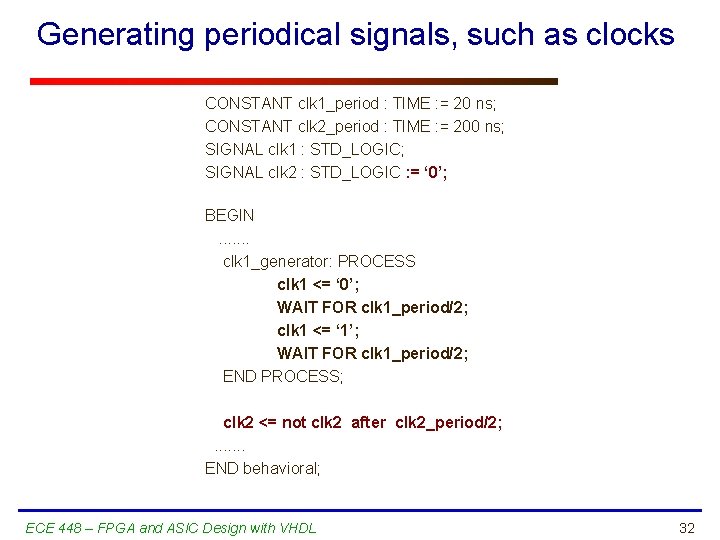

Generating periodical signals, such as clocks CONSTANT clk 1_period : TIME : = 20 ns; CONSTANT clk 2_period : TIME : = 200 ns; SIGNAL clk 1 : STD_LOGIC; SIGNAL clk 2 : STD_LOGIC : = ‘ 0’; BEGIN. . . . clk 1_generator: PROCESS clk 1 <= ‘ 0’; WAIT FOR clk 1_period/2; clk 1 <= ‘ 1’; WAIT FOR clk 1_period/2; END PROCESS; clk 2 <= not clk 2 after clk 2_period/2; . . . . END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 32

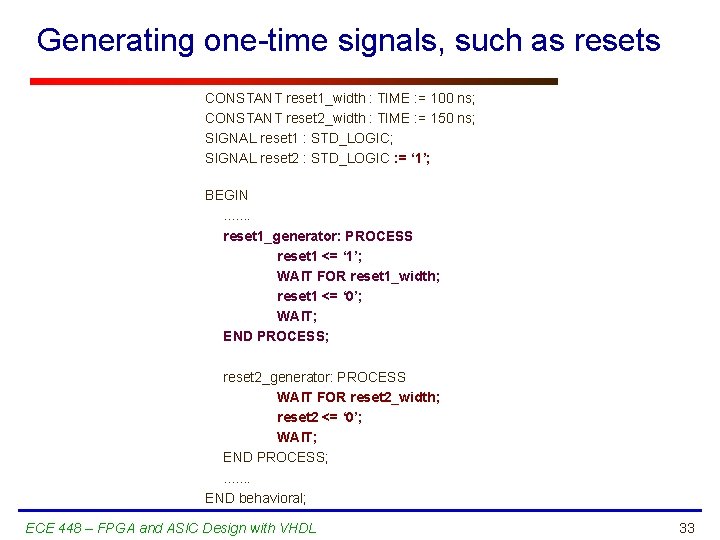

Generating one-time signals, such as resets CONSTANT reset 1_width : TIME : = 100 ns; CONSTANT reset 2_width : TIME : = 150 ns; SIGNAL reset 1 : STD_LOGIC; SIGNAL reset 2 : STD_LOGIC : = ‘ 1’; BEGIN. . . . reset 1_generator: PROCESS reset 1 <= ‘ 1’; WAIT FOR reset 1_width; reset 1 <= ‘ 0’; WAIT; END PROCESS; reset 2_generator: PROCESS WAIT FOR reset 2_width; reset 2 <= ‘ 0’; WAIT; END PROCESS; . . . . END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 33

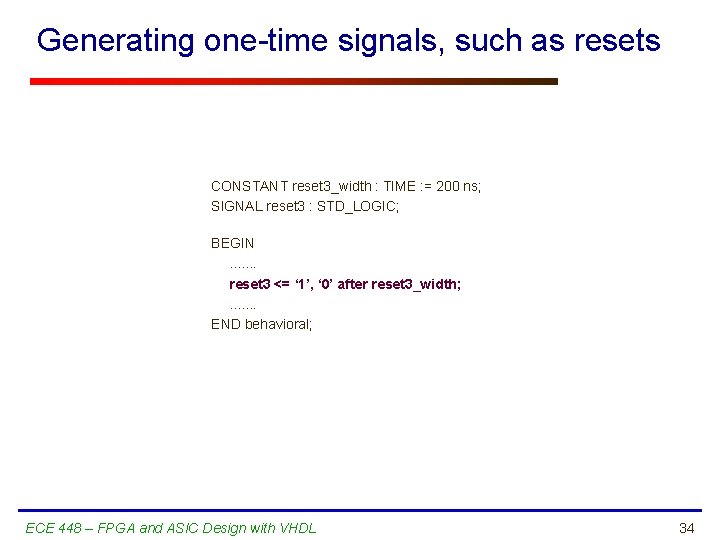

Generating one-time signals, such as resets CONSTANT reset 3_width : TIME : = 200 ns; SIGNAL reset 3 : STD_LOGIC; BEGIN. . . . reset 3 <= ‘ 1’, ‘ 0’ after reset 3_width; . . . . END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 34

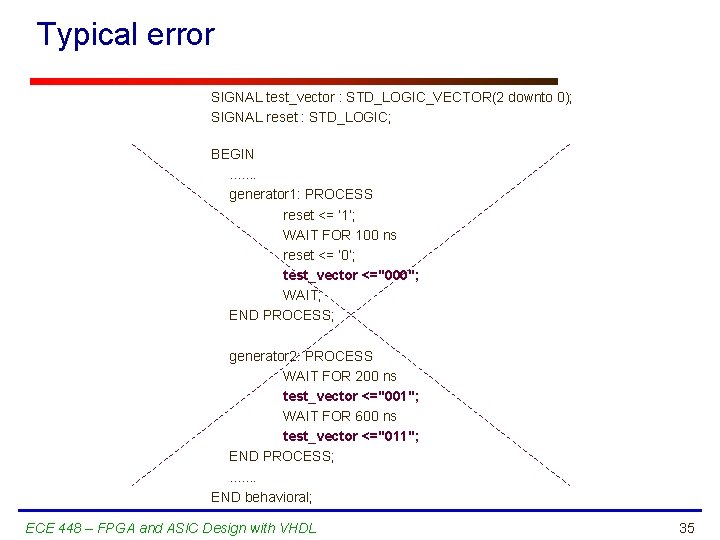

Typical error SIGNAL test_vector : STD_LOGIC_VECTOR(2 downto 0); SIGNAL reset : STD_LOGIC; BEGIN. . . . generator 1: PROCESS reset <= ‘ 1’; WAIT FOR 100 ns reset <= ‘ 0’; test_vector <="000"; WAIT; END PROCESS; generator 2: PROCESS WAIT FOR 200 ns test_vector <="001"; WAIT FOR 600 ns test_vector <="011"; END PROCESS; . . . . END behavioral; ECE 448 – FPGA and ASIC Design with VHDL 35

Asserts and Reports ECE 448 – FPGA and ASIC Design with VHDL 36

Assert is a non-synthesizable statement whose purpose is to write out messages on the screen when problems are found during simulation. Depending on the severity of the problem, The simulator is instructed to continue simulation or halt. 37

![Assert - syntax ASSERT condition [REPORT "message“] [SEVERITY severity_level ]; The message is written Assert - syntax ASSERT condition [REPORT "message“] [SEVERITY severity_level ]; The message is written](http://slidetodoc.com/presentation_image_h2/f62afd27e9deb114b1d818c8124b3139/image-38.jpg)

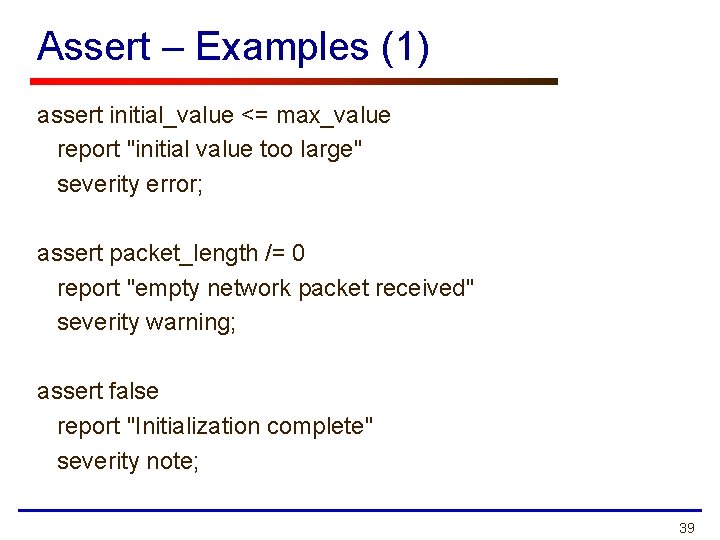

Assert - syntax ASSERT condition [REPORT "message“] [SEVERITY severity_level ]; The message is written when the condition is FALSE. Severity_level can be: Note, Warning, Error (default), or Failure. 38

Assert – Examples (1) assert initial_value <= max_value report "initial value too large" severity error; assert packet_length /= 0 report "empty network packet received" severity warning; assert false report "Initialization complete" severity note; 39

![Report - syntax REPORT "message" [SEVERITY severity_level ]; The message is always written. Severity_level Report - syntax REPORT "message" [SEVERITY severity_level ]; The message is always written. Severity_level](http://slidetodoc.com/presentation_image_h2/f62afd27e9deb114b1d818c8124b3139/image-40.jpg)

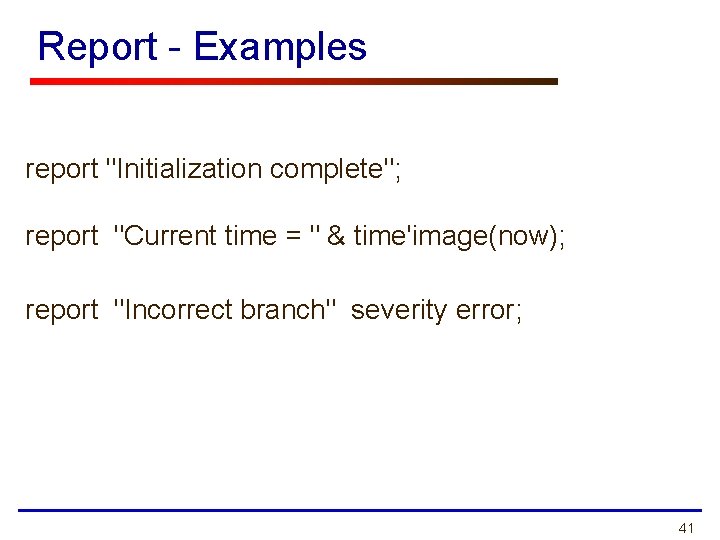

Report - syntax REPORT "message" [SEVERITY severity_level ]; The message is always written. Severity_level can be: Note, Warning, Error (default), or Failure. 40

Report - Examples report "Initialization complete"; report "Current time = " & time'image(now); report "Incorrect branch" severity error; 41

Records and Arrays of Test Vectors in Testbenches ECE 448 – FPGA and ASIC Design with VHDL

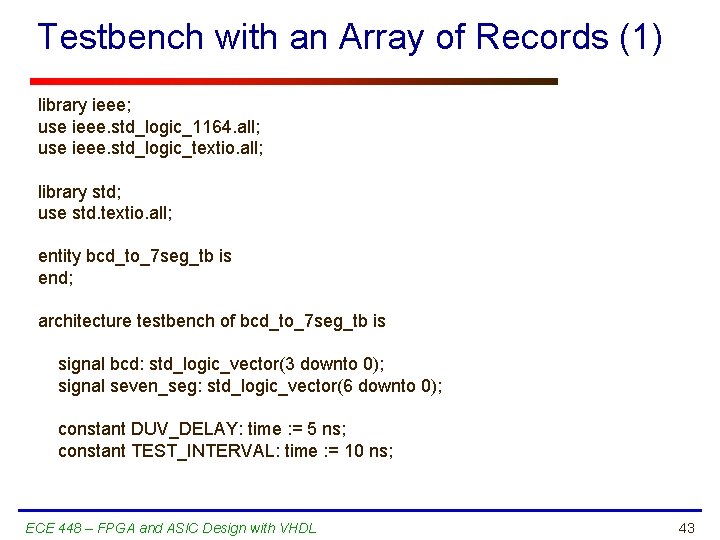

Testbench with an Array of Records (1) library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_textio. all; library std; use std. textio. all; entity bcd_to_7 seg_tb is end; architecture testbench of bcd_to_7 seg_tb is signal bcd: std_logic_vector(3 downto 0); signal seven_seg: std_logic_vector(6 downto 0); constant DUV_DELAY: time : = 5 ns; constant TEST_INTERVAL: time : = 10 ns; ECE 448 – FPGA and ASIC Design with VHDL 43

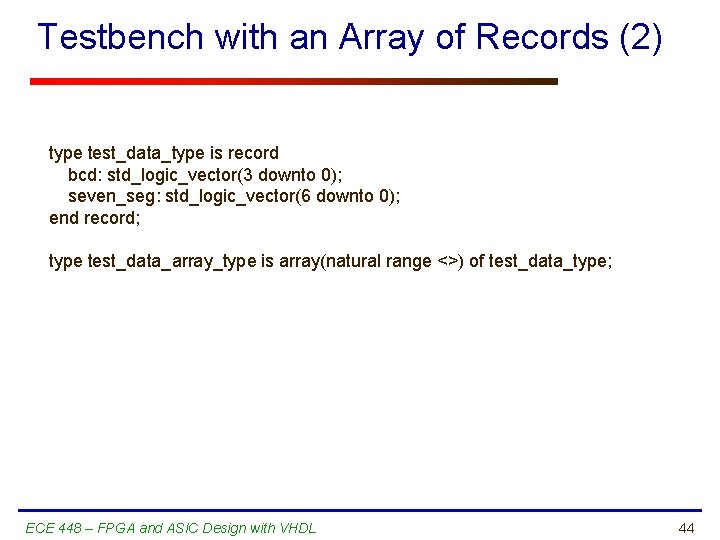

Testbench with an Array of Records (2) type test_data_type is record bcd: std_logic_vector(3 downto 0); seven_seg: std_logic_vector(6 downto 0); end record; type test_data_array_type is array(natural range <>) of test_data_type; ECE 448 – FPGA and ASIC Design with VHDL 44

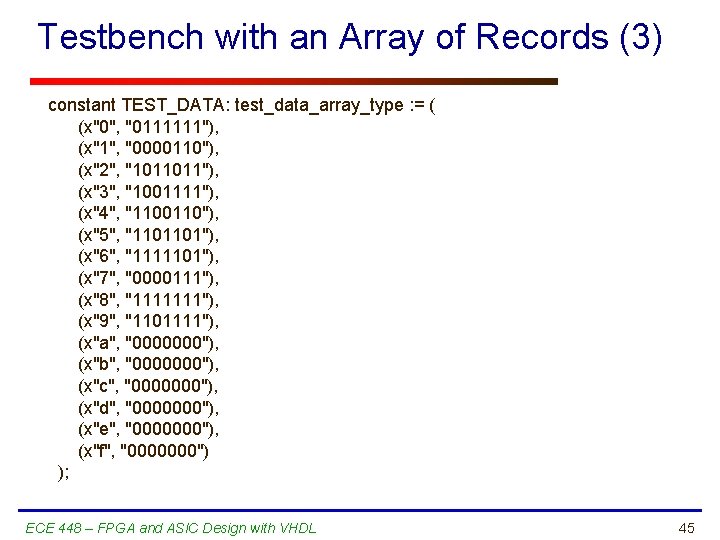

Testbench with an Array of Records (3) constant TEST_DATA: test_data_array_type : = ( (x"0", "0111111"), (x"1", "0000110"), (x"2", "1011011"), (x"3", "1001111"), (x"4", "1100110"), (x"5", "1101101"), (x"6", "1111101"), (x"7", "0000111"), (x"8", "1111111"), (x"9", "1101111"), (x"a", "0000000"), (x"b", "0000000"), (x"c", "0000000"), (x"d", "0000000"), (x"e", "0000000"), (x"f", "0000000") ); ECE 448 – FPGA and ASIC Design with VHDL 45

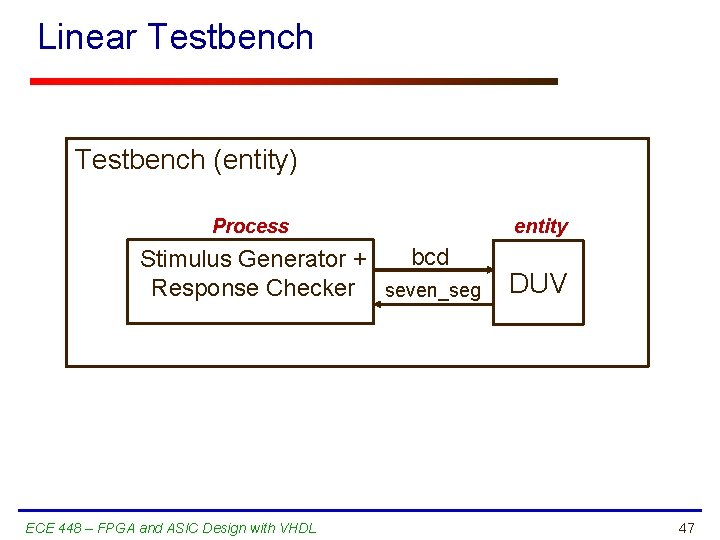

Linear testbench ECE 448 – FPGA and ASIC Design with VHDL

Linear Testbench (entity) Process bcd Stimulus Generator + Response Checker seven_seg ECE 448 – FPGA and ASIC Design with VHDL entity DUV 47

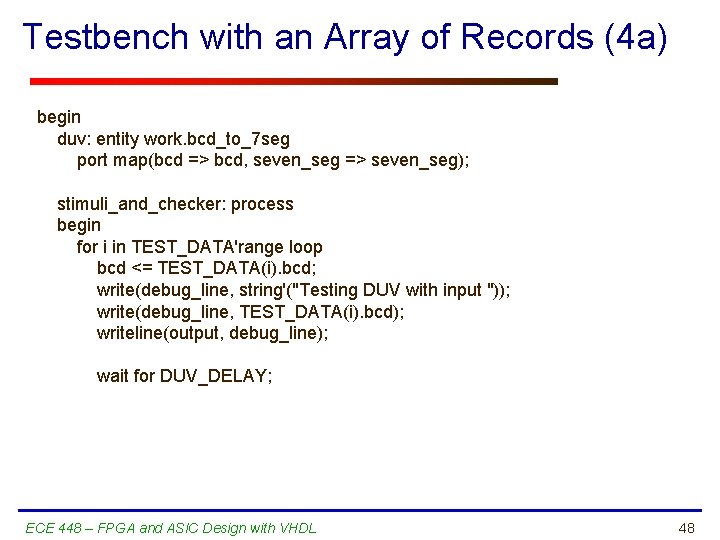

Testbench with an Array of Records (4 a) begin duv: entity work. bcd_to_7 seg port map(bcd => bcd, seven_seg => seven_seg); stimuli_and_checker: process begin for i in TEST_DATA'range loop bcd <= TEST_DATA(i). bcd; write(debug_line, string'("Testing DUV with input ")); write(debug_line, TEST_DATA(i). bcd); writeline(output, debug_line); wait for DUV_DELAY; ECE 448 – FPGA and ASIC Design with VHDL 48

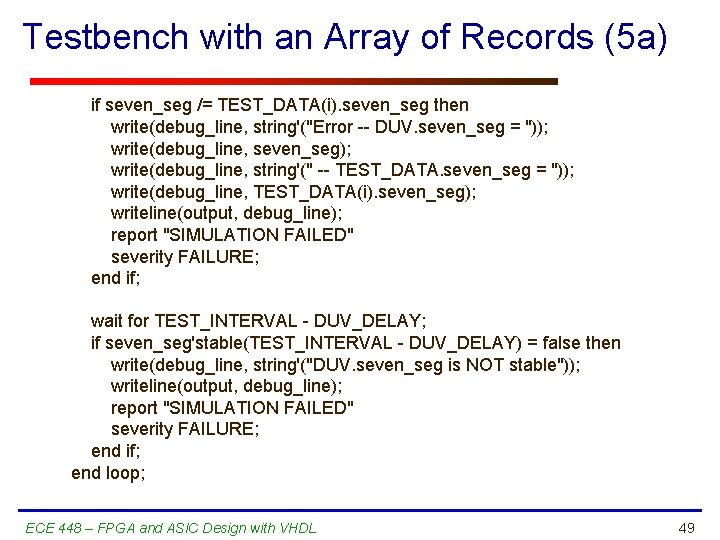

Testbench with an Array of Records (5 a) if seven_seg /= TEST_DATA(i). seven_seg then write(debug_line, string'("Error -- DUV. seven_seg = ")); write(debug_line, seven_seg); write(debug_line, string'(" -- TEST_DATA. seven_seg = ")); write(debug_line, TEST_DATA(i). seven_seg); writeline(output, debug_line); report "SIMULATION FAILED" severity FAILURE; end if; wait for TEST_INTERVAL - DUV_DELAY; if seven_seg'stable(TEST_INTERVAL - DUV_DELAY) = false then write(debug_line, string'("DUV. seven_seg is NOT stable")); writeline(output, debug_line); report "SIMULATION FAILED" severity FAILURE; end if; end loop; ECE 448 – FPGA and ASIC Design with VHDL 49

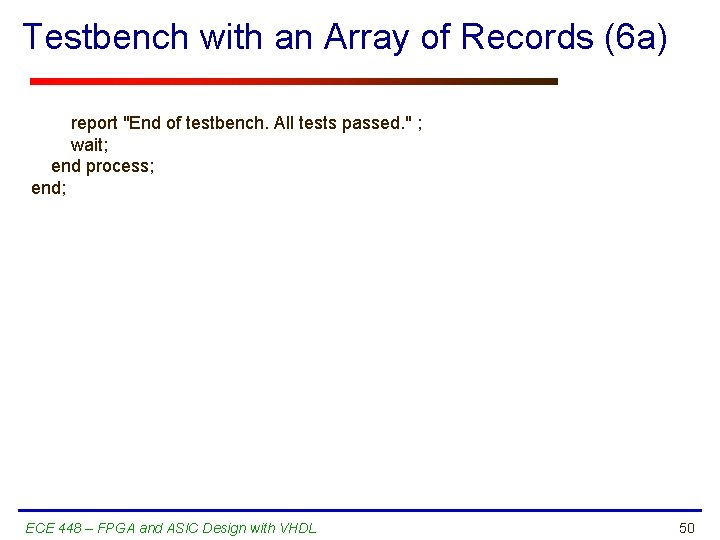

Testbench with an Array of Records (6 a) report "End of testbench. All tests passed. " ; wait; end process; end; ECE 448 – FPGA and ASIC Design with VHDL 50

Separate stimulus generation from response checking ECE 448 – FPGA and ASIC Design with VHDL

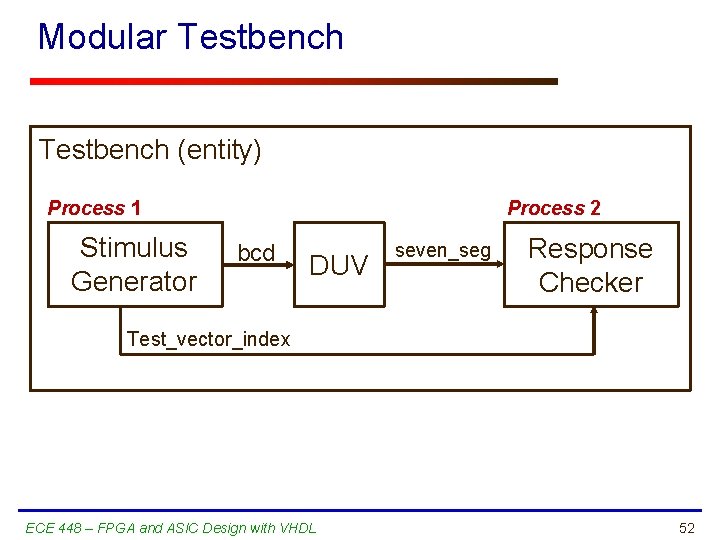

Modular Testbench (entity) Process 1 Stimulus Generator Process 2 bcd DUV seven_seg Response Checker Test_vector_index ECE 448 – FPGA and ASIC Design with VHDL 52

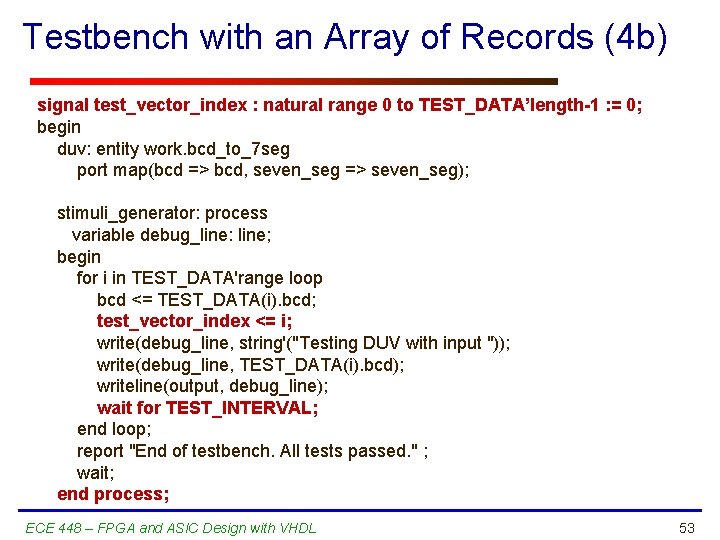

Testbench with an Array of Records (4 b) signal test_vector_index : natural range 0 to TEST_DATA’length-1 : = 0; begin duv: entity work. bcd_to_7 seg port map(bcd => bcd, seven_seg => seven_seg); stimuli_generator: process variable debug_line: line; begin for i in TEST_DATA'range loop bcd <= TEST_DATA(i). bcd; test_vector_index <= i; write(debug_line, string'("Testing DUV with input ")); write(debug_line, TEST_DATA(i). bcd); writeline(output, debug_line); wait for TEST_INTERVAL; end loop; report "End of testbench. All tests passed. " ; wait; end process; ECE 448 – FPGA and ASIC Design with VHDL 53

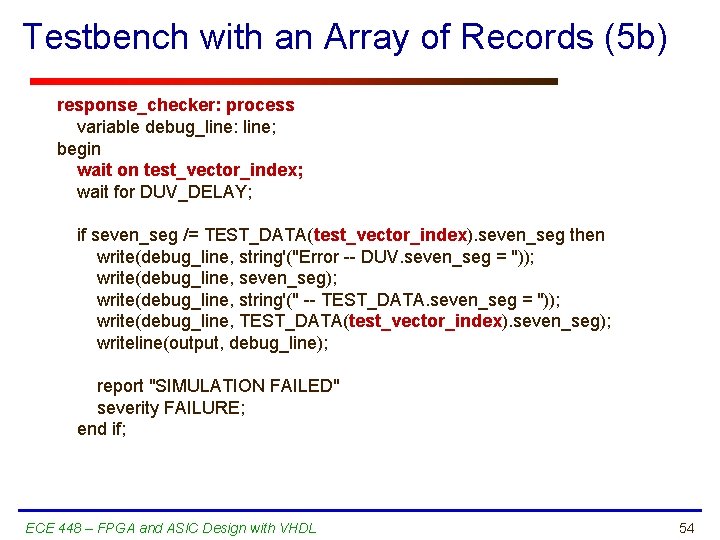

Testbench with an Array of Records (5 b) response_checker: process variable debug_line: line; begin wait on test_vector_index; wait for DUV_DELAY; if seven_seg /= TEST_DATA(test_vector_index). seven_seg then write(debug_line, string'("Error -- DUV. seven_seg = ")); write(debug_line, seven_seg); write(debug_line, string'(" -- TEST_DATA. seven_seg = ")); write(debug_line, TEST_DATA(test_vector_index). seven_seg); writeline(output, debug_line); report "SIMULATION FAILED" severity FAILURE; end if; ECE 448 – FPGA and ASIC Design with VHDL 54

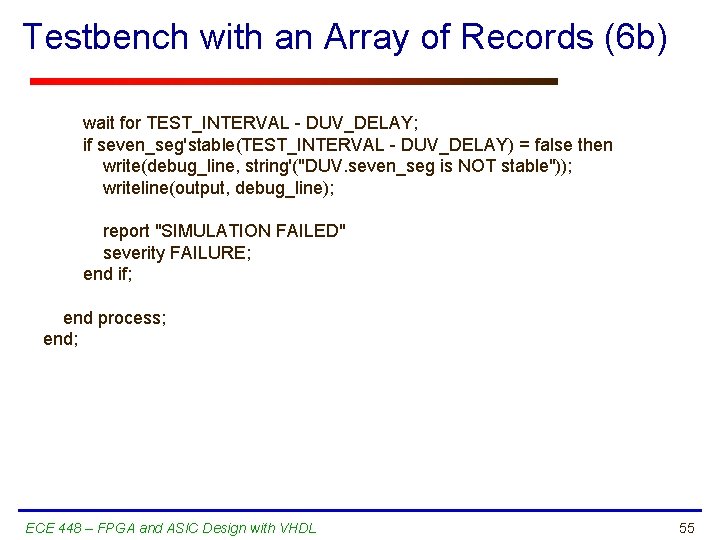

Testbench with an Array of Records (6 b) wait for TEST_INTERVAL - DUV_DELAY; if seven_seg'stable(TEST_INTERVAL - DUV_DELAY) = false then write(debug_line, string'("DUV. seven_seg is NOT stable")); writeline(output, debug_line); report "SIMULATION FAILED" severity FAILURE; end if; end process; end; ECE 448 – FPGA and ASIC Design with VHDL 55

Variables ECE 448 – FPGA and ASIC Design with VHDL

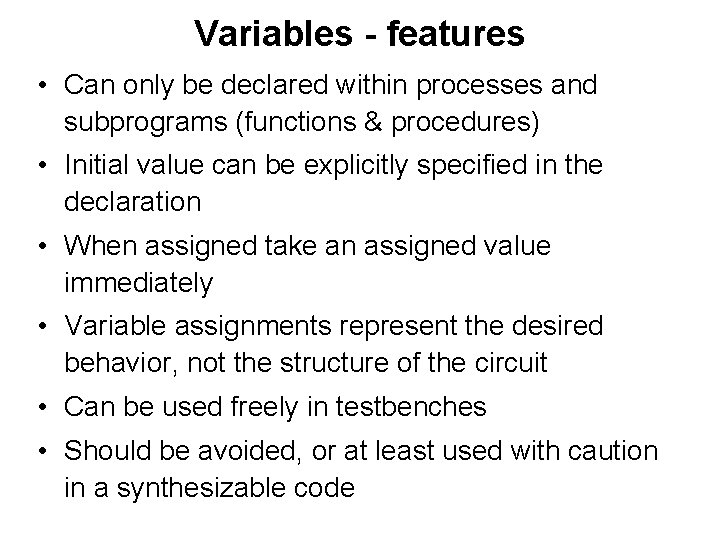

Variables - features • Can only be declared within processes and subprograms (functions & procedures) • Initial value can be explicitly specified in the declaration • When assigned take an assigned value immediately • Variable assignments represent the desired behavior, not the structure of the circuit • Can be used freely in testbenches • Should be avoided, or at least used with caution in a synthesizable code

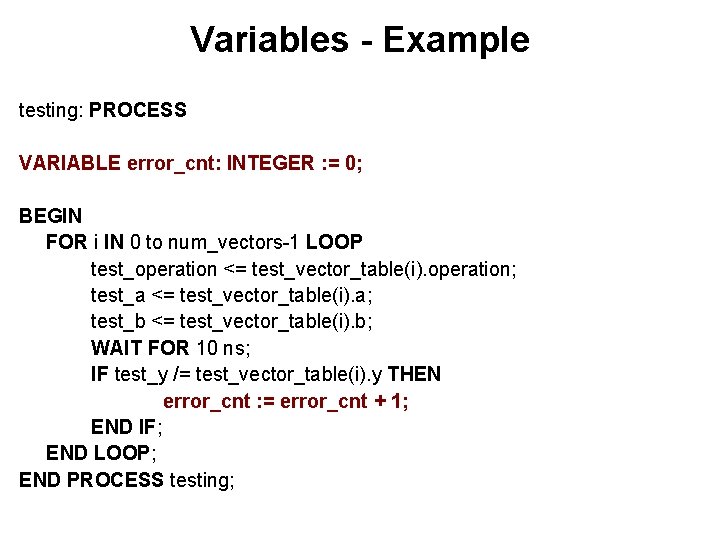

Variables - Example testing: PROCESS VARIABLE error_cnt: INTEGER : = 0; BEGIN FOR i IN 0 to num_vectors-1 LOOP test_operation <= test_vector_table(i). operation; test_a <= test_vector_table(i). a; test_b <= test_vector_table(i). b; WAIT FOR 10 ns; IF test_y /= test_vector_table(i). y THEN error_cnt : = error_cnt + 1; END IF; END LOOP; END PROCESS testing;

Part 4 Introduction to Lab 1: Developing Effective Testbenches ECE 448 – FPGA and ASIC Design with VHDL

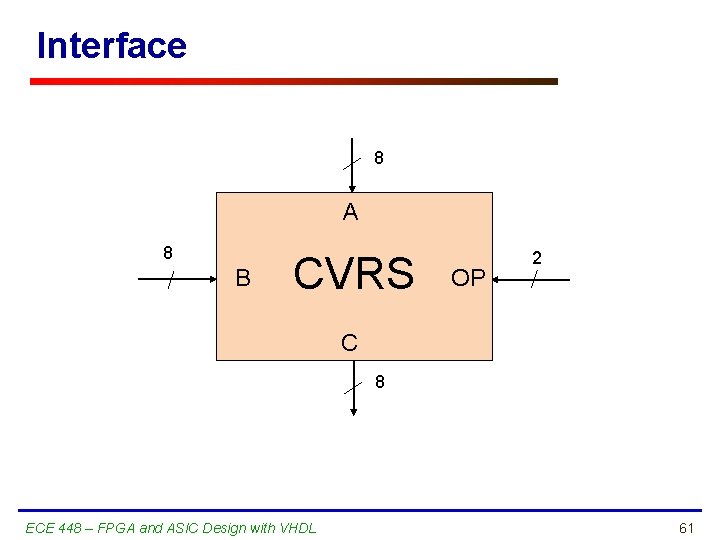

Verifying Combinational Logic Combinational Variable Rotator-Shifter (CVRS) ECE 448 – FPGA and ASIC Design with VHDL

Interface 8 A 8 B CVRS OP 2 C 8 ECE 448 – FPGA and ASIC Design with VHDL 61

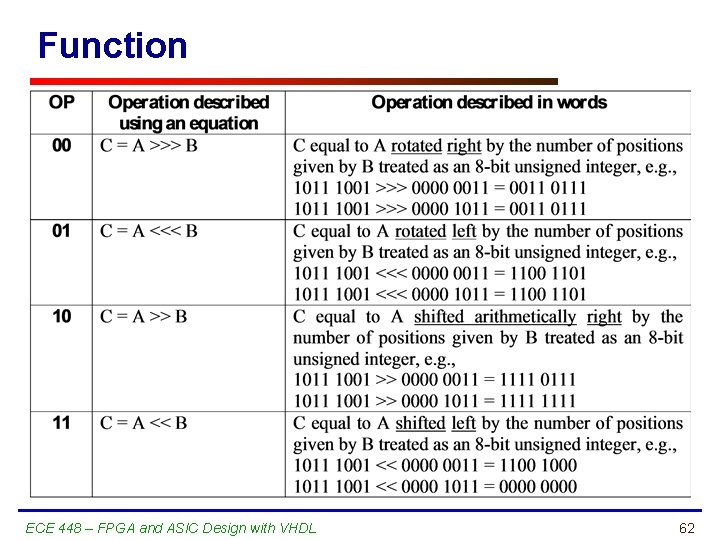

Function ECE 448 – FPGA and ASIC Design with VHDL 62

Discrepencies One of the provided models is correct. The second model contains several discrepancies compared to the specification. These discrepancies may have, for example, the following forms: 1. Incorrect output for a specific value of OP 2. Incorrect output for a subset of allowed B values 3. Incorrect output for a subset of allowed A values ECE 448 – FPGA and ASIC Design with VHDL 63

Testbench Requirements Your testbench should automatically compare the actual outputs with expected outputs for 1. All values of the input OP 2. At least 8 substantially different values of A (you can select these values at random, or according to an arbitrary deterministic pattern) 3. At least 8 different values of B (including values of B ≥ 8) ECE 448 – FPGA and ASIC Design with VHDL 64

Tasks and Deliverables Tasks: 1. Write a testbench capable of verifying CVRS, using at least 256 different combinations of inputs. 2. Write a short report describing all discrepancies between the above specification and the faulty model. Deliverables: 1. VHDL code of the testbench. 2. Waveforms obtained by running your testbench in the Vivado Simulator (in the PDF format) 3. Report describing all discrepancies you have managed to detect. ECE 448 – FPGA and ASIC Design with VHDL 65

Verifying Sequential Logic Sequential Rotator- Shifter (SRS) ECE 448 – FPGA and ASIC Design with VHDL

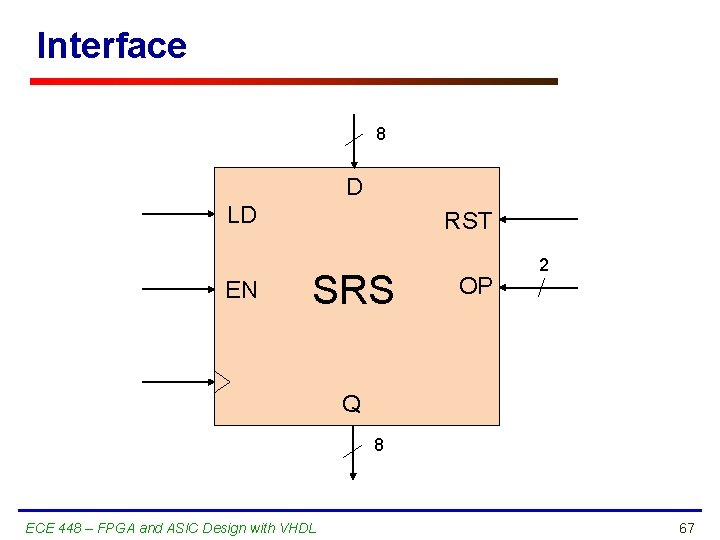

Interface 8 D LD EN RST SRS OP 2 Q 8 ECE 448 – FPGA and ASIC Design with VHDL 67

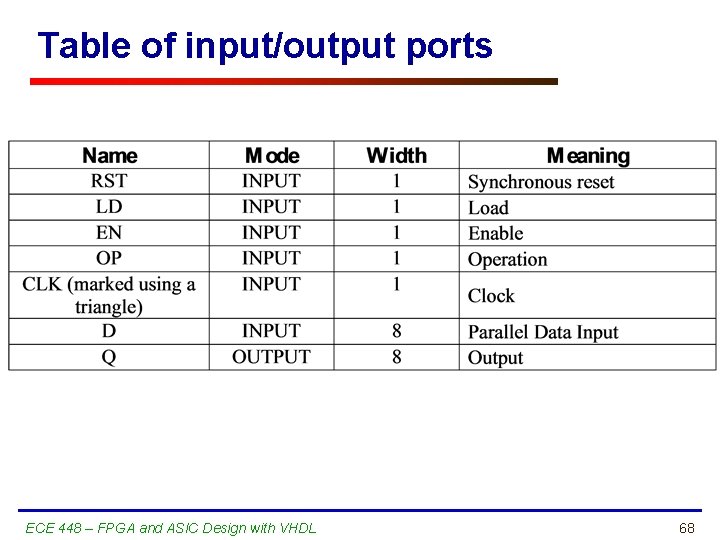

Table of input/output ports ECE 448 – FPGA and ASIC Design with VHDL 68

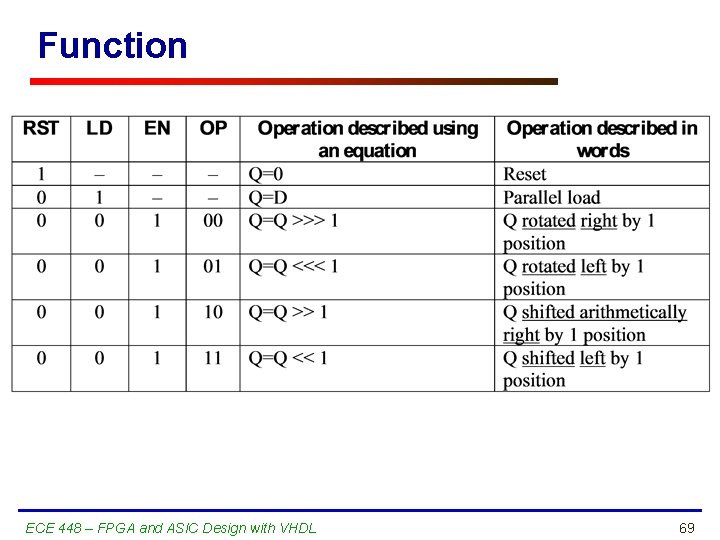

Function ECE 448 – FPGA and ASIC Design with VHDL 69

Discrepencies One of the models is correct. The other model contains several discrepancies compared to the specification. These discrepancies may have, for example, the following forms: 1. Incorrect output for a specific combination of values of RST, LD, EN, and OP 2. Incorrect output for a subset of allowed D values 3. Incorrect output for a subset of allowed Q values. ECE 448 – FPGA and ASIC Design with VHDL 70

Testbench Requirements Your testbench should automatically compare the actual outputs with expected outputs for 1. All meaningful combinations of the inputs RST, LD, and EN 2. All values of the input OP 3. At least 8 substantially different values of D (you can select these values at random, or according to an arbitrary deterministic pattern) 4. At least 8 different values of the internal state Q reached after loading a new value of D. ECE 448 – FPGA and ASIC Design with VHDL 71

Tasks and Deliverables Tasks: 1. Write a testbench capable of fully verifying the SRS circuit defined above. 2. Write a short report describing all discrepancies between the above specification and the faulty models. Deliverables: 1. VHDL code of the testbench. 2. Waveforms obtained by running your testbench in the Vivado Simulator (in the PDF format) 3. Report describing all discrepancies you have managed to detect. ECE 448 – FPGA and ASIC Design with VHDL 72

Part 5 Lab 1 Exercise ECE 448 – FPGA and ASIC Design with VHDL 73

Part 6 Hands-on Session: Vivado Simulator ECE 448 – FPGA and ASIC Design with VHDL 74

Hands-on Session: Vivado Simulator https: //ece. gmu. edu/tutorials-and-lab-manuals • Resources on Simulators : Vivado Simulator ECE 448 – FPGA and ASIC Design with VHDL 75

- Slides: 75