ECE 448 Lab 4 Using FPro So C

ECE 448: Lab 4 Using FPro So. C with customized hardware cores (cont)

Agenda for today Part 1: Basic MIMO I/O Core Construction (Timer Core) Part 2: Lab 4 Exercise 2

Part 1 Basic MIMO I/O Core Construction (Timer Core) ECE 448 – FPGA and ASIC Design with VHDL

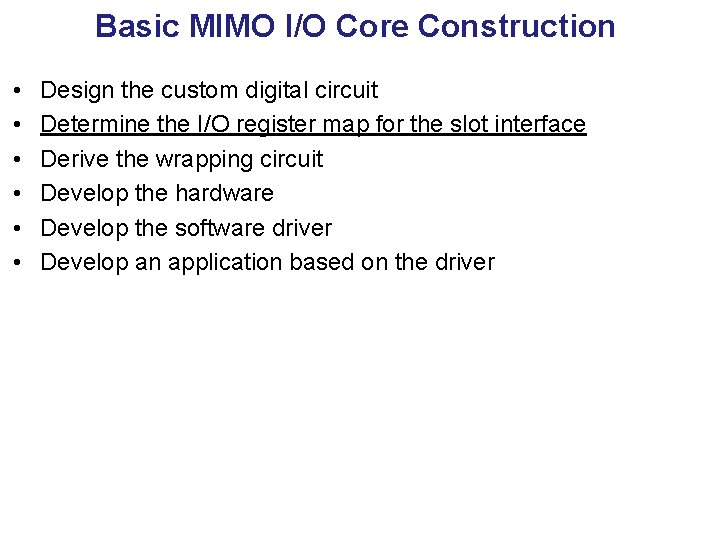

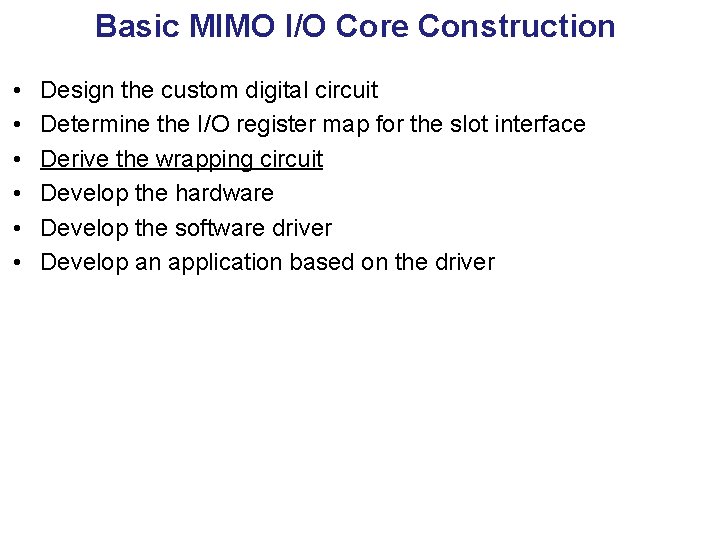

Basic MIMO I/O Core Construction • • • Design the custom digital circuit Determine the I/O register map for the slot interface Derive the wrapping circuit Develop the hardware Develop the software driver Develop an application based on the driver

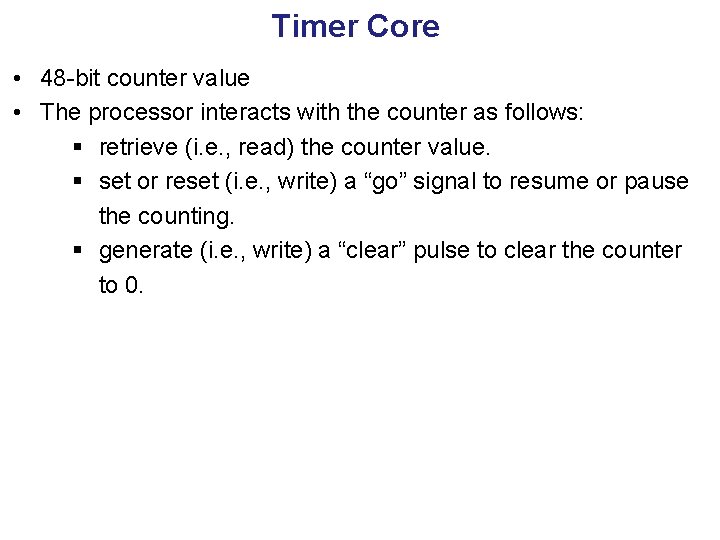

Timer Core • 48 -bit counter value • The processor interacts with the counter as follows: § retrieve (i. e. , read) the counter value. § set or reset (i. e. , write) a “go” signal to resume or pause the counting. § generate (i. e. , write) a “clear” pulse to clear the counter to 0.

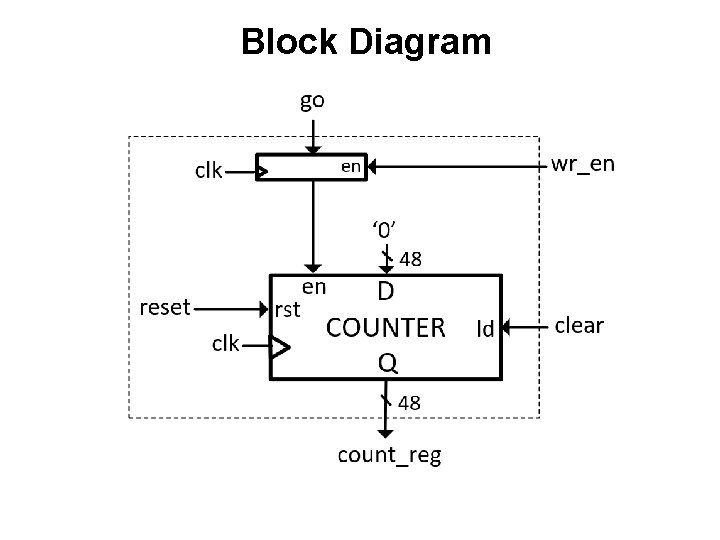

Block Diagram

Basic MIMO I/O Core Construction • • • Design the custom digital circuit Determine the I/O register map for the slot interface Derive the wrapping circuit Develop the hardware Develop the software driver Develop an application based on the driver

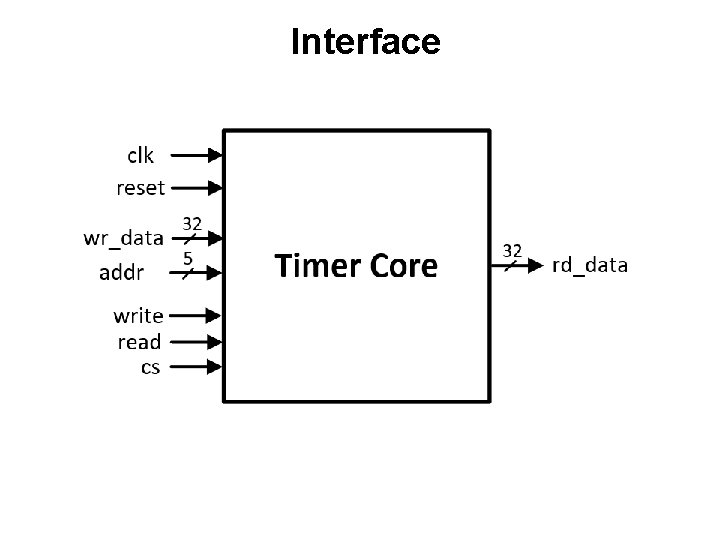

Interface

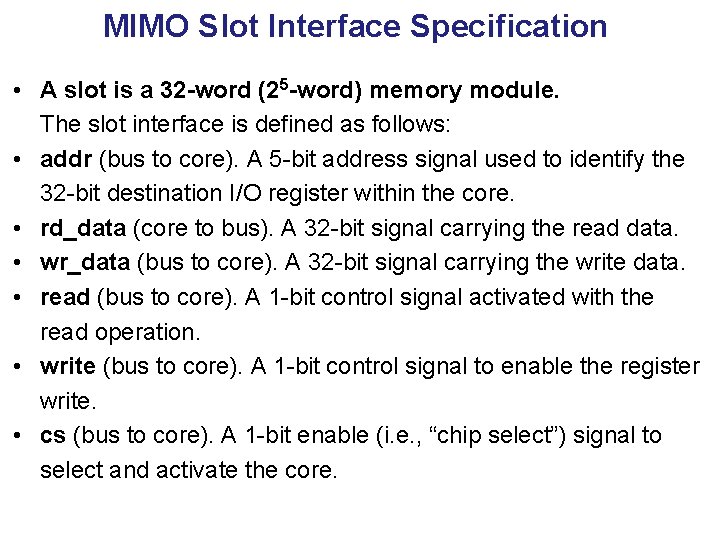

MIMO Slot Interface Specification • A slot is a 32 -word (25 -word) memory module. The slot interface is defined as follows: • addr (bus to core). A 5 -bit address signal used to identify the 32 -bit destination I/O register within the core. • rd_data (core to bus). A 32 -bit signal carrying the read data. • wr_data (bus to core). A 32 -bit signal carrying the write data. • read (bus to core). A 1 -bit control signal activated with the read operation. • write (bus to core). A 1 -bit control signal to enable the register write. • cs (bus to core). A 1 -bit enable (i. e. , “chip select”) signal to select and activate the core.

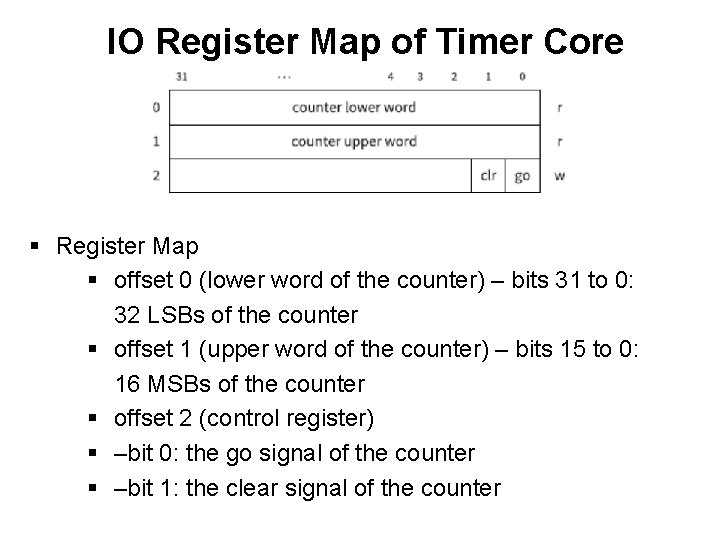

IO Register Map of Timer Core § Register Map § offset 0 (lower word of the counter) – bits 31 to 0: 32 LSBs of the counter § offset 1 (upper word of the counter) – bits 15 to 0: 16 MSBs of the counter § offset 2 (control register) § –bit 0: the go signal of the counter § –bit 1: the clear signal of the counter

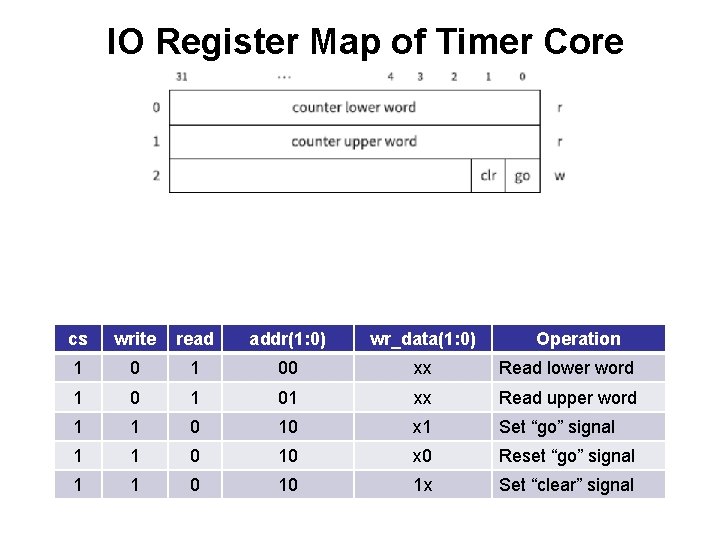

IO Register Map of Timer Core cs write read addr(1: 0) wr_data(1: 0) Operation 1 00 xx Read lower word 1 01 xx Read upper word 1 1 0 10 x 1 Set “go” signal 1 1 0 10 x 0 Reset “go” signal 1 1 0 10 1 x Set “clear” signal

Basic MIMO I/O Core Construction • • • Design the custom digital circuit Determine the I/O register map for the slot interface Derive the wrapping circuit Develop the hardware Develop the software driver Develop an application based on the driver

Wrapping Circuit cs write read addr(1: 0) wr_data(1: 0) Operation 1 00 xx Read lower word 1 01 xx Read upper word 1 1 0 10 x 1 Set “go” signal 1 1 0 10 x 0 Reset “go” signal 1 1 0 10 1 x Set “clear” signal

Basic MIMO I/O Core Construction • • • Design the custom digital circuit Determine the I/O register map for the slot interface Derive the wrapping circuit Develop the hardware Develop the software driver Develop an application based on the driver

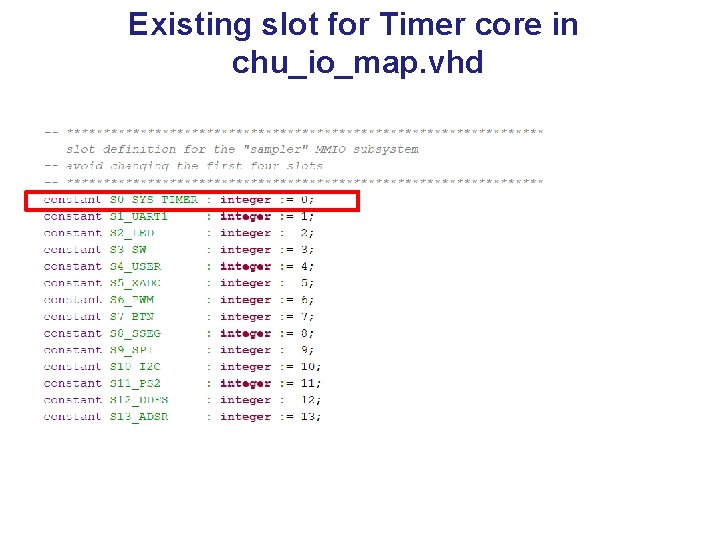

Existing slot for Timer core in chu_io_map. vhd

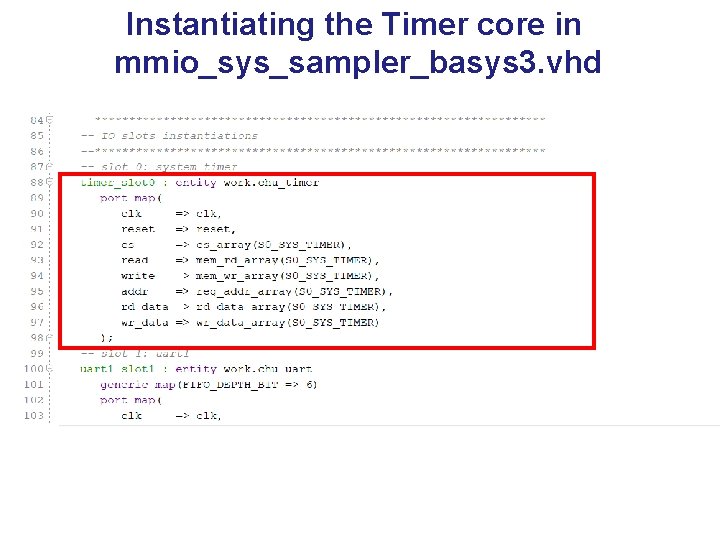

Instantiating the Timer core in mmio_sys_sampler_basys 3. vhd

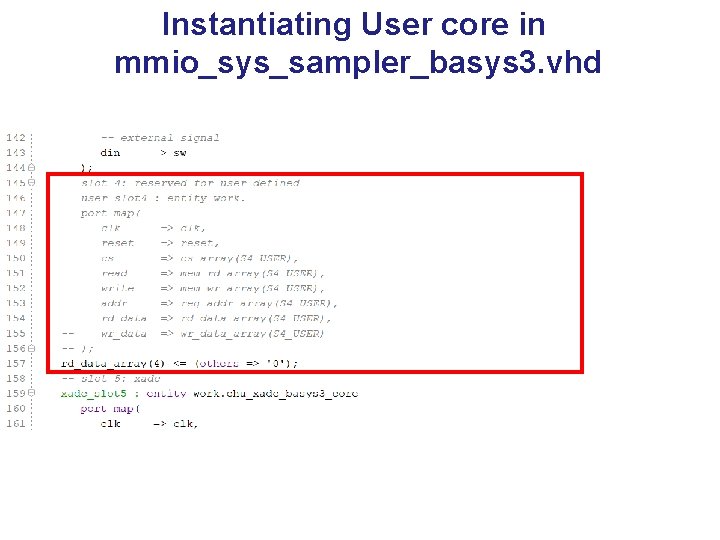

Instantiating User core in mmio_sys_sampler_basys 3. vhd

Basic MIMO I/O Core Construction • • • Design the custom digital circuit Determine the I/O register map for the slot interface Derive the wrapping circuit Develop the hardware Develop the software driver Develop an application based on the driver

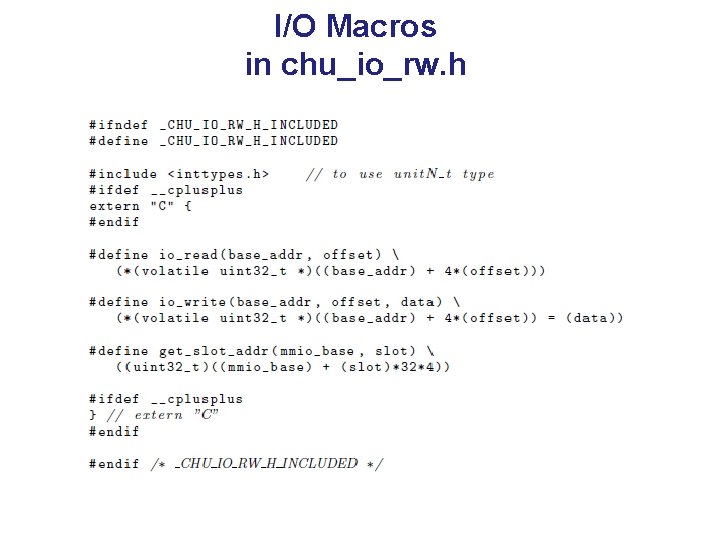

I/O Macros in chu_io_rw. h

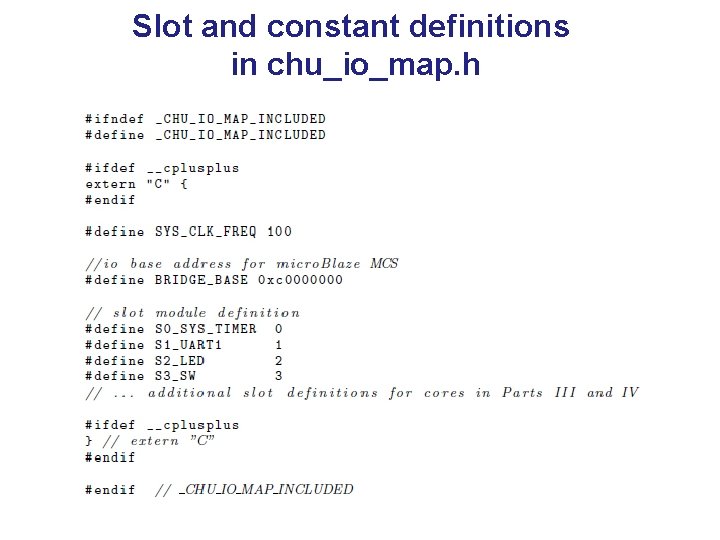

Slot and constant definitions in chu_io_map. h

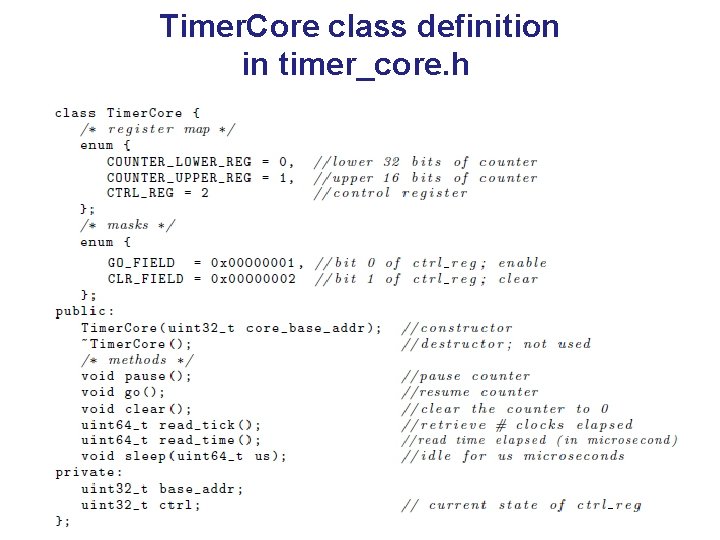

Timer. Core class definition in timer_core. h

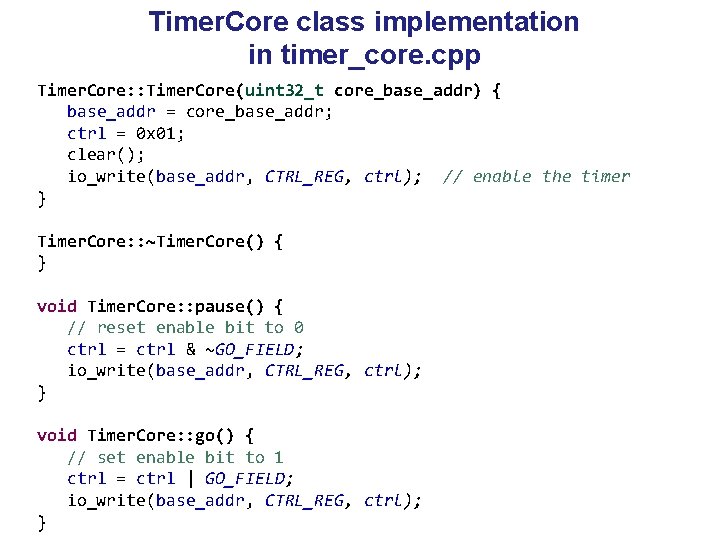

Timer. Core class implementation in timer_core. cpp Timer. Core: : Timer. Core(uint 32_t core_base_addr) { base_addr = core_base_addr; ctrl = 0 x 01; clear(); io_write(base_addr, CTRL_REG, ctrl); // enable the timer } Timer. Core: : ~Timer. Core() { } void Timer. Core: : pause() { // reset enable bit to 0 ctrl = ctrl & ~GO_FIELD; io_write(base_addr, CTRL_REG, ctrl); } void Timer. Core: : go() { // set enable bit to 1 ctrl = ctrl | GO_FIELD; io_write(base_addr, CTRL_REG, ctrl); }

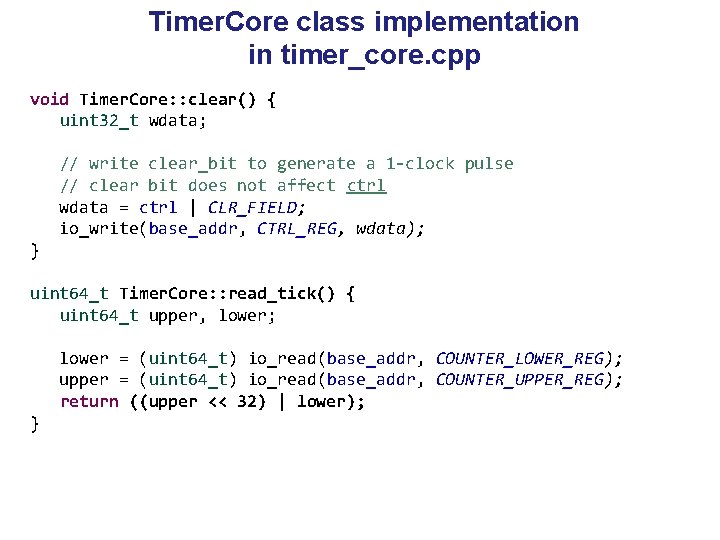

Timer. Core class implementation in timer_core. cpp void Timer. Core: : clear() { uint 32_t wdata; // write clear_bit to generate a 1 -clock pulse // clear bit does not affect ctrl wdata = ctrl | CLR_FIELD; io_write(base_addr, CTRL_REG, wdata); } uint 64_t Timer. Core: : read_tick() { uint 64_t upper, lower; lower = (uint 64_t) io_read(base_addr, COUNTER_LOWER_REG); upper = (uint 64_t) io_read(base_addr, COUNTER_UPPER_REG); return ((upper << 32) | lower); }

Basic MIMO I/O Core Construction • • • Design the custom digital circuit Determine the I/O register map for the slot interface Derive the wrapping circuit Develop the hardware Develop the software driver Develop an application based on the driver

Application Code #include "chu_io_map. h" #include "timer_core. h" Timer. Core timer((get_slot_addr(BRIDGE_BASE, S 0_SYS_TIMER))); int main(){ timer. clear(); timer. go(); timer. pause(); uint 64_t ticks = timer. read_tick(); }

Part 2 Lab 4 Exercise 2 ECE 448 – FPGA and ASIC Design with VHDL

- Slides: 26