ECE 448 Lecture 12 VGA Display Part 3

- Slides: 30

ECE 448 Lecture 12 VGA Display Part 3 Animation ECE 448 – FPGA and ASIC Design with VHDL George Mason University

Required Reading • Old Edition of the Textbook 2008 (see Piazza) P. Chu, FPGA Prototyping by VHDL Examples Chapter 12, VGA Controller I: Graphic • Source Code of Examples http: //academic. csuohio. edu/chu_p/rtl/fpga_vhdl. html • Basys 3 FPGA Board Reference Manual 7. VGA Port ECE 448 – FPGA and ASIC Design with VHDL 2

PONG ECE 448 – FPGA and ASIC Design with VHDL 3

PONG • Commonly regarded as the first "commercially successful" video game • Released by Atari in 1972 • Created by Allan Alcorn as a training exercise assigned to him by Atari co-founder Nolan Bushnell • The first prototype developed completely in hardware using TTL devices • Originally used as an arcade video game • Home version released during the 1975 Christmas season ECE 448 – FPGA and ASIC Design with VHDL 4

PONG ECE 448 – FPGA and ASIC Design with VHDL 5

PONG – Interesting Videos Pong Game http: //www. ponggame. org First documented Video Ping-Pong game – 1969 https: //www. youtube. com/watch? v=XNRx 5 hc 4 g. Yc Classic Game Room HD - PONG for Nintendo DS / GBA https: //www. youtube. com/watch? v=Trez. Fj. GF-Kg ECE 448 – FPGA and ASIC Design with VHDL 6

Animation ECE 448 – FPGA and ASIC Design with VHDL 7

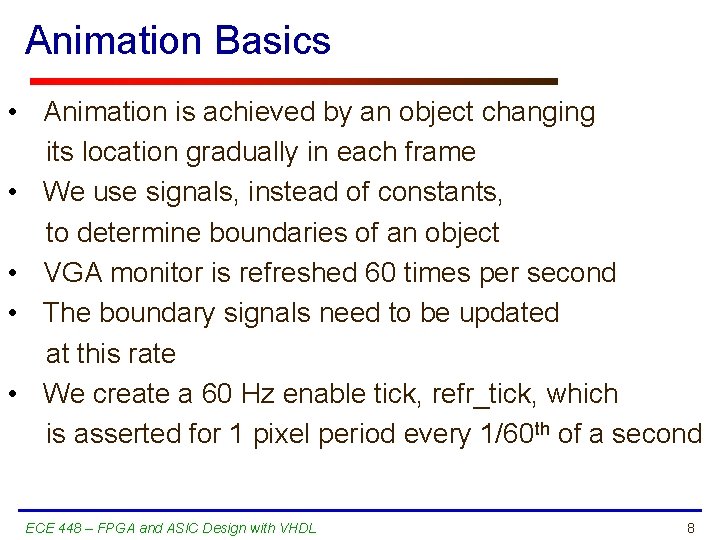

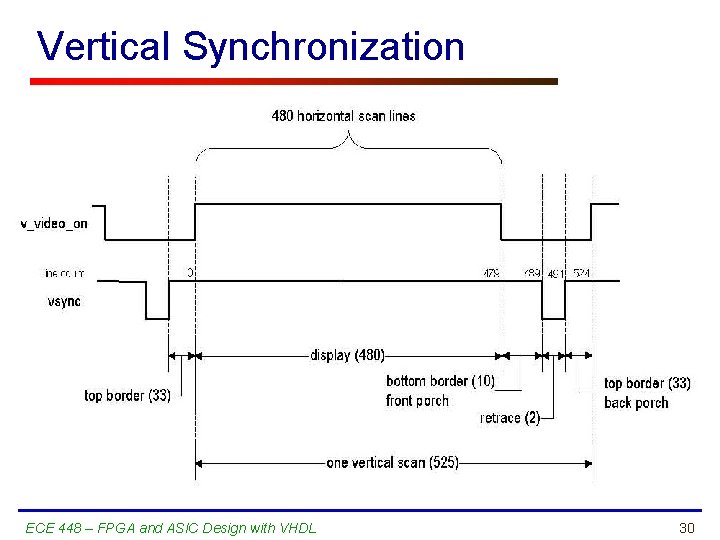

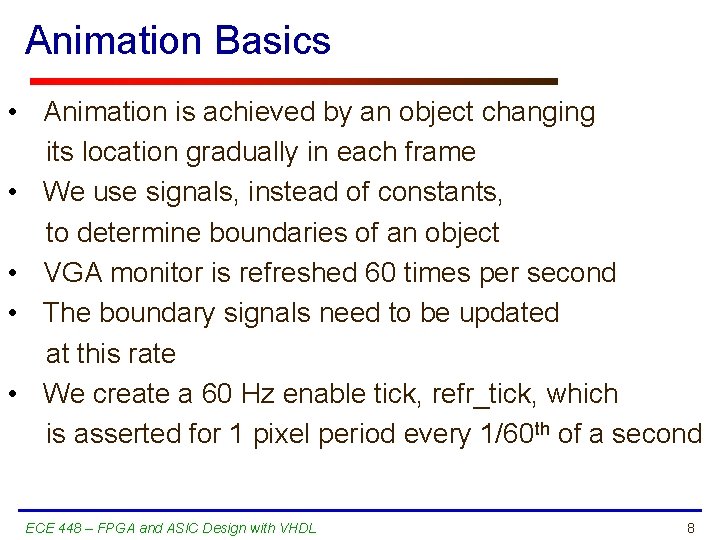

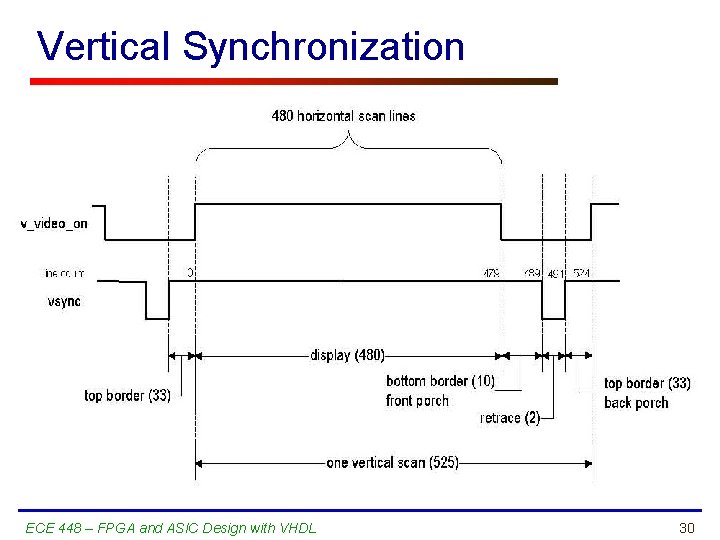

Animation Basics • Animation is achieved by an object changing its location gradually in each frame • We use signals, instead of constants, to determine boundaries of an object • VGA monitor is refreshed 60 times per second • The boundary signals need to be updated at this rate • We create a 60 Hz enable tick, refr_tick, which is asserted for 1 pixel period every 1/60 th of a second ECE 448 – FPGA and ASIC Design with VHDL 8

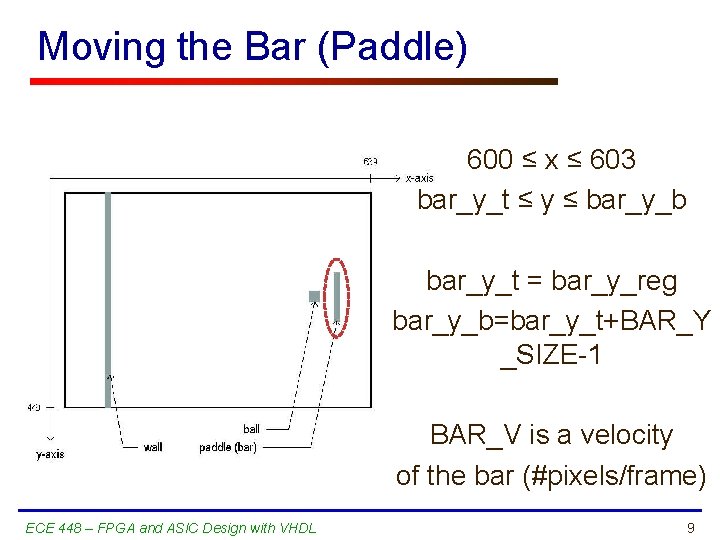

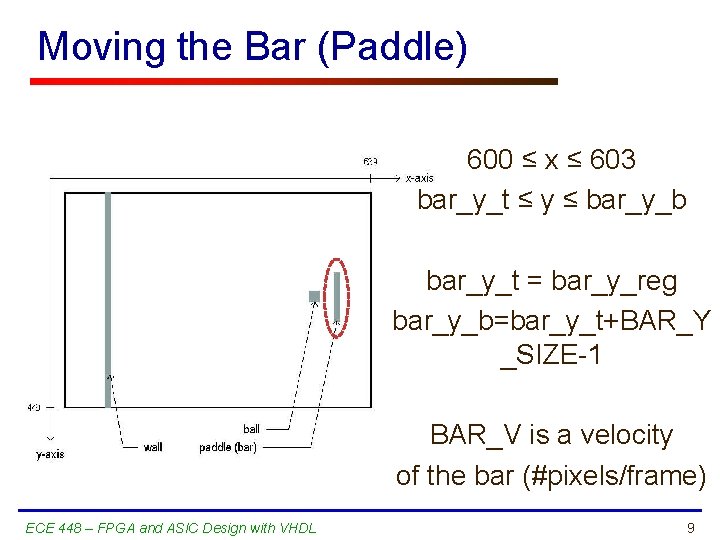

Moving the Bar (Paddle) 600 ≤ x ≤ 603 bar_y_t ≤ y ≤ bar_y_b bar_y_t = bar_y_reg bar_y_b=bar_y_t+BAR_Y _SIZE-1 BAR_V is a velocity of the bar (#pixels/frame) ECE 448 – FPGA and ASIC Design with VHDL 9

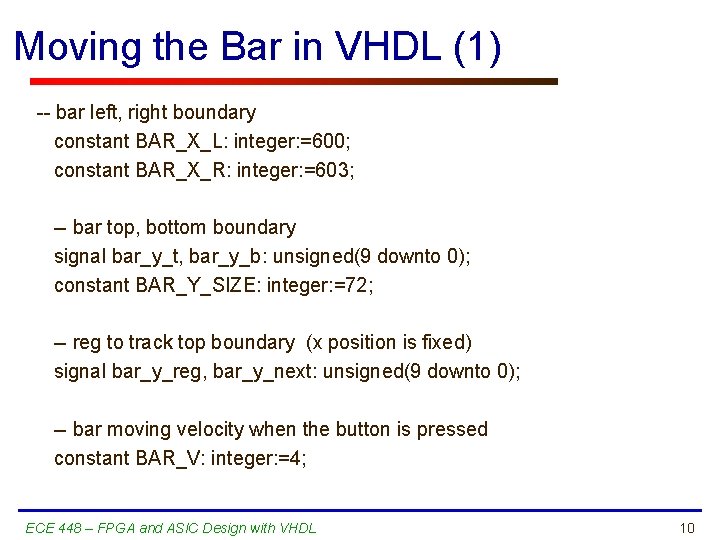

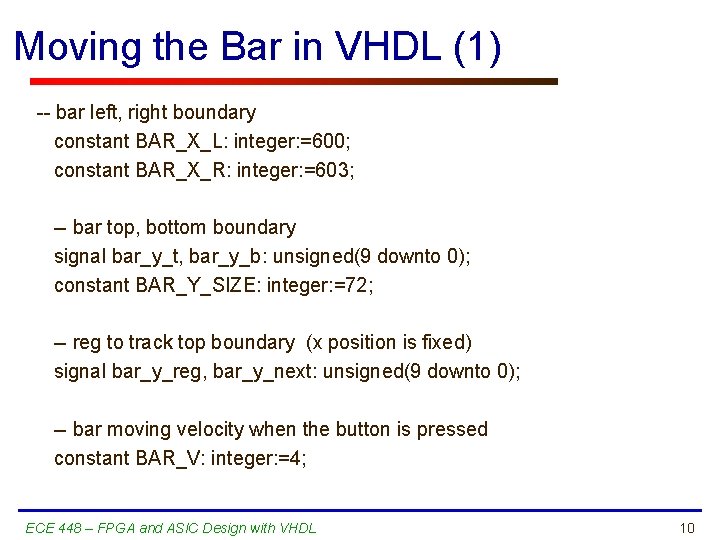

Moving the Bar in VHDL (1) -- bar left, right boundary constant BAR_X_L: integer: =600; constant BAR_X_R: integer: =603; -- bar top, bottom boundary signal bar_y_t, bar_y_b: unsigned(9 downto 0); constant BAR_Y_SIZE: integer: =72; -- reg to track top boundary (x position is fixed) signal bar_y_reg, bar_y_next: unsigned(9 downto 0); -- bar moving velocity when the button is pressed constant BAR_V: integer: =4; ECE 448 – FPGA and ASIC Design with VHDL 10

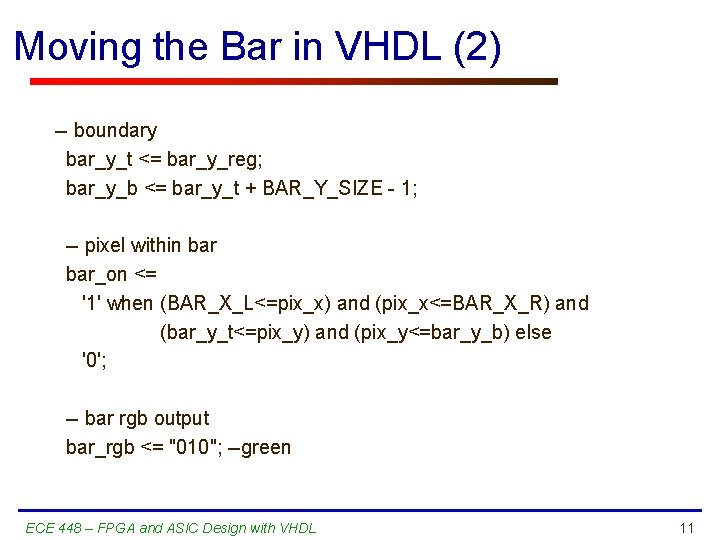

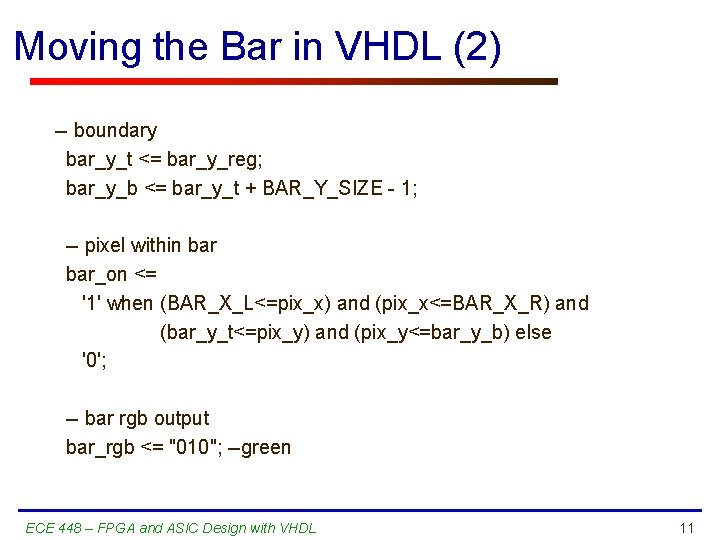

Moving the Bar in VHDL (2) -- boundary bar_y_t <= bar_y_reg; bar_y_b <= bar_y_t + BAR_Y_SIZE - 1; -- pixel within bar_on <= '1' when (BAR_X_L<=pix_x) and (pix_x<=BAR_X_R) and (bar_y_t<=pix_y) and (pix_y<=bar_y_b) else '0'; -- bar rgb output bar_rgb <= "010"; --green ECE 448 – FPGA and ASIC Design with VHDL 11

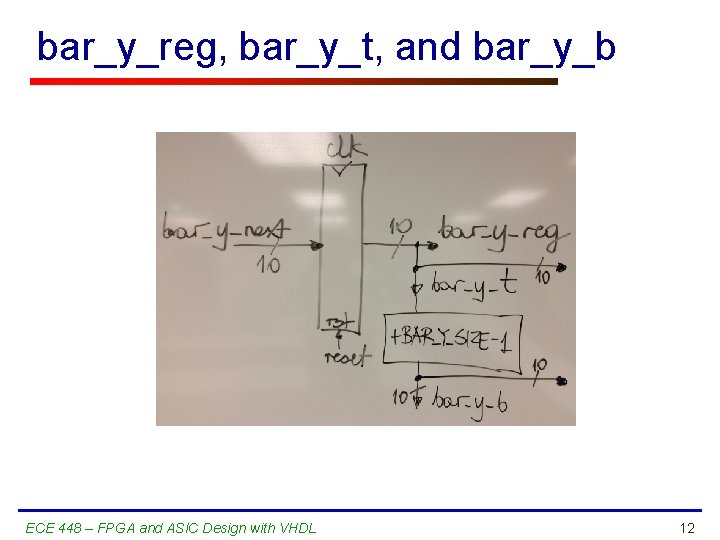

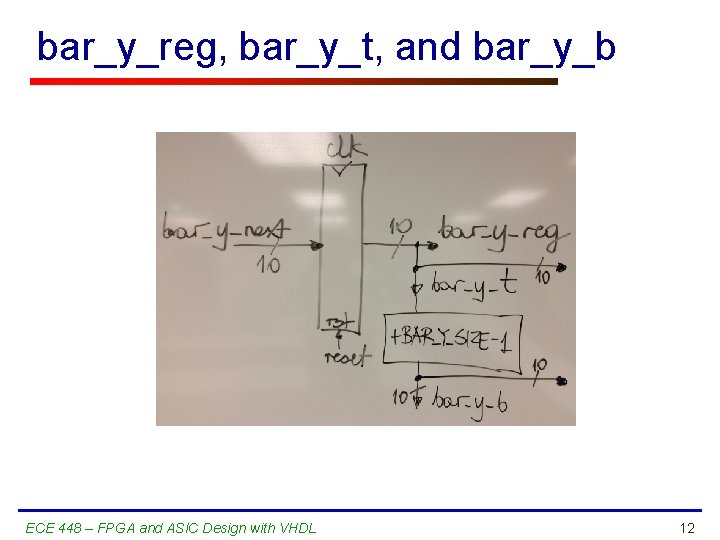

bar_y_reg, bar_y_t, and bar_y_b ECE 448 – FPGA and ASIC Design with VHDL 12

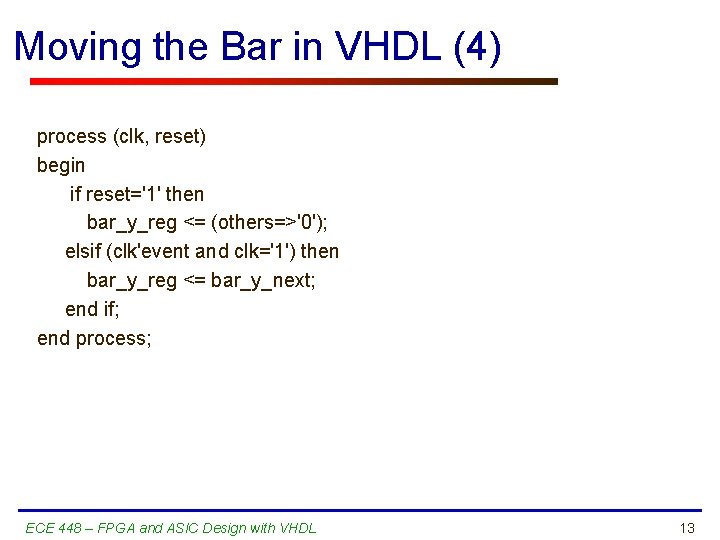

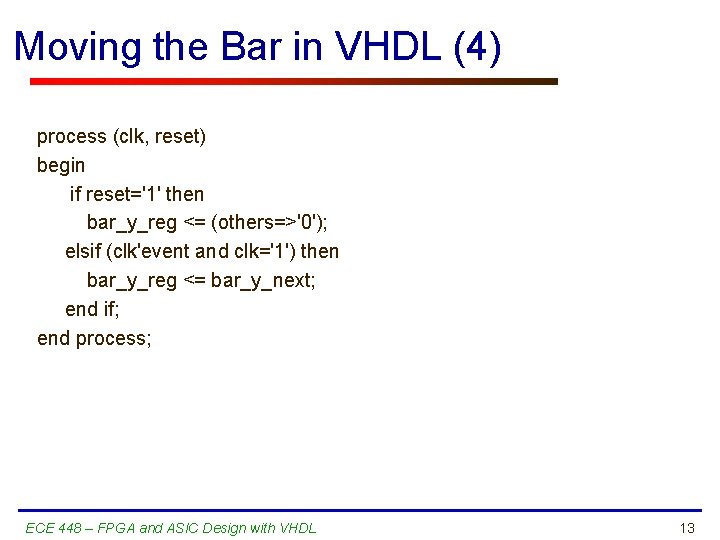

Moving the Bar in VHDL (4) process (clk, reset) begin if reset='1' then bar_y_reg <= (others=>'0'); elsif (clk'event and clk='1') then bar_y_reg <= bar_y_next; end if; end process; ECE 448 – FPGA and ASIC Design with VHDL 13

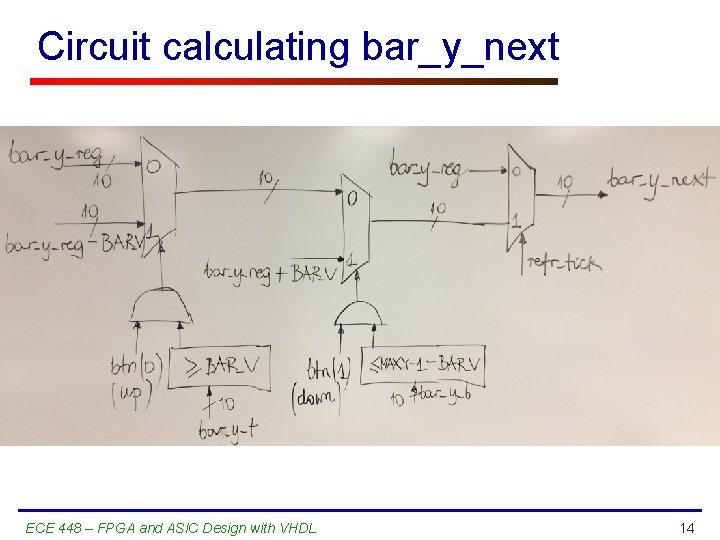

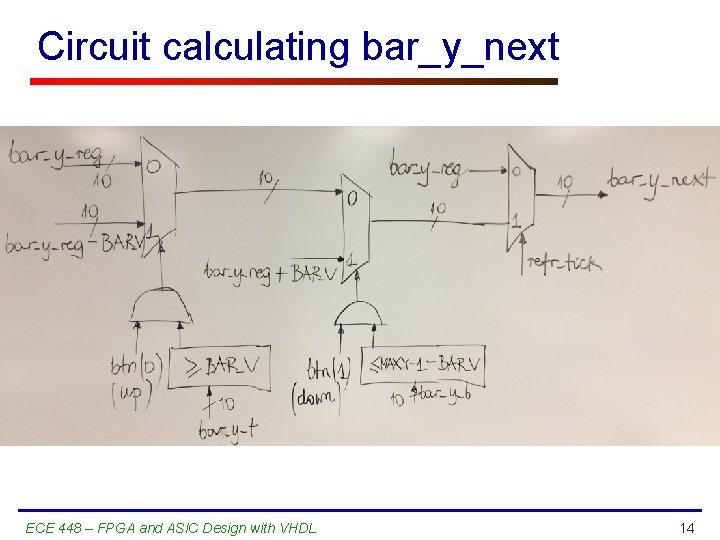

Circuit calculating bar_y_next ECE 448 – FPGA and ASIC Design with VHDL 14

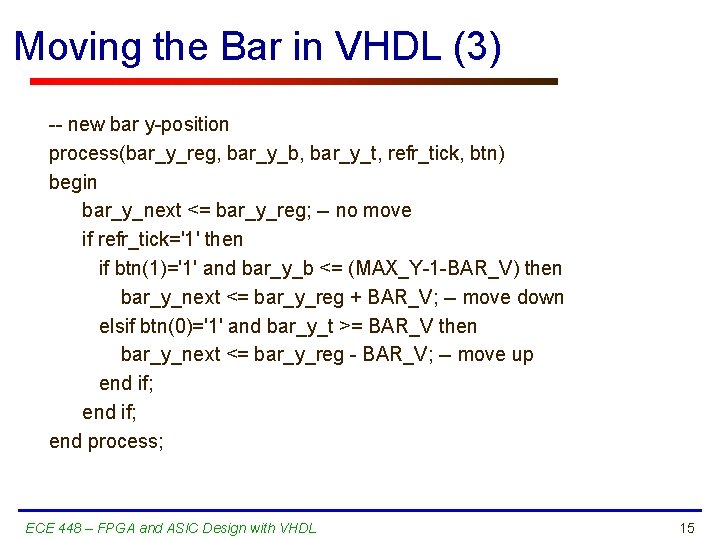

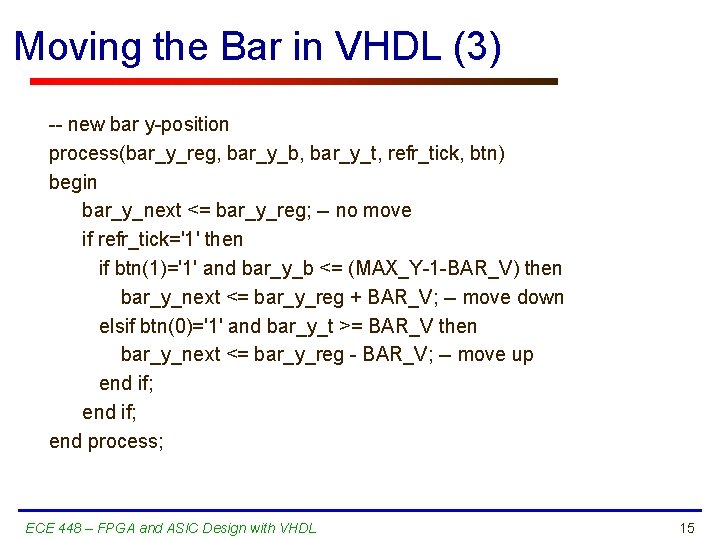

Moving the Bar in VHDL (3) -- new bar y-position process(bar_y_reg, bar_y_b, bar_y_t, refr_tick, btn) begin bar_y_next <= bar_y_reg; -- no move if refr_tick='1' then if btn(1)='1' and bar_y_b <= (MAX_Y-1 -BAR_V) then bar_y_next <= bar_y_reg + BAR_V; -- move down elsif btn(0)='1' and bar_y_t >= BAR_V then bar_y_next <= bar_y_reg - BAR_V; -- move up end if; end process; ECE 448 – FPGA and ASIC Design with VHDL 15

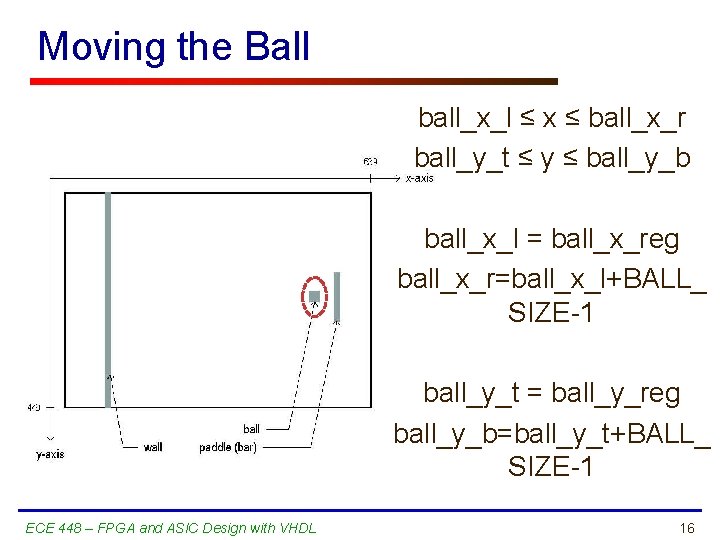

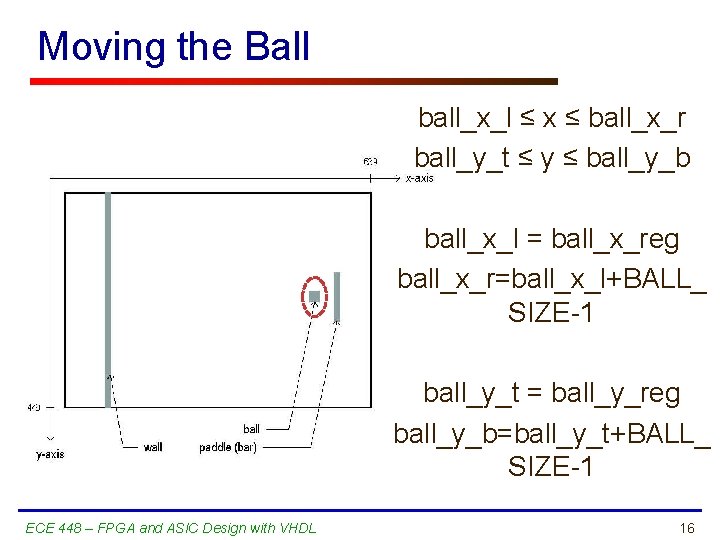

Moving the Ball ball_x_l ≤ x ≤ ball_x_r ball_y_t ≤ y ≤ ball_y_b ball_x_l = ball_x_reg ball_x_r=ball_x_l+BALL_ SIZE-1 ball_y_t = ball_y_reg ball_y_b=ball_y_t+BALL_ SIZE-1 ECE 448 – FPGA and ASIC Design with VHDL 16

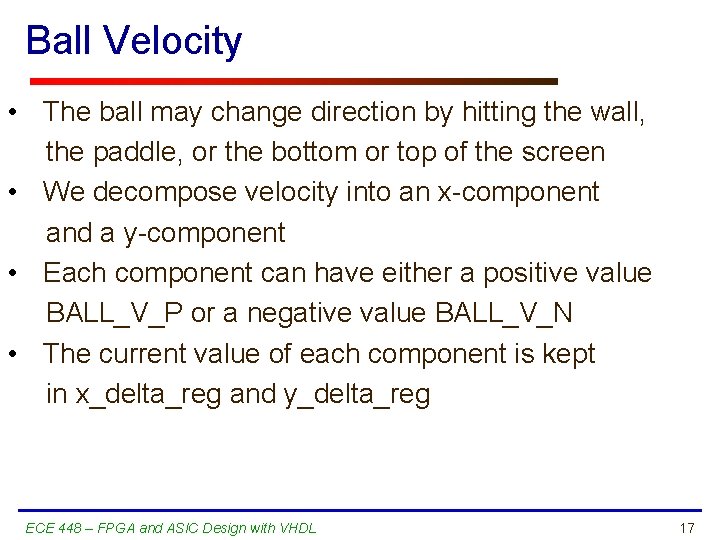

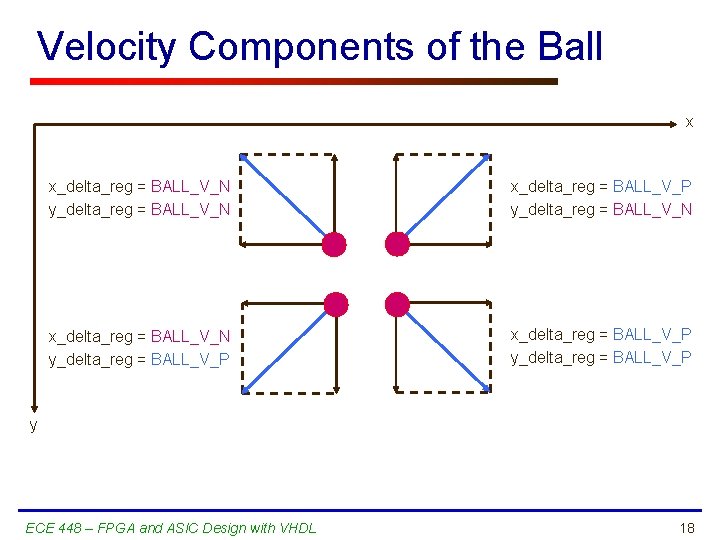

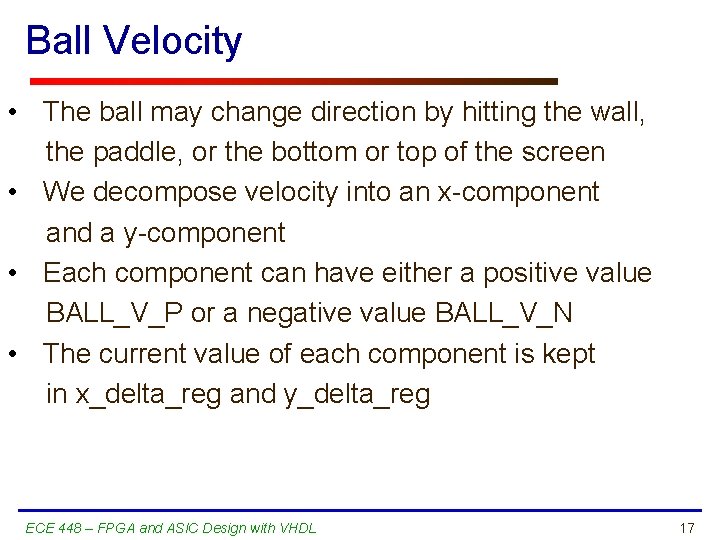

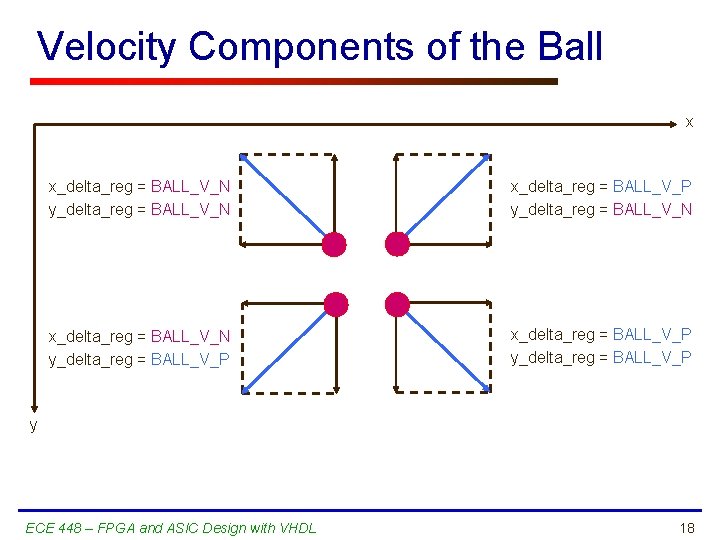

Ball Velocity • The ball may change direction by hitting the wall, the paddle, or the bottom or top of the screen • We decompose velocity into an x-component and a y-component • Each component can have either a positive value BALL_V_P or a negative value BALL_V_N • The current value of each component is kept in x_delta_reg and y_delta_reg ECE 448 – FPGA and ASIC Design with VHDL 17

Velocity Components of the Ball x x_delta_reg = BALL_V_N y_delta_reg = BALL_V_N x_delta_reg = BALL_V_P y_delta_reg = BALL_V_N x_delta_reg = BALL_V_N y_delta_reg = BALL_V_P x_delta_reg = BALL_V_P y ECE 448 – FPGA and ASIC Design with VHDL 18

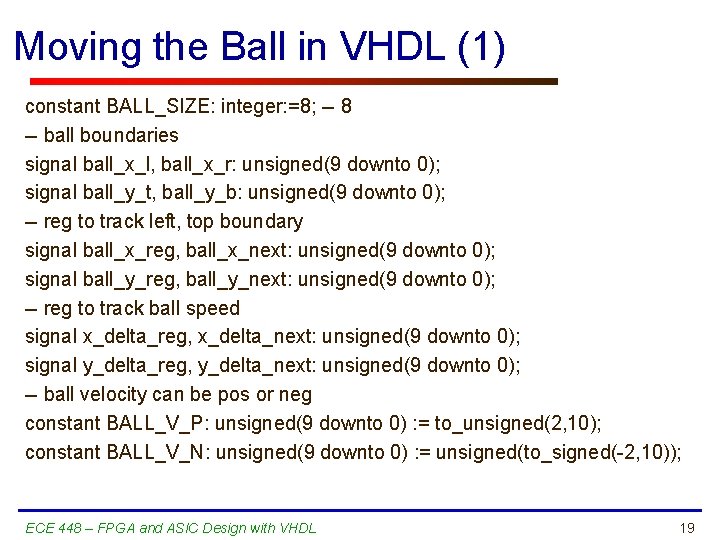

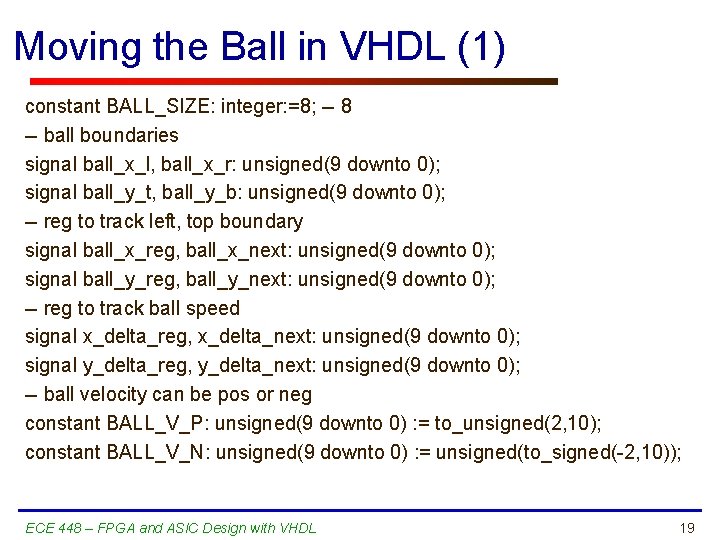

Moving the Ball in VHDL (1) constant BALL_SIZE: integer: =8; -- 8 -- ball boundaries signal ball_x_l, ball_x_r: unsigned(9 downto 0); signal ball_y_t, ball_y_b: unsigned(9 downto 0); -- reg to track left, top boundary signal ball_x_reg, ball_x_next: unsigned(9 downto 0); signal ball_y_reg, ball_y_next: unsigned(9 downto 0); -- reg to track ball speed signal x_delta_reg, x_delta_next: unsigned(9 downto 0); signal y_delta_reg, y_delta_next: unsigned(9 downto 0); -- ball velocity can be pos or neg constant BALL_V_P: unsigned(9 downto 0) : = to_unsigned(2, 10); constant BALL_V_N: unsigned(9 downto 0) : = unsigned(to_signed(-2, 10)); ECE 448 – FPGA and ASIC Design with VHDL 19

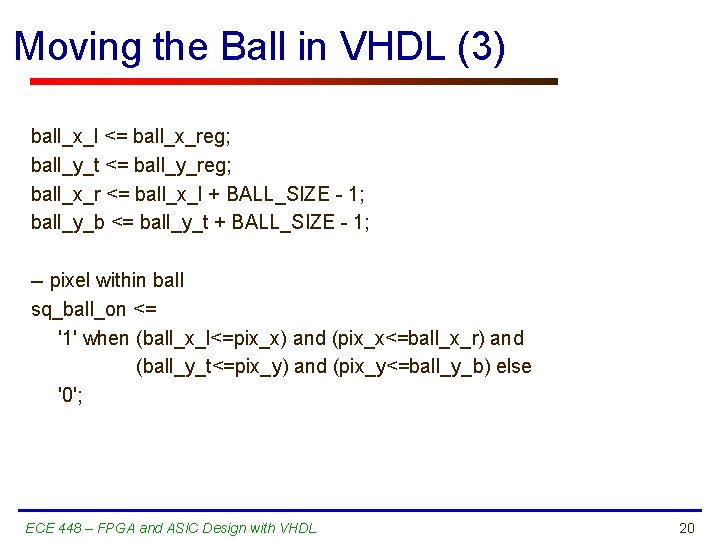

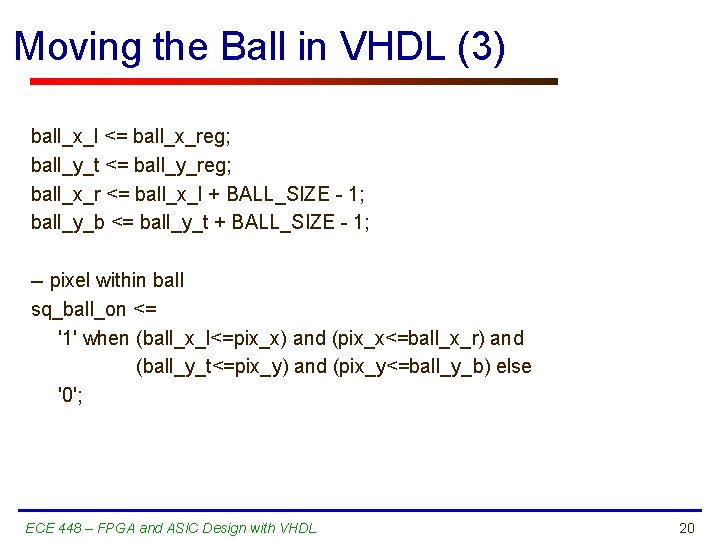

Moving the Ball in VHDL (3) ball_x_l <= ball_x_reg; ball_y_t <= ball_y_reg; ball_x_r <= ball_x_l + BALL_SIZE - 1; ball_y_b <= ball_y_t + BALL_SIZE - 1; -- pixel within ball sq_ball_on <= '1' when (ball_x_l<=pix_x) and (pix_x<=ball_x_r) and (ball_y_t<=pix_y) and (pix_y<=ball_y_b) else '0'; ECE 448 – FPGA and ASIC Design with VHDL 20

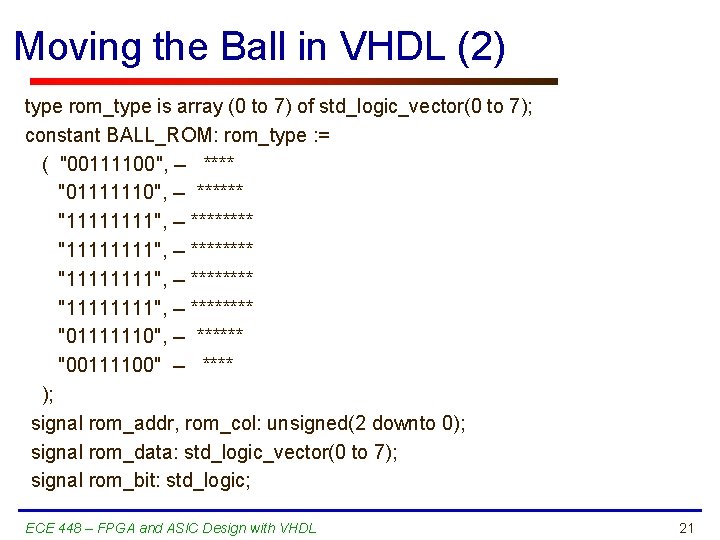

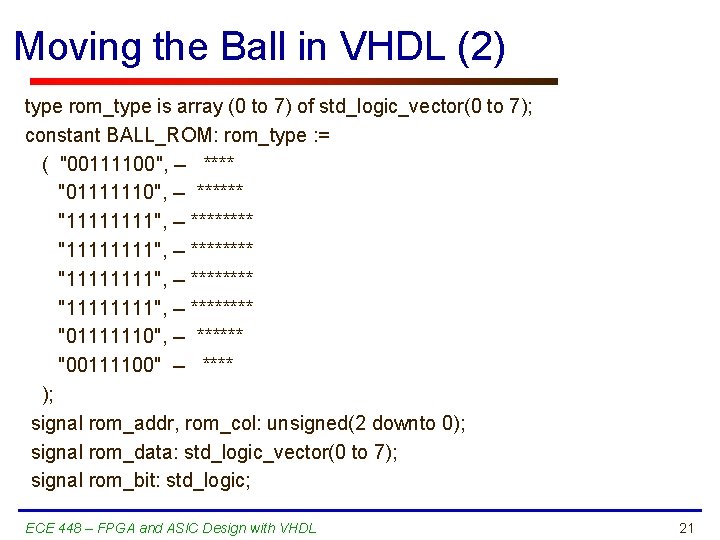

Moving the Ball in VHDL (2) type rom_type is array (0 to 7) of std_logic_vector(0 to 7); constant BALL_ROM: rom_type : = ( "00111100", -- **** "01111110", -- ****** "11111111", -- ******** "01111110", -- ****** "00111100" -- **** ); signal rom_addr, rom_col: unsigned(2 downto 0); signal rom_data: std_logic_vector(0 to 7); signal rom_bit: std_logic; ECE 448 – FPGA and ASIC Design with VHDL 21

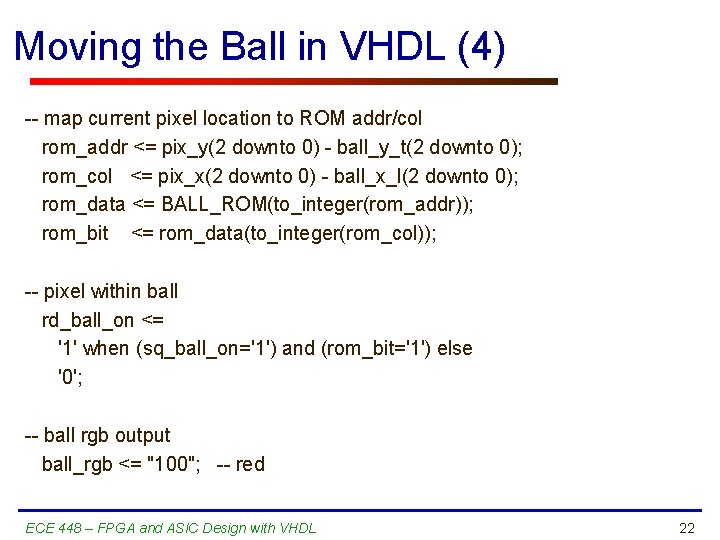

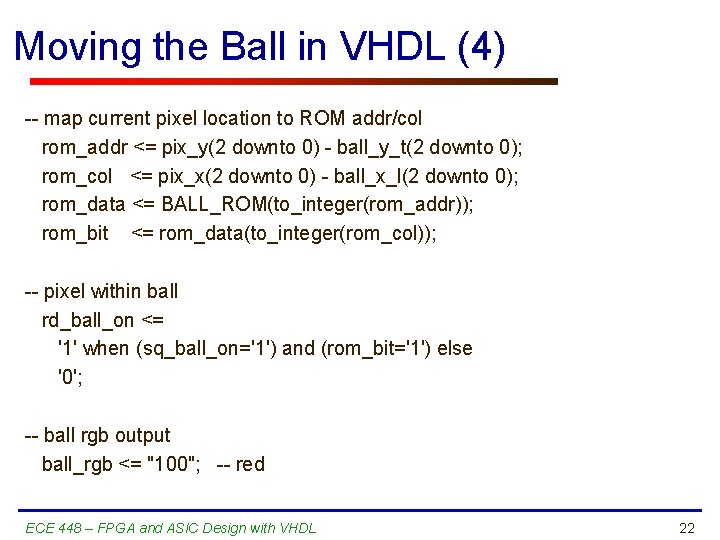

Moving the Ball in VHDL (4) -- map current pixel location to ROM addr/col rom_addr <= pix_y(2 downto 0) - ball_y_t(2 downto 0); rom_col <= pix_x(2 downto 0) - ball_x_l(2 downto 0); rom_data <= BALL_ROM(to_integer(rom_addr)); rom_bit <= rom_data(to_integer(rom_col)); -- pixel within ball rd_ball_on <= '1' when (sq_ball_on='1') and (rom_bit='1') else '0'; -- ball rgb output ball_rgb <= "100"; -- red ECE 448 – FPGA and ASIC Design with VHDL 22

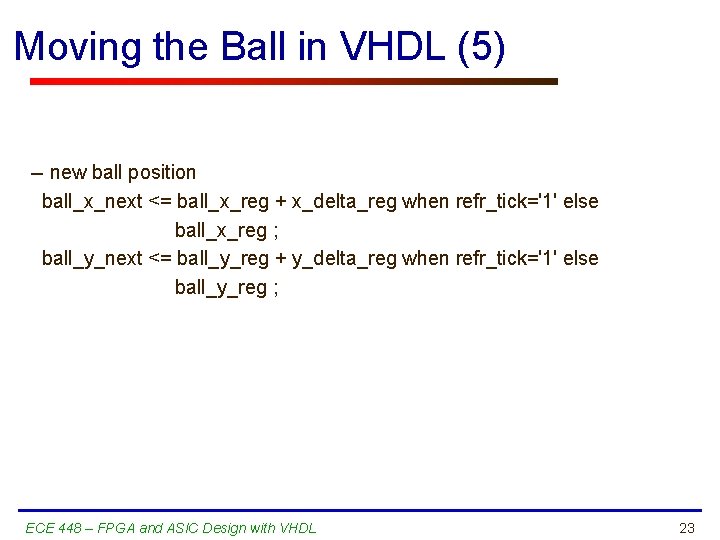

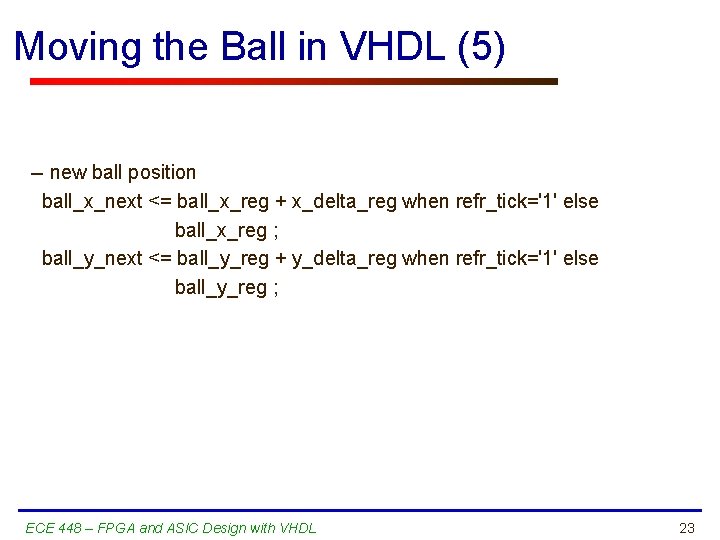

Moving the Ball in VHDL (5) -- new ball position ball_x_next <= ball_x_reg + x_delta_reg when refr_tick='1' else ball_x_reg ; ball_y_next <= ball_y_reg + y_delta_reg when refr_tick='1' else ball_y_reg ; ECE 448 – FPGA and ASIC Design with VHDL 23

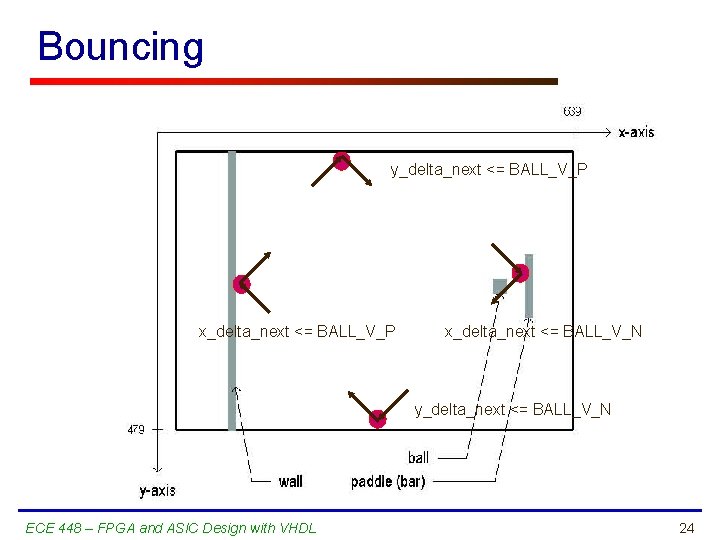

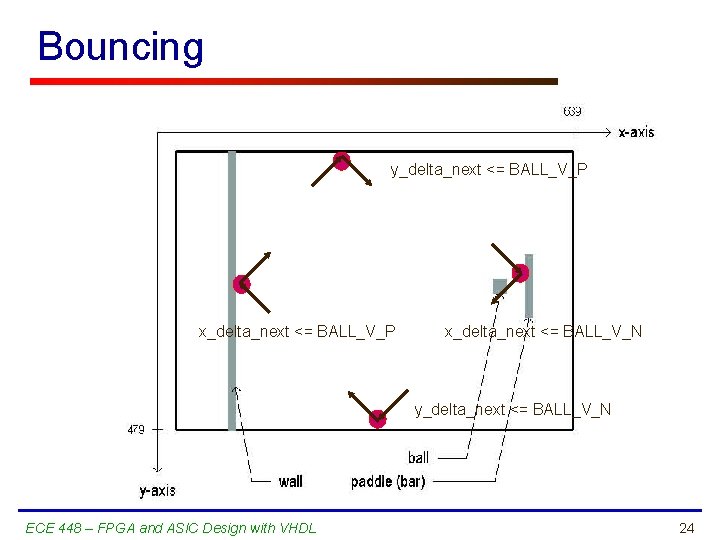

Bouncing y_delta_next <= BALL_V_P x_delta_next <= BALL_V_N y_delta_next <= BALL_V_N ECE 448 – FPGA and ASIC Design with VHDL 24

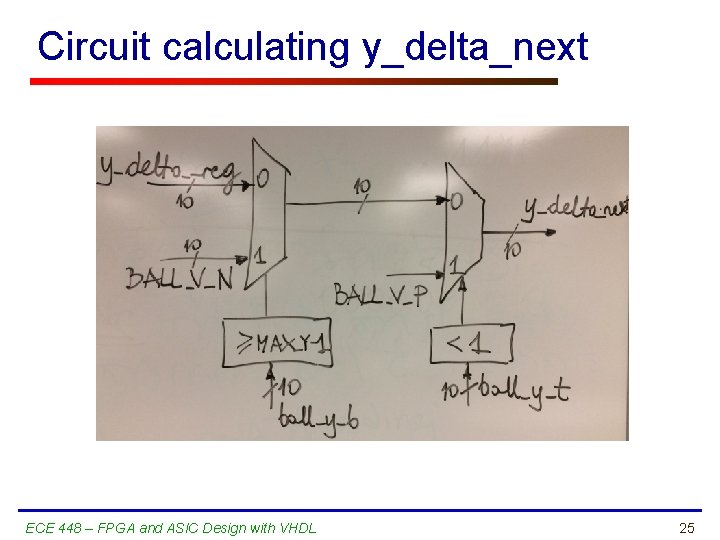

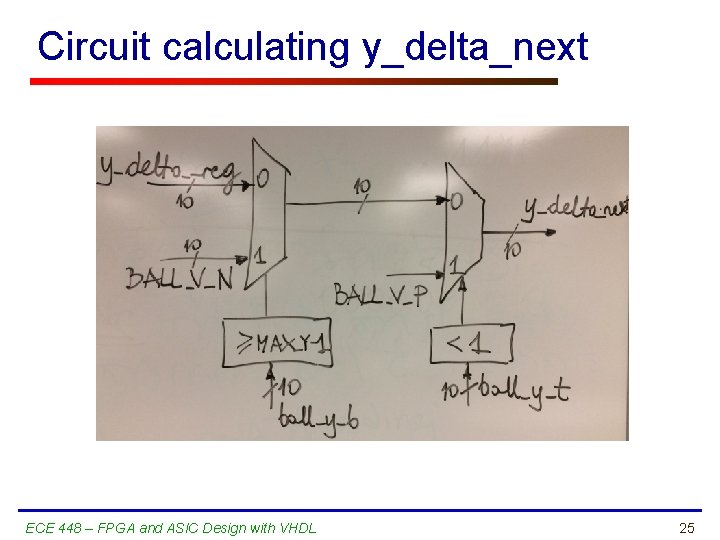

Circuit calculating y_delta_next ECE 448 – FPGA and ASIC Design with VHDL 25

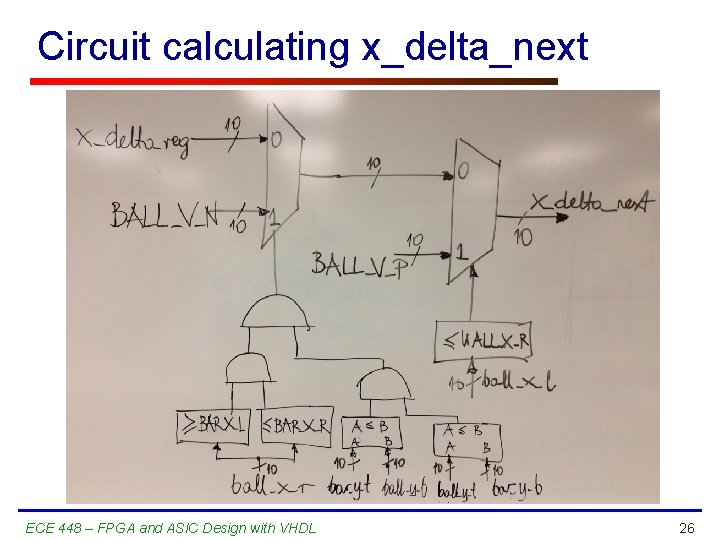

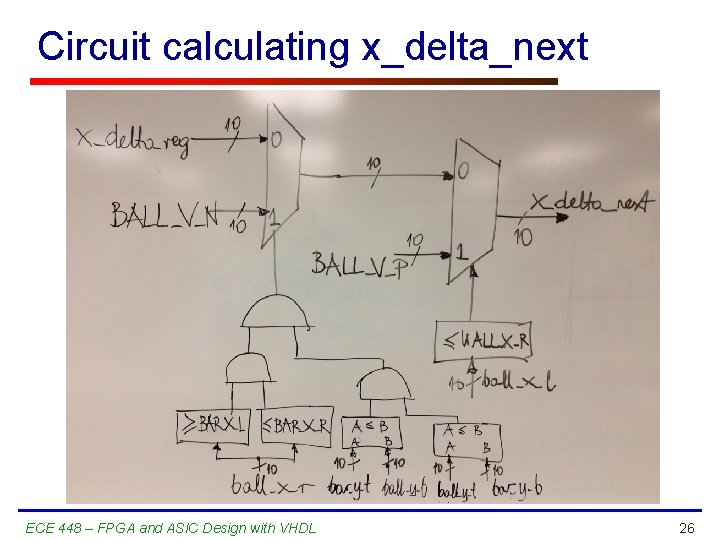

Circuit calculating x_delta_next ECE 448 – FPGA and ASIC Design with VHDL 26

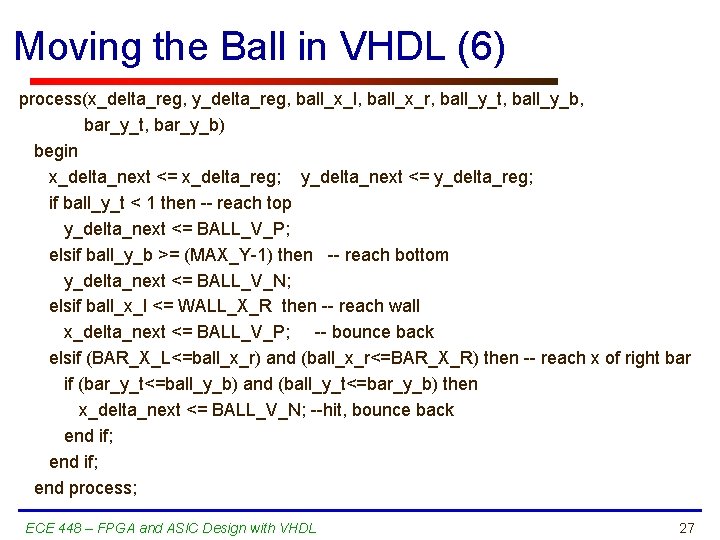

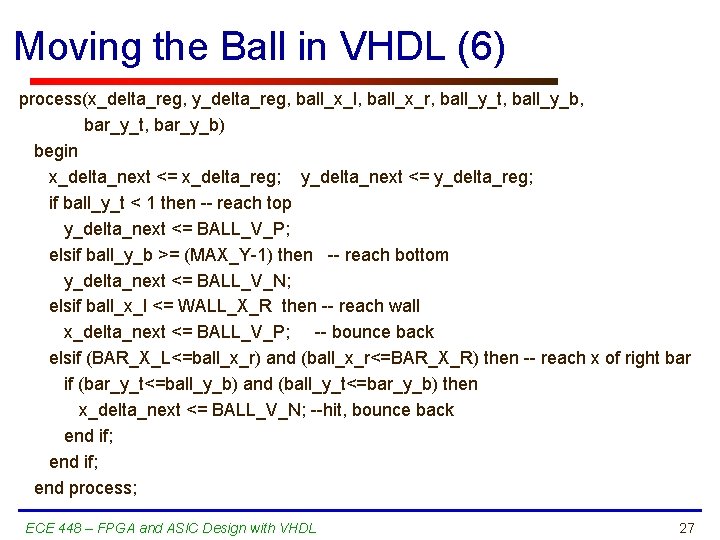

Moving the Ball in VHDL (6) process(x_delta_reg, y_delta_reg, ball_x_l, ball_x_r, ball_y_t, ball_y_b, bar_y_t, bar_y_b) begin x_delta_next <= x_delta_reg; y_delta_next <= y_delta_reg; if ball_y_t < 1 then -- reach top y_delta_next <= BALL_V_P; elsif ball_y_b >= (MAX_Y-1) then -- reach bottom y_delta_next <= BALL_V_N; elsif ball_x_l <= WALL_X_R then -- reach wall x_delta_next <= BALL_V_P; -- bounce back elsif (BAR_X_L<=ball_x_r) and (ball_x_r<=BAR_X_R) then -- reach x of right bar if (bar_y_t<=ball_y_b) and (ball_y_t<=bar_y_b) then x_delta_next <= BALL_V_N; --hit, bounce back end if; end process; ECE 448 – FPGA and ASIC Design with VHDL 27

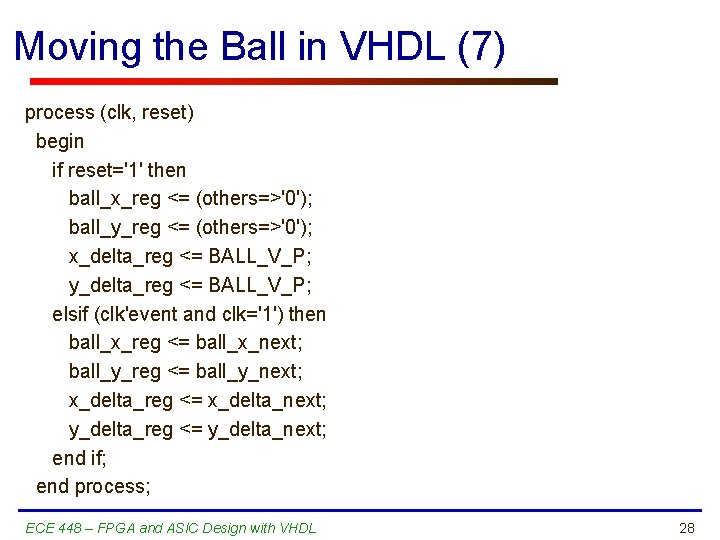

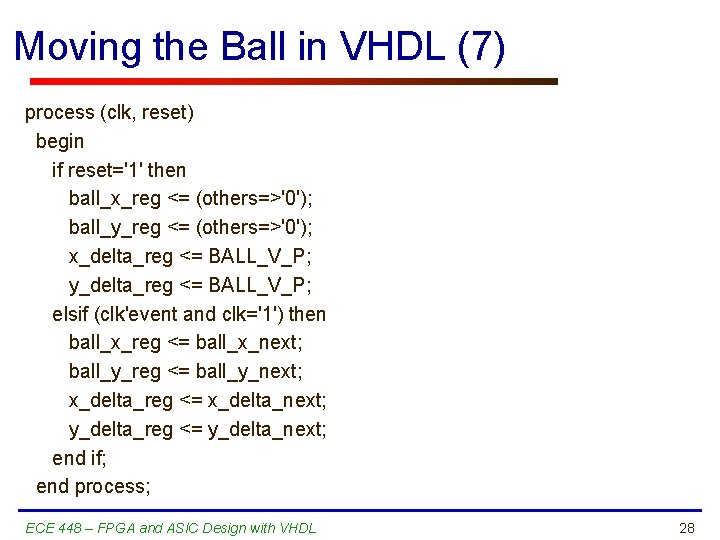

Moving the Ball in VHDL (7) process (clk, reset) begin if reset='1' then ball_x_reg <= (others=>'0'); ball_y_reg <= (others=>'0'); x_delta_reg <= BALL_V_P; y_delta_reg <= BALL_V_P; elsif (clk'event and clk='1') then ball_x_reg <= ball_x_next; ball_y_reg <= ball_y_next; x_delta_reg <= x_delta_next; y_delta_reg <= y_delta_next; end if; end process; ECE 448 – FPGA and ASIC Design with VHDL 28

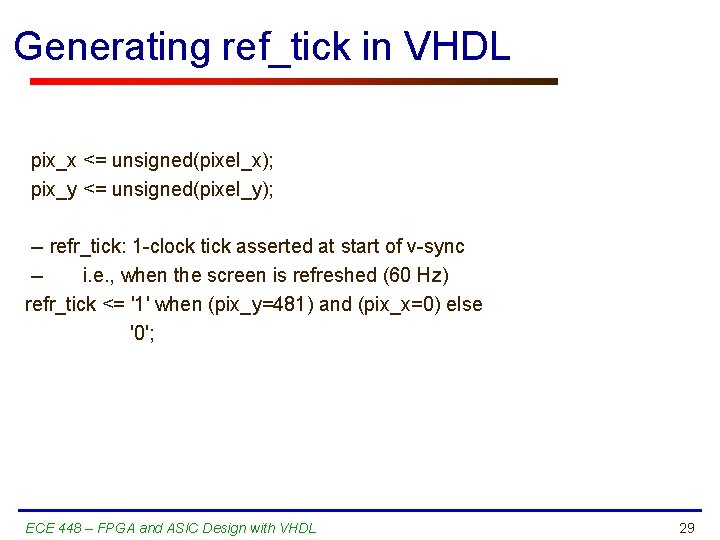

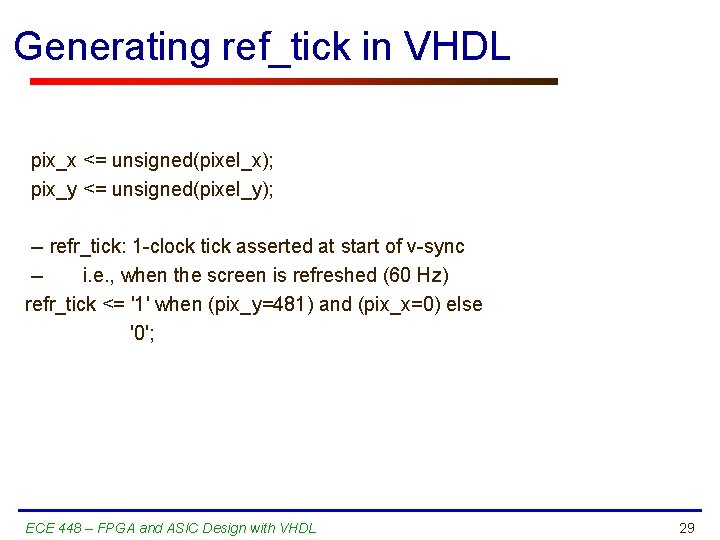

Generating ref_tick in VHDL pix_x <= unsigned(pixel_x); pix_y <= unsigned(pixel_y); -- refr_tick: 1 -clock tick asserted at start of v-sync -i. e. , when the screen is refreshed (60 Hz) refr_tick <= '1' when (pix_y=481) and (pix_x=0) else '0'; ECE 448 – FPGA and ASIC Design with VHDL 29

Vertical Synchronization ECE 448 – FPGA and ASIC Design with VHDL 30