HERD Trigger Subsystem hardware Design HERD Group baotwihep

HERD Trigger Sub-system hardware Design HERD Group baotw@ihep. ac. cn Institute of High Energy Physics, CAS 2018. 03. 27

HERD Trigger Sub-system Requirements and performance Structure, components, interface Data & trigger flow, Working mode , Power management

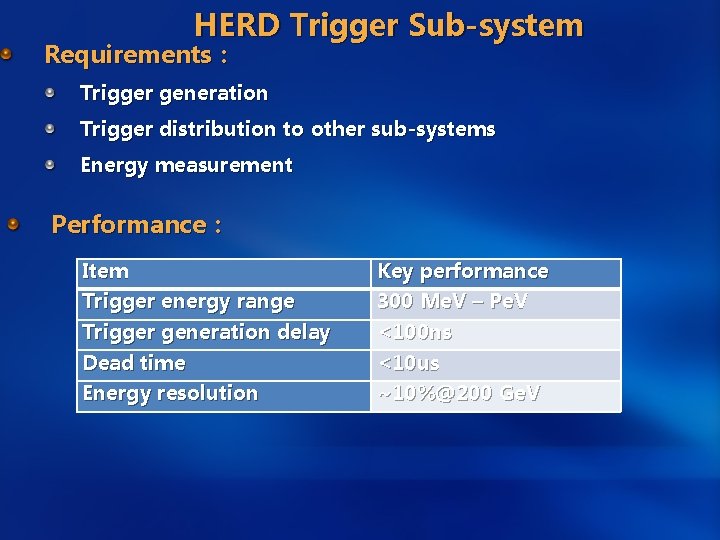

HERD Trigger Sub-system Requirements: Trigger generation Trigger distribution to other sub-systems Energy measurement Performance: Item Trigger energy range Key performance 300 Me. V – Pe. V Trigger generation delay Dead time <100 ns <10 us Energy resolution ~10%@200 Ge. V

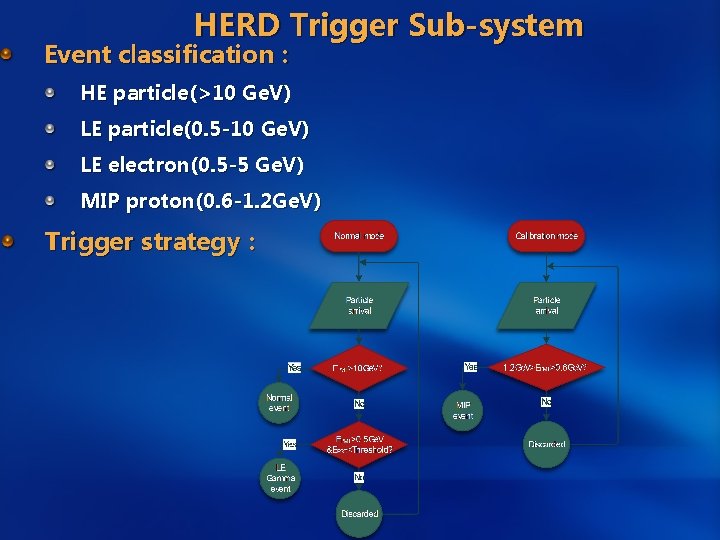

HERD Trigger Sub-system Event classification: HE particle(>10 Ge. V) LE particle(0. 5 -10 Ge. V) LE electron(0. 5 -5 Ge. V) MIP proton(0. 6 -1. 2 Ge. V) Trigger strategy:

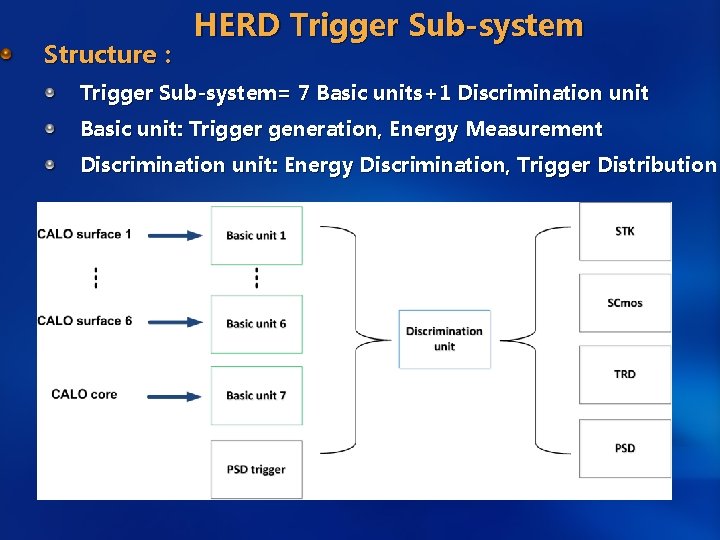

Structure: HERD Trigger Sub-system= 7 Basic units+1 Discrimination unit Basic unit: Trigger generation, Energy Measurement Discrimination unit: Energy Discrimination, Trigger Distribution

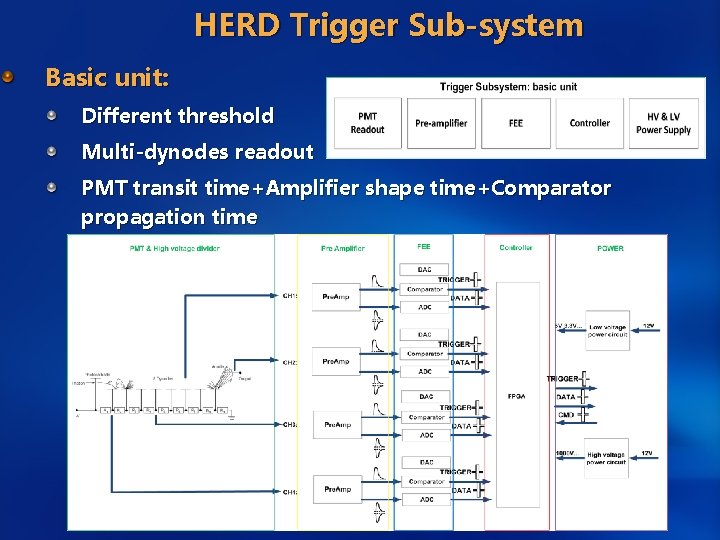

HERD Trigger Sub-system Basic unit: Different threshold Multi-dynodes readout PMT transit time+Amplifier shape time+Comparator propagation time

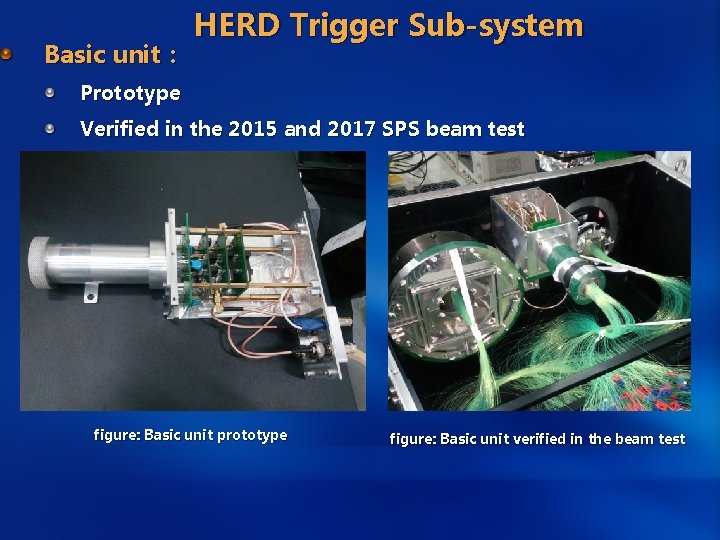

Basic unit: HERD Trigger Sub-system Prototype Verified in the 2015 and 2017 SPS beam test figure: Basic unit prototype figure: Basic unit verified in the beam test

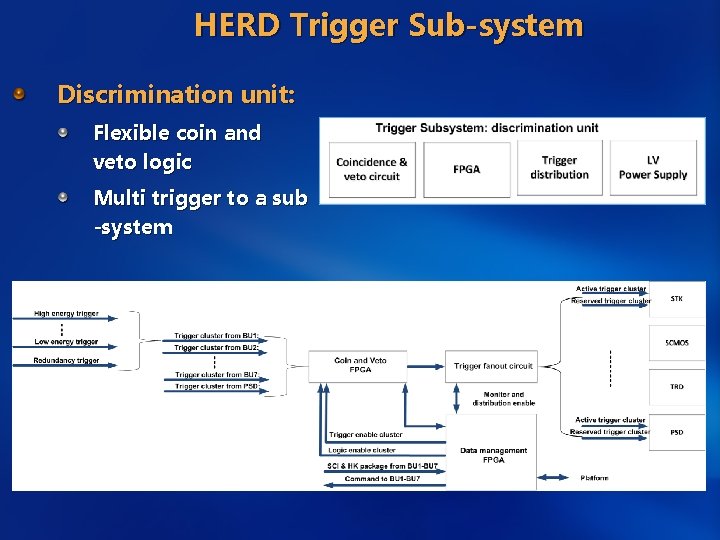

HERD Trigger Sub-system Discrimination unit: Flexible coin and veto logic Multi trigger to a sub -system

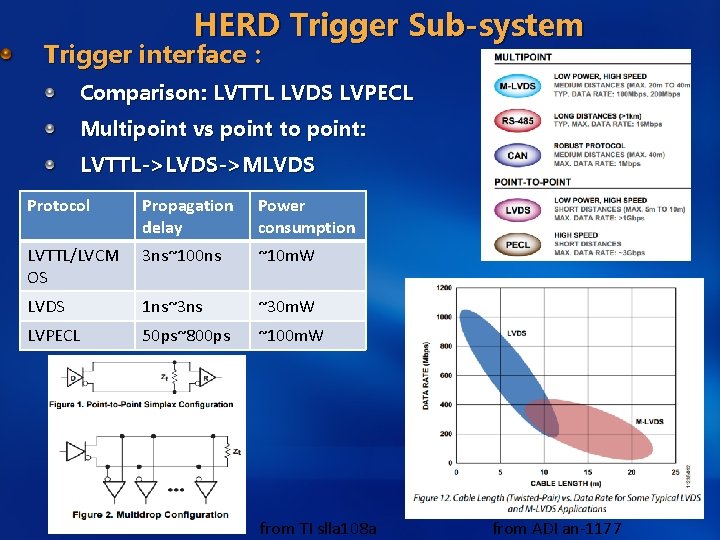

HERD Trigger Sub-system Trigger interface: Comparison: LVTTL LVDS LVPECL Multipoint vs point to point: LVTTL->LVDS->MLVDS Protocol Propagation delay Power consumption LVTTL/LVCM OS 3 ns~100 ns ~10 m. W LVDS 1 ns~3 ns ~30 m. W LVPECL 50 ps~800 ps ~100 m. W from TI slla 108 a from ADI an-1177

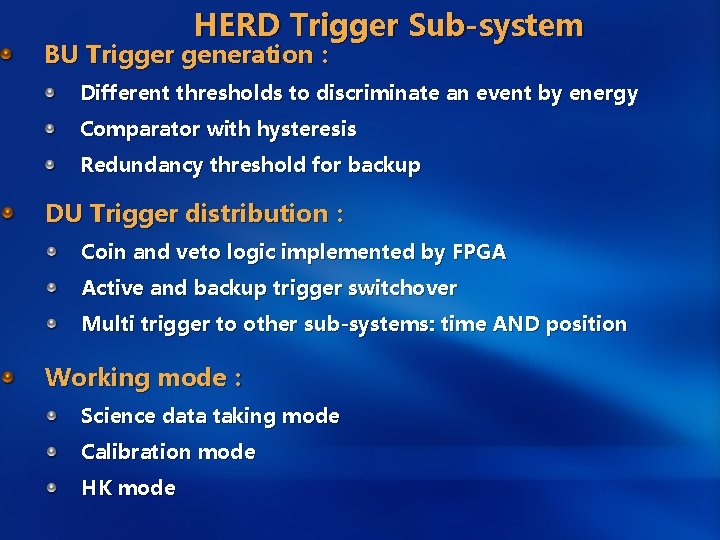

HERD Trigger Sub-system BU Trigger generation: Different thresholds to discriminate an event by energy Comparator with hysteresis Redundancy threshold for backup DU Trigger distribution: Coin and veto logic implemented by FPGA Active and backup trigger switchover Multi trigger to other sub-systems: time AND position Working mode: Science data taking mode Calibration mode HK mode

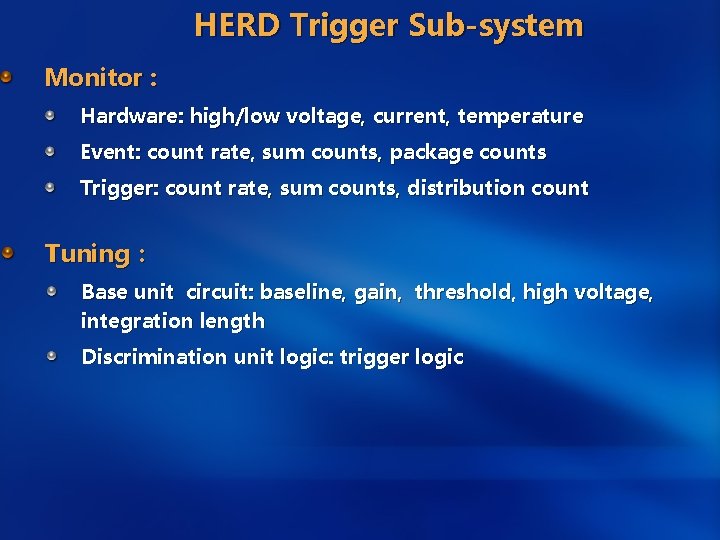

HERD Trigger Sub-system Monitor : Hardware: high/low voltage, current, temperature Event: count rate, sum counts, package counts Trigger: count rate, sum counts, distribution count Tuning: Base unit circuit: baseline, gain, threshold, high voltage, integration length Discrimination unit logic: trigger logic

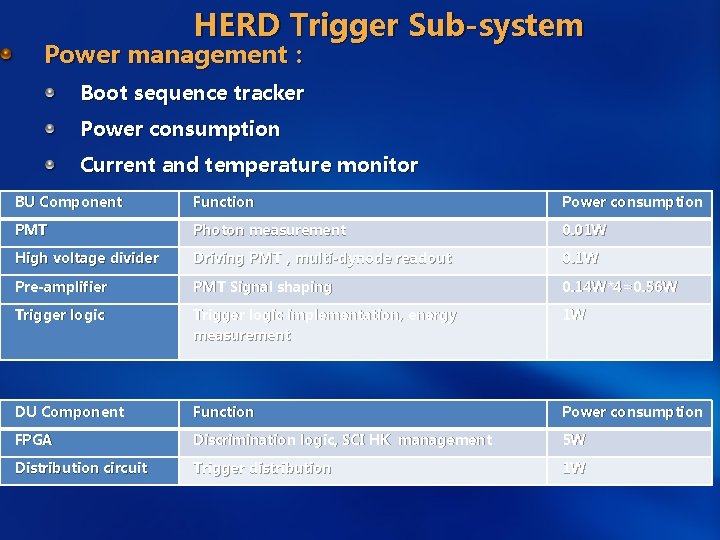

HERD Trigger Sub-system Power management: Boot sequence tracker Power consumption Current and temperature monitor BU Component Function Power consumption PMT Photon measurement 0. 01 W High voltage divider Driving PMT,multi-dynode readout 0. 1 W Pre-amplifier PMT Signal shaping 0. 14 W*4=0. 56 W Trigger logic implementation, energy measurement 1 W DU Component Function Power consumption FPGA Discrimination logic, SCI HK management 5 W Distribution circuit Trigger distribution 1 W

Summary Herd Trigger Sub-system : Requirements and performance Base units and discrimination unit Trigger and science data flow Interface Working mode Monitor Tuning Power management

Thank you! Tianwei Bao baotw@ihep. ac. cn Institute of High Energy Physics, CAS 2018. 03. 27

- Slides: 14