CMOS Detector Technology Markus Loose Alan Hoffman Vyshnavi

- Slides: 44

CMOS Detector Technology Markus Loose Alan Hoffman Vyshnavi Suntharalingam Rockwell Scientific Raytheon Vision Systems MIT Lincoln Laboratory Scientific Detector Workshop, Sicily 2005 CMOS -

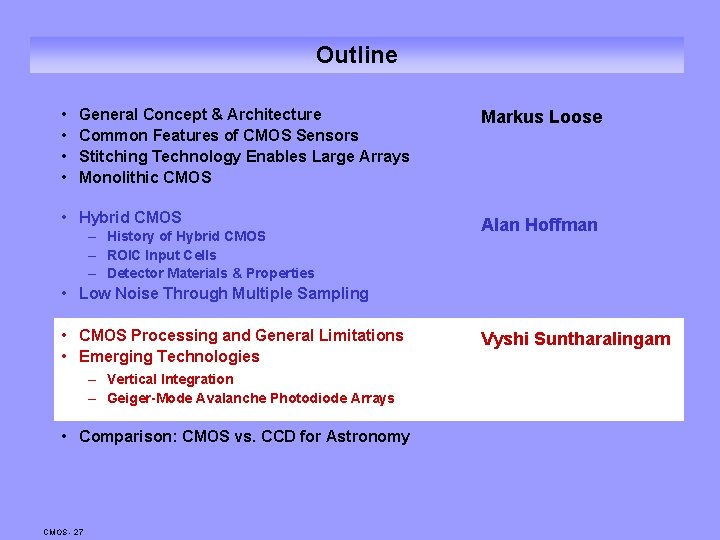

Outline • • General Concept & Architecture Common Features of CMOS Sensors Stitching Technology Enables Large Arrays Monolithic CMOS • Hybrid CMOS – History of Hybrid CMOS – ROIC Input Cells – Detector Materials & Properties Markus Loose Alan Hoffman • Low Noise Through Multiple Sampling • CMOS Processing and General Limitations • Emerging Technologies – Vertical Integration – Geiger-Mode Avalanche Photodiode Arrays • Comparison: CMOS vs. CCD for Astronomy CMOS - 2 Vyshi Suntharalingam

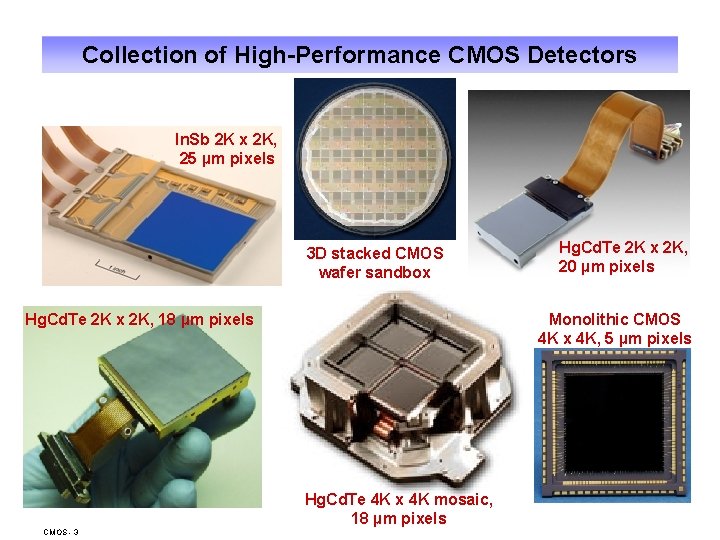

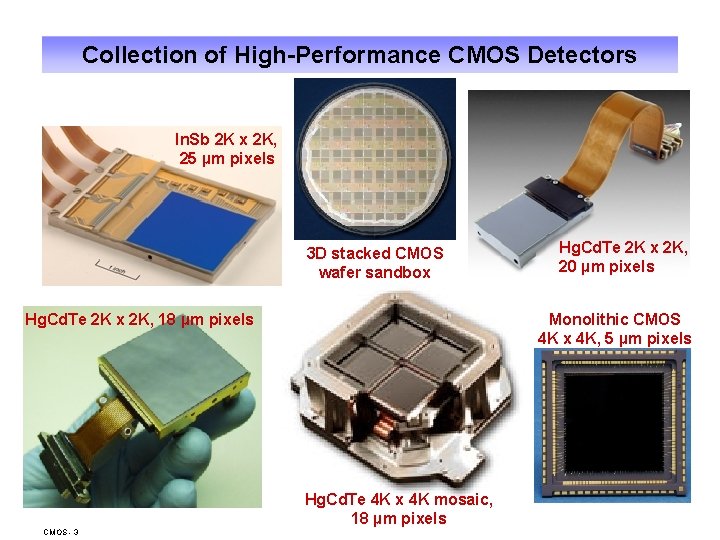

Collection of High-Performance CMOS Detectors In. Sb 2 K x 2 K, 25 µm pixels 3 D stacked CMOS wafer sandbox Hg. Cd. Te 2 K x 2 K, 18 µm pixels CMOS - 3 Hg. Cd. Te 2 K x 2 K, 20 µm pixels Monolithic CMOS 4 K x 4 K, 5 µm pixels Hg. Cd. Te 4 K x 4 K mosaic, 18 µm pixels

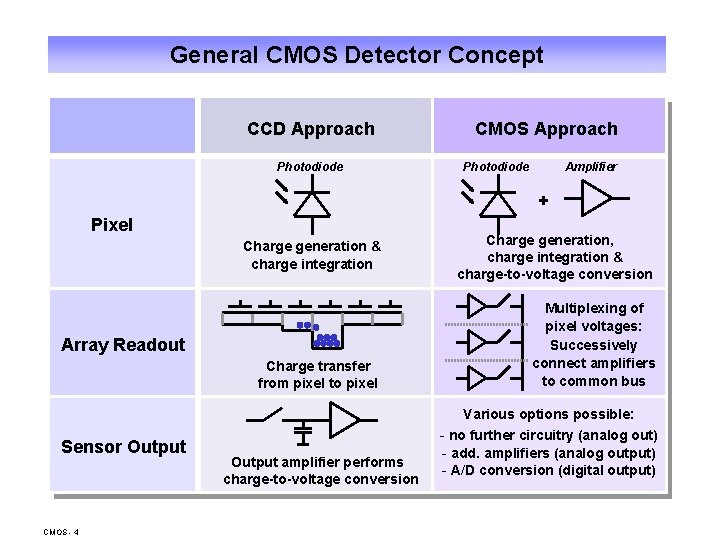

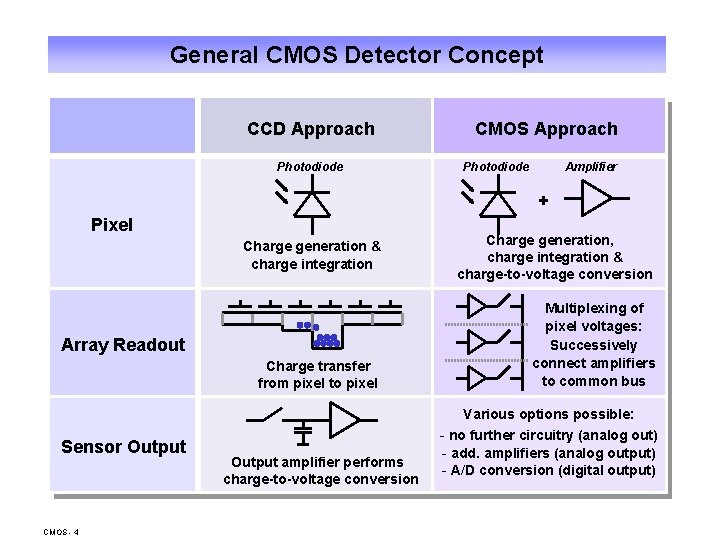

General CMOS Detector Concept CCD Approach Photodiode CMOS Approach Photodiode Amplifier + Pixel Charge generation & charge integration Array Readout Charge transfer from pixel to pixel Sensor Output CMOS - 4 Output amplifier performs charge-to-voltage conversion Charge generation, charge integration & charge-to-voltage conversion Multiplexing of pixel voltages: Successively connect amplifiers to common bus Various options possible: - no further circuitry (analog out) - add. amplifiers (analog output) - A/D conversion (digital output)

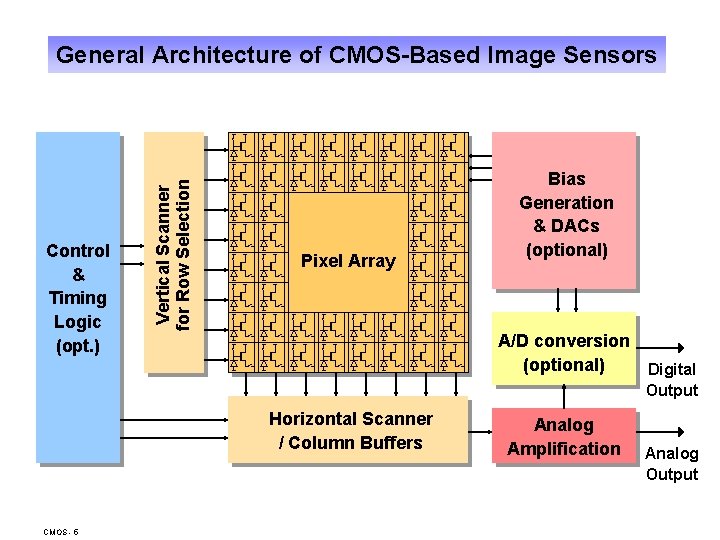

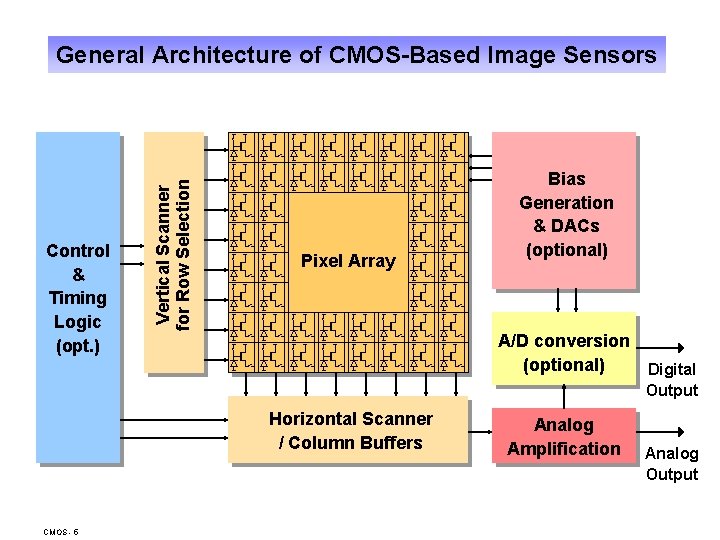

Control & Timing Logic (opt. ) Vertical Scanner for Row Selection General Architecture of CMOS-Based Image Sensors Pixel Array Bias Generation & DACs (optional) A/D conversion (optional) Digital Output Horizontal Scanner / Column Buffers CMOS - 5 Analog Amplification Analog Output

Common CMOS Features • CMOS sensors/multiplexers utilize the same process as modern microchips – Many foundries available worldwide – Cost efficient – Latest processes available down to 0. 13 µm • CMOS process enables integration of many additional features – – – Various pixel circuits from 3 transistors up to many 100 transistors per pixel Random pixel access, windowing, subsampling and binning Bias generation (DACs) Analog signal processing (e. g. CDS, programmable gain, noise filter) A/D conversion Logic (timing control, digital signal processing, etc. ) • Electronic shutter (snapshot, rolling shutter, non-destructive reads) – No mechanical shutter required • Low power consumption • Radiation tolerant (by process and by design) CMOS - 6

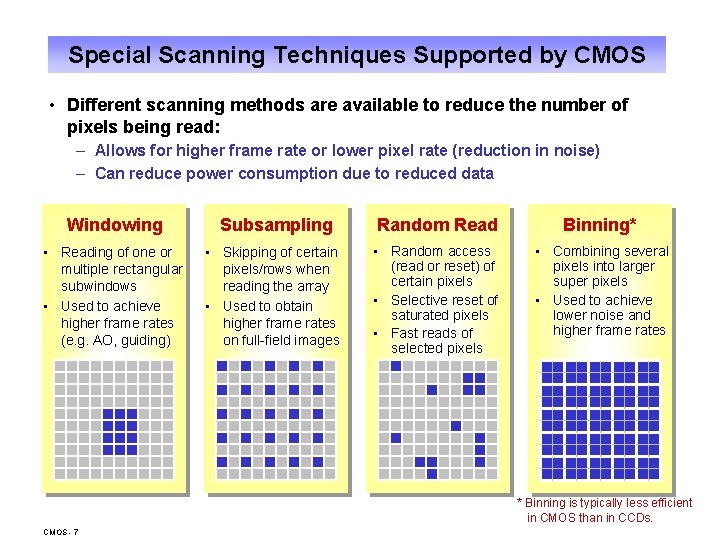

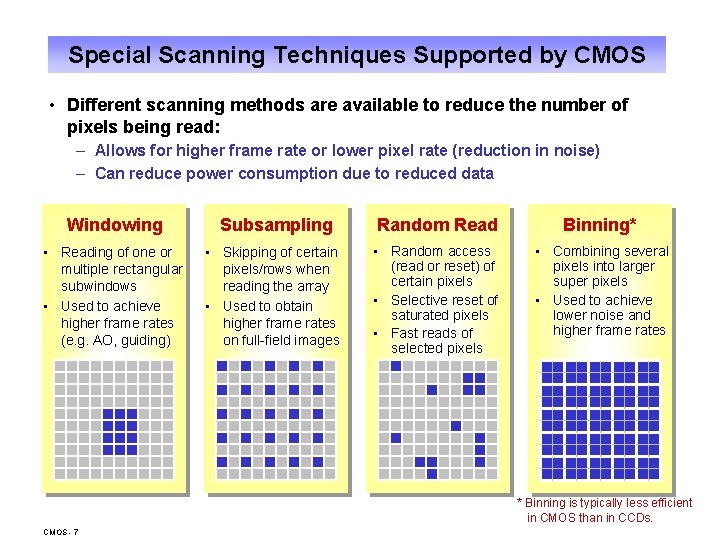

Special Scanning Techniques Supported by CMOS • Different scanning methods are available to reduce the number of pixels being read: – Allows for higher frame rate or lower pixel rate (reduction in noise) – Can reduce power consumption due to reduced data Windowing Subsampling Random Read Binning* • Reading of one or multiple rectangular subwindows • Used to achieve higher frame rates (e. g. AO, guiding) • Skipping of certain pixels/rows when reading the array • Used to obtain higher frame rates on full-field images • Random access (read or reset) of certain pixels • Selective reset of saturated pixels • Fast reads of selected pixels • Combining several pixels into larger super pixels • Used to achieve lower noise and higher frame rates * Binning is typically less efficient in CMOS than in CCDs. CMOS - 7

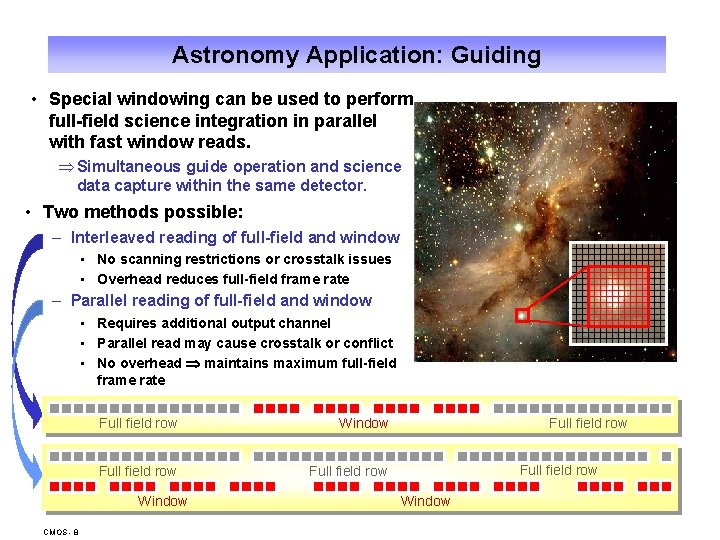

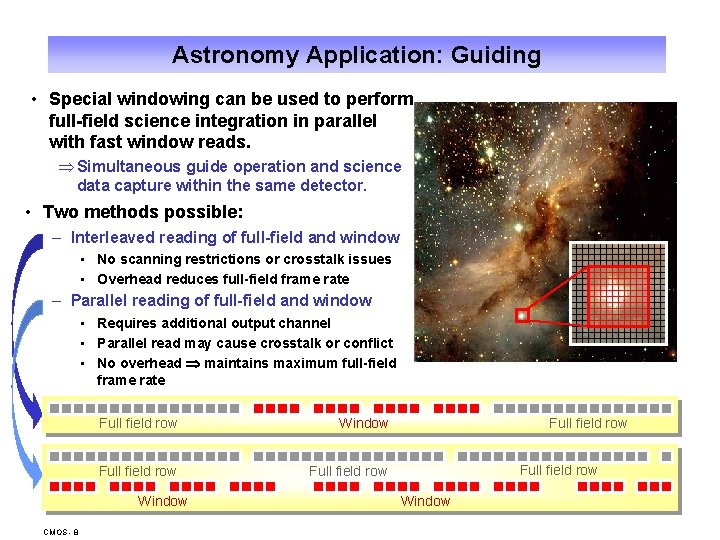

Astronomy Application: Guiding • Special windowing can be used to perform full-field science integration in parallel with fast window reads. Þ Simultaneous guide operation and science data capture within the same detector. • Two methods possible: – Interleaved reading of full-field and window • No scanning restrictions or crosstalk issues • Overhead reduces full-field frame rate – Parallel reading of full-field and window • Requires additional output channel • Parallel read may cause crosstalk or conflict • No overhead maintains maximum full-field frame rate Full field row Window CMOS - 8 Full field row Window

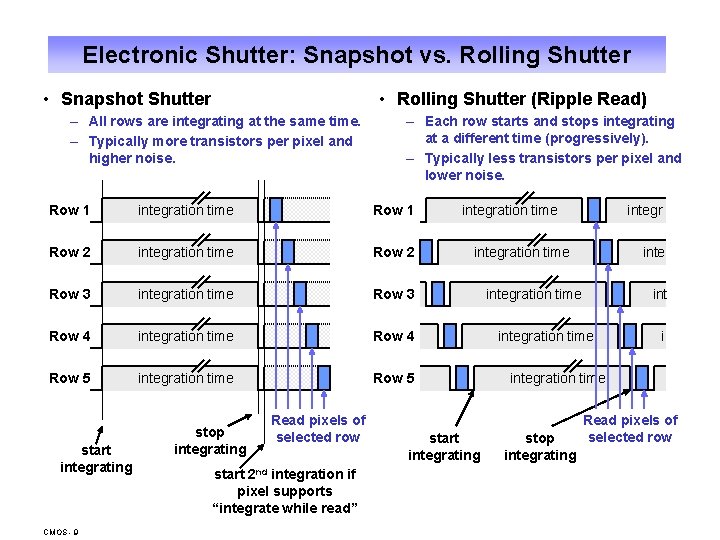

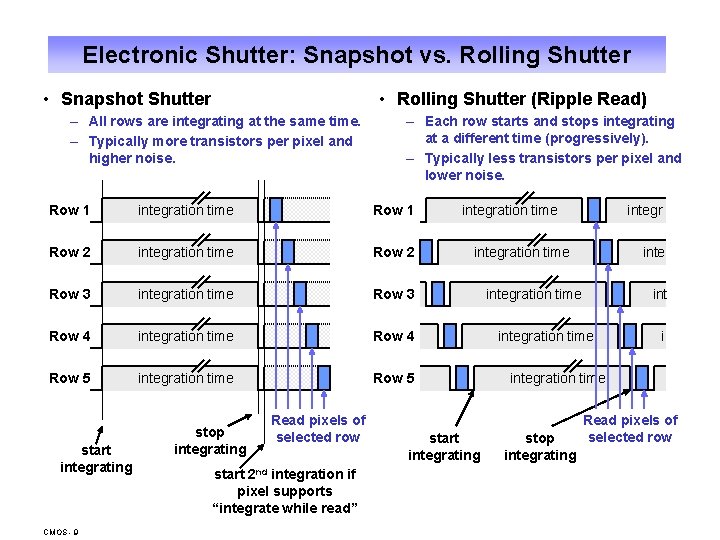

Electronic Shutter: Snapshot vs. Rolling Shutter • Snapshot Shutter • Rolling Shutter (Ripple Read) – All rows are integrating at the same time. – Typically more transistors per pixel and higher noise. – Each row starts and stops integrating at a different time (progressively). – Typically less transistors per pixel and lower noise. Row 1 integration time Row 1 Row 2 integration time Row 2 Row 3 integration time Row 3 Row 4 integration time Row 4 Row 5 integration time Row 5 start integrating CMOS - 9 stop integrating Read pixels of selected row start 2 nd integration if pixel supports “integrate while read” integration time start integrating integration time i integration time stop integrating Read pixels of selected row

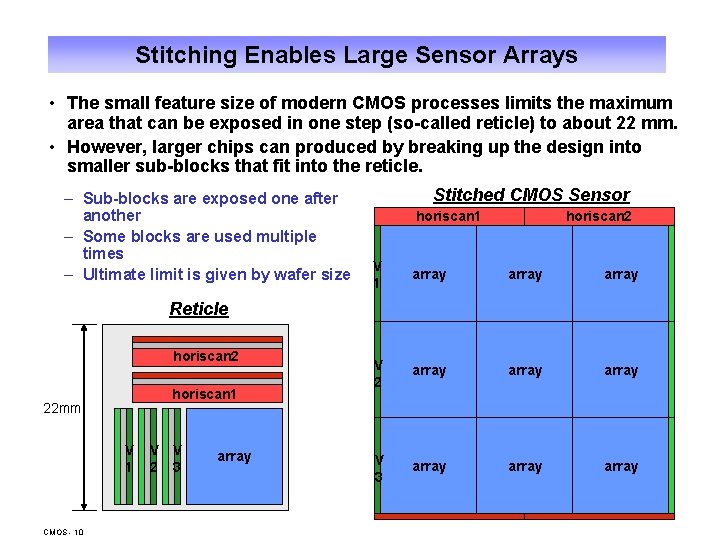

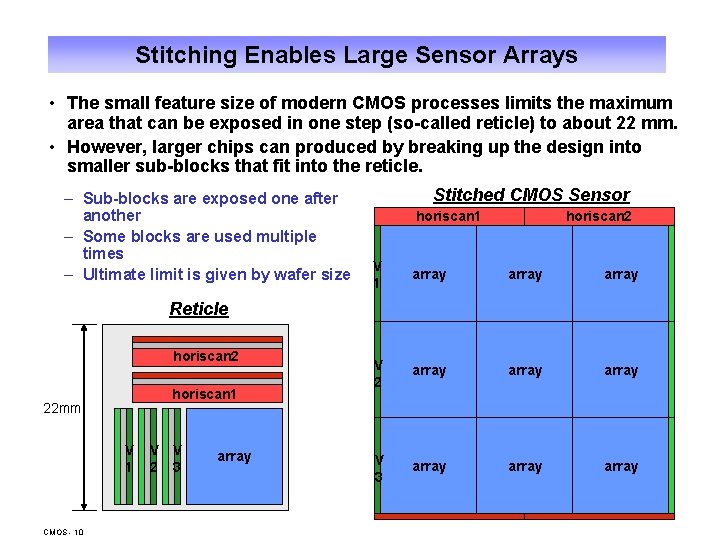

Stitching Enables Large Sensor Arrays • The small feature size of modern CMOS processes limits the maximum area that can be exposed in one step (so-called reticle) to about 22 mm. • However, larger chips can produced by breaking up the design into smaller sub-blocks that fit into the reticle. – Sub-blocks are exposed one after another – Some blocks are used multiple times – Ultimate limit is given by wafer size Stitched CMOS Sensor horiscan 1 horiscan 2 V 1 array V 2 array V 3 array Reticle horiscan 2 horiscan 1 22 mm V 1 CMOS - 10 V V 2 3 array

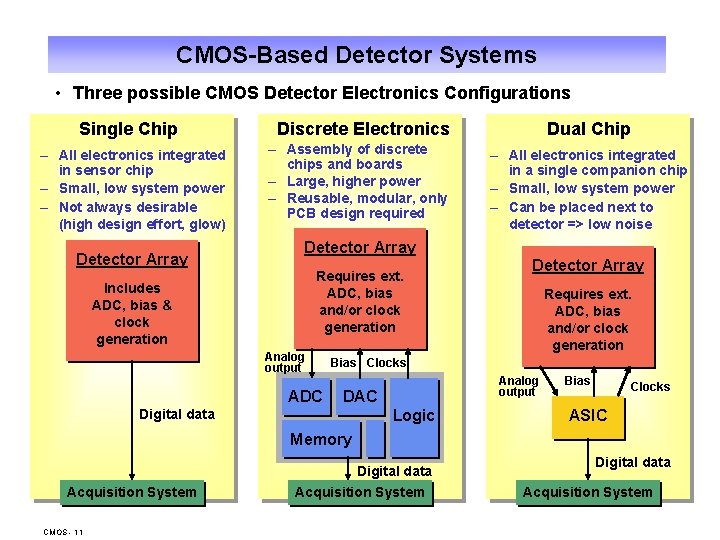

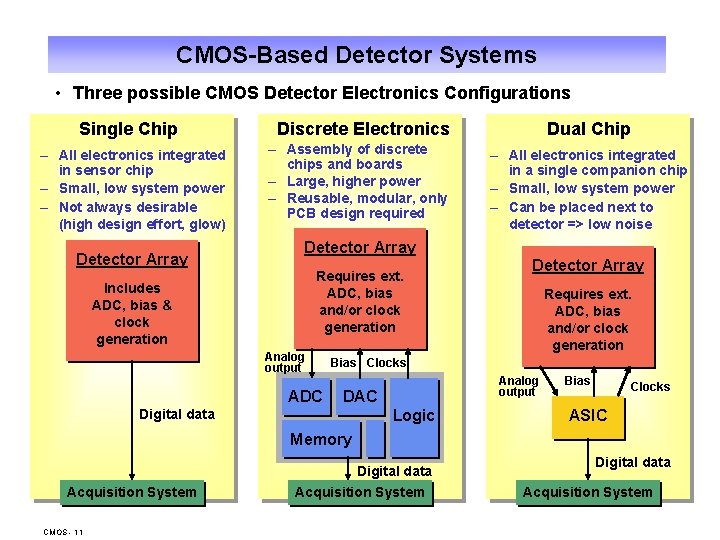

CMOS-Based Detector Systems • Three possible CMOS Detector Electronics Configurations Single Chip – All electronics integrated in sensor chip – Small, low system power – Not always desirable (high design effort, glow) Detector Array Discrete Electronics – Assembly of discrete chips and boards – Large, higher power – Reusable, modular, only PCB design required Dual Chip – All electronics integrated in a single companion chip – Small, low system power – Can be placed next to detector => low noise Detector Array Requires ext. ADC, bias and/or clock generation Includes ADC, bias & clock generation Analog output ADC Detector Array Requires ext. ADC, bias and/or clock generation Bias Clocks Analog output DAC Digital data Logic Bias Clocks ASIC Memory Digital data Acquisition System CMOS - 11 Acquisition System Digital data Acquisition System

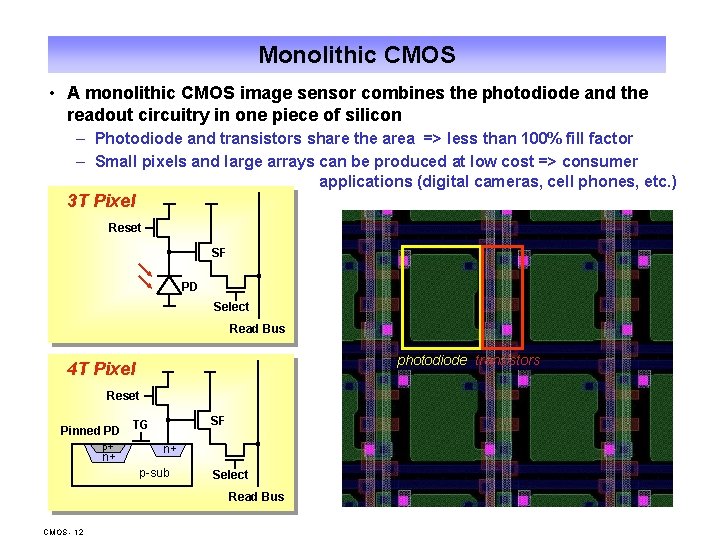

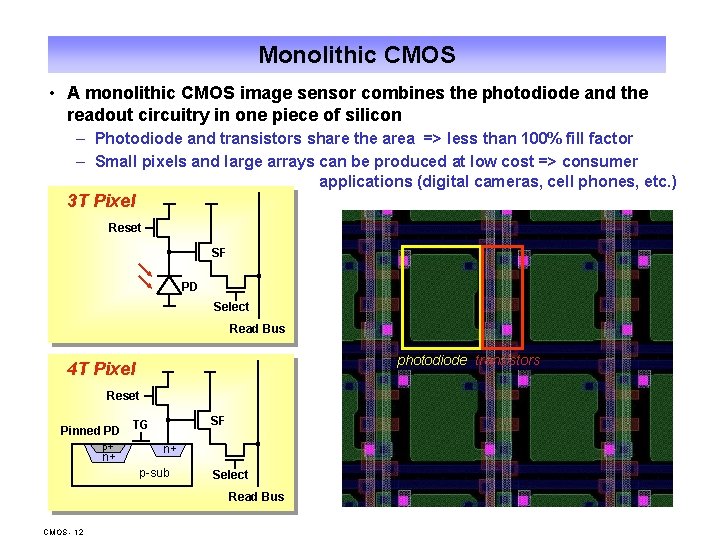

Monolithic CMOS • A monolithic CMOS image sensor combines the photodiode and the readout circuitry in one piece of silicon – Photodiode and transistors share the area => less than 100% fill factor – Small pixels and large arrays can be produced at low cost => consumer applications (digital cameras, cell phones, etc. ) 3 T Pixel Reset SF PD Select Read Bus photodiode transistors 4 T Pixel Reset Pinned PD p+ n+ SF TG n+ p-sub Select Read Bus CMOS - 12

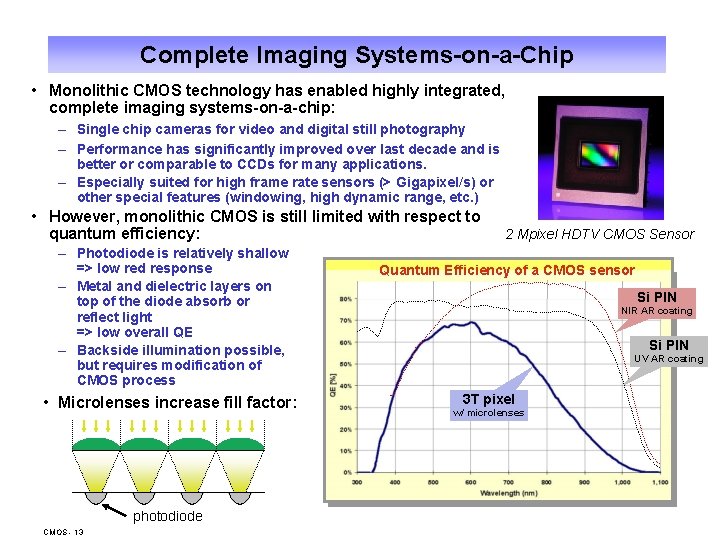

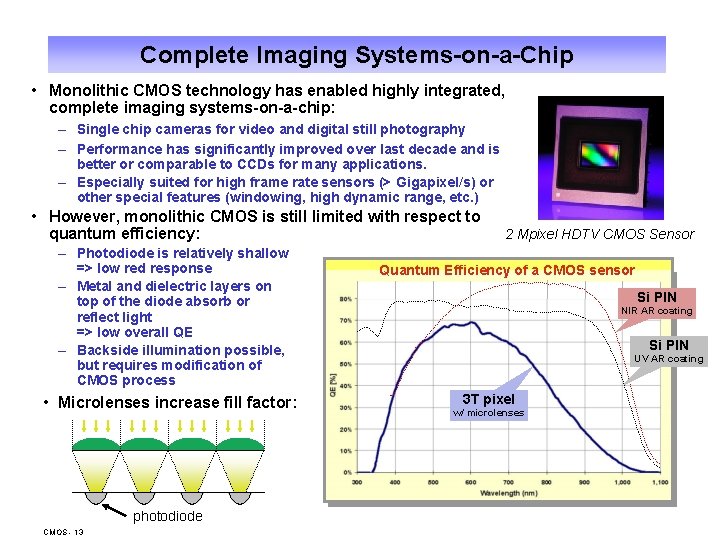

Complete Imaging Systems-on-a-Chip • Monolithic CMOS technology has enabled highly integrated, complete imaging systems-on-a-chip: – Single chip cameras for video and digital still photography – Performance has significantly improved over last decade and is better or comparable to CCDs for many applications. – Especially suited for high frame rate sensors (> Gigapixel/s) or other special features (windowing, high dynamic range, etc. ) • However, monolithic CMOS is still limited with respect to quantum efficiency: – Photodiode is relatively shallow => low red response – Metal and dielectric layers on top of the diode absorb or reflect light => low overall QE – Backside illumination possible, but requires modification of CMOS process • Microlenses increase fill factor: photodiode CMOS - 13 2 Mpixel HDTV CMOS Sensor Quantum Efficiency of a CMOS sensor Si PIN NIR AR coating Si PIN UV AR coating 3 T pixel w/ microlenses

Outline • • General Concept & Architecture Common Features of CMOS Sensors Stitching Technology Enables Large Arrays Monolithic CMOS • Hybrid CMOS – History of Hybrid CMOS – ROIC Input Cells – Detector Materials & Properties Markus Loose Alan Hoffman • Low Noise Through Multiple Sampling • CMOS Processing and General Limitations • Emerging Technologies – Vertical Integration – Geiger-Mode Avalanche Photodiode Arrays • Comparison: CMOS vs. CCD for Astronomy CMOS - 14 Vyshi Suntharalingam

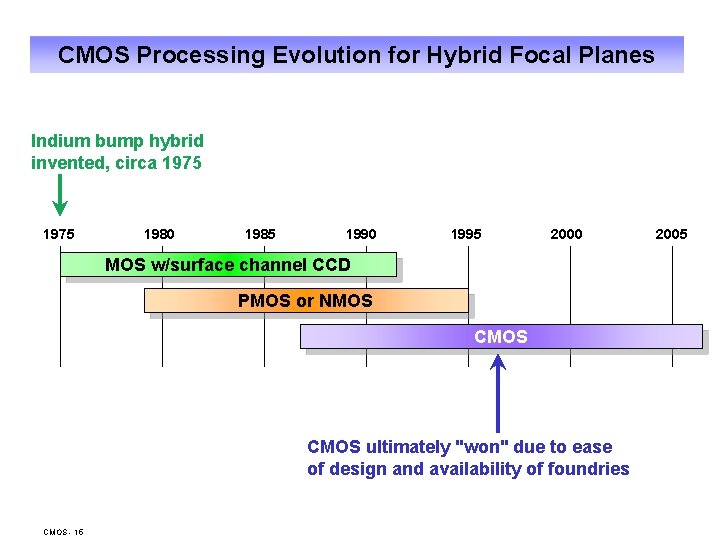

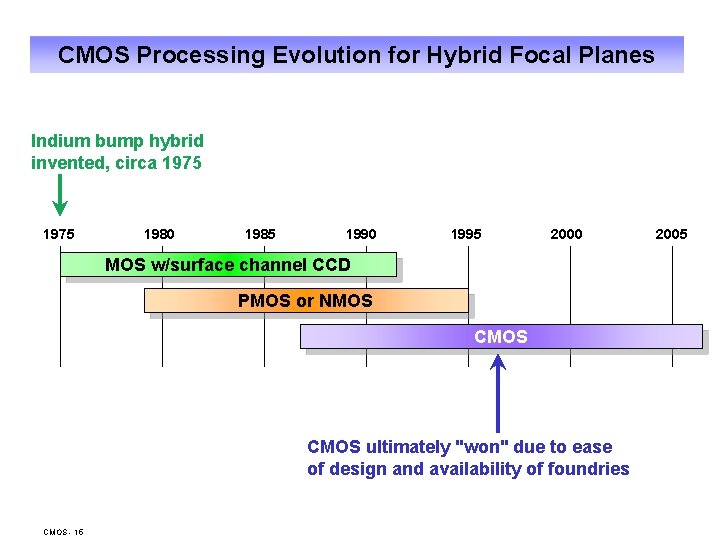

CMOS Processing Evolution for Hybrid Focal Planes Indium bump hybrid invented, circa 1975 1980 1985 1990 1995 2000 MOS w/surface channel CCD PMOS or NMOS CMOS ultimately "won" due to ease of design and availability of foundries CMOS - 15 2005

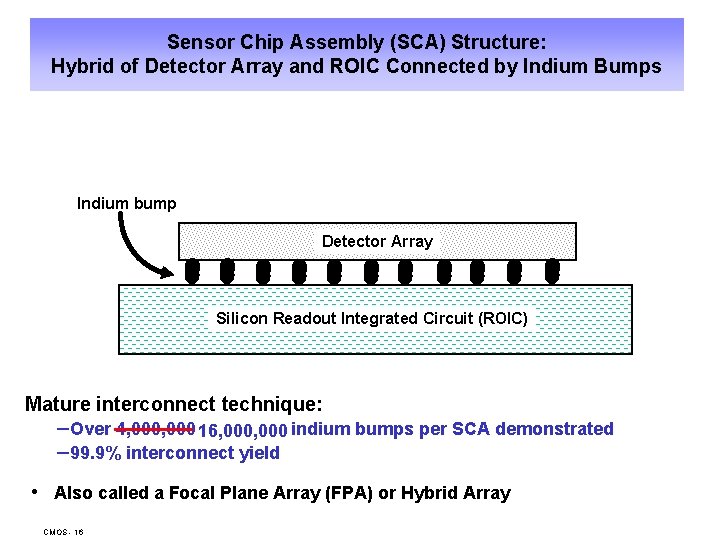

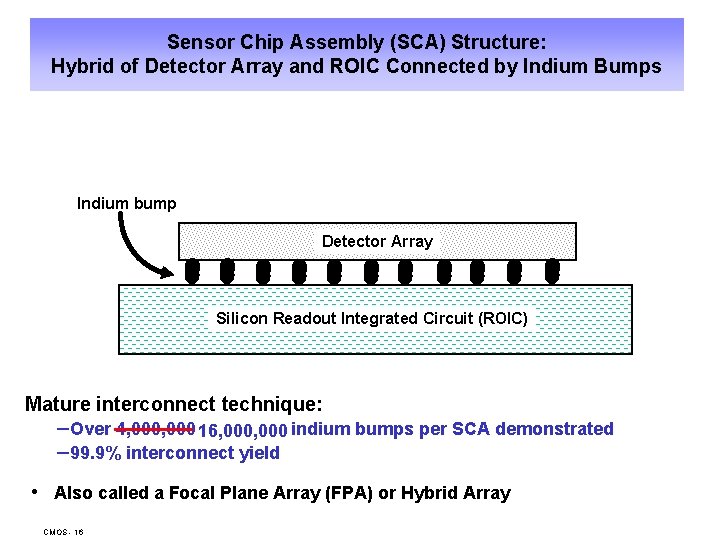

Sensor Chip Assembly (SCA) Structure: Hybrid of Detector Array and ROIC Connected by Indium Bumps Detector Array Indium bump Detector Array Silicon Readout Integrated Circuit (ROIC) Mature interconnect technique: – Over 4, 000 16, 000 indium bumps per SCA demonstrated – 99. 9% interconnect yield • Also called a Focal Plane Array (FPA) or Hybrid Array CMOS - 16

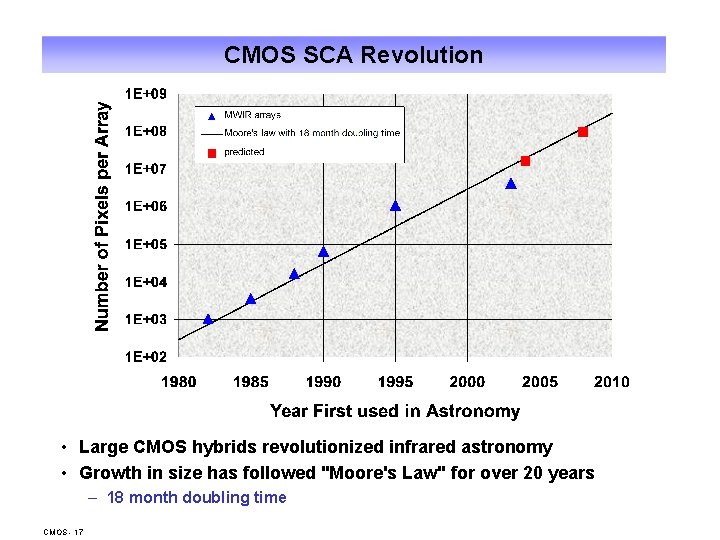

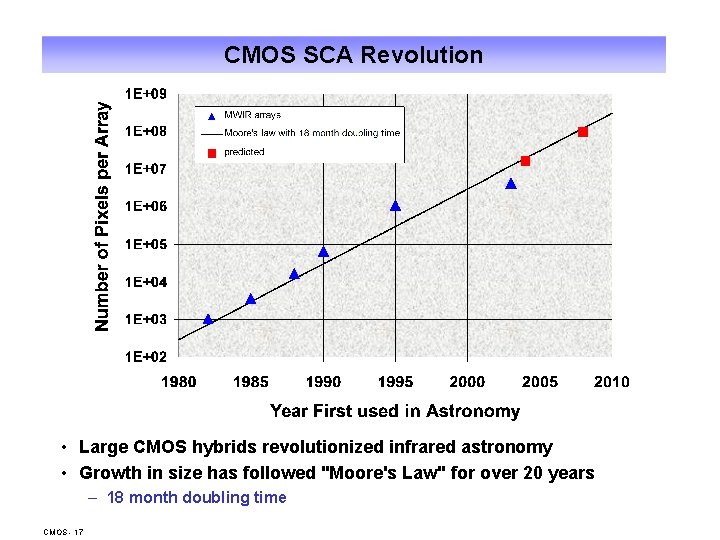

CMOS SCA Revolution • Large CMOS hybrids revolutionized infrared astronomy • Growth in size has followed "Moore's Law" for over 20 years – 18 month doubling time CMOS - 17

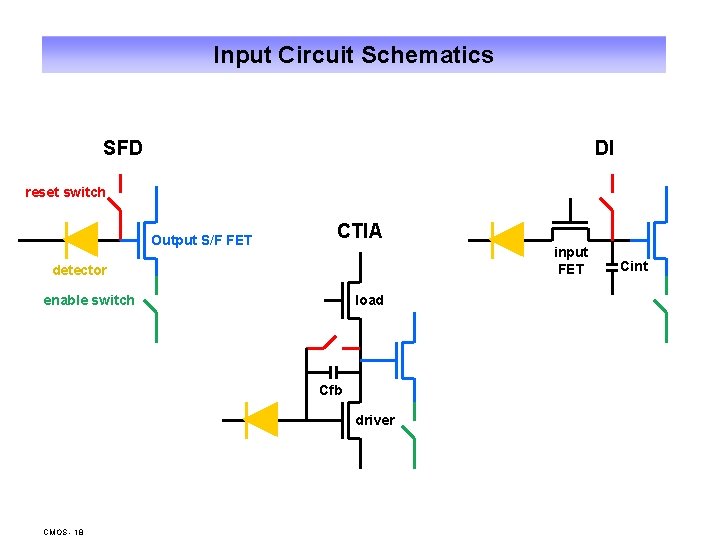

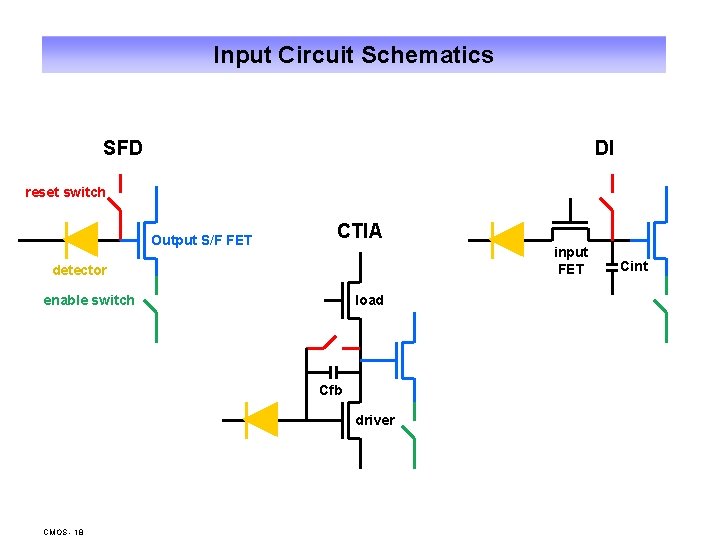

Input Circuit Schematics SFD DI reset switch Output S/F FET CTIA input FET detector enable switch load Cfb driver CMOS - 18 Cint

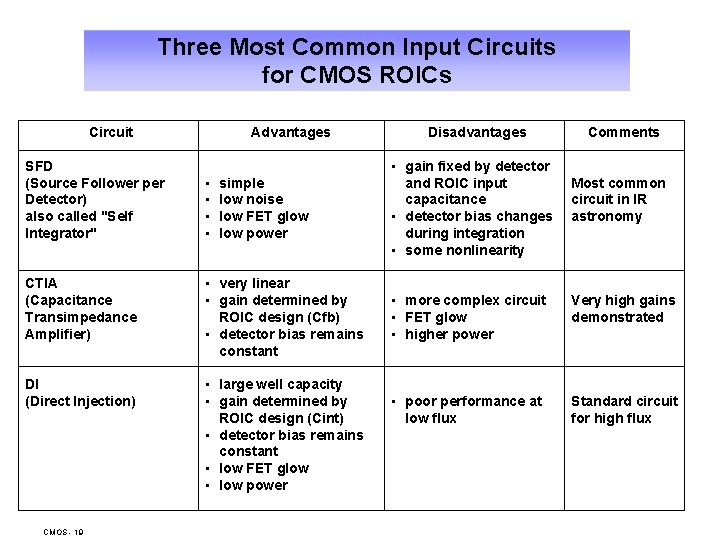

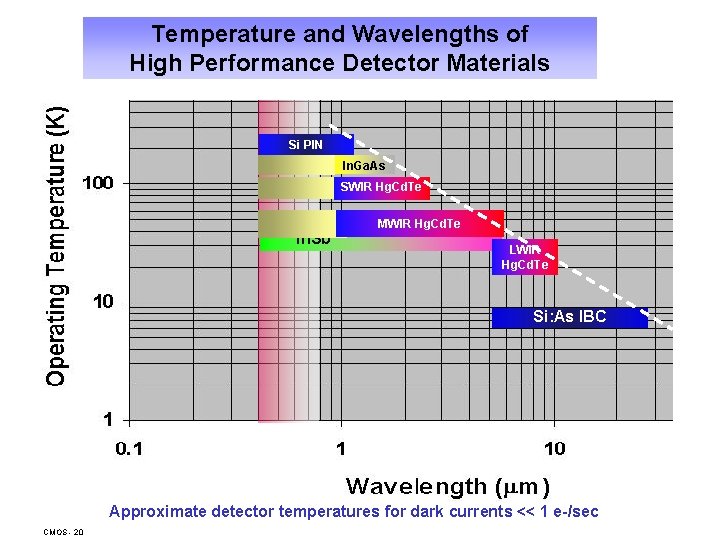

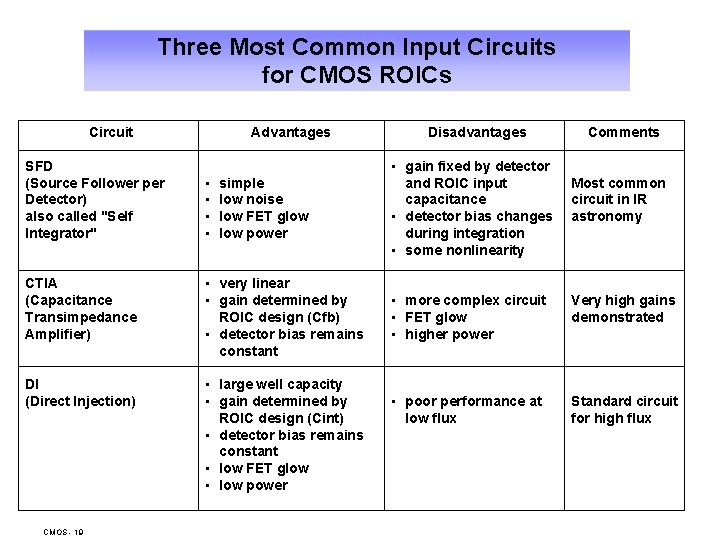

Three Most Common Input Circuits for CMOS ROICs Circuit SFD (Source Follower per Detector) also called "Self Integrator" Advantages • • simple low noise low FET glow power CTIA (Capacitance Transimpedance Amplifier) • very linear • gain determined by ROIC design (Cfb) • detector bias remains constant DI (Direct Injection) • large well capacity • gain determined by ROIC design (Cint) • detector bias remains constant • low FET glow • low power CMOS - 19 Disadvantages • gain fixed by detector and ROIC input capacitance • detector bias changes during integration • some nonlinearity Comments Most common circuit in IR astronomy • more complex circuit • FET glow • higher power Very high gains demonstrated • poor performance at low flux Standard circuit for high flux

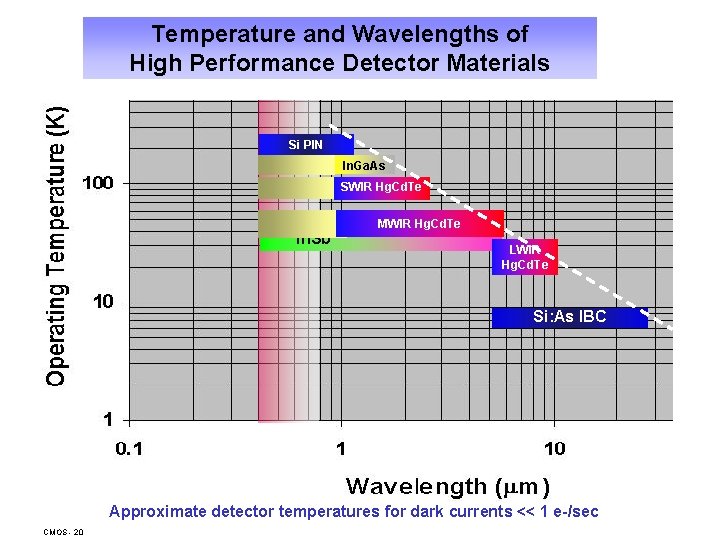

Temperature and Wavelengths of High Performance Detector Materials Si PIN In. Ga. As SWIR Hg. Cd. Te In. Sb MWIR Hg. Cd. Te LWIR Hg. Cd. Te Si: As IBC Approximate detector temperatures for dark currents << 1 e-/sec CMOS - 20

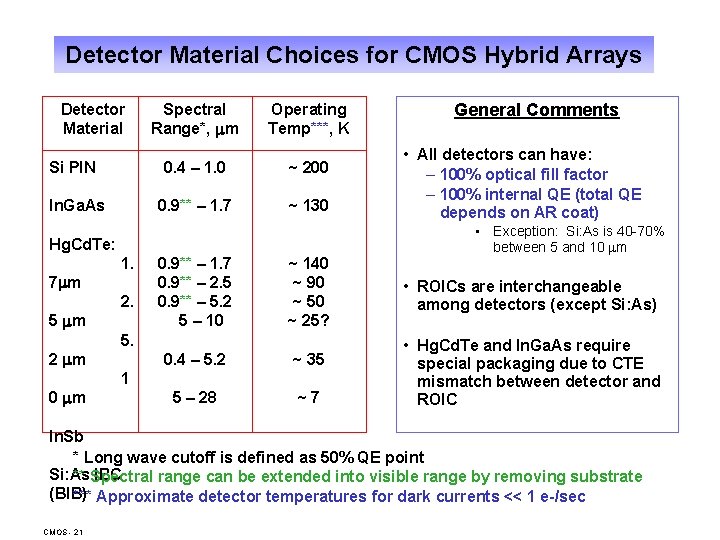

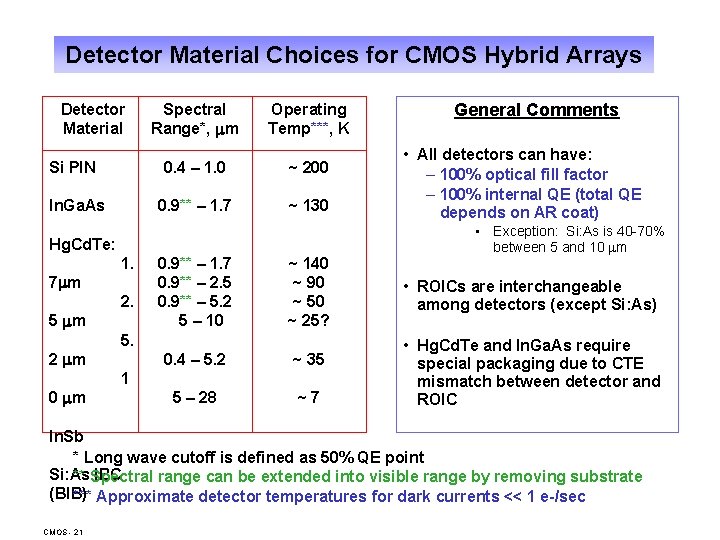

Detector Material Choices for CMOS Hybrid Arrays Detector Material Si PIN In. Ga. As Spectral Range*, m Operating Temp***, K 0. 4 – 1. 0 ~ 200 0. 9** – 1. 7 ~ 130 Hg. Cd. Te: 1. 7 m 5 m 2 m 0 m 2. 0. 9** – 1. 7 0. 9** – 2. 5 0. 9** – 5. 2 5 – 10 ~ 140 ~ 90 ~ 50 ~ 25? 5. 0. 4 – 5. 2 ~ 35 5 – 28 ~7 1 General Comments • All detectors can have: – 100% optical fill factor – 100% internal QE (total QE depends on AR coat) • Exception: Si: As is 40 -70% between 5 and 10 m • ROICs are interchangeable among detectors (except Si: As) • Hg. Cd. Te and In. Ga. As require special packaging due to CTE mismatch between detector and ROIC In. Sb * Long wave cutoff is defined as 50% QE point Si: As IBC ** Spectral range can be extended into visible range by removing substrate (BIB) *** Approximate detector temperatures for dark currents << 1 e-/sec CMOS - 21

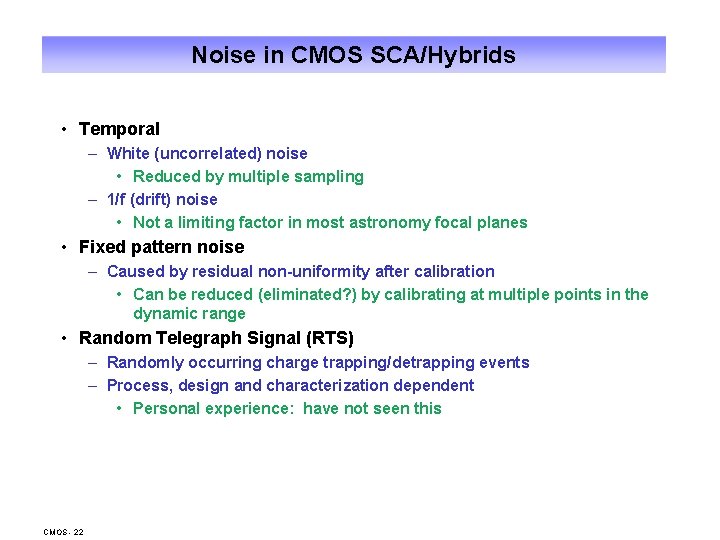

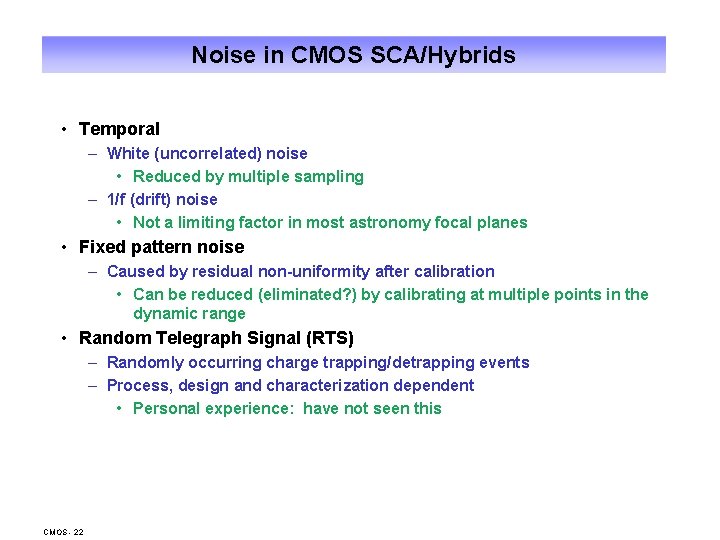

Noise in CMOS SCA/Hybrids • Temporal – White (uncorrelated) noise • Reduced by multiple sampling – 1/f (drift) noise • Not a limiting factor in most astronomy focal planes • Fixed pattern noise – Caused by residual non-uniformity after calibration • Can be reduced (eliminated? ) by calibrating at multiple points in the dynamic range • Random Telegraph Signal (RTS) – Randomly occurring charge trapping/detrapping events – Process, design and characterization dependent • Personal experience: have not seen this CMOS - 22

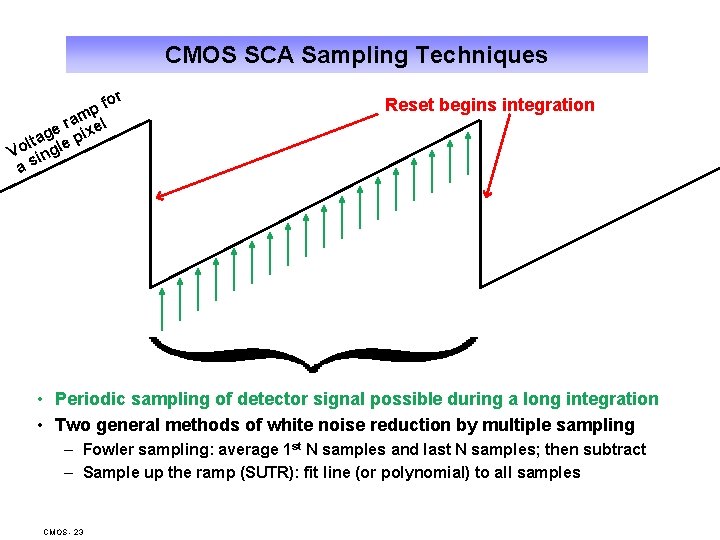

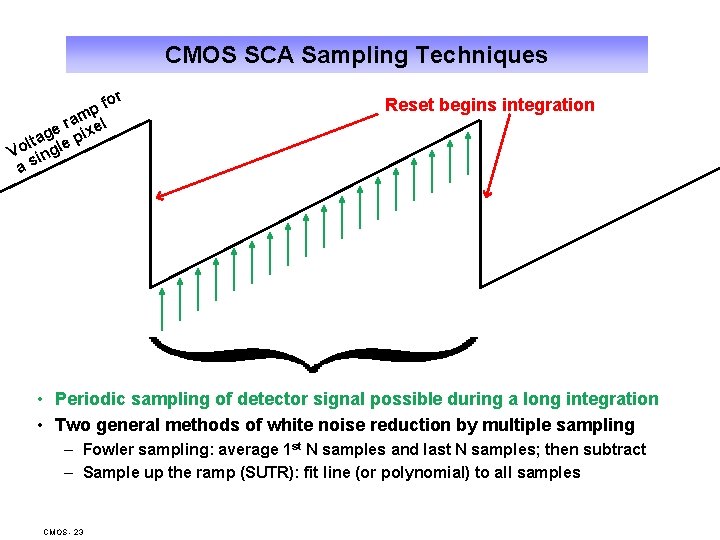

CMOS SCA Sampling Techniques or pf m ra xel e ag l e p i t l Vo ing as Reset begins integration • Periodic sampling of detector signal possible during a long integration • Two general methods of white noise reduction by multiple sampling – Fowler sampling: average 1 st N samples and last N samples; then subtract – Sample up the ramp (SUTR): fit line (or polynomial) to all samples CMOS - 23

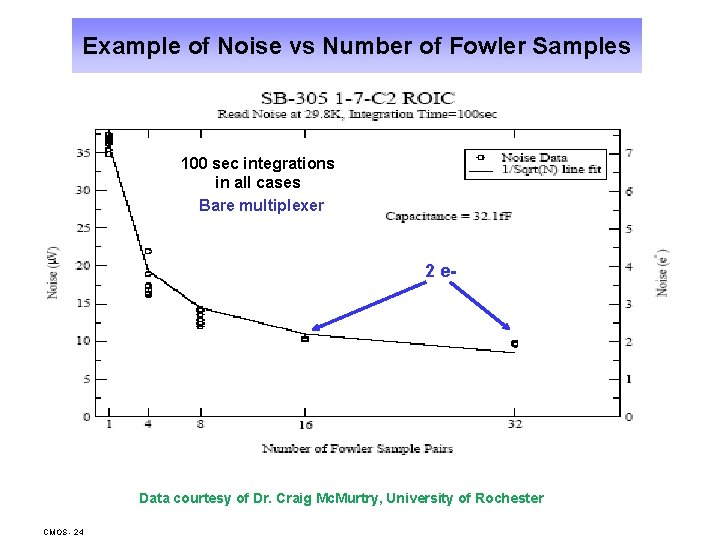

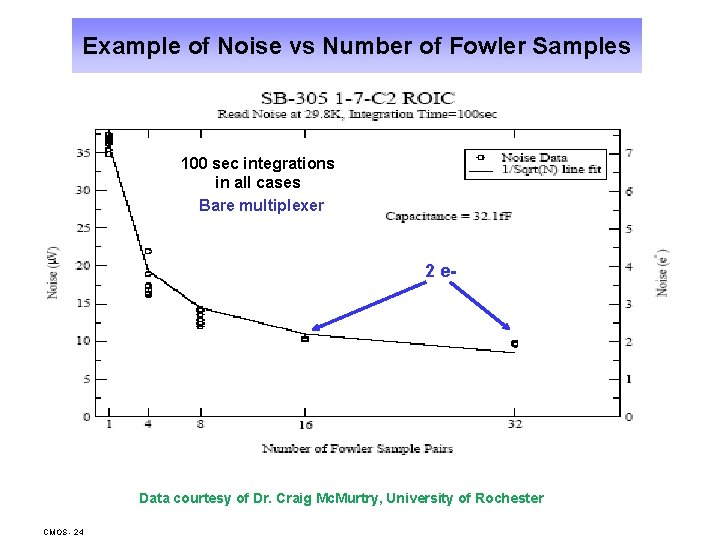

Example of Noise vs Number of Fowler Samples 100 sec integrations in all cases Bare multiplexer 2 e- Data courtesy of Dr. Craig Mc. Murtry, University of Rochester CMOS - 24

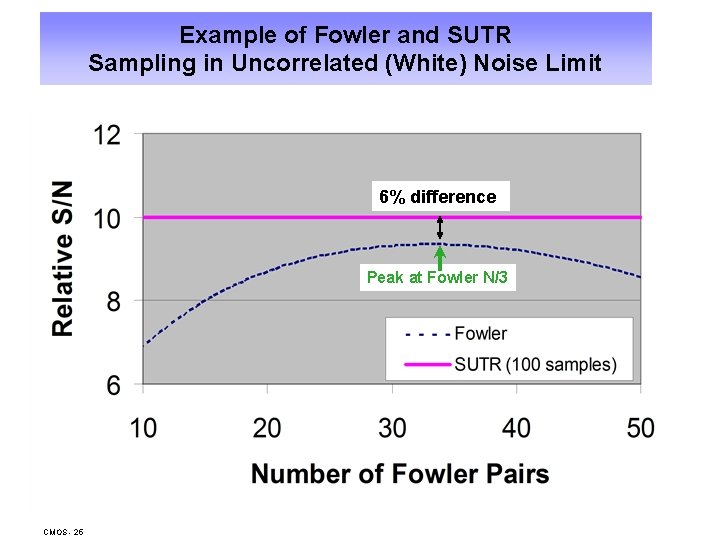

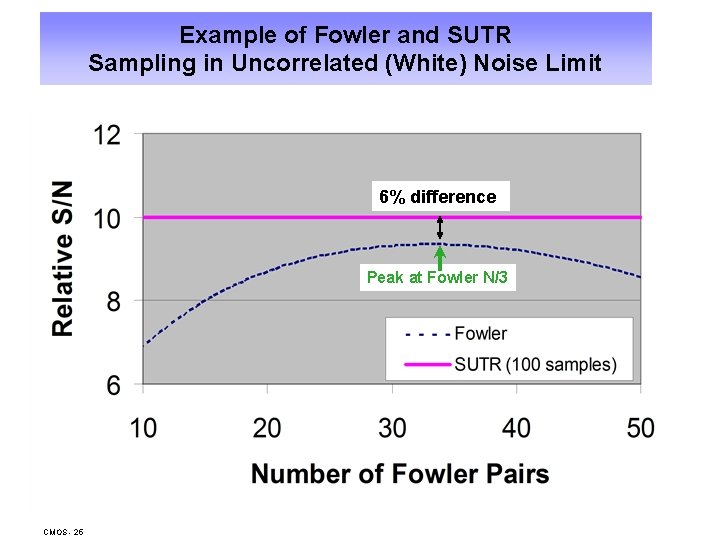

Example of Fowler and SUTR Sampling in Uncorrelated (White) Noise Limit 6% difference Peak at Fowler N/3 CMOS - 25

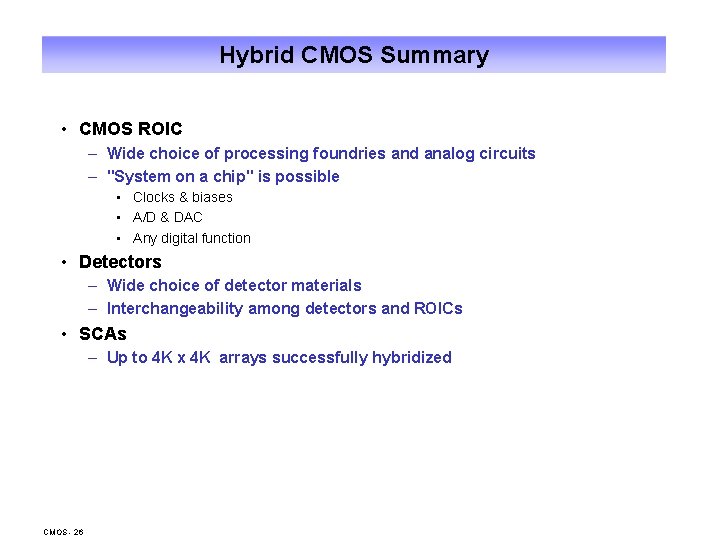

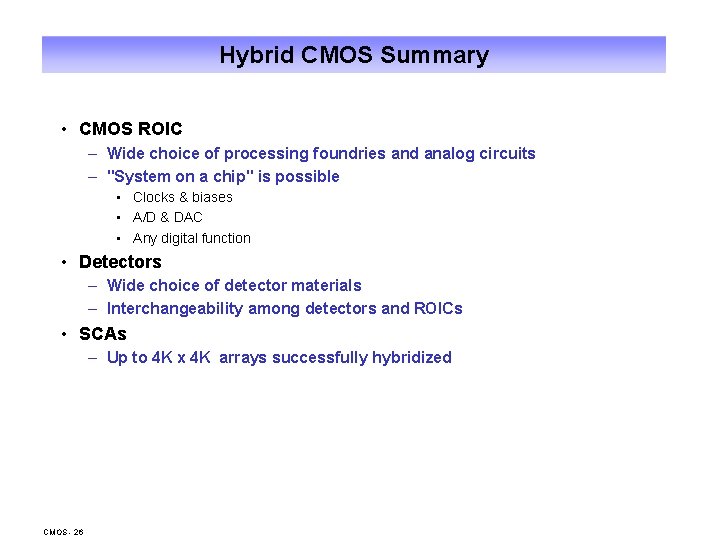

Hybrid CMOS Summary • CMOS ROIC – Wide choice of processing foundries and analog circuits – "System on a chip" is possible • Clocks & biases • A/D & DAC • Any digital function • Detectors – Wide choice of detector materials – Interchangeability among detectors and ROICs • SCAs – Up to 4 K x 4 K arrays successfully hybridized CMOS - 26

Outline • • General Concept & Architecture Common Features of CMOS Sensors Stitching Technology Enables Large Arrays Monolithic CMOS • Hybrid CMOS – History of Hybrid CMOS – ROIC Input Cells – Detector Materials & Properties Markus Loose Alan Hoffman • Low Noise Through Multiple Sampling • CMOS Processing and General Limitations • Emerging Technologies – Vertical Integration – Geiger-Mode Avalanche Photodiode Arrays • Comparison: CMOS vs. CCD for Astronomy CMOS - 27 Vyshi Suntharalingam

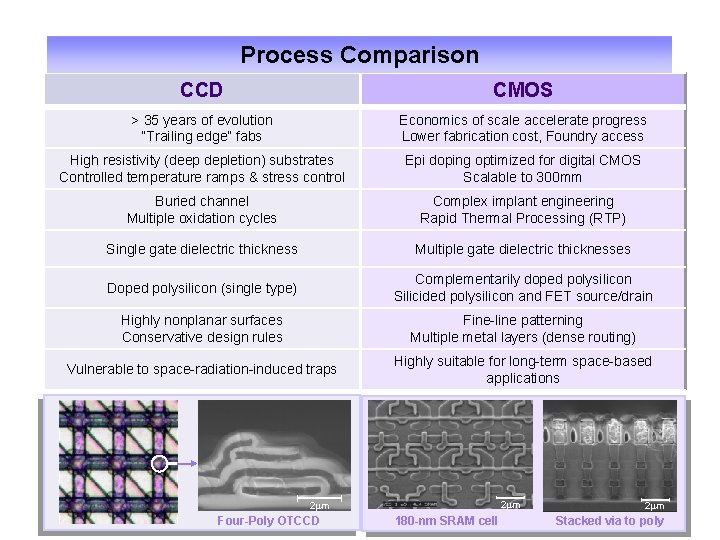

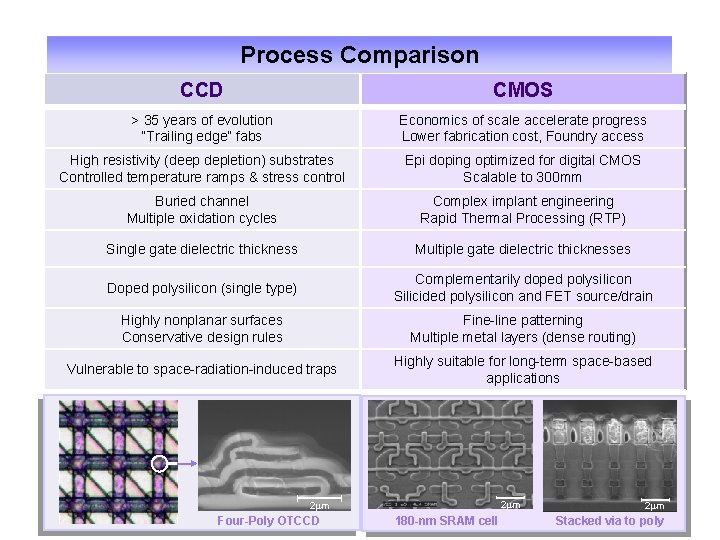

Process Comparison CCD CMOS > 35 years of evolution “Trailing edge” fabs Economics of scale accelerate progress Lower fabrication cost, Foundry access High resistivity (deep depletion) substrates Controlled temperature ramps & stress control Epi doping optimized for digital CMOS Scalable to 300 mm Buried channel Multiple oxidation cycles Complex implant engineering Rapid Thermal Processing (RTP) Single gate dielectric thickness Multiple gate dielectric thicknesses Doped polysilicon (single type) Complementarily doped polysilicon Silicided polysilicon and FET source/drain Highly nonplanar surfaces Conservative design rules Fine-line patterning Multiple metal layers (dense routing) Vulnerable to space-radiation-induced traps Highly suitable for long-term space-based applications 2 m Four-Poly OTCCD CMOS - 28 180 -nm SRAM cell 2 m Stacked via to poly

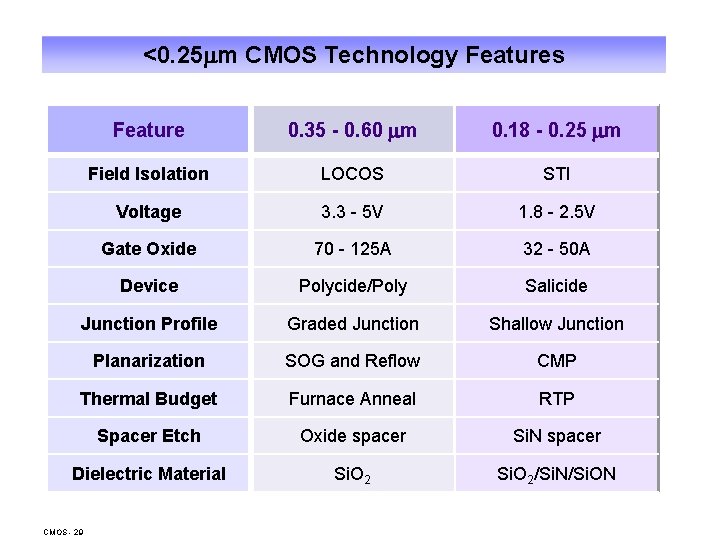

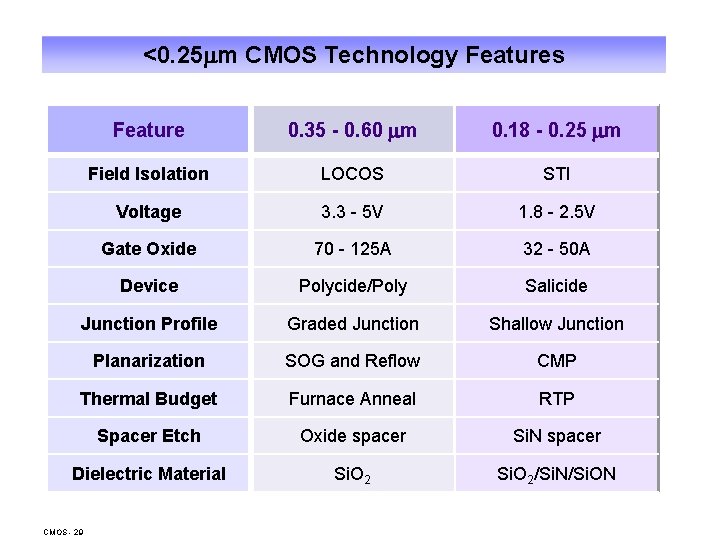

<0. 25 m CMOS Technology Features Feature 0. 35 - 0. 60 m 0. 18 - 0. 25 m Field Isolation LOCOS STI Voltage 3. 3 - 5 V 1. 8 - 2. 5 V Gate Oxide 70 - 125 A 32 - 50 A Device Polycide/Poly Salicide Junction Profile Graded Junction Shallow Junction Planarization SOG and Reflow CMP Thermal Budget Furnace Anneal RTP Spacer Etch Oxide spacer Si. N spacer Dielectric Material Si. O 2/Si. N/Si. ON CMOS - 29

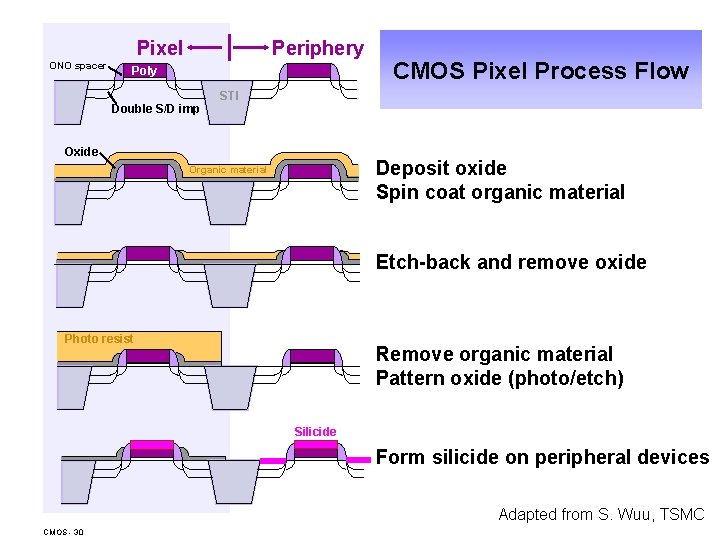

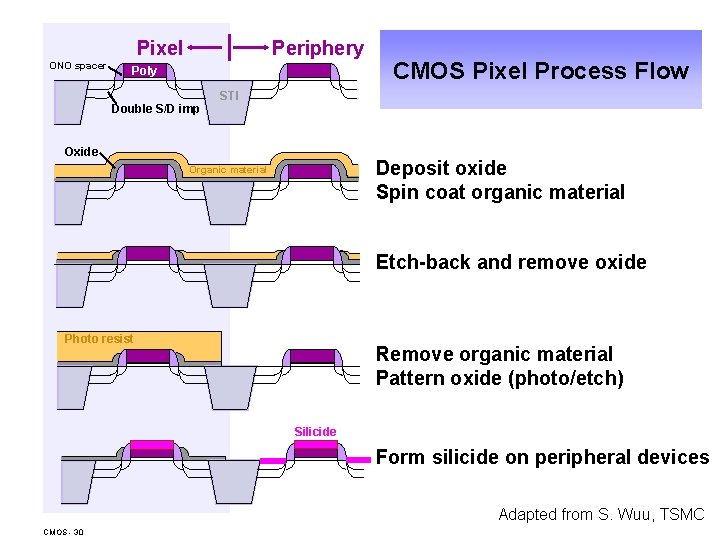

Periphery Pixel ONO spacer Poly Double S/D imp CMOS Pixel Process Flow STI Oxide Deposit oxide Spin coat organic material Organic material Etch-back and remove oxide Photo resist Remove organic material Pattern oxide (photo/etch) Silicide Form silicide on peripheral devices Adapted from S. Wuu, TSMC CMOS - 30

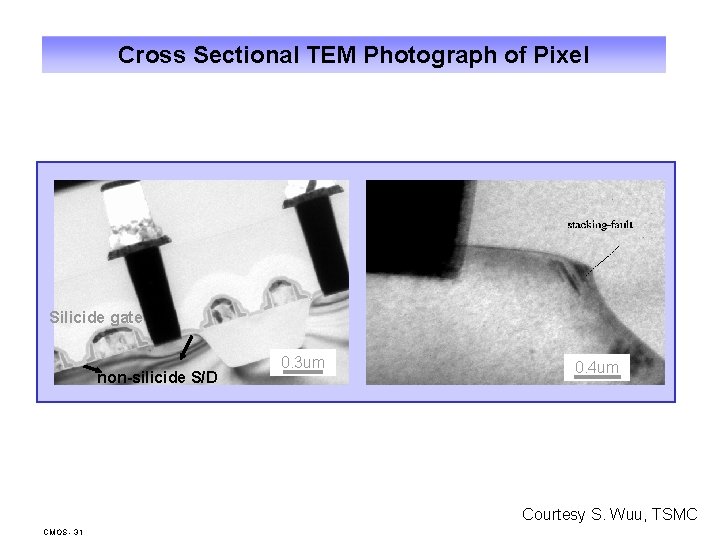

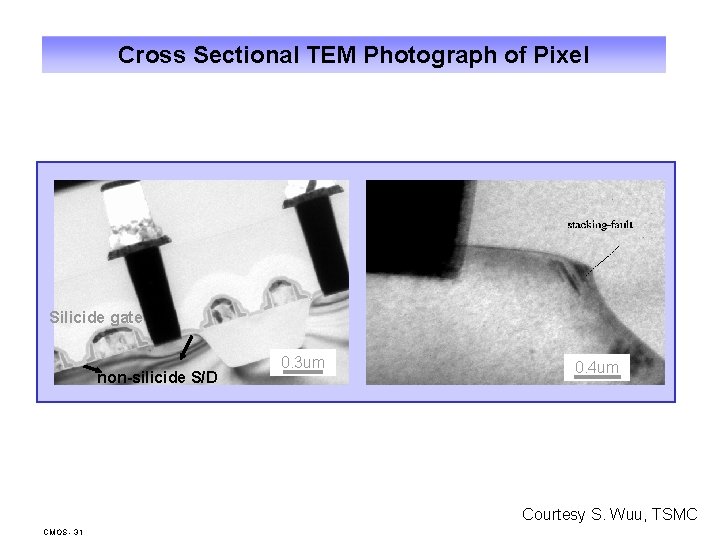

Cross Sectional TEM Photograph of Pixel Silicide gate non-silicide S/D 0. 3 um 0. 4 um Courtesy S. Wuu, TSMC CMOS - 31

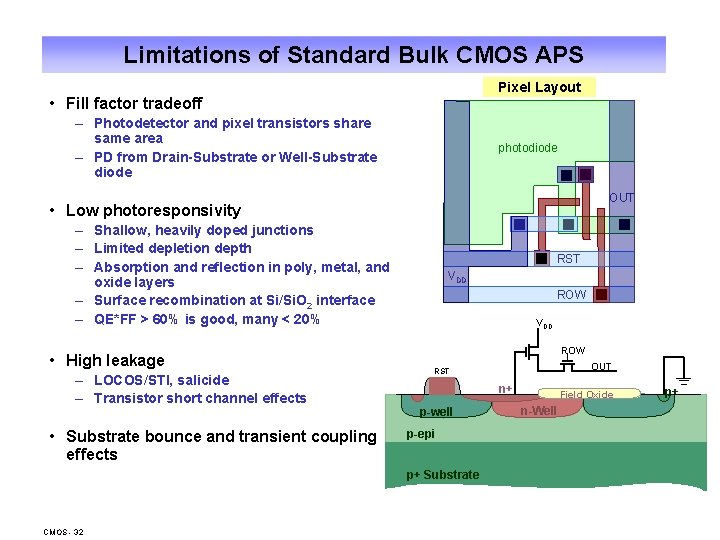

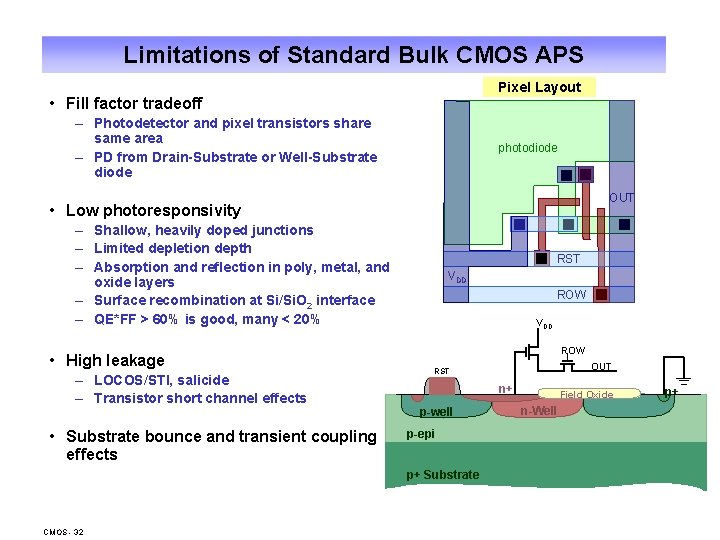

Limitations of Standard Bulk CMOS APS Pixel Layout • Fill factor tradeoff – Photodetector and pixel transistors share same area – PD from Drain-Substrate or Well-Substrate diode photodiode OUT • Low photoresponsivity – Shallow, heavily doped junctions – Limited depletion depth – Absorption and reflection in poly, metal, and oxide layers – Surface recombination at Si/Si. O 2 interface – QE*FF > 60% is good, many < 20% • High leakage – LOCOS/STI, salicide – Transistor short channel effects • Substrate bounce and transient coupling effects RST VDD ROW n+ p-well p-epi p+ Substrate CMOS - 32 OUT RST Field Oxide n-Well p+

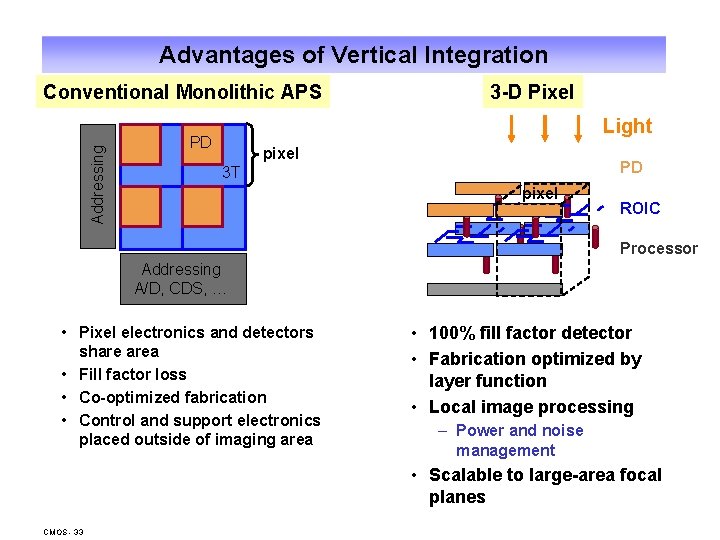

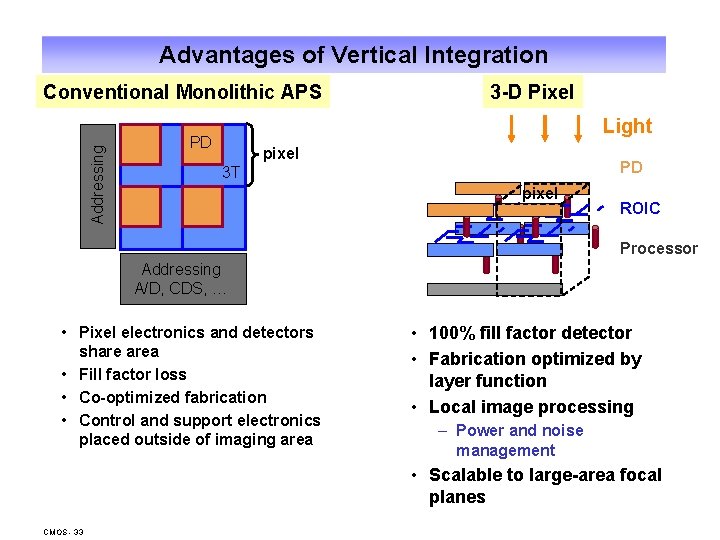

Advantages of Vertical Integration Addressing Conventional Monolithic APS 3 -D Pixel Light PD pixel PD 3 T pixel ROIC Processor Addressing A/D, CDS, … • Pixel electronics and detectors share area • Fill factor loss • Co-optimized fabrication • Control and support electronics placed outside of imaging area • 100% fill factor detector • Fabrication optimized by layer function • Local image processing – Power and noise management • Scalable to large-area focal planes CMOS - 33

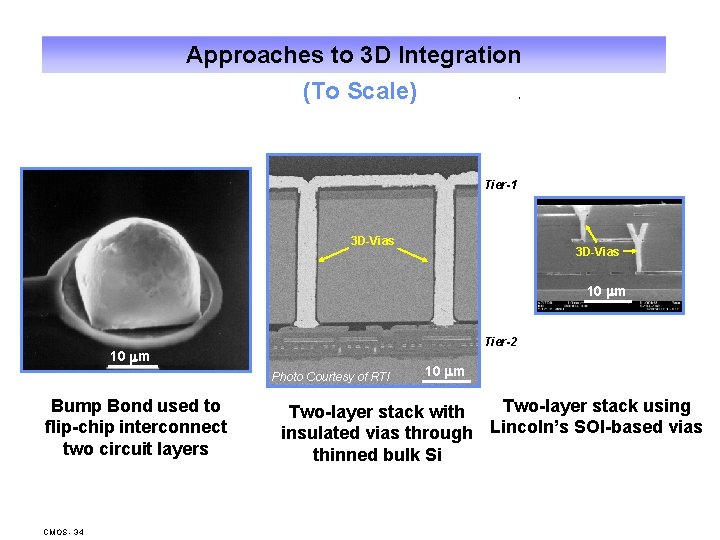

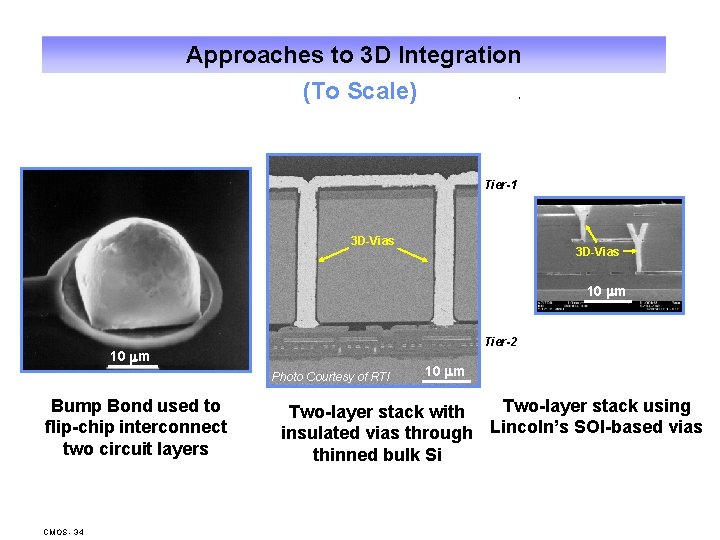

Approaches to 3 D Integration (To Scale) Tier-1 3 D-Vias 10 m Tier-2 10 m Photo Courtesy of RTI Bump Bond used to flip-chip interconnect two circuit layers CMOS - 34 10 m Two-layer stack using Two-layer stack with insulated vias through Lincoln’s SOI-based vias thinned bulk Si

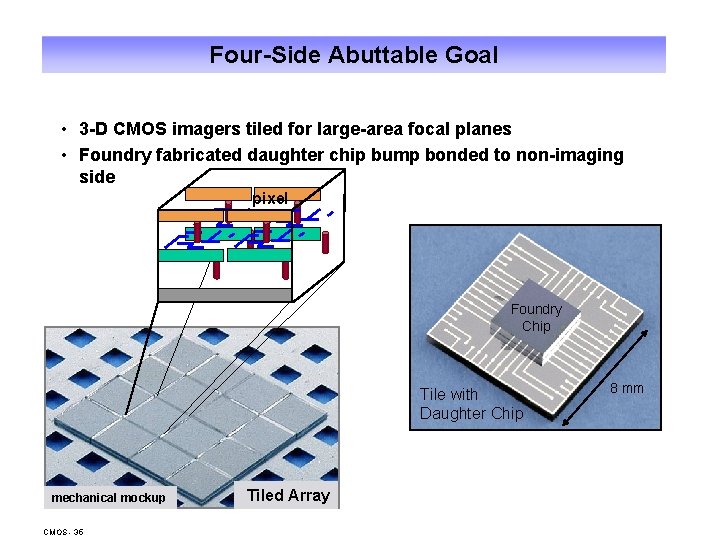

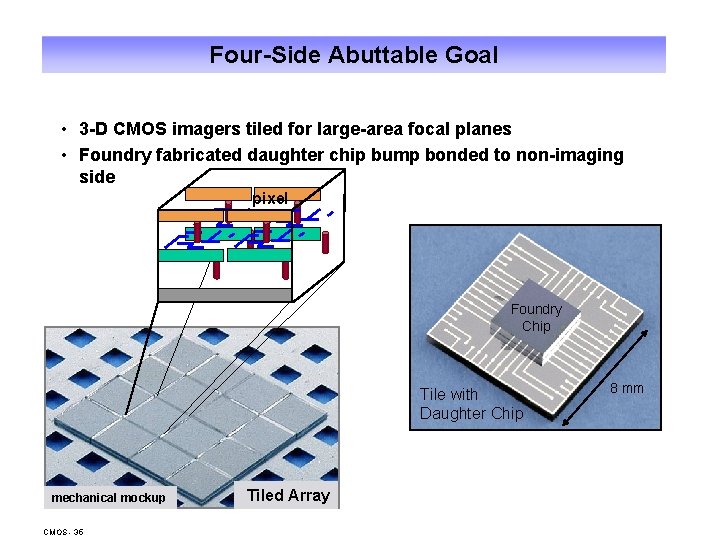

Four-Side Abuttable Goal • 3 -D CMOS imagers tiled for large-area focal planes • Foundry fabricated daughter chip bump bonded to non-imaging side pixel Foundry Chip Tile with Daughter Chip mechanical mockup CMOS - 35 Tiled Array 8 mm

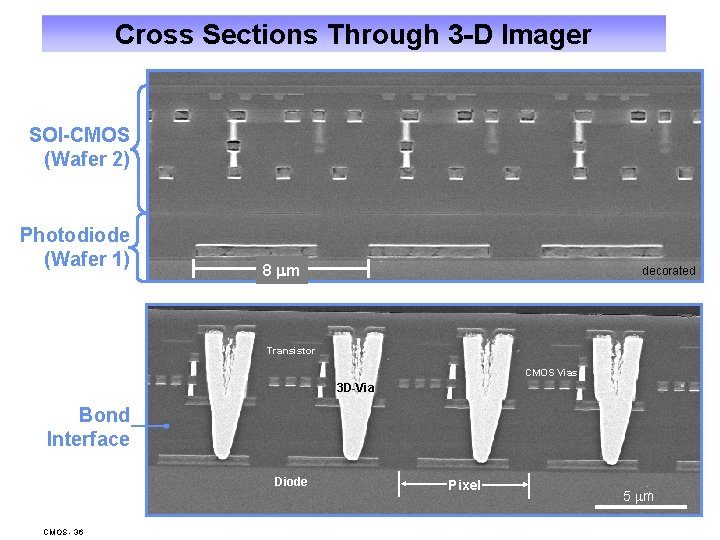

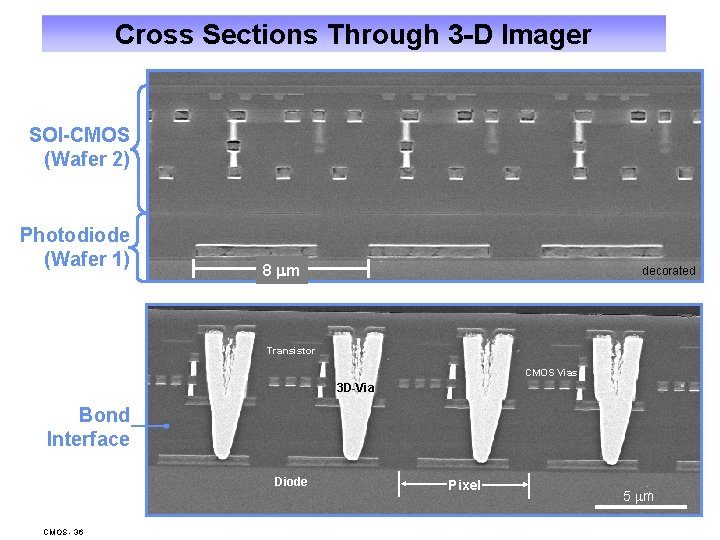

Cross Sections Through 3 -D Imager SOI-CMOS (Wafer 2) SEM cross section Photodiode (Wafer 1) 8 m decorated Transistor CMOS Vias 3 D-Via Bond Interface Diode CMOS - 36 Pixel 5 m

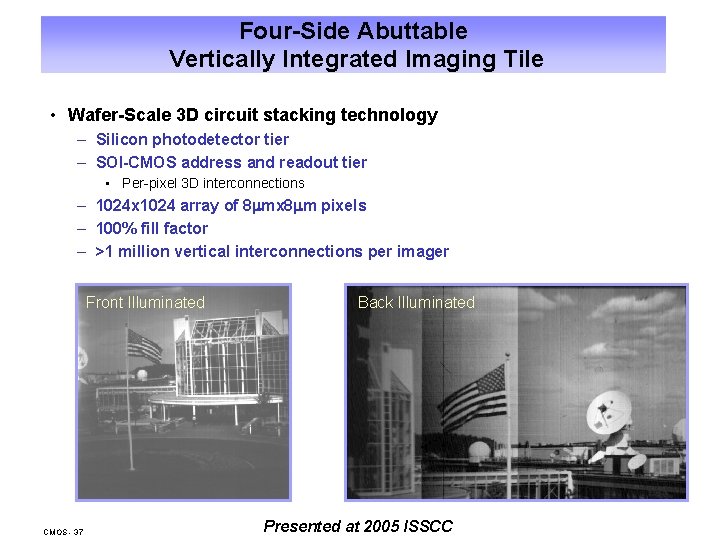

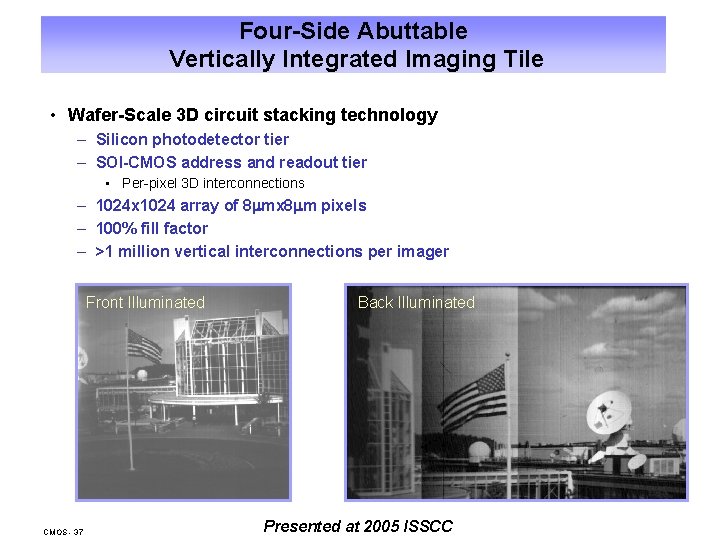

Four-Side Abuttable Vertically Integrated Imaging Tile • Wafer-Scale 3 D circuit stacking technology – Silicon photodetector tier – SOI-CMOS address and readout tier • Per-pixel 3 D interconnections – 1024 x 1024 array of 8 mx 8 m pixels – 100% fill factor – >1 million vertical interconnections per imager Front Illuminated CMOS - 37 Back Illuminated Presented at 2005 ISSCC

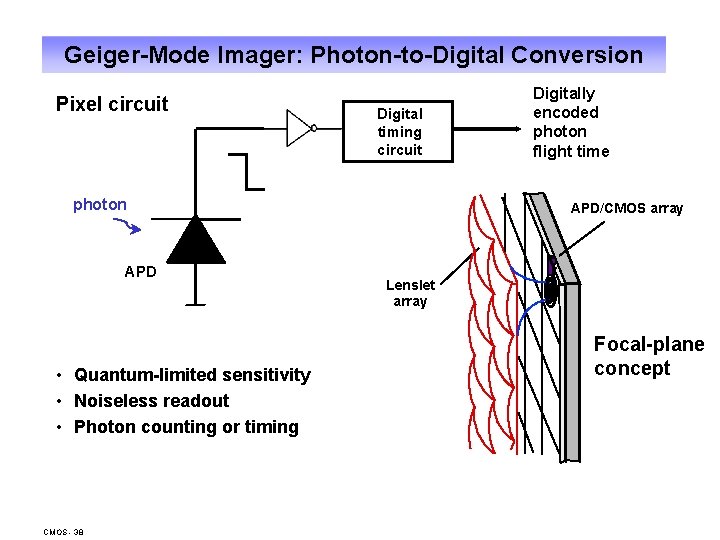

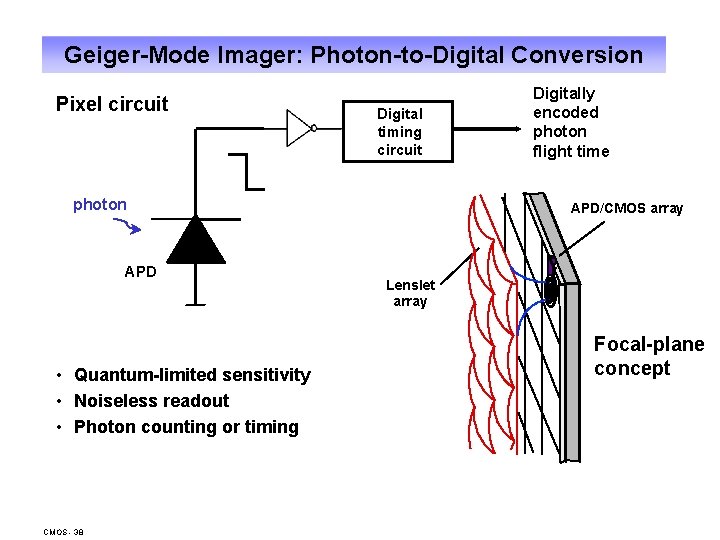

Geiger-Mode Imager: Photon-to-Digital Conversion Pixel circuit Digital timing circuit photon APD • Quantum-limited sensitivity • Noiseless readout • Photon counting or timing CMOS - 38 Digitally encoded photon flight time APD/CMOS array Lenslet array Focal-plane concept

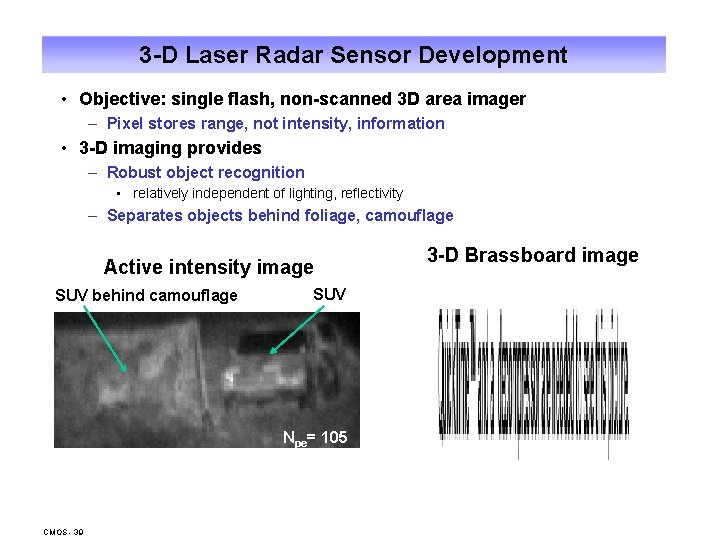

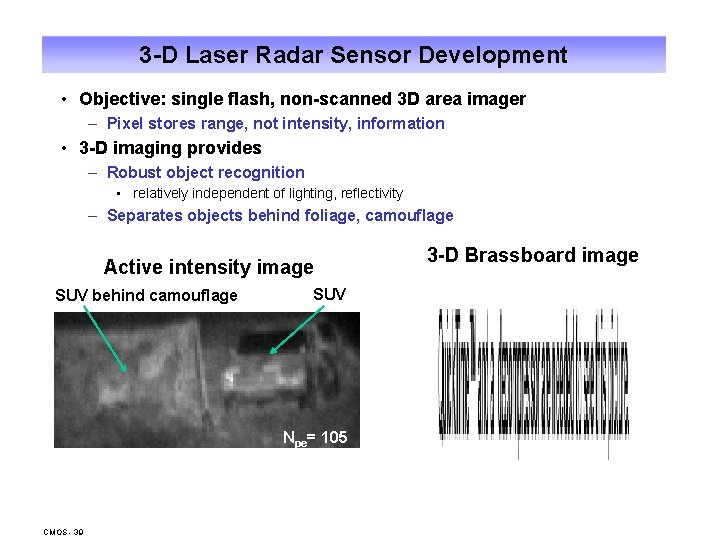

3 -D Laser Radar Sensor Development • Objective: single flash, non-scanned 3 D area imager – Pixel stores range, not intensity, information • 3 -D imaging provides – Robust object recognition • relatively independent of lighting, reflectivity – Separates objects behind foliage, camouflage Active intensity image SUV behind camouflage SUV Npe= 105 CMOS - 39 3 -D Brassboard image

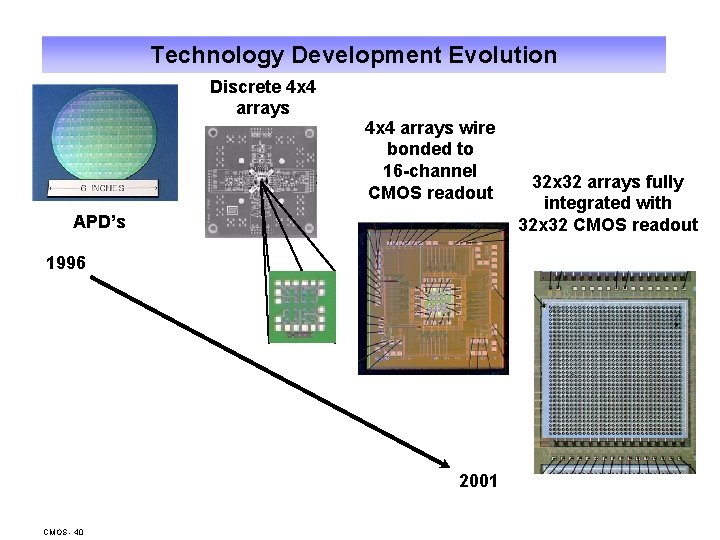

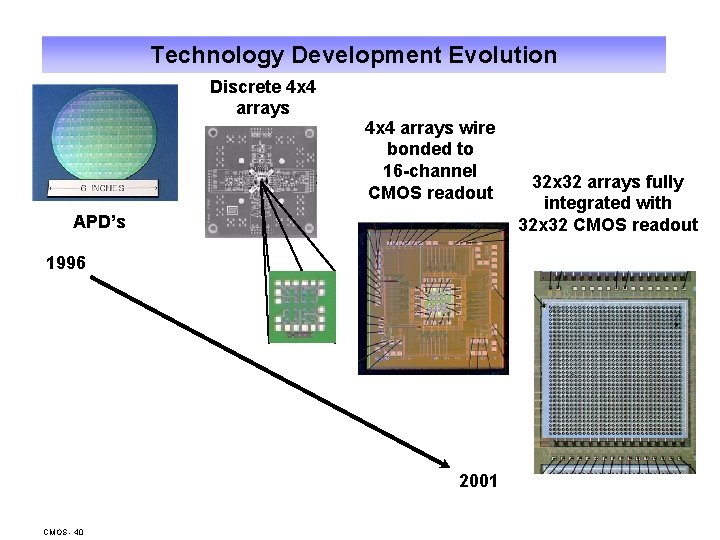

Technology Development Evolution Discrete 4 x 4 arrays wire bonded to 16 -channel CMOS readout APD’s 1996 2001 CMOS - 40 32 x 32 arrays fully integrated with 32 x 32 CMOS readout

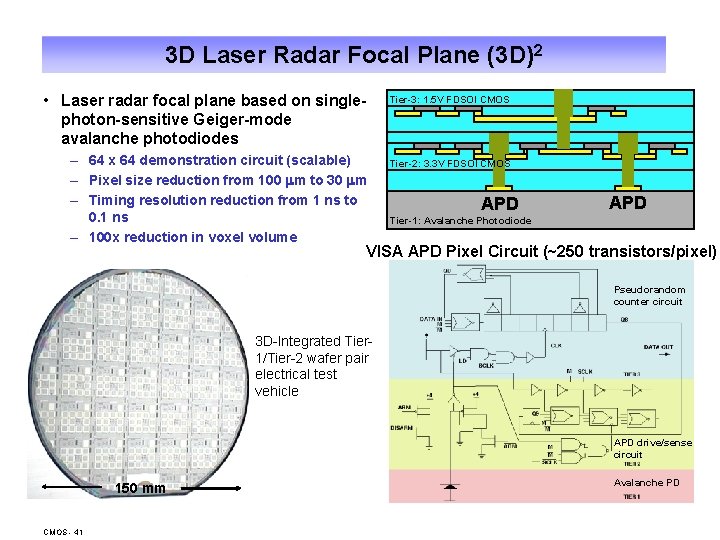

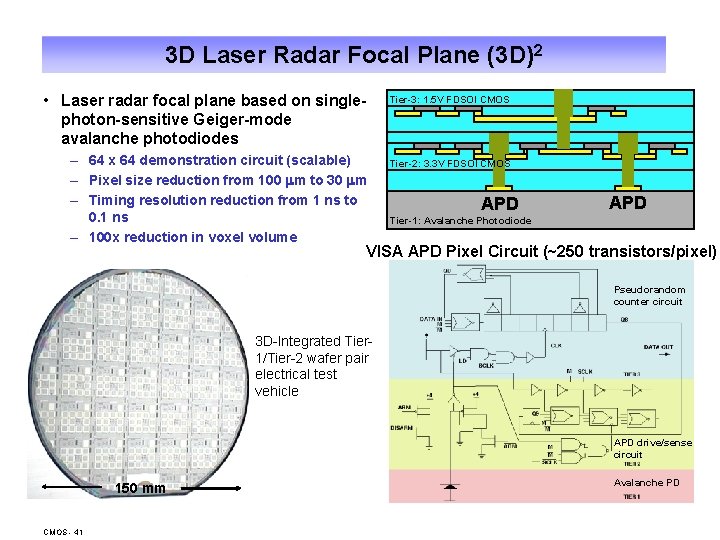

3 D Laser Radar Focal Plane (3 D)2 • Laser radar focal plane based on singlephoton-sensitive Geiger-mode avalanche photodiodes – 64 x 64 demonstration circuit (scalable) – Pixel size reduction from 100 m to 30 m – Timing resolution reduction from 1 ns to 0. 1 ns – 100 x reduction in voxel volume Tier-3: 1. 5 V FDSOI CMOS Tier-2: 3. 3 V FDSOI CMOS APD Tier-1: Avalanche Photodiode VISA APD Pixel Circuit (~250 transistors/pixel) Pseudorandom counter circuit 3 D-Integrated Tier 1/Tier-2 wafer pair electrical test vehicle APD drive/sense circuit 150 mm CMOS - 41 Avalanche PD

Outline • • General Concept & Architecture Common Features of CMOS Sensors Stitching Technology Enables Large Arrays Monolithic CMOS • Hybrid CMOS – History of Hybrid CMOS – ROIC Input Cells – Detector Materials & Properties Markus Loose Alan Hoffman • Low Noise Through Multiple Sampling • CMOS Processing and General Limitations • Emerging Technologies – Vertical Integration – Geiger-Mode Avalanche Photodiode Arrays • Comparison: CMOS vs. CCD for Astronomy CMOS - 42 Vyshi Suntharalingam

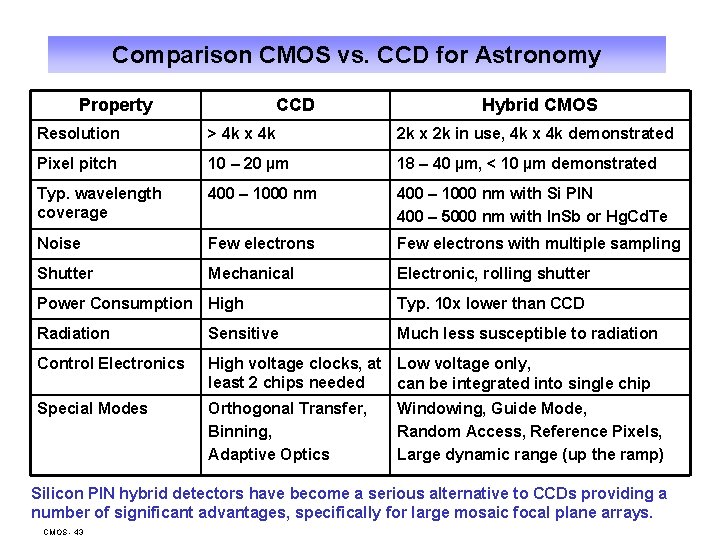

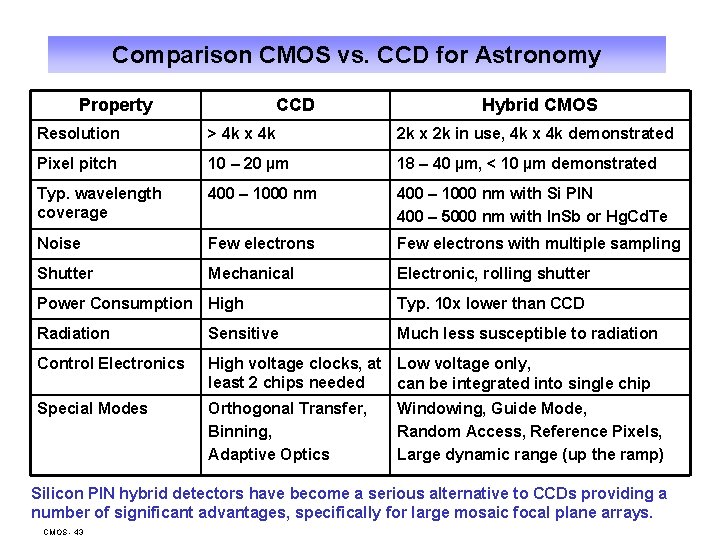

Comparison CMOS vs. CCD for Astronomy Property CCD Hybrid CMOS Resolution > 4 k x 4 k 2 k x 2 k in use, 4 k x 4 k demonstrated Pixel pitch 10 – 20 µm 18 – 40 µm, < 10 µm demonstrated Typ. wavelength coverage 400 – 1000 nm with Si PIN 400 – 5000 nm with In. Sb or Hg. Cd. Te Noise Few electrons with multiple sampling Shutter Mechanical Electronic, rolling shutter Power Consumption High Typ. 10 x lower than CCD Radiation Sensitive Much less susceptible to radiation Control Electronics High voltage clocks, at Low voltage only, least 2 chips needed can be integrated into single chip Special Modes Orthogonal Transfer, Binning, Adaptive Optics Windowing, Guide Mode, Random Access, Reference Pixels, Large dynamic range (up the ramp) Silicon PIN hybrid detectors have become a serious alternative to CCDs providing a number of significant advantages, specifically for large mosaic focal plane arrays. CMOS - 43

Conclusion CCD It’s happening! CMOS - 44