CHAPTER FIVE SYNCHRONOUS SEQUENTIAL LOGIC 1 SEQUENTIAL CIRCUITS

- Slides: 60

CHAPTER FIVE SYNCHRONOUS SEQUENTIAL LOGIC 1

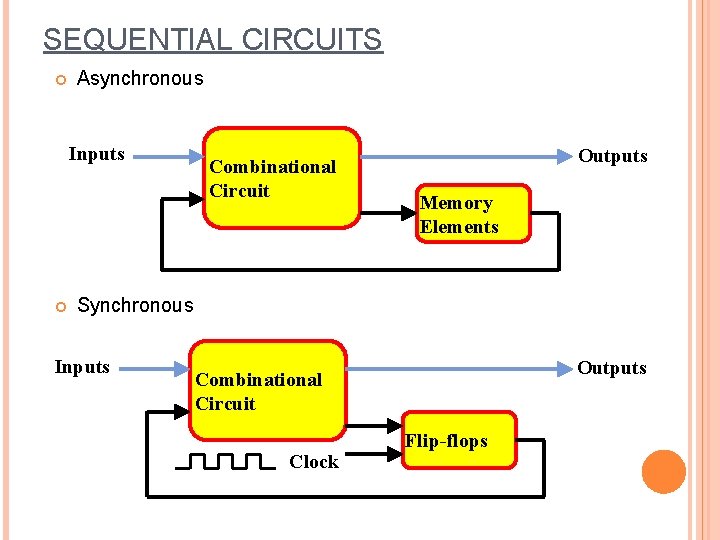

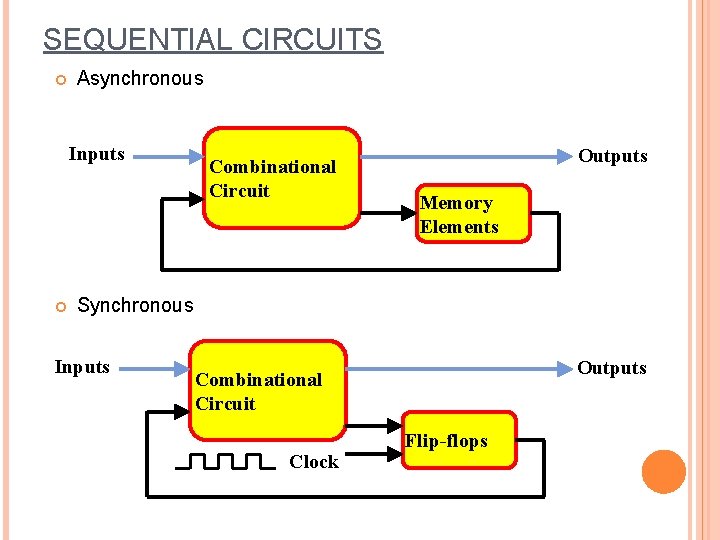

SEQUENTIAL CIRCUITS Asynchronous Inputs Combinational Circuit Outputs Memory Elements Synchronous Inputs Outputs Combinational Circuit Clock Flip-flops 2

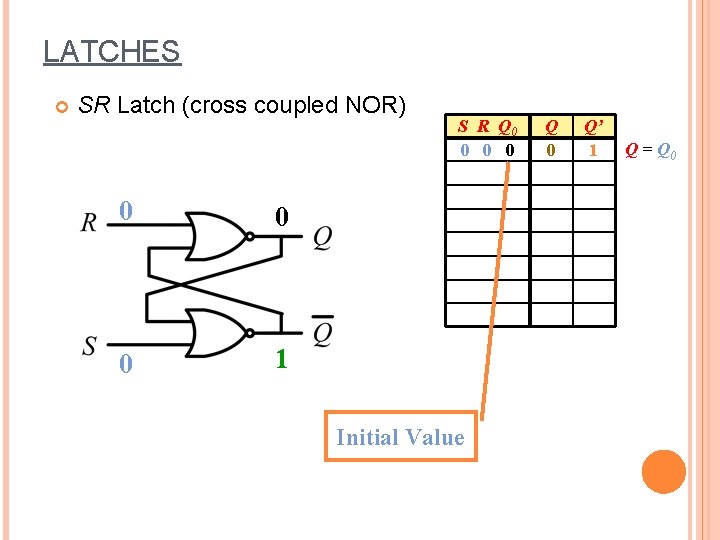

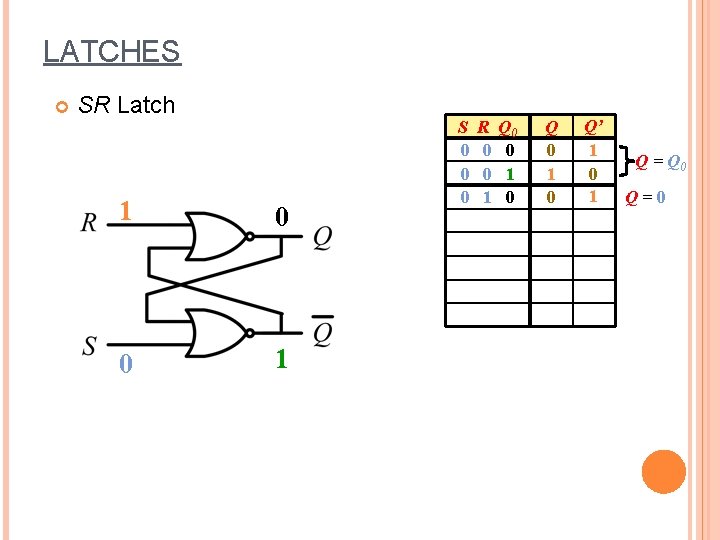

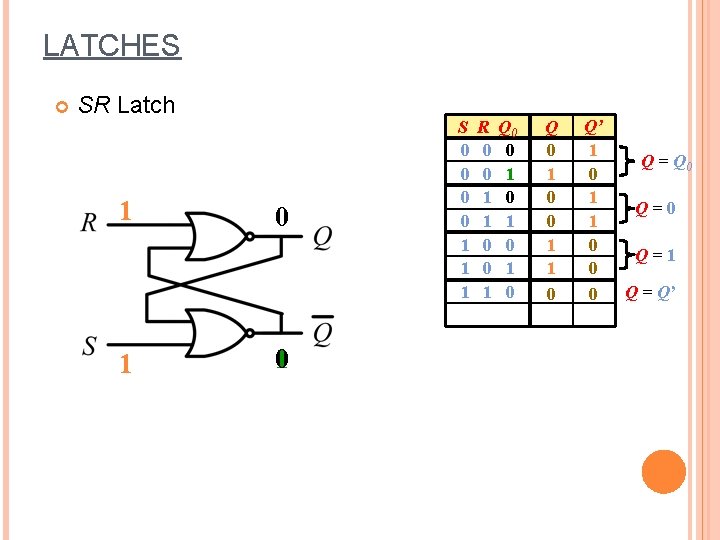

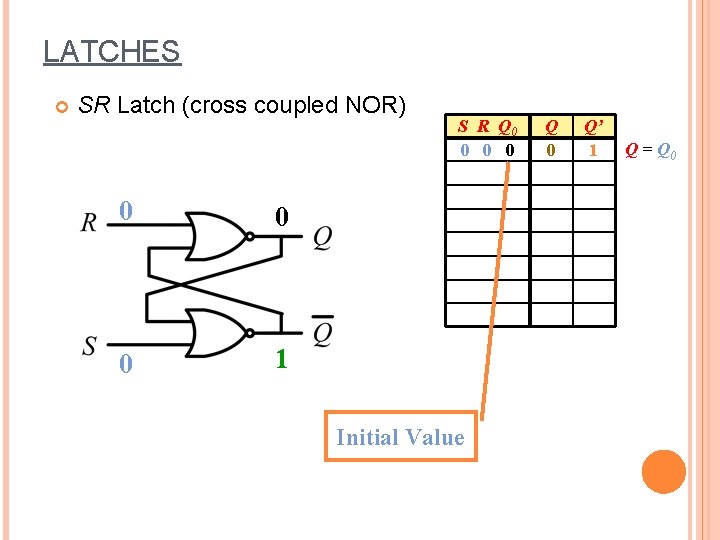

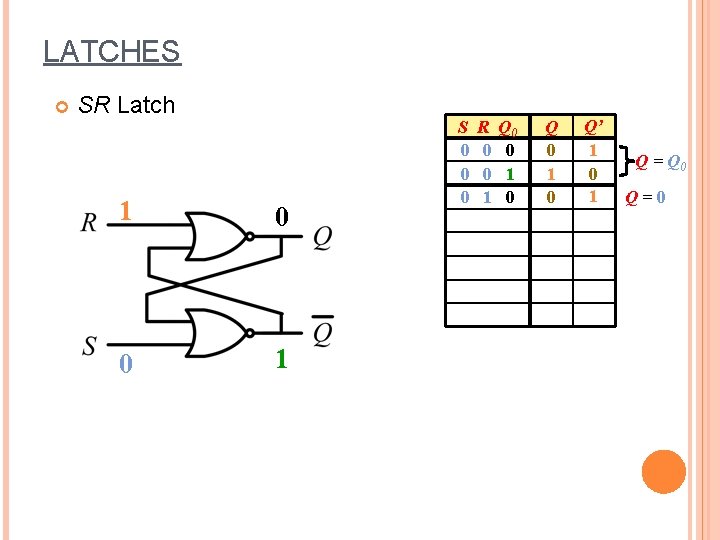

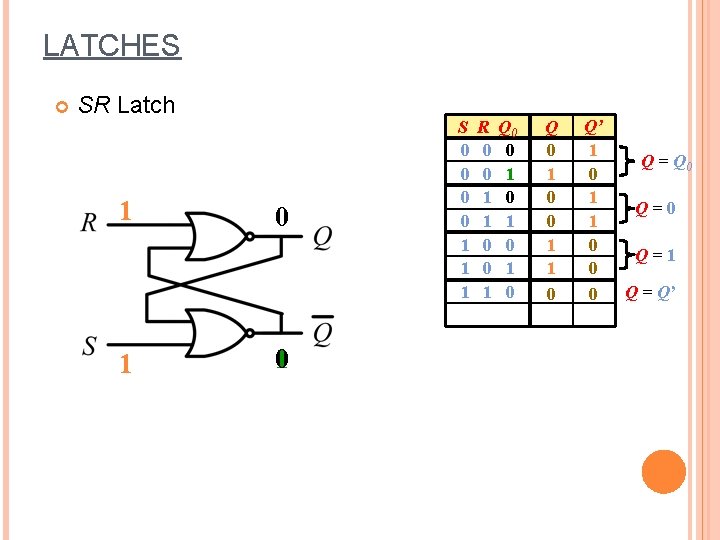

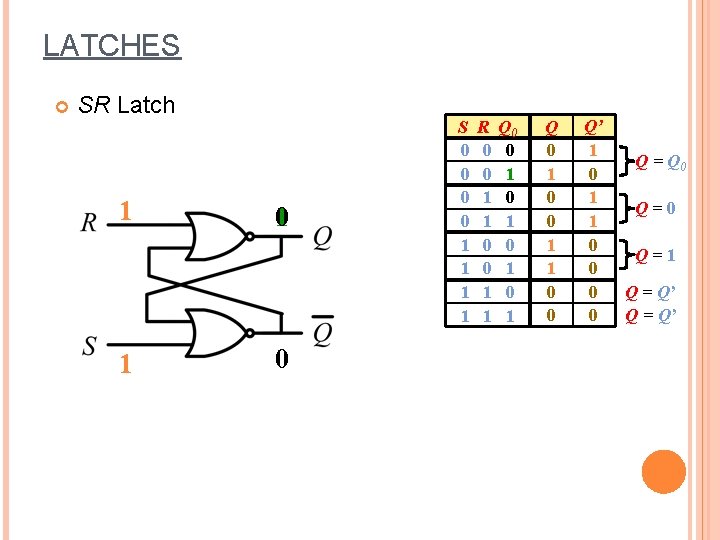

LATCHES SR Latch (cross coupled NOR) 0 0 0 1 S R Q 0 0 Q 0 Q’ 1 Q = Q 0 Initial Value 3

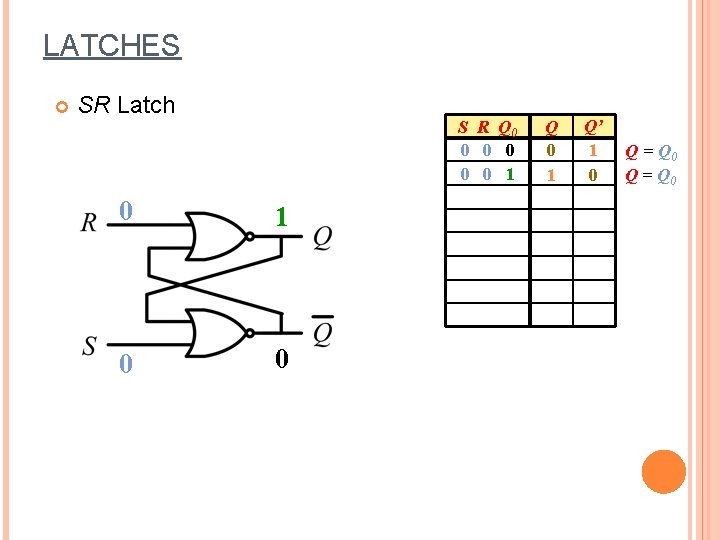

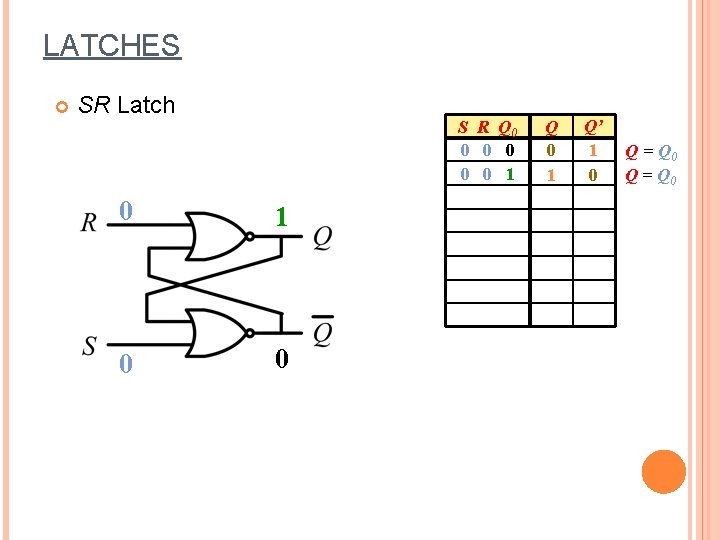

LATCHES SR Latch S R Q 0 0 0 1 0 0 Q 0 1 Q’ 1 0 Q = Q 0 4

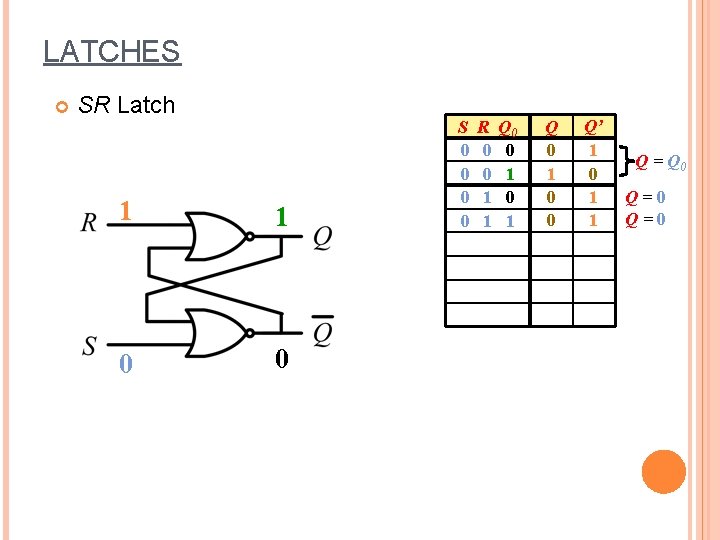

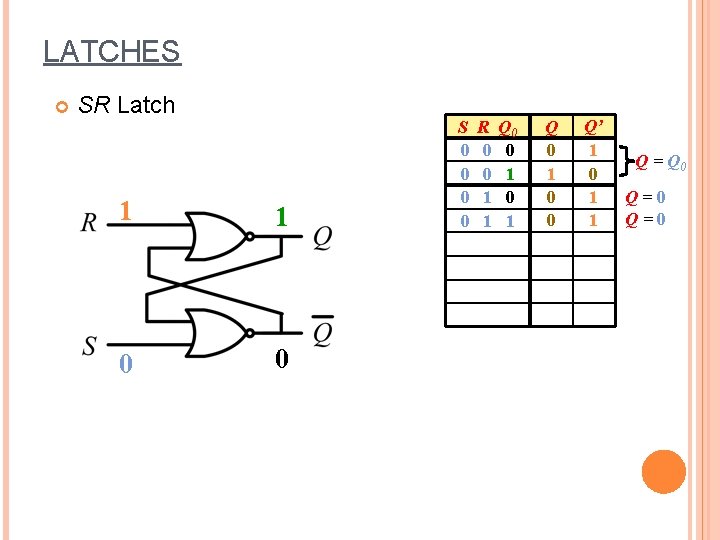

LATCHES SR Latch 1 0 0 1 S 0 0 0 R 0 0 1 Q 0 0 1 0 Q’ 1 0 1 Q = Q 0 Q=0 5

LATCHES SR Latch 1 1 0 0 S 0 0 R 0 0 1 1 Q 0 0 1 Q 0 1 0 0 Q’ 1 0 1 1 Q = Q 0 Q=0 6

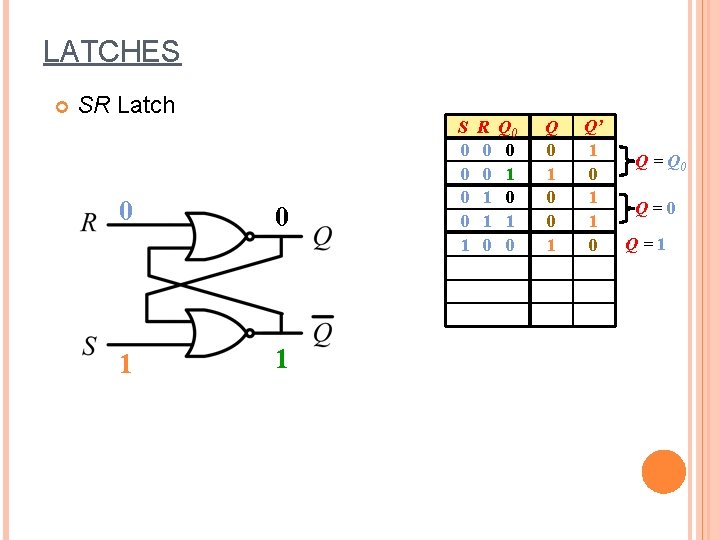

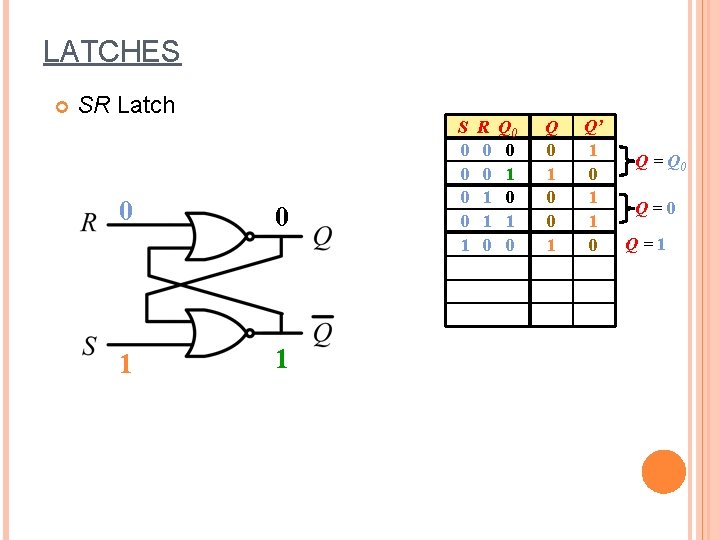

LATCHES SR Latch 0 1 0 S 0 0 1 R 0 0 1 1 0 Q 0 0 1 0 Q 0 1 0 0 1 Q’ 1 0 1 1 0 Q = Q 0 Q=1 1 7

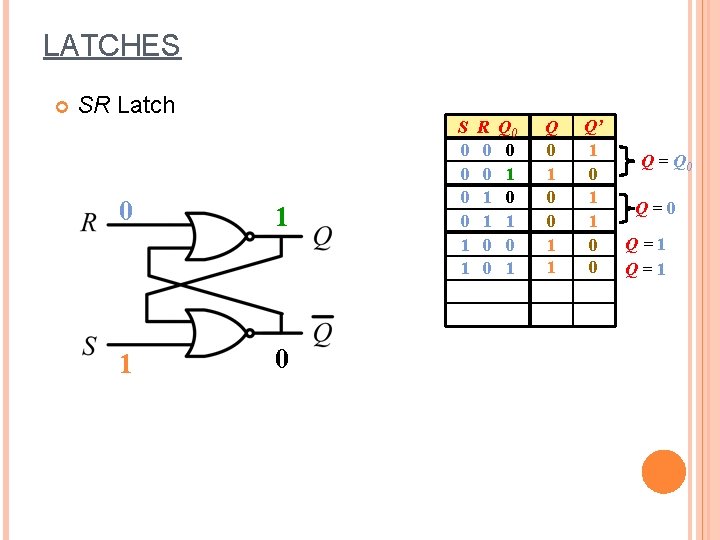

LATCHES SR Latch 0 1 1 S 0 0 1 1 R 0 0 1 1 0 0 Q 0 0 1 0 1 Q 0 1 0 0 1 1 Q’ 1 0 1 1 0 0 Q = Q 0 Q=1 Q=1 0 8

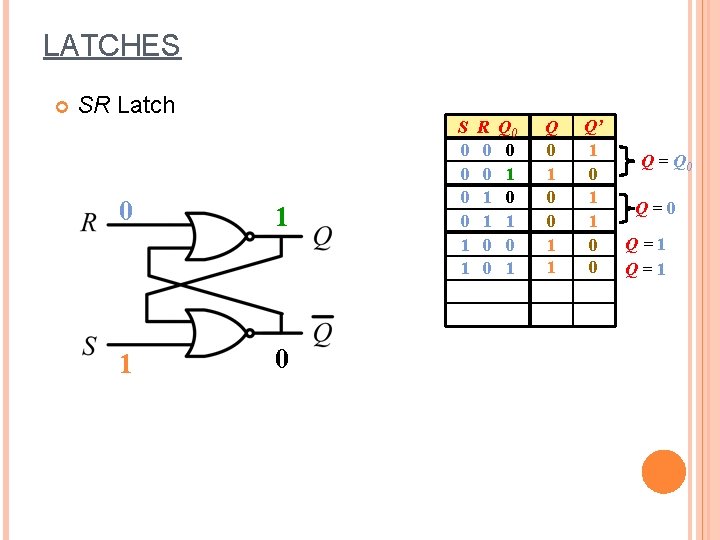

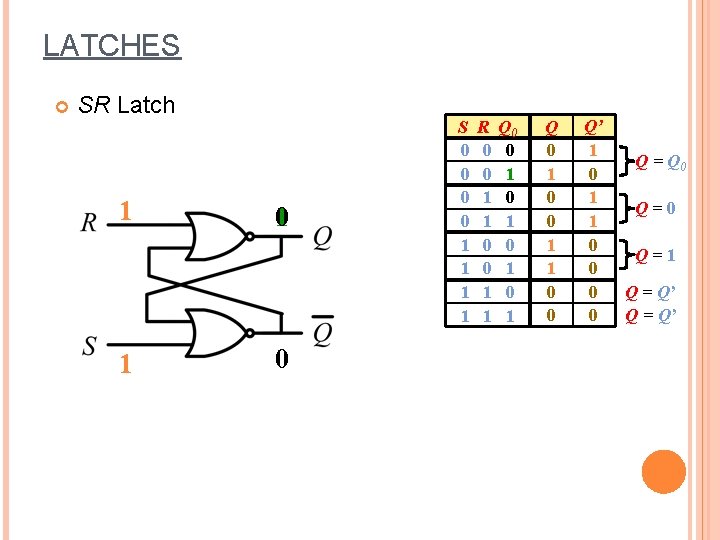

LATCHES SR Latch 1 1 0 S 0 0 1 1 1 R 0 0 1 1 0 0 1 Q 0 0 1 0 1 0 Q 0 1 0 0 1 1 0 Q’ 1 0 1 1 0 0 0 Q = Q 0 Q=1 Q = Q’ 10 9

LATCHES SR Latch 1 1 10 S 0 0 1 1 R 0 0 1 1 Q 0 0 1 0 1 Q 0 1 0 0 1 1 0 0 Q’ 1 0 1 1 0 0 Q = Q 0 Q=1 Q = Q’ 0 10

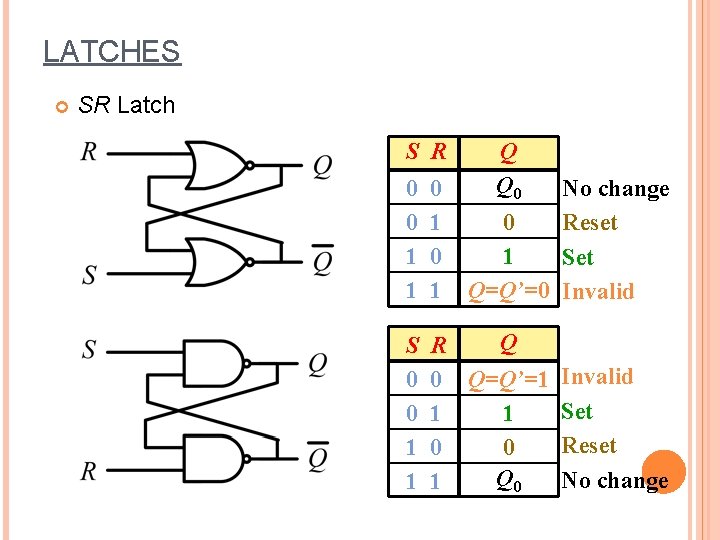

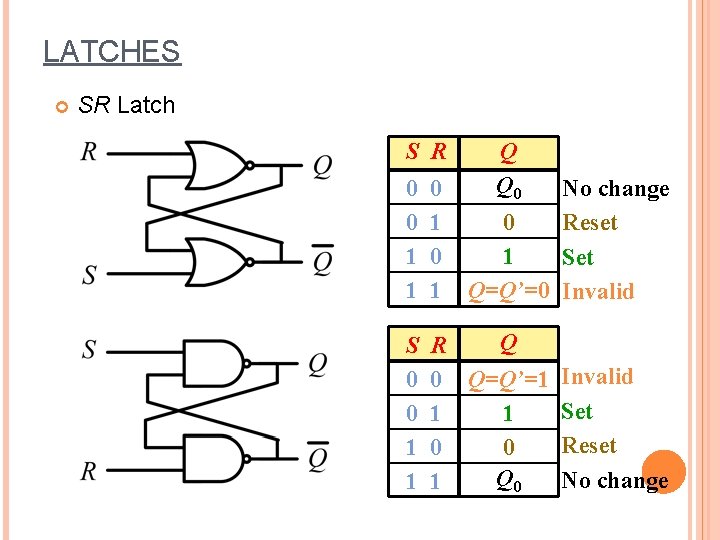

LATCHES SR Latch S R Q Q 0 0 0 1 1 0 1 S 0 0 1 1 Q R 0 Q=Q’=1 Invalid Set 1 1 Reset 0 0 Q 0 No change 1 No change 0 Reset 1 Set Q=Q’=0 Invalid 11

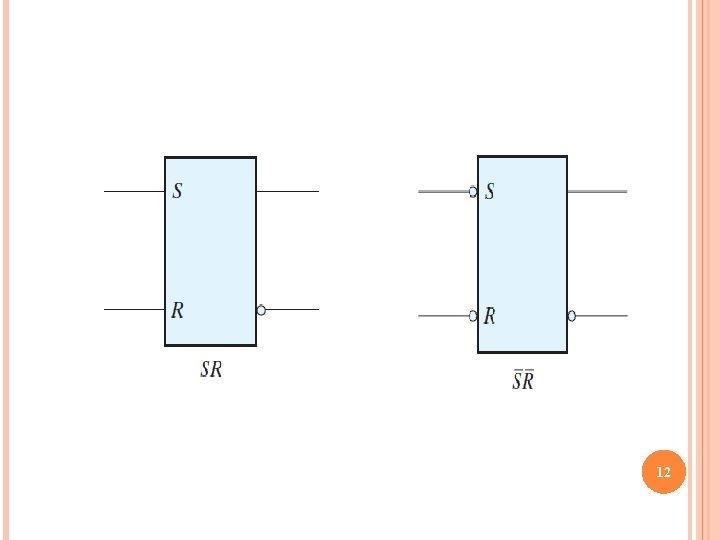

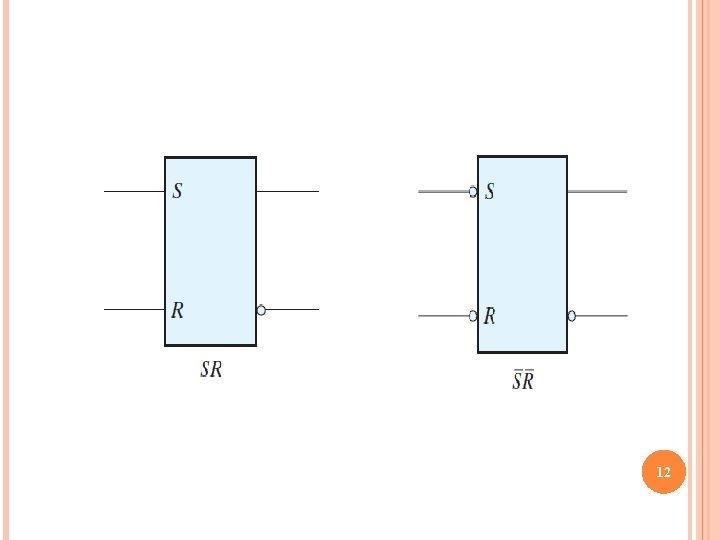

12

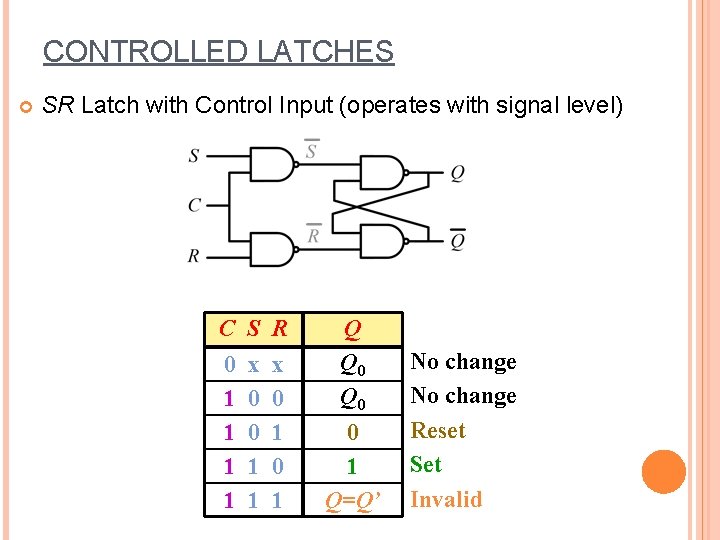

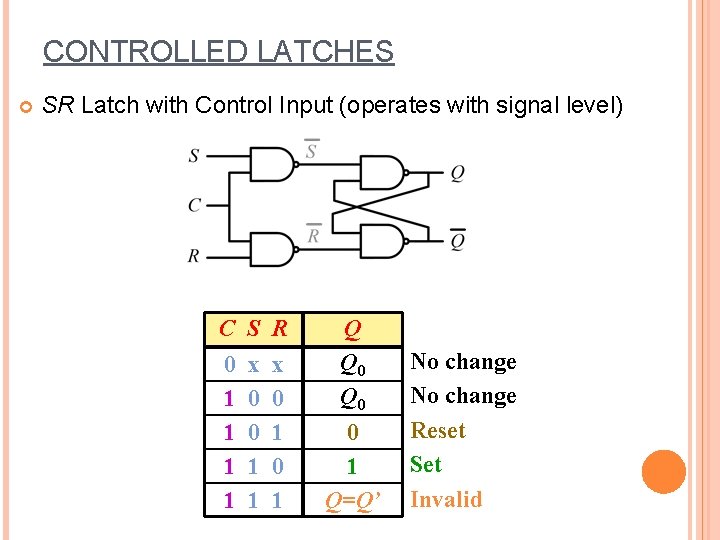

CONTROLLED LATCHES SR Latch with Control Input (operates with signal level) C S R 0 1 1 x 0 1 Q Q 0 0 1 Q=Q’ No change Reset Set Invalid 13

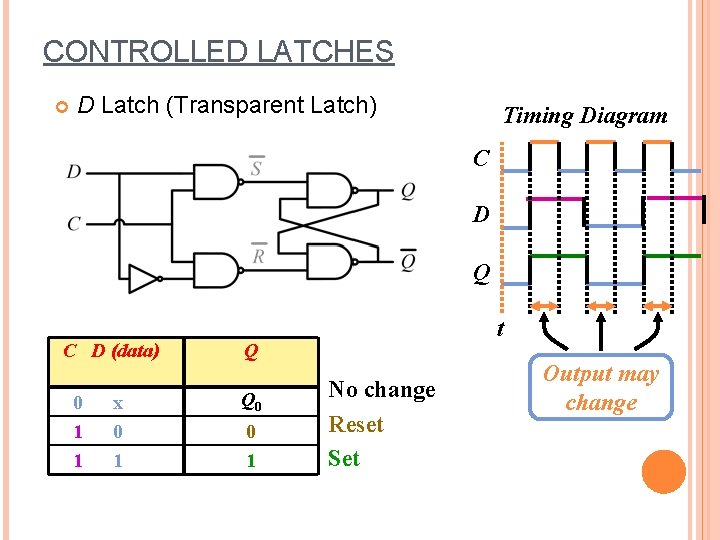

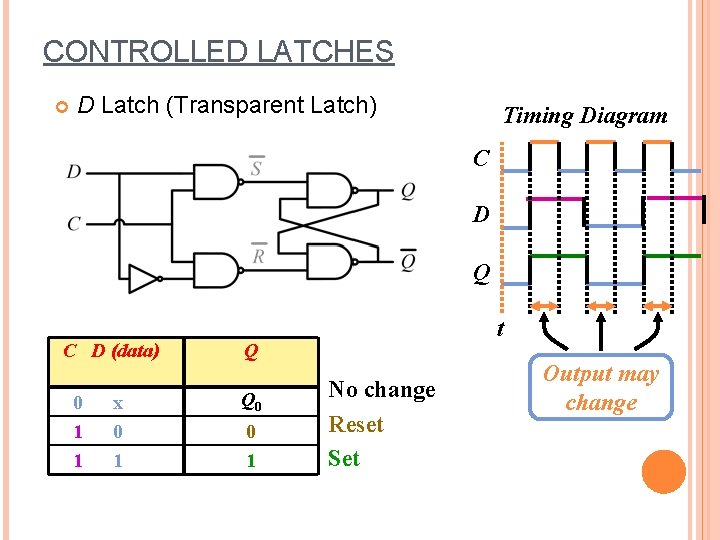

CONTROLLED LATCHES D Latch (Transparent Latch) Timing Diagram C D Q C D (data) 0 1 1 x 0 1 t Q Q 0 0 1 No change Reset Set Output may change 14

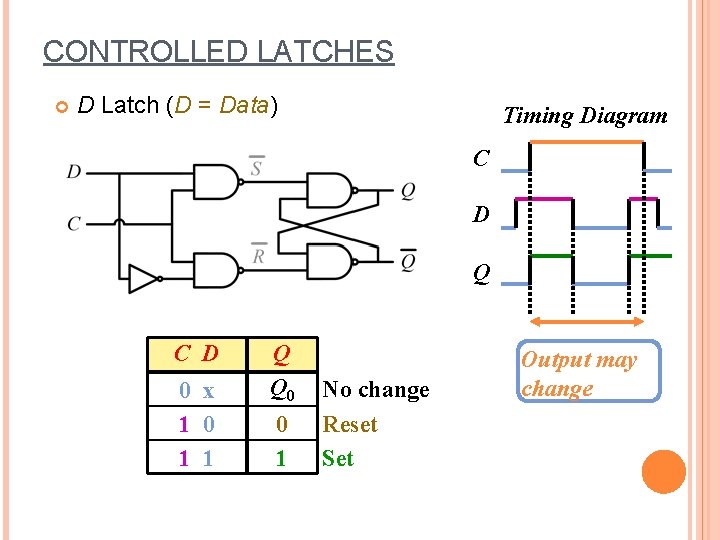

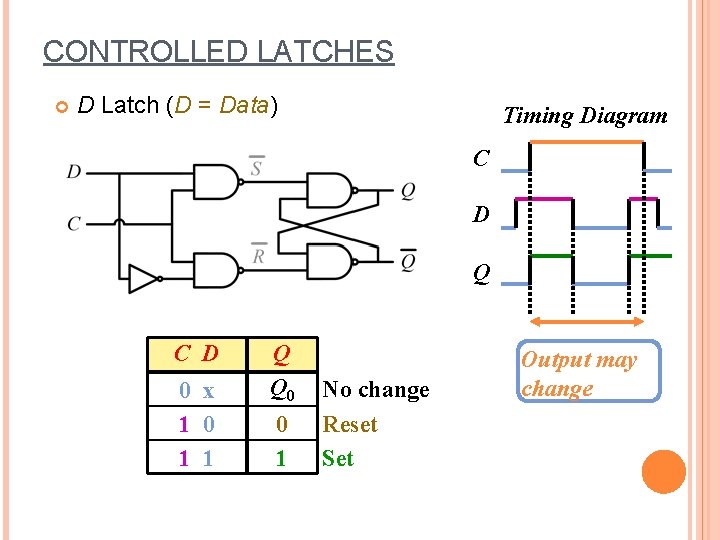

CONTROLLED LATCHES D Latch (D = Data) Timing Diagram C D Q C D 0 x 1 0 1 1 Q Q 0 0 1 No change Reset Set Output may change 15

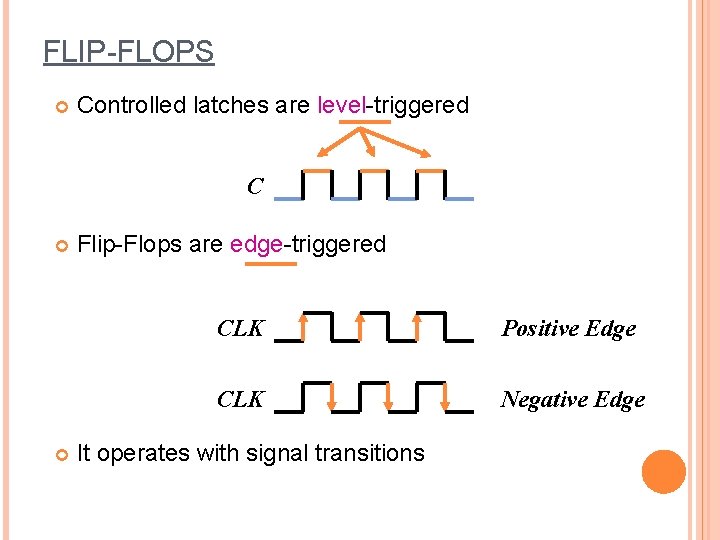

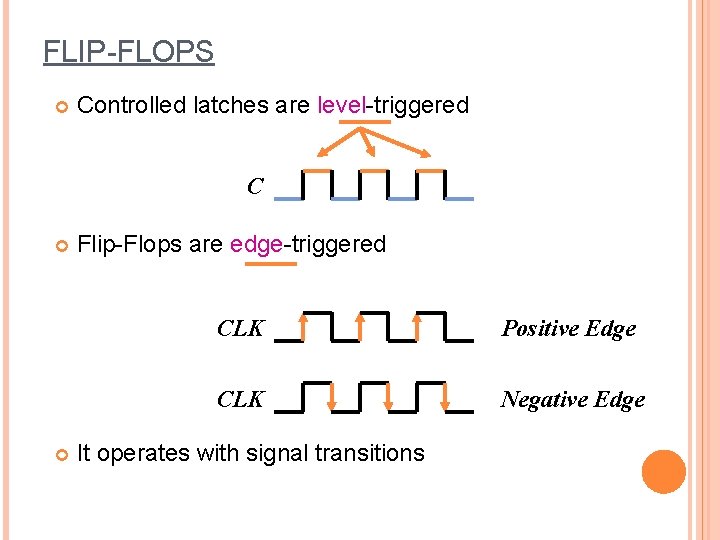

FLIP-FLOPS Controlled latches are level-triggered C Flip-Flops are edge-triggered CLK Positive Edge CLK Negative Edge It operates with signal transitions 16

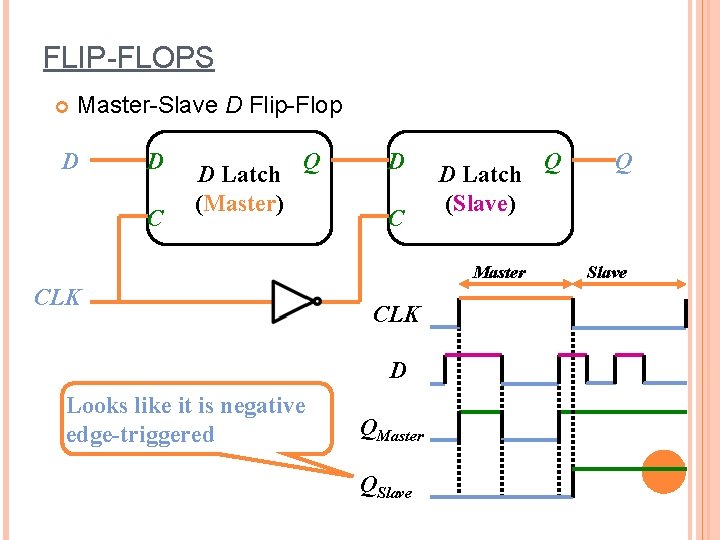

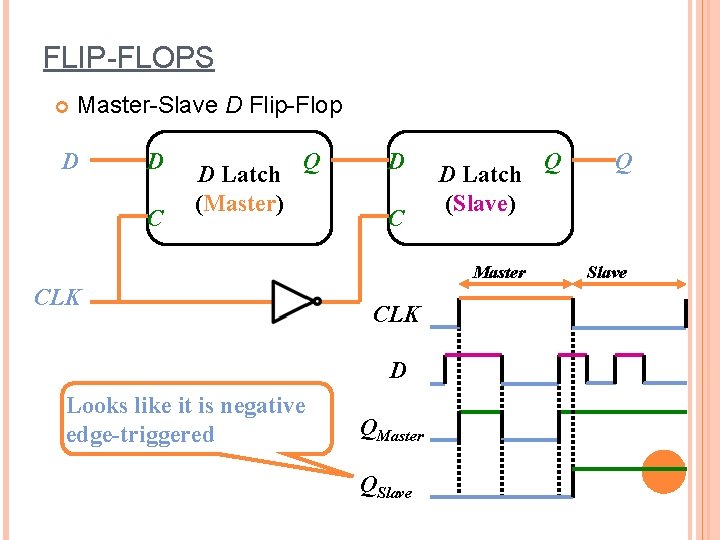

FLIP-FLOPS Master-Slave D Flip-Flop D D C D Latch (Master) Q D C D Latch (Slave) Master CLK Q Q Slave CLK D Looks like it is negative edge-triggered QMaster QSlave 17

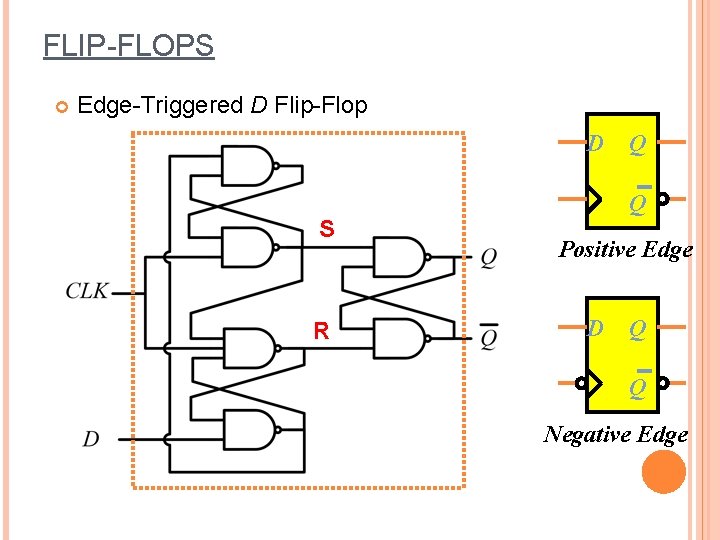

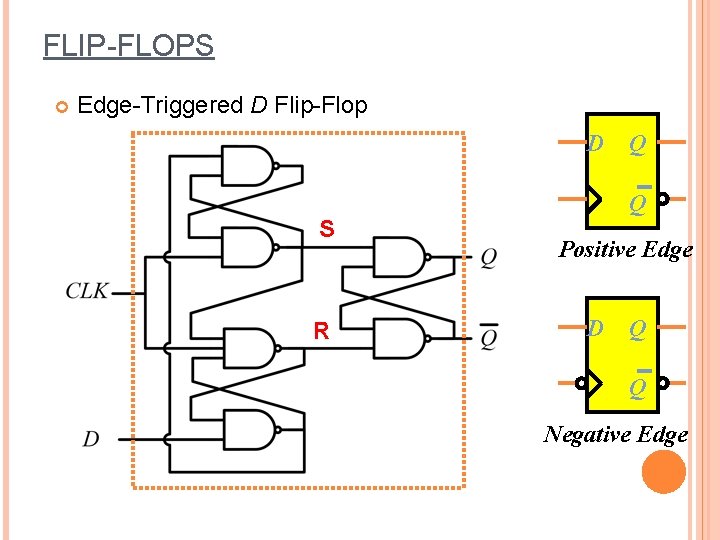

FLIP-FLOPS Edge-Triggered D Flip-Flop D S R Q Q Positive Edge D Q Q Negative Edge 18

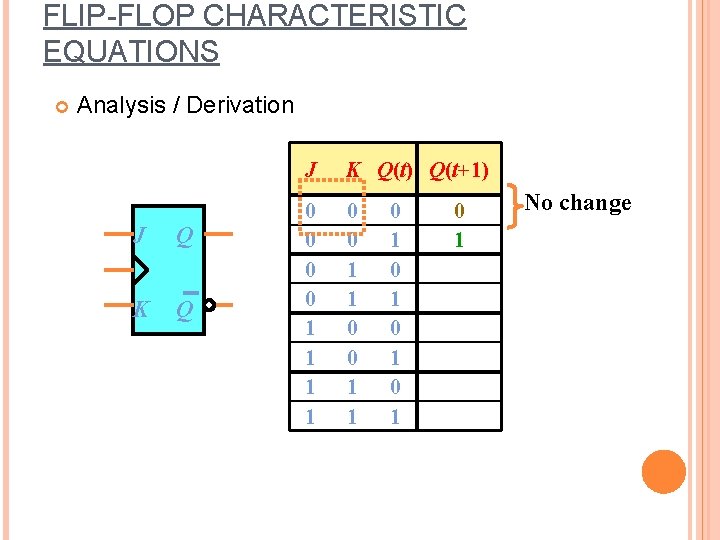

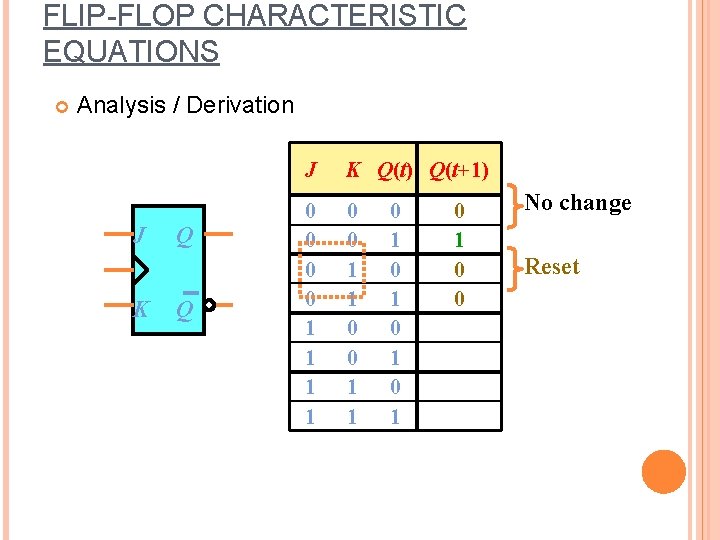

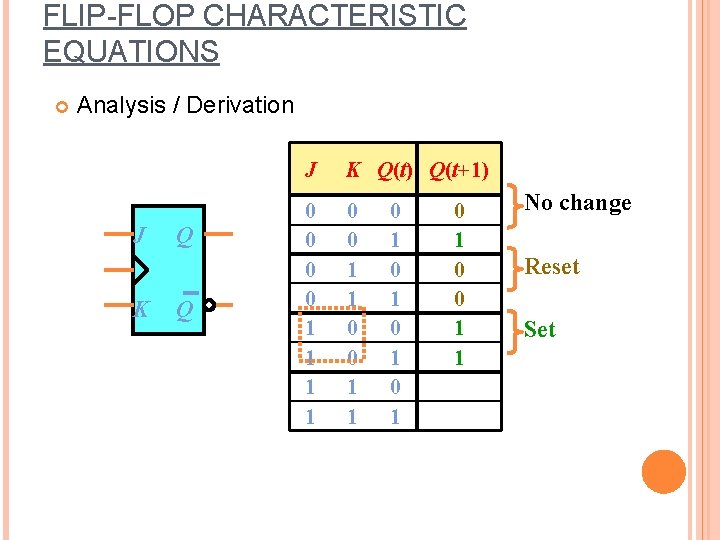

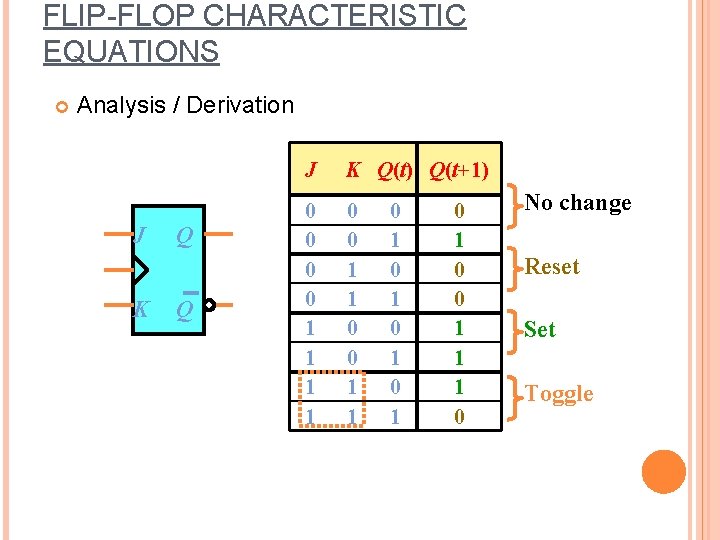

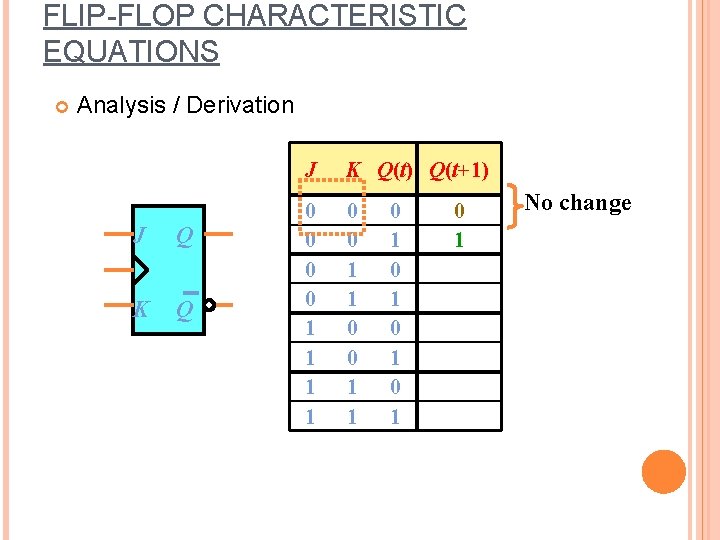

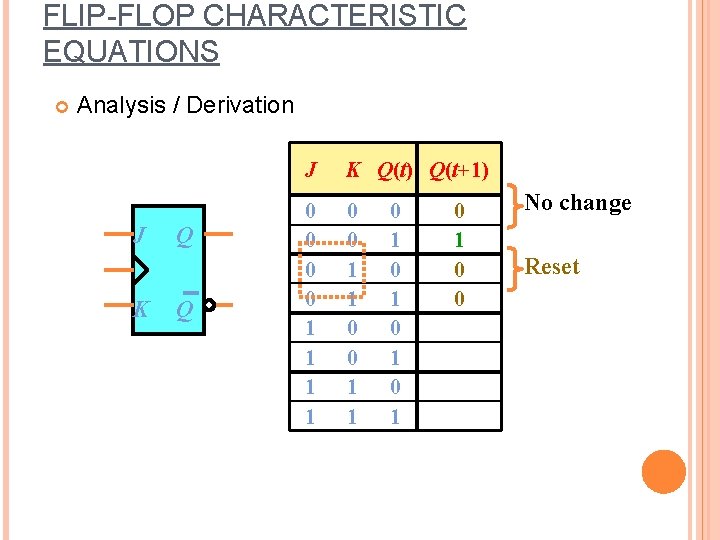

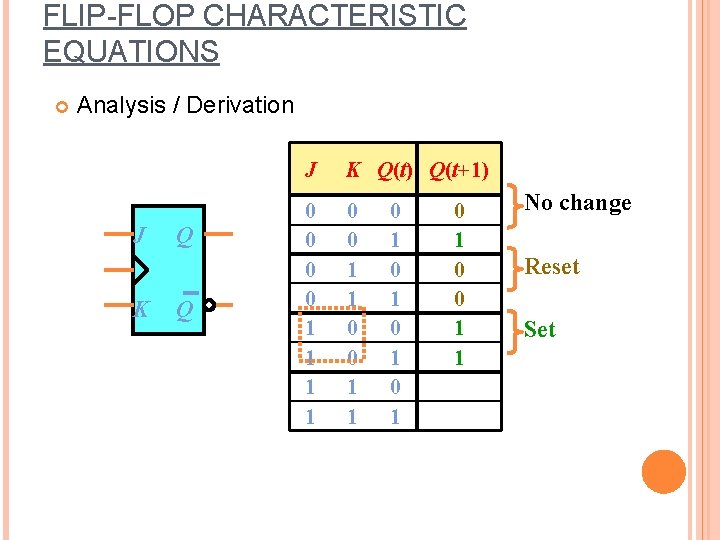

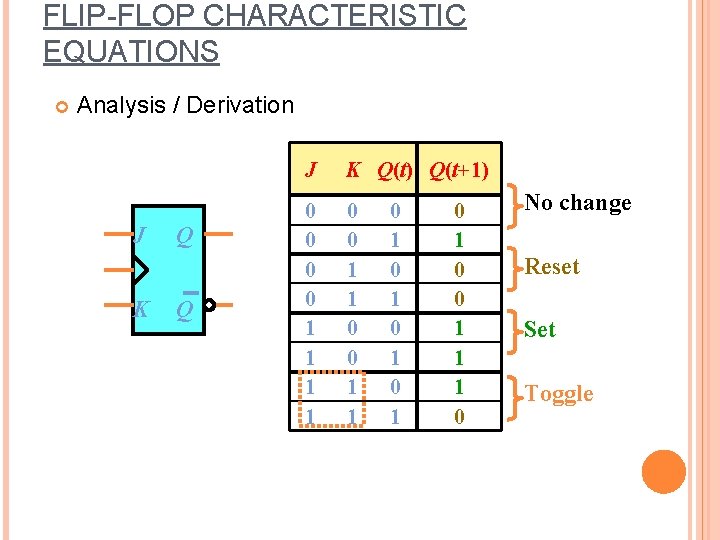

FLIP-FLOP CHARACTERISTIC EQUATIONS Analysis / Derivation J K Q Q J K Q(t) Q(t+1) 0 0 1 1 0 1 0 1 0 1 No change Reset Set Toggle 19

FLIP-FLOP CHARACTERISTIC EQUATIONS Analysis / Derivation J K Q Q J K Q(t) Q(t+1) 0 0 1 1 0 1 0 1 0 1 0 0 No change Reset Set Toggle 20

FLIP-FLOP CHARACTERISTIC EQUATIONS Analysis / Derivation J K Q Q J K Q(t) Q(t+1) 0 0 1 1 0 1 0 1 0 1 0 0 1 1 No change Reset Set Toggle 21

FLIP-FLOP CHARACTERISTIC EQUATIONS Analysis / Derivation J K Q Q J K Q(t) Q(t+1) 0 0 1 1 0 1 0 1 0 1 0 0 1 1 1 0 No change Reset Set Toggle 22

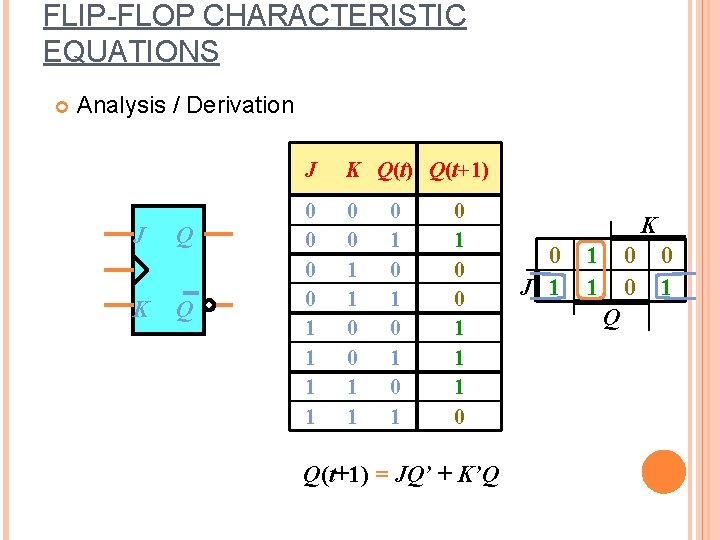

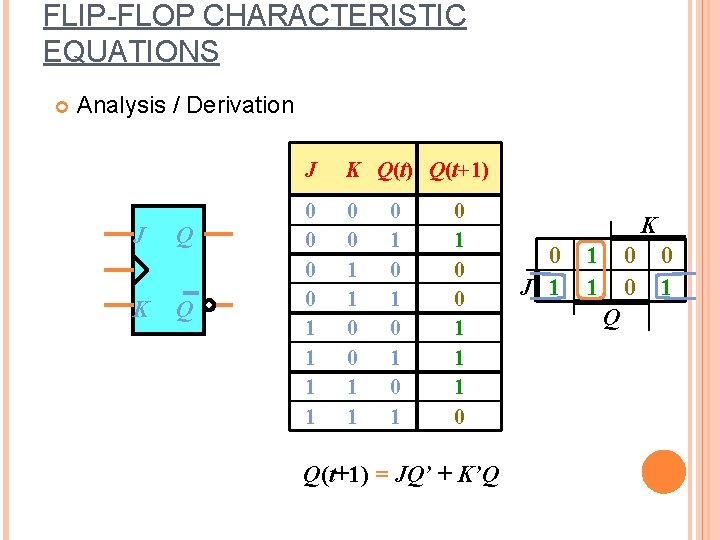

FLIP-FLOP CHARACTERISTIC EQUATIONS Analysis / Derivation J Q K Q J K Q(t) Q(t+1) 0 0 1 1 0 1 0 1 0 1 0 0 1 1 1 0 K 0 J 1 1 1 0 0 0 1 Q Q(t+1) = JQ’ + K’Q 23

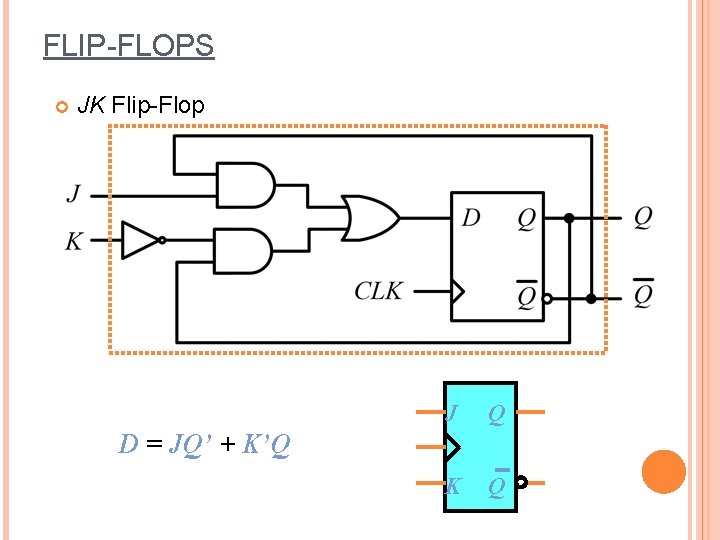

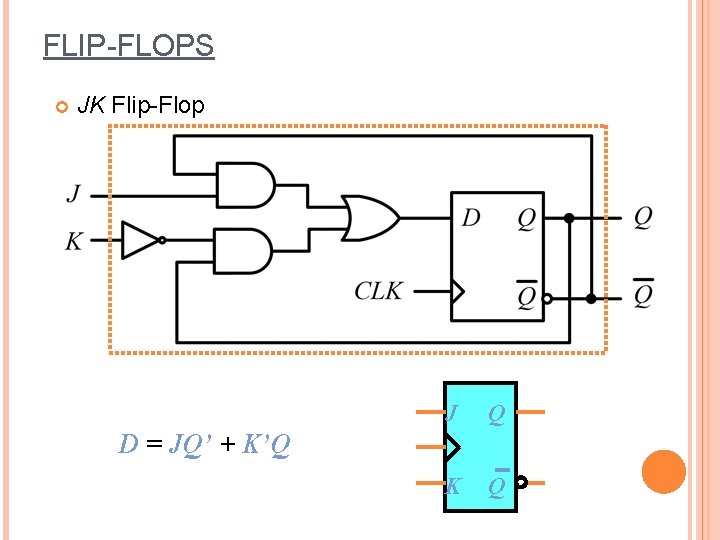

FLIP-FLOPS JK Flip-Flop J Q K Q D = JQ’ + K’Q 24

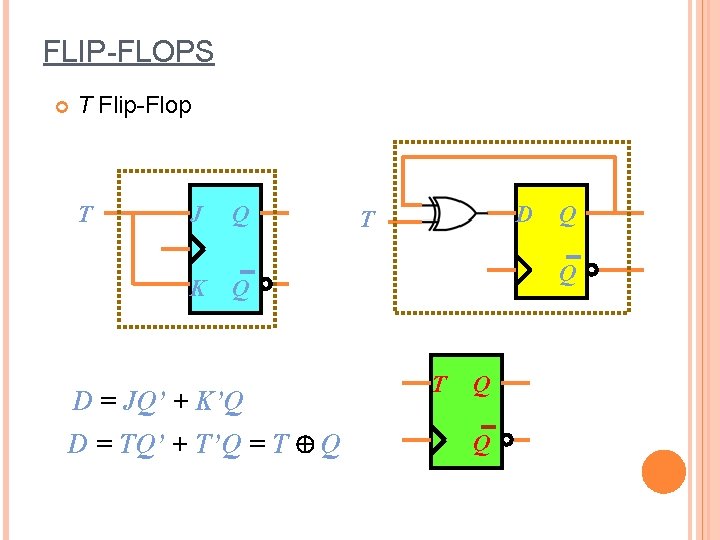

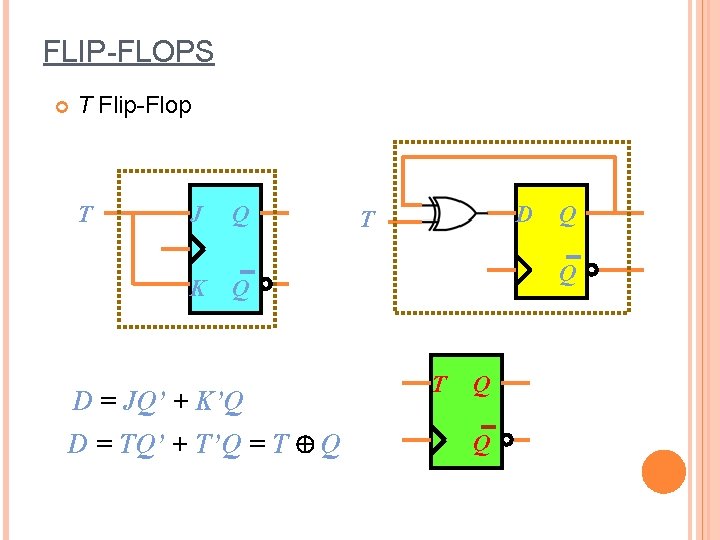

FLIP-FLOPS T Flip-Flop T J Q K Q D = JQ’ + K’Q D = TQ’ + T’Q = T Q D T Q Q 25

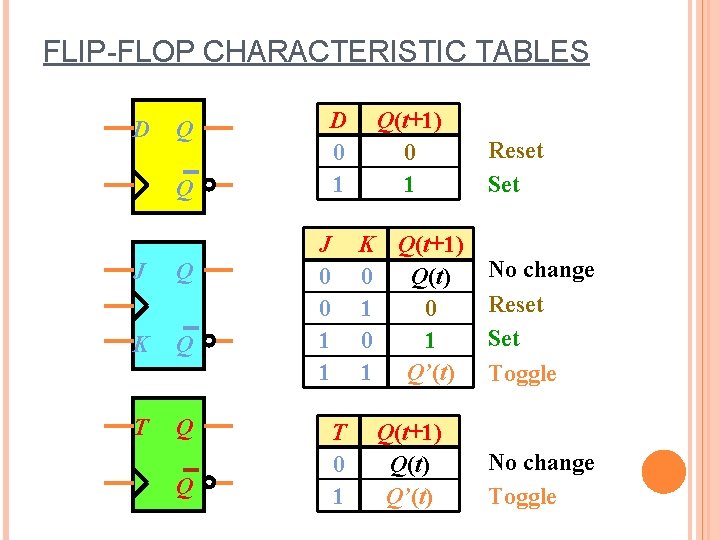

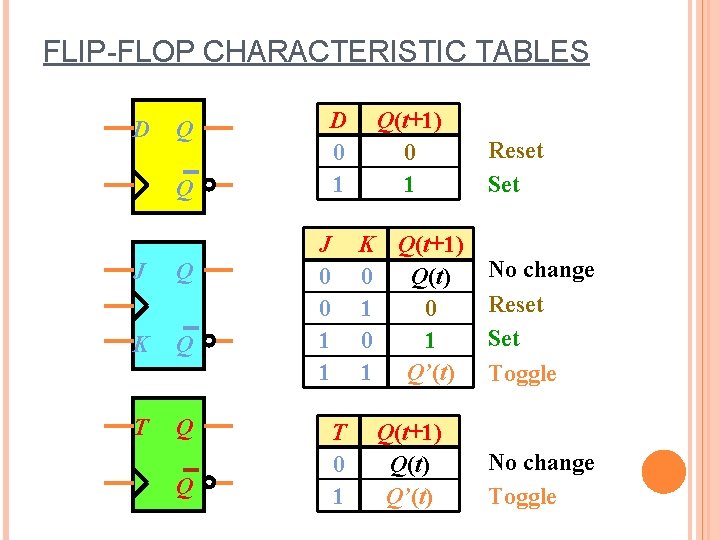

FLIP-FLOP CHARACTERISTIC TABLES D Q Q J Q K Q T Q Q D 0 1 J 0 0 1 1 T 0 1 Q(t+1) 0 1 Reset Set K Q(t+1) 0 Q(t) 1 0 0 1 1 Q’(t) No change Reset Set Toggle Q(t+1) Q(t) Q’(t) No change Toggle 26

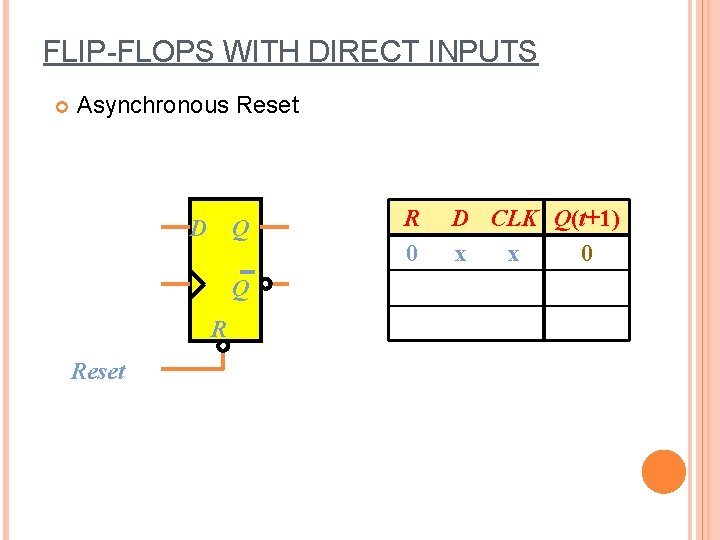

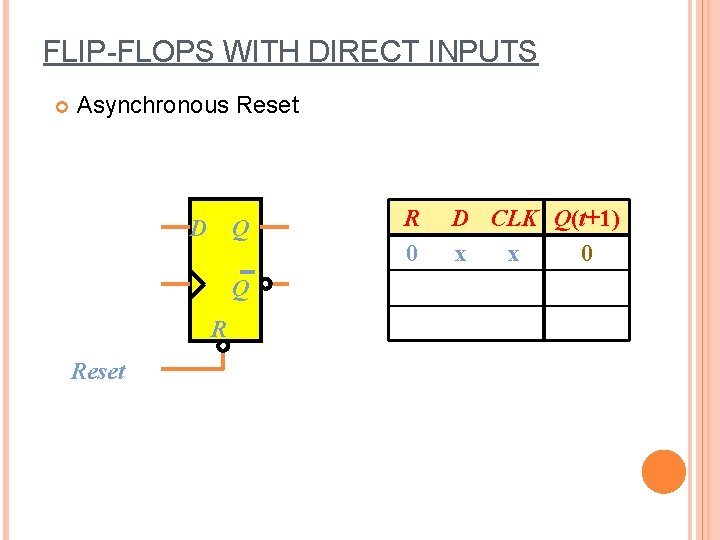

FLIP-FLOPS WITH DIRECT INPUTS Asynchronous Reset D Q R 0 D CLK Q(t+1) x x 0 Q R Reset 27

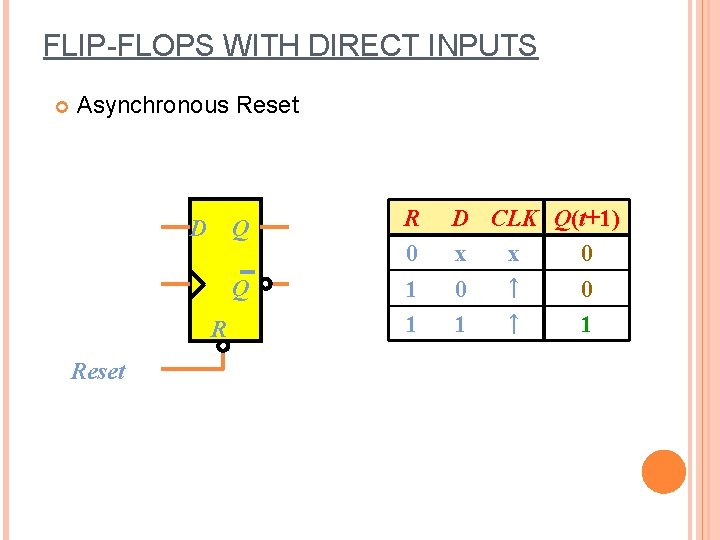

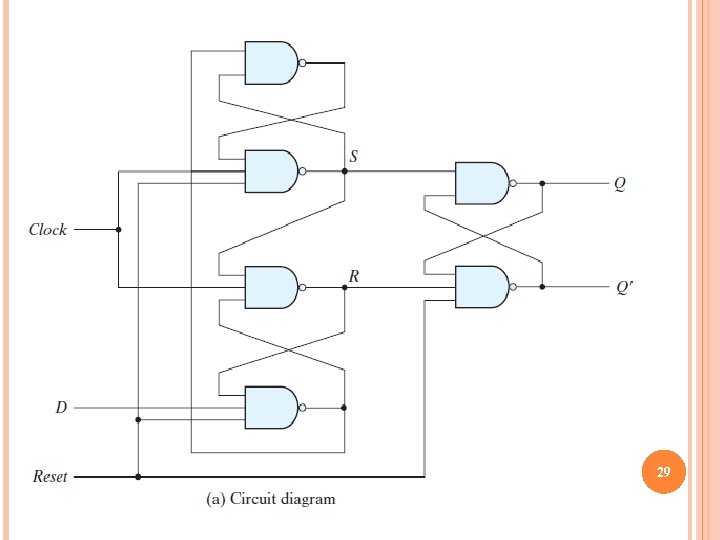

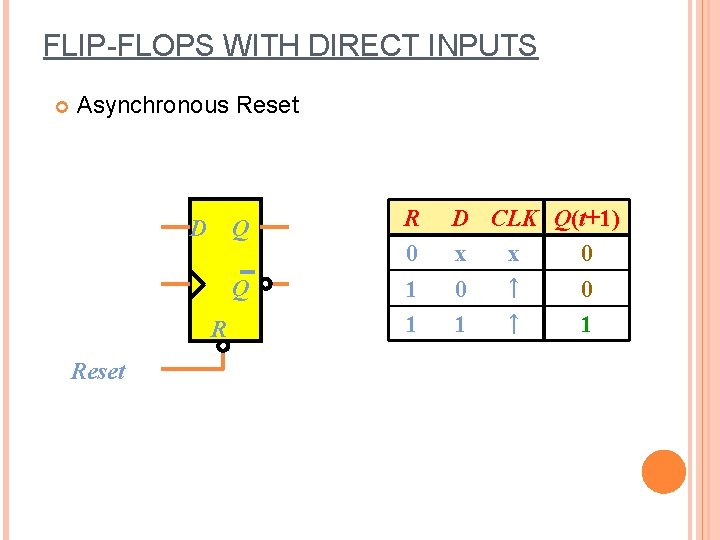

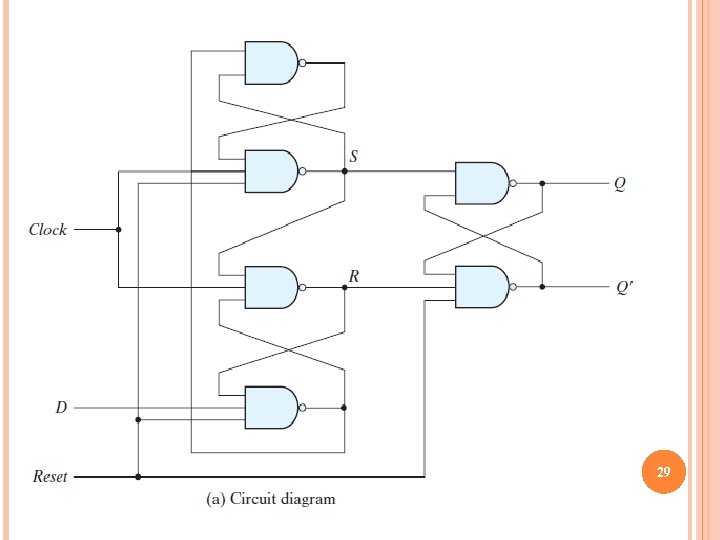

FLIP-FLOPS WITH DIRECT INPUTS Asynchronous Reset D Q Q R R 0 1 1 D CLK Q(t+1) x x 0 ↑ 0 0 ↑ 1 1 Reset 28

29

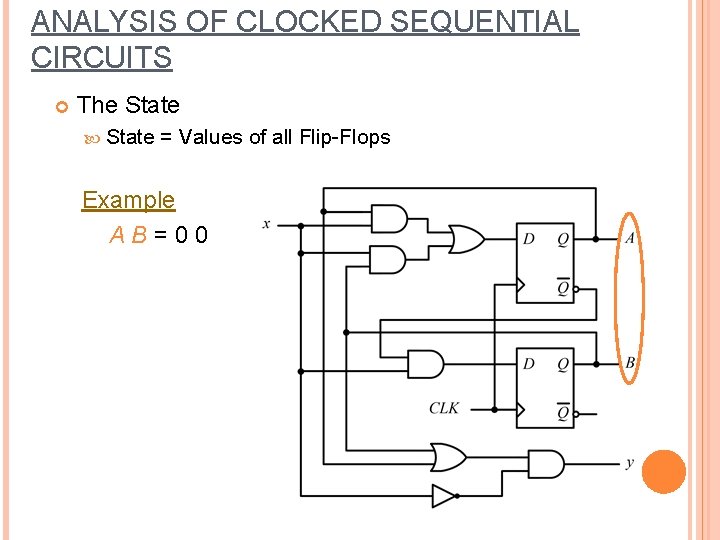

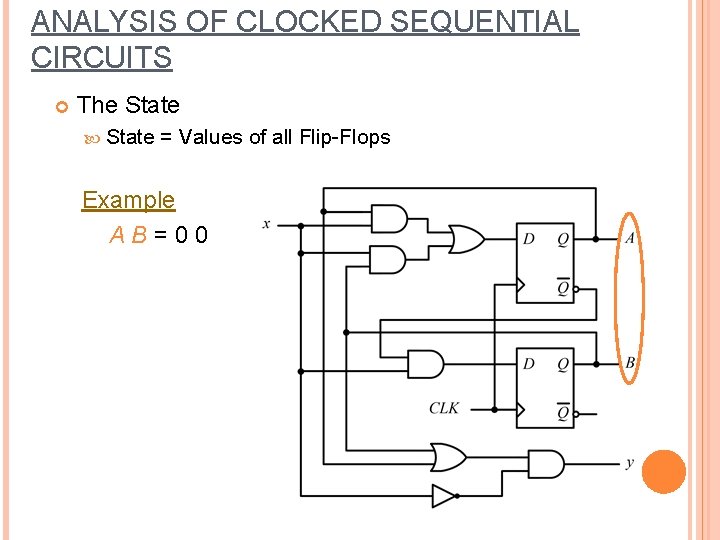

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS The State = Values of all Flip-Flops Example AB=00 30

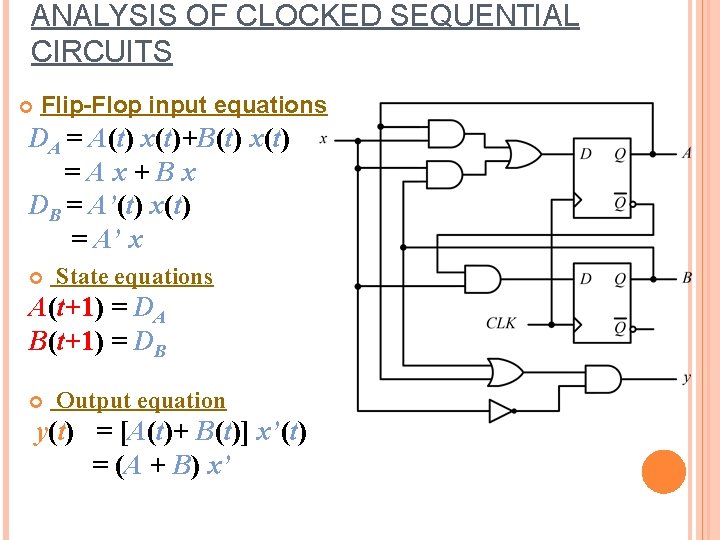

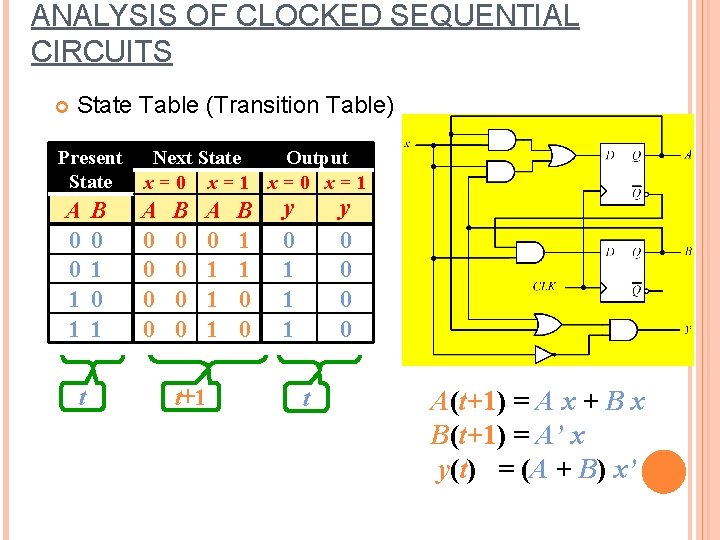

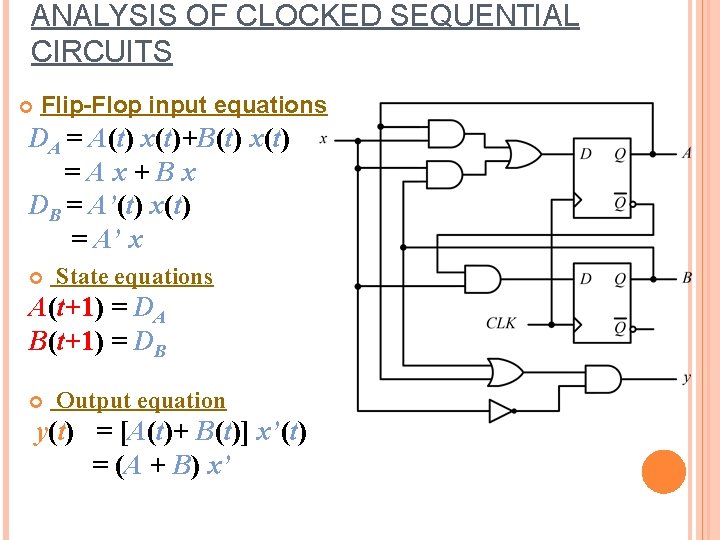

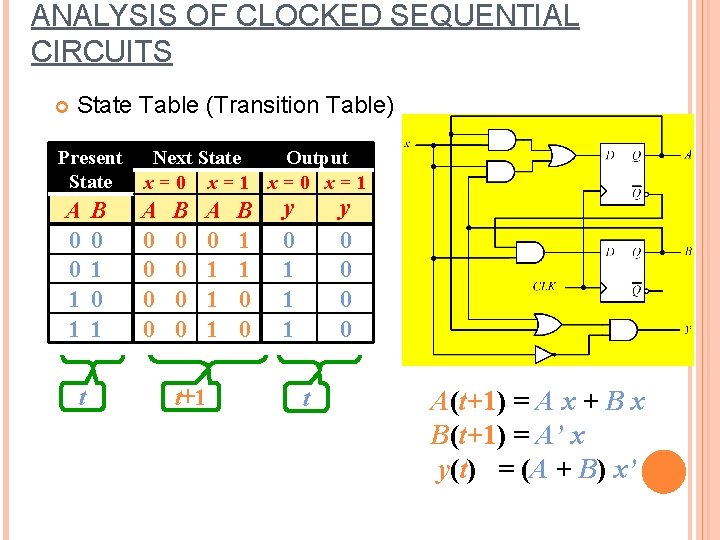

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS Flip-Flop input equations DA = A(t) x(t)+B(t) x(t) =Ax+Bx DB = A’(t) x(t) = A’ x State equations A(t+1) = DA B(t+1) = DB Output equation y(t) = [A(t)+ B(t)] x’(t) = (A + B) x’ 31

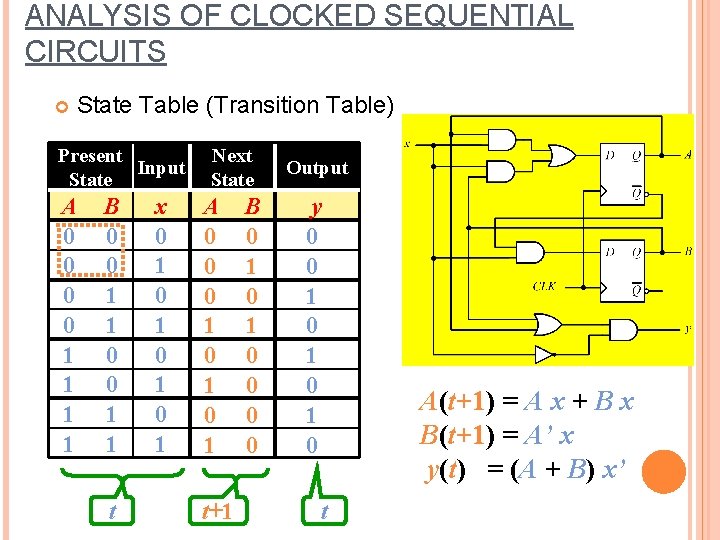

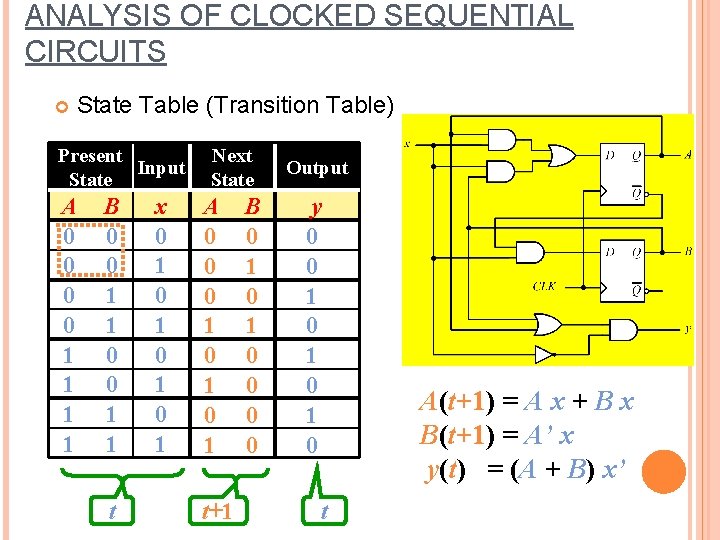

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS State Table (Transition Table) Present Input State A 0 0 1 1 B 0 0 1 1 t x 0 1 0 1 Next State A 0 0 0 1 0 1 t+1 B 0 1 0 0 Output y 0 0 1 0 1 0 t A(t+1) = A x + B x B(t+1) = A’ x y(t) = (A + B) x’ 32

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS State Table (Transition Table) Present State A 0 0 1 1 t B 0 1 Next State Output x=0 x=1 A 0 0 B 0 0 A 0 1 1 1 t+1 B 1 1 0 0 y 0 1 1 1 y 0 0 t A(t+1) = A x + B x B(t+1) = A’ x y(t) = (A + B) x’ 33

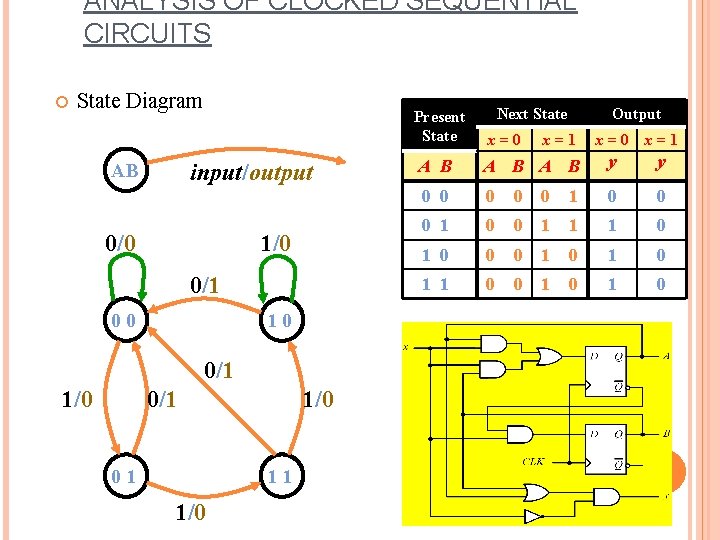

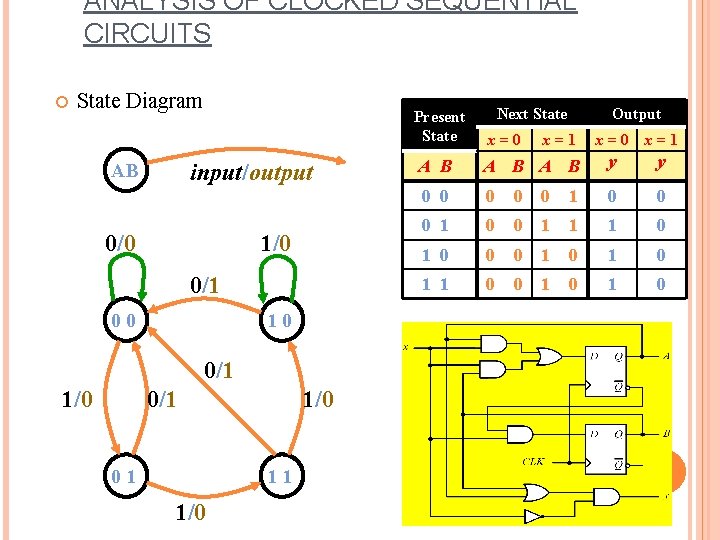

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS State Diagram Present State input/output AB 0/0 1/0 0/1 00 Next State x=0 Output x=1 x=0 x=1 A B A B y y 0 0 0 1 1 1 0 0 0 1 0 1 1 0 0 1 0 10 0/1 1/0 0/1 01 1/0 11 1/0 34

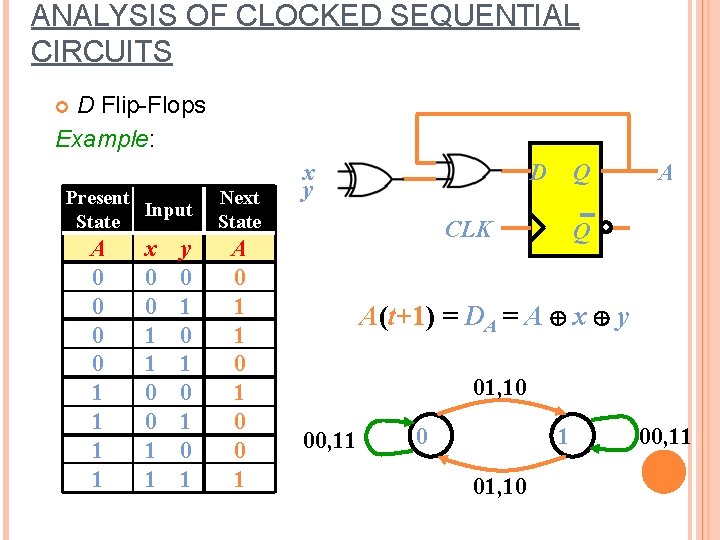

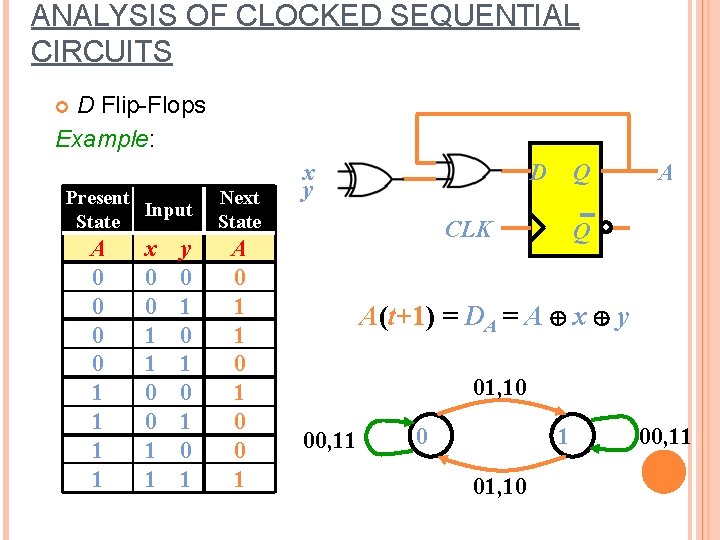

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS D Flip-Flops Example: Present Input State A 0 0 1 1 x 0 0 1 1 y 0 1 0 1 Next State A 0 1 1 0 0 1 x y D Q CLK A Q A(t+1) = DA = A x y 01, 10 00, 11 0 1 00, 11 01, 10 35

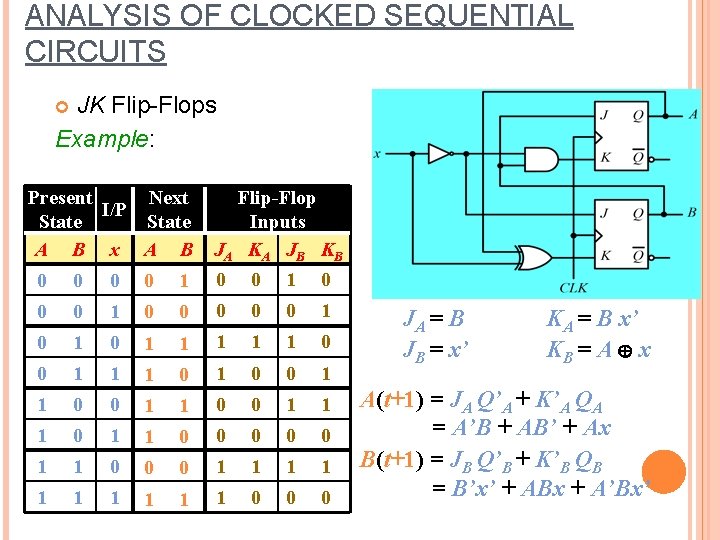

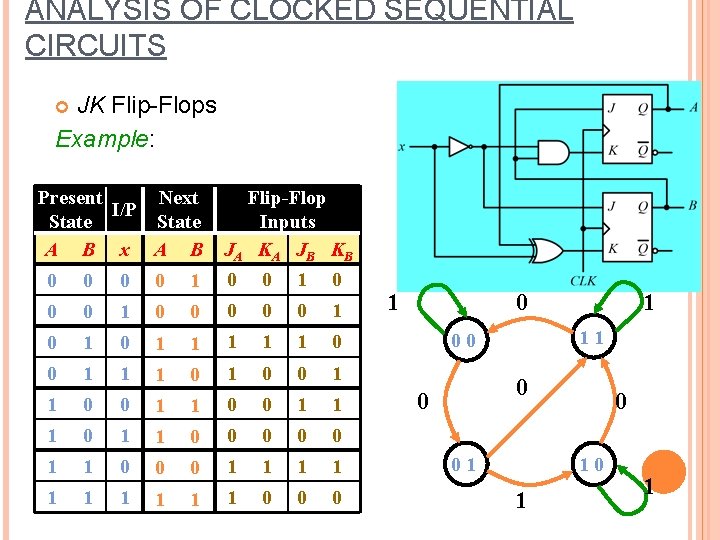

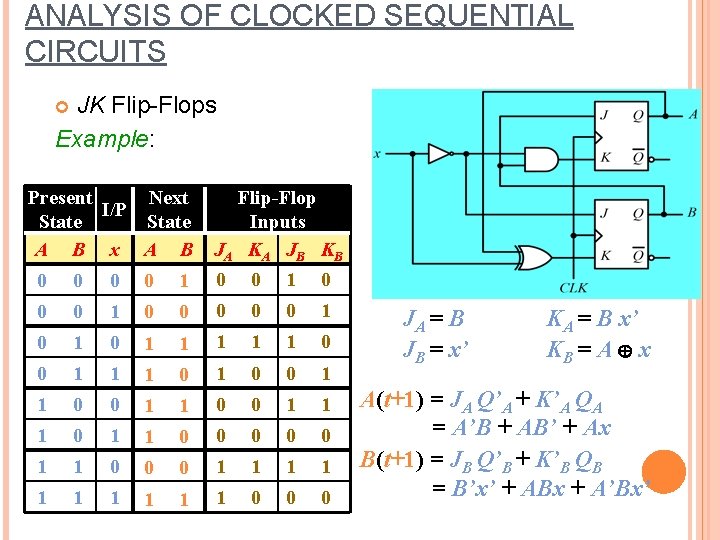

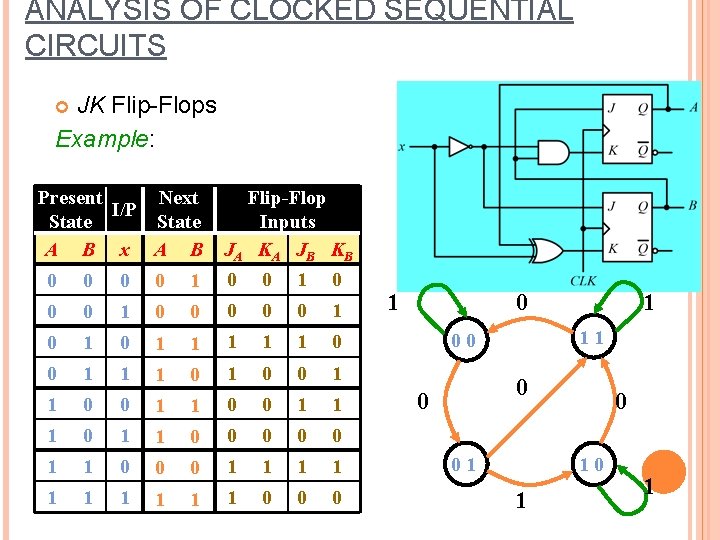

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS JK Flip-Flops Example: Present Next I/P State A B x A B Flip-Flop Inputs JA KA JB KB 0 0 1 0 0 0 1 0 1 1 1 0 0 1 1 0 0 1 1 1 0 0 0 1 1 1 1 1 0 0 0 JA = B JB = x’ KA = B x’ KB = A x A(t+1) = JA Q’A + K’A QA = A’B + AB’ + Ax B(t+1) = JB Q’B + K’B QB = B’x’ + ABx + A’Bx’ 36

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS JK Flip-Flops Example: Present Next I/P State A B x A B Flip-Flop Inputs JA KA JB KB 0 0 1 0 0 0 1 0 1 1 1 0 0 1 1 0 0 1 1 1 0 0 0 1 1 1 1 1 0 0 0 1 11 00 0 0 01 0 10 1 1 37

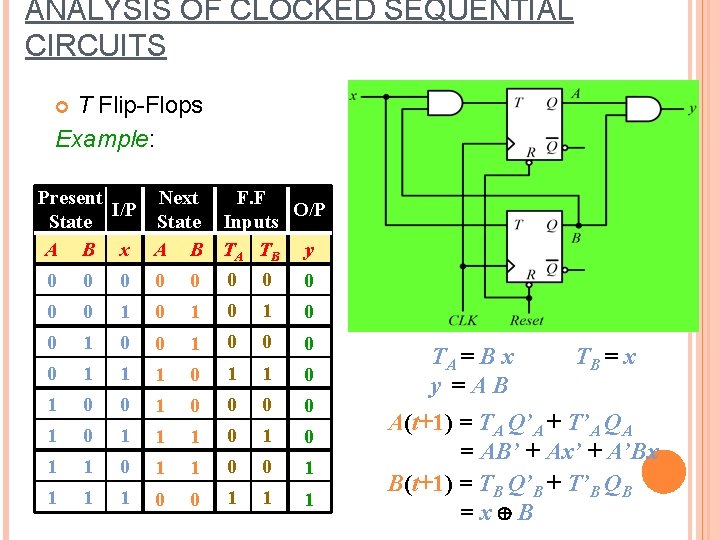

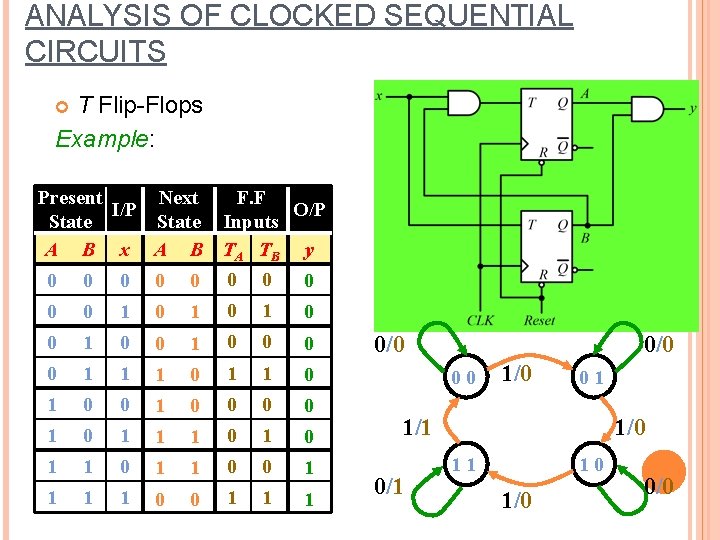

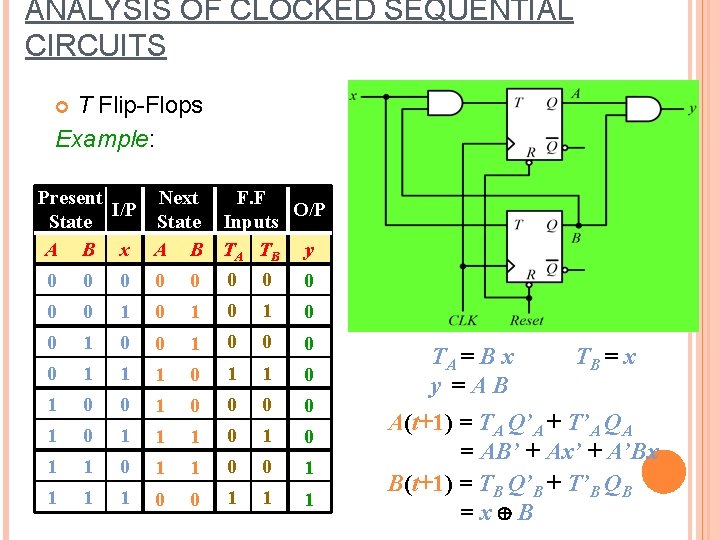

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS T Flip-Flops Example: Present Next F. F I/P O/P State Inputs A B x A B TA TB y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 0 1 1 1 0 0 1 1 0 0 1 1 1 TA = B x y =AB TB = x A(t+1) = TA Q’A + T’A QA = AB’ + Ax’ + A’Bx B(t+1) = TB Q’B + T’B QB =x B 38

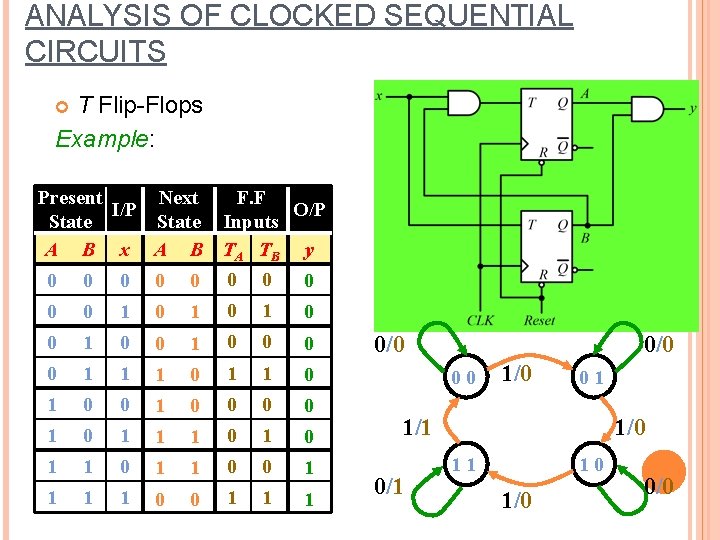

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS T Flip-Flops Example: Present Next F. F I/P O/P State Inputs A B x A B TA TB y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 0 1 1 1 0 0 1 1 0 0 1 1 1 0/0 00 1/0 01 1/1 0/1 1/0 11 10 1/0 0/0 39

THE PROBLEMS: 5. 3, 5. 4, 5. 6 5. 7, 5. 9, 5. 10, 5. 11 40

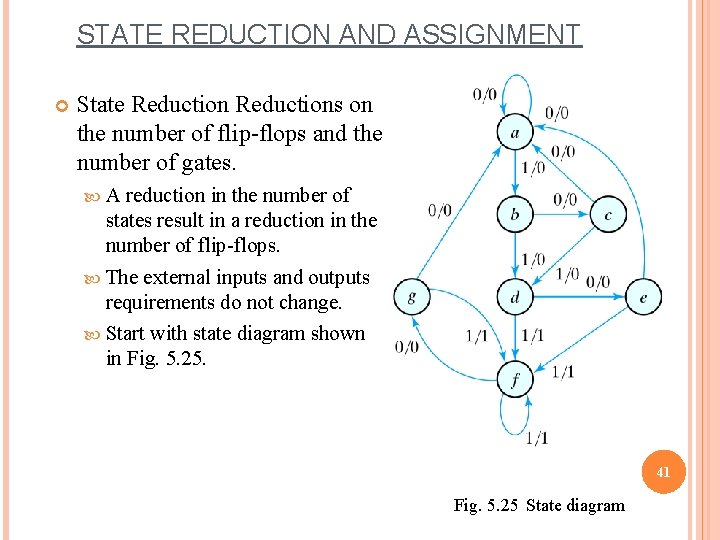

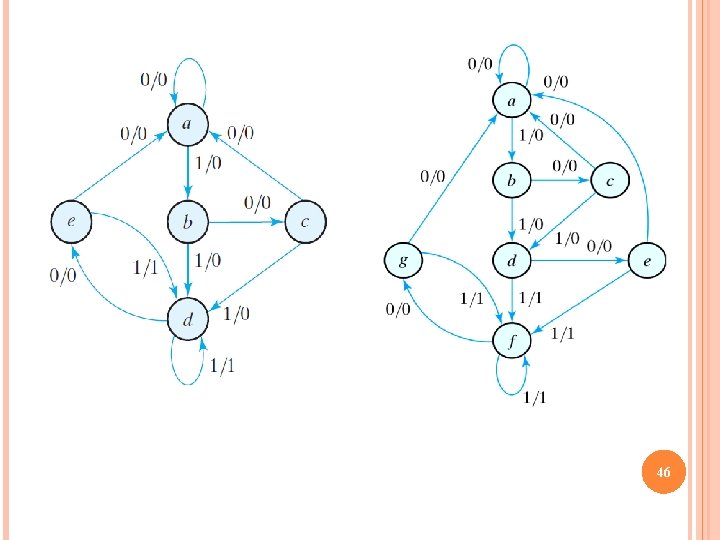

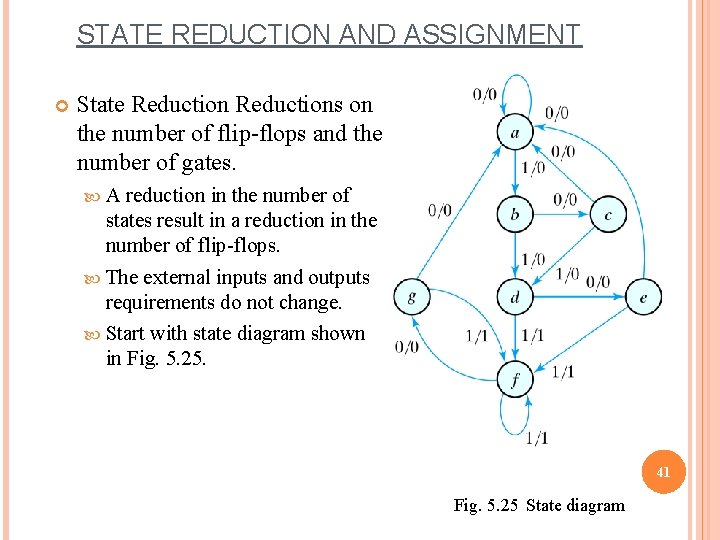

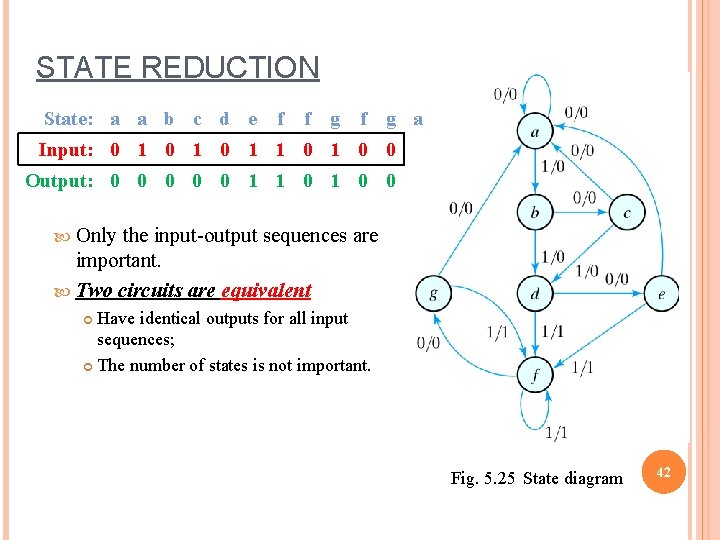

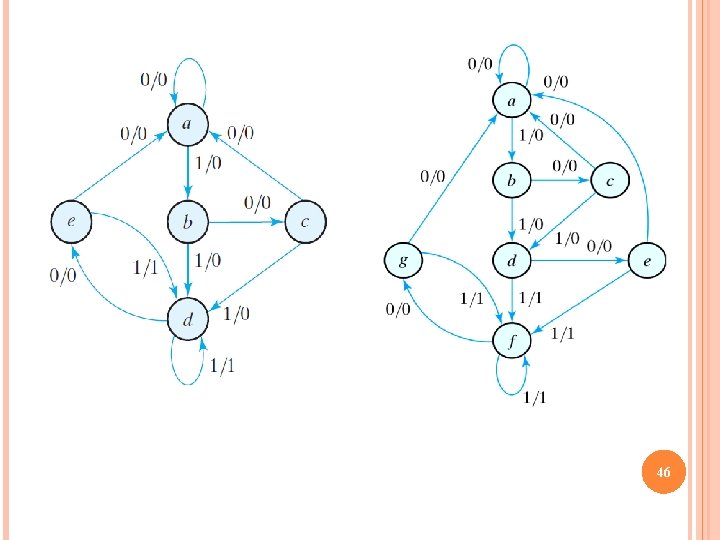

STATE REDUCTION AND ASSIGNMENT State Reductions on the number of flip-flops and the number of gates. A reduction in the number of states result in a reduction in the number of flip-flops. The external inputs and outputs requirements do not change. Start with state diagram shown in Fig. 5. 25. 41 Fig. 5. 25 State diagram

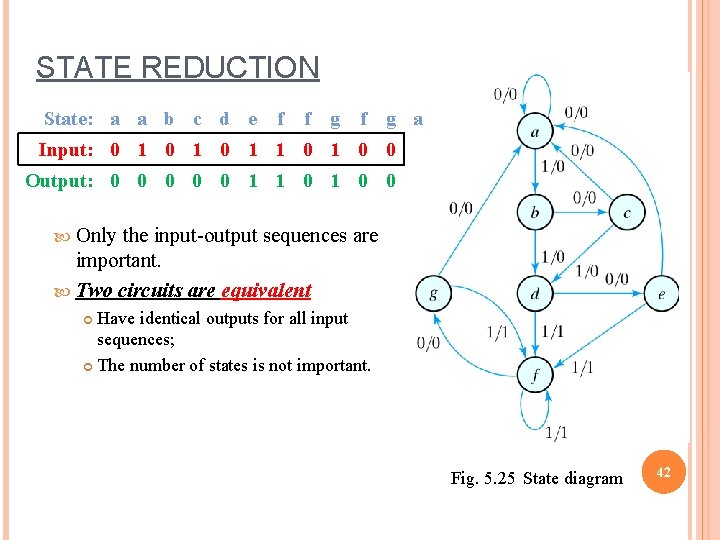

STATE REDUCTION State: a a b c d e f f g a Input: 0 1 0 1 1 0 0 Output: 0 0 0 1 1 0 0 Only the input-output sequences are important. Two circuits are equivalent Have identical outputs for all input sequences; The number of states is not important. Fig. 5. 25 State diagram 42

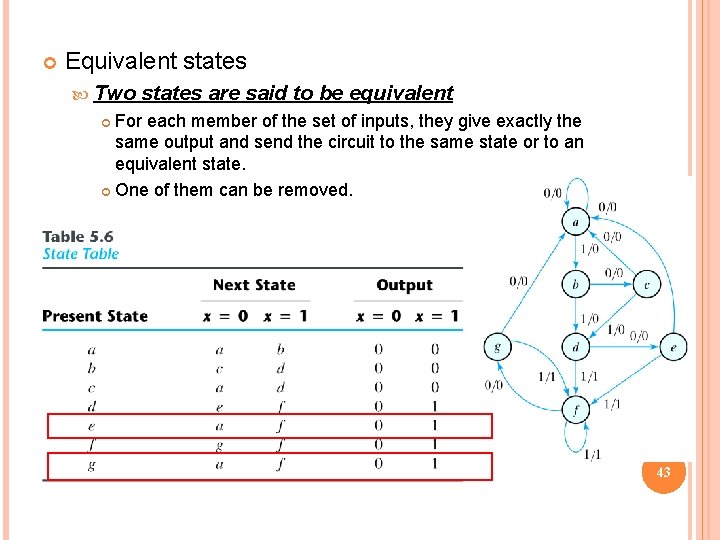

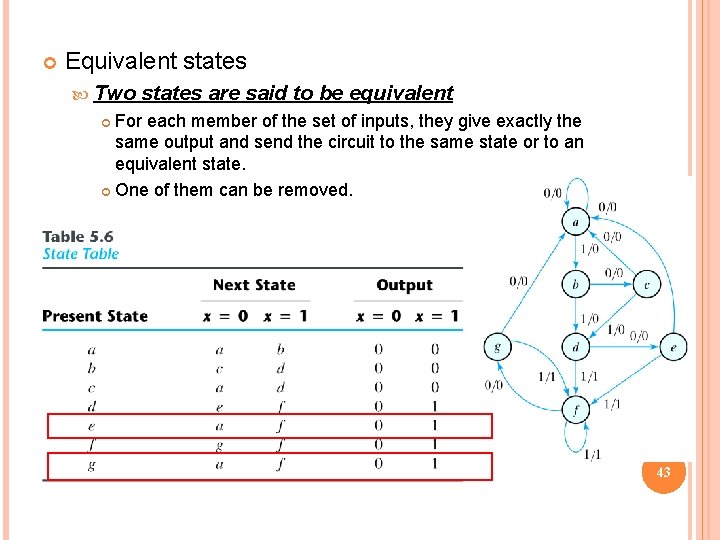

Equivalent states Two states are said to be equivalent For each member of the set of inputs, they give exactly the same output and send the circuit to the same state or to an equivalent state. One of them can be removed. 43

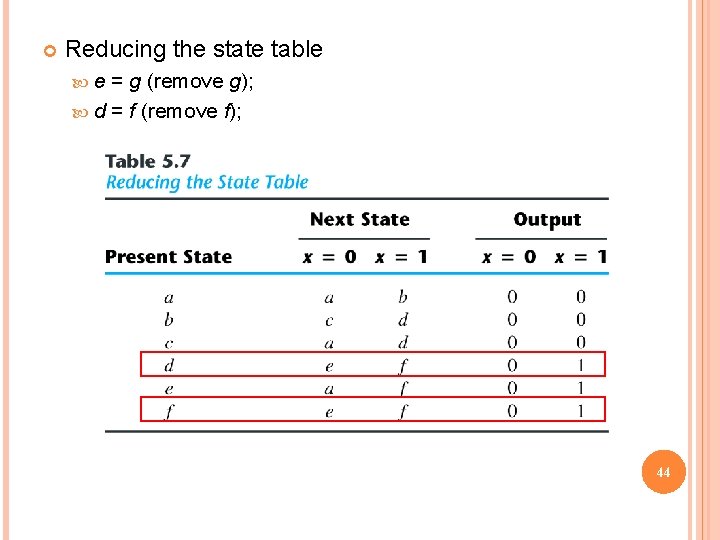

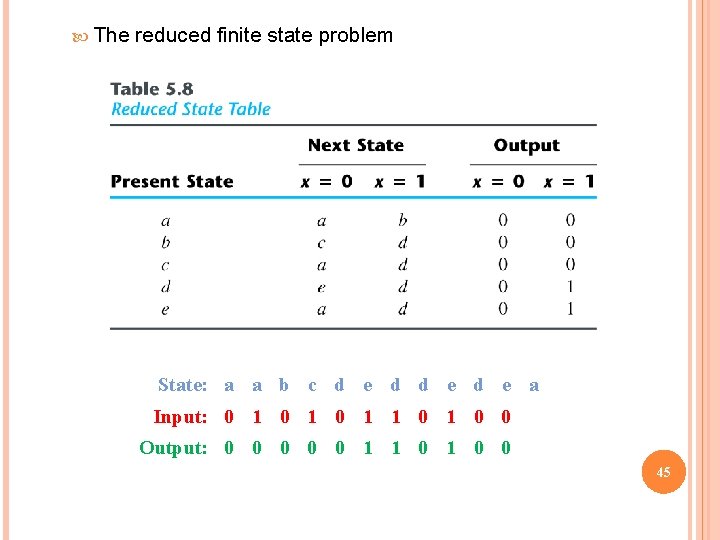

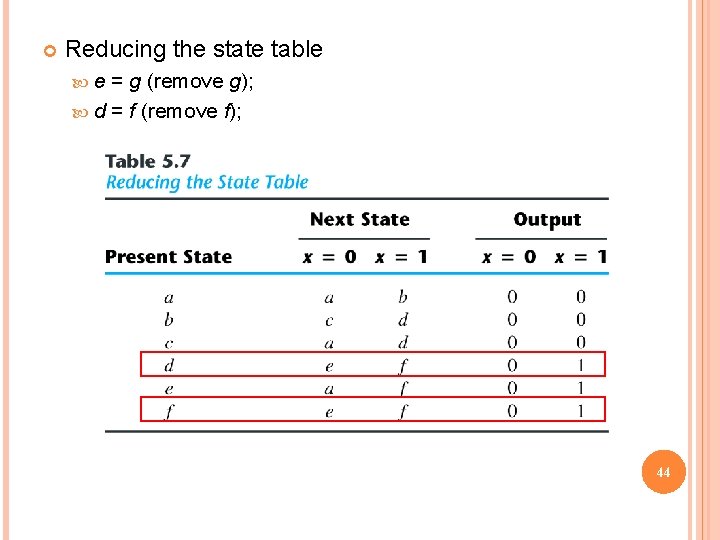

Reducing the state table e = g (remove g); d = f (remove f); 44

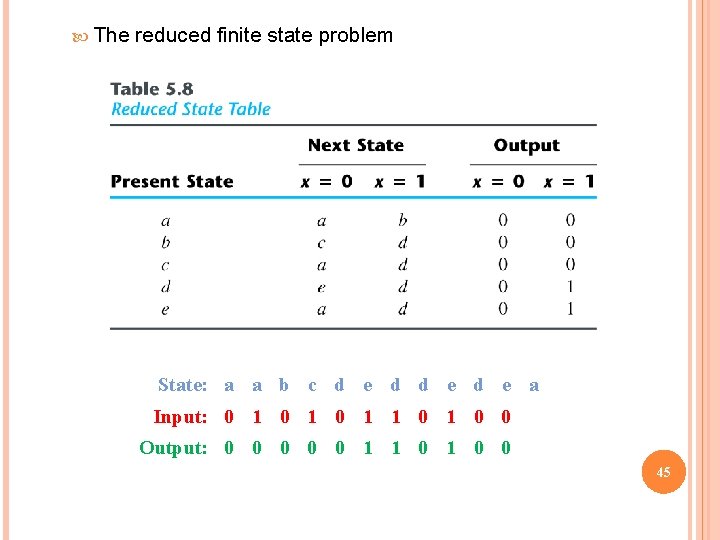

The reduced finite state problem State: a a b c d e d e a Input: 0 1 0 1 1 0 0 Output: 0 0 0 1 1 0 0 45

46

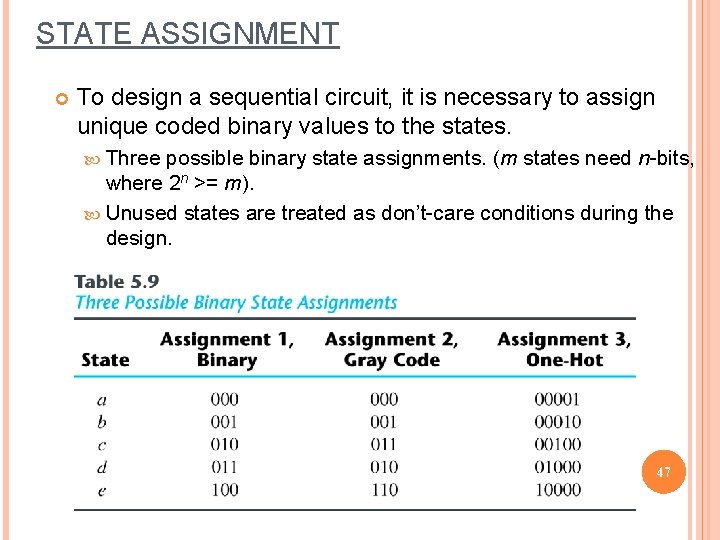

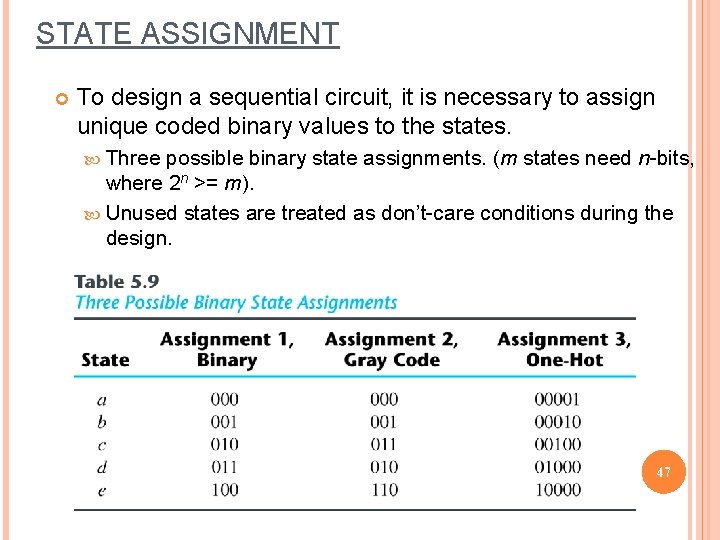

STATE ASSIGNMENT To design a sequential circuit, it is necessary to assign unique coded binary values to the states. Three possible binary state assignments. (m states need n-bits, where 2 n >= m). Unused states are treated as don’t-care conditions during the design. 47

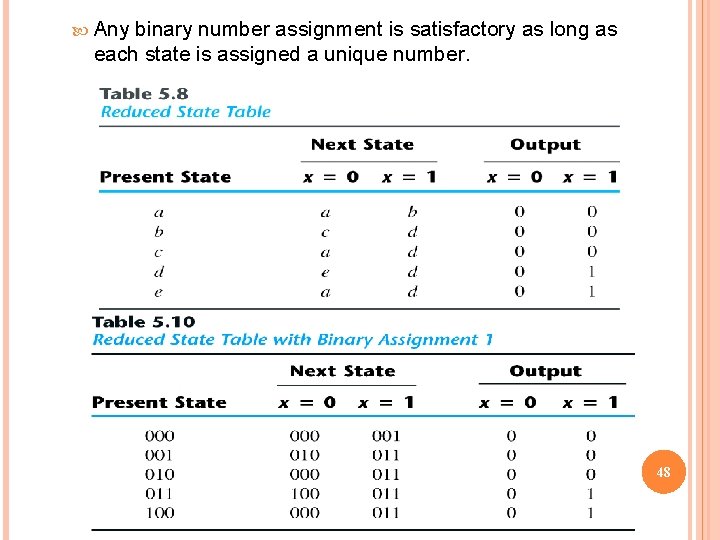

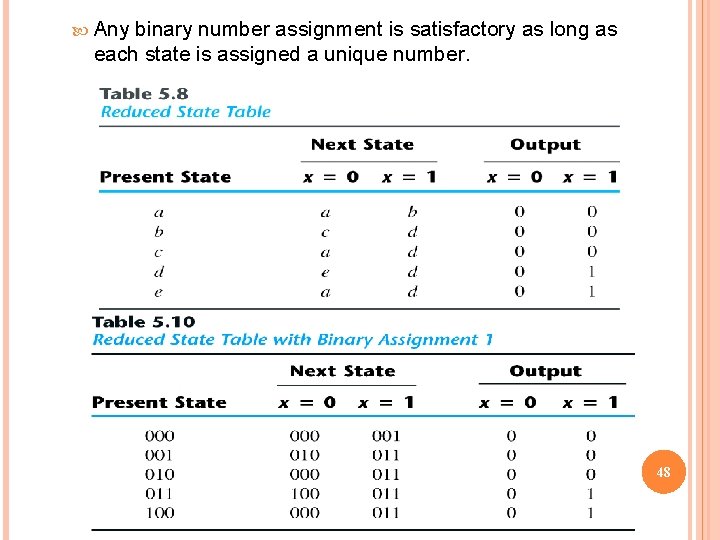

Any binary number assignment is satisfactory as long as each state is assigned a unique number. 48

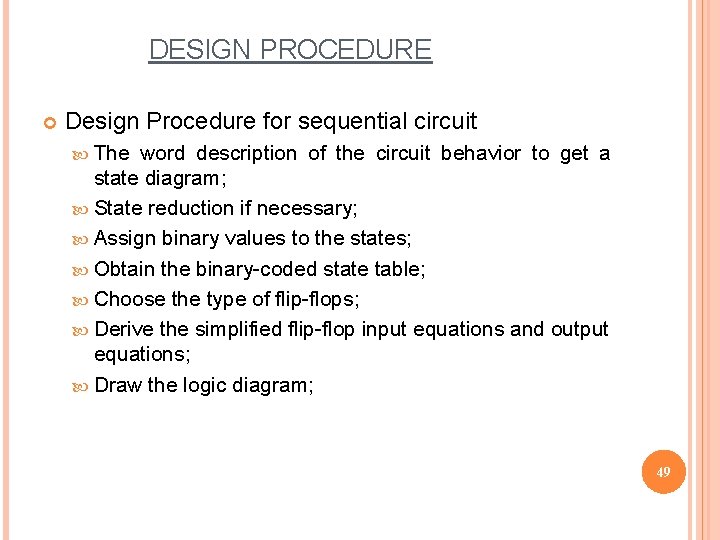

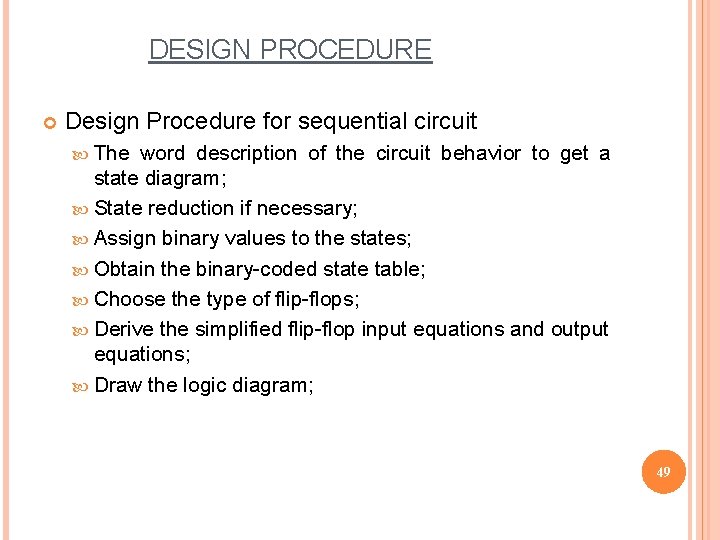

DESIGN PROCEDURE Design Procedure for sequential circuit The word description of the circuit behavior to get a state diagram; State reduction if necessary; Assign binary values to the states; Obtain the binary-coded state table; Choose the type of flip-flops; Derive the simplified flip-flop input equations and output equations; Draw the logic diagram; 49

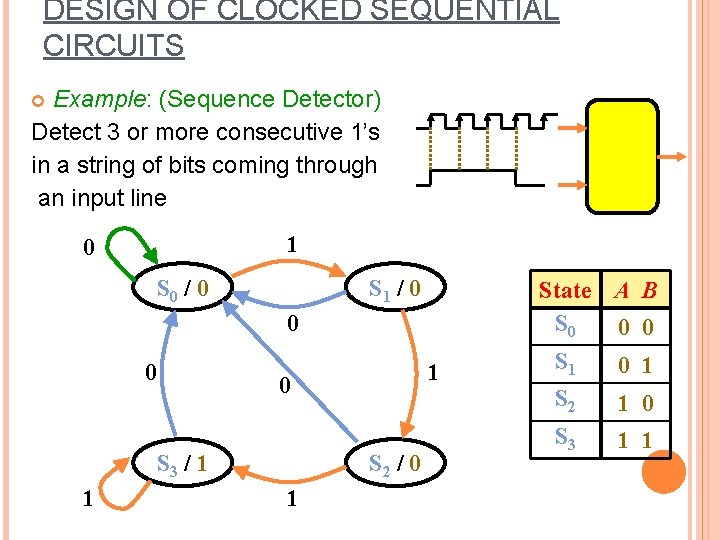

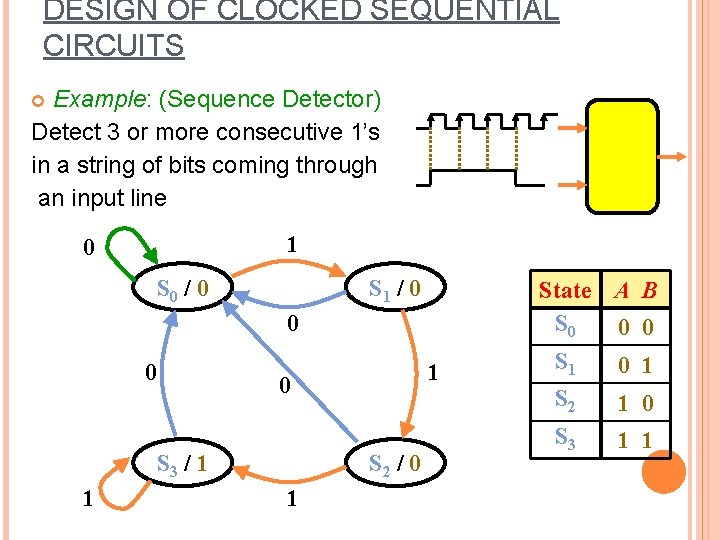

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS Example: (Sequence Detector) Detect 3 or more consecutive 1’s in a string of bits coming through an input line 1 0 S 0 / 0 S 1 / 0 0 0 S 3 / 1 1 1 0 S 2 / 0 1 State A B S 0 0 0 S 1 0 1 S 2 1 0 S 3 1 1

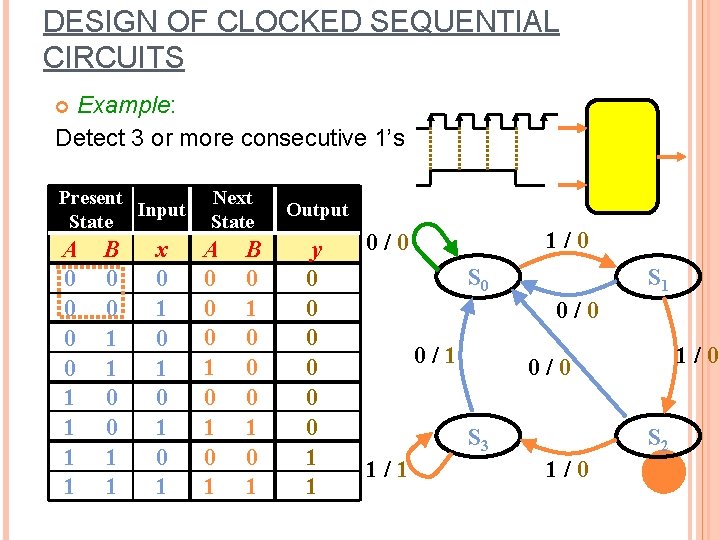

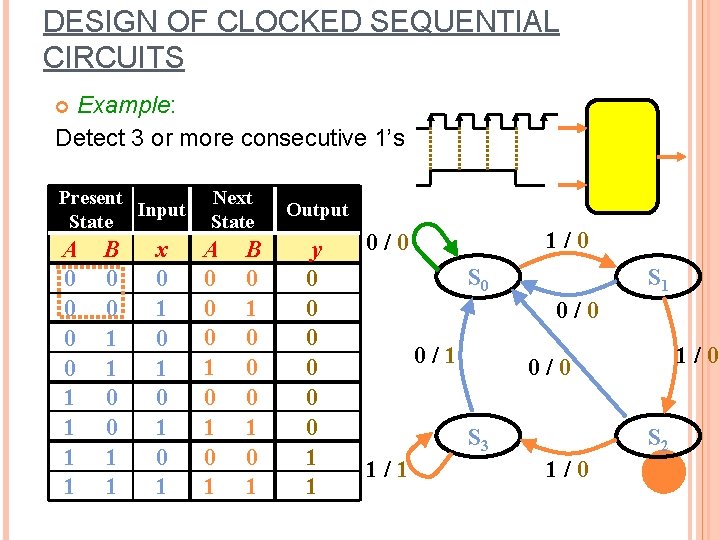

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS Example: Detect 3 or more consecutive 1’s Present Input State A 0 0 1 1 B 0 0 1 1 x 0 1 0 1 Next State A 0 0 0 1 0 1 B 0 1 0 0 0 1 Output y 0 0 0 1 1 1/0 0/0 S 1 0/0 0/1 S 3 1/1 1/0 0/0 S 2 1/0

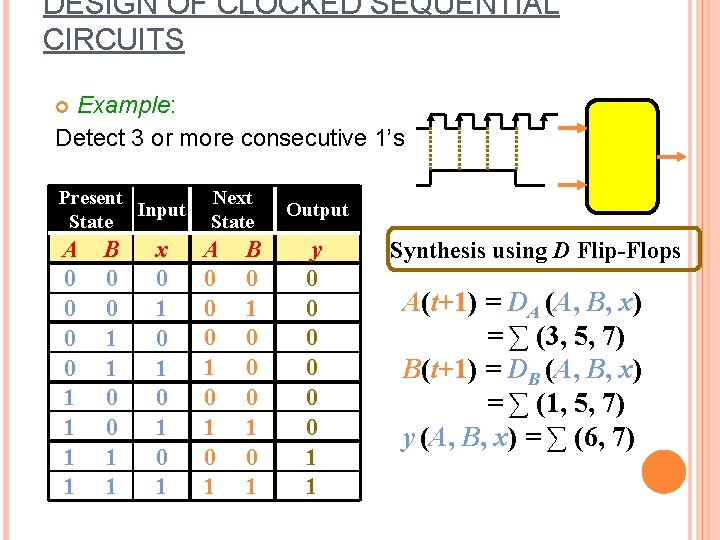

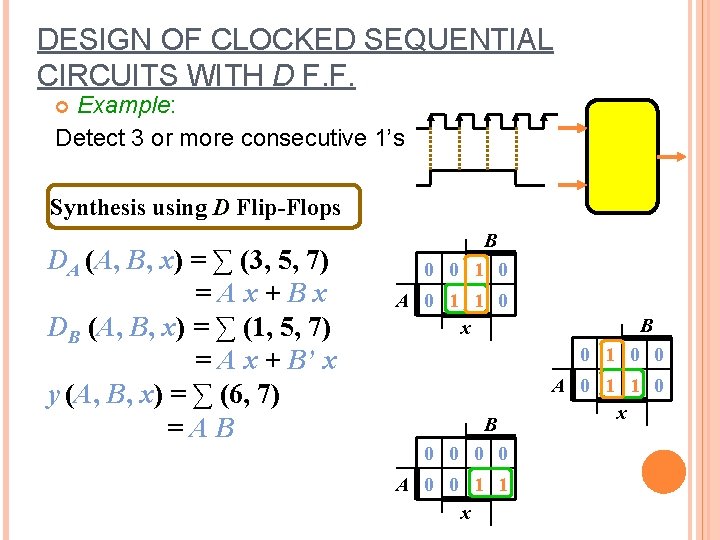

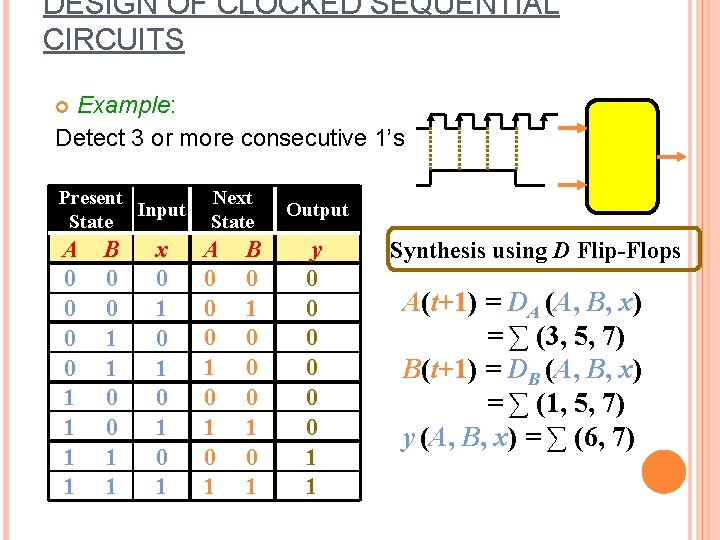

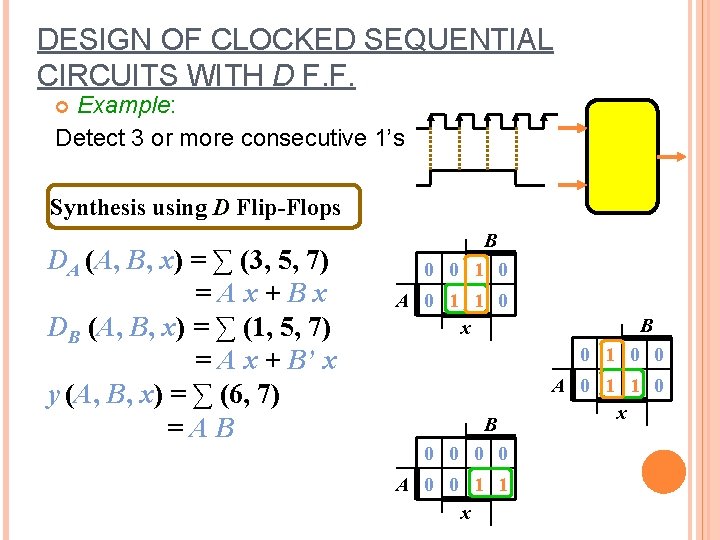

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS Example: Detect 3 or more consecutive 1’s Present Input State A 0 0 1 1 B 0 0 1 1 x 0 1 0 1 Next State A 0 0 0 1 0 1 B 0 1 0 0 0 1 Output y 0 0 0 1 1 Synthesis using D Flip-Flops A(t+1) = DA (A, B, x) = ∑ (3, 5, 7) B(t+1) = DB (A, B, x) = ∑ (1, 5, 7) y (A, B, x) = ∑ (6, 7)

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS WITH D F. F. Example: Detect 3 or more consecutive 1’s Synthesis using D Flip-Flops DA (A, B, x) = ∑ (3, 5, 7) =Ax+Bx DB (A, B, x) = ∑ (1, 5, 7) = A x + B’ x y (A, B, x) = ∑ (6, 7) =AB B 0 0 1 0 A 0 1 1 0 x B 0 1 0 0 B 0 0 A 0 0 1 1 x A 0 1 1 0 x

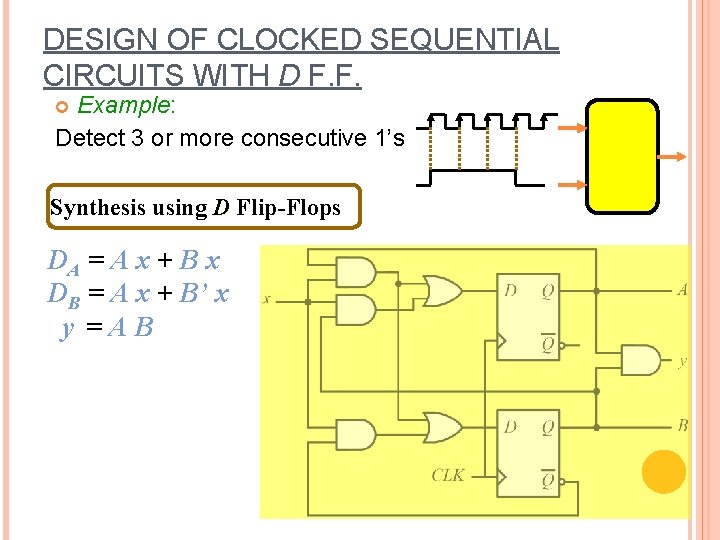

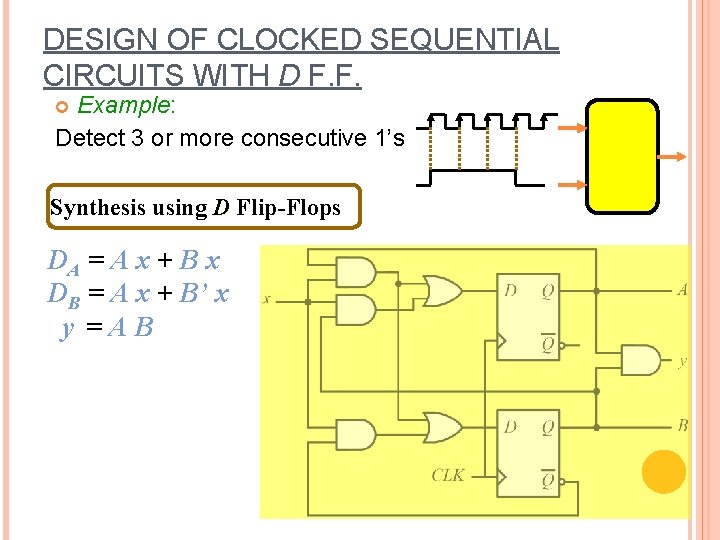

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS WITH D F. F. Example: Detect 3 or more consecutive 1’s Synthesis using D Flip-Flops DA = A x + B x DB = A x + B’ x y =AB

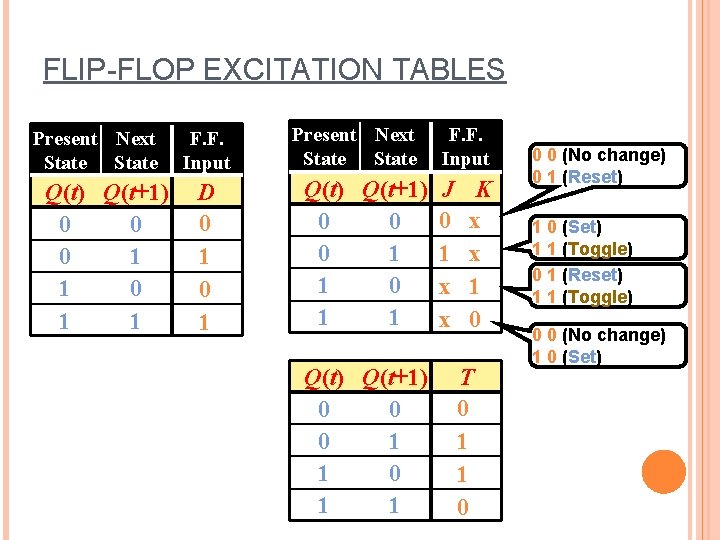

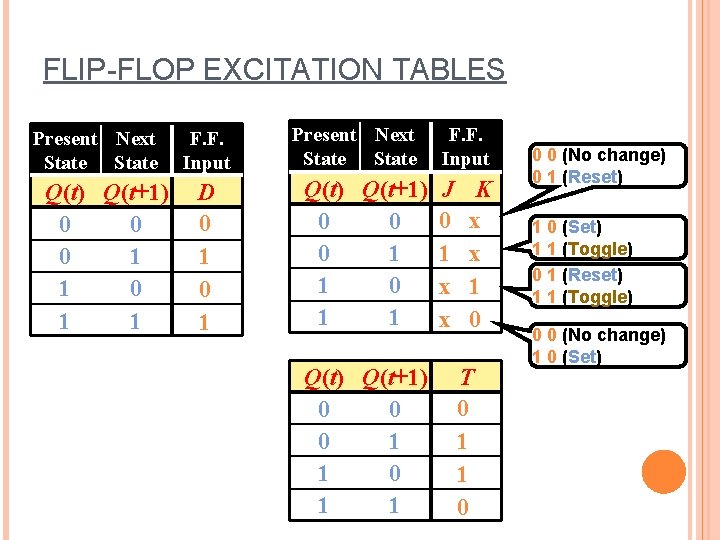

FLIP-FLOP EXCITATION TABLES Present Next State Q(t) Q(t+1) 0 0 0 1 1 F. F. Input D 0 1 Present Next State F. F. Input Q(t) Q(t+1) J K 0 x 0 0 1 x 0 1 1 0 x 1 1 1 x 0 Q(t) Q(t+1) 0 0 0 1 1 T 0 1 1 0 0 0 (No change) 0 1 (Reset) 1 0 (Set) 1 1 (Toggle) 0 1 (Reset) 1 1 (Toggle) 0 0 (No change) 1 0 (Set)

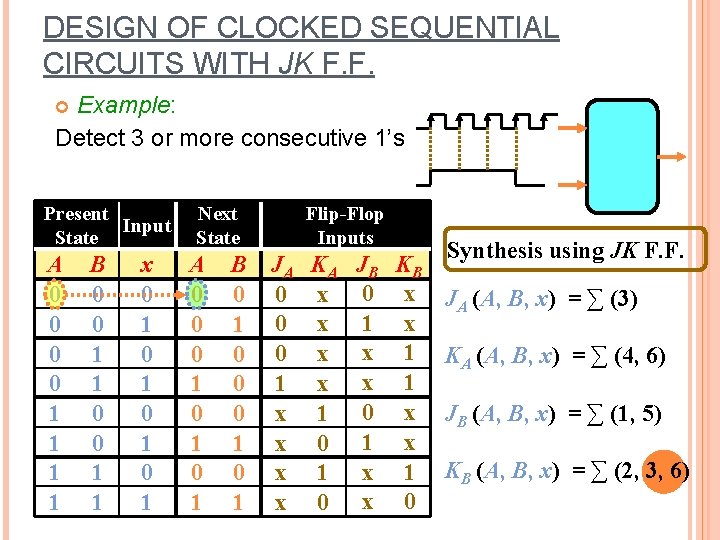

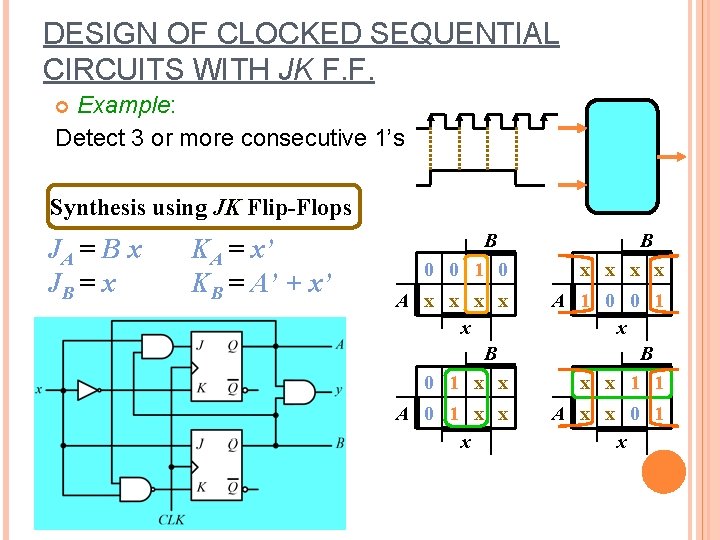

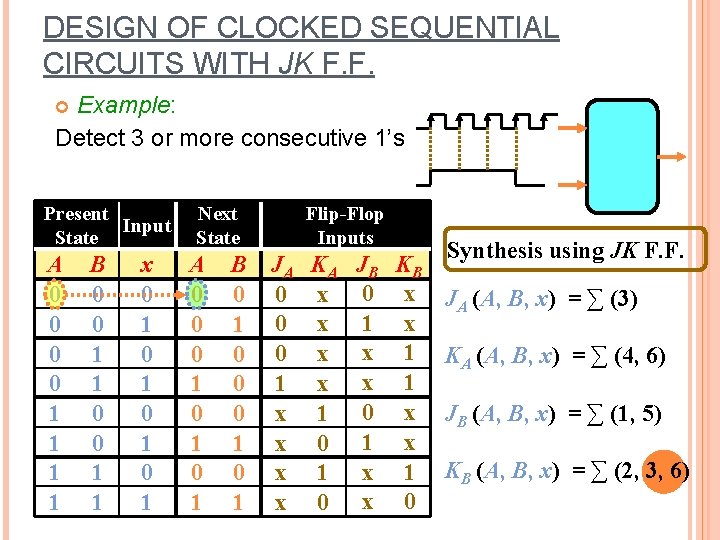

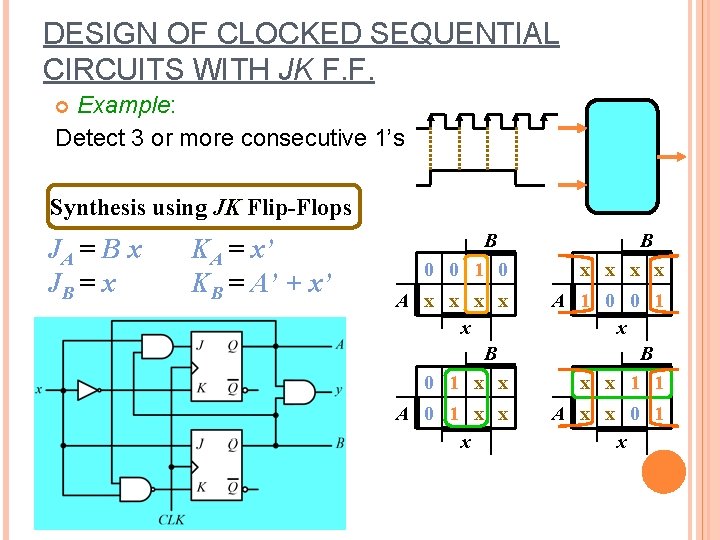

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS WITH JK F. F. Example: Detect 3 or more consecutive 1’s Present Input State A 0 0 1 1 B 0 0 1 1 x 0 1 0 1 Next State A 0 0 0 1 0 1 B JA 0 0 1 0 x 1 x Flip-Flop Inputs KA x x 1 0 JB KB 0 x 1 x 1 0 x 1 x 0 Synthesis using JK F. F. JA (A, B, x) = ∑ (3) KA (A, B, x) = ∑ (4, 6) JB (A, B, x) = ∑ (1, 5) KB (A, B, x) = ∑ (2, 3, 6)

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS WITH JK F. F. Example: Detect 3 or more consecutive 1’s Synthesis using JK Flip-Flops JA = B x JB = x KA = x’ KB = A’ + x’ B B 0 0 1 0 x x A x x x B 0 1 x x A 1 0 0 1 x B x x 1 1 A 0 1 x x x A x x 0 1 x

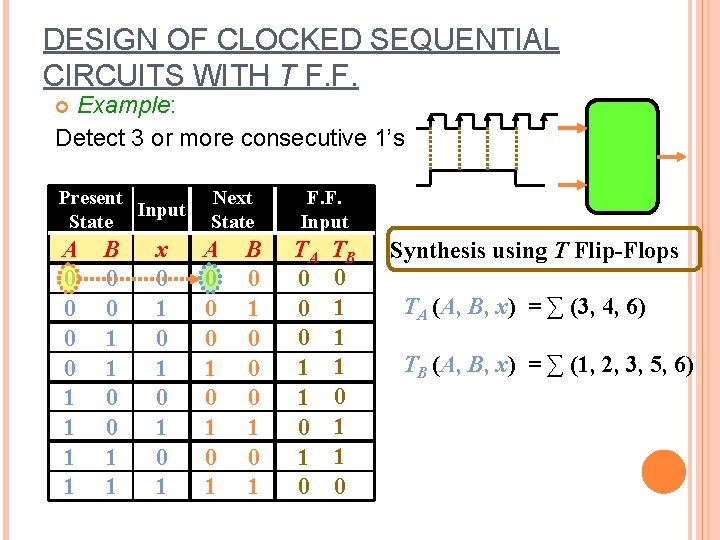

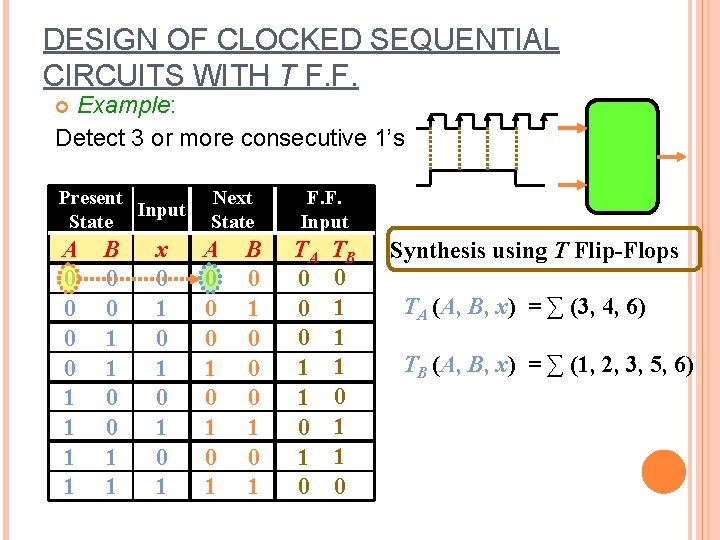

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS WITH T F. F. Example: Detect 3 or more consecutive 1’s Present Input State A 0 0 1 1 B 0 0 1 1 x 0 1 0 1 Next State A 0 0 0 1 0 1 B 0 1 0 0 0 1 F. F. Input TA 0 0 0 1 1 0 TB 0 1 1 1 0 Synthesis using T Flip-Flops TA (A, B, x) = ∑ (3, 4, 6) TB (A, B, x) = ∑ (1, 2, 3, 5, 6)

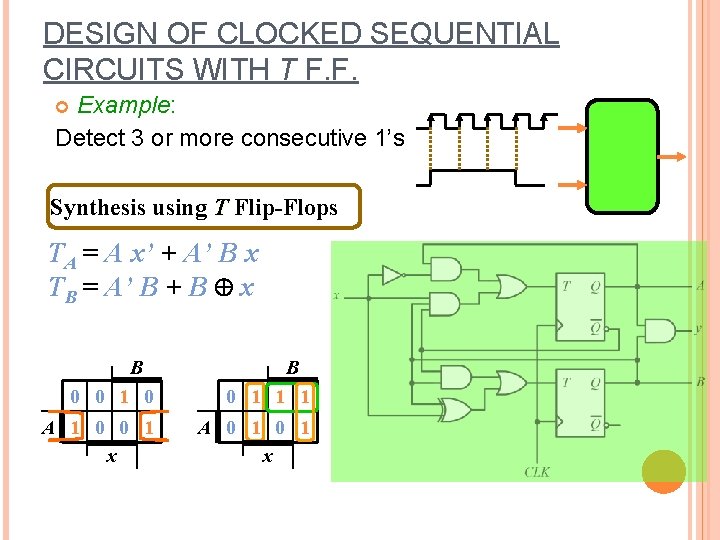

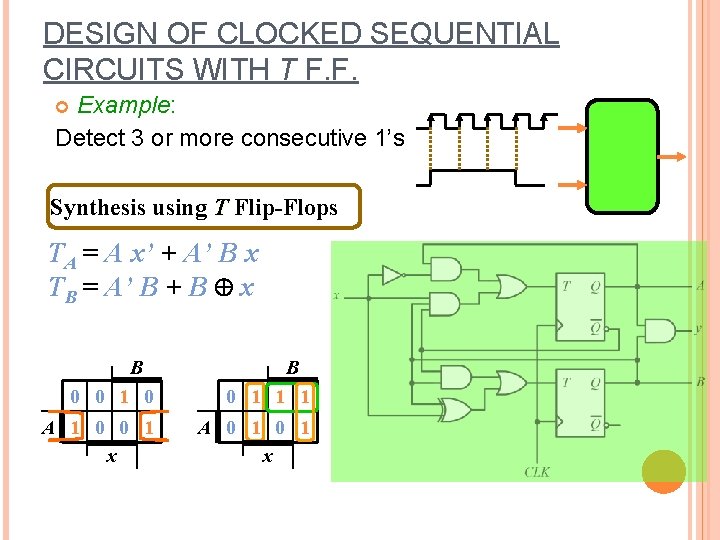

DESIGN OF CLOCKED SEQUENTIAL CIRCUITS WITH T F. F. Example: Detect 3 or more consecutive 1’s Synthesis using T Flip-Flops TA = A x’ + A’ B x TB = A’ B + B x B B 0 0 1 1 1 A 1 0 0 1 x A 0 1 x

The problems are: 5. 12, 5. 13, 5. 14, 5. 15, 5. 16, 5. 18, 60