CHAPTER FIVE SYNCHRONOUS SEQUENTIAL LOGIC 1 FLIPFLOP CHARACTERISTIC

- Slides: 26

CHAPTER FIVE SYNCHRONOUS SEQUENTIAL LOGIC 1

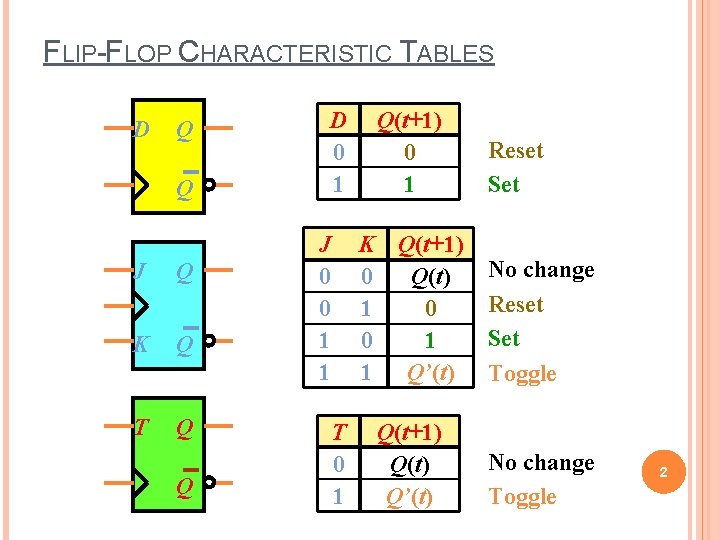

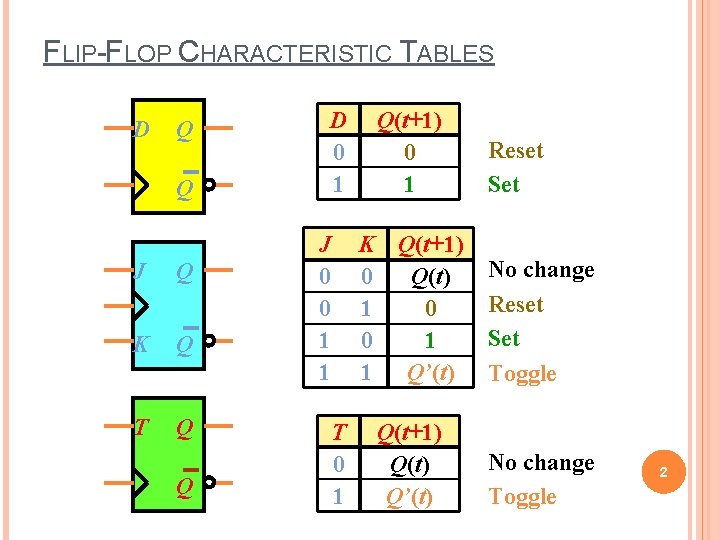

FLIP-FLOP CHARACTERISTIC TABLES D Q Q J Q K Q T Q Q D 0 1 J 0 0 1 1 T 0 1 Q(t+1) 0 1 Reset Set K Q(t+1) 0 Q(t) 1 0 0 1 1 Q’(t) No change Reset Set Toggle Q(t+1) Q(t) Q’(t) No change Toggle 2

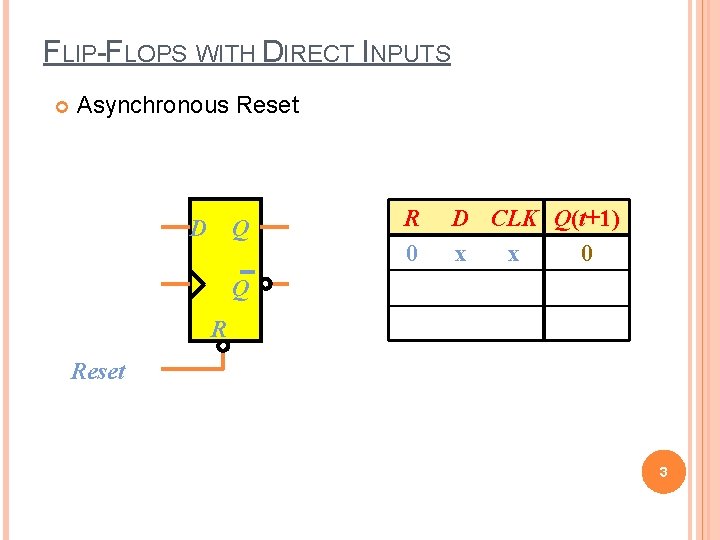

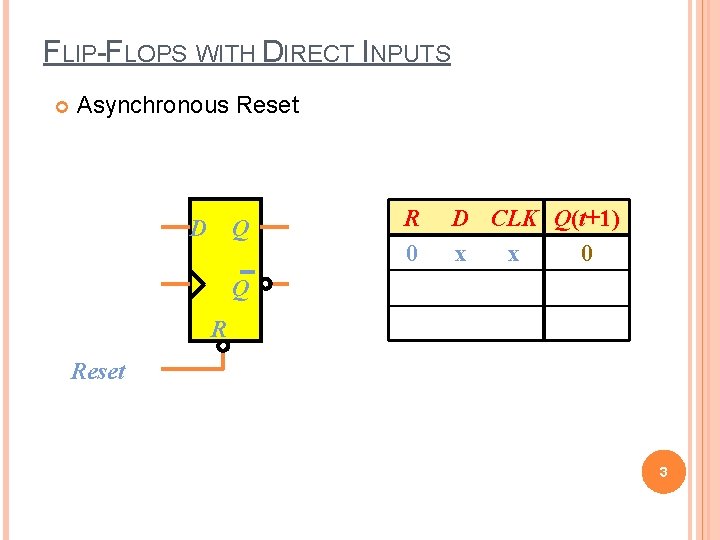

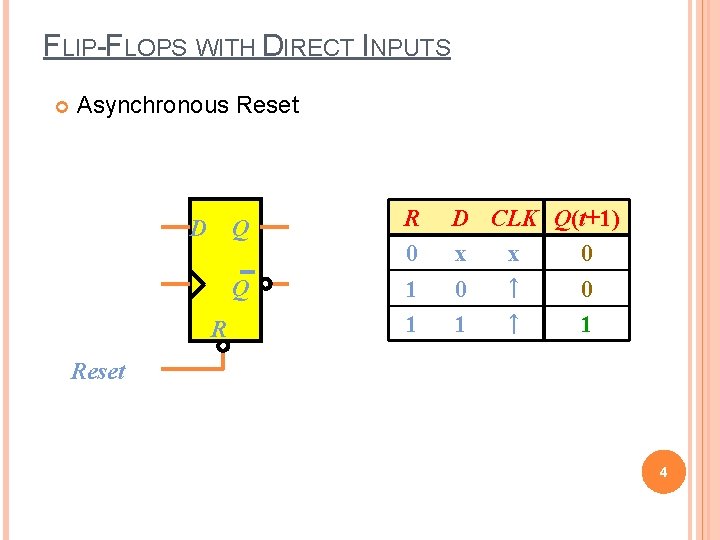

FLIP-FLOPS WITH DIRECT INPUTS Asynchronous Reset D Q R 0 D CLK Q(t+1) x x 0 Q R Reset 3

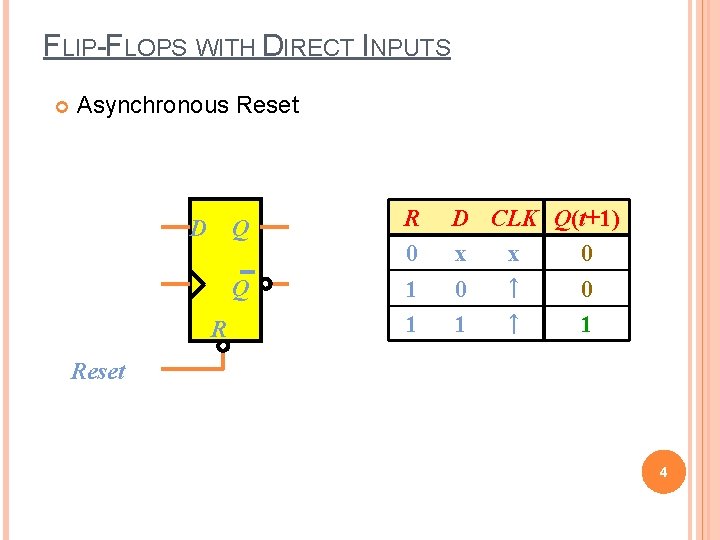

FLIP-FLOPS WITH DIRECT INPUTS Asynchronous Reset D Q Q R R 0 1 1 D CLK Q(t+1) x x 0 ↑ 0 0 ↑ 1 1 Reset 4

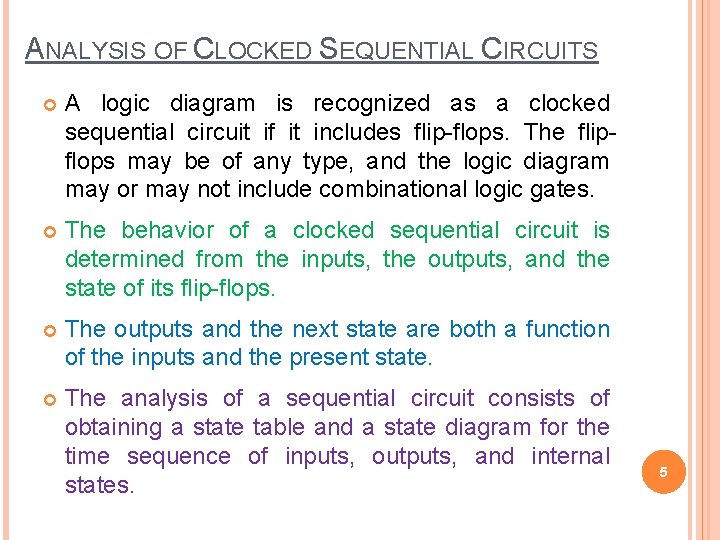

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS A logic diagram is recognized as a clocked sequential circuit if it includes flip-flops. The flipflops may be of any type, and the logic diagram may or may not include combinational logic gates. The behavior of a clocked sequential circuit is determined from the inputs, the outputs, and the state of its flip-flops. The outputs and the next state are both a function of the inputs and the present state. The analysis of a sequential circuit consists of obtaining a state table and a state diagram for the time sequence of inputs, outputs, and internal states. 5

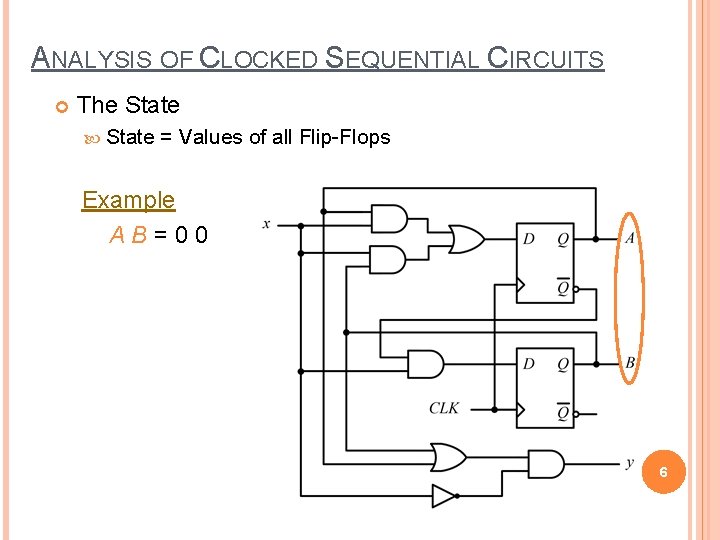

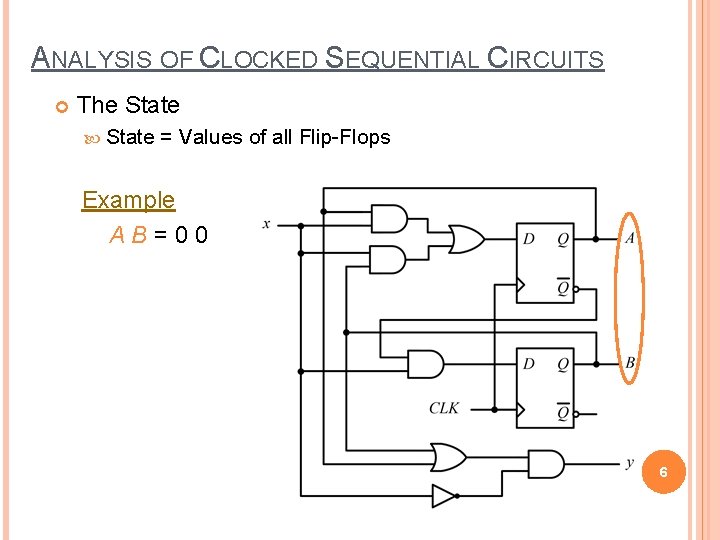

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS The State = Values of all Flip-Flops Example AB=00 6

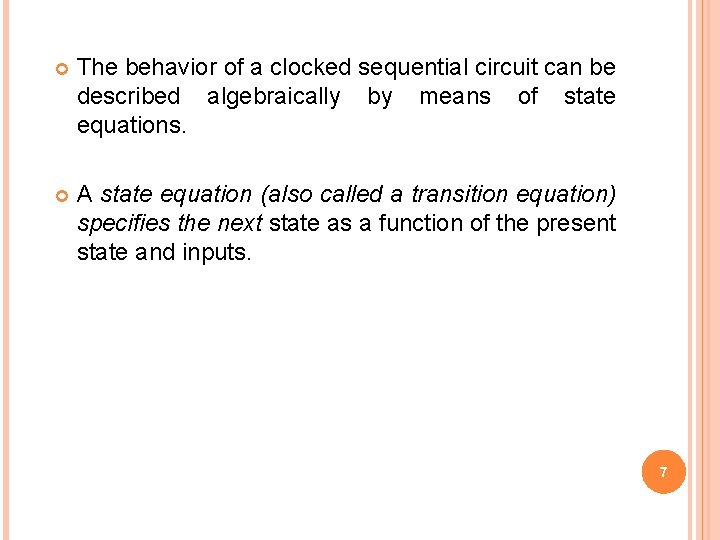

The behavior of a clocked sequential circuit can be described algebraically by means of state equations. A state equation (also called a transition equation) specifies the next state as a function of the present state and inputs. 7

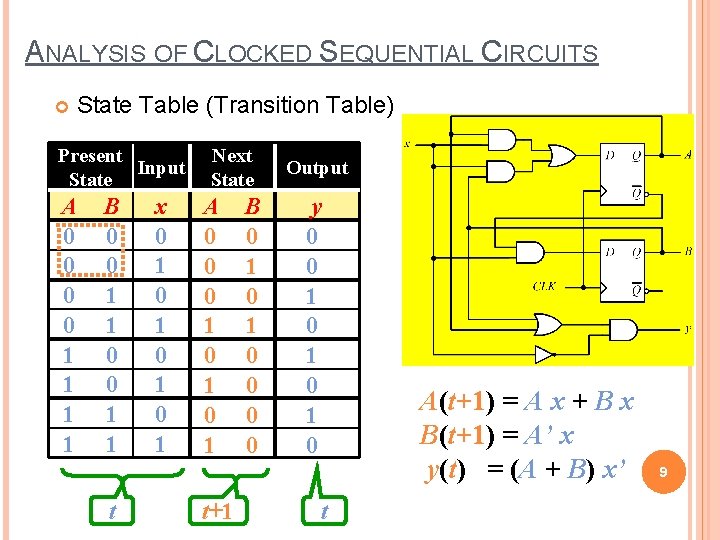

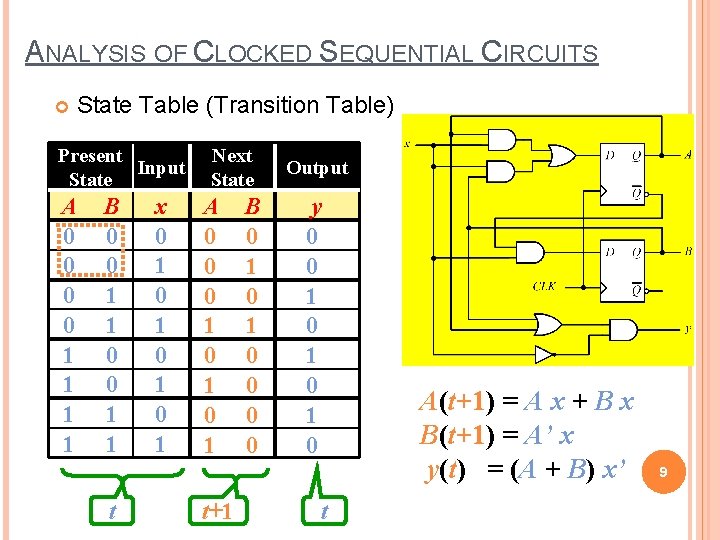

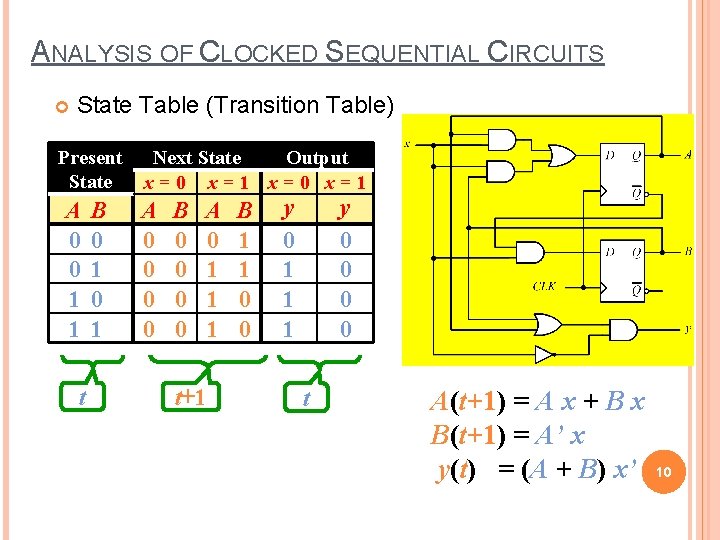

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS Flip-Flop input equations DA = A(t) x(t)+B(t) x(t) =Ax+Bx DB = A’(t) x(t) = A’ x State equations A(t+1) = DA B(t+1) = DB Output equation y(t) = [A(t)+ B(t)] x’(t) = (A + B) x’ 8

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS State Table (Transition Table) Present Input State A 0 0 1 1 B 0 0 1 1 t x 0 1 0 1 Next State A 0 0 0 1 0 1 t+1 B 0 1 0 0 Output y 0 0 1 0 1 0 t A(t+1) = A x + B x B(t+1) = A’ x y(t) = (A + B) x’ 9

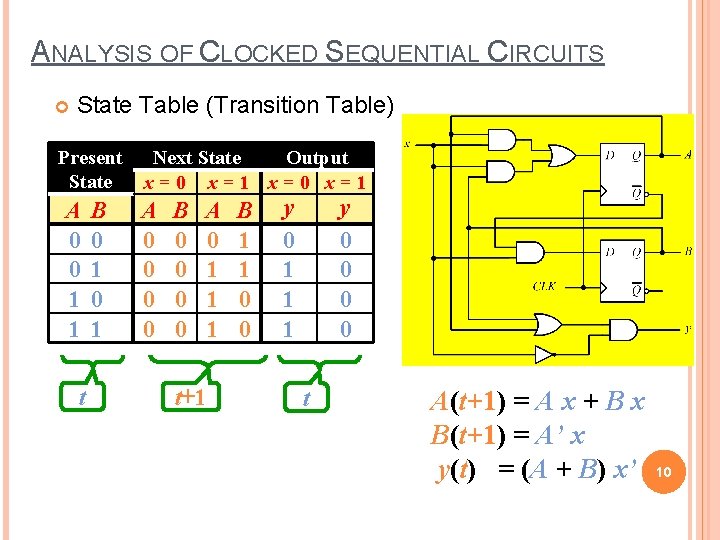

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS State Table (Transition Table) Present State A 0 0 1 1 t B 0 1 Next State Output x=0 x=1 A 0 0 B 0 0 A 0 1 1 1 t+1 B 1 1 0 0 y 0 1 1 1 y 0 0 t A(t+1) = A x + B x B(t+1) = A’ x y(t) = (A + B) x’ 10

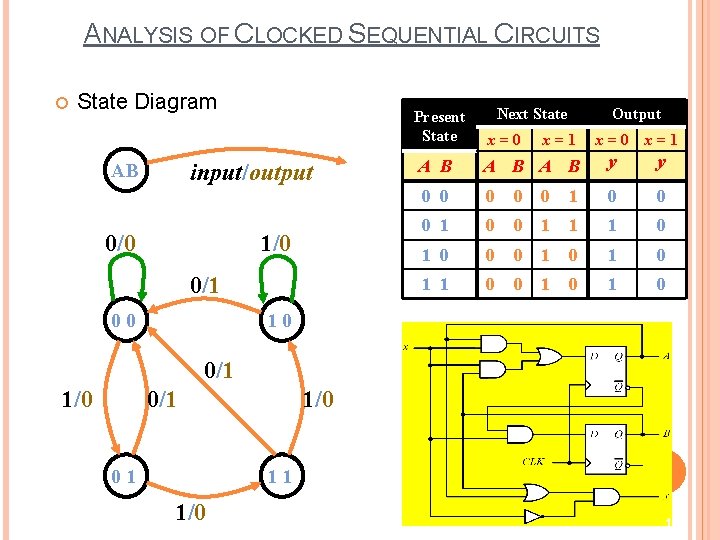

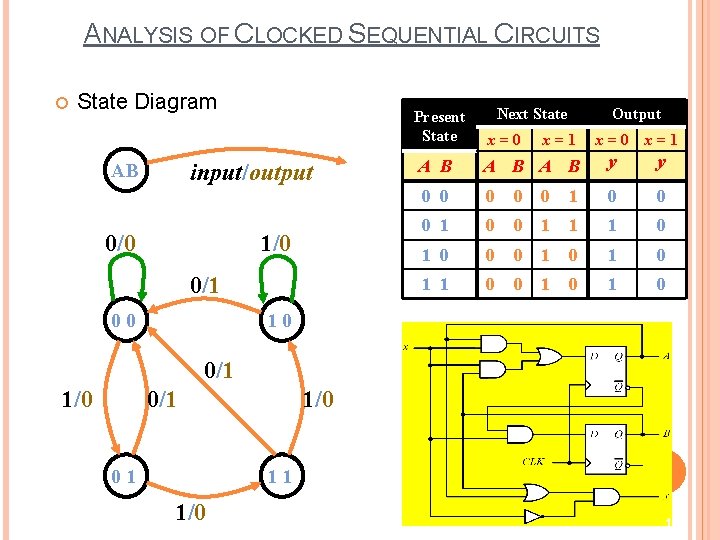

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS State Diagram Present State input/output AB 0/0 1/0 0/1 00 Next State x=0 Output x=1 x=0 x=1 A B A B y y 0 0 0 1 1 1 0 0 0 1 0 1 1 0 0 1 0 10 0/1 1/0 0/1 01 1/0 11

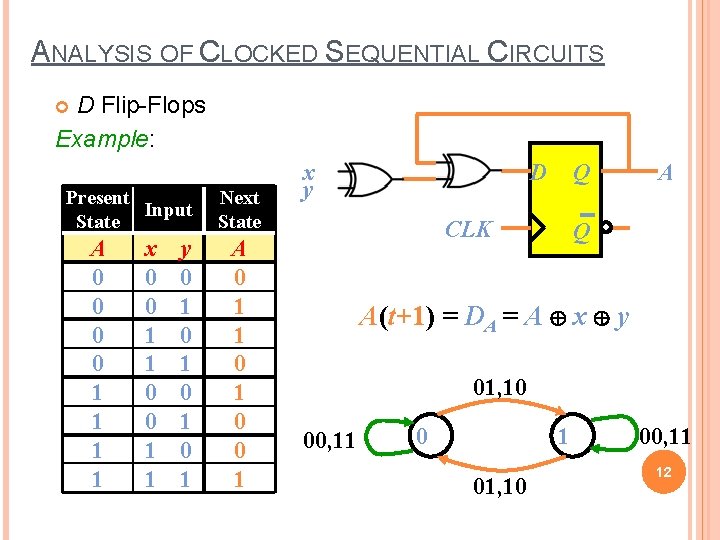

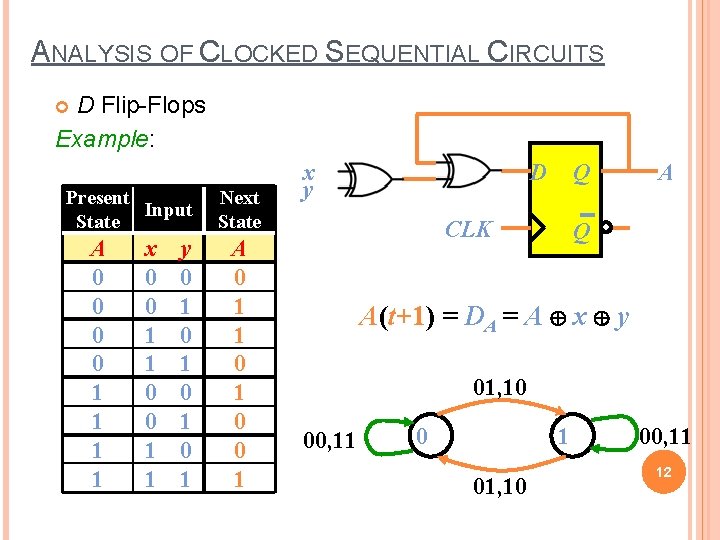

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS D Flip-Flops Example: Present Input State A 0 0 1 1 x 0 0 1 1 y 0 1 0 1 Next State A 0 1 1 0 0 1 x y D Q CLK A Q A(t+1) = DA = A x y 01, 10 00, 11 0 1 01, 10 00, 11 12

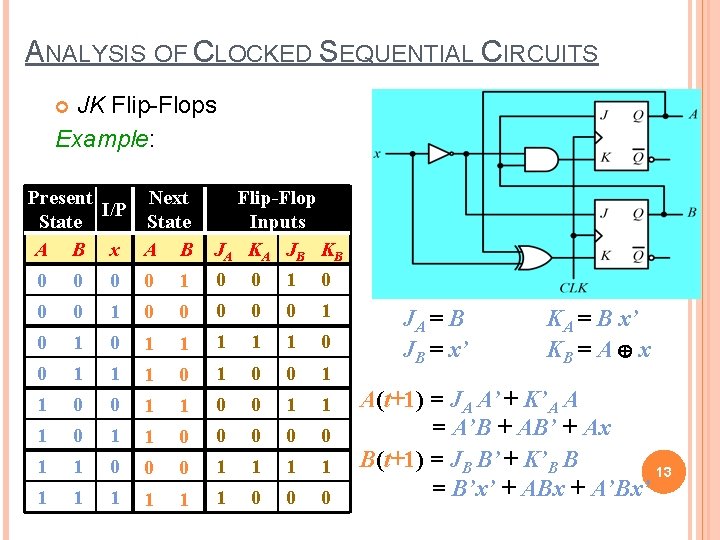

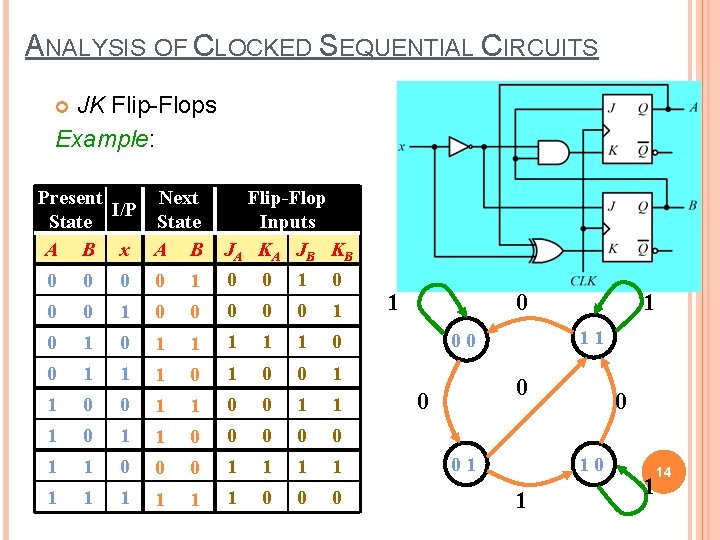

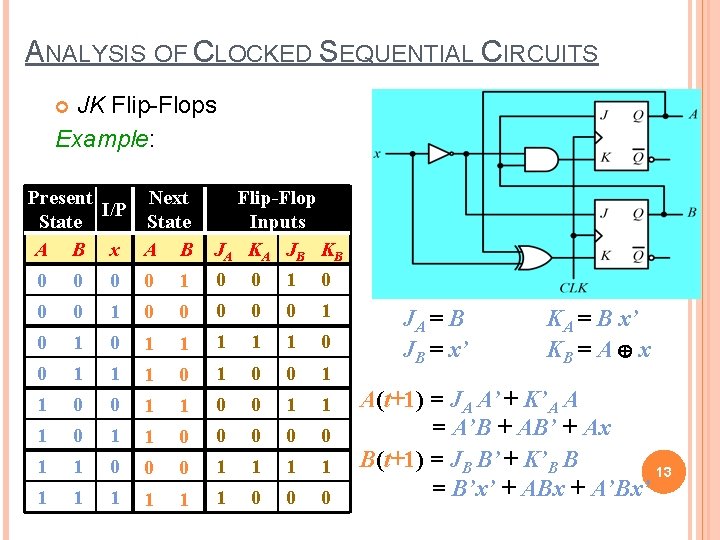

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS JK Flip-Flops Example: Present Next I/P State A B x A B Flip-Flop Inputs JA KA JB KB 0 0 1 0 0 0 1 0 1 1 1 0 0 1 1 0 0 1 1 1 0 0 0 1 1 1 1 1 0 0 0 JA = B JB = x’ KA = B x’ KB = A x A(t+1) = JA A’ + K’A A = A’B + AB’ + Ax B(t+1) = JB B’ + K’B B 13 = B’x’ + ABx + A’Bx’

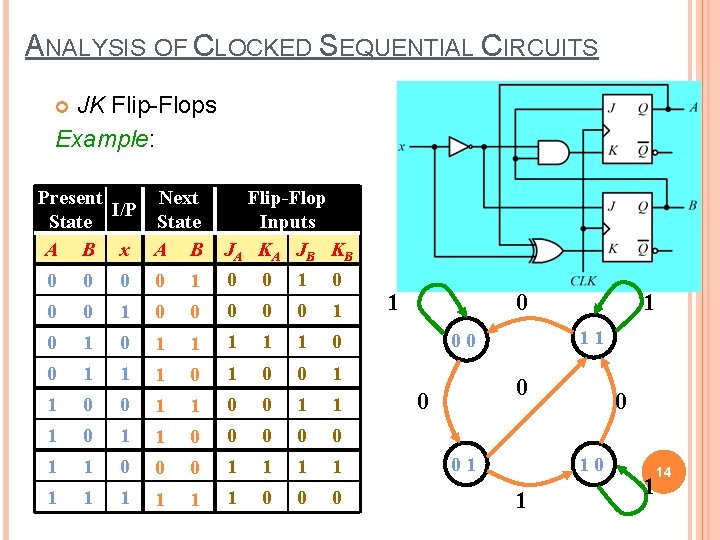

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS JK Flip-Flops Example: Present Next I/P State A B x A B Flip-Flop Inputs JA KA JB KB 0 0 1 0 0 0 1 0 1 1 1 0 0 1 1 0 0 1 1 1 0 0 0 1 1 1 1 1 0 0 0 1 11 00 0 0 01 0 10 1 1 14

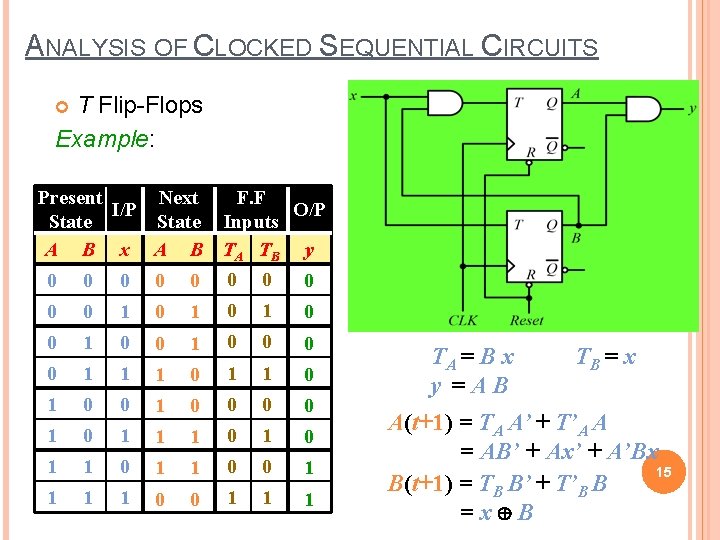

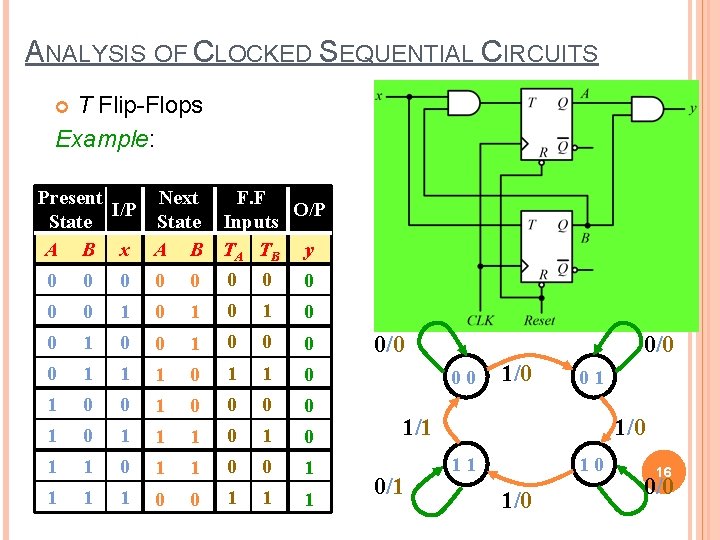

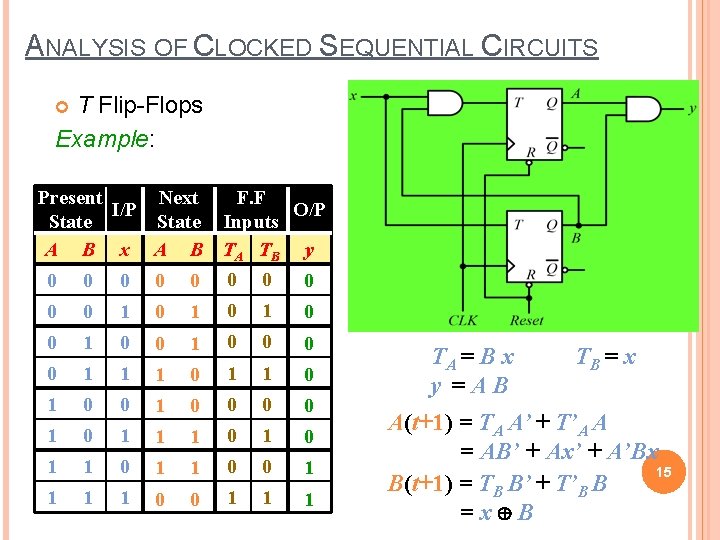

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS T Flip-Flops Example: Present Next F. F I/P O/P State Inputs A B x A B TA TB y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 0 1 1 1 0 0 1 1 0 0 1 1 1 TA = B x y =AB TB = x A(t+1) = TA A’ + T’A A = AB’ + Ax’ + A’Bx 15 B(t+1) = TB B’ + T’B B =x B

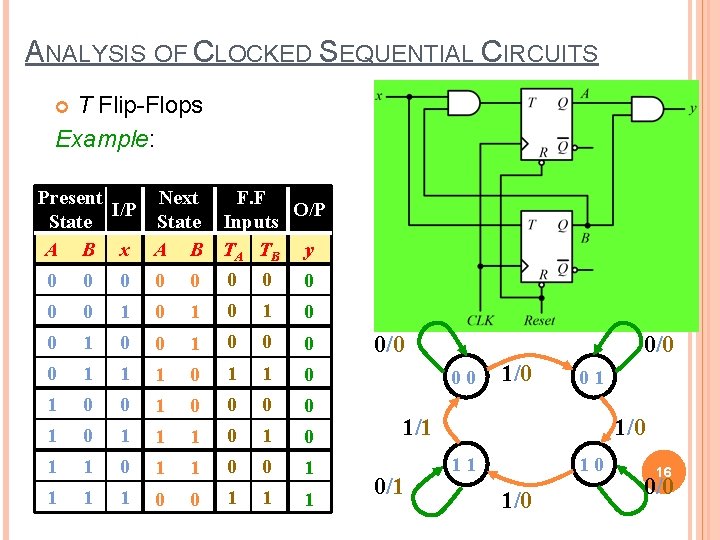

ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS T Flip-Flops Example: Present Next F. F I/P O/P State Inputs A B x A B TA TB y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 0 1 1 1 0 0 1 1 0 0 1 1 1 0/0 00 1/0 01 1/1 0/1 1/0 11 10 1/0 16 0/0

THE PROBLEMS: 5. 3, 5. 4, 5. 6 5. 7, 5. 9, 5. 10, 5. 11 17

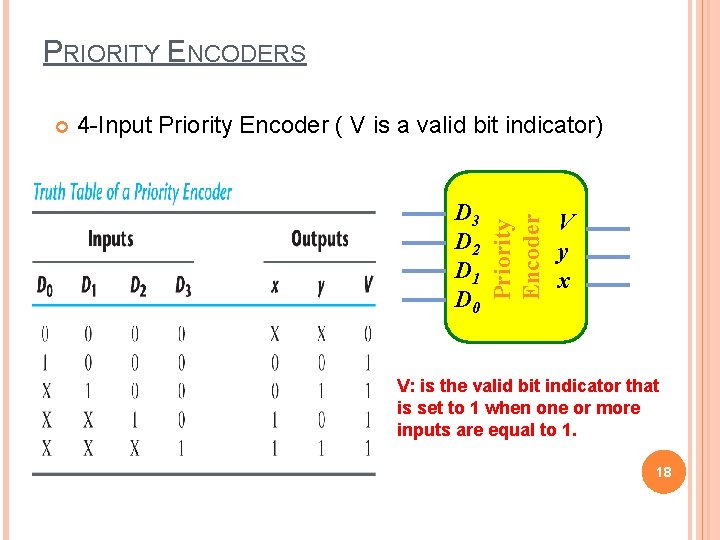

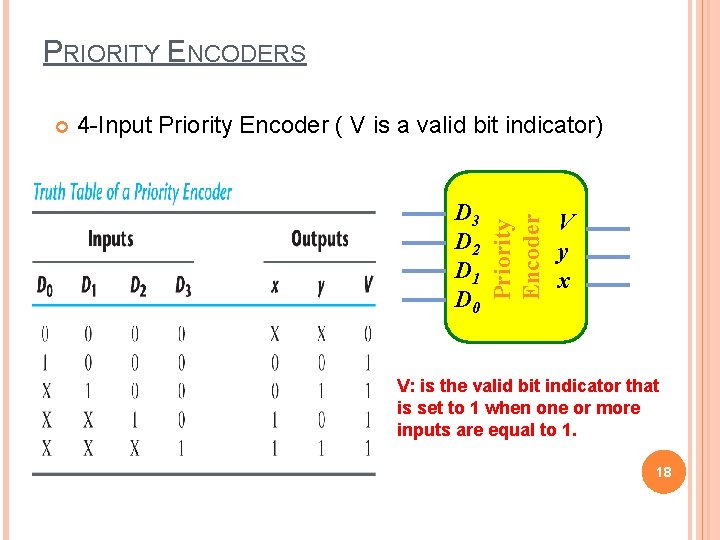

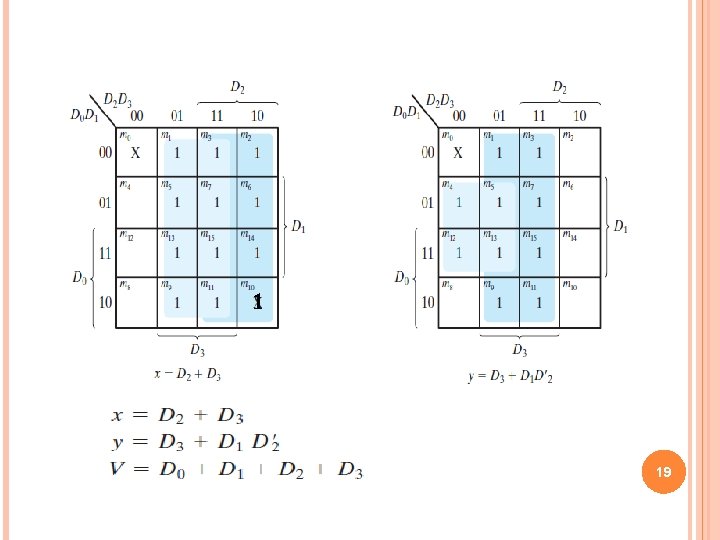

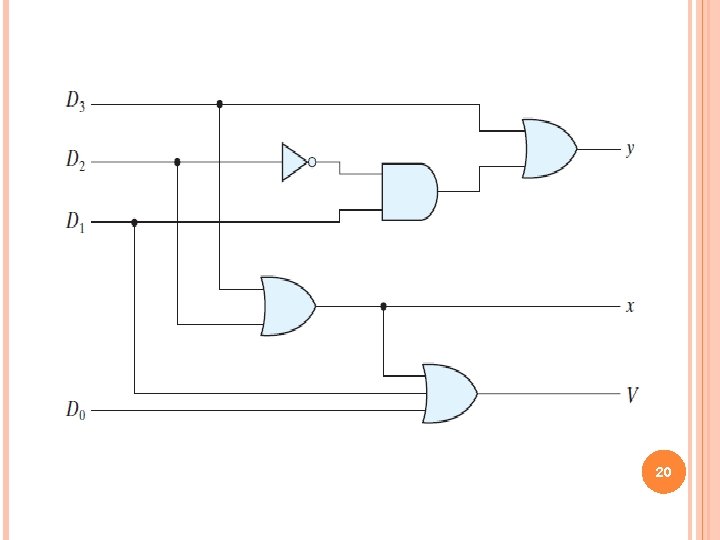

PRIORITY ENCODERS 4 -Input Priority Encoder ( V is a valid bit indicator) D 3 D 2 D 1 D 0 Priority Encoder V y x V: is the valid bit indicator that is set to 1 when one or more inputs are equal to 1. 18

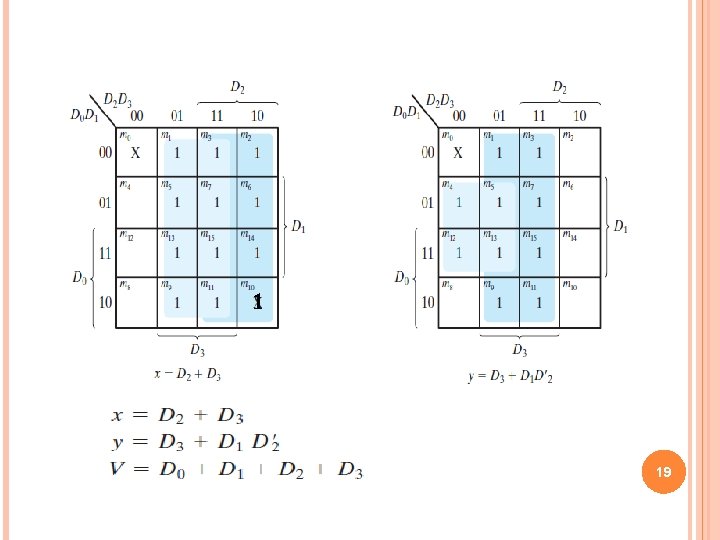

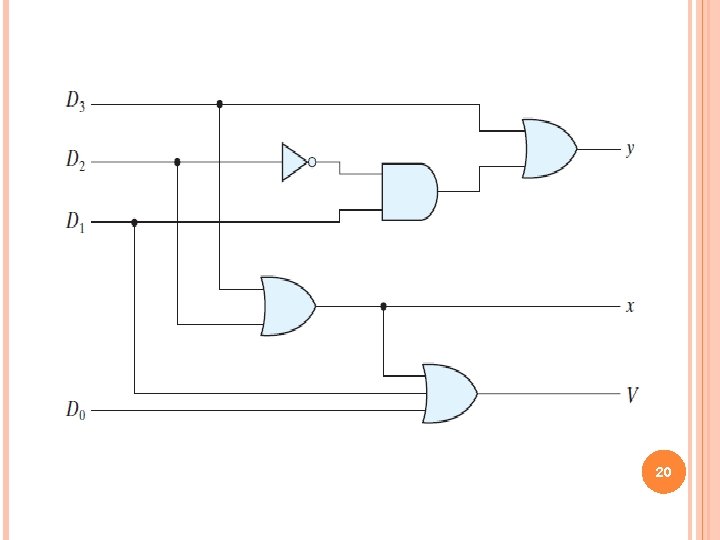

1 19

20

CHAPTER SIX REGISTERS AND COUNTERS 21

A clocked sequential circuit consists of a group of flip-flops and combinational gates connected to form a feedback path. A circuit with flip-flops is considered a sequential circuit even in the absence of combinational gates. Circuits that include flip-flops are classified by the function they perform. Two such circuits are registers and counters. 22

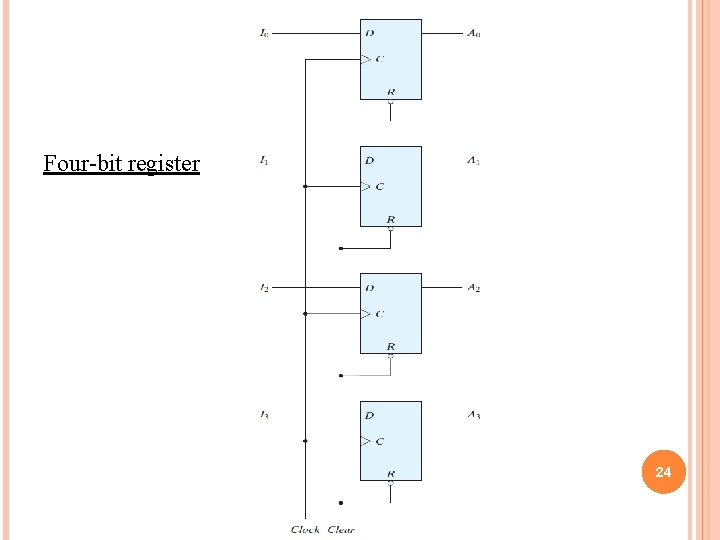

A register is a group of flip-flops, each one of which is capable of storing one bit of information. An n-bit register consists of a group of n flip-flops. A register consists of a group of flip-flops together with gates that affect their operation. (they determine how the information is transferred into register). A counter is a special type of register that goes through a predetermined sequence of binary states. 23

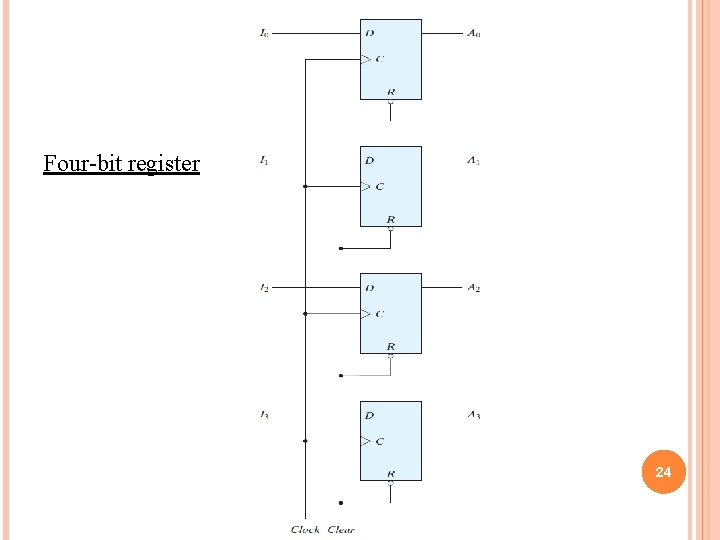

Four-bit register 24

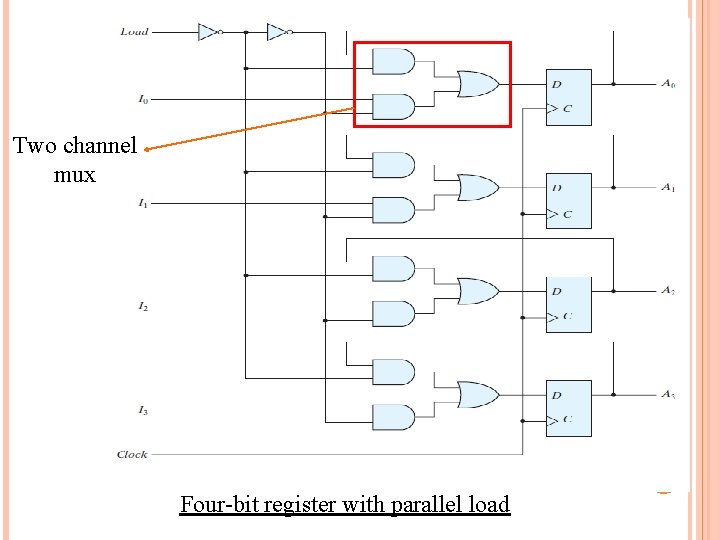

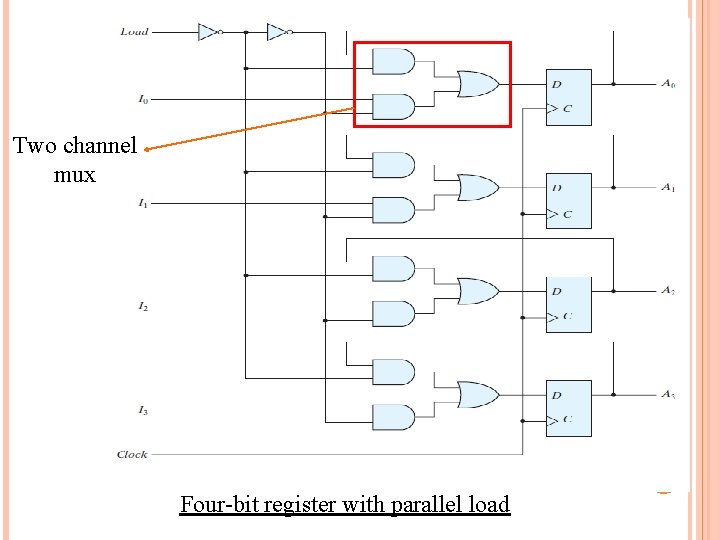

CLEAR or RESET. When CLEAR is 0 the flip flop is resetting independent of clock and D values. It is useful because in digital systems when the power is turned on the state of flip-flops is unknown. Direct input CLEAR can bring all flip-flops to the known starting state prior to the clock operation. REGISTER WITH PARALLEL LOAD The transfer of new information into a register is referred to as loading or updating the register. If all the bits of the register are loaded simultaneously with a common clock pulse, we say that the loading is done in parallel. 25

Two channel mux 26 Four-bit register with parallel load