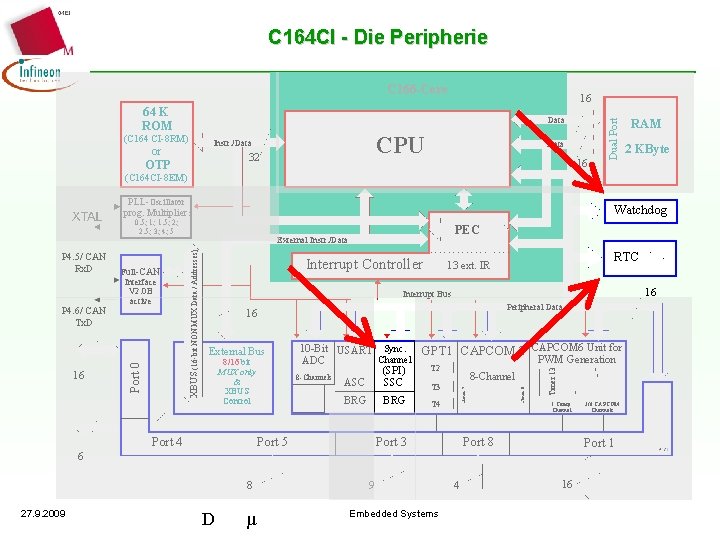

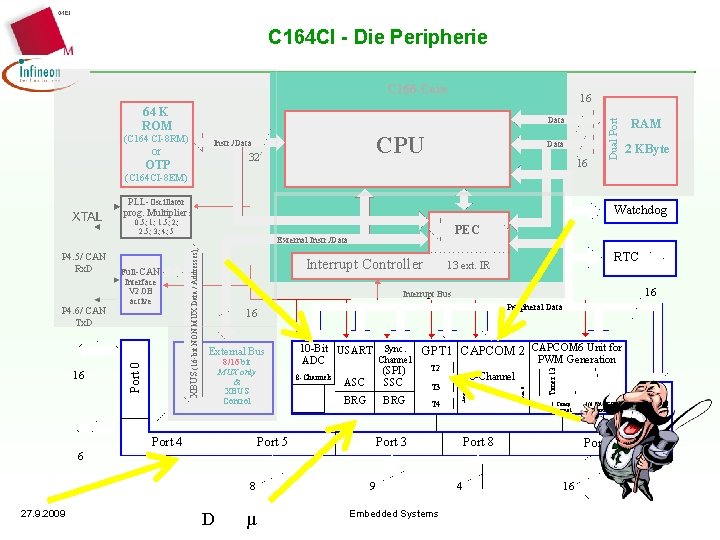

C 164 CI Die Peripherie C 166 Core

- Slides: 38

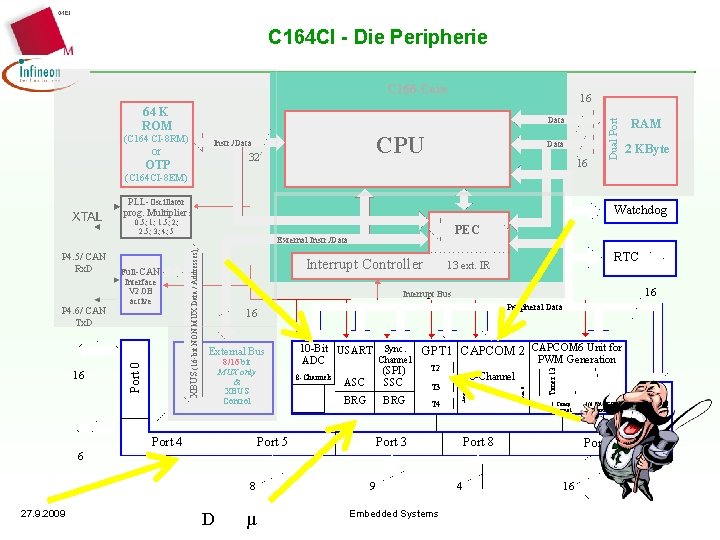

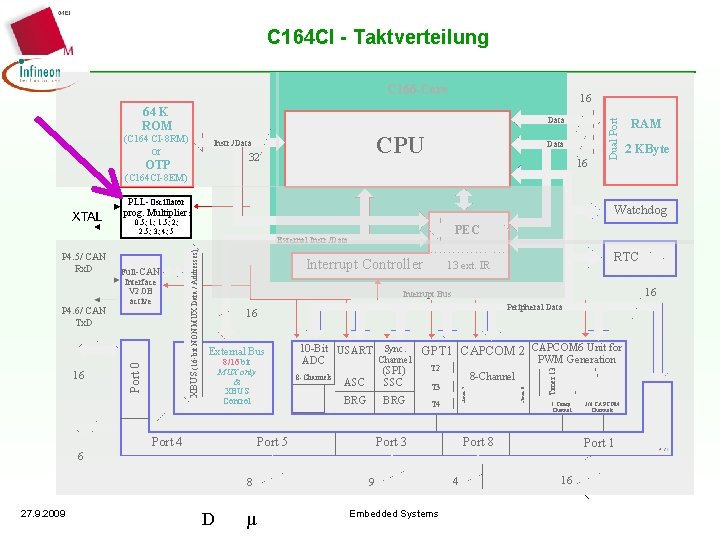

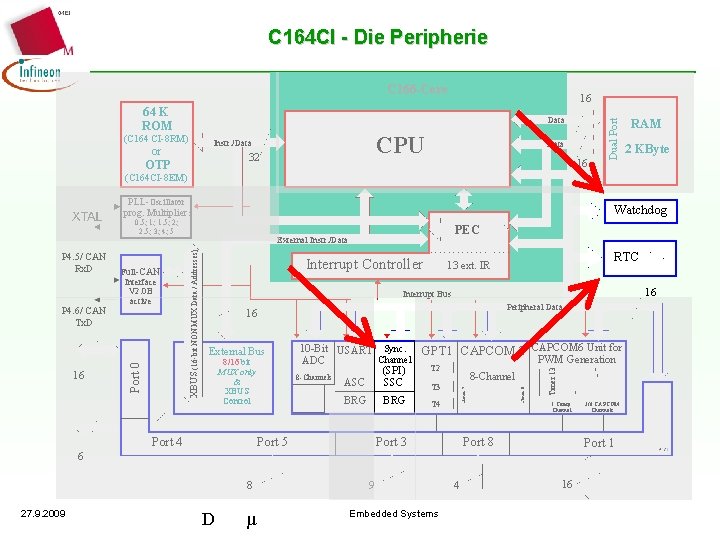

C 164 CI - Die Peripherie C 166 -Core Data (C 164 CI-8 RM) or OTP CPU Instr. /Data 32 Data 16 Dual Port 64 K ROM 16 RAM 2 KByte (C 164 CI-8 EM) PLL-Oscillator prog. Multiplier: Watchdog 0. 5; 1; 1. 5; 2; 2. 5; 3; 4; 5 Interrupt Controller RTC 13 ext. IR 16 Interrupt Bus Peripheral Data 16 Port 4 BRG T 4 Port 3 Port 5 Timer 13 8/16 bit MUX only & XBUS Control 10 -Bit USART Sync. GPT 1 CAPCOM 2 CAPCOM 6 Unit for PWM Generation Channel ADC T 2 (SPI) 8 -Channels ASC SSC T 3 Timer 8 External Bus Timer 7 16 XBUS (16 -bit NON MUX Data / Addresses) P 4. 6/ CAN Tx. D Full-CAN Interface V 2. 0 B active Port 0 P 4. 5/ CAN Rx. D PEC External Instr. /Data 1 Comp. Channel Port 8 Port 1 6 8 27. 9. 2009 D µ 9 Embedded Systems 4 3/6 CAPCOM Channels 16

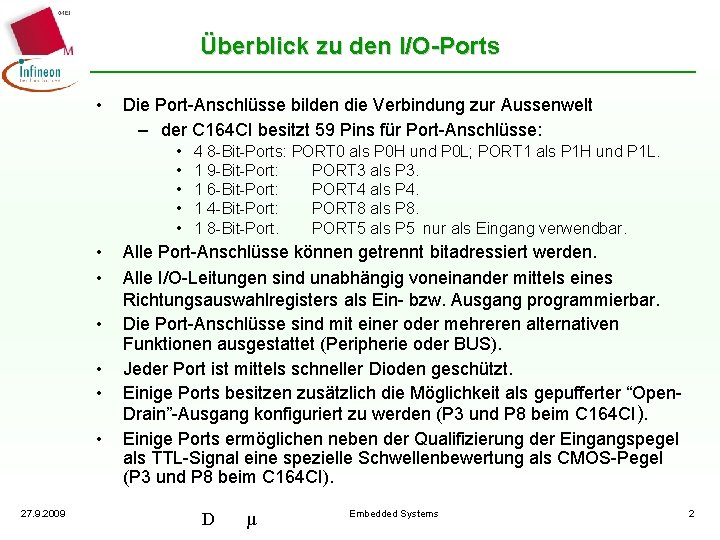

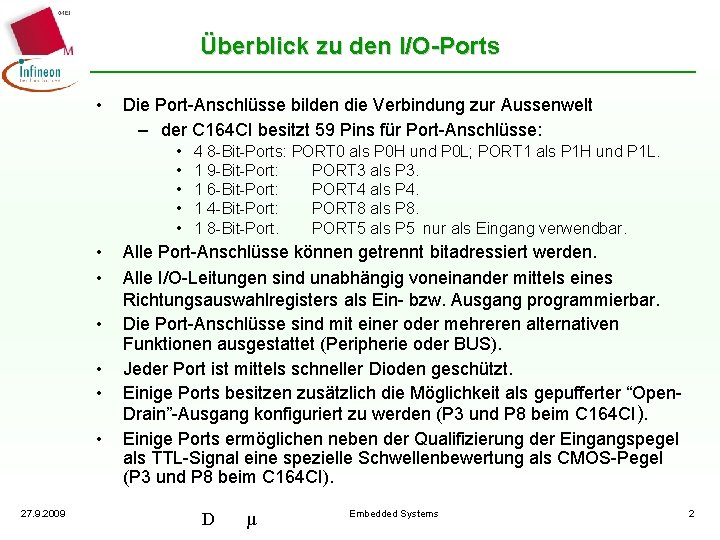

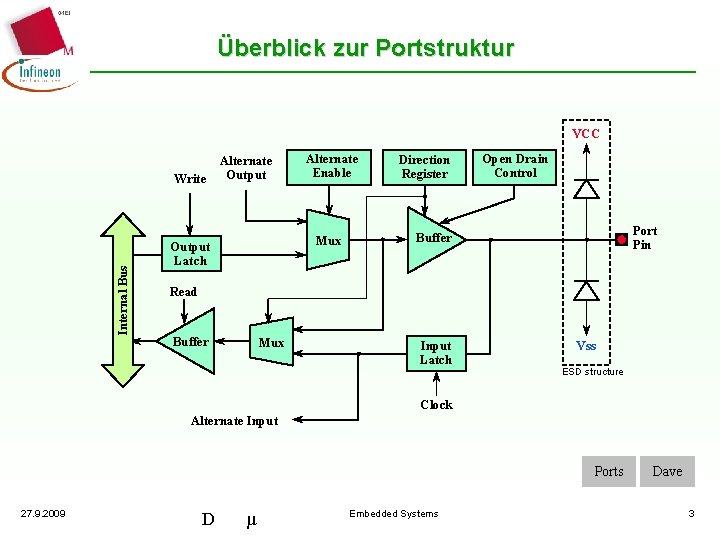

Überblick zu den I/O-Ports • Die Port-Anschlüsse bilden die Verbindung zur Aussenwelt – der C 164 CI besitzt 59 Pins für Port-Anschlüsse: • • • 27. 9. 2009 4 8 -Bit-Ports: PORT 0 als P 0 H und P 0 L; PORT 1 als P 1 H und P 1 L. 1 9 -Bit-Port: PORT 3 als P 3. 1 6 -Bit-Port: PORT 4 als P 4. 1 4 -Bit-Port: PORT 8 als P 8. 1 8 -Bit-Port. PORT 5 als P 5 nur als Eingang verwendbar. Alle Port-Anschlüsse können getrennt bitadressiert werden. Alle I/O-Leitungen sind unabhängig voneinander mittels eines Richtungsauswahlregisters als Ein- bzw. Ausgang programmierbar. Die Port-Anschlüsse sind mit einer oder mehreren alternativen Funktionen ausgestattet (Peripherie oder BUS). Jeder Port ist mittels schneller Dioden geschützt. Einige Ports besitzen zusätzlich die Möglichkeit als gepufferter “Open. Drain”-Ausgang konfiguriert zu werden (P 3 und P 8 beim C 164 CI). Einige Ports ermöglichen neben der Qualifizierung der Eingangspegel als TTL-Signal eine spezielle Schwellenbewertung als CMOS-Pegel (P 3 und P 8 beim C 164 CI). D µ Embedded Systems 2

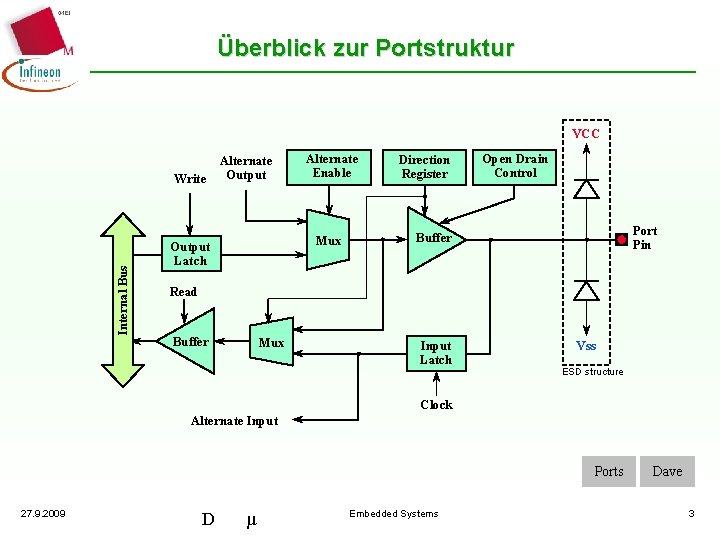

Überblick zur Portstruktur VCC Internal Bus Write Alternate Output Alternate Enable Mux Output Latch Direction Register Open Drain Control Port Pin Buffer Read Buffer Mux Input Latch Vss ESD structure Clock Alternate Input Ports 27. 9. 2009 D µ Embedded Systems Dave 3

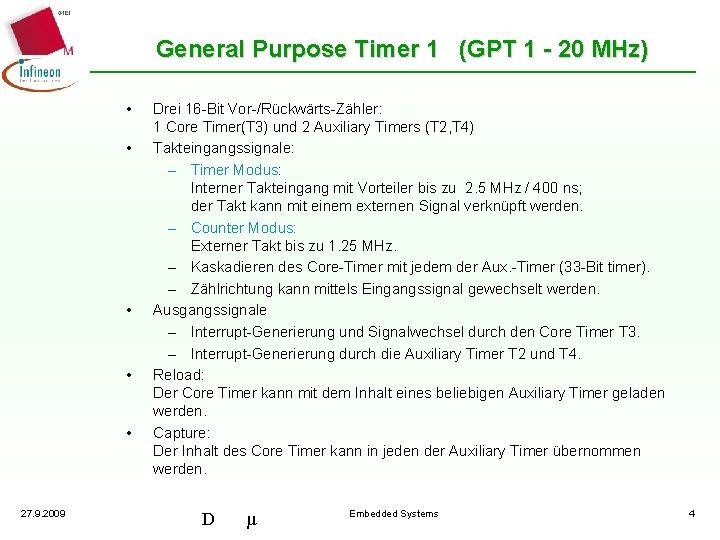

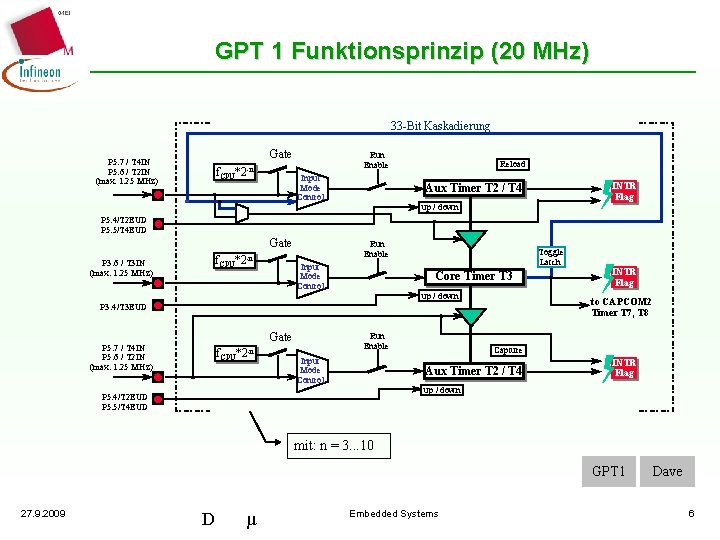

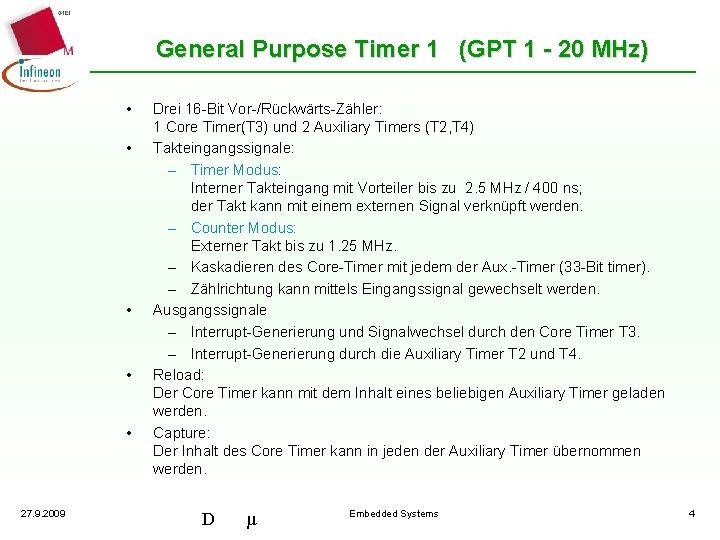

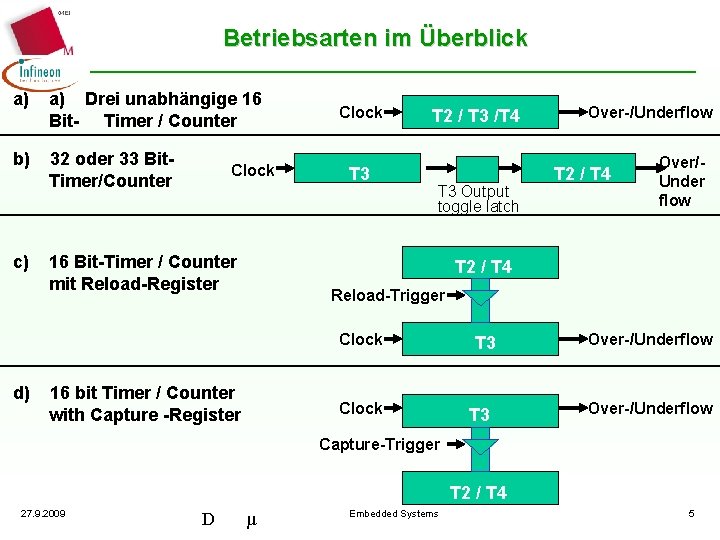

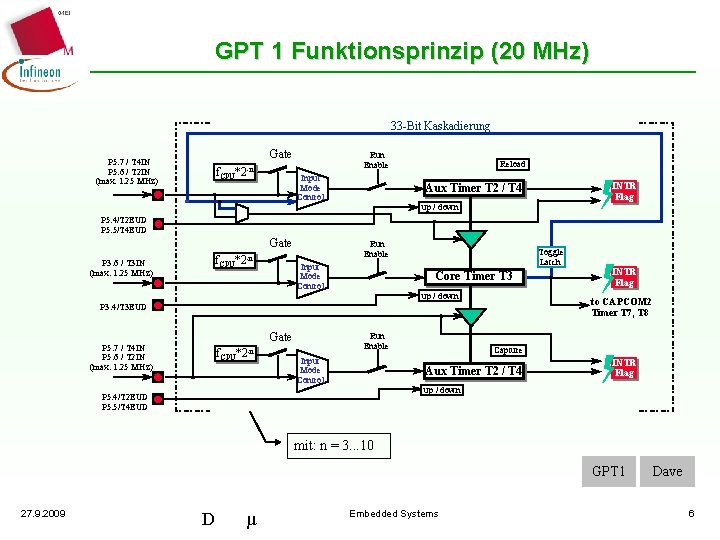

General Purpose Timer 1 (GPT 1 - 20 MHz) • • • 27. 9. 2009 Drei 16 -Bit Vor-/Rückwärts-Zähler: 1 Core Timer(T 3) und 2 Auxiliary Timers (T 2, T 4) Takteingangssignale: – Timer Modus: Interner Takteingang mit Vorteiler bis zu 2. 5 MHz / 400 ns; der Takt kann mit einem externen Signal verknüpft werden. – Counter Modus: Externer Takt bis zu 1. 25 MHz. – Kaskadieren des Core-Timer mit jedem der Aux. -Timer (33 -Bit timer). – Zählrichtung kann mittels Eingangssignal gewechselt werden. Ausgangssignale – Interrupt-Generierung und Signalwechsel durch den Core Timer T 3. – Interrupt-Generierung durch die Auxiliary Timer T 2 und T 4. Reload: Der Core Timer kann mit dem Inhalt eines beliebigen Auxiliary Timer geladen werden. Capture: Der Inhalt des Core Timer kann in jeden der Auxiliary Timer übernommen werden. D µ Embedded Systems 4

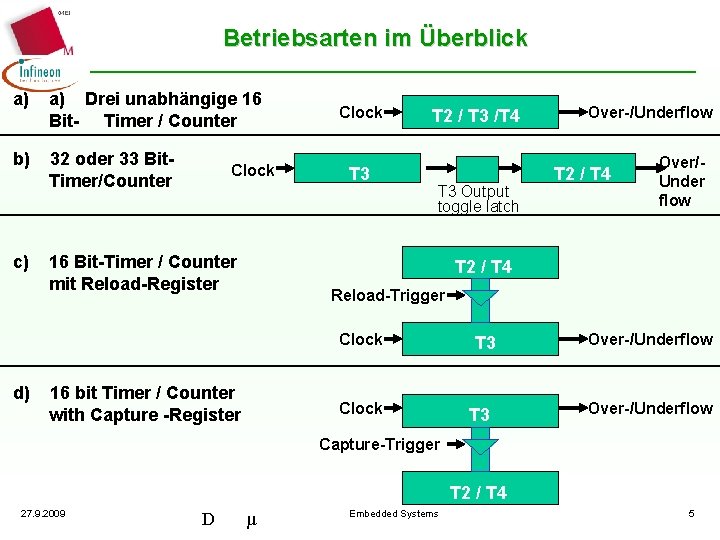

Betriebsarten im Überblick a) a) Drei unabhängige 16 Bit- Timer / Counter b) 32 oder 33 Bit. Timer/Counter c) Clock 16 Bit-Timer / Counter mit Reload-Register Clock T 3 T 2 / T 3 /T 4 T 3 Output toggle latch T 2 / T 4 Over/Under flow T 2 / T 4 Reload-Trigger Clock d) Over-/Underflow 16 bit Timer / Counter with Capture -Register Clock T 3 Over-/Underflow Capture-Trigger T 2//T 4 T 2 27. 9. 2009 D µ Embedded Systems 5

GPT 1 Funktionsprinzip (20 MHz) 33 -Bit Kaskadierung Gate P 5. 7 / T 4 IN P 5. 6 / T 2 IN (max. 1. 25 MHz) f. CPU*2 -n Run Enable Input Mode Control Reload INTR Flag Aux Timer T 2 / T 4 up / down P 5. 4/T 2 EUD P 5. 5/T 4 EUD Gate f. CPU*2 -n P 3. 6 / T 3 IN (max. 1. 25 MHz) Run Enable Input Mode Control Toggle Latch Core Timer T 3 up / down to CAPCOM 2 Timer T 7, T 8 P 3. 4/T 3 EUD Gate P 5. 7 / T 4 IN P 5. 6 / T 2 IN (max. 1. 25 MHz) f. CPU*2 -n Run Enable Input Mode Control INTR Flag Capture Aux Timer T 2 / T 4 INTR Flag up / down P 5. 4/T 2 EUD P 5. 5/T 4 EUD mit: n = 3. . . 10 GPT 1 27. 9. 2009 D µ Embedded Systems Dave 6

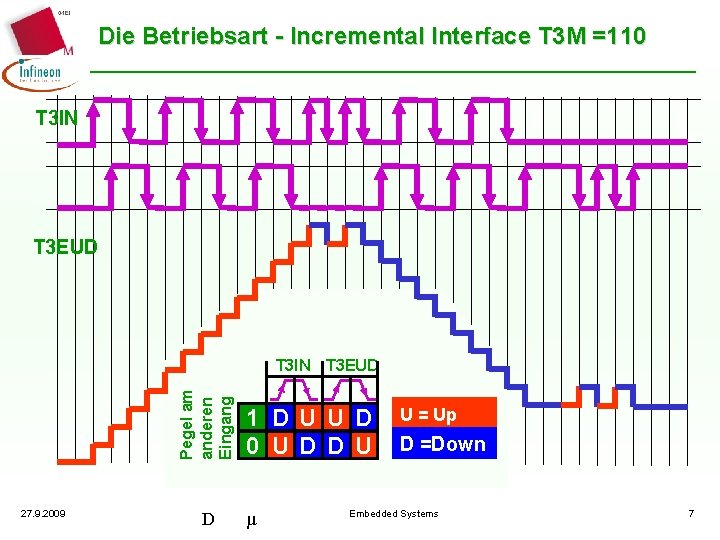

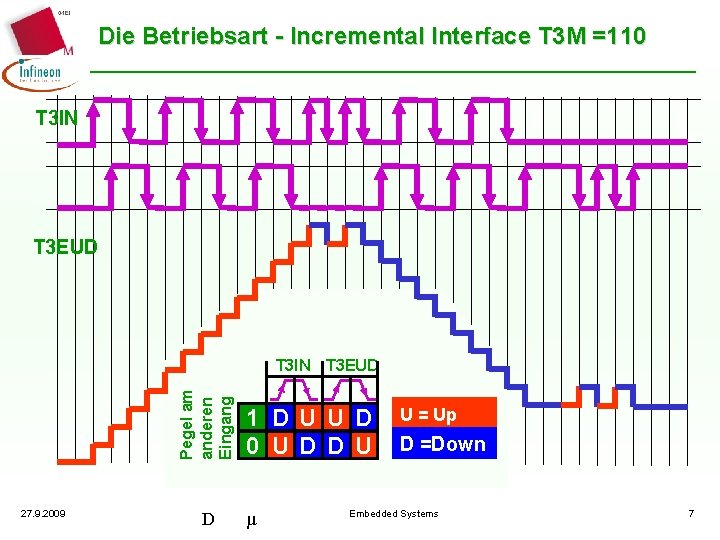

Die Betriebsart - Incremental Interface T 3 M =110 T 3 IN T 3 EUD Pegel am anderen Eingang T 3 IN T 3 EUD 27. 9. 2009 D 1 D U U D 0 U D D U µ U = Up D =Down Embedded Systems 7

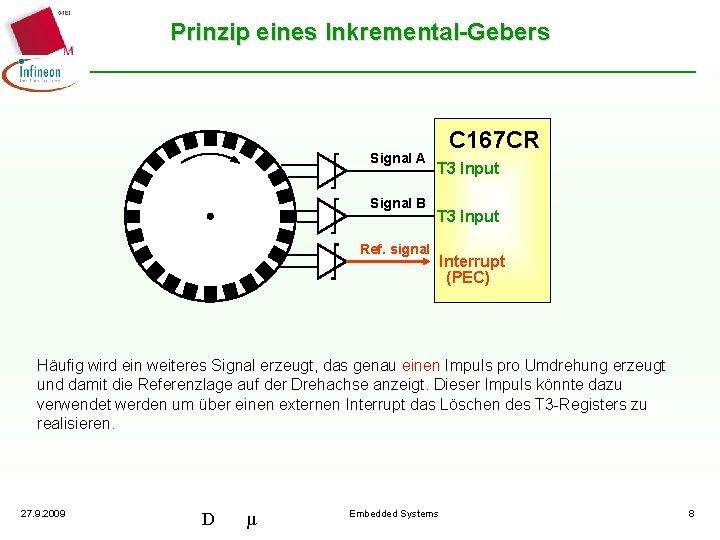

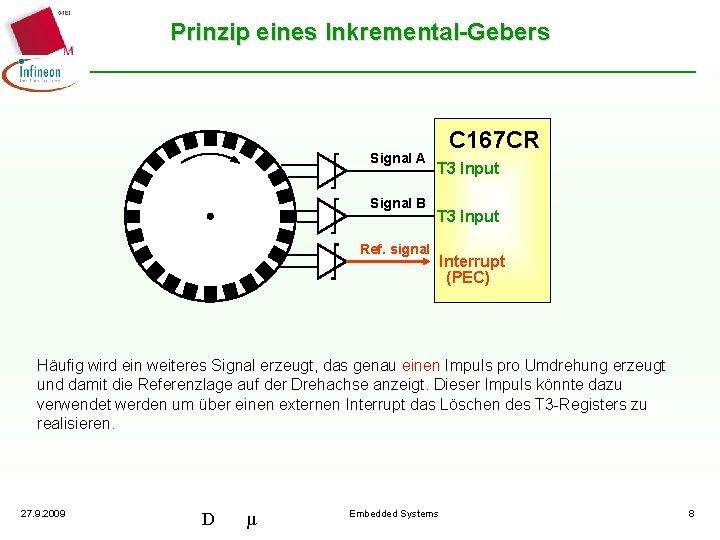

Prinzip eines Inkremental-Gebers Signal A Signal B C 167 CR T 3 Input Ref. signal Interrupt (PEC) Häufig wird ein weiteres Signal erzeugt, das genau einen Impuls pro Umdrehung erzeugt und damit die Referenzlage auf der Drehachse anzeigt. Dieser Impuls könnte dazu verwendet werden um über einen externen Interrupt das Löschen des T 3 -Registers zu realisieren. 27. 9. 2009 D µ Embedded Systems 8

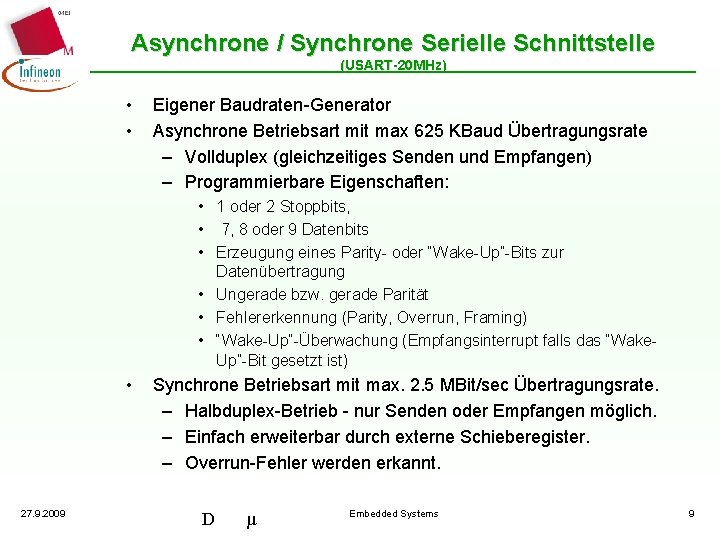

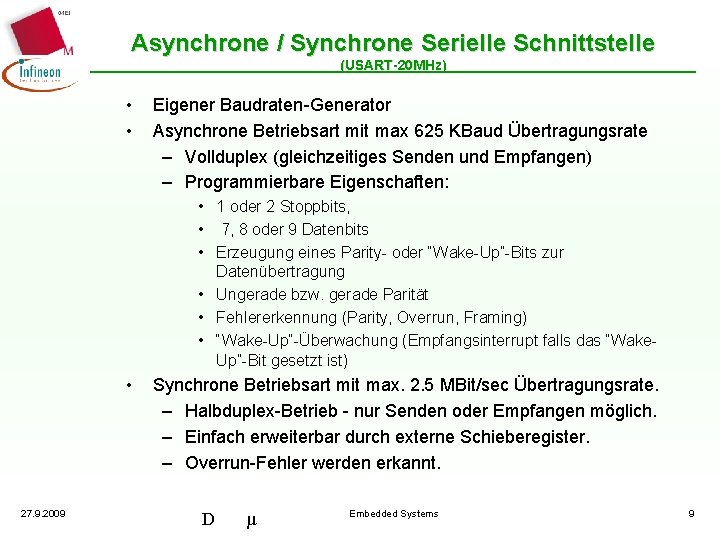

Asynchrone / Synchrone Serielle Schnittstelle (USART-20 MHz) • • Eigener Baudraten-Generator Asynchrone Betriebsart mit max 625 KBaud Übertragungsrate – Vollduplex (gleichzeitiges Senden und Empfangen) – Programmierbare Eigenschaften: • 1 oder 2 Stoppbits, • 7, 8 oder 9 Datenbits • Erzeugung eines Parity- oder “Wake-Up”-Bits zur Datenübertragung • Ungerade bzw. gerade Parität • Fehlererkennung (Parity, Overrun, Framing) • “Wake-Up”-Überwachung (Empfangsinterrupt falls das “Wake. Up”-Bit gesetzt ist) • 27. 9. 2009 Synchrone Betriebsart mit max. 2. 5 MBit/sec Übertragungsrate. – Halbduplex-Betrieb - nur Senden oder Empfangen möglich. – Einfach erweiterbar durch externe Schieberegister. – Overrun-Fehler werden erkannt. D µ Embedded Systems 9

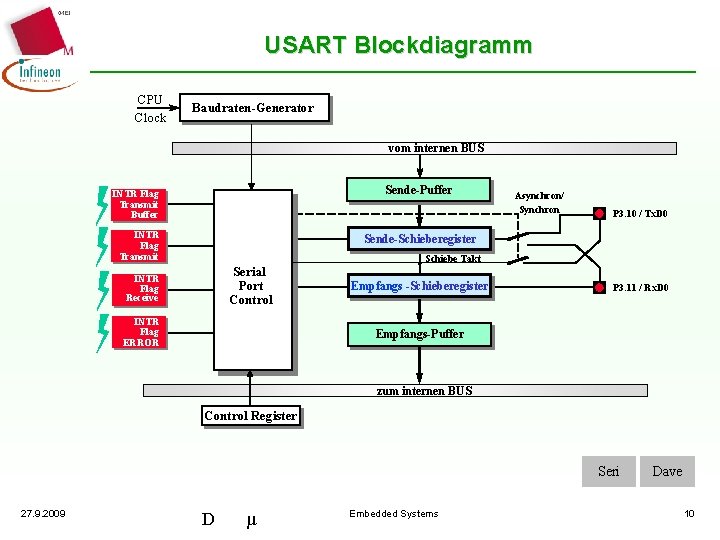

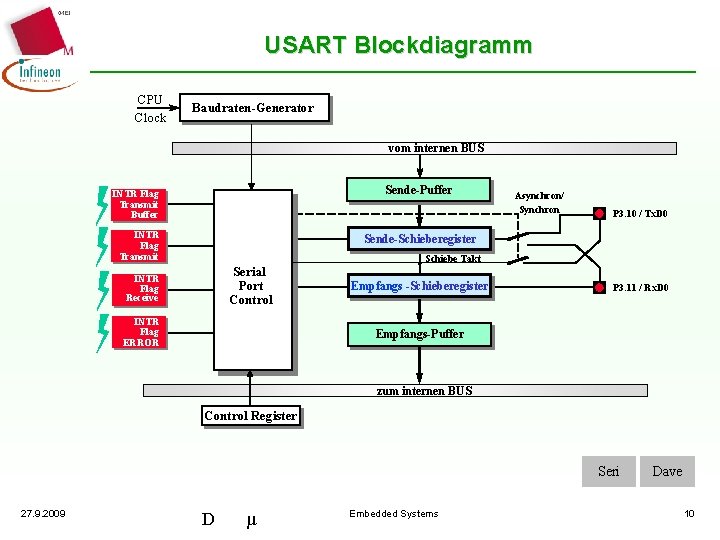

USART Blockdiagramm CPU Clock Baudraten-Generator vom internen BUS Sende-Puffer INTR Flag Transmit Buffer INTR Flag Transmit Asynchron/ Synchron P 3. 10 / Tx. D 0 Sende-Schieberegister Schiebe Takt Serial Port Control INTR Flag Receive INTR Flag ERROR Empfangs -Schieberegister P 3. 11 / Rx. D 0 Empfangs-Puffer zum internen BUS Control Register Seri 27. 9. 2009 D µ Embedded Systems Dave 10

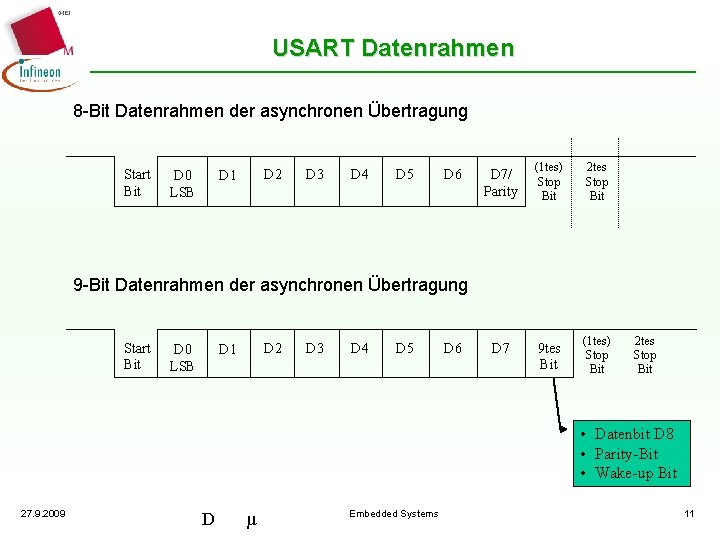

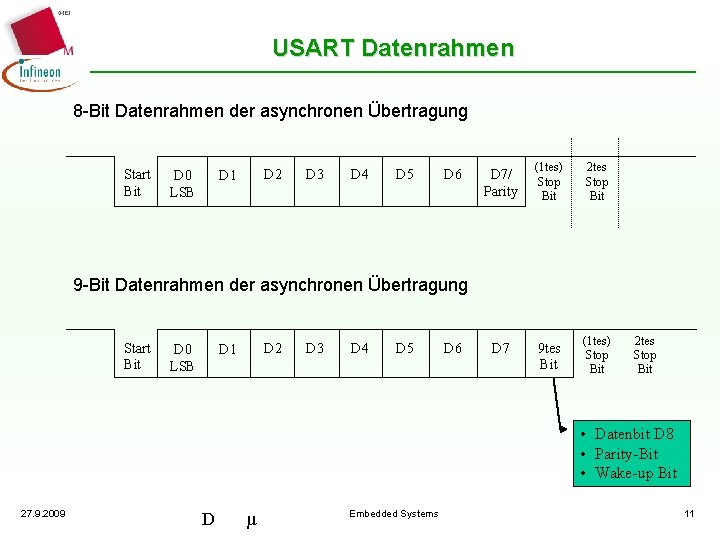

USART Datenrahmen 8 -Bit Datenrahmen der asynchronen Übertragung Start Bit D 0 LSB D 2 D 1 D 3 D 4 D 5 D 6 D 7/ Parity (1 tes) Stop Bit 2 tes Stop Bit 9 tes Bit (1 tes) Stop Bit 9 -Bit Datenrahmen der asynchronen Übertragung Start Bit D 0 LSB D 2 D 1 D 3 D 4 D 5 D 6 D 7 2 tes Stop Bit • Datenbit D 8 • Parity-Bit • Wake-up Bit 27. 9. 2009 D µ Embedded Systems 11

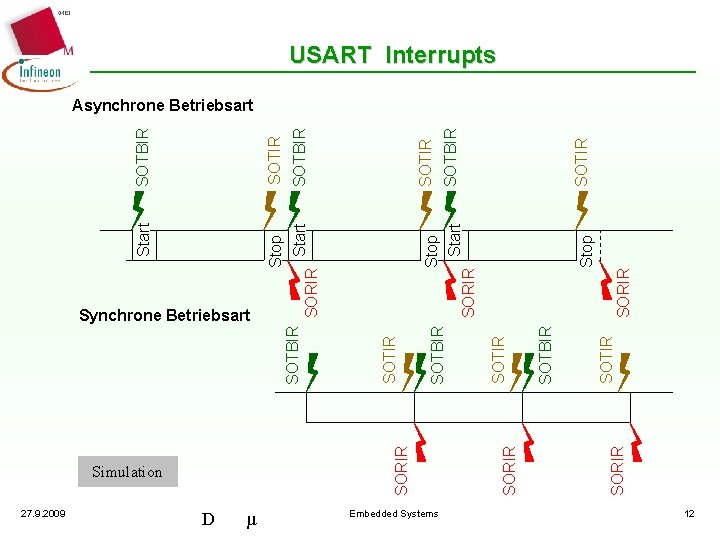

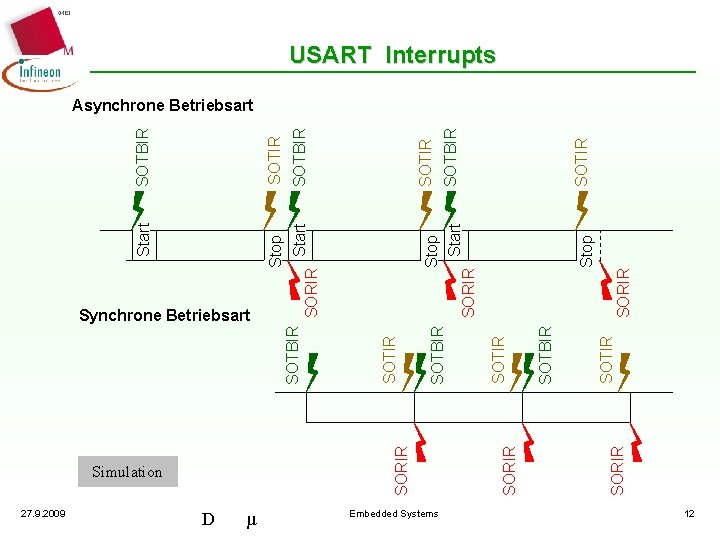

Simulation 27. 9. 2009 D µ Embedded Systems SORIR Synchrone Betriebsart SOTIR SOTBIR SOTIR SORIR Stop Start SORIR Stop SOTBIR Start SORIR Start SOTIR SOTBIR USART Interrupts Asynchrone Betriebsart 12

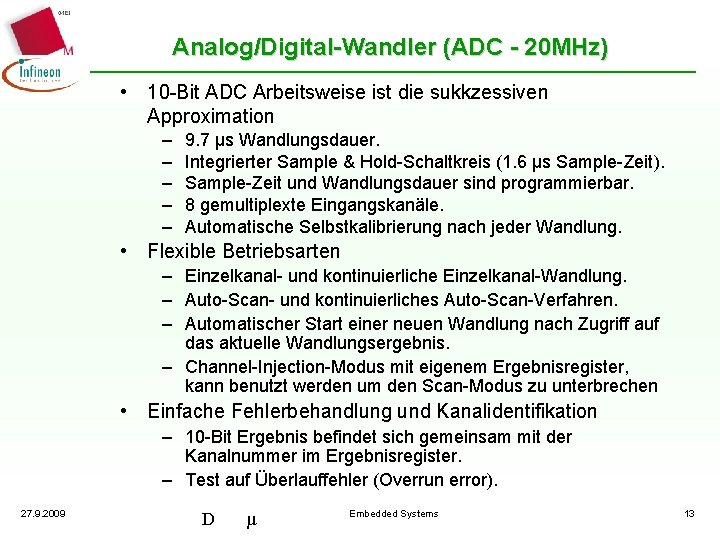

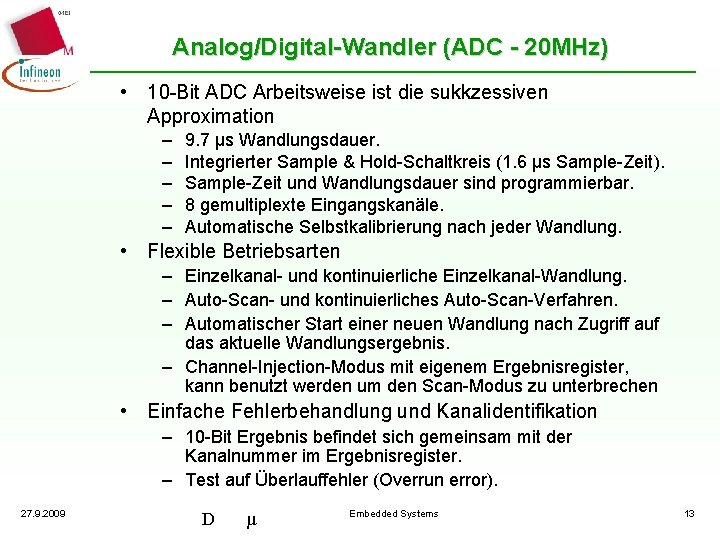

Analog/Digital-Wandler (ADC - 20 MHz) • 10 -Bit ADC Arbeitsweise ist die sukkzessiven Approximation – – – 9. 7 µs Wandlungsdauer. Integrierter Sample & Hold-Schaltkreis (1. 6 µs Sample-Zeit). Sample-Zeit und Wandlungsdauer sind programmierbar. 8 gemultiplexte Eingangskanäle. Automatische Selbstkalibrierung nach jeder Wandlung. • Flexible Betriebsarten – Einzelkanal- und kontinuierliche Einzelkanal-Wandlung. – Auto-Scan- und kontinuierliches Auto-Scan-Verfahren. – Automatischer Start einer neuen Wandlung nach Zugriff auf das aktuelle Wandlungsergebnis. – Channel-Injection-Modus mit eigenem Ergebnisregister, kann benutzt werden um den Scan-Modus zu unterbrechen • Einfache Fehlerbehandlung und Kanalidentifikation – 10 -Bit Ergebnis befindet sich gemeinsam mit der Kanalnummer im Ergebnisregister. – Test auf Überlauffehler (Overrun error). 27. 9. 2009 D µ Embedded Systems 13

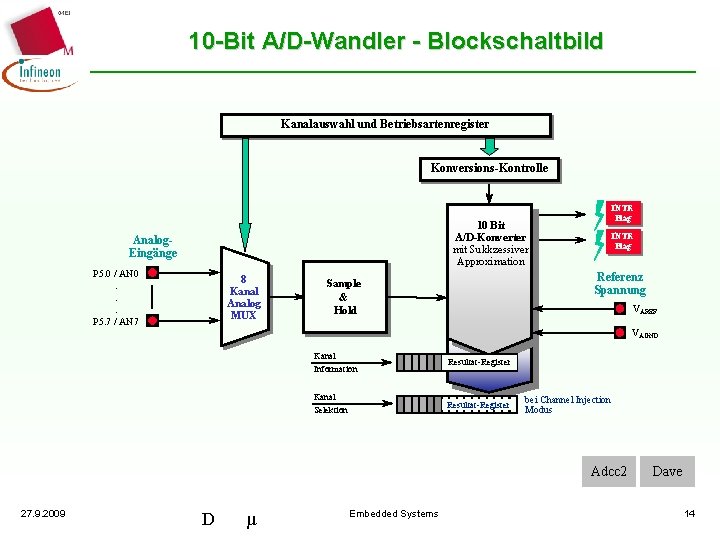

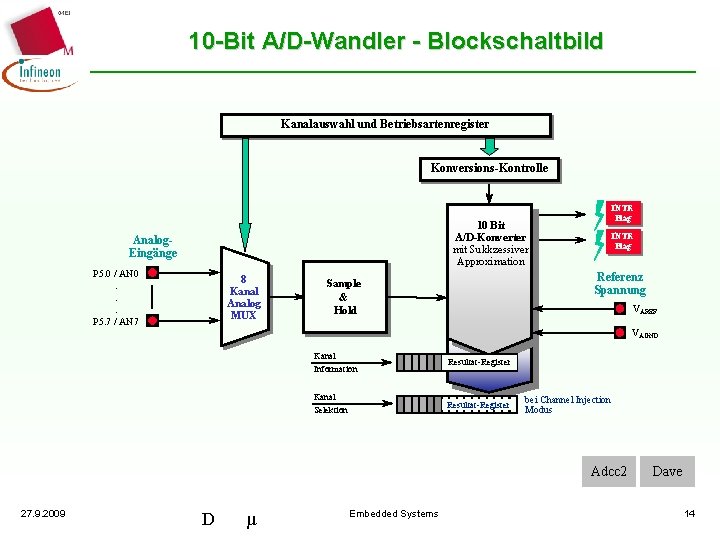

10 -Bit A/D-Wandler - Blockschaltbild Kanalauswahl und Betriebsartenregister Konversions-Kontrolle 10 Bit A/D-Konverter mit Sukkzessiver Approximation Analog. Eingänge P 5. 0 / AN 0. . . P 5. 7 / AN 7 8 Kanal Analog MUX INTR Flag Referenz Spannung Sample & Hold VAREF VAGND Kanal Information Resultat-Register Kanal Selektion Resultat-Register bei Channel Injection Modus Adcc 2 27. 9. 2009 D µ Embedded Systems Dave 14

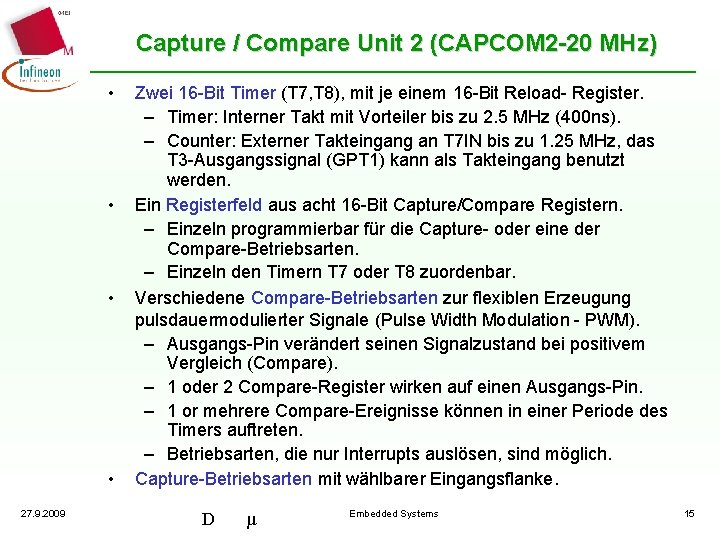

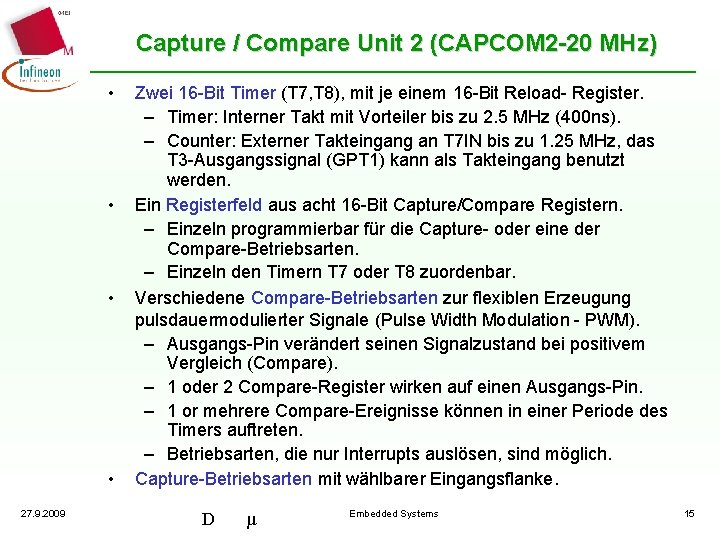

Capture / Compare Unit 2 (CAPCOM 2 -20 MHz) • • 27. 9. 2009 Zwei 16 -Bit Timer (T 7, T 8), mit je einem 16 -Bit Reload- Register. – Timer: Interner Takt mit Vorteiler bis zu 2. 5 MHz (400 ns). – Counter: Externer Takteingang an T 7 IN bis zu 1. 25 MHz, das T 3 -Ausgangssignal (GPT 1) kann als Takteingang benutzt werden. Ein Registerfeld aus acht 16 -Bit Capture/Compare Registern. – Einzeln programmierbar für die Capture- oder eine der Compare-Betriebsarten. – Einzeln den Timern T 7 oder T 8 zuordenbar. Verschiedene Compare-Betriebsarten zur flexiblen Erzeugung pulsdauermodulierter Signale (Pulse Width Modulation - PWM). – Ausgangs-Pin verändert seinen Signalzustand bei positivem Vergleich (Compare). – 1 oder 2 Compare-Register wirken auf einen Ausgangs-Pin. – 1 or mehrere Compare-Ereignisse können in einer Periode des Timers auftreten. – Betriebsarten, die nur Interrupts auslösen, sind möglich. Capture-Betriebsarten mit wählbarer Eingangsflanke. D µ Embedded Systems 15

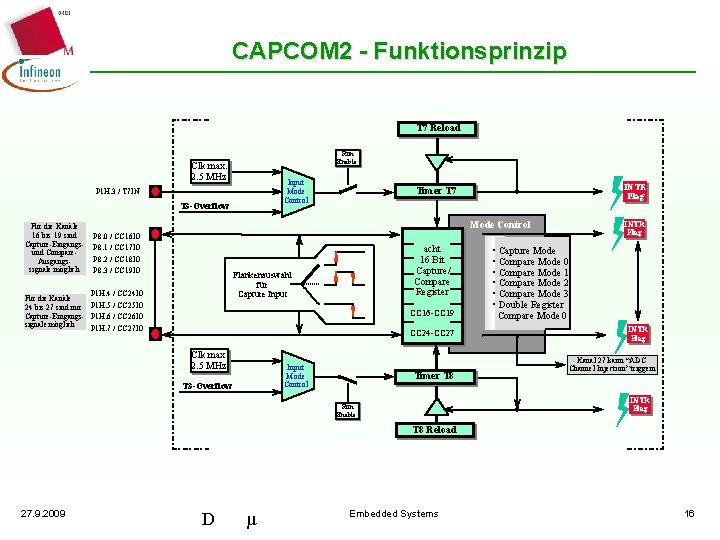

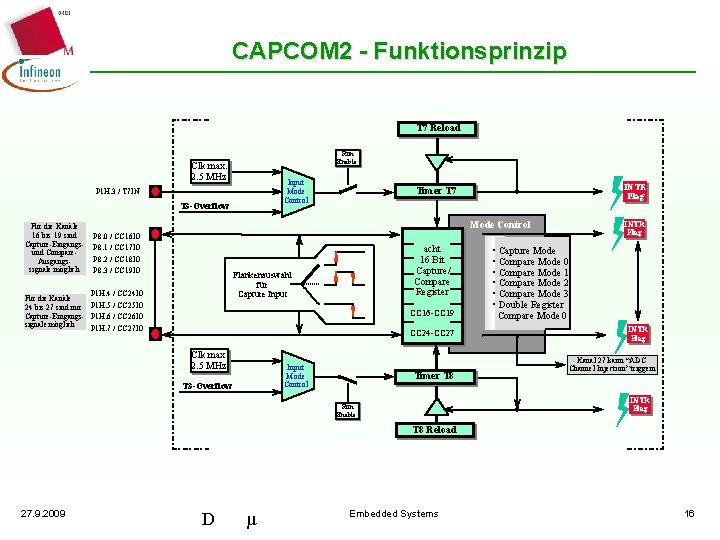

CAPCOM 2 - Funktionsprinzip T 7 Reload Run Enable Clk max. 2. 5 MHz Input Mode Control P 1 H. 3 / T 7 IN T 3 -Overflow Für die Kanäle 16 bis 19 sind Capture-Eingangsund Compare. Ausgangssignale möglich INTR Flag Timer T 7 Mode Control P 8. 0 / CC 16 IO P 8. 1 / CC 17 IO P 8. 2 / CC 18 IO P 8. 3 / CC 19 IO acht 16 Bit Capture/ Compare Register Flankenauswahl für Capture Input P 1 H. 4 / CC 24 IO Für die Kanäle 24 bis 27 sind nur P 1 H. 5 / CC 25 IO Capture-Eingangs- P 1 H. 6 / CC 26 IO signale möglich P 1 H. 7 / CC 27 IO CC 16 -CC 19 CC 24 -CC 27 Clk max 2. 5 MHz Input Mode Control T 3 -Overflow Timer T 8 INTR Flag • Capture Mode • Compare Mode 0 • Compare Mode 1 • Compare Mode 2 • Compare Mode 3 • Double Register Compare Mode 0 INTR Flag Kanal 27 kann “ADC Channel Injection” triggern INTR Flag Run Enable T 8 Reload 27. 9. 2009 D µ Embedded Systems 16

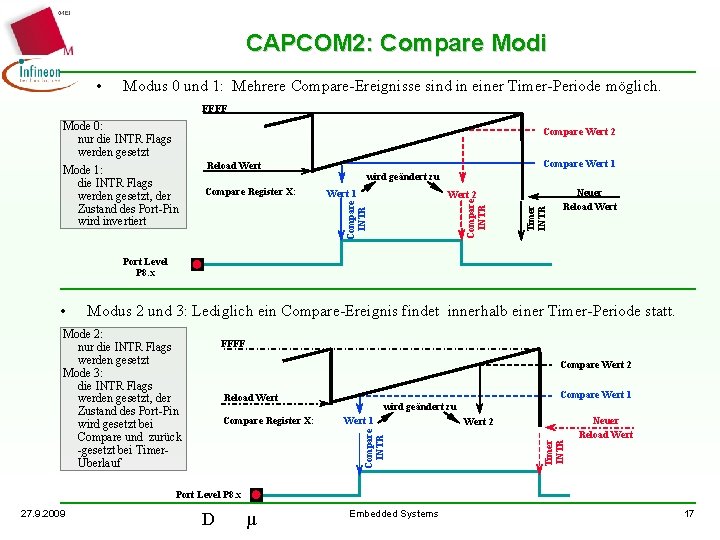

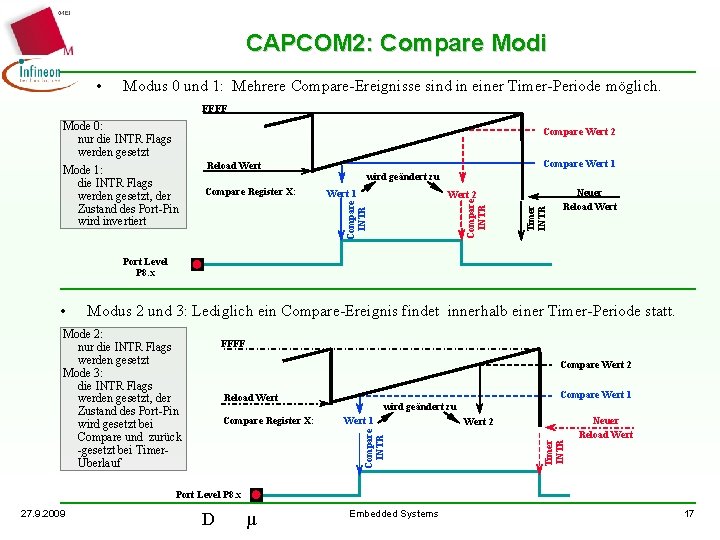

CAPCOM 2: Compare Modi • Modus 0 und 1: Mehrere Compare-Ereignisse sind in einer Timer-Periode möglich. FFFF Compare Wert 2 Compare Wert 1 Reload Wert wird geändert zu Wert 1 Timer INTR Wert 2 Compare INTR Compare Register X: Compare INTR Mode 0: nur die INTR Flags werden gesetzt Mode 1: die INTR Flags werden gesetzt, der Zustand des Port-Pin wird invertiert Neuer Reload Wert Port Level P 8. x Modus 2 und 3: Lediglich ein Compare-Ereignis findet innerhalb einer Timer-Periode statt. Mode 2: nur die INTR Flags werden gesetzt Mode 3: die INTR Flags werden gesetzt, der Zustand des Port-Pin wird gesetzt bei Compare und zurück -gesetzt bei TimerÜberlauf FFFF Compare Wert 2 Compare Wert 1 Reload Wert 1 Compare INTR Compare Register X: wird geändert zu Wert 2 Timer INTR • Neuer Reload Wert Port Level P 8. x 27. 9. 2009 D µ Embedded Systems 17

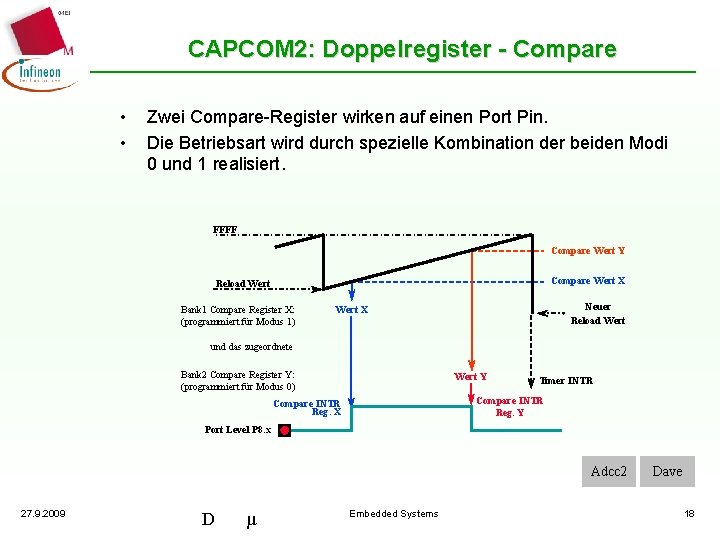

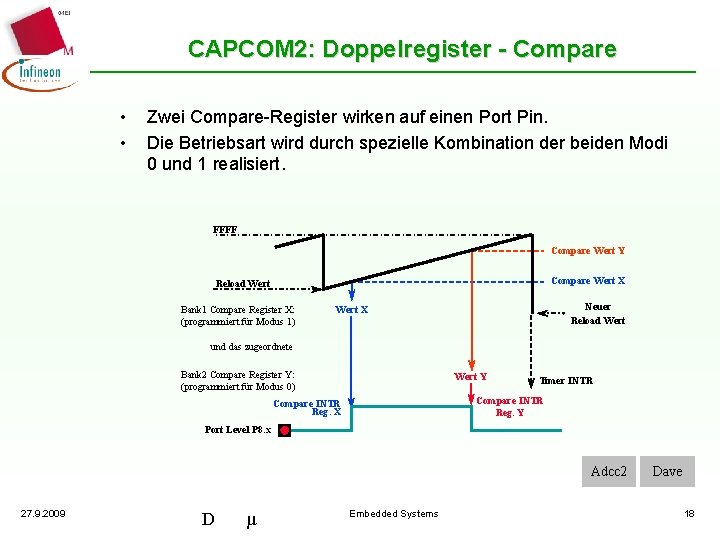

CAPCOM 2: Doppelregister - Compare • • Zwei Compare-Register wirken auf einen Port Pin. Die Betriebsart wird durch spezielle Kombination der beiden Modi 0 und 1 realisiert. FFFF Compare Wert Y Compare Wert X Reload Wert Bank 1 Compare Register X: (programmiert für Modus 1) Neuer Reload Wert X und das zugeordnete Bank 2 Compare Register Y: (programmiert für Modus 0) Wert Y Timer INTR Compare INTR Reg. Y Compare INTR Reg. X Port Level P 8. x Adcc 2 27. 9. 2009 D µ Embedded Systems Dave 18

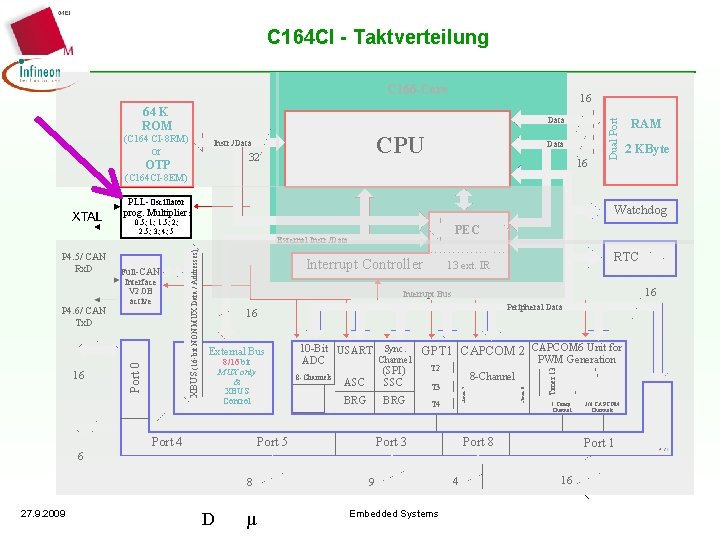

C 164 CI - Taktverteilung C 166 -Core Data (C 164 CI-8 RM) or OTP CPU Instr. /Data 32 Data 16 Dual Port 64 K ROM 16 RAM 2 KByte (C 164 CI-8 EM) PLL-Oscillator prog. Multiplier: Watchdog 0. 5; 1; 1. 5; 2; 2. 5; 3; 4; 5 Interrupt Controller RTC 13 ext. IR 16 Interrupt Bus Peripheral Data 16 Port 4 BRG T 4 Port 3 Port 5 Timer 13 8/16 bit MUX only & XBUS Control 10 -Bit USART Sync. GPT 1 CAPCOM 2 CAPCOM 6 Unit for PWM Generation Channel ADC T 2 (SPI) 8 -Channels ASC SSC T 3 Timer 8 External Bus Timer 7 16 XBUS (16 -bit NON MUX Data / Addresses) P 4. 6/ CAN Tx. D Full-CAN Interface V 2. 0 B active Port 0 P 4. 5/ CAN Rx. D PEC External Instr. /Data 1 Comp. Channel Port 8 Port 1 6 8 27. 9. 2009 D µ 9 Embedded Systems 4 3/6 CAPCOM Channels 16

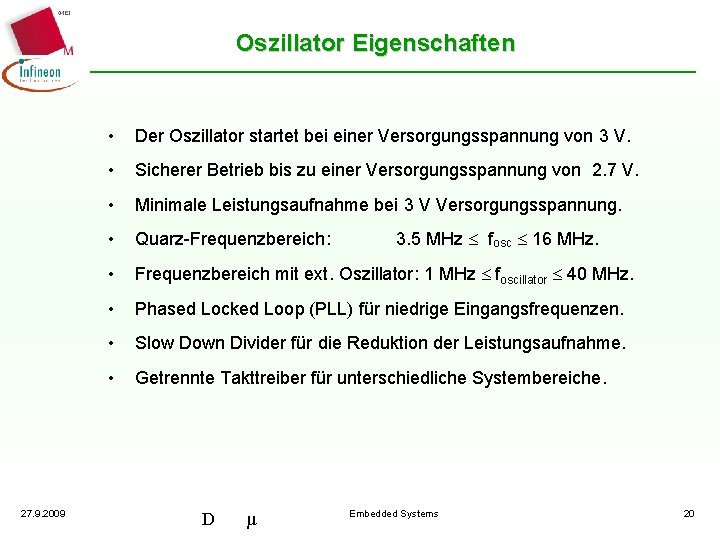

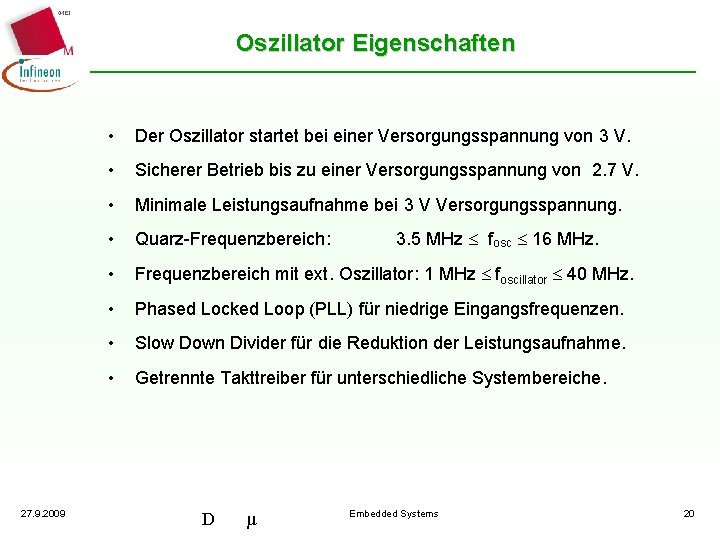

Oszillator Eigenschaften 27. 9. 2009 • Der Oszillator startet bei einer Versorgungsspannung von 3 V. • Sicherer Betrieb bis zu einer Versorgungsspannung von 2. 7 V. • Minimale Leistungsaufnahme bei 3 V Versorgungsspannung. • Quarz-Frequenzbereich: • Frequenzbereich mit ext. Oszillator: 1 MHz foscillator 40 MHz. • Phased Locked Loop (PLL) für niedrige Eingangsfrequenzen. • Slow Down Divider für die Reduktion der Leistungsaufnahme. • Getrennte Takttreiber für unterschiedliche Systembereiche. D µ 3. 5 MHz fosc 16 MHz. Embedded Systems 20

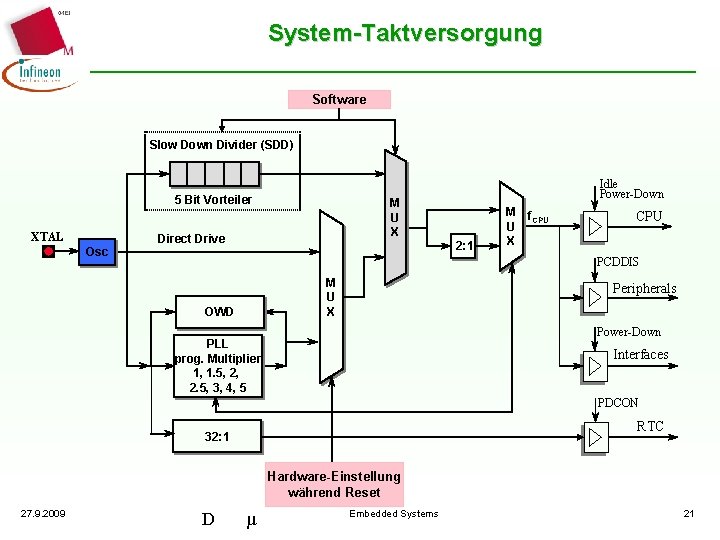

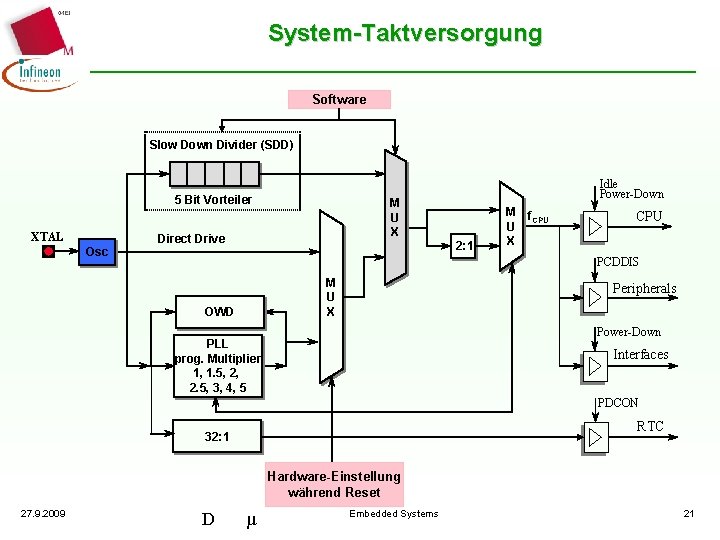

System-Taktversorgung Software Slow Down Divider (SDD) 5 Bit Vorteiler XTAL Idle Power-Down M U X Direct Drive 2: 1 Osc M U X f. CPU PCDDIS M U X OWD Peripherals Power-Down PLL prog. Multiplier 1, 1. 5, 2, 2. 5, 3, 4, 5 Interfaces PDCON RTC 32: 1 Hardware-Einstellung während Reset 27. 9. 2009 D µ Embedded Systems 21

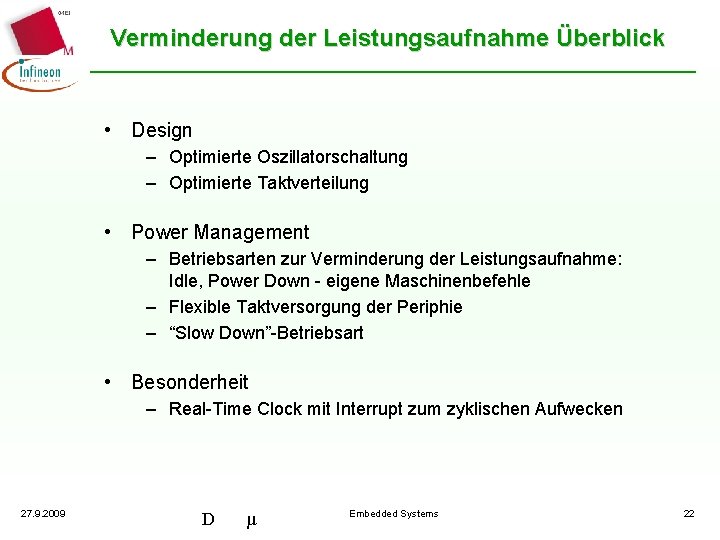

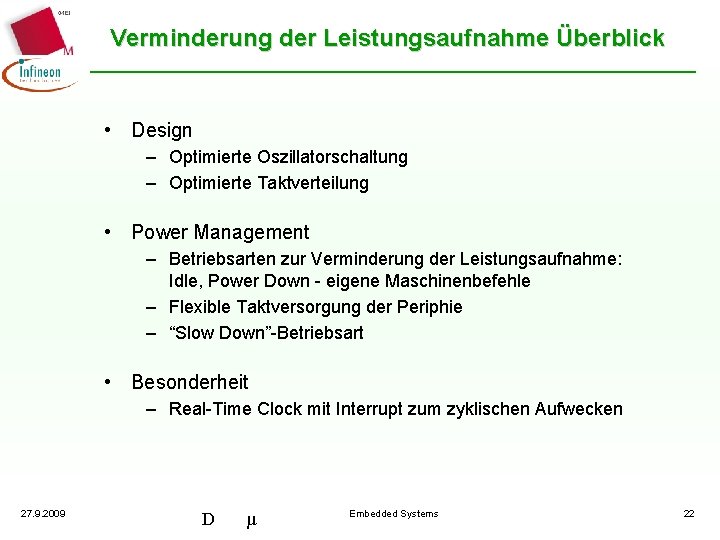

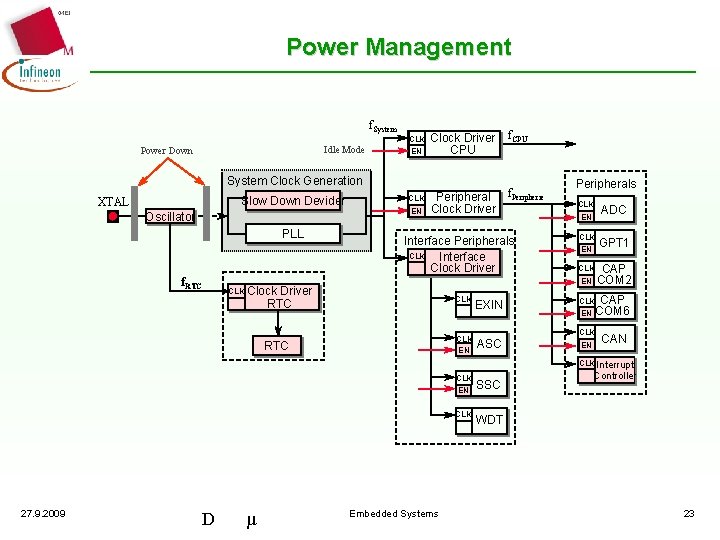

Verminderung der Leistungsaufnahme Überblick • Design – Optimierte Oszillatorschaltung – Optimierte Taktverteilung • Power Management – Betriebsarten zur Verminderung der Leistungsaufnahme: Idle, Power Down - eigene Maschinenbefehle – Flexible Taktversorgung der Periphie – “Slow Down”-Betriebsart • Besonderheit – Real-Time Clock mit Interrupt zum zyklischen Aufwecken 27. 9. 2009 D µ Embedded Systems 22

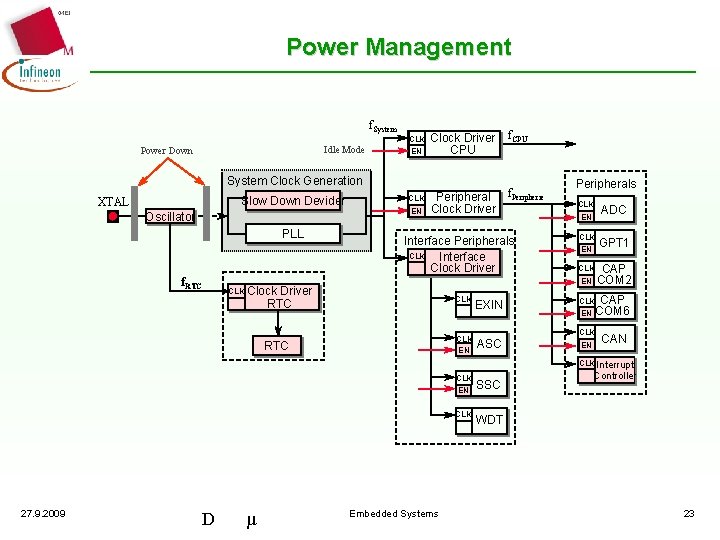

Power Management f. System CLK Idle Mode Power Down EN System Clock Generation Slow Down Devider XTAL Oscillator PLL f. RTC CLK EN Clock Driver CPU f. CPU Peripheral f. Peripherie Clock Driver Interface Peripherals CLK Interface Clock Driver Peripherals CLK ADC EN CLK EN Clock Driver RTC CLK EN RTC EXIN CLK EN CLK ASC EN GPT 1 CAP COM 2 CAP COM 6 CAN CLK Interrupt CLK EN CLK 27. 9. 2009 D µ Embedded Systems SSC Controller WDT 23

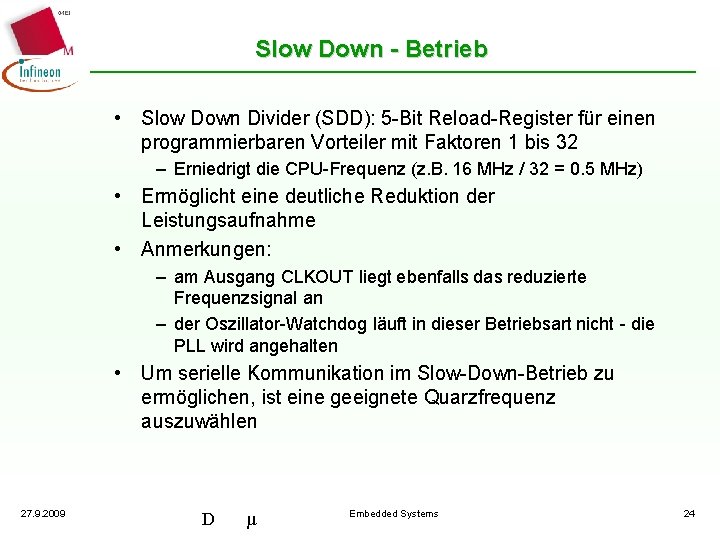

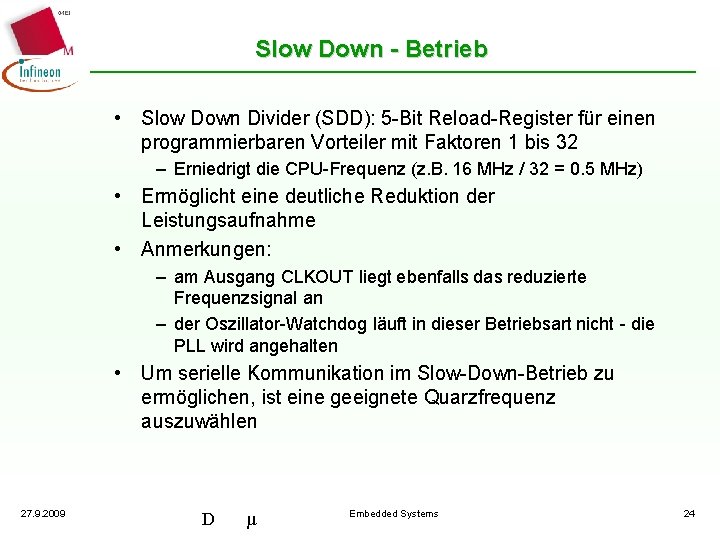

Slow Down - Betrieb • Slow Down Divider (SDD): 5 -Bit Reload-Register für einen programmierbaren Vorteiler mit Faktoren 1 bis 32 – Erniedrigt die CPU-Frequenz (z. B. 16 MHz / 32 = 0. 5 MHz) • Ermöglicht eine deutliche Reduktion der Leistungsaufnahme • Anmerkungen: – am Ausgang CLKOUT liegt ebenfalls das reduzierte Frequenzsignal an – der Oszillator-Watchdog läuft in dieser Betriebsart nicht - die PLL wird angehalten • Um serielle Kommunikation im Slow-Down-Betrieb zu ermöglichen, ist eine geeignete Quarzfrequenz auszuwählen 27. 9. 2009 D µ Embedded Systems 24

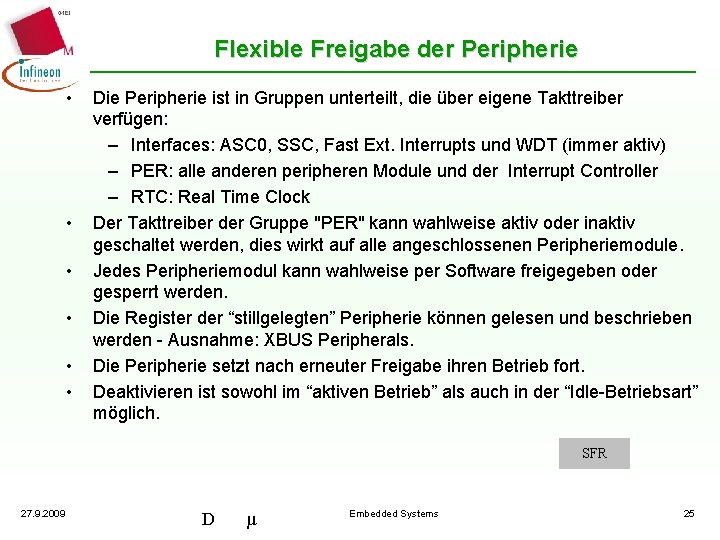

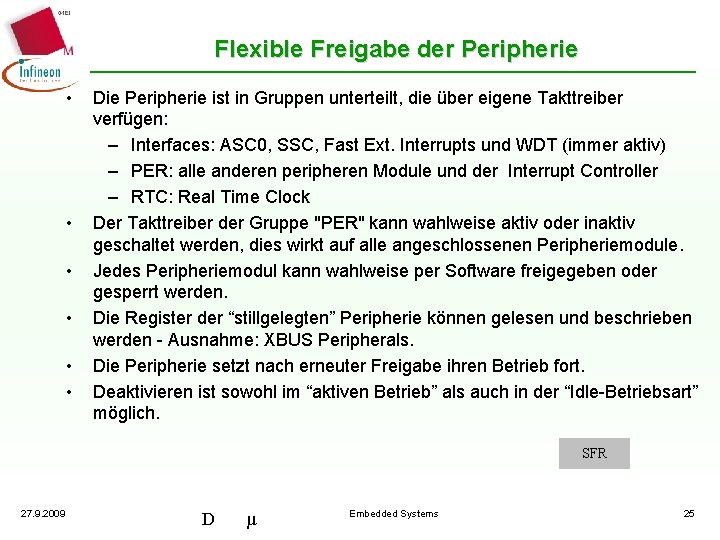

Flexible Freigabe der Peripherie • • • Die Peripherie ist in Gruppen unterteilt, die über eigene Takttreiber verfügen: – Interfaces: ASC 0, SSC, Fast Ext. Interrupts und WDT (immer aktiv) – PER: alle anderen peripheren Module und der Interrupt Controller – RTC: Real Time Clock Der Takttreiber der Gruppe "PER" kann wahlweise aktiv oder inaktiv geschaltet werden, dies wirkt auf alle angeschlossenen Peripheriemodule. Jedes Peripheriemodul kann wahlweise per Software freigegeben oder gesperrt werden. Die Register der “stillgelegten” Peripherie können gelesen und beschrieben werden - Ausnahme: XBUS Peripherals. Die Peripherie setzt nach erneuter Freigabe ihren Betrieb fort. Deaktivieren ist sowohl im “aktiven Betrieb” als auch in der “Idle-Betriebsart” möglich. SFR 27. 9. 2009 D µ Embedded Systems 25

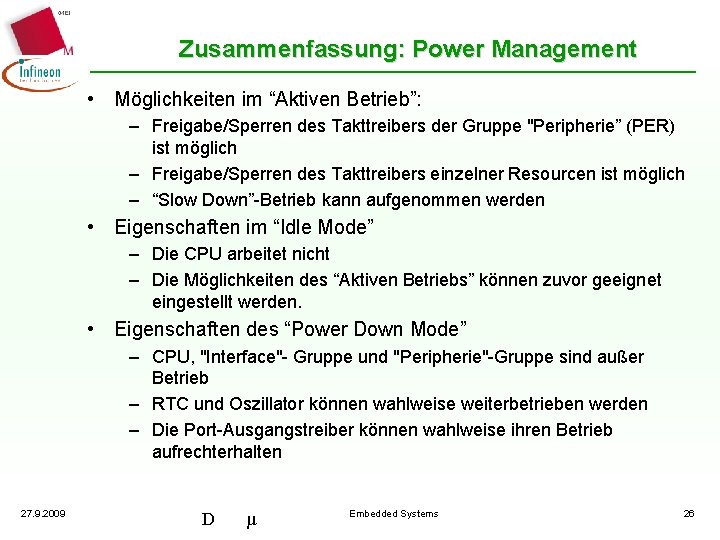

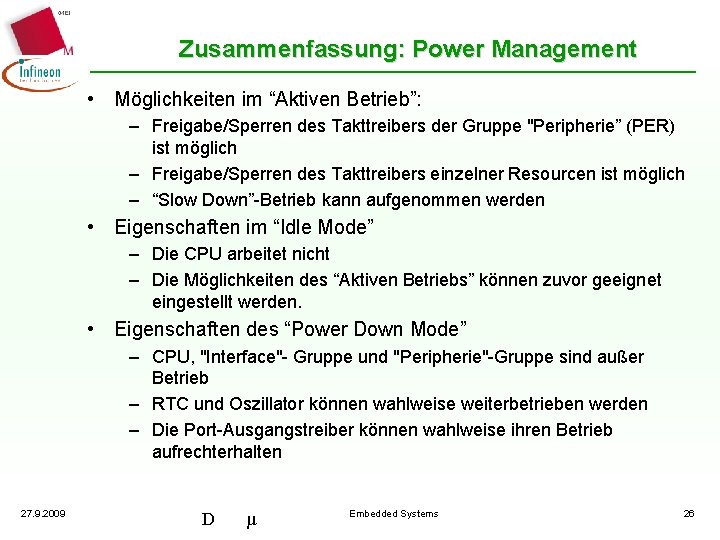

Zusammenfassung: Power Management • Möglichkeiten im “Aktiven Betrieb”: – Freigabe/Sperren des Takttreibers der Gruppe "Peripherie” (PER) ist möglich – Freigabe/Sperren des Takttreibers einzelner Resourcen ist möglich – “Slow Down”-Betrieb kann aufgenommen werden • Eigenschaften im “Idle Mode” – Die CPU arbeitet nicht – Die Möglichkeiten des “Aktiven Betriebs” können zuvor geeignet eingestellt werden. • Eigenschaften des “Power Down Mode” – CPU, "Interface"- Gruppe und "Peripherie"-Gruppe sind außer Betrieb – RTC und Oszillator können wahlweise weiterbetrieben werden – Die Port-Ausgangstreiber können wahlweise ihren Betrieb aufrechterhalten 27. 9. 2009 D µ Embedded Systems 26

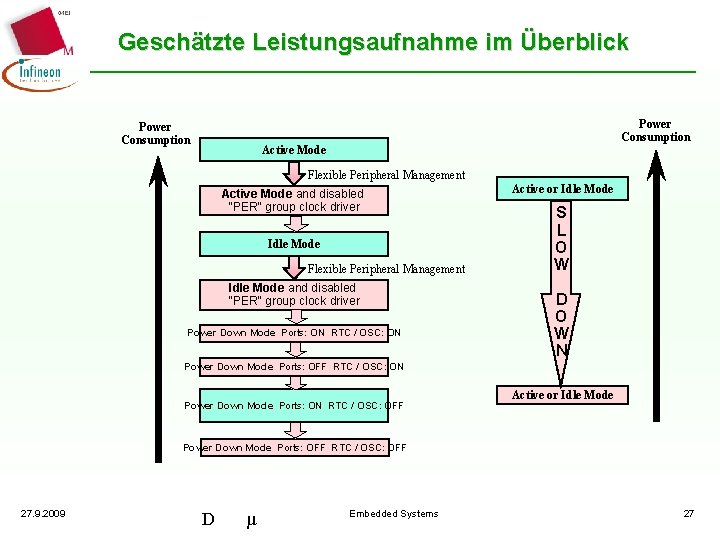

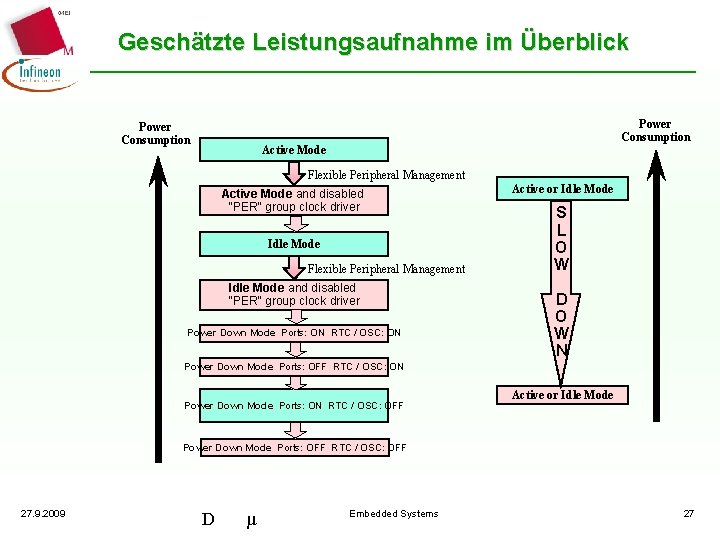

Geschätzte Leistungsaufnahme im Überblick Power Consumption Active Mode Flexible Peripheral Management Active Mode and disabled "PER" group clock driver Idle Mode Flexible Peripheral Management Idle Mode and disabled "PER" group clock driver Power Down Mode Ports: ON RTC / OSC: ON Active or Idle Mode S L O W D O W N Power Down Mode Ports: OFF RTC / OSC: ON Power Down Mode Ports: ON RTC / OSC: OFF Active or Idle Mode Power Down Mode Ports: OFF RTC / OSC: OFF 27. 9. 2009 D µ Embedded Systems 27

C 164 CI - Die Peripherie C 166 -Core Data (C 164 CI-8 RM) or OTP CPU Instr. /Data 32 Data 16 Dual Port 64 K ROM 16 RAM 2 KByte (C 164 CI-8 EM) PLL-Oscillator prog. Multiplier: Watchdog 0. 5; 1; 1. 5; 2; 2. 5; 3; 4; 5 Interrupt Controller RTC 13 ext. IR 16 Interrupt Bus Peripheral Data 16 Port 4 BRG T 4 Port 3 Port 5 Timer 13 8/16 bit MUX only & XBUS Control 10 -Bit USART Sync. GPT 1 CAPCOM 2 CAPCOM 6 Unit for PWM Generation Channel ADC T 2 (SPI) 8 -Channels ASC SSC T 3 Timer 8 External Bus Timer 7 16 XBUS (16 -bit NON MUX Data / Addresses) P 4. 6/ CAN Tx. D Full-CAN Interface V 2. 0 B active Port 0 P 4. 5/ CAN Rx. D PEC External Instr. /Data 1 Comp. Channel Port 8 Port 1 6 8 27. 9. 2009 D µ 9 Embedded Systems 4 3/6 CAPCOM Channels 16

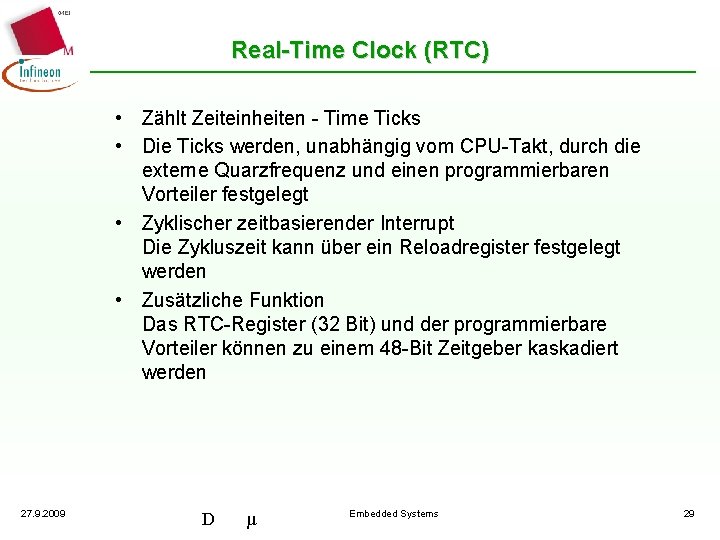

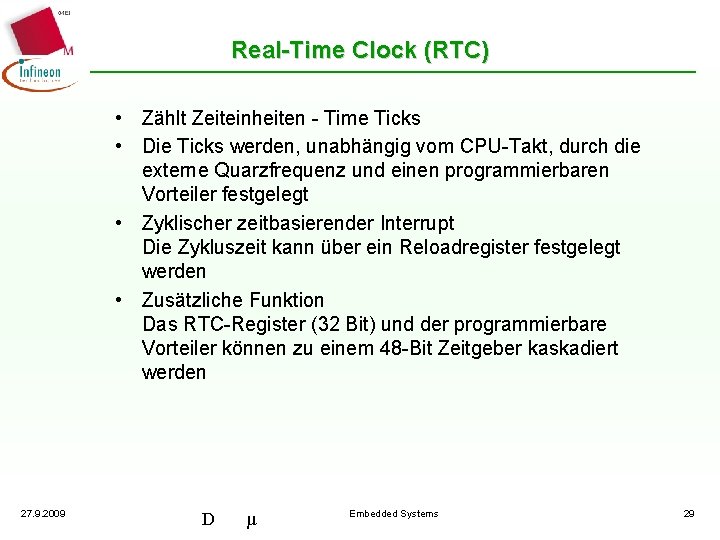

Real-Time Clock (RTC) • Zählt Zeiteinheiten - Time Ticks • Die Ticks werden, unabhängig vom CPU-Takt, durch die externe Quarzfrequenz und einen programmierbaren Vorteiler festgelegt • Zyklischer zeitbasierender Interrupt Die Zykluszeit kann über ein Reloadregister festgelegt werden • Zusätzliche Funktion Das RTC-Register (32 Bit) und der programmierbare Vorteiler können zu einem 48 -Bit Zeitgeber kaskadiert werden 27. 9. 2009 D µ Embedded Systems 29

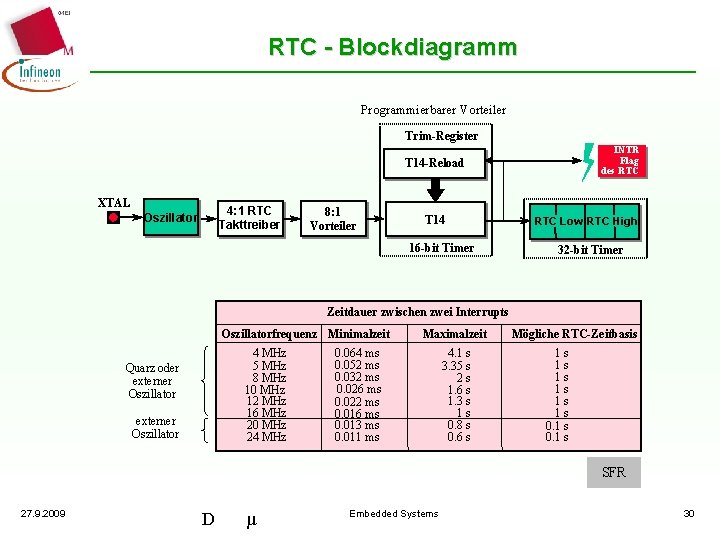

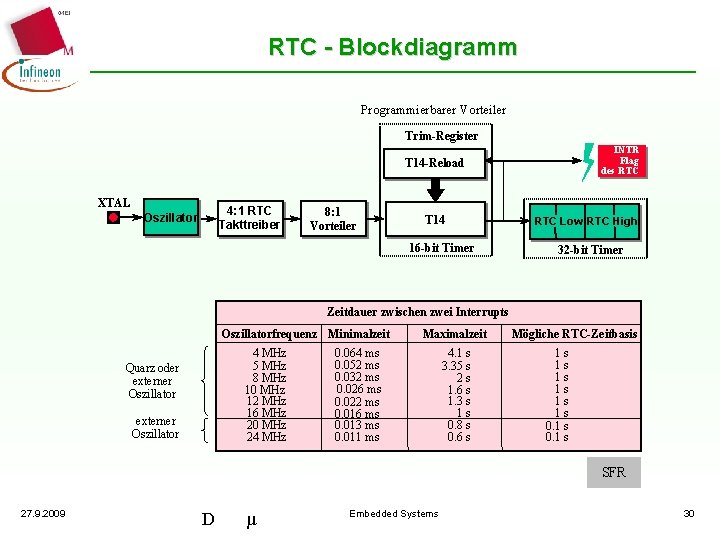

RTC - Blockdiagramm Programmierbarer Vorteiler Trim-Register INTR Flag des RTC T 14 -Reload XTAL 4: 1 RTC Takttreiber Oszillator 8: 1 Vorteiler T 14 16 -bit Timer RTC Low RTC High 32 -bit Timer Zeitdauer zwischen zwei Interrupts Oszillatorfrequenz Minimalzeit 4 MHz 5 MHz 8 MHz 10 MHz 12 MHz 16 MHz 20 MHz 24 MHz Quarz oder externer Oszillator Maximalzeit 0. 064 ms 0. 052 ms 0. 032 ms 0. 026 ms 0. 022 ms 0. 016 ms 0. 013 ms 0. 011 ms 4. 1 s 3. 35 s 2 s 1. 6 s 1. 3 s 1 s 0. 8 s 0. 6 s Mögliche RTC-Zeitbasis 1 s 1 s 1 s 0. 1 s SFR 27. 9. 2009 D µ Embedded Systems 30

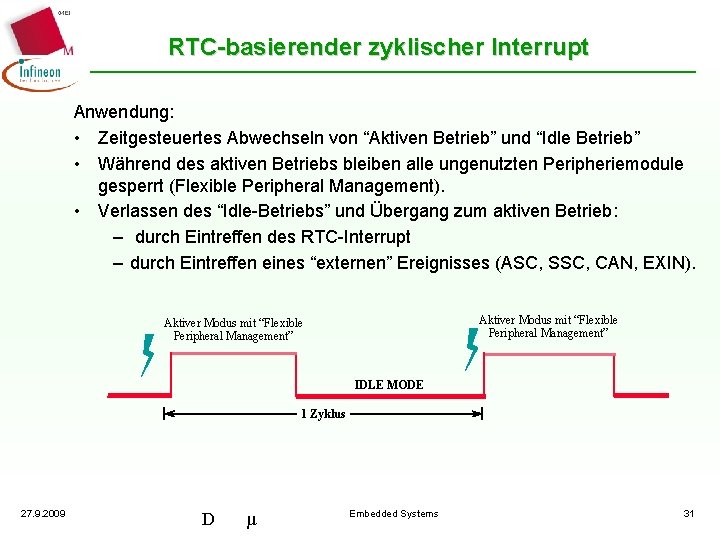

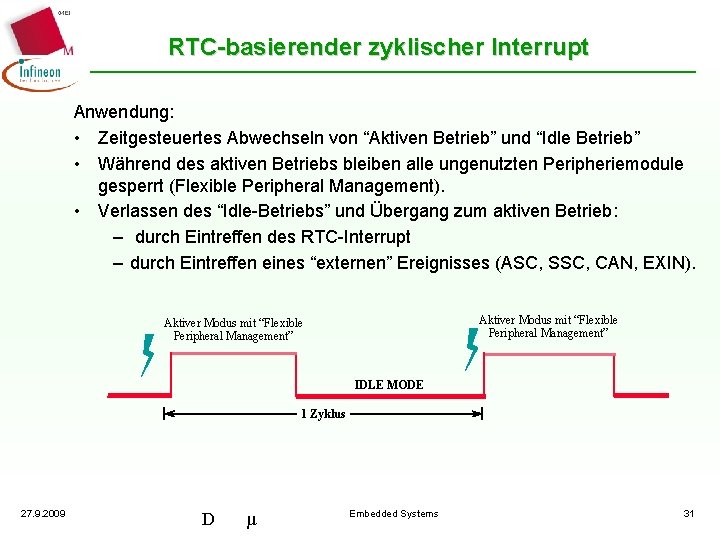

RTC-basierender zyklischer Interrupt Anwendung: • Zeitgesteuertes Abwechseln von “Aktiven Betrieb” und “Idle Betrieb” • Während des aktiven Betriebs bleiben alle ungenutzten Peripheriemodule gesperrt (Flexible Peripheral Management). • Verlassen des “Idle-Betriebs” und Übergang zum aktiven Betrieb: – durch Eintreffen des RTC-Interrupt – durch Eintreffen eines “externen” Ereignisses (ASC, SSC, CAN, EXIN). Aktiver Modus mit “Flexible Peripheral Management” IDLE MODE 1 Zyklus 27. 9. 2009 D µ Embedded Systems 31

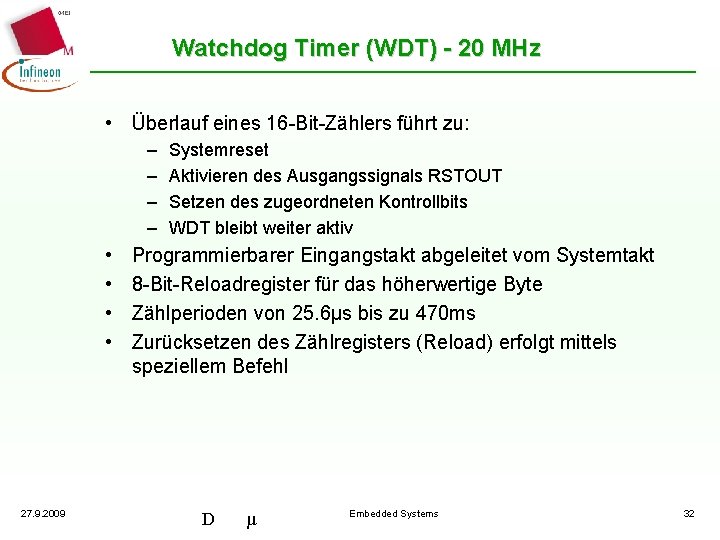

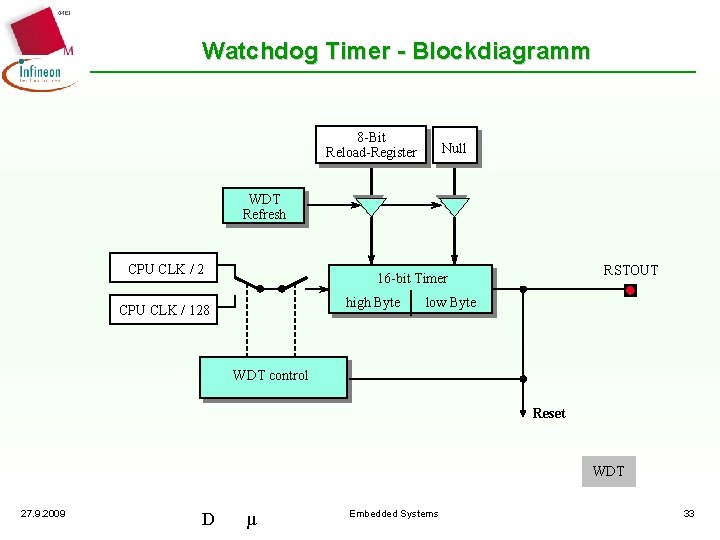

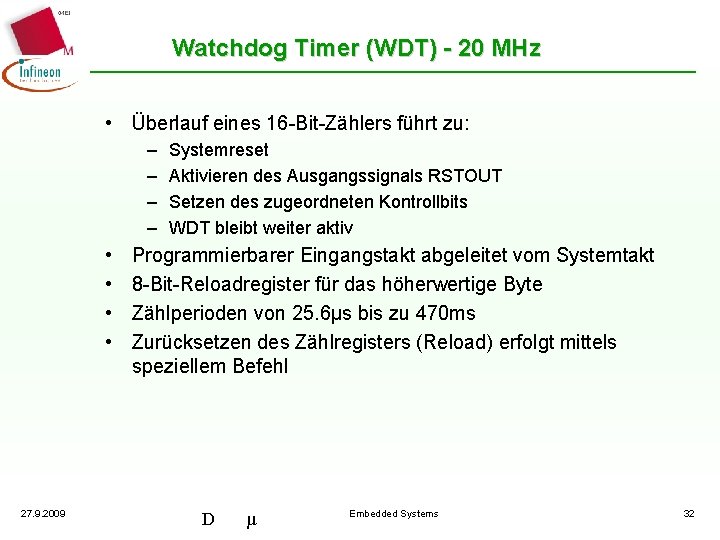

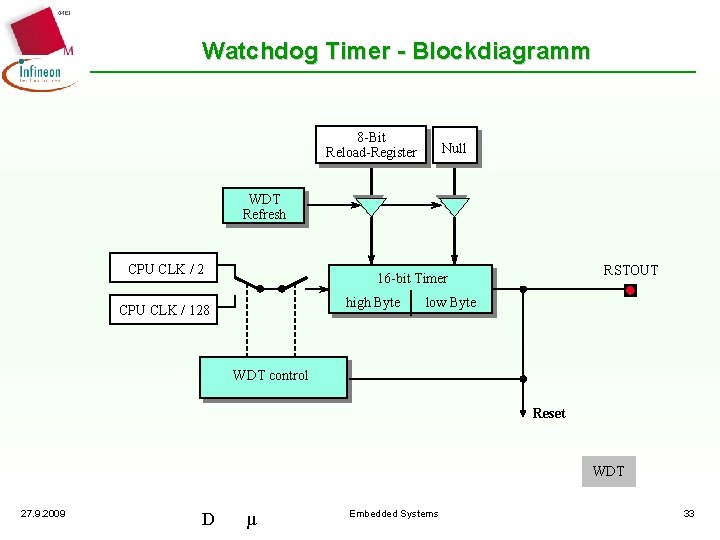

Watchdog Timer (WDT) - 20 MHz • Überlauf eines 16 -Bit-Zählers führt zu: – – • • 27. 9. 2009 Systemreset Aktivieren des Ausgangssignals RSTOUT Setzen des zugeordneten Kontrollbits WDT bleibt weiter aktiv Programmierbarer Eingangstakt abgeleitet vom Systemtakt 8 -Bit-Reloadregister für das höherwertige Byte Zählperioden von 25. 6µs bis zu 470 ms Zurücksetzen des Zählregisters (Reload) erfolgt mittels speziellem Befehl D µ Embedded Systems 32

Watchdog Timer - Blockdiagramm 8 -Bit Reload-Register Null WDT Refresh CPU CLK / 2 RSTOUT 16 -bit Timer high Byte CPU CLK / 128 low Byte WDT control Reset WDT 27. 9. 2009 D µ Embedded Systems 33

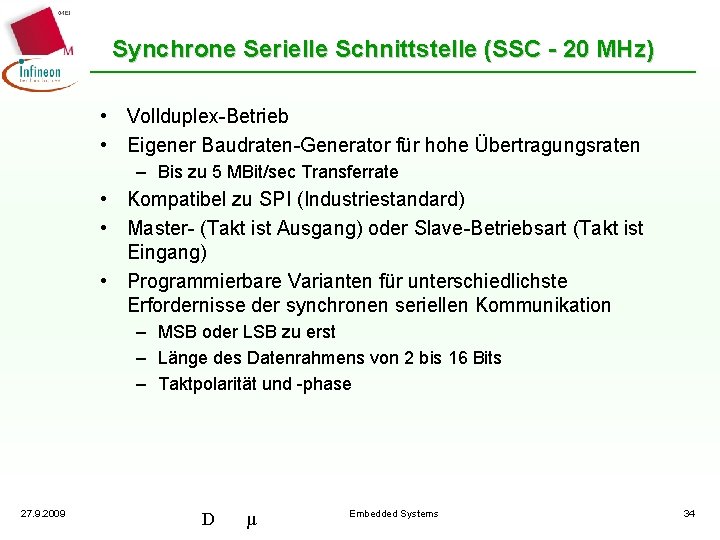

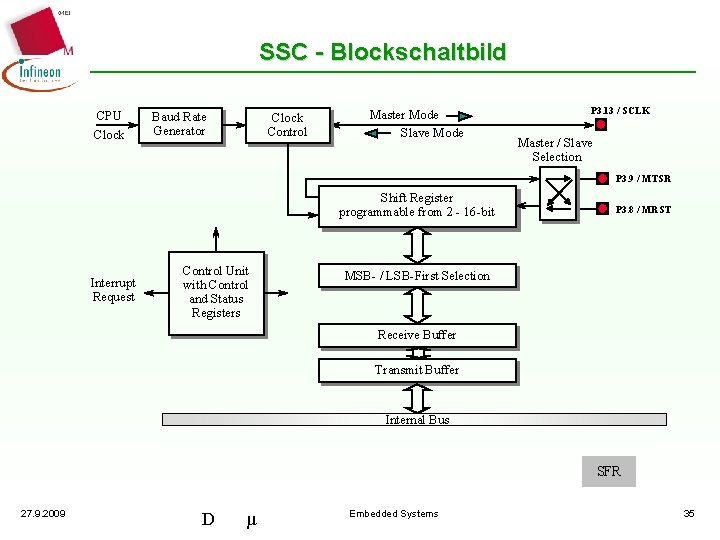

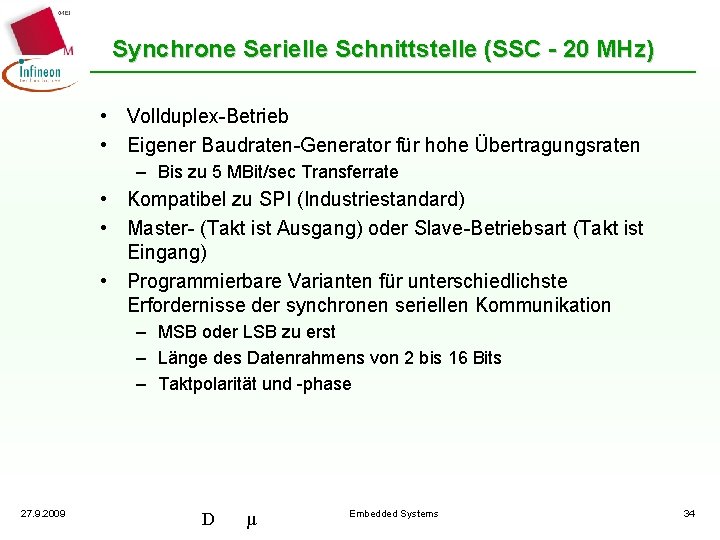

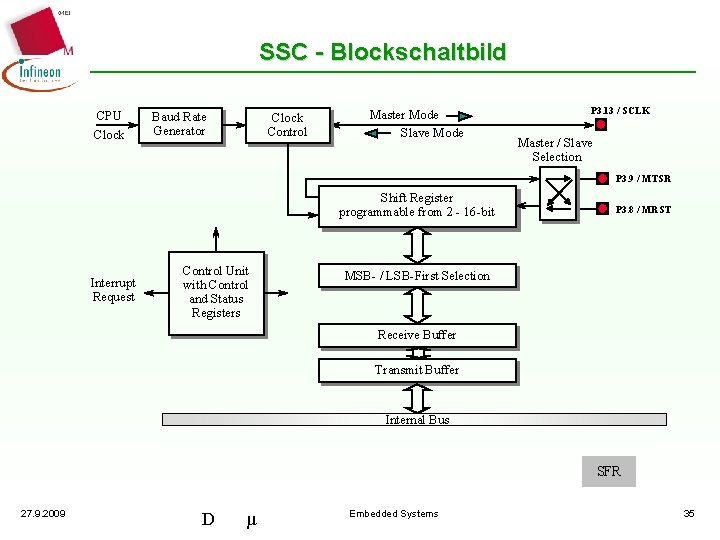

Synchrone Serielle Schnittstelle (SSC - 20 MHz) • Vollduplex-Betrieb • Eigener Baudraten-Generator für hohe Übertragungsraten – Bis zu 5 MBit/sec Transferrate • Kompatibel zu SPI (Industriestandard) • Master- (Takt ist Ausgang) oder Slave-Betriebsart (Takt ist Eingang) • Programmierbare Varianten für unterschiedlichste Erfordernisse der synchronen seriellen Kommunikation – MSB oder LSB zu erst – Länge des Datenrahmens von 2 bis 16 Bits – Taktpolarität und -phase 27. 9. 2009 D µ Embedded Systems 34

SSC - Blockschaltbild CPU Clock Baud Rate Generator Clock Control Master Mode Slave Mode P 3. 13 / SCLK Master / Slave Selection P 3. 9 / MTSR Shift Register programmable from 2 - 16 -bit Interrupt Request Control Unit with Control and Status Registers P 3. 8 / MRST MSB- / LSB-First Selection Receive Buffer Transmit Buffer Internal Bus SFR 27. 9. 2009 D µ Embedded Systems 35

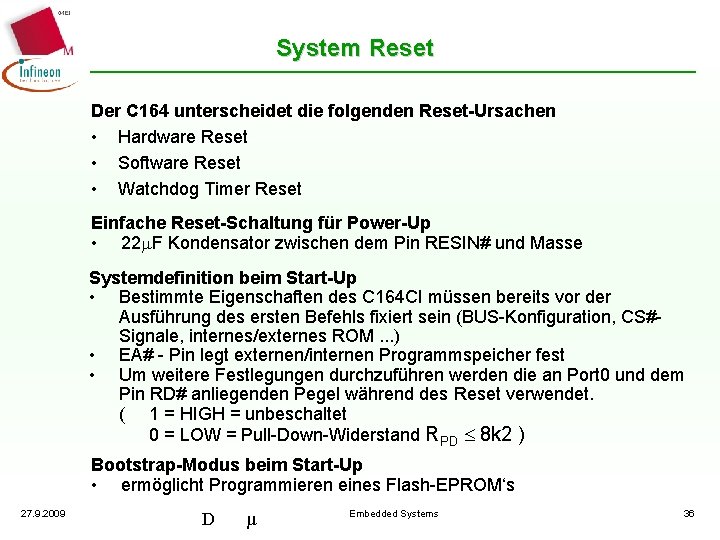

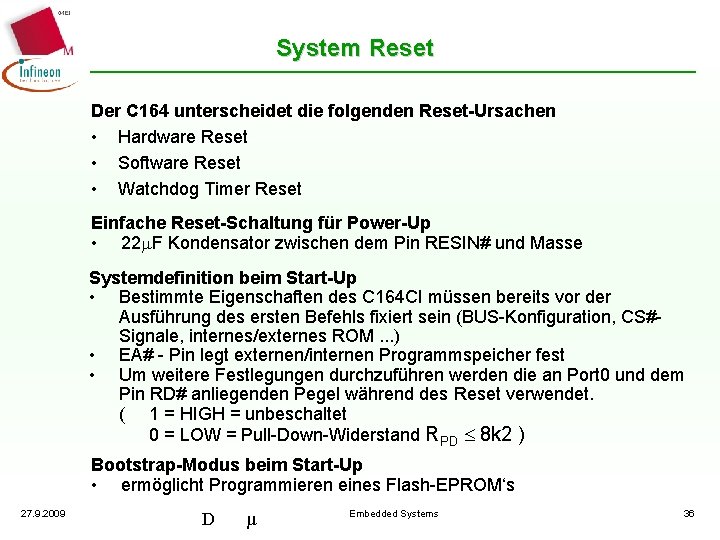

System Reset Der C 164 unterscheidet die folgenden Reset-Ursachen • Hardware Reset • Software Reset • Watchdog Timer Reset Einfache Reset-Schaltung für Power-Up • 22 F Kondensator zwischen dem Pin RESIN# und Masse Systemdefinition beim Start-Up • Bestimmte Eigenschaften des C 164 CI müssen bereits vor der Ausführung des ersten Befehls fixiert sein (BUS-Konfiguration, CS#Signale, internes/externes ROM. . . ) • EA# - Pin legt externen/internen Programmspeicher fest • Um weitere Festlegungen durchzuführen werden die an Port 0 und dem Pin RD# anliegenden Pegel während des Reset verwendet. ( 1 = HIGH = unbeschaltet 0 = LOW = Pull-Down-Widerstand RPD 8 k 2 ) Bootstrap-Modus beim Start-Up • ermöglicht Programmieren eines Flash-EPROM‘s 27. 9. 2009 D µ Embedded Systems 36

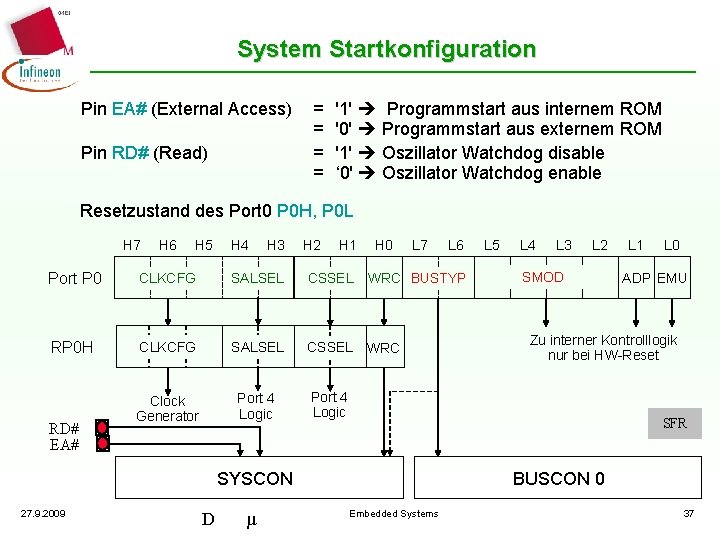

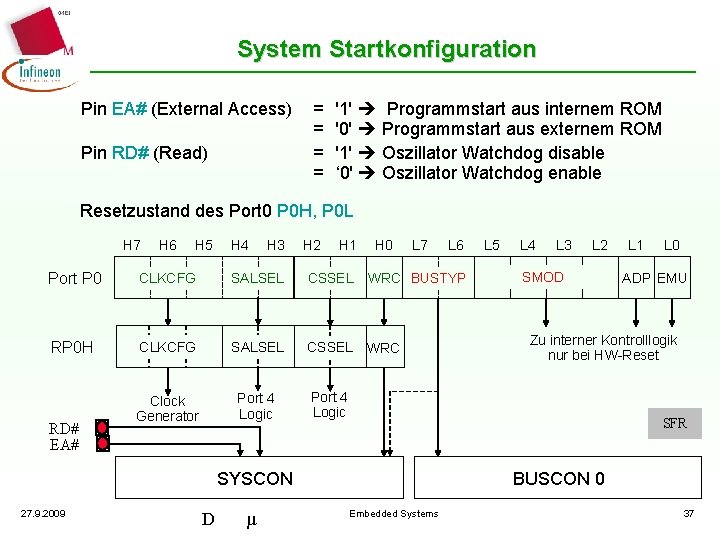

System Startkonfiguration Pin EA# (External Access) Pin RD# (Read) = = '1' Programmstart aus internem ROM '0' Programmstart aus externem ROM '1' Oszillator Watchdog disable ‘ 0' Oszillator Watchdog enable Resetzustand des Port 0 P 0 H, P 0 L H 7 H 6 H 5 H 4 H 3 H 2 H 1 H 0 L 7 L 6 Port P 0 CLKCFG SALSEL CSSEL WRC BUSTYP RP 0 H CLKCFG SALSEL CSSEL WRC Clock Generator Port 4 Logic RD# EA# D µ L 4 L 3 L 2 SMOD L 1 L 0 ADP EMU Zu interner Kontrolllogik nur bei HW-Reset SFR SYSCON 27. 9. 2009 L 5 BUSCON 0 Embedded Systems 37

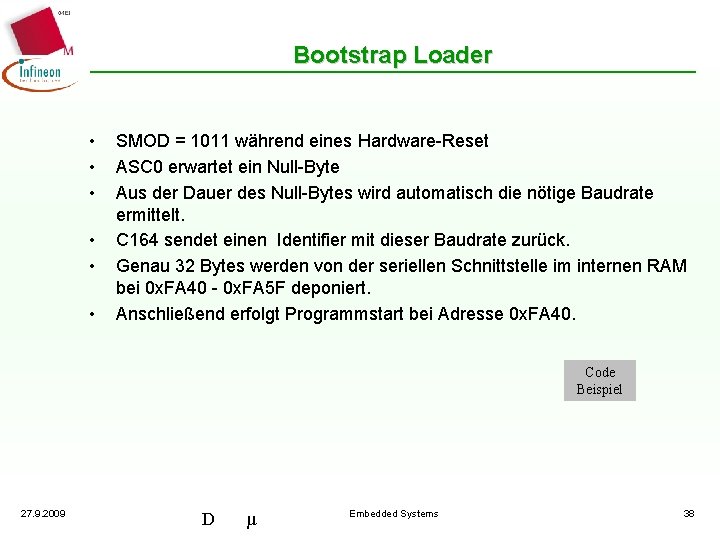

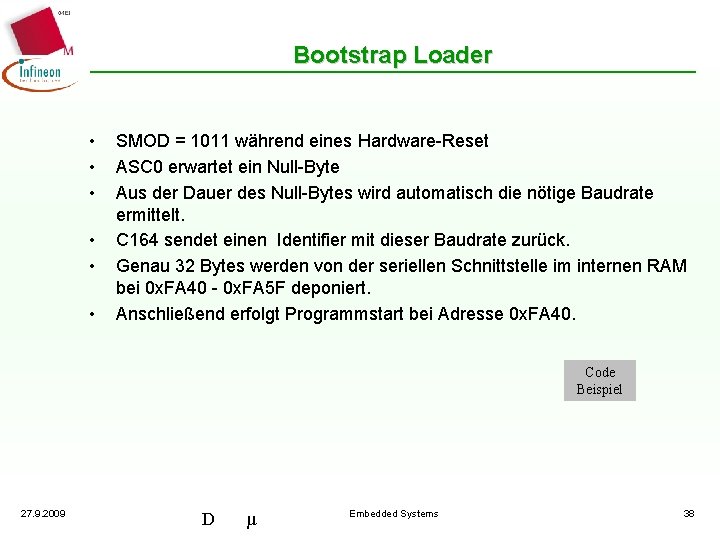

Bootstrap Loader • • • SMOD = 1011 während eines Hardware-Reset ASC 0 erwartet ein Null-Byte Aus der Dauer des Null-Bytes wird automatisch die nötige Baudrate ermittelt. C 164 sendet einen Identifier mit dieser Baudrate zurück. Genau 32 Bytes werden von der seriellen Schnittstelle im internen RAM bei 0 x. FA 40 - 0 x. FA 5 F deponiert. Anschließend erfolgt Programmstart bei Adresse 0 x. FA 40. Code Beispiel 27. 9. 2009 D µ Embedded Systems 38