VHDL library IEEE use IEEE STDLOGIC1164 ALL use

VHDL – 입출력 선언 § § library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; § § § § entity rc_ro_vhdl is Port ( RSTB : in STD_LOGIC; CLK_4 M : in STD_LOGIC; RF_DATA : in STD_LOGIC_VECTOR (2 downto 0); MTL_A : out STD_LOGIC; MTL_B : out STD_LOGIC; MTL_n. A : out STD_LOGIC; MTL_n. B : out STD_LOGIC; MTR_A : out STD_LOGIC; MTR_B : out STD_LOGIC; MTR_n. A : out STD_LOGIC; MTR_n. B : out STD_LOGIC); end rc_ro_vhdl; // 시스템 Reset 신호 // 4 MHz 클럭 신호 // 무선 통신 송신기 // 좌 모터 출력신호 // 우 모터 출력신호 시스템 분석 및 설계 TU

VHDL – 변수 선언 § architecture Behavioral of rc_ro_vhdl is § signal forward : std_logic; § § § signal signal signal 호 signal // ‘ 1’이면 전진, ‘ 0’이면 후진 mtl_speed : std_logic_vector (1 downto 0); mtr_speed : std_logic_vector (1 downto 0); speed_l : integer range 0 to 25000; speed_r : integer range 0 to 25000; motor_lcnt : integer range 0 to 25000; phase_lclk : std_logic; motor_rcnt : integer range 0 to 25000; phase_rclk : std_logic; phase_lcnt : std_logic_vector (1 downto 0); // 4개의 (좌)스텝 구분을 위한 신호 phase_lout : std_logic_vector (3 downto 0); // 좌 스텝 모터의 출력 신호 묶음 phase_rcnt : std_logic_vector (1 downto 0); // 4개의 (우)스텝 구분을 위한 신 phase_rout : std_logic_vector (3 downto 0); // 우 스텝 모터의 출력 신호 묶음 § begin 시스템 분석 및 설계 TU

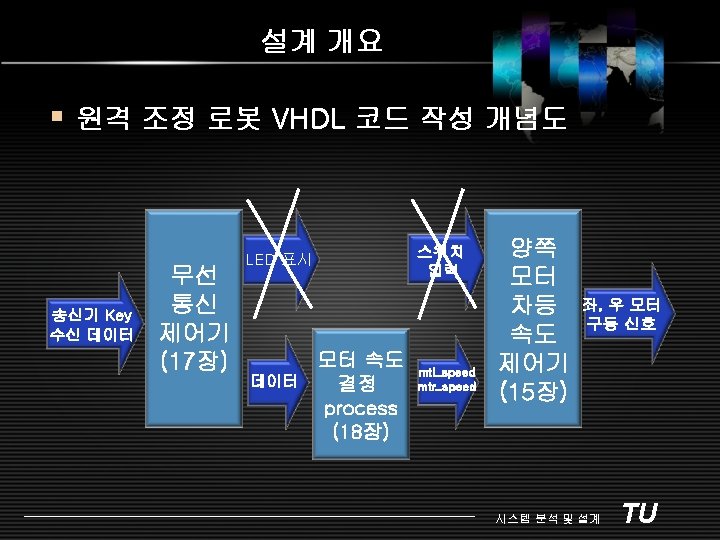

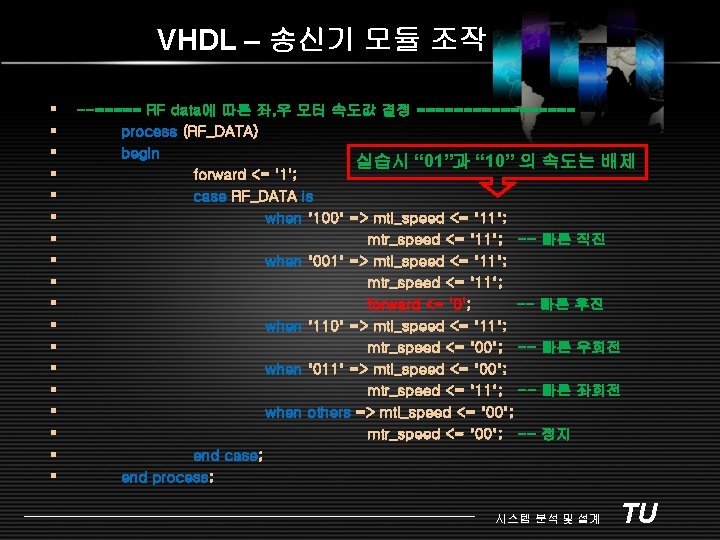

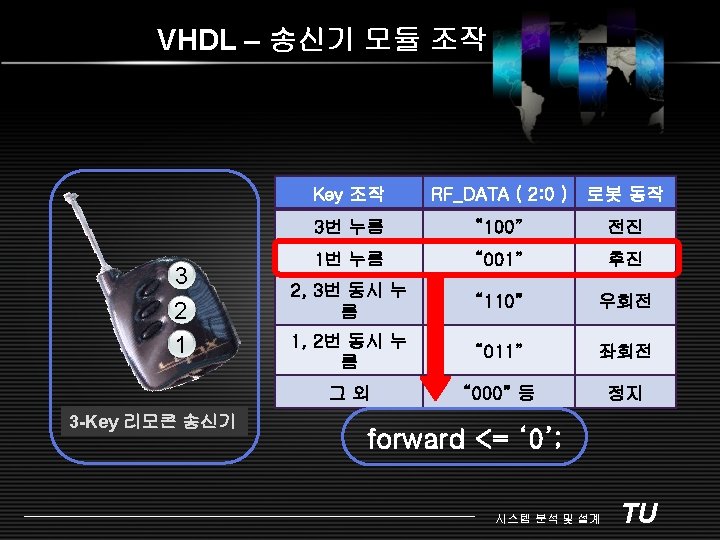

VHDL – 송신기 모듈 조작 § § § § § --===== RF data에 따른 좌, 우 모터 속도값 결정 ========= process (RF_DATA) begin 실습시 “ 01”과 “ 10” 의 속도는 배제 forward <= '1'; case RF_DATA is when "100" => mtl_speed <= "11"; mtr_speed <= "11"; -- 빠른 직진 when "001" => mtl_speed <= "11"; mtr_speed <= "11"; forward <= '0'; -- 빠른 후진 when "110" => mtl_speed <= "11"; mtr_speed <= "00"; -- 빠른 우회전 when "011" => mtl_speed <= "00"; mtr_speed <= "11"; -- 빠른 좌회전 when others => mtl_speed <= "00"; mtr_speed <= "00"; -- 정지 end case; end process; 시스템 분석 및 설계 TU

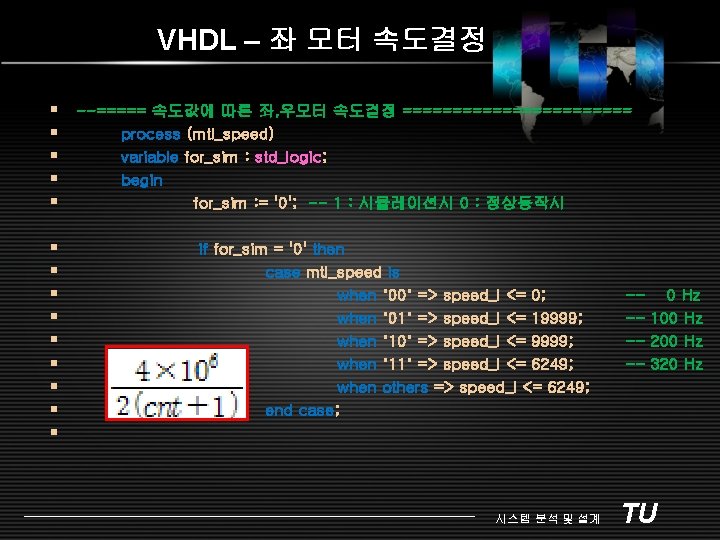

VHDL – 좌 모터 속도결정 § --===== 속도값에 따른 좌, 우모터 속도결정 ============ § process (mtl_speed) § variable for_sim : std_logic; § begin § for_sim : = '0'; -- 1 : 시뮬레이션시 0 : 정상동작시 § § § § § if for_sim = '0' then case mtl_speed is when "00" => speed_l <= 0; when "01" => speed_l <= 19999; when "10" => speed_l <= 9999; when "11" => speed_l <= 6249; when others => speed_l <= 6249; end case; 시스템 분석 및 설계 -- 0 Hz -- 100 Hz -- 200 Hz -- 320 Hz TU

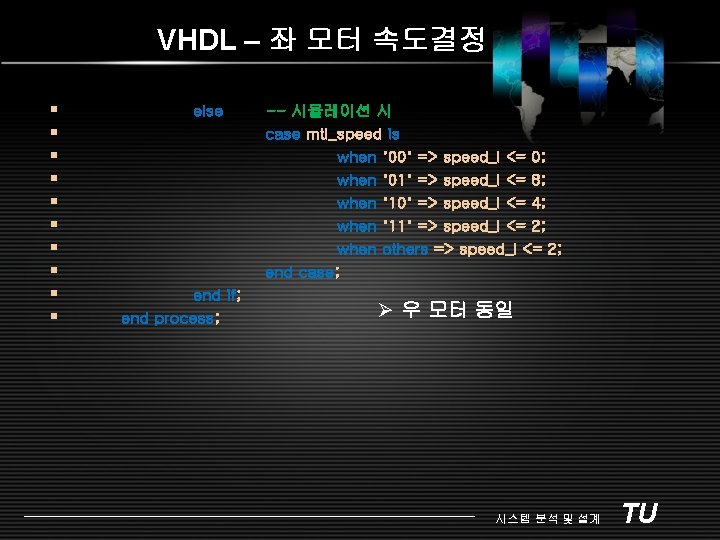

VHDL – 좌 모터 속도결정 § § § § § else end if; end process; -- 시뮬레이션 시 case mtl_speed is when "00" => speed_l <= 0; when "01" => speed_l <= 8; when "10" => speed_l <= 4; when "11" => speed_l <= 2; when others => speed_l <= 2; end case; Ø 우 모터 동일 시스템 분석 및 설계 TU

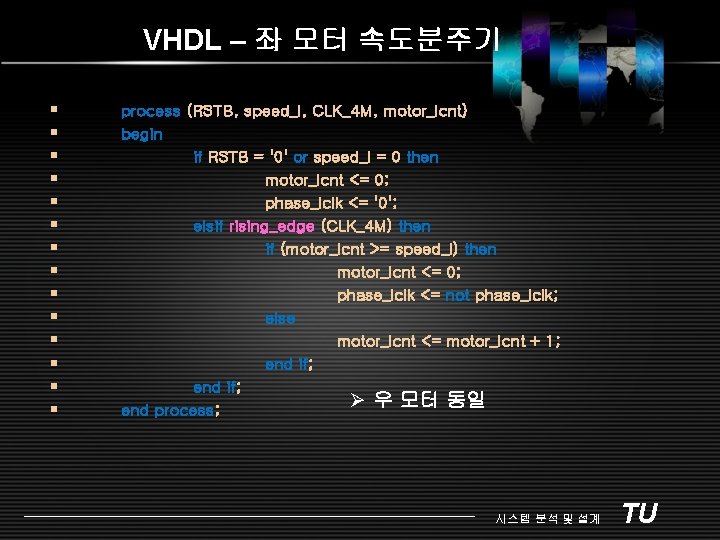

VHDL – 좌 모터 속도분주기 § § § § process (RSTB, speed_l, CLK_4 M, motor_lcnt) begin if RSTB = '0' or speed_l = 0 then motor_lcnt <= 0; phase_lclk <= '0'; elsif rising_edge (CLK_4 M) then if (motor_lcnt >= speed_l) then motor_lcnt <= 0; phase_lclk <= not phase_lclk; else motor_lcnt <= motor_lcnt + 1; end if; Ø 우 모터 동일 end process; 시스템 분석 및 설계 TU

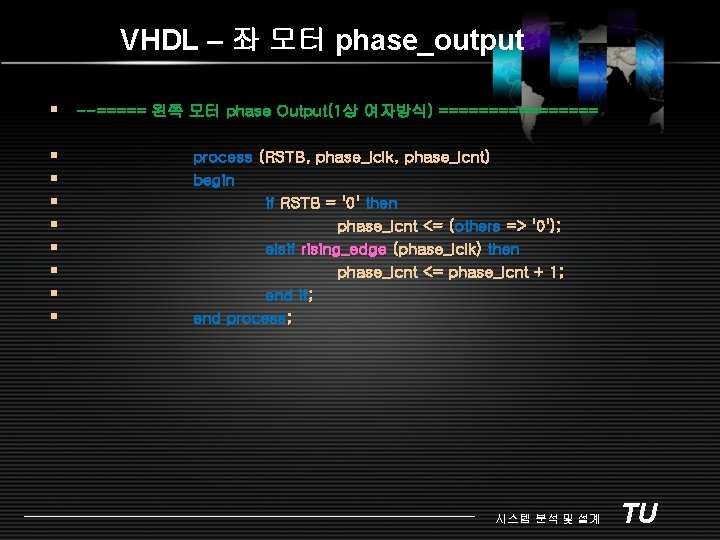

VHDL – 좌 모터 phase_output § --===== 왼쪽 모터 phase Output(1상 여자방식) ======== § § § § process (RSTB, phase_lclk, phase_lcnt) begin if RSTB = '0' then phase_lcnt <= (others => '0'); elsif rising_edge (phase_lclk) then phase_lcnt <= phase_lcnt + 1; end if; end process; 시스템 분석 및 설계 TU

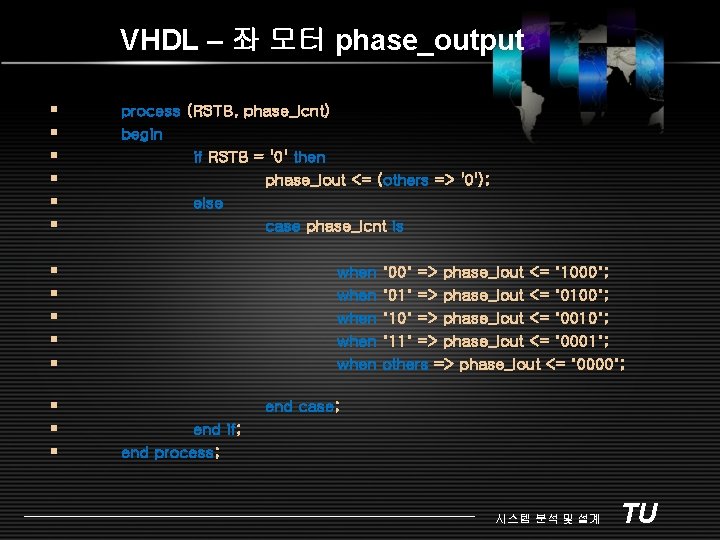

VHDL – 좌 모터 phase_output § § § process (RSTB, phase_lcnt) begin if RSTB = '0' then phase_lout <= (others => '0'); else case phase_lcnt is § § § § when when "00" => phase_lout <= "1000"; "01" => phase_lout <= "0100"; "10" => phase_lout <= "0010"; "11" => phase_lout <= "0001"; others => phase_lout <= "0000"; end case; end if; end process; 시스템 분석 및 설계 TU

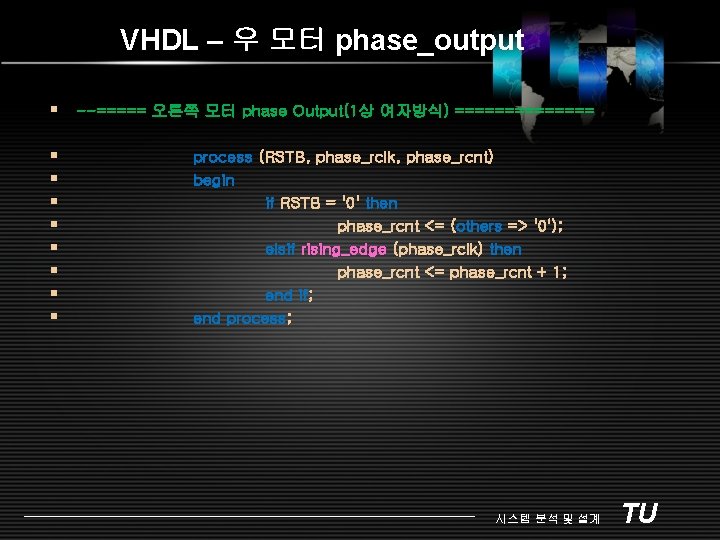

VHDL – 우 모터 phase_output § --===== 오른쪽 모터 phase Output(1상 여자방식) ======= § § § § process (RSTB, phase_rclk, phase_rcnt) begin if RSTB = '0' then phase_rcnt <= (others => '0'); elsif rising_edge (phase_rclk) then phase_rcnt <= phase_rcnt + 1; end if; end process; 시스템 분석 및 설계 TU

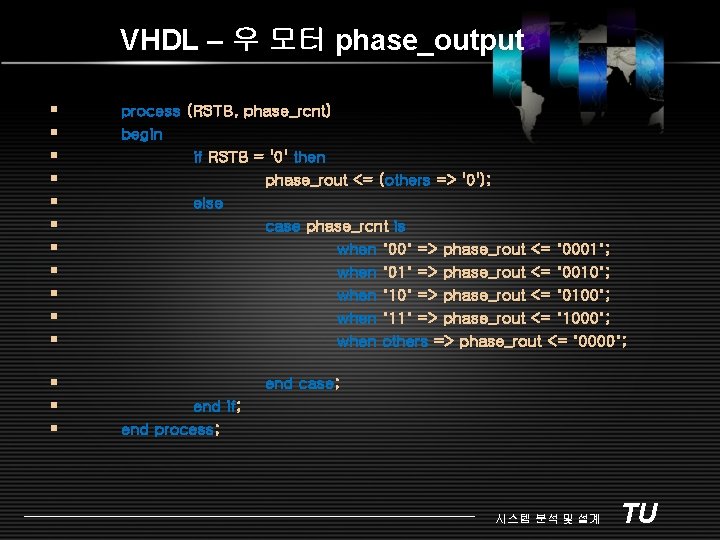

VHDL – 우 모터 phase_output § § § § process (RSTB, phase_rcnt) begin if RSTB = '0' then phase_rout <= (others => '0'); else case phase_rcnt is when "00" => phase_rout <= "0001"; when "01" => phase_rout <= "0010"; when "10" => phase_rout <= "0100"; when "11" => phase_rout <= "1000"; when others => phase_rout <= "0000"; end case; end if; end process; 시스템 분석 및 설계 TU

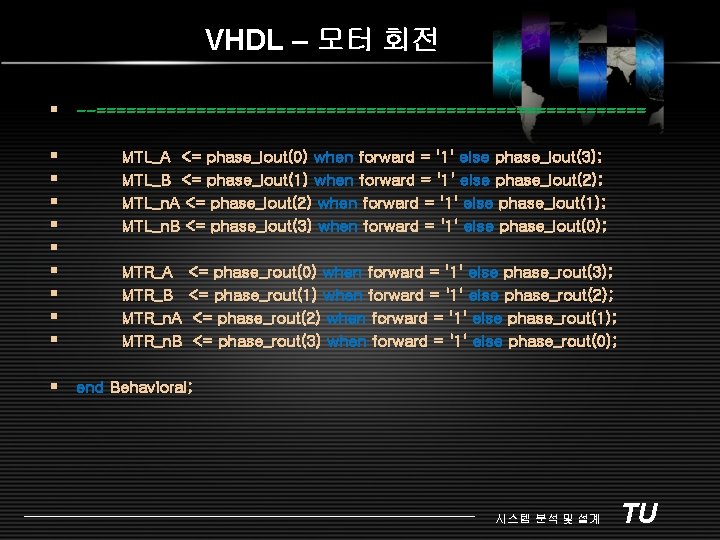

VHDL – 모터 회전 § --============================ § § § § § MTL_A <= phase_lout(0) when forward = '1' else phase_lout(3); MTL_B <= phase_lout(1) when forward = '1' else phase_lout(2); MTL_n. A <= phase_lout(2) when forward = '1' else phase_lout(1); MTL_n. B <= phase_lout(3) when forward = '1' else phase_lout(0); MTR_A MTR_B MTR_n. A MTR_n. B <= phase_rout(0) when forward = '1' else phase_rout(3); <= phase_rout(1) when forward = '1' else phase_rout(2); <= phase_rout(2) when forward = '1' else phase_rout(1); <= phase_rout(3) when forward = '1' else phase_rout(0); § end Behavioral; 시스템 분석 및 설계 TU

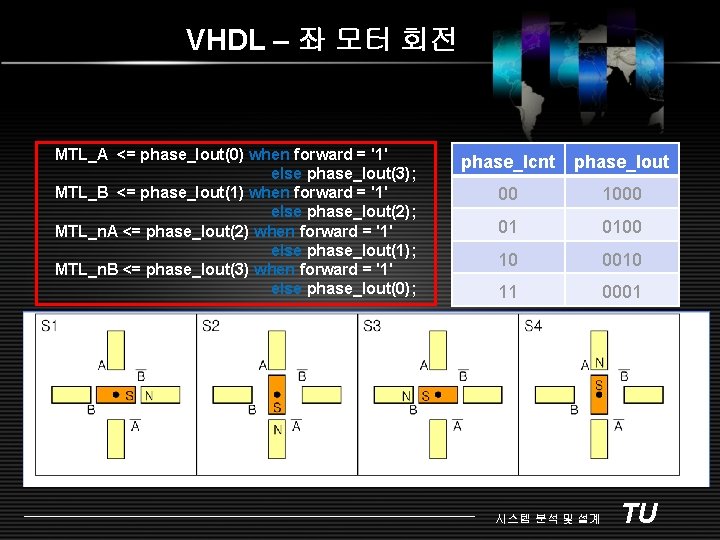

VHDL – 좌 모터 회전 MTL_A <= phase_lout(0) when forward = '1' else phase_lout(3); MTL_B <= phase_lout(1) when forward = '1' else phase_lout(2); MTL_n. A <= phase_lout(2) when forward = '1' else phase_lout(1); MTL_n. B <= phase_lout(3) when forward = '1' else phase_lout(0); phase_lcnt phase_lout 00 1000 01 0100 10 0010 11 0001 시스템 분석 및 설계 TU

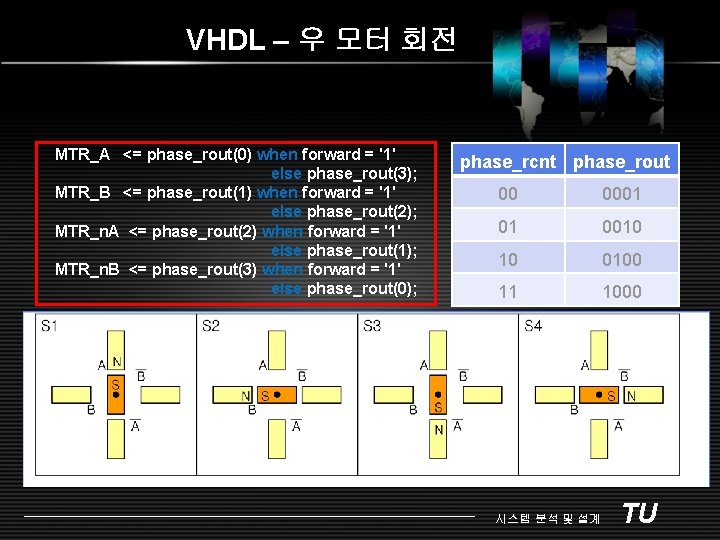

VHDL – 우 모터 회전 MTR_A <= phase_rout(0) when forward = '1' else phase_rout(3); MTR_B <= phase_rout(1) when forward = '1' else phase_rout(2); MTR_n. A <= phase_rout(2) when forward = '1' else phase_rout(1); MTR_n. B <= phase_rout(3) when forward = '1' else phase_rout(0); phase_rcnt phase_rout 00 0001 01 0010 10 0100 11 1000 시스템 분석 및 설계 TU

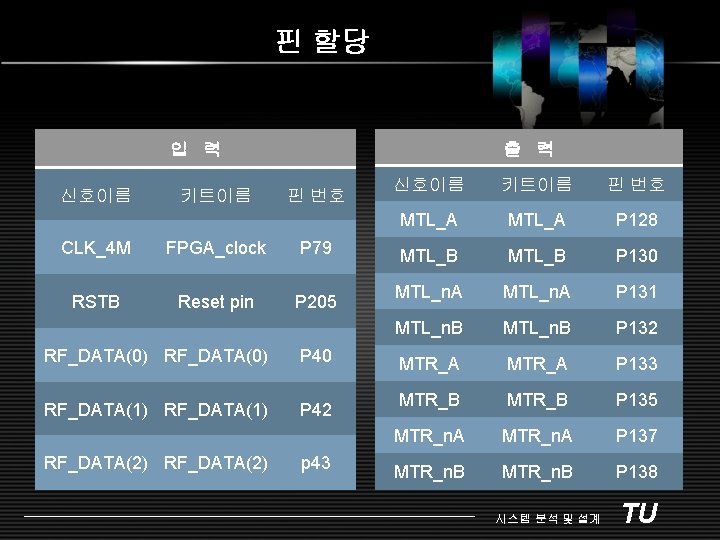

핀 할당 출 력 입 력 신호이름 키트이름 핀 번호 CLK_4 M FPGA_clock P 79 RSTB Reset pin P 205 RF_DATA(0) P 40 RF_DATA(1) P 42 RF_DATA(2) p 43 신호이름 키트이름 핀 번호 MTL_A P 128 MTL_B P 130 MTL_n. A P 131 MTL_n. B P 132 MTR_A P 133 MTR_B P 135 MTR_n. A P 137 MTR_n. B P 138 시스템 분석 및 설계 TU

- Slides: 23