Verilog HDL A solution for Everybody By Anil

Verilog HDL: A solution for Everybody By, Anil Kumar Ram Rakhyani (akram@)

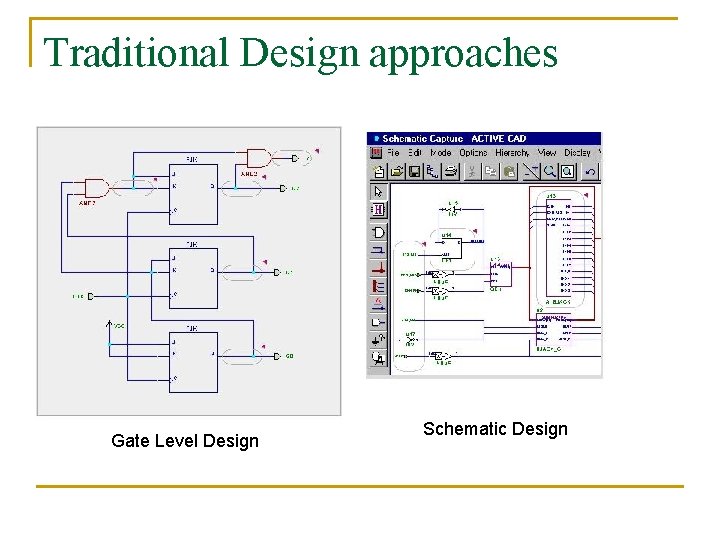

Traditional Design approaches Gate Level Design Schematic Design

Where is the problem? n System specification is behavioral n Manual Translation of design in Boolean equations n Handling of large Complex Designs n Can we still use SPICE for simulating Digital circuits?

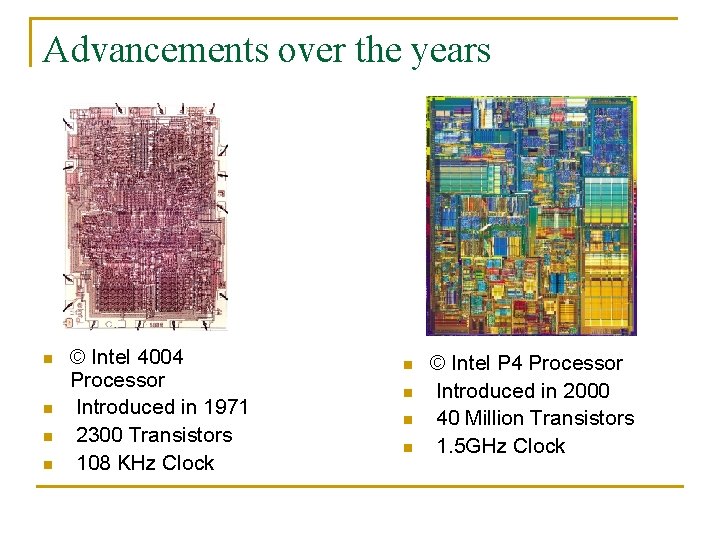

Advancements over the years n n © Intel 4004 Processor Introduced in 1971 2300 Transistors 108 KHz Clock n n © Intel P 4 Processor Introduced in 2000 40 Million Transistors 1. 5 GHz Clock

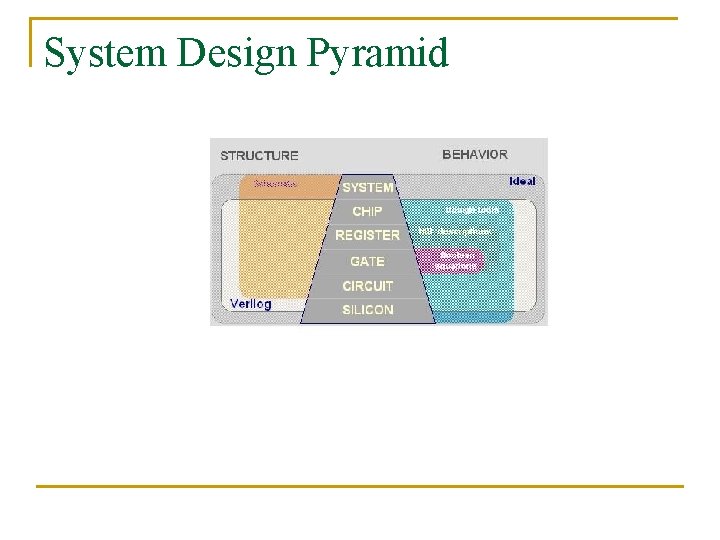

System Design Pyramid

History: n n Need: a simple, intuitive and effective way of describing digital circuits for modeling, simulation and analysis. Developed in 1984 -85 by Philip Moorby In 1990 Cadence opened the language to the public Standardization of language by IEEE in 1995

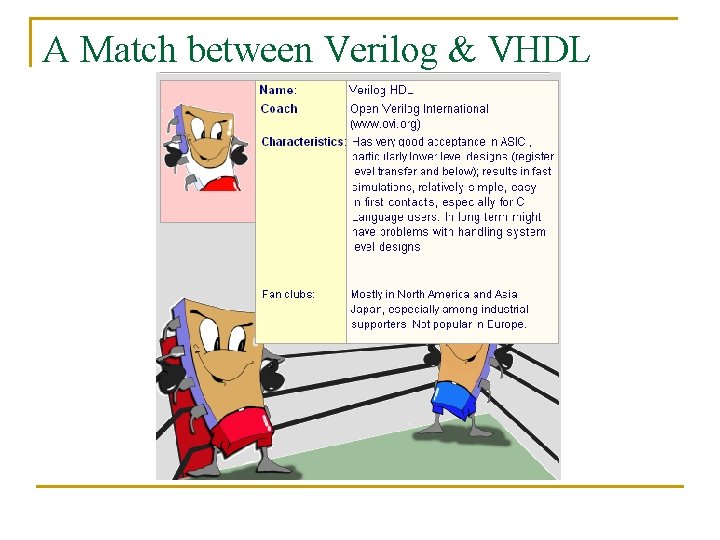

A Match between Verilog & VHDL

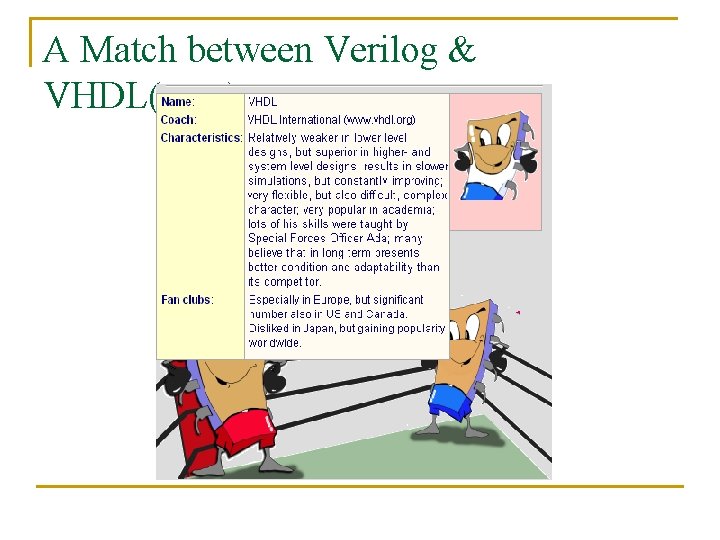

A Match between Verilog & VHDL(con. )

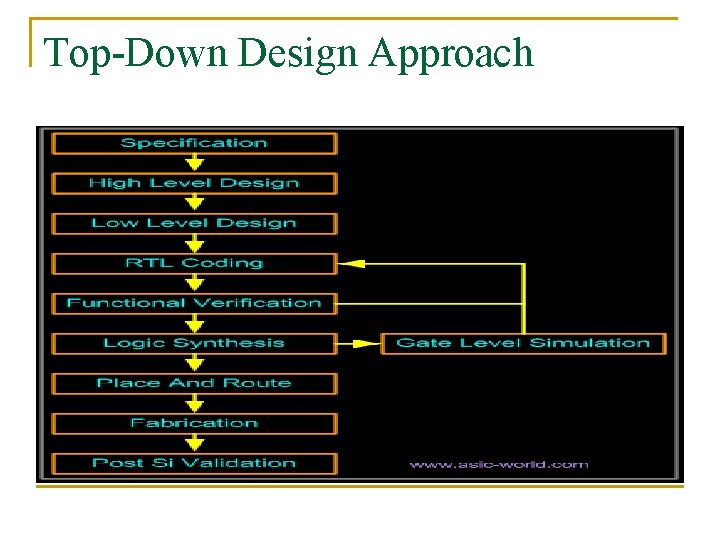

Top-Down Design Approach

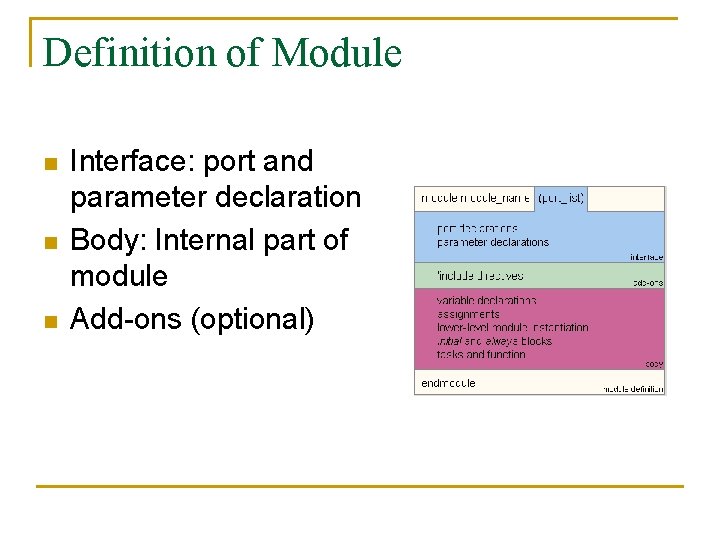

Definition of Module n n n Interface: port and parameter declaration Body: Internal part of module Add-ons (optional)

Some points to remember n The name of Module n Comments in Verilog q q n One line comment (// …………. ) Block Comment (/*……………. */) Description of Module (optional but suggested)

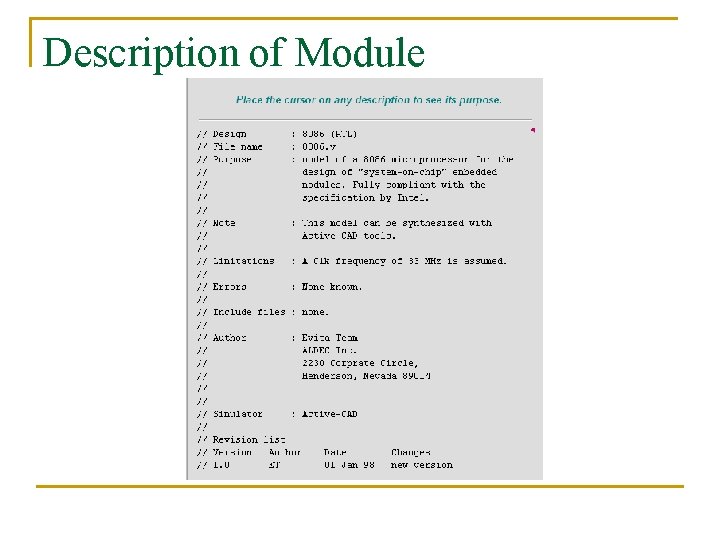

Description of Module

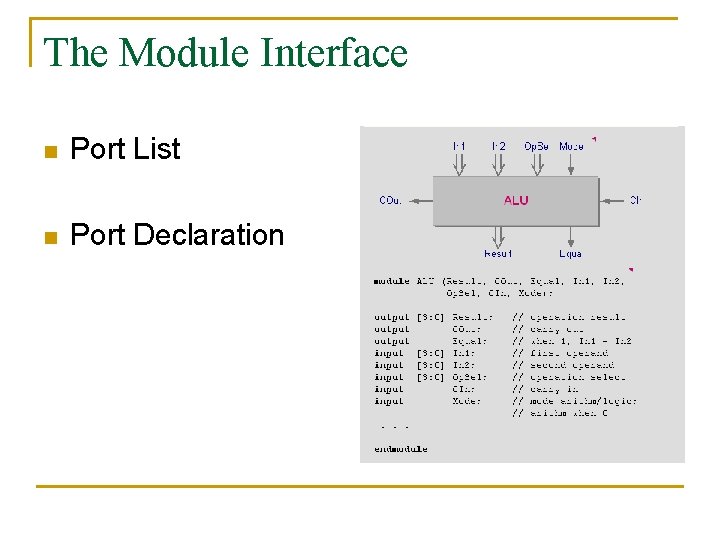

The Module Interface n Port List n Port Declaration

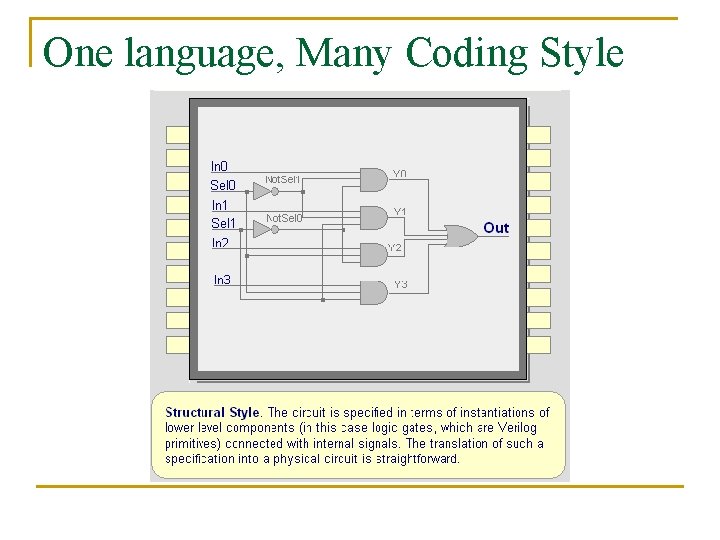

One language, Many Coding Style

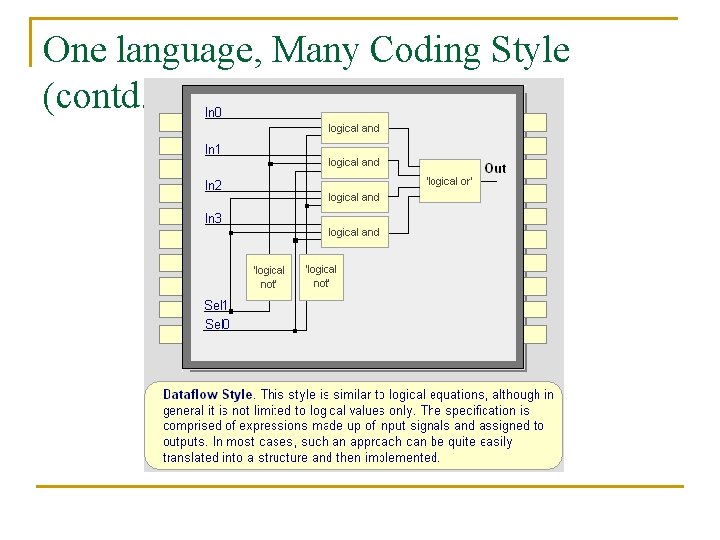

One language, Many Coding Style (contd. )

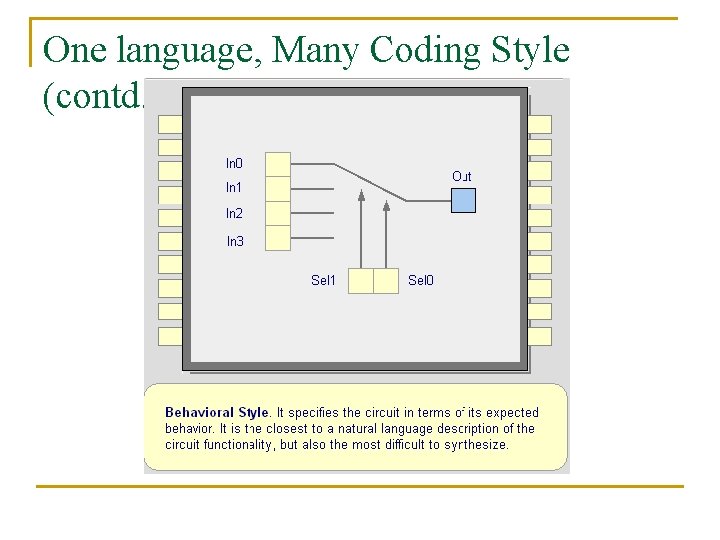

One language, Many Coding Style (contd. )

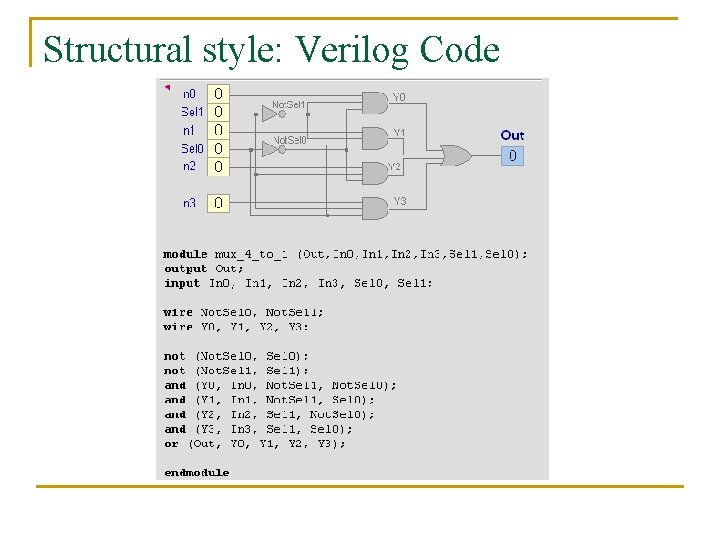

Structural style: Verilog Code

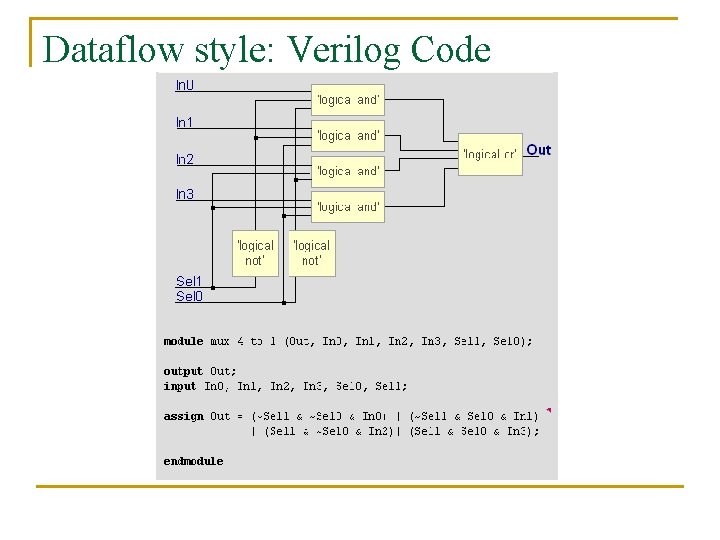

Dataflow style: Verilog Code

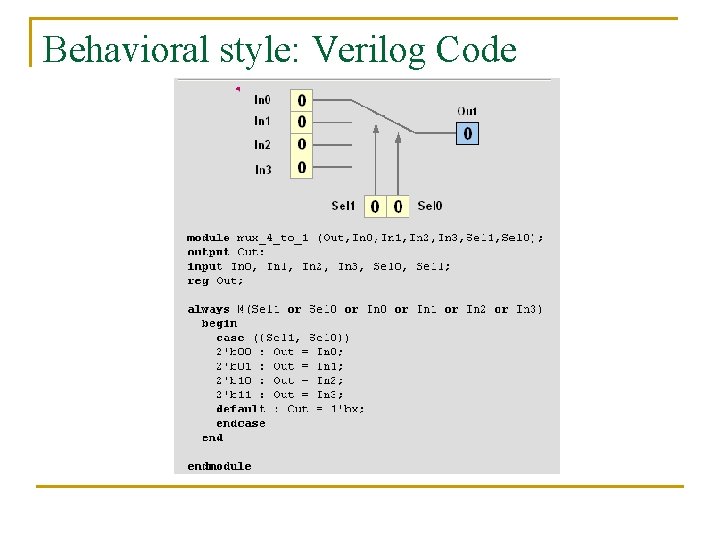

Behavioral style: Verilog Code

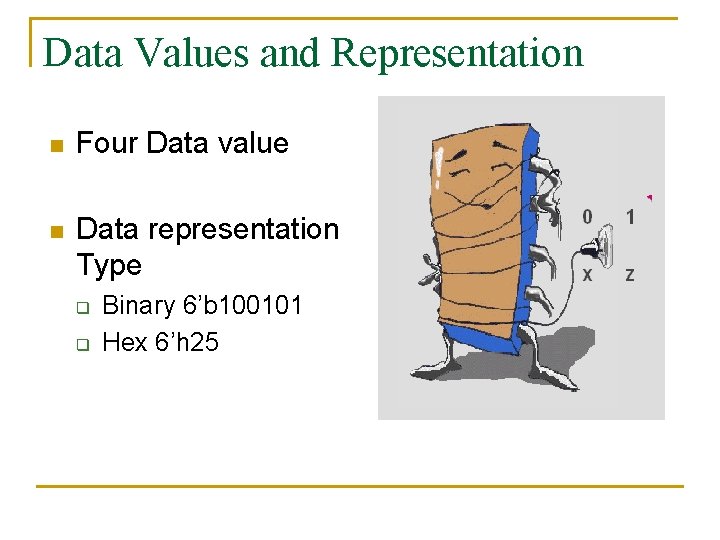

Data Values and Representation n Four Data value n Data representation Type q q Binary 6’b 100101 Hex 6’h 25

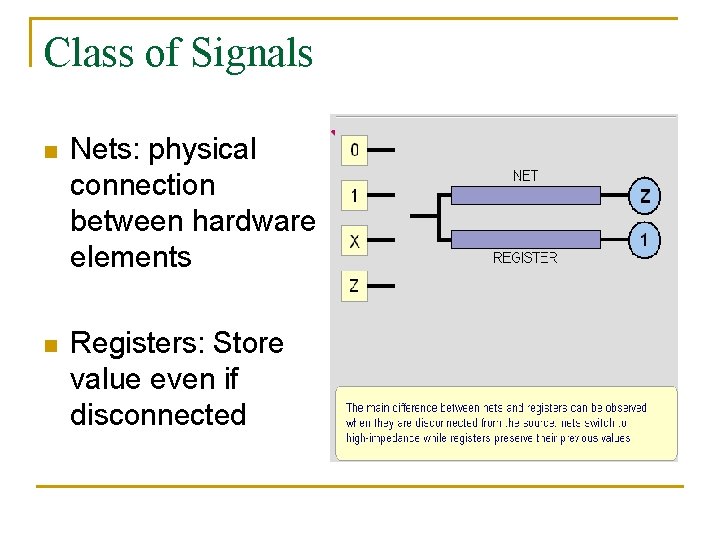

Class of Signals n Nets: physical connection between hardware elements n Registers: Store value even if disconnected

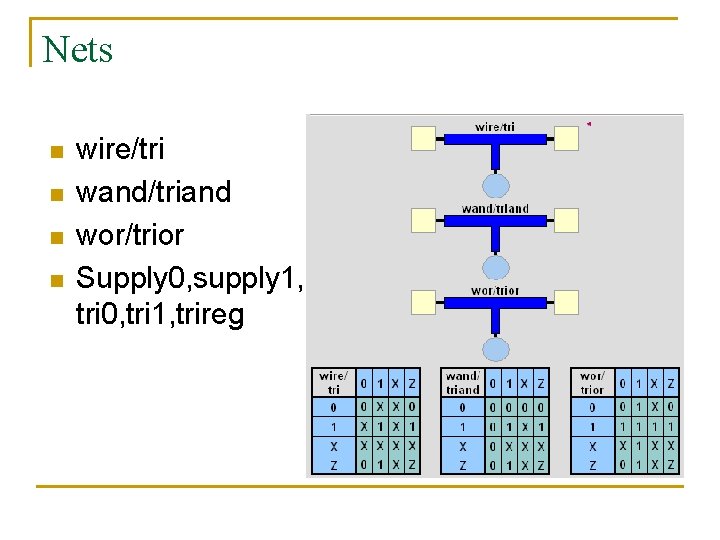

Nets n n wire/tri wand/triand wor/trior Supply 0, supply 1, tri 0, tri 1, trireg

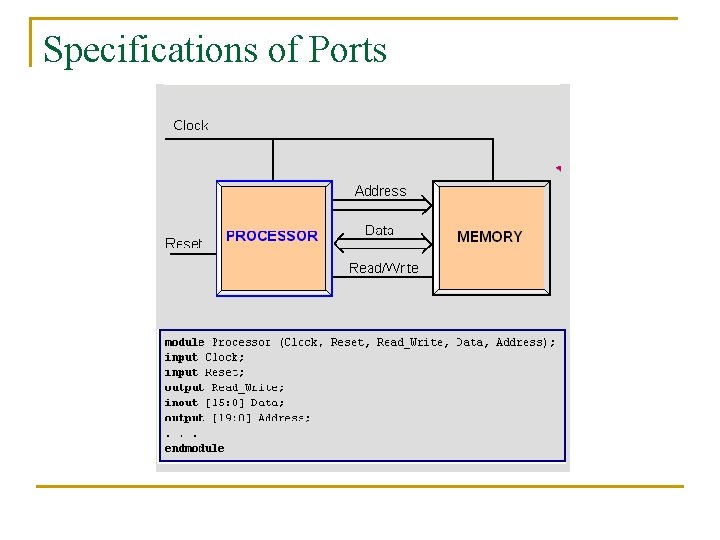

Specifications of Ports

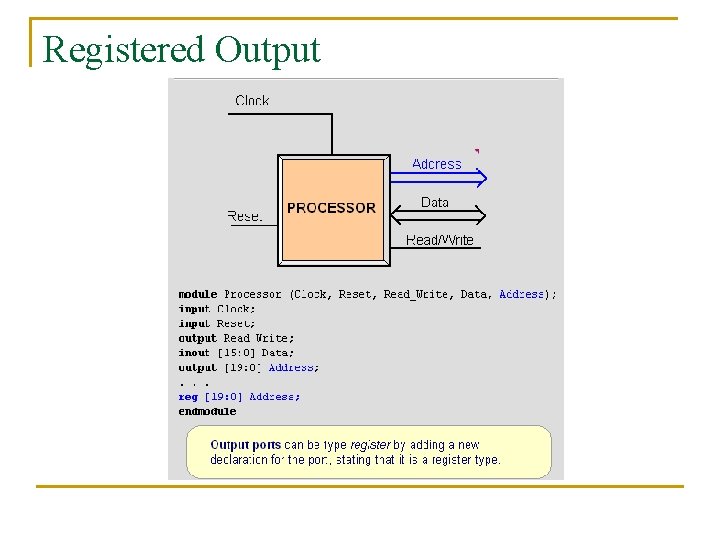

Registered Output

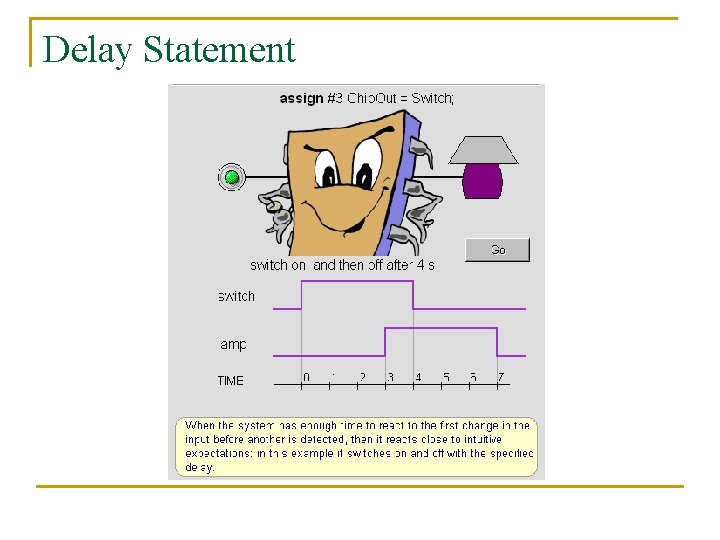

Delay Statement

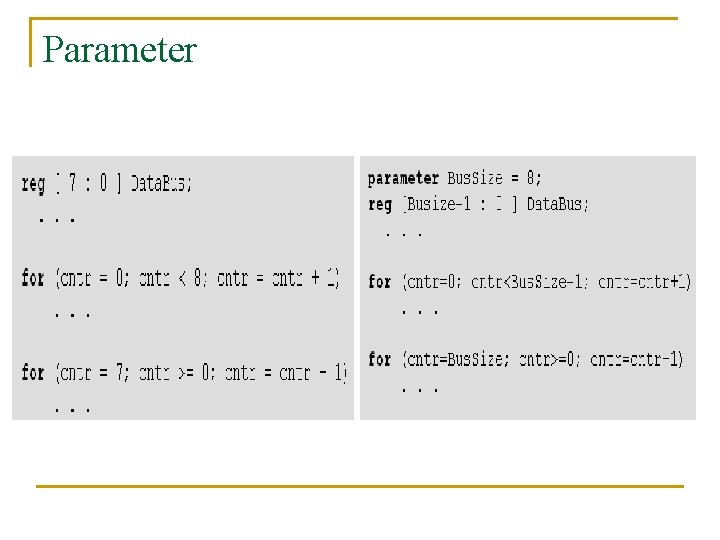

Parameter

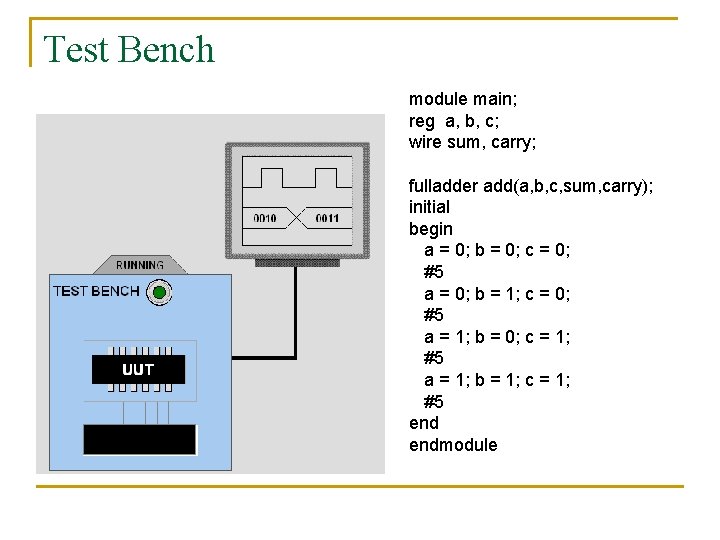

Test Bench module main; reg a, b, c; wire sum, carry; fulladder add(a, b, c, sum, carry); initial begin a = 0; b = 0; c = 0; #5 a = 0; b = 1; c = 0; #5 a = 1; b = 0; c = 1; #5 a = 1; b = 1; c = 1; #5 endmodule

![Memory Operation reg [31: 0] register_file [0: 7]; wire [31: 0] rf_bus; wire r Memory Operation reg [31: 0] register_file [0: 7]; wire [31: 0] rf_bus; wire r](http://slidetodoc.com/presentation_image_h/e635dd8c50d32f1bc97444a288a6e797/image-28.jpg)

Memory Operation reg [31: 0] register_file [0: 7]; wire [31: 0] rf_bus; wire r 2 b 4; assign rf_bus = register_file [2]; assign r 2 b 4 = rf_bus[4]; Can’t use register_file[2][4] for assigning value to variable r 2 b 4

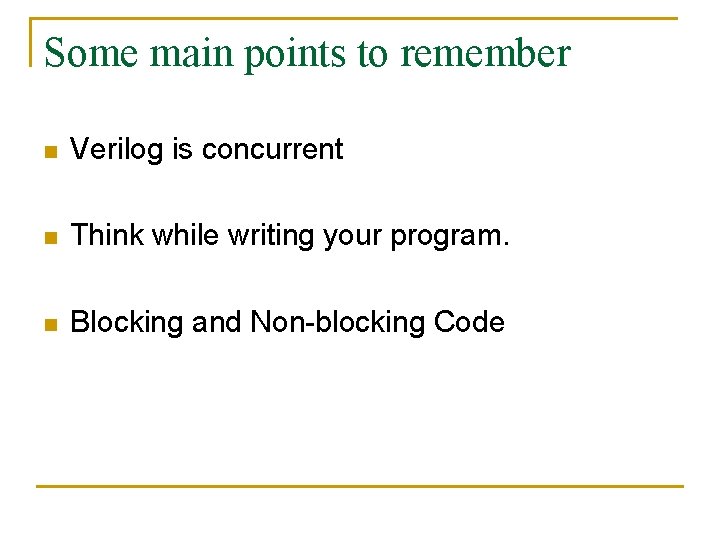

Some main points to remember n Verilog is concurrent n Think while writing your program. n Blocking and Non-blocking Code

References: n Evita_verilog Tutorial, www. aldec. com n http: //www. asic-world. com/verilog/

- Slides: 30