Intel MP Organization Intel MP Organization n Registers

![Solution - a n MOV CL, LIST[BX+SI] q Addressing Mode : base relative-plus-Index addressing Solution - a n MOV CL, LIST[BX+SI] q Addressing Mode : base relative-plus-Index addressing](https://slidetodoc.com/presentation_image/147df18ed65019170dfb901b741f39f8/image-34.jpg)

![Solution - b n MOV CX, [BX+SI] q Addressing Mode : base plus-Index addressing Solution - b n MOV CX, [BX+SI] q Addressing Mode : base plus-Index addressing](https://slidetodoc.com/presentation_image/147df18ed65019170dfb901b741f39f8/image-35.jpg)

![Solution n MOV AH, [4500 H] q q Addressing Mode : direct addressing mode Solution n MOV AH, [4500 H] q q Addressing Mode : direct addressing mode](https://slidetodoc.com/presentation_image/147df18ed65019170dfb901b741f39f8/image-36.jpg)

- Slides: 36

Intel MP Organization

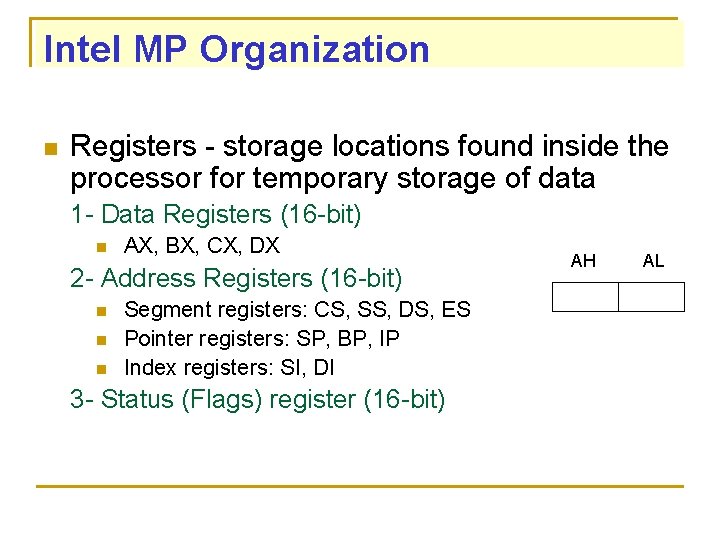

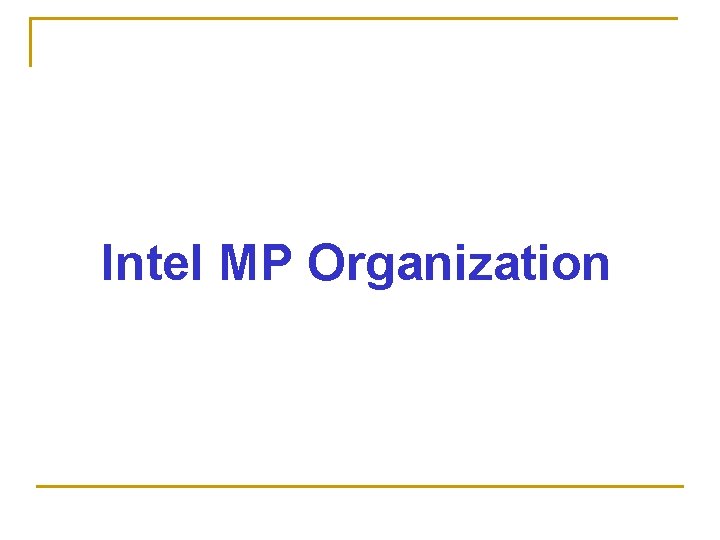

Intel MP Organization n Registers - storage locations found inside the processor for temporary storage of data 1 - Data Registers (16 -bit) n AX, BX, CX, DX 2 - Address Registers (16 -bit) n n n Segment registers: CS, SS, DS, ES Pointer registers: SP, BP, IP Index registers: SI, DI 3 - Status (Flags) register (16 -bit) AH AL

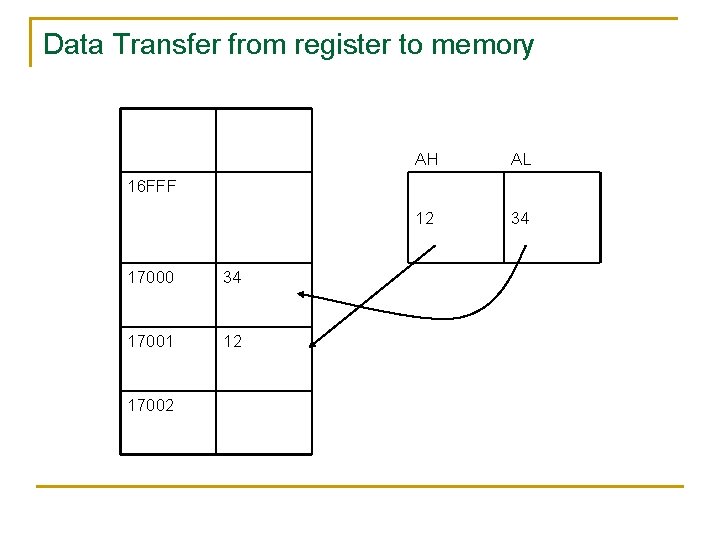

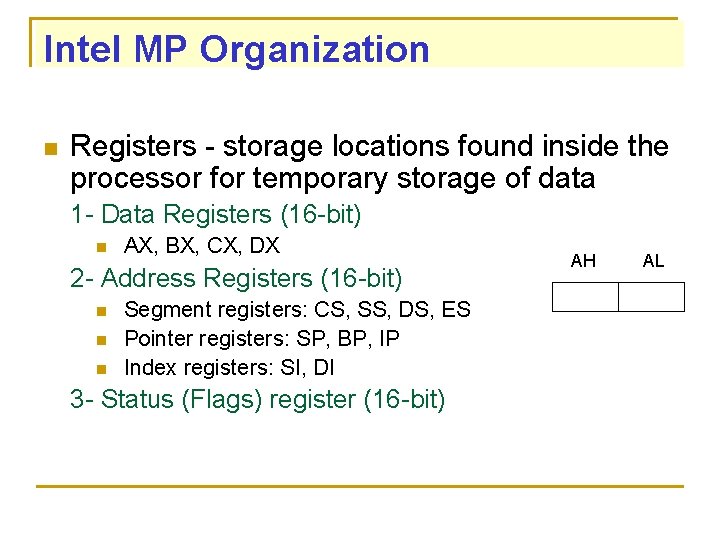

Data Transfer from register to memory AH AL 12 34 16 FFF 17000 34 17001 12 17002

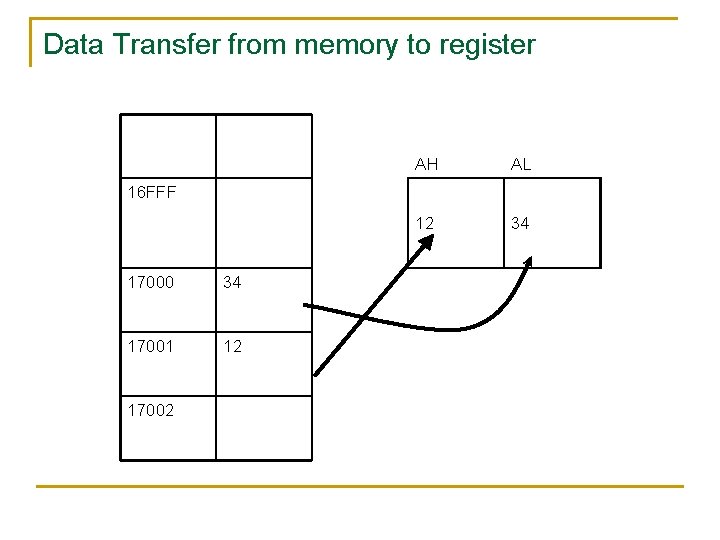

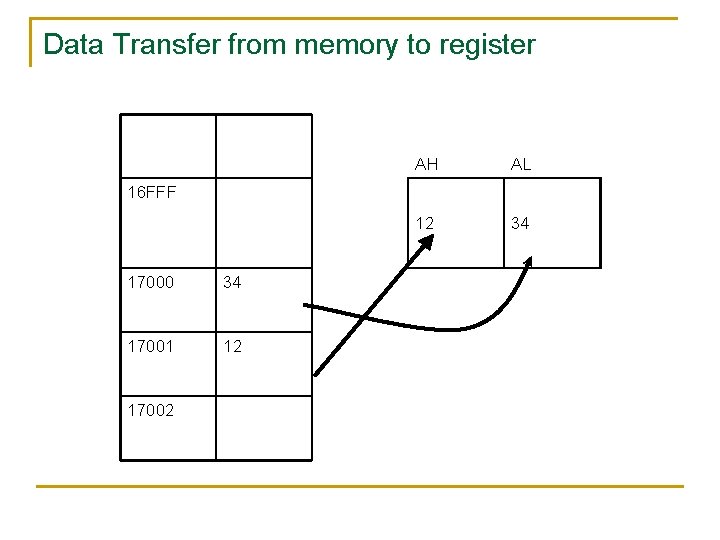

Data Transfer from memory to register AH AL 12 34 16 FFF 17000 34 17001 12 17002

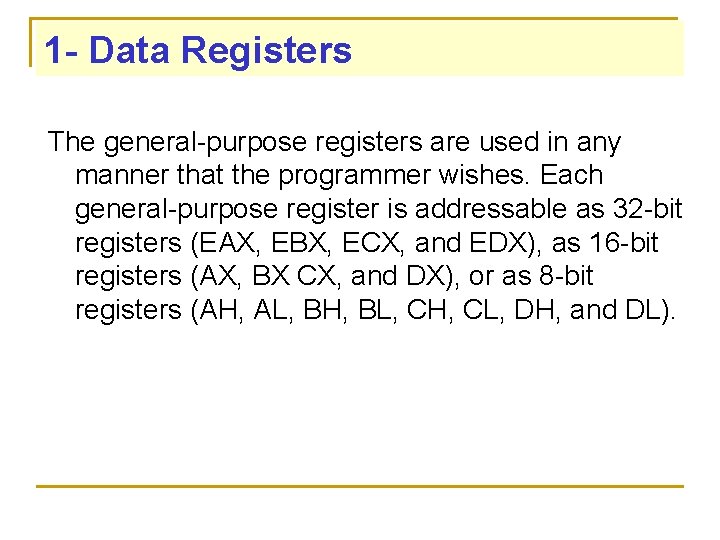

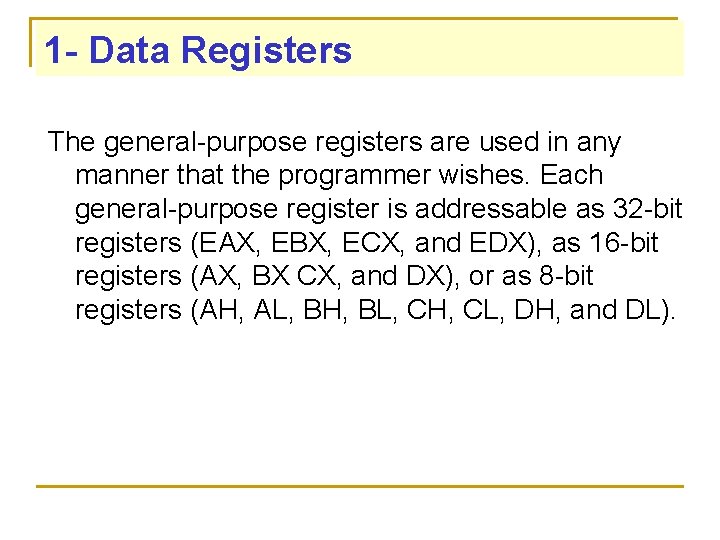

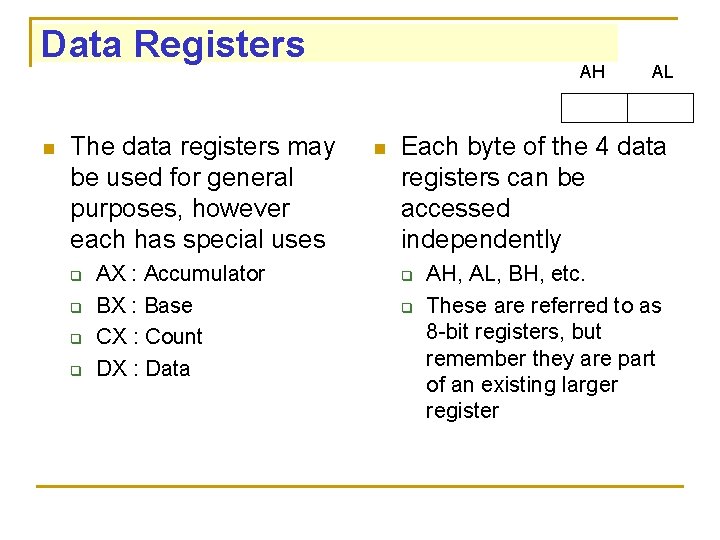

1 - Data Registers The general-purpose registers are used in any manner that the programmer wishes. Each general-purpose register is addressable as 32 -bit registers (EAX, EBX, ECX, and EDX), as 16 -bit registers (AX, BX CX, and DX), or as 8 -bit registers (AH, AL, BH, BL, CH, CL, DH, and DL).

Data Registers AH AL n The data registers may be used for general purposes, however each has special uses q q AX : Accumulator BX : Base CX : Count DX : Data n Each byte of the 4 data registers can be accessed independently q q AH, AL, BH, etc. These are referred to as 8 -bit registers, but remember they are part of an existing larger register

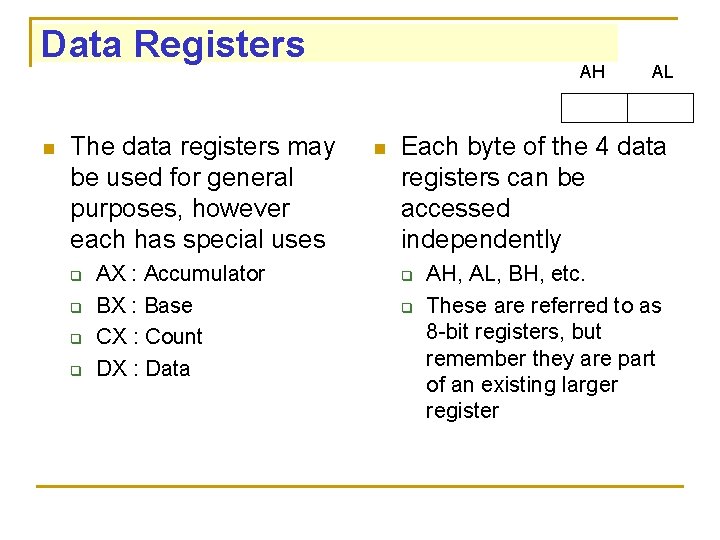

Storing data in Registers AH Byte Value 3 F AX Word value 143 E AL AH 3 F Or AX 3 F BH BL BX 14 3 E Double word 789 A 345 B DX AL DH DL AH AL 78 9 A 34 5 B AX Or EAX 78 9 A

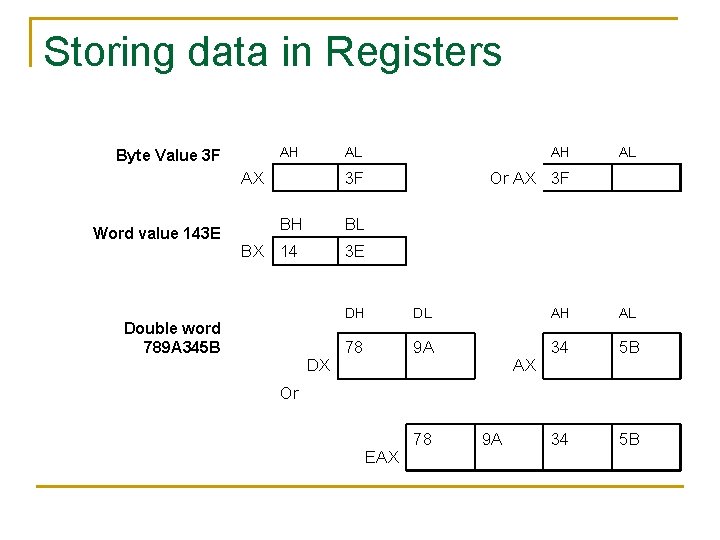

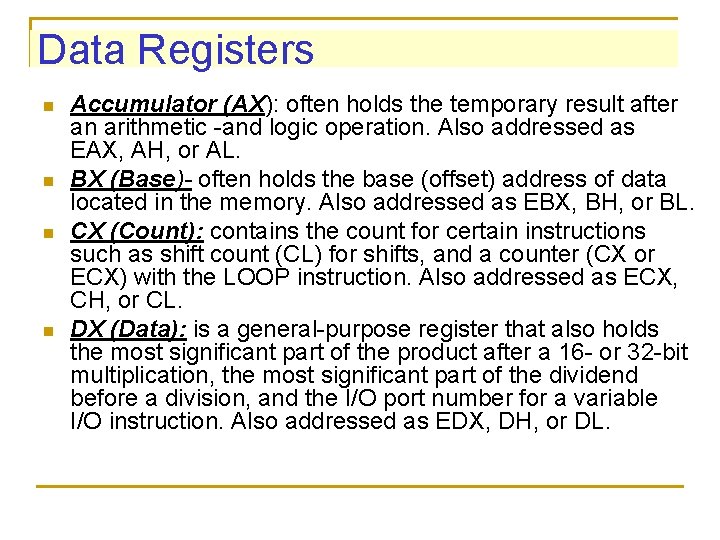

Data Registers n n Accumulator (AX): often holds the temporary result after an arithmetic -and logic operation. Also addressed as EAX, AH, or AL. BX (Base)- often holds the base (offset) address of data located in the memory. Also addressed as EBX, BH, or BL. CX (Count): contains the count for certain instructions such as shift count (CL) for shifts, and a counter (CX or ECX) with the LOOP instruction. Also addressed as ECX, CH, or CL. DX (Data): is a general-purpose register that also holds the most significant part of the product after a 16 - or 32 -bit multiplication, the most significant part of the dividend before a division, and the I/O port number for a variable I/O instruction. Also addressed as EDX, DH, or DL.

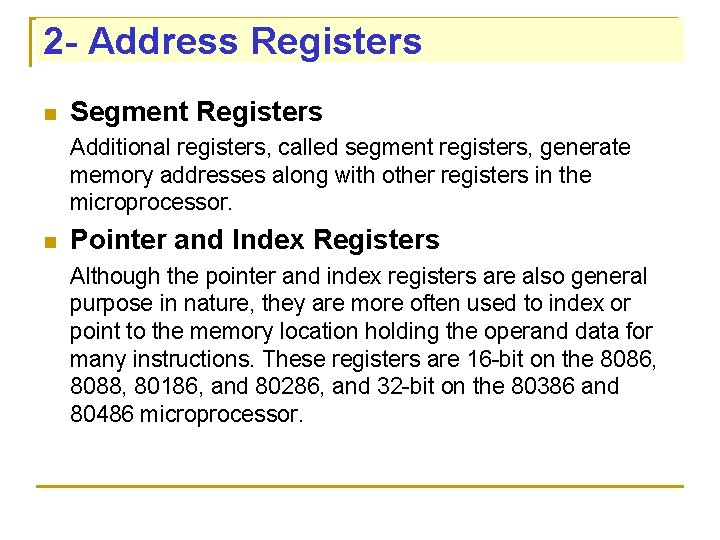

2 - Address Registers n Segment Registers Additional registers, called segment registers, generate memory addresses along with other registers in the microprocessor. n Pointer and Index Registers Although the pointer and index registers are also general purpose in nature, they are more often used to index or point to the memory location holding the operand data for many instructions. These registers are 16 -bit on the 8086, 8088, 80186, and 80286, and 32 -bit on the 80386 and 80486 microprocessor.

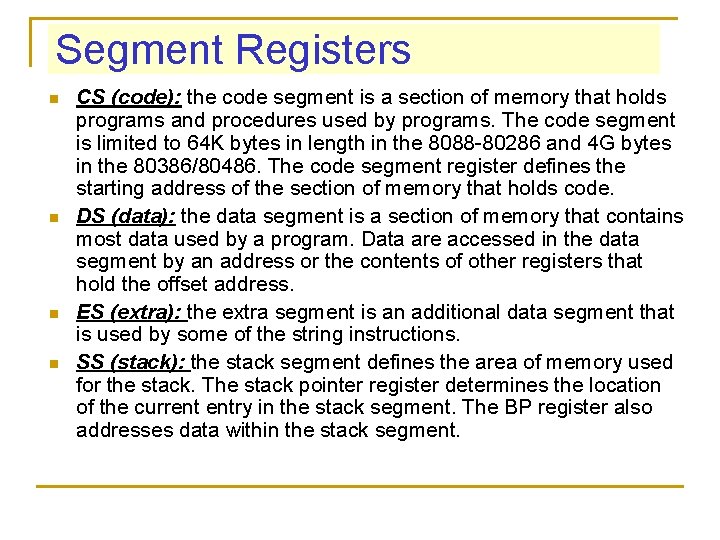

Segment Registers n n CS (code): the code segment is a section of memory that holds programs and procedures used by programs. The code segment is limited to 64 K bytes in length in the 8088 -80286 and 4 G bytes in the 80386/80486. The code segment register defines the starting address of the section of memory that holds code. DS (data): the data segment is a section of memory that contains most data used by a program. Data are accessed in the data segment by an address or the contents of other registers that hold the offset address. ES (extra): the extra segment is an additional data segment that is used by some of the string instructions. SS (stack): the stack segment defines the area of memory used for the stack. The stack pointer register determines the location of the current entry in the stack segment. The BP register also addresses data within the stack segment.

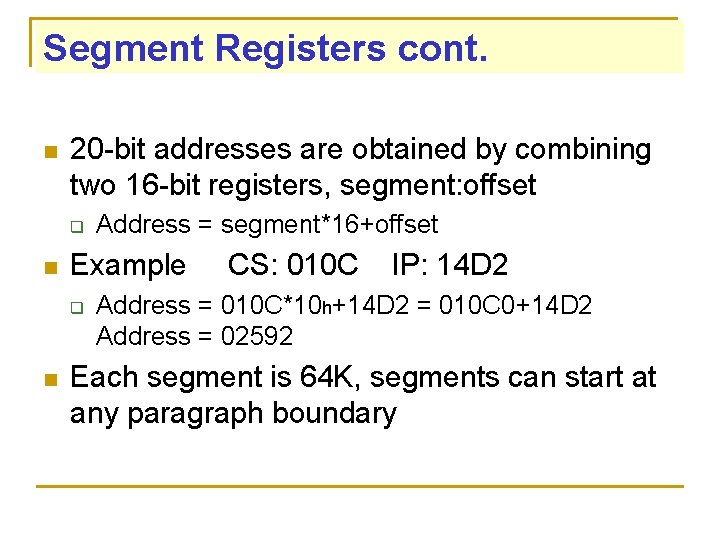

Segment Registers cont. n 20 -bit addresses are obtained by combining two 16 -bit registers, segment: offset q n Example CS: 010 C IP: 14 D 2 q n Address = segment*16+offset Address = 010 C*10 h+14 D 2 = 010 C 0+14 D 2 Address = 02592 Each segment is 64 K, segments can start at any paragraph boundary

Pointer and Index Registers n IP (Instruction Pointer): contains the address of the next instruction to be executed n n SP (Stack Pointer): used to address data in LIFO (last-in, first-out) stack memory. This occurs most often when the PUSH and POP instructions are executed or when a subroutine is CALLed or RETurned from in a program. This register is also the 32 -bit ESP register. BP (Base Pointer): is a general-purpose pointer often used to address an array of data in the stack memory. This register is also the 32 -bit EBP register. SI (Source Index): used to address source data indirectly for use with the string instructions. This register is also the 32 -bit ESI register. DI (Destination Index): normally used destination data indirectly for use with the string instructions. This register Is also the 32 -bit EDI register.

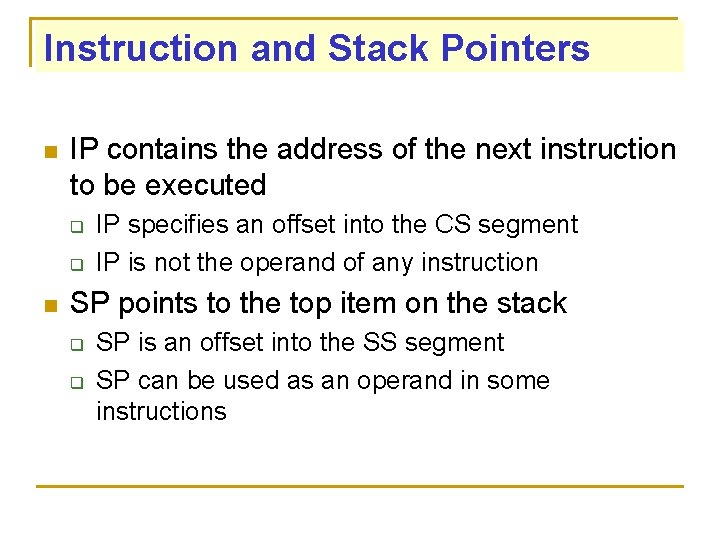

Instruction and Stack Pointers n IP contains the address of the next instruction to be executed q q n IP specifies an offset into the CS segment IP is not the operand of any instruction SP points to the top item on the stack q q SP is an offset into the SS segment SP can be used as an operand in some instructions

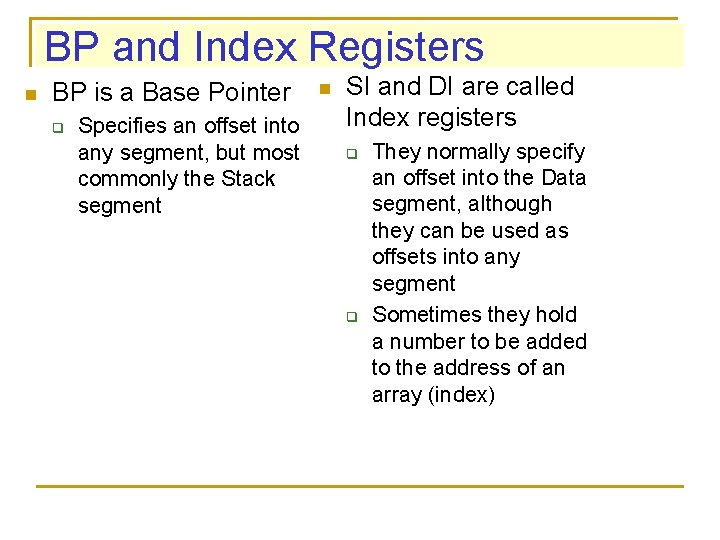

BP and Index Registers n BP is a Base Pointer q Specifies an offset into any segment, but most commonly the Stack segment n SI and DI are called Index registers q q They normally specify an offset into the Data segment, although they can be used as offsets into any segment Sometimes they hold a number to be added to the address of an array (index)

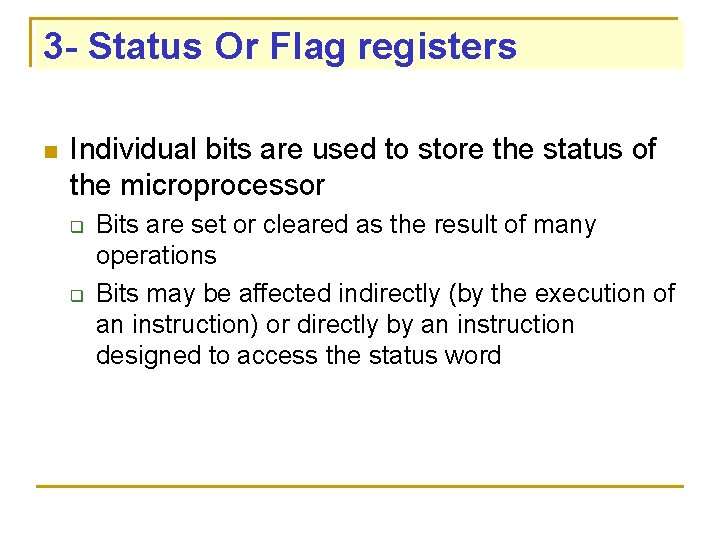

3 - Status Or Flag registers n Individual bits are used to store the status of the microprocessor q q Bits are set or cleared as the result of many operations Bits may be affected indirectly (by the execution of an instruction) or directly by an instruction designed to access the status word

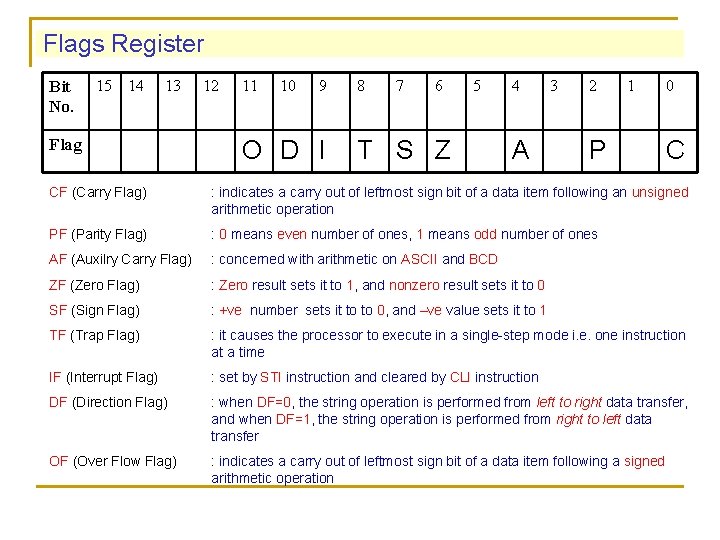

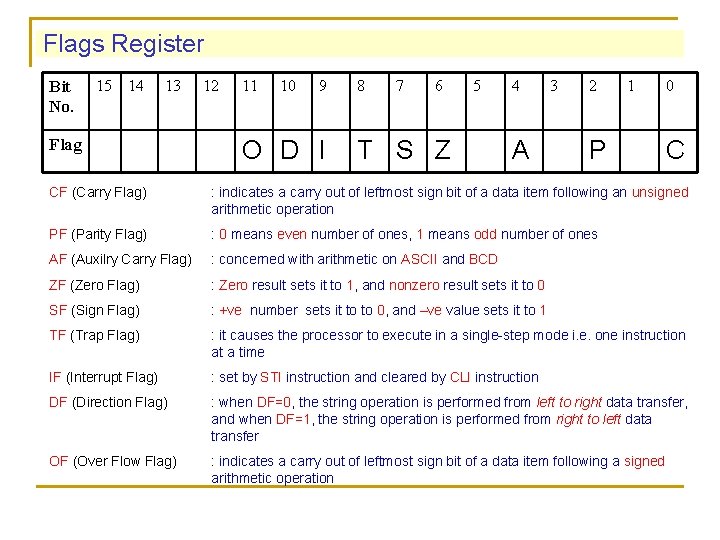

Flags Register Bit No. 15 14 13 Flag 12 11 10 9 O D I 8 7 6 5 T S Z 4 A 3 2 P 1 0 C CF (Carry Flag) : indicates a carry out of leftmost sign bit of a data item following an unsigned arithmetic operation PF (Parity Flag) : 0 means even number of ones, 1 means odd number of ones AF (Auxilry Carry Flag) : concerned with arithmetic on ASCII and BCD ZF (Zero Flag) : Zero result sets it to 1, and nonzero result sets it to 0 SF (Sign Flag) : +ve number sets it to to 0, and –ve value sets it to 1 TF (Trap Flag) : it causes the processor to execute in a single-step mode i. e. one instruction at a time IF (Interrupt Flag) : set by STI instruction and cleared by CLI instruction DF (Direction Flag) : when DF=0, the string operation is performed from left to right data transfer, and when DF=1, the string operation is performed from right to left data transfer OF (Over Flow Flag) : indicates a carry out of leftmost sign bit of a data item following a signed arithmetic operation

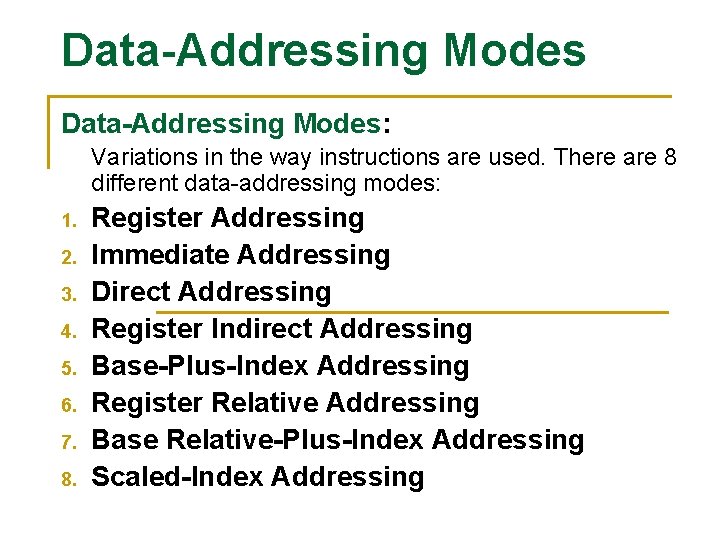

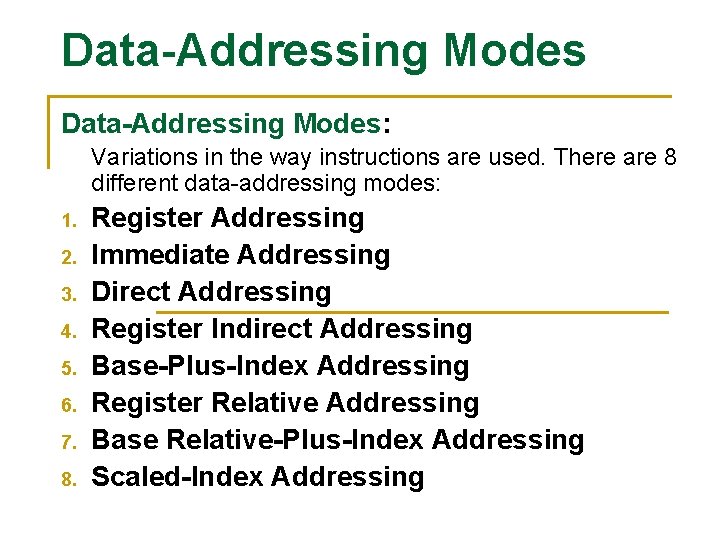

Data-Addressing Modes: Variations in the way instructions are used. There are 8 different data-addressing modes: 1. 2. 3. 4. 5. 6. 7. 8. Register Addressing Immediate Addressing Direct Addressing Register Indirect Addressing Base-Plus-Index Addressing Register Relative Addressing Base Relative-Plus-Index Addressing Scaled-Index Addressing

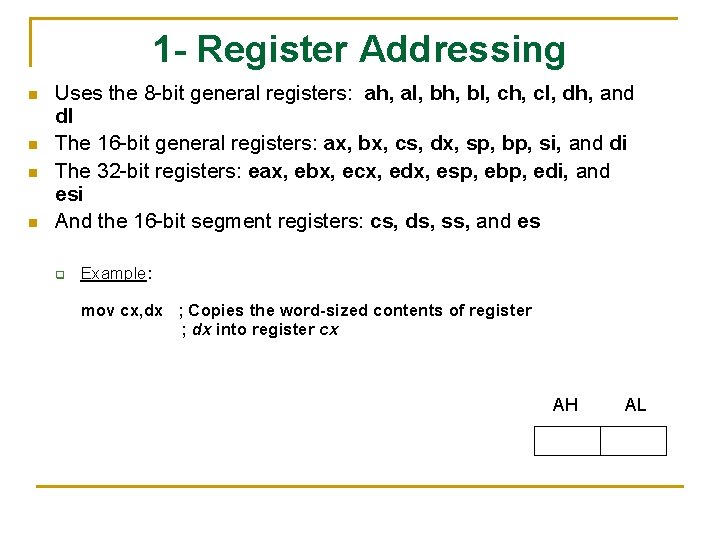

1 - Register Addressing n n Uses the 8 -bit general registers: ah, al, bh, bl, ch, cl, dh, and dl The 16 -bit general registers: ax, bx, cs, dx, sp, bp, si, and di The 32 -bit registers: eax, ebx, ecx, edx, esp, ebp, edi, and esi And the 16 -bit segment registers: cs, ds, ss, and es q Example: mov cx, dx ; Copies the word-sized contents of register ; dx into register cx AH AL

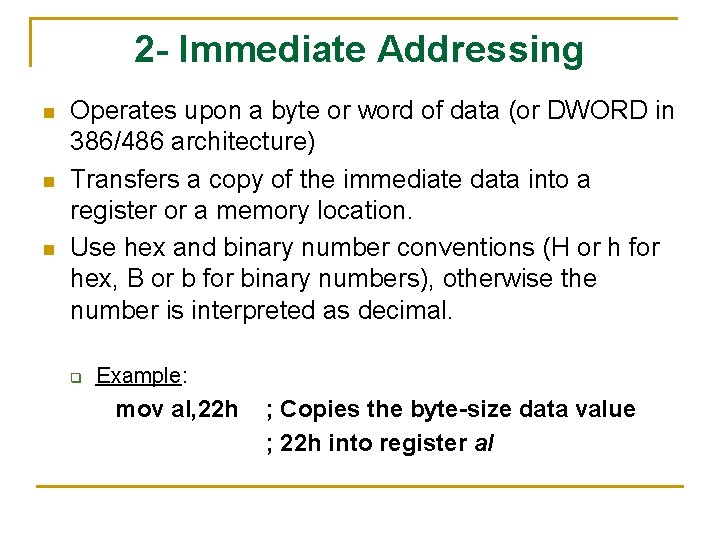

2 - Immediate Addressing n n n Operates upon a byte or word of data (or DWORD in 386/486 architecture) Transfers a copy of the immediate data into a register or a memory location. Use hex and binary number conventions (H or h for hex, B or b for binary numbers), otherwise the number is interpreted as decimal. q Example: mov al, 22 h ; Copies the byte-size data value ; 22 h into register al

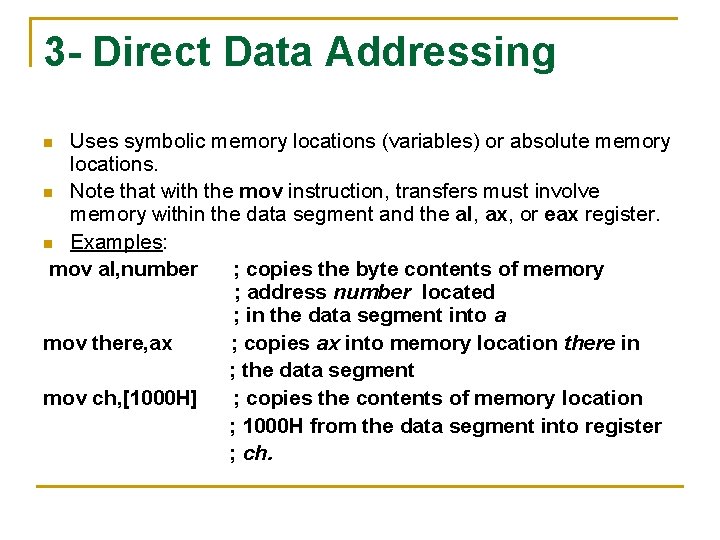

3 - Direct Data Addressing Uses symbolic memory locations (variables) or absolute memory locations. n Note that with the mov instruction, transfers must involve memory within the data segment and the al, ax, or eax register. n Examples: mov al, number ; copies the byte contents of memory ; address number located ; in the data segment into a mov there, ax ; copies ax into memory location there in ; the data segment mov ch, [1000 H] ; copies the contents of memory location ; 1000 H from the data segment into register ; ch. n

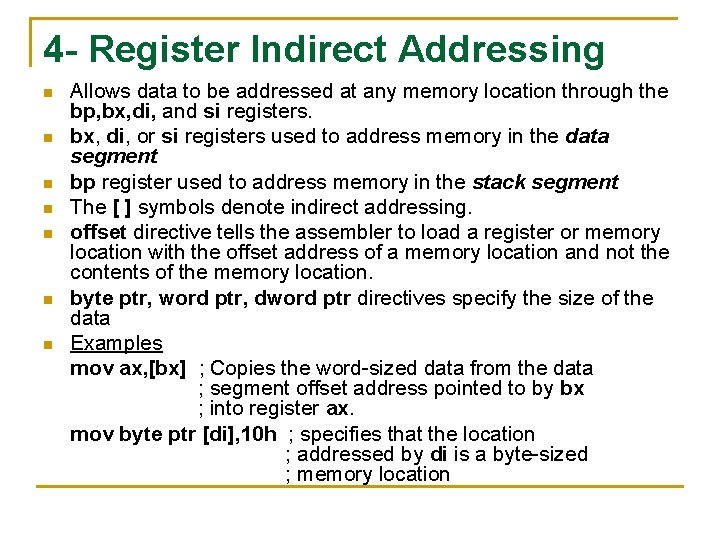

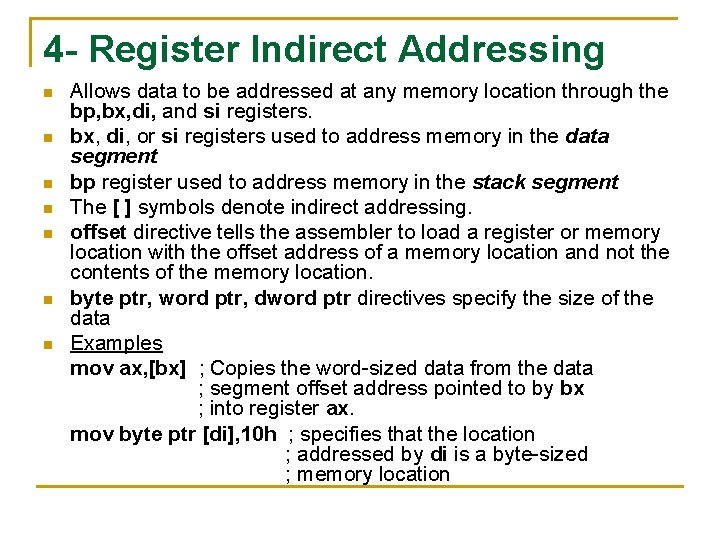

4 - Register Indirect Addressing n n n n Allows data to be addressed at any memory location through the bp, bx, di, and si registers. bx, di, or si registers used to address memory in the data segment bp register used to address memory in the stack segment The [ ] symbols denote indirect addressing. offset directive tells the assembler to load a register or memory location with the offset address of a memory location and not the contents of the memory location. byte ptr, word ptr, dword ptr directives specify the size of the data Examples mov ax, [bx] ; Copies the word-sized data from the data ; segment offset address pointed to by bx ; into register ax. mov byte ptr [di], 10 h ; specifies that the location ; addressed by di is a byte-sized ; memory location

OFFSET and PTR n The OFFSET directive indicates an offset address to the assembler Example: MOV SI, DATA ; loads the contents of address DATA into SI MOV SI, OFFSET DATA; loads the address of DATA into SI n The PTR directive indicates the type of data (Byte or Word) Example: MOV [BX], 2 ; does this instruction move 8 - or 16 -bit number 2 into the memory? To solve this conflict MOV BYTE PTR[BX], 2 ; moves a 2 into the 8 -bit memory location addressed by BX

Register Indirect Addressing, cont. n Example Program: This program reads in 50 bytes n of data from DATA_PORT and stores the data in TABLE mov bx, offset table ; address table mov cx, 50 ; load counter again: in al, data_port ; read input port mov [bx], al ; save data inc bx ; address next dec cx jnz again ; repeat 50 times

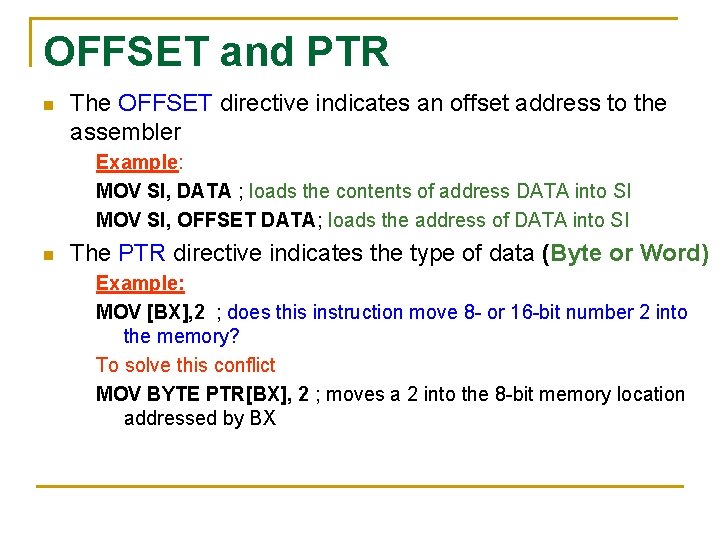

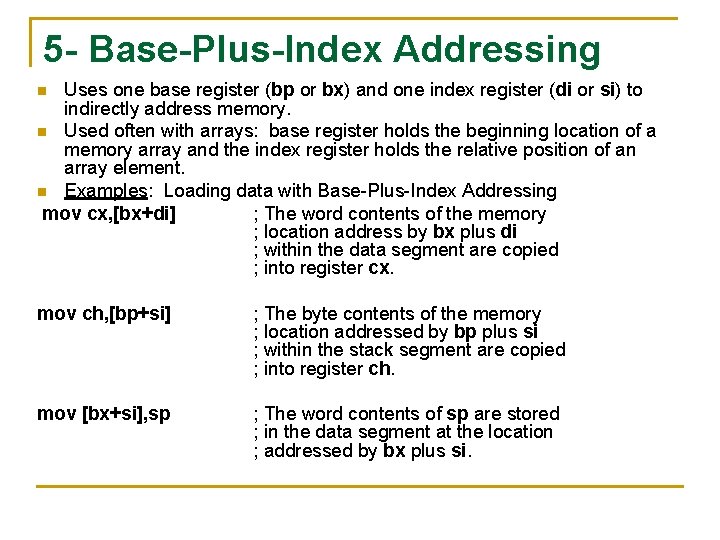

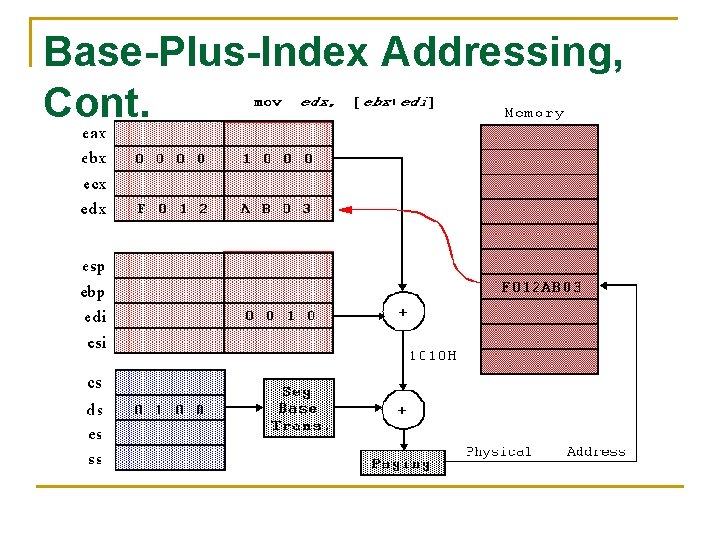

5 - Base-Plus-Index Addressing Uses one base register (bp or bx) and one index register (di or si) to indirectly address memory. n Used often with arrays: base register holds the beginning location of a memory array and the index register holds the relative position of an array element. n Examples: Loading data with Base-Plus-Index Addressing mov cx, [bx+di] ; The word contents of the memory ; location address by bx plus di ; within the data segment are copied ; into register cx. n mov ch, [bp+si] ; The byte contents of the memory ; location addressed by bp plus si ; within the stack segment are copied ; into register ch. mov [bx+si], sp ; The word contents of sp are stored ; in the data segment at the location ; addressed by bx plus si.

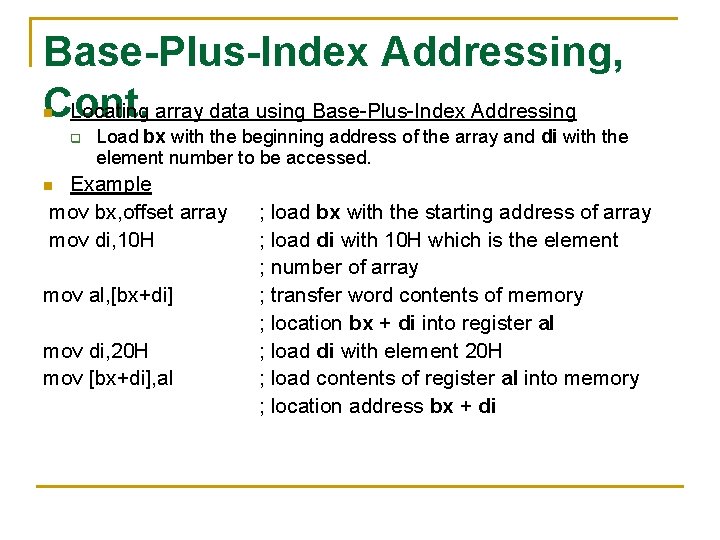

Base-Plus-Index Addressing, Cont. Locating array data using Base-Plus-Index Addressing n q Load bx with the beginning address of the array and di with the element number to be accessed. Example mov bx, offset array mov di, 10 H mov al, [bx+di] mov di, 20 H mov [bx+di], al n ; load bx with the starting address of array ; load di with 10 H which is the element ; number of array ; transfer word contents of memory ; location bx + di into register al ; load di with element 20 H ; load contents of register al into memory ; location address bx + di

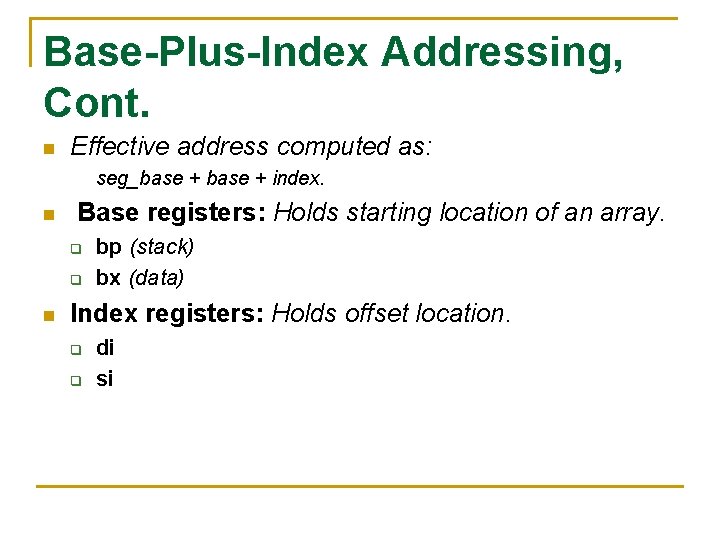

Base-Plus-Index Addressing, Cont. n Effective address computed as: seg_base + index. n Base registers: Holds starting location of an array. q q n bp (stack) bx (data) Index registers: Holds offset location. q q di si

Base-Plus-Index Addressing, Cont.

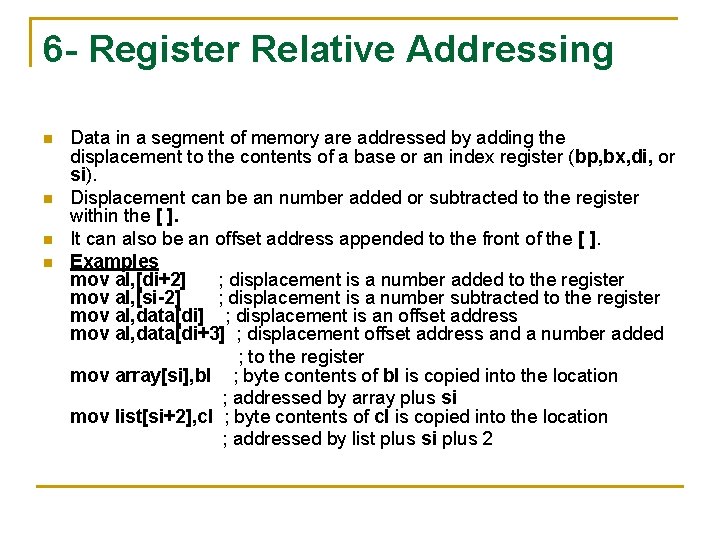

6 - Register Relative Addressing Data in a segment of memory are addressed by adding the displacement to the contents of a base or an index register (bp, bx, di, or si). n Displacement can be an number added or subtracted to the register within the [ ]. n It can also be an offset address appended to the front of the [ ]. n Examples mov al, [di+2] ; displacement is a number added to the register mov al, [si-2] ; displacement is a number subtracted to the register mov al, data[di] ; displacement is an offset address mov al, data[di+3] ; displacement offset address and a number added ; to the register mov array[si], bl ; byte contents of bl is copied into the location ; addressed by array plus si mov list[si+2], cl ; byte contents of cl is copied into the location ; addressed by list plus si plus 2 n

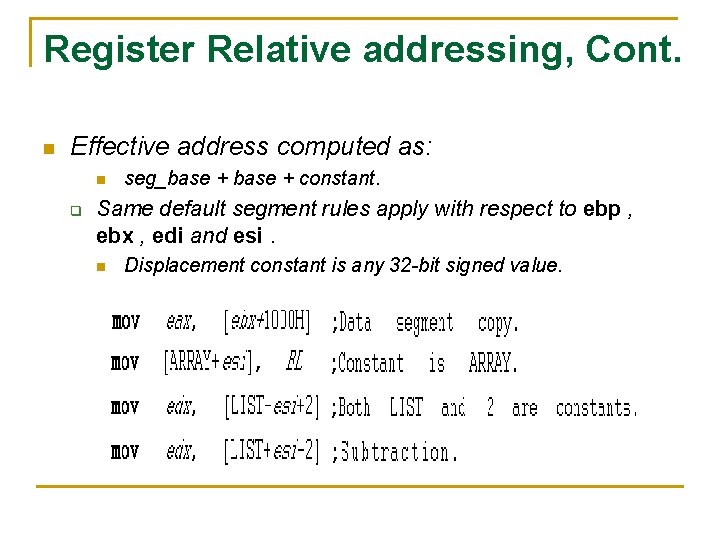

Register Relative addressing, Cont. n Effective address computed as: n q seg_base + constant. Same default segment rules apply with respect to ebp , ebx , edi and esi. n Displacement constant is any 32 -bit signed value.

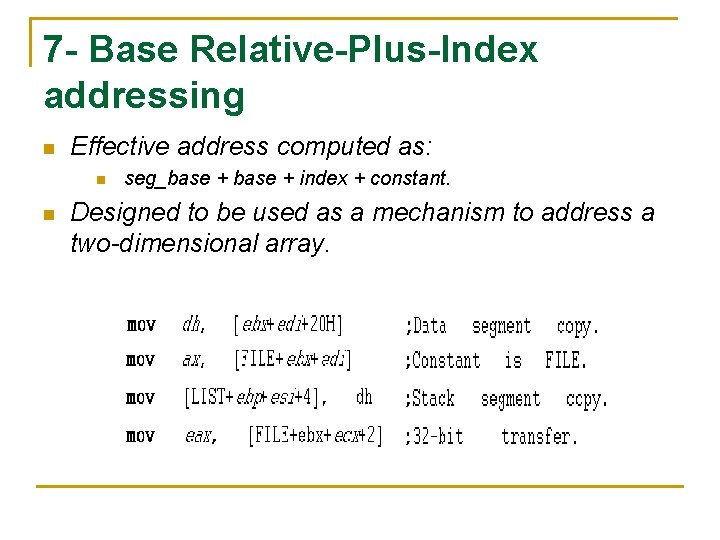

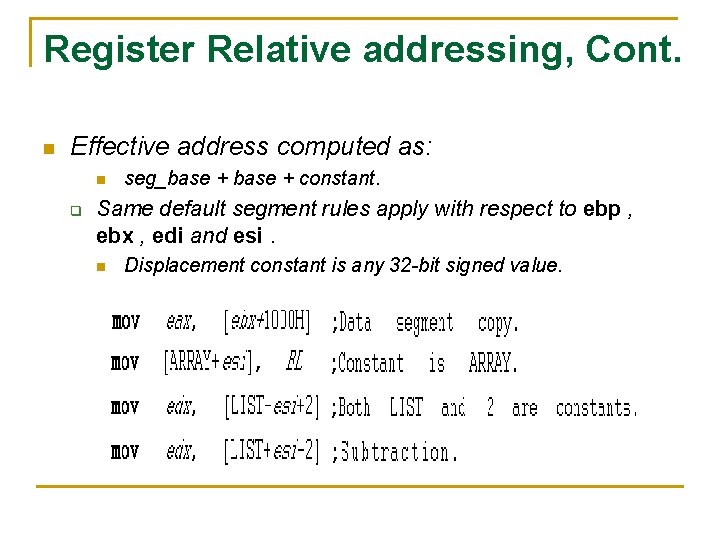

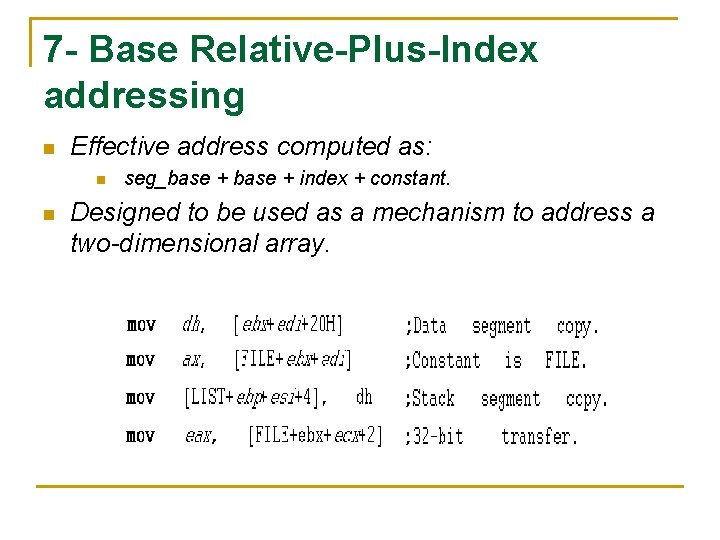

7 - Base Relative-Plus-Index addressing n Effective address computed as: n n seg_base + index + constant. Designed to be used as a mechanism to address a two-dimensional array.

Base Relative-Plus-Index addressing, cont.

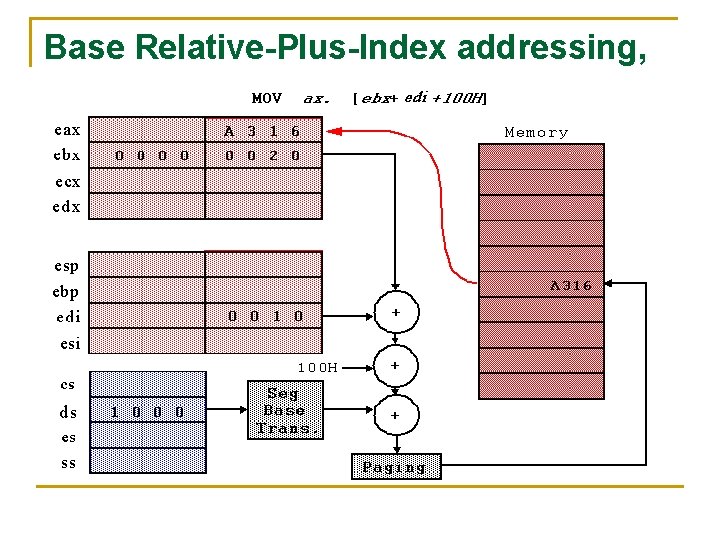

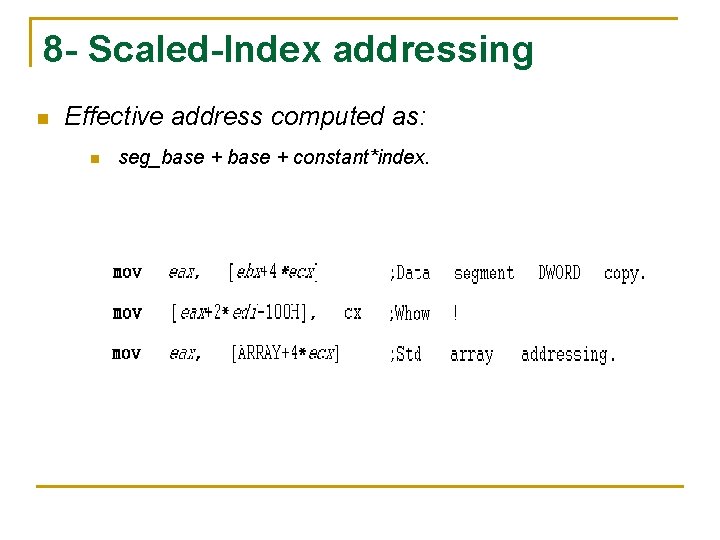

8 - Scaled-Index addressing n Effective address computed as: n seg_base + constant*index.

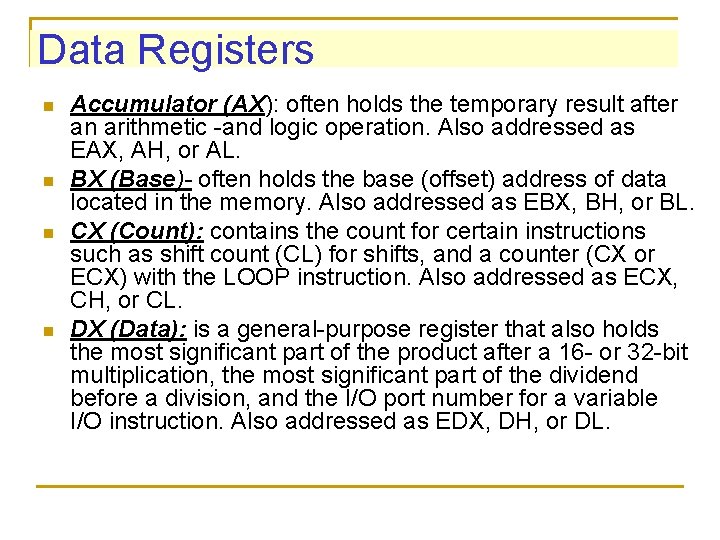

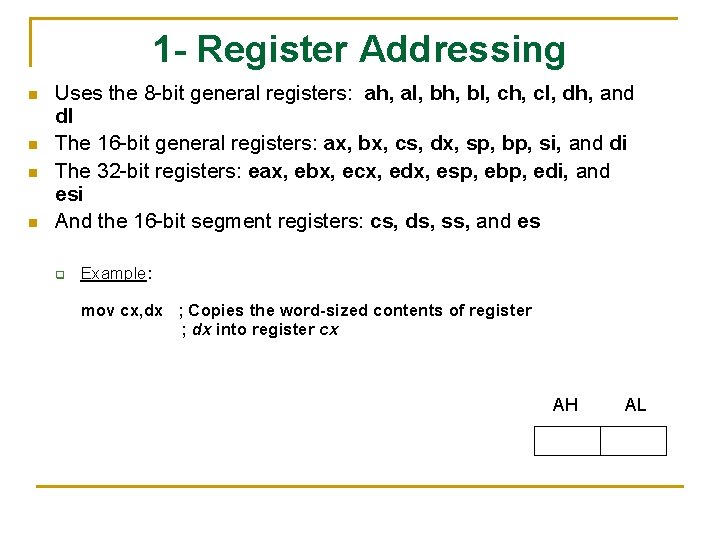

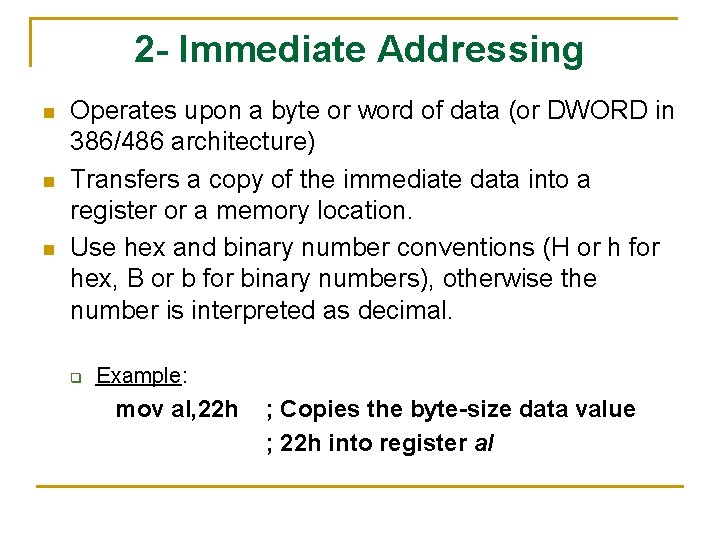

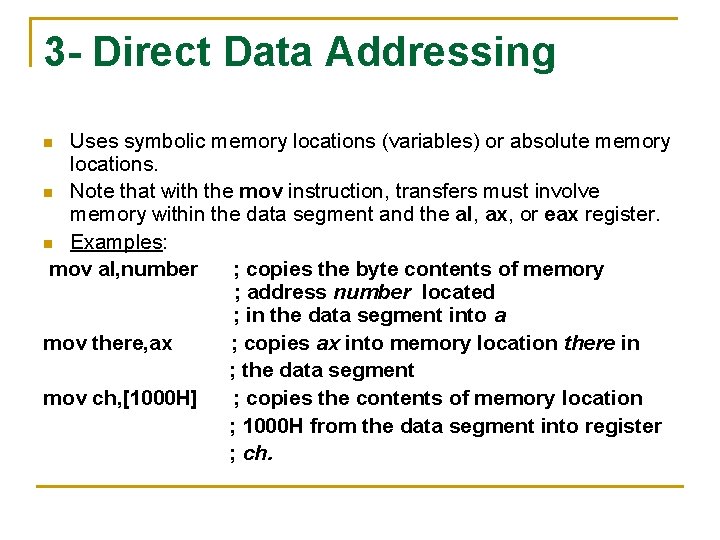

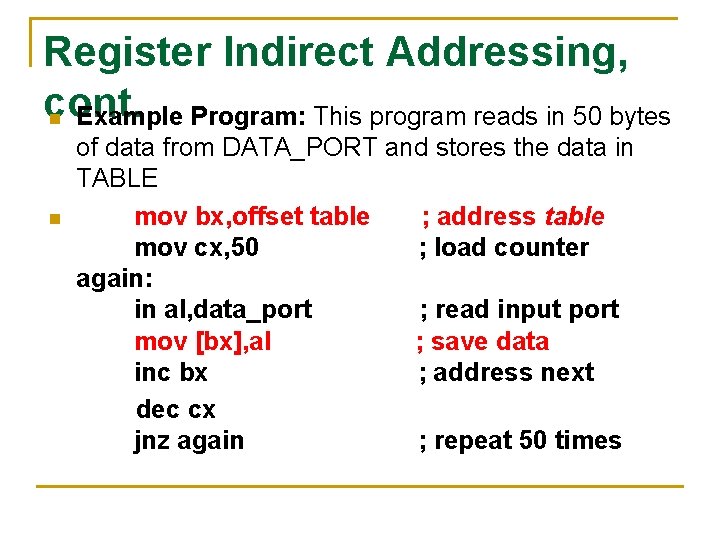

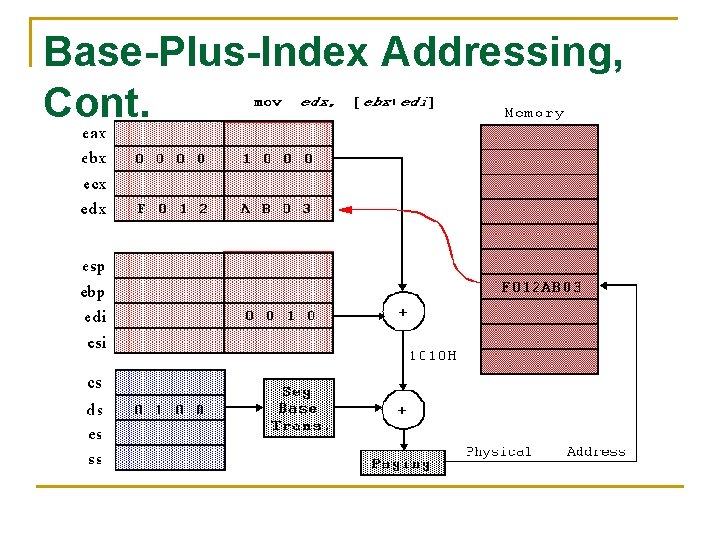

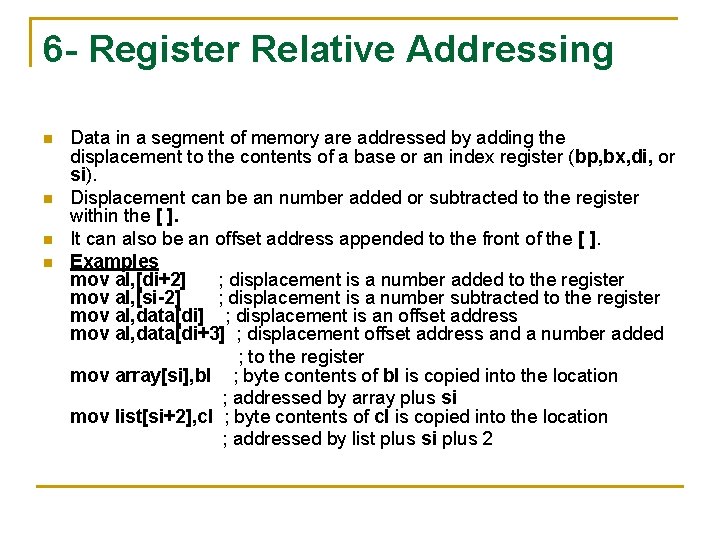

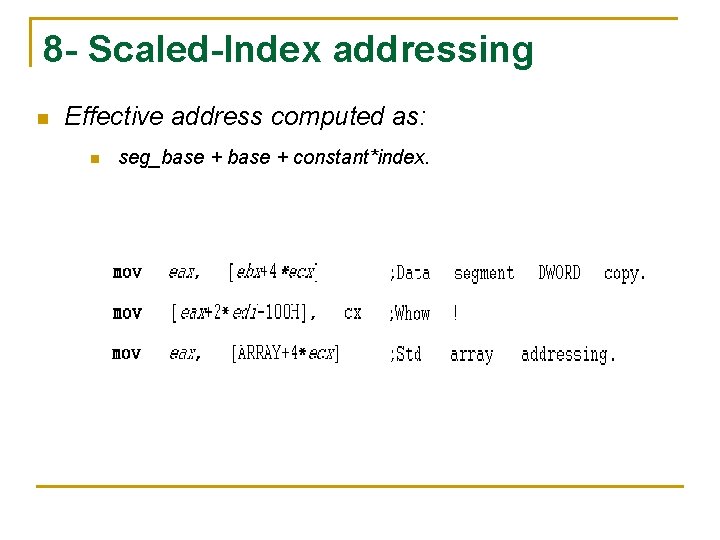

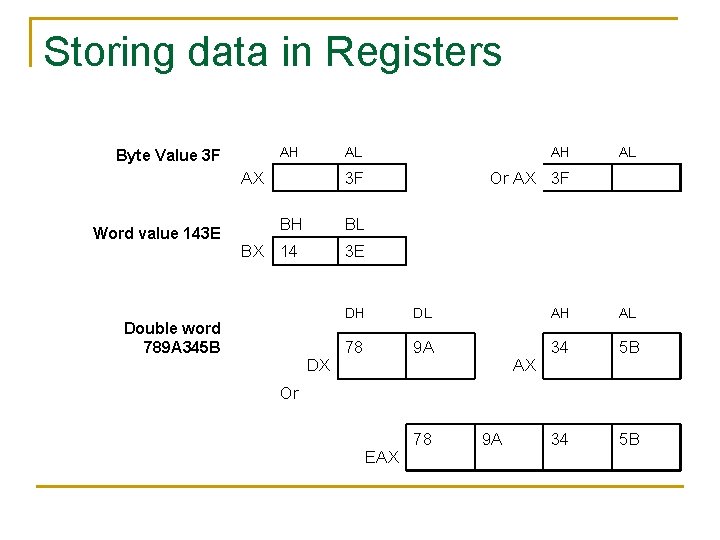

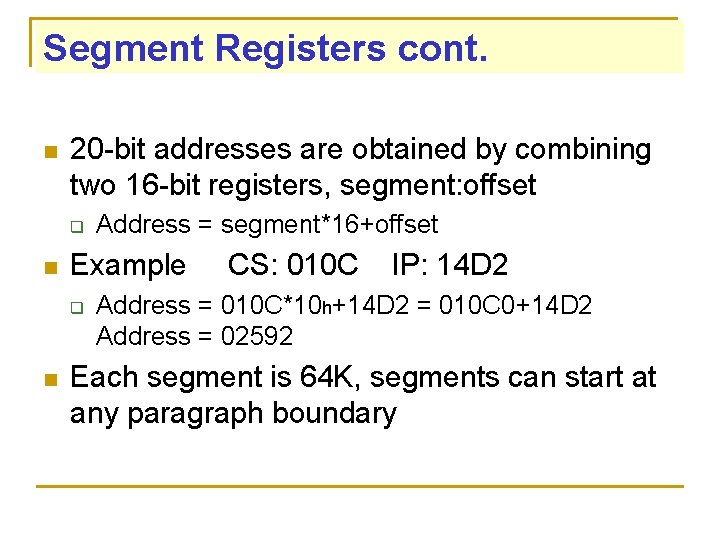

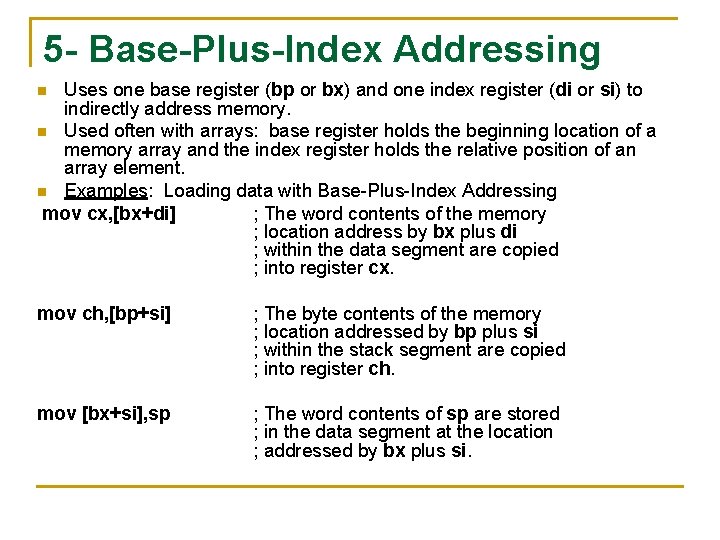

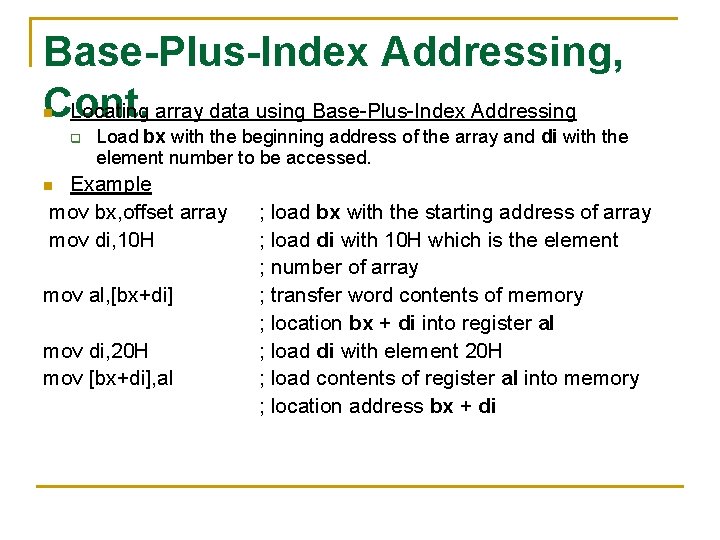

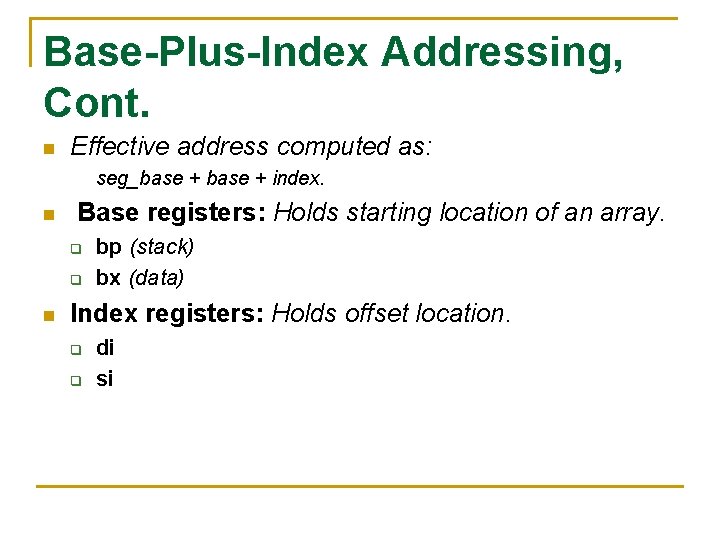

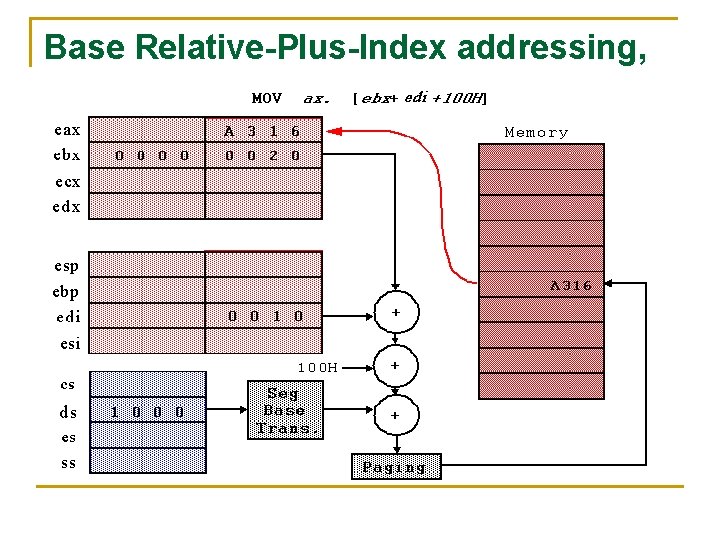

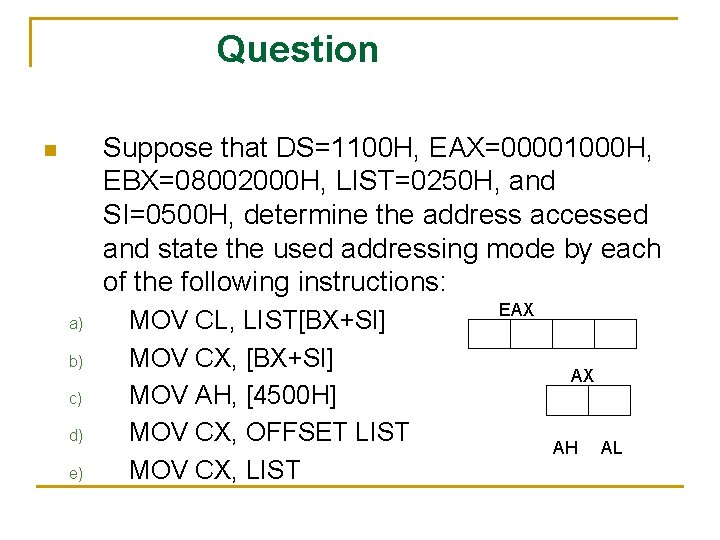

Question Suppose that DS=1100 H, EAX=00001000 H, EBX=08002000 H, LIST=0250 H, and SI=0500 H, determine the address accessed and state the used addressing mode by each of the following instructions: n a) b) c) d) e) MOV CL, LIST[BX+SI] MOV CX, [BX+SI] MOV AH, [4500 H] MOV CX, OFFSET LIST MOV CX, LIST EAX AX AH AL

![Solution a n MOV CL LISTBXSI q Addressing Mode base relativeplusIndex addressing Solution - a n MOV CL, LIST[BX+SI] q Addressing Mode : base relative-plus-Index addressing](https://slidetodoc.com/presentation_image/147df18ed65019170dfb901b741f39f8/image-34.jpg)

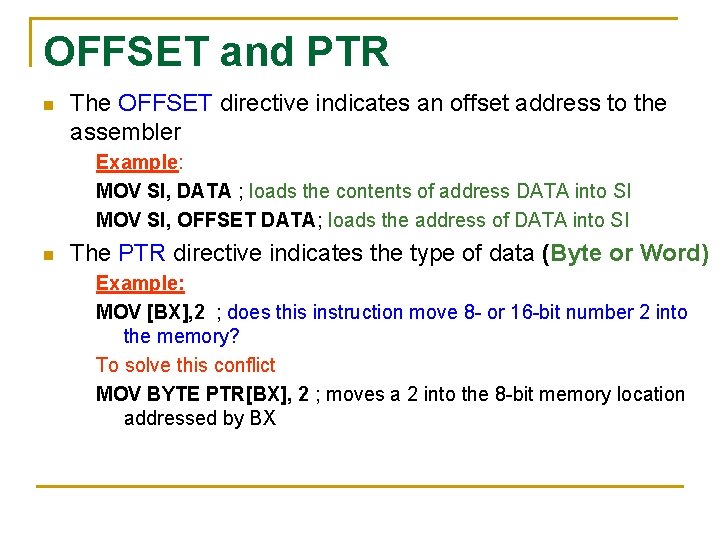

Solution - a n MOV CL, LIST[BX+SI] q Addressing Mode : base relative-plus-Index addressing mode Effective address=DS*10 H+LIST+BX+SI = 11000 + 0250 +2000 + 0500=13750 1374 D 78 1374 E 1374 F 78 13750 12 34 CH CL 12

![Solution b n MOV CX BXSI q Addressing Mode base plusIndex addressing Solution - b n MOV CX, [BX+SI] q Addressing Mode : base plus-Index addressing](https://slidetodoc.com/presentation_image/147df18ed65019170dfb901b741f39f8/image-35.jpg)

Solution - b n MOV CX, [BX+SI] q Addressing Mode : base plus-Index addressing mode Effective address=DS*10 H+BX+SI = 11000 +2000+ 0500=13500 n 134 FD 134 FE 134 FF 13500 33 13501 21 CH CL 21 33

![Solution n MOV AH 4500 H q q Addressing Mode direct addressing mode Solution n MOV AH, [4500 H] q q Addressing Mode : direct addressing mode](https://slidetodoc.com/presentation_image/147df18ed65019170dfb901b741f39f8/image-36.jpg)

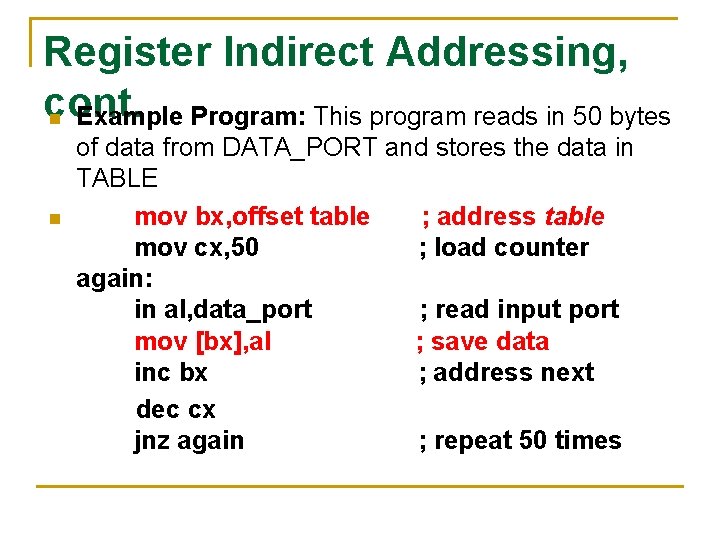

Solution n MOV AH, [4500 H] q q Addressing Mode : direct addressing mode Effective address=DS*10 h+4500 h = 11000 + 4500 = 15500 h 154 FD AH 154 FE 154 FF 55 15500 55 AL