Registers and Shift Registers Discussion D 8 2

![module johnson 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; johnson module johnson 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; johnson](https://slidetodoc.com/presentation_image/8167325cac15597ccc323ad3a6b1dd53/image-14.jpg)

![module rand 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; rand module rand 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; rand](https://slidetodoc.com/presentation_image/8167325cac15597ccc323ad3a6b1dd53/image-18.jpg)

- Slides: 22

Registers and Shift Registers Discussion D 8. 2

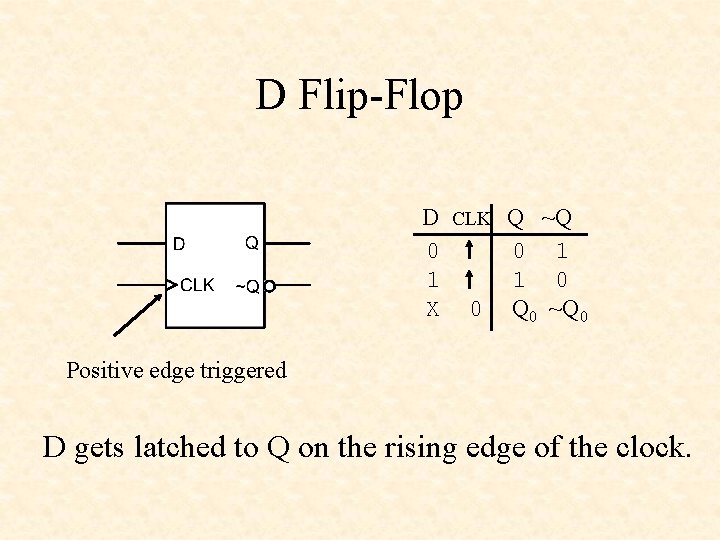

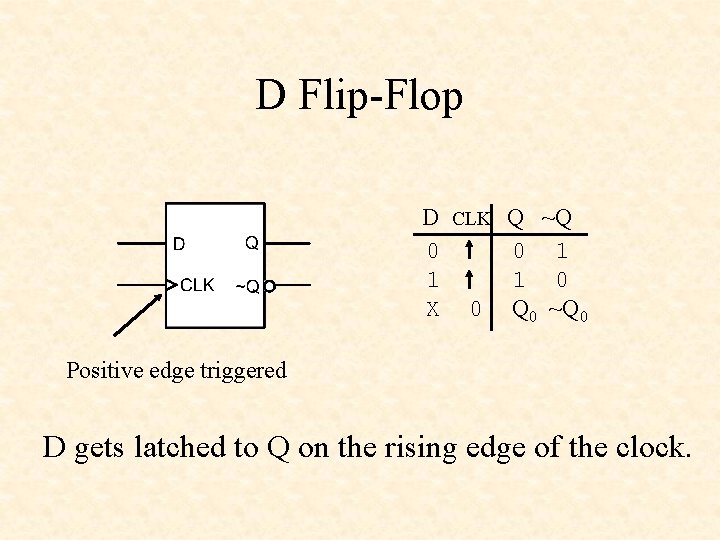

D Flip-Flop D CLK Q ~Q 0 0 1 1 1 0 X 0 Q 0 ~Q 0 Positive edge triggered D gets latched to Q on the rising edge of the clock.

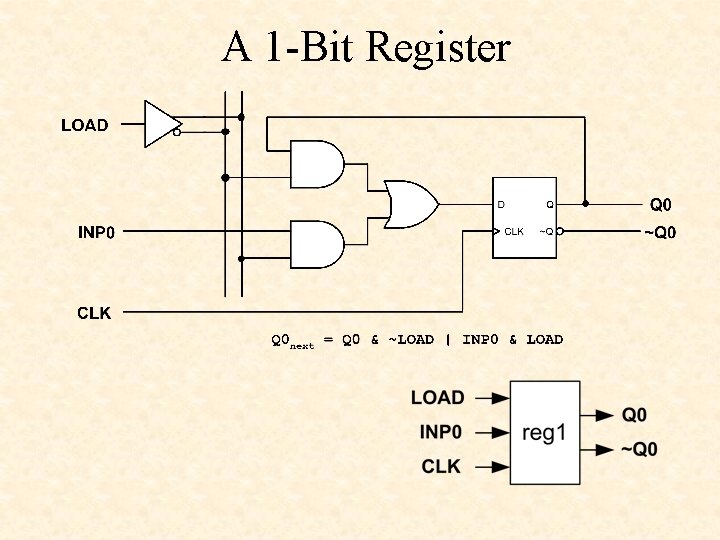

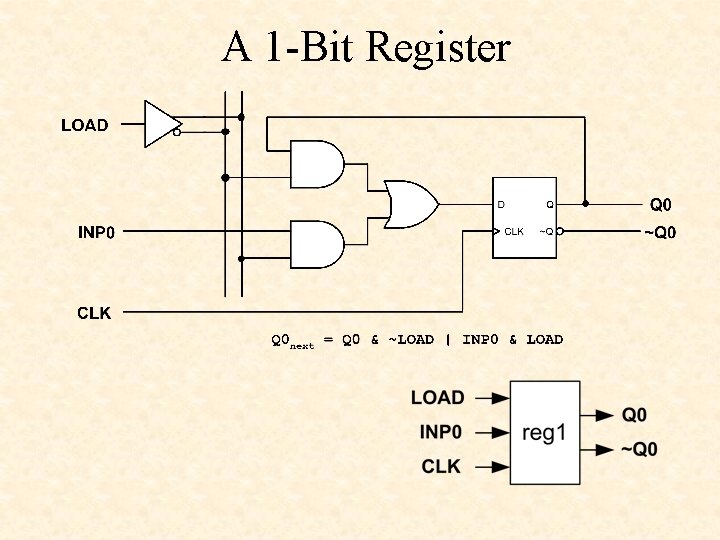

A 1 -Bit Register

A 1 -Bit Register If LOAD = 1, then INP 0 gets latched to Q 0 on the rising edge of the clock, CLK

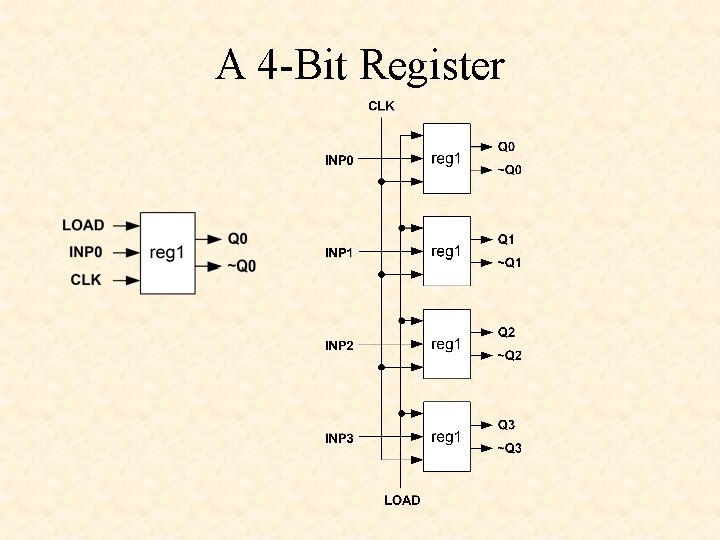

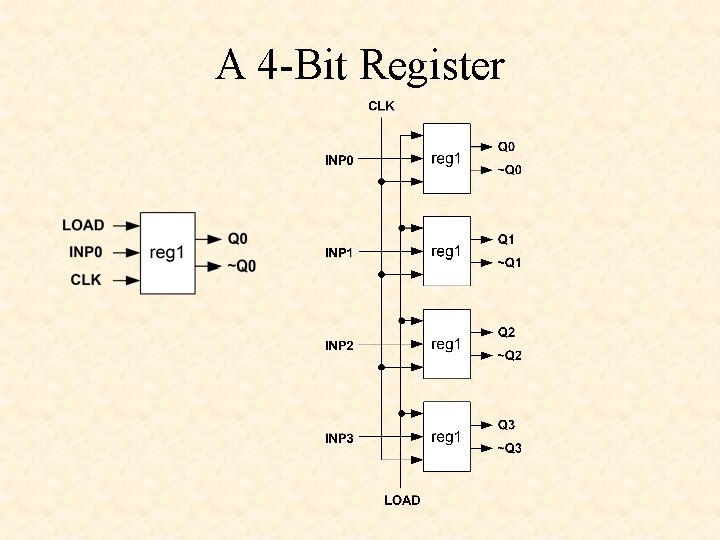

A 4 -Bit Register

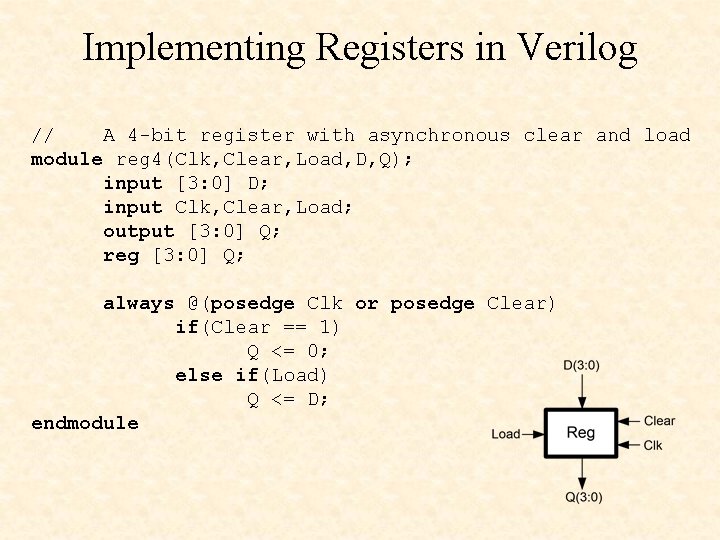

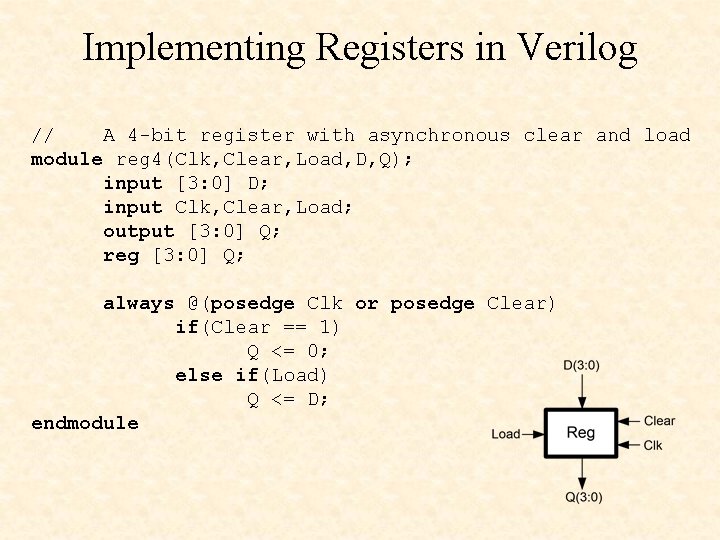

Implementing Registers in Verilog // A 4 -bit register with asynchronous clear and load module reg 4(Clk, Clear, Load, D, Q); input [3: 0] D; input Clk, Clear, Load; output [3: 0] Q; reg [3: 0] Q; always @(posedge Clk or posedge Clear) if(Clear == 1) Q <= 0; else if(Load) Q <= D; endmodule

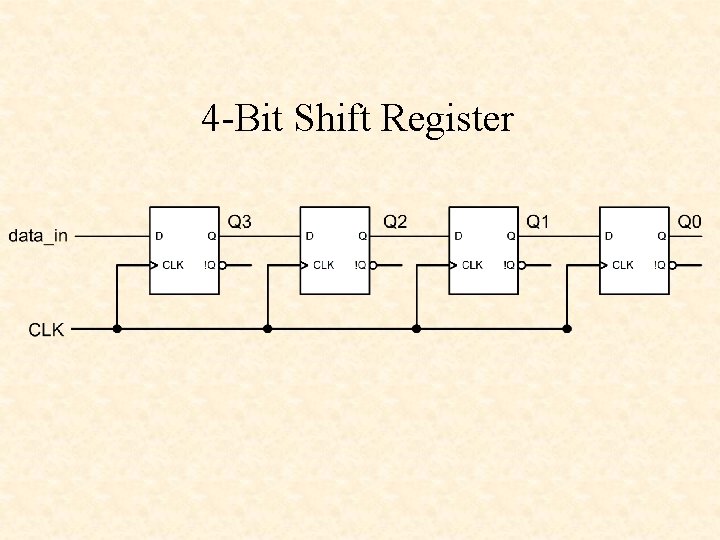

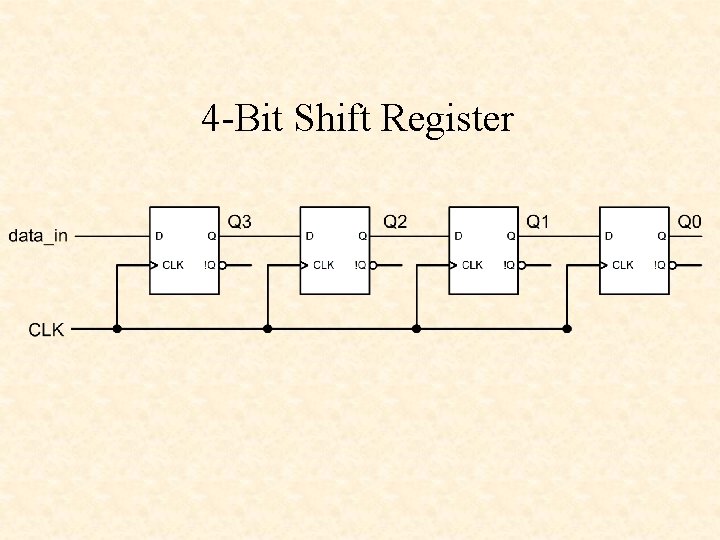

4 -Bit Shift Register

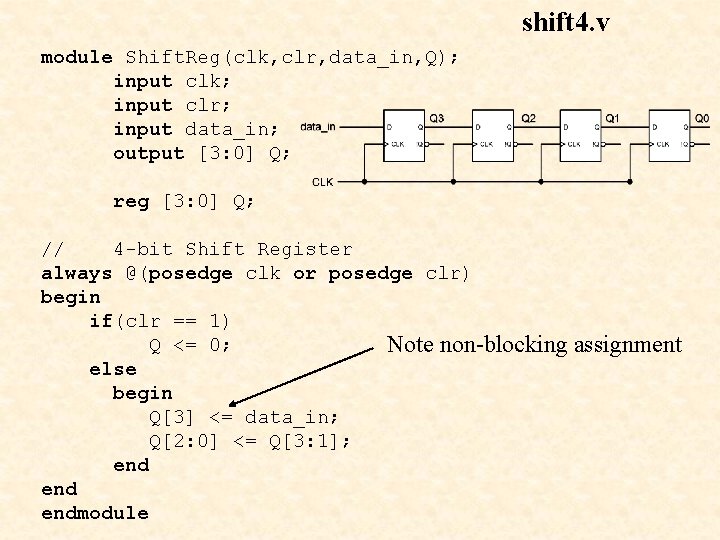

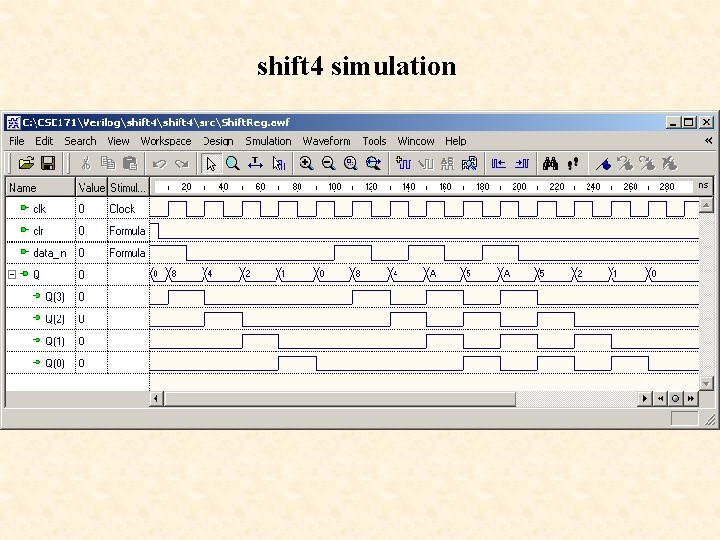

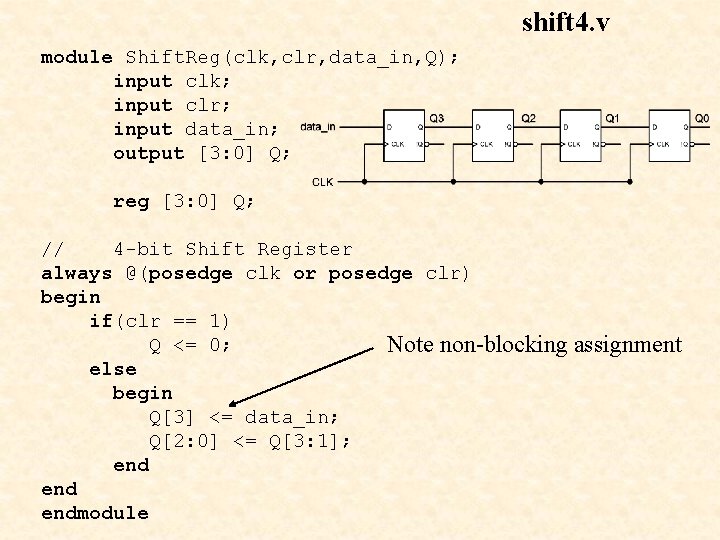

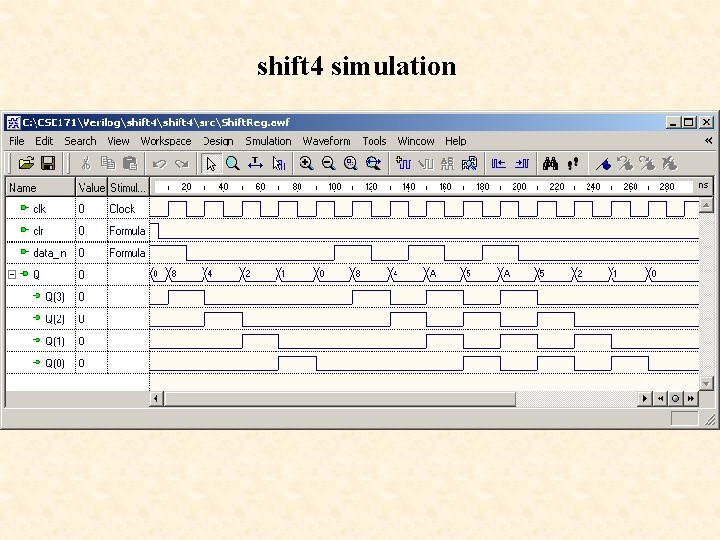

shift 4. v module Shift. Reg(clk, clr, data_in, Q); input clk; input clr; input data_in; output [3: 0] Q; reg [3: 0] Q; // 4 -bit Shift Register always @(posedge clk or posedge clr) begin if(clr == 1) Q <= 0; Note non-blocking else begin Q[3] <= data_in; Q[2: 0] <= Q[3: 1]; end endmodule assignment

shift 4 simulation

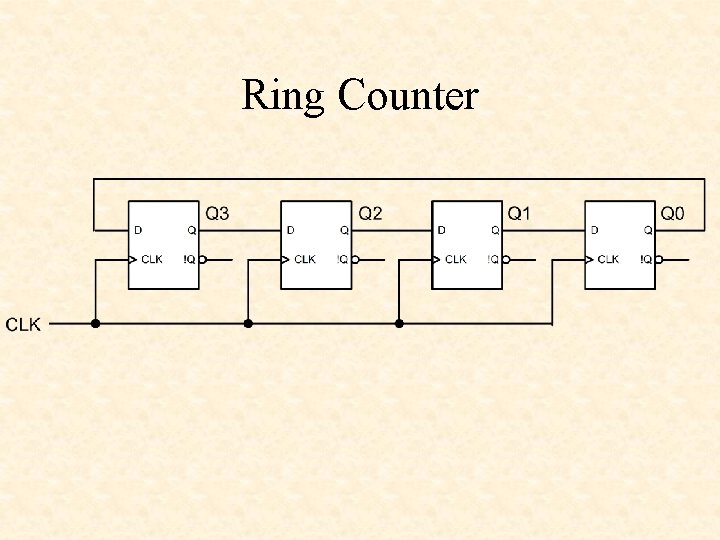

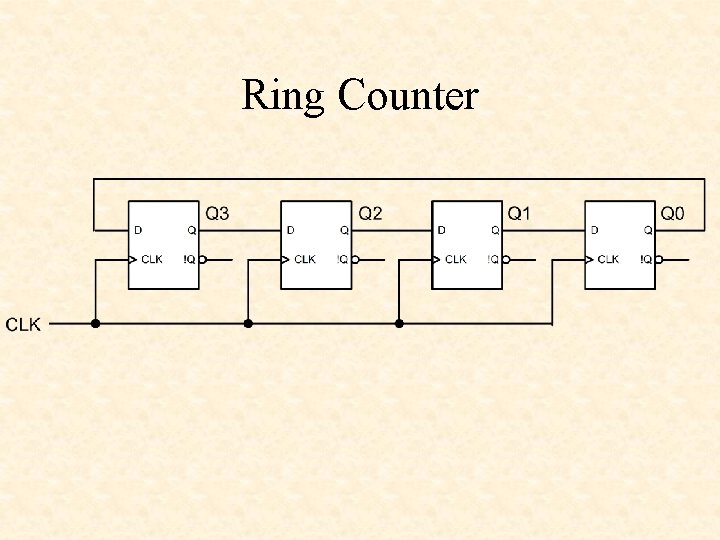

Ring Counter

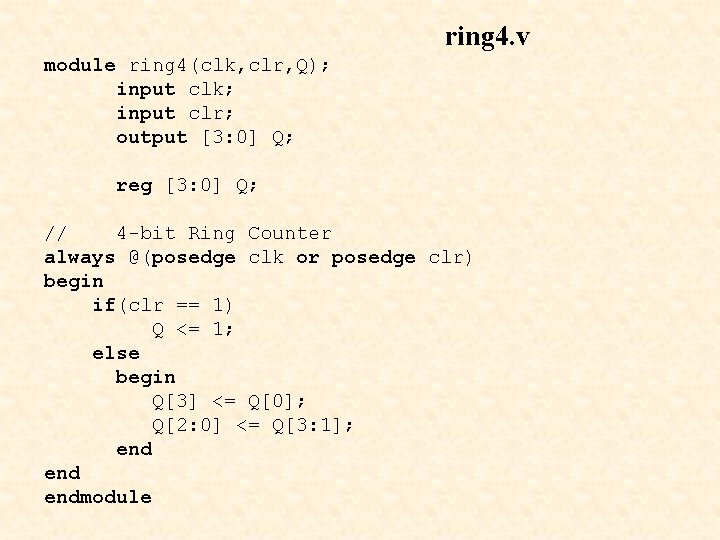

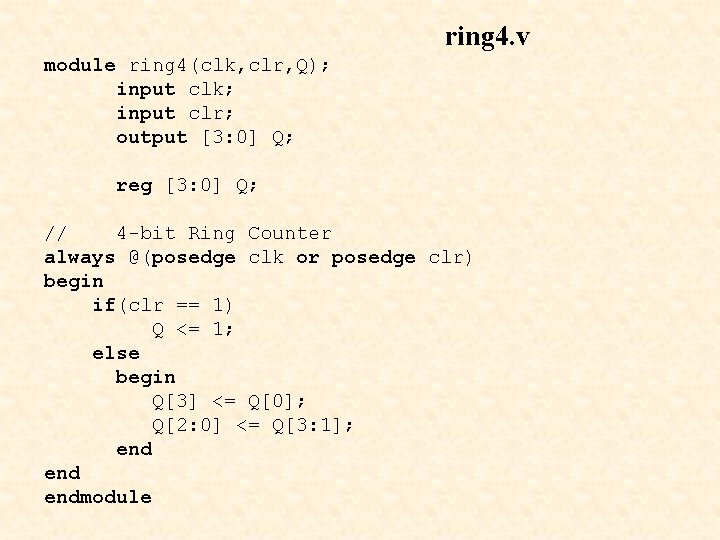

ring 4. v module ring 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; reg [3: 0] Q; // 4 -bit Ring Counter always @(posedge clk or posedge clr) begin if(clr == 1) Q <= 1; else begin Q[3] <= Q[0]; Q[2: 0] <= Q[3: 1]; end endmodule

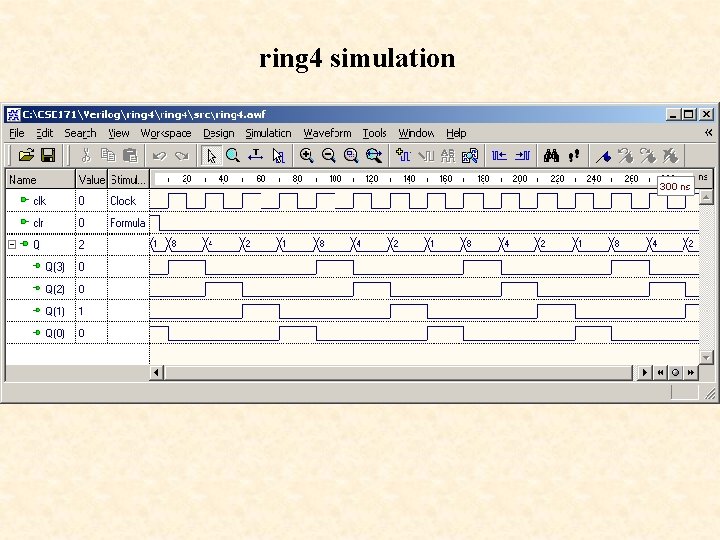

ring 4 simulation

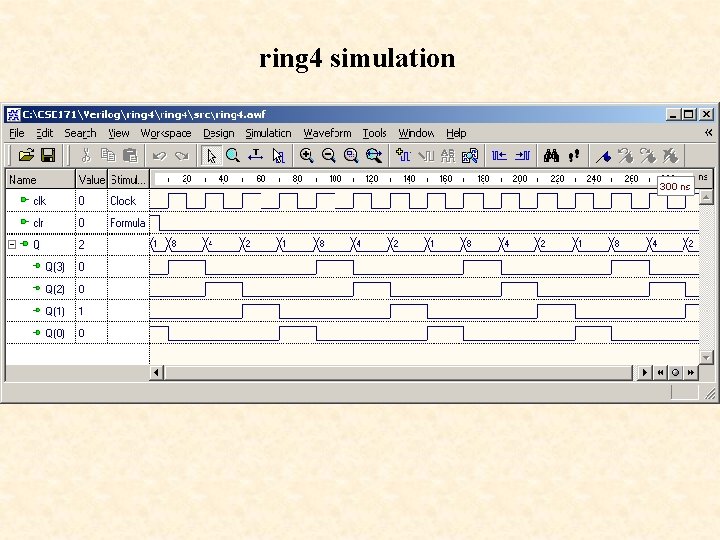

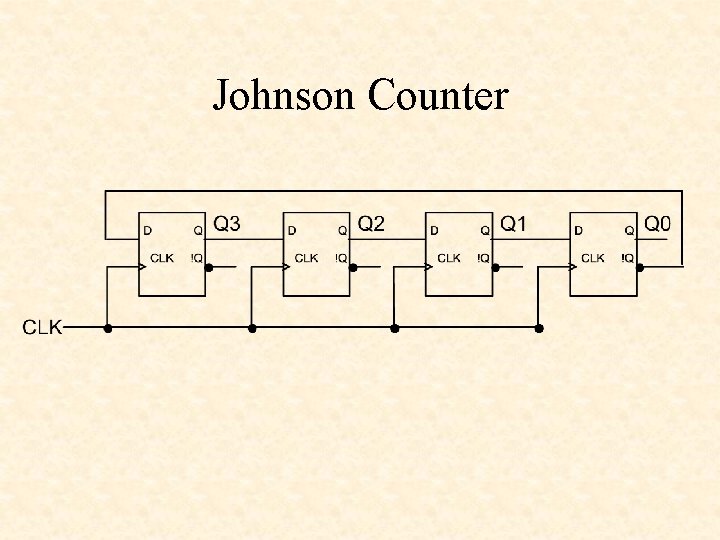

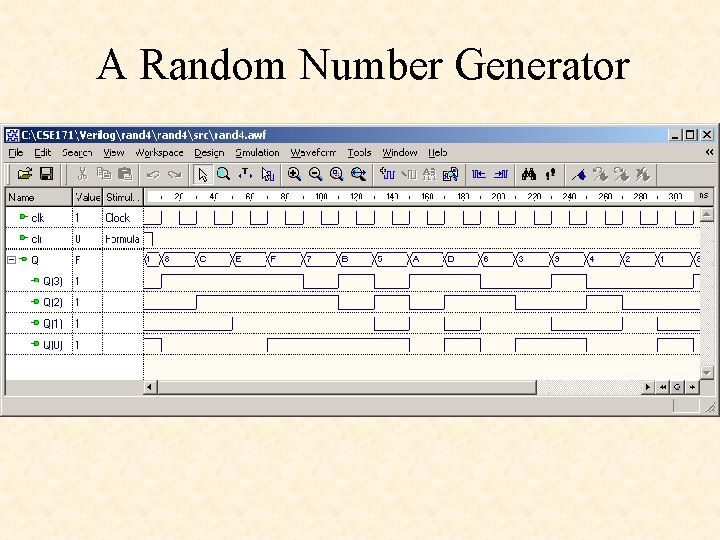

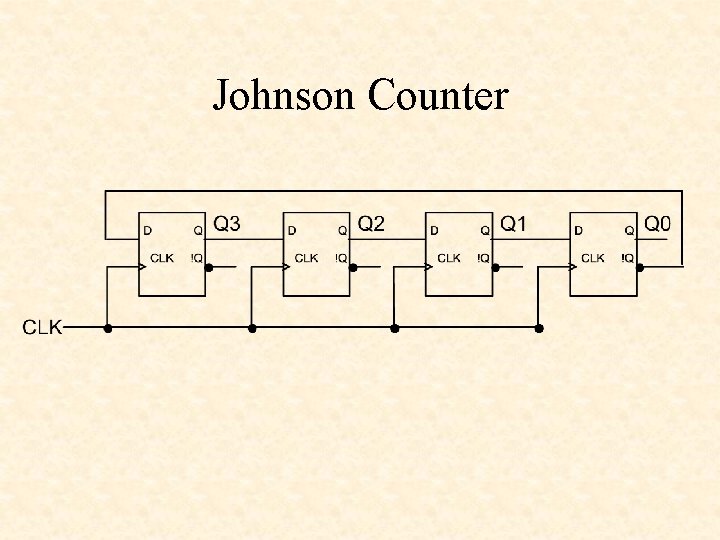

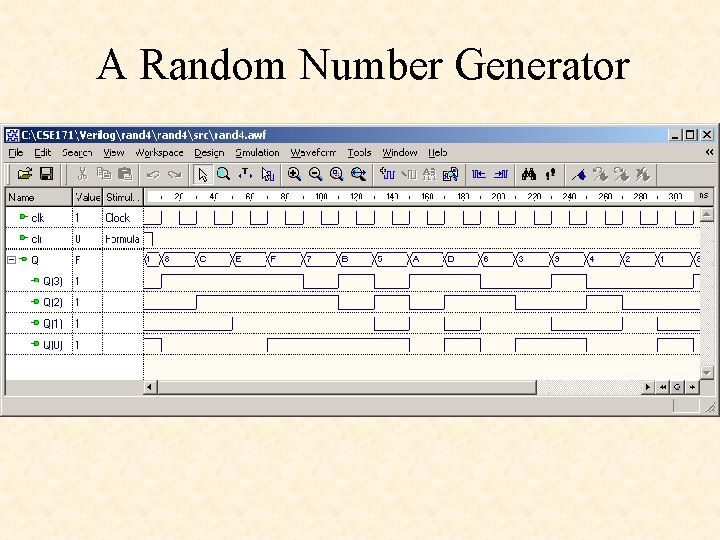

Johnson Counter

![module johnson 4clk clr Q input clk input clr output 3 0 Q johnson module johnson 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; johnson](https://slidetodoc.com/presentation_image/8167325cac15597ccc323ad3a6b1dd53/image-14.jpg)

module johnson 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; johnson 4. v reg [3: 0] Q; // 4 -bit Johnson Counter always @(posedge clk or posedge clr) begin if(clr == 1) Q <= 0; else begin Q[3] <= ~Q[0]; Q[2: 0] <= Q[3: 1]; end endmodule

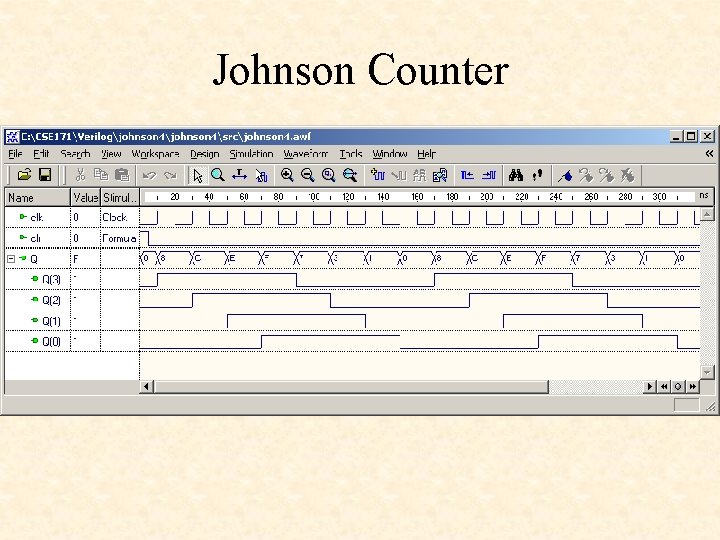

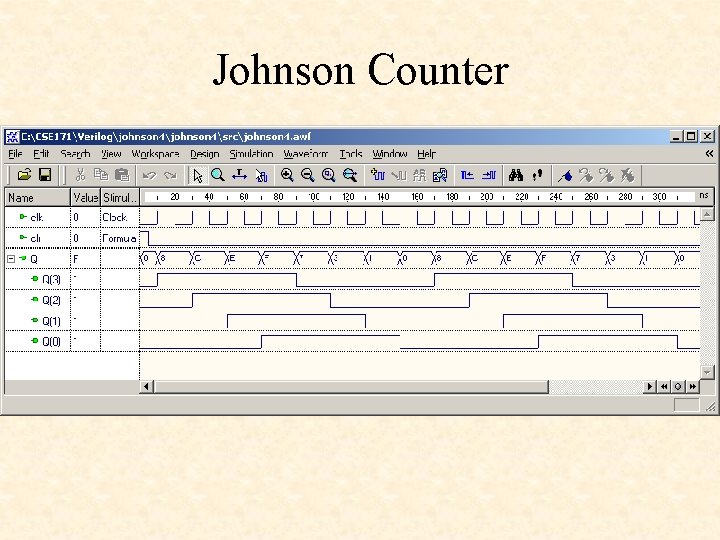

Johnson Counter

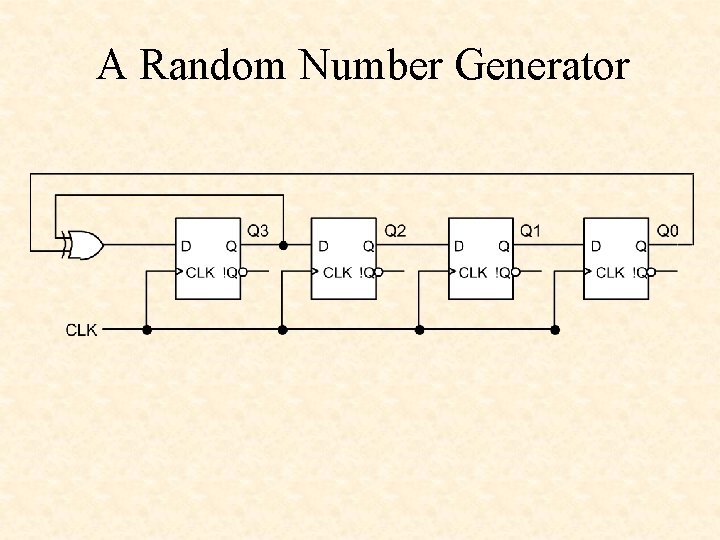

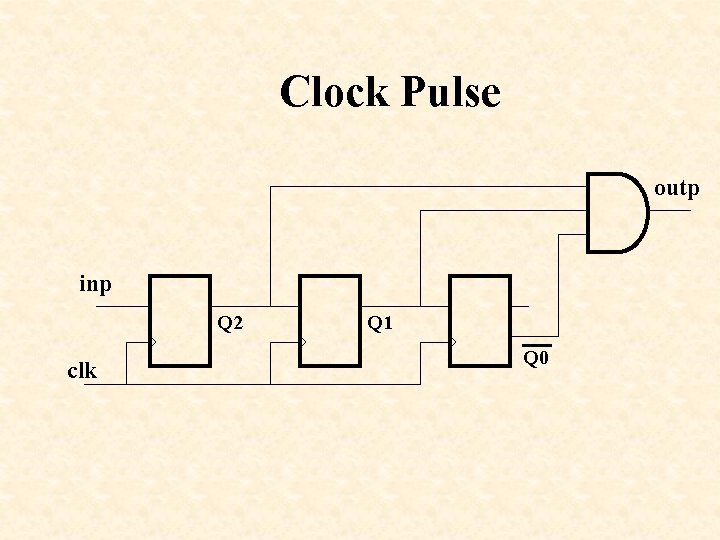

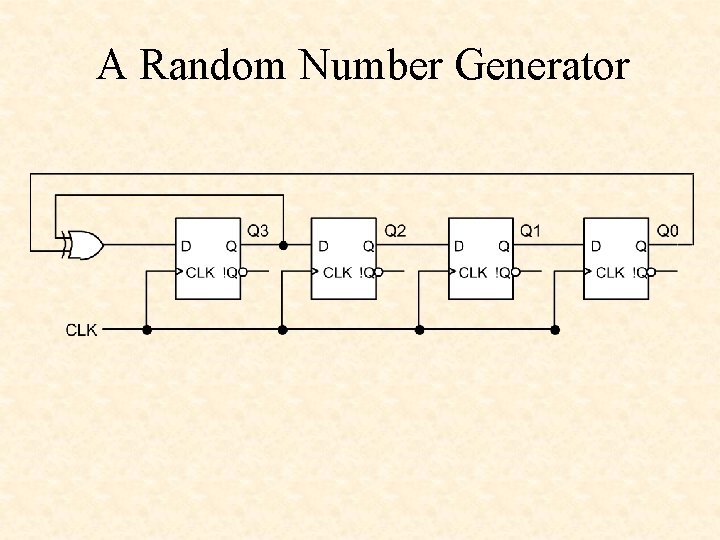

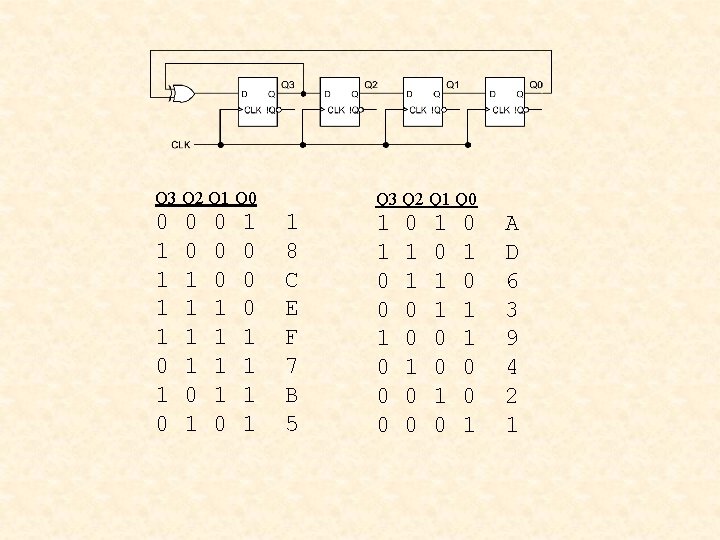

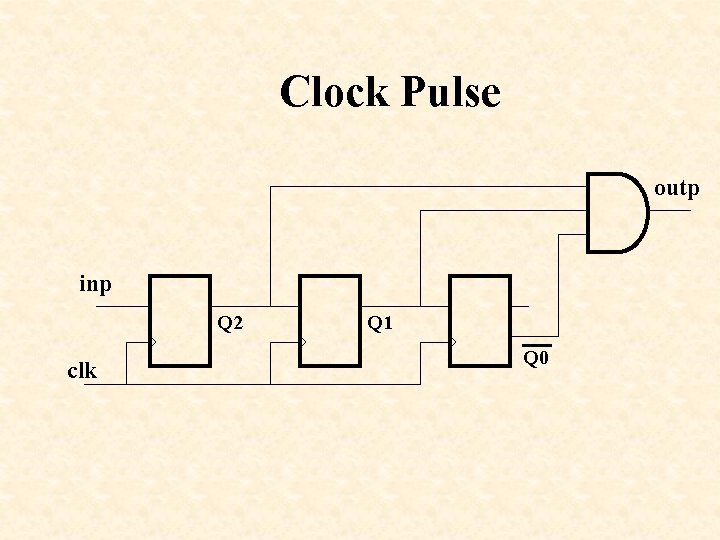

A Random Number Generator

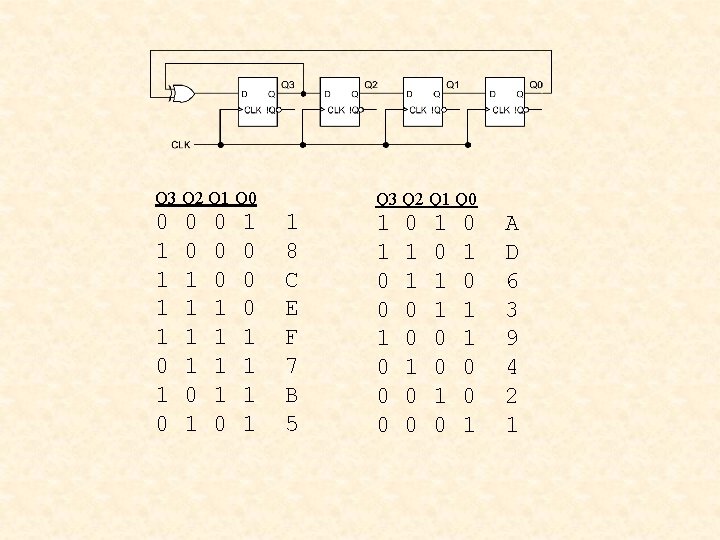

Q 3 Q 2 Q 1 Q 0 0 1 1 1 1 0 1 0 0 0 1 1 Q 3 Q 2 Q 1 Q 0 1 8 C E F 7 B 5 1 1 0 0 0 0 1 1 0 0 1 0 1 1 0 0 1 A D 6 3 9 4 2 1

![module rand 4clk clr Q input clk input clr output 3 0 Q rand module rand 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; rand](https://slidetodoc.com/presentation_image/8167325cac15597ccc323ad3a6b1dd53/image-18.jpg)

module rand 4(clk, clr, Q); input clk; input clr; output [3: 0] Q; rand 4. v reg [3: 0] Q; // 4 -bit Random number generator always @(posedge clk or posedge clr) begin if(clr == 1) Q <= 1; else begin Q[3] <= Q[3] ^ Q[0]; Q[2: 0] <= Q[3: 1]; end endmodule

A Random Number Generator

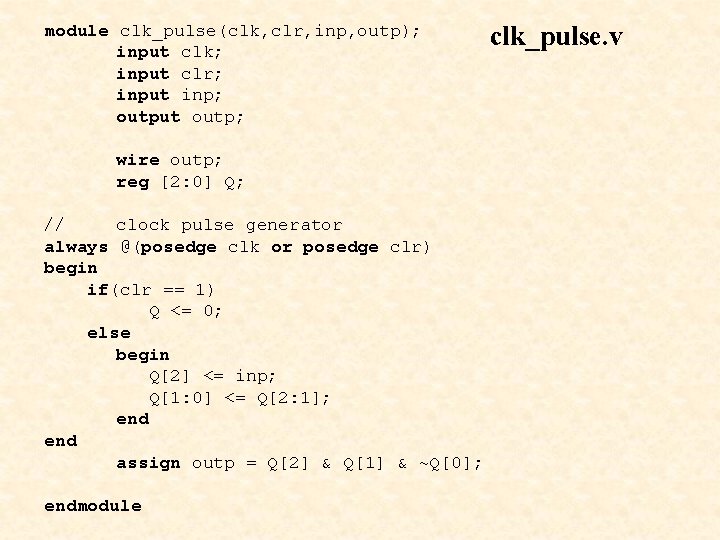

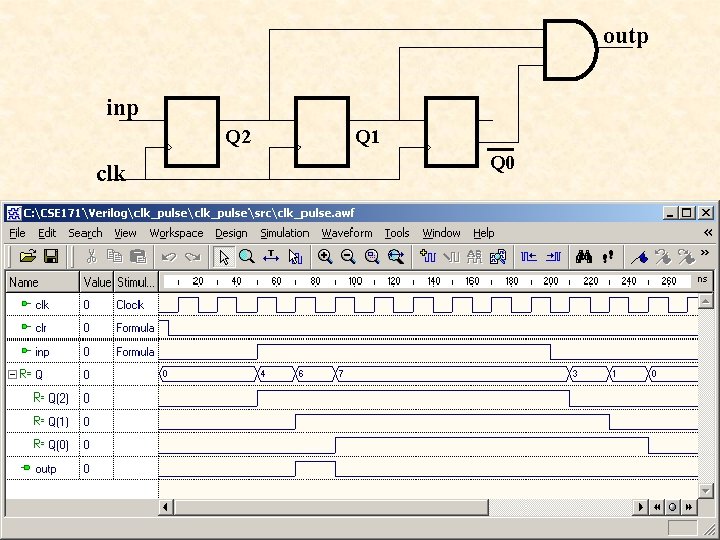

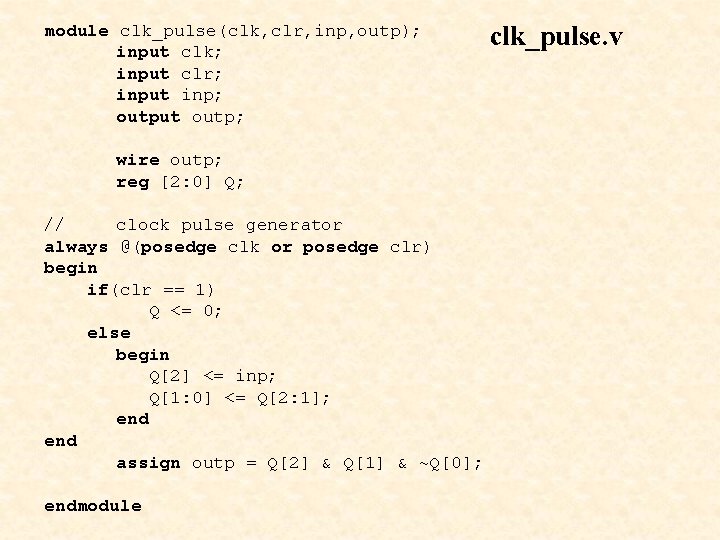

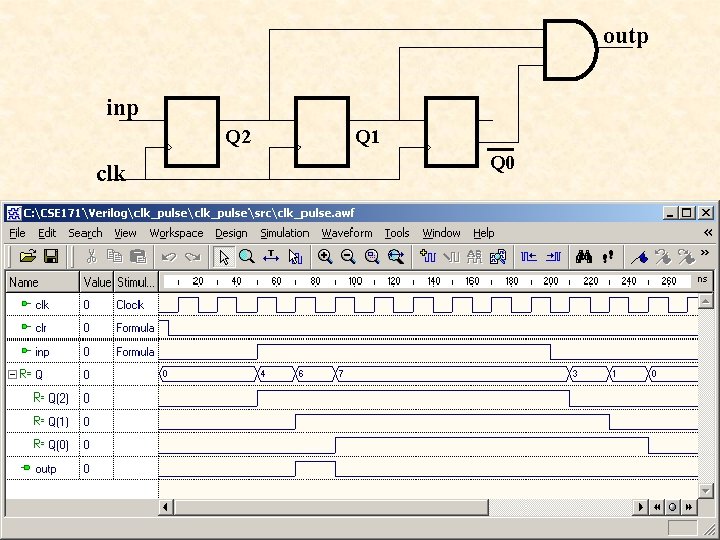

Clock Pulse outp inp Q 2 clk Q 1 Q 0

module clk_pulse(clk, clr, inp, outp); input clk; input clr; input inp; output outp; wire outp; reg [2: 0] Q; // clock pulse generator always @(posedge clk or posedge clr) begin if(clr == 1) Q <= 0; else begin Q[2] <= inp; Q[1: 0] <= Q[2: 1]; end assign outp = Q[2] & Q[1] & ~Q[0]; endmodule clk_pulse. v

outp inp Q 2 clk Q 1 Q 0