Registers Discussion D 5 1 Examples 30 Registers

- Slides: 18

Registers Discussion D 5. 1 Examples 30

Registers and Counters • 1 -Bit Register • 4 -Bit Register • N-Bit Register

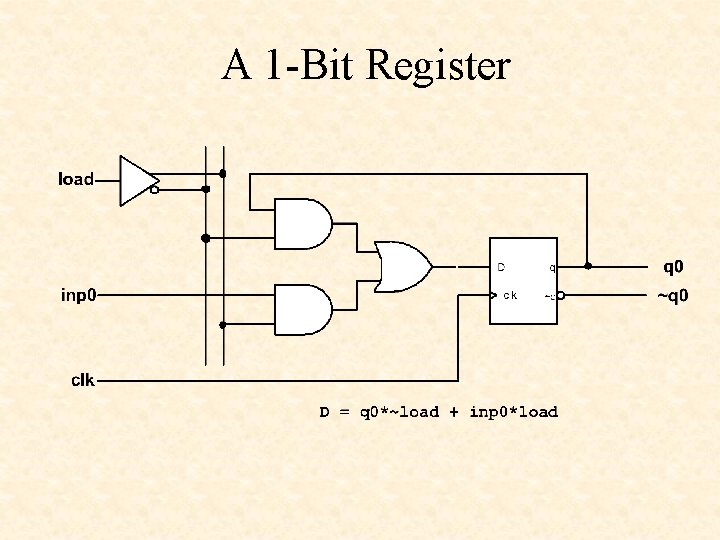

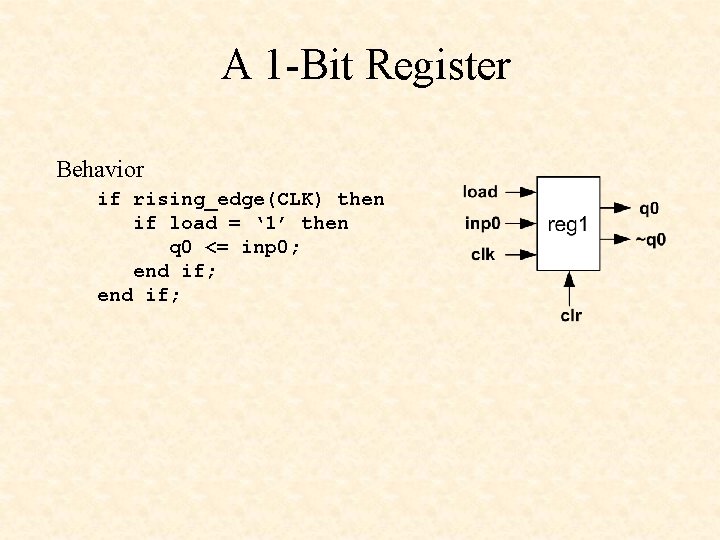

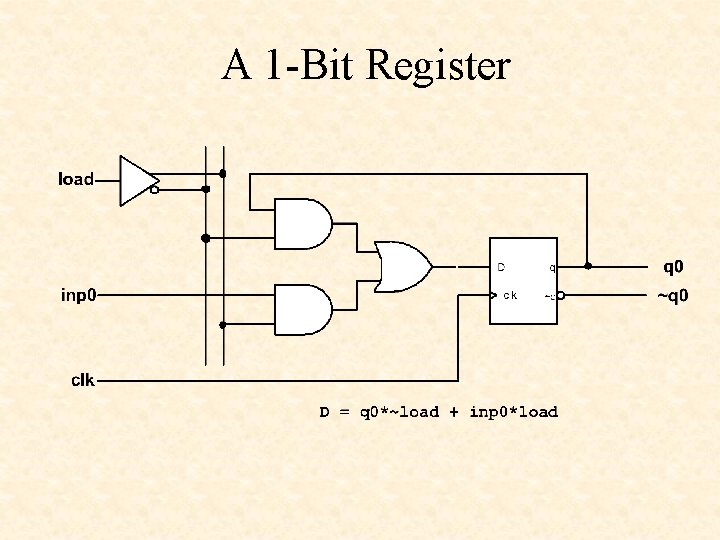

A 1 -Bit Register

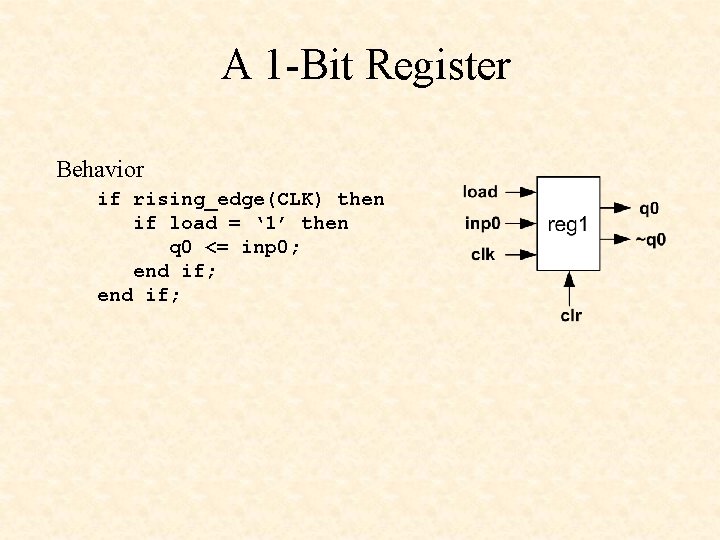

A 1 -Bit Register Behavior if rising_edge(CLK) then if load = ‘ 1’ then q 0 <= inp 0; end if;

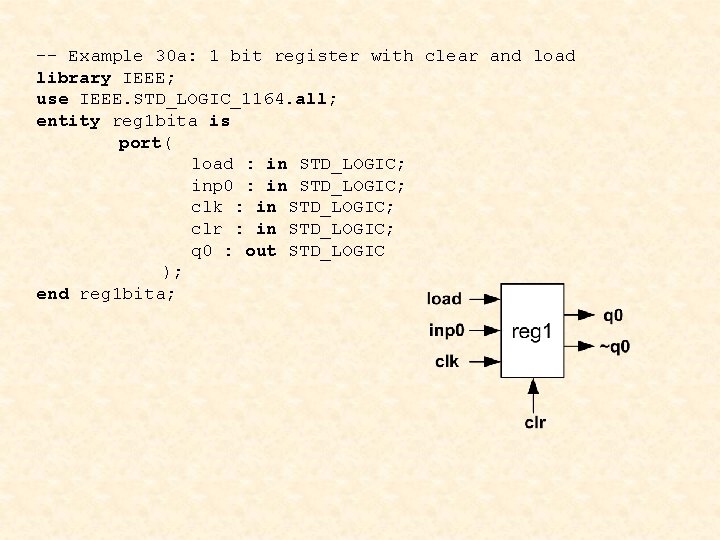

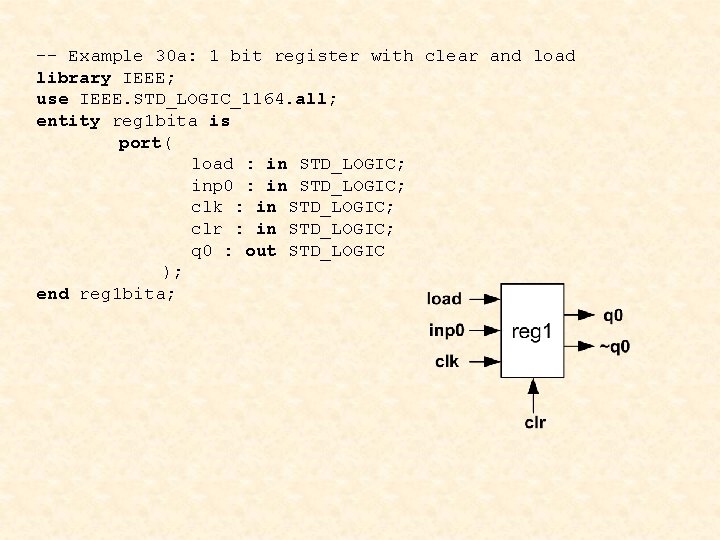

-- Example 30 a: 1 bit register with clear and load library IEEE; use IEEE. STD_LOGIC_1164. all; entity reg 1 bita is port( load : in STD_LOGIC; inp 0 : in STD_LOGIC; clk : in STD_LOGIC; clr : in STD_LOGIC; q 0 : out STD_LOGIC ); end reg 1 bita;

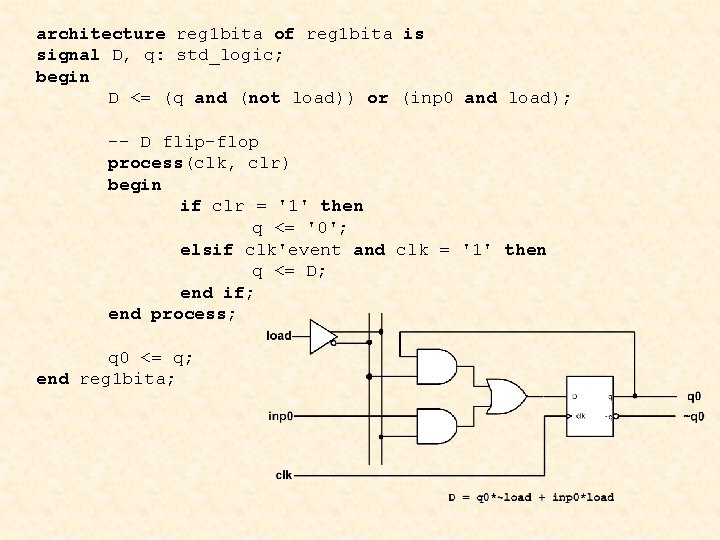

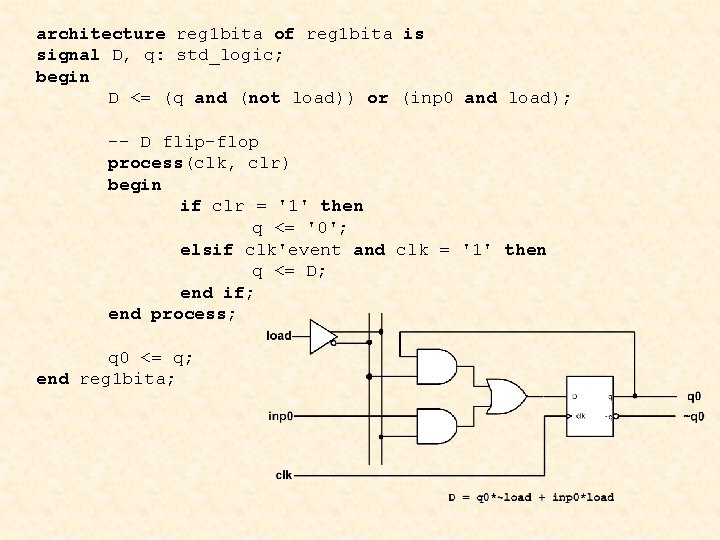

architecture reg 1 bita of reg 1 bita is signal D, q: std_logic; begin D <= (q and (not load)) or (inp 0 and load); -- D flip-flop process(clk, clr) begin if clr = '1' then q <= '0'; elsif clk'event and clk = '1' then q <= D; end if; end process; q 0 <= q; end reg 1 bita;

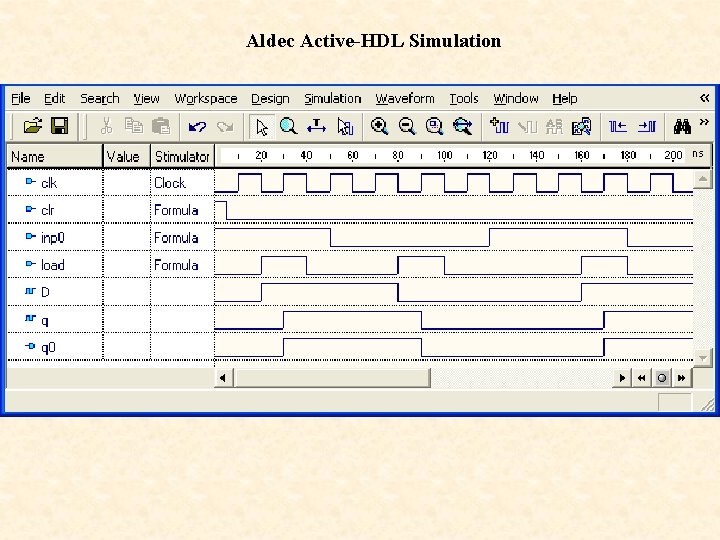

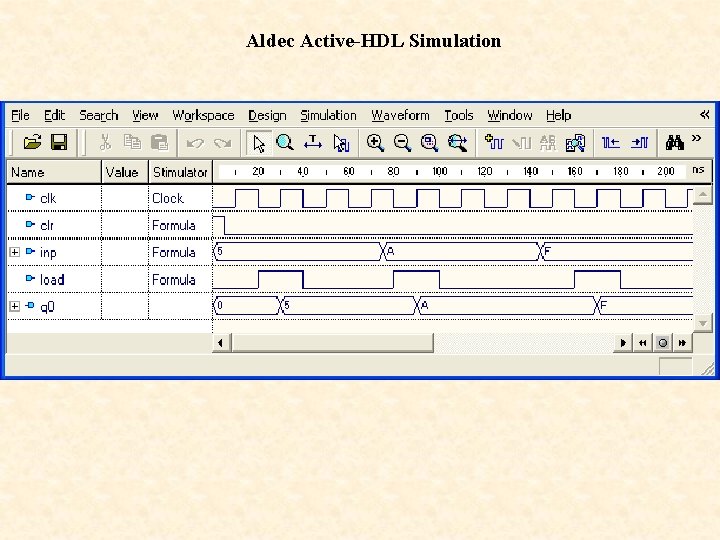

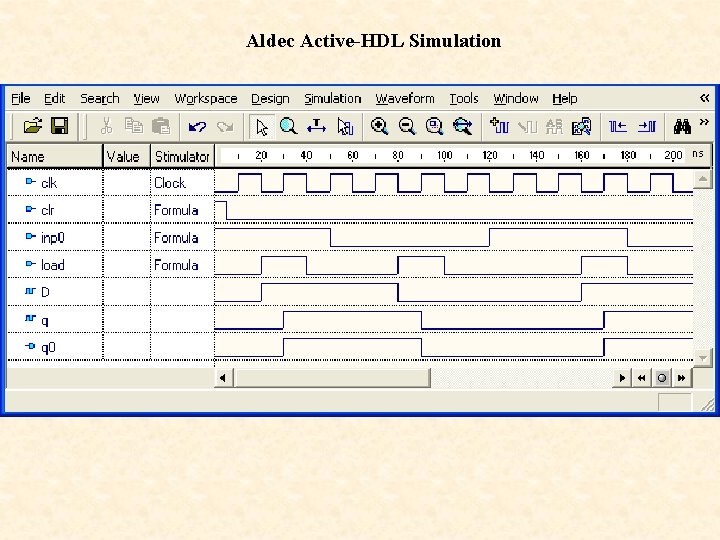

Aldec Active-HDL Simulation

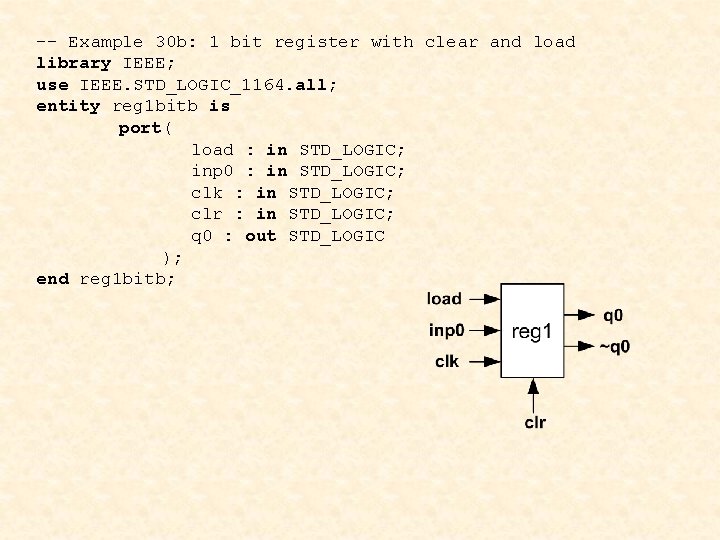

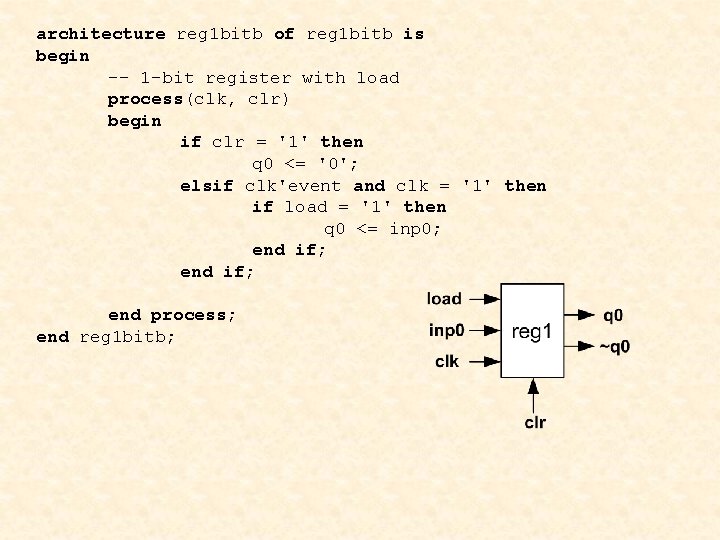

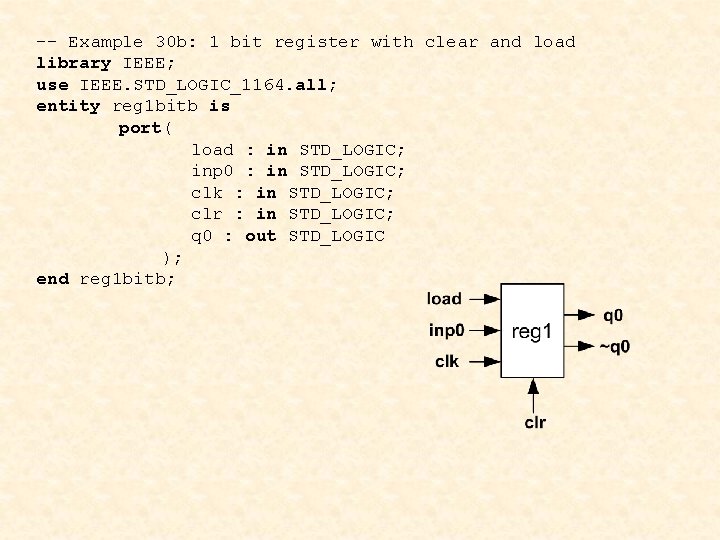

-- Example 30 b: 1 bit register with clear and load library IEEE; use IEEE. STD_LOGIC_1164. all; entity reg 1 bitb is port( load : in STD_LOGIC; inp 0 : in STD_LOGIC; clk : in STD_LOGIC; clr : in STD_LOGIC; q 0 : out STD_LOGIC ); end reg 1 bitb;

architecture reg 1 bitb of reg 1 bitb is begin -- 1 -bit register with load process(clk, clr) begin if clr = '1' then q 0 <= '0'; elsif clk'event and clk = '1' then if load = '1' then q 0 <= inp 0; end if; end process; end reg 1 bitb;

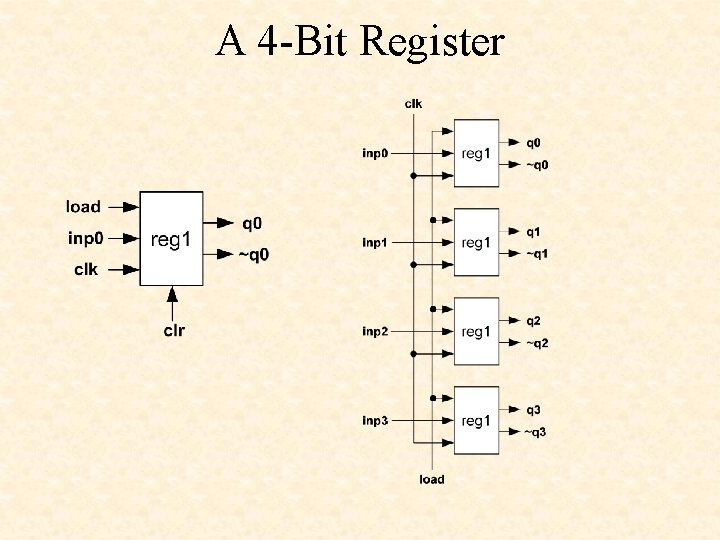

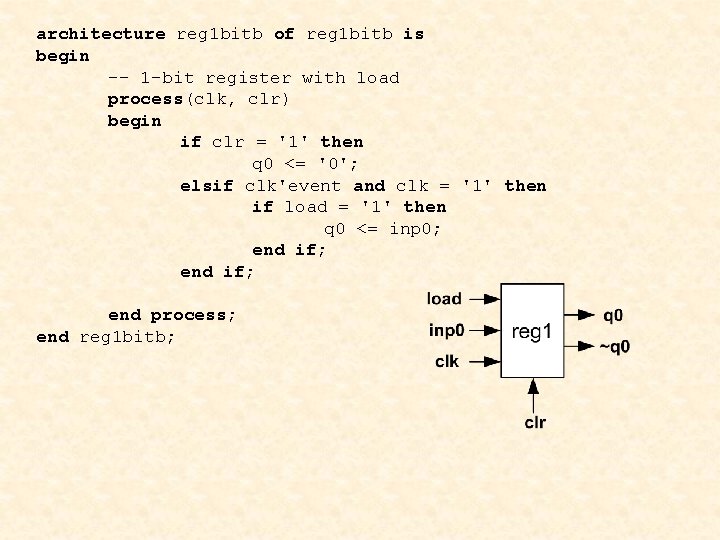

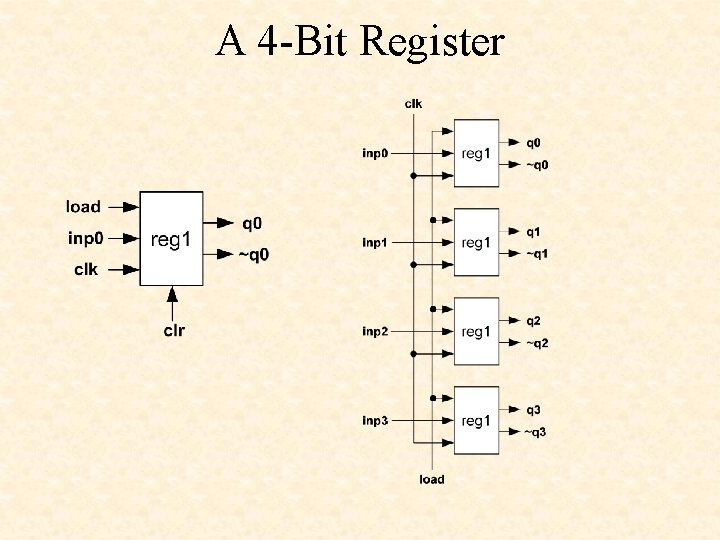

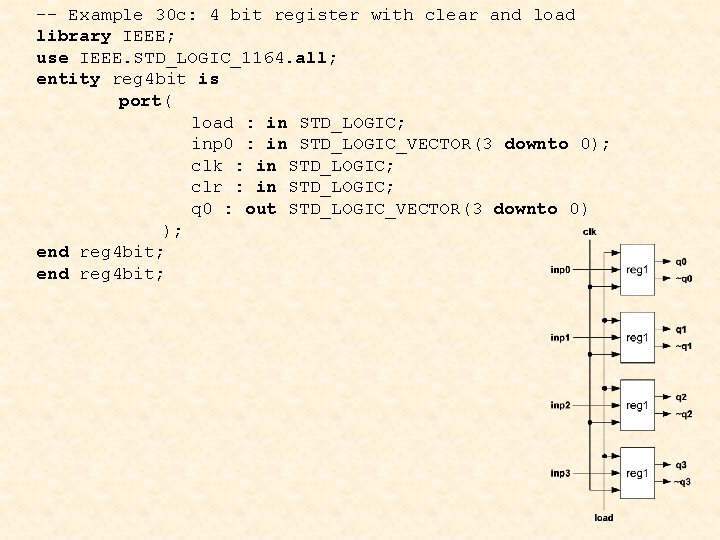

A 4 -Bit Register

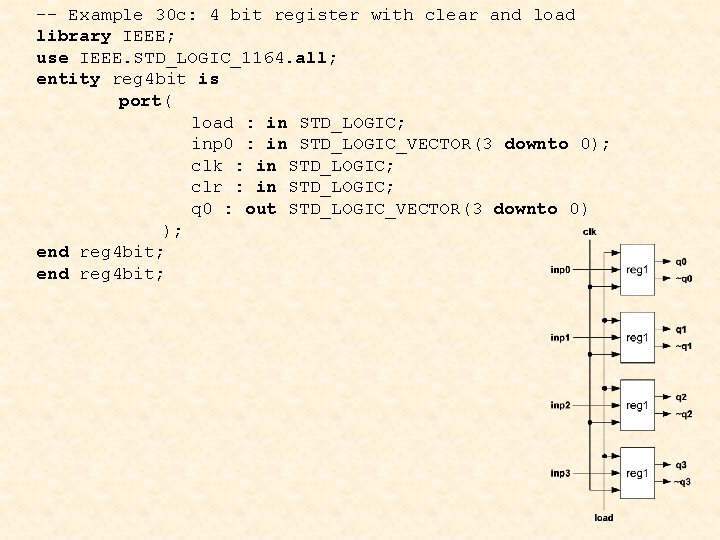

-- Example 30 c: 4 bit register with clear and load library IEEE; use IEEE. STD_LOGIC_1164. all; entity reg 4 bit is port( load : in STD_LOGIC; inp 0 : in STD_LOGIC_VECTOR(3 downto 0); clk : in STD_LOGIC; clr : in STD_LOGIC; q 0 : out STD_LOGIC_VECTOR(3 downto 0) ); end reg 4 bit;

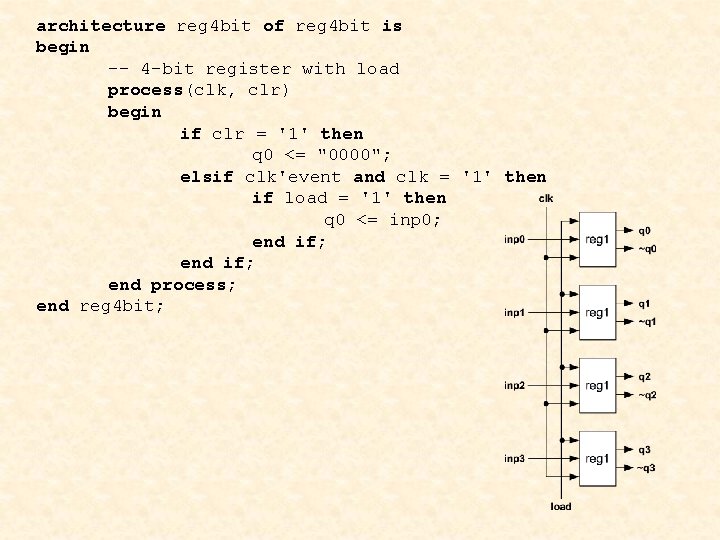

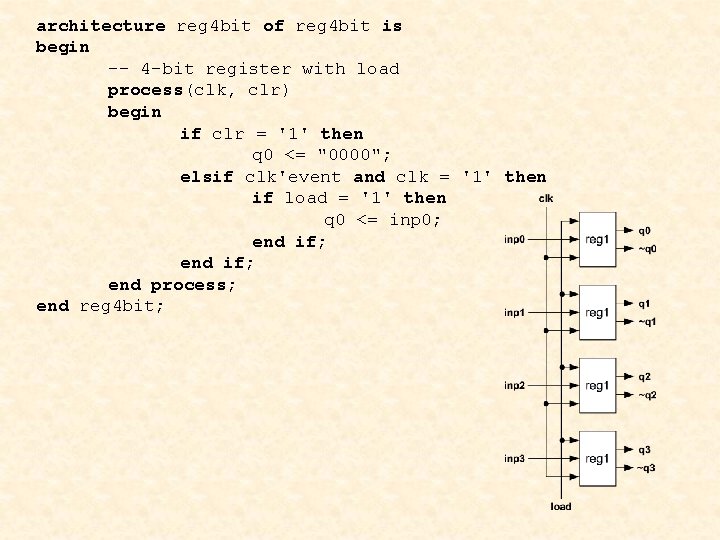

architecture reg 4 bit of reg 4 bit is begin -- 4 -bit register with load process(clk, clr) begin if clr = '1' then q 0 <= "0000"; elsif clk'event and clk = '1' then if load = '1' then q 0 <= inp 0; end if; end process; end reg 4 bit;

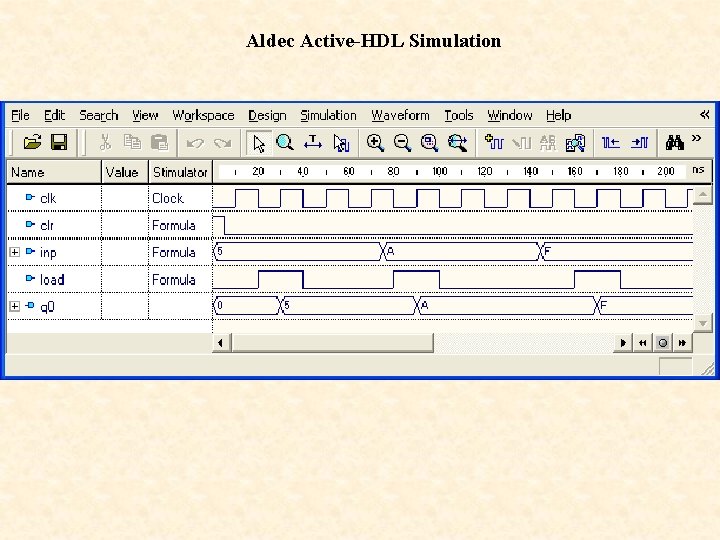

Aldec Active-HDL Simulation

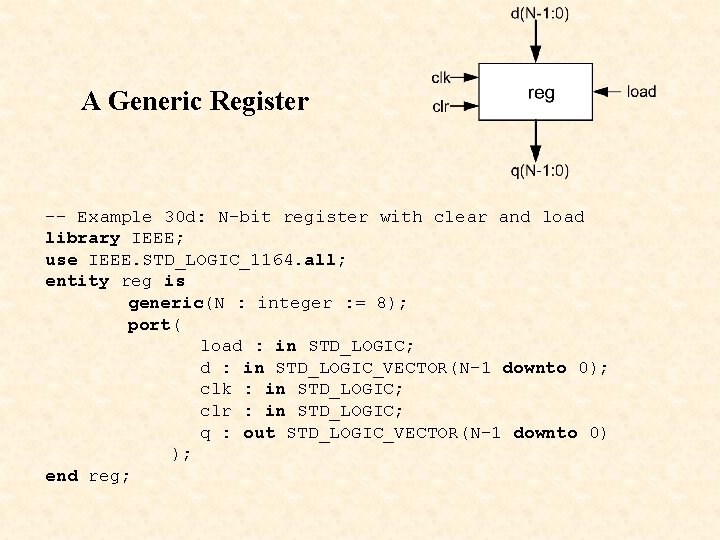

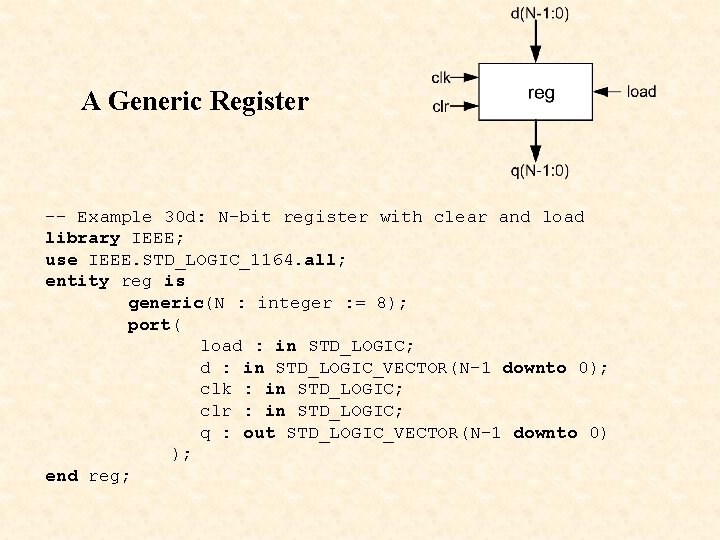

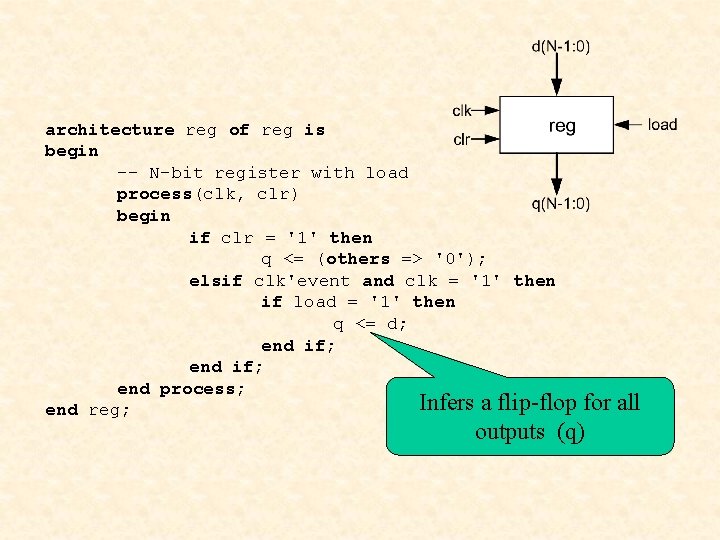

A Generic Register -- Example 30 d: N-bit register with clear and load library IEEE; use IEEE. STD_LOGIC_1164. all; entity reg is generic(N : integer : = 8); port( load : in STD_LOGIC; d : in STD_LOGIC_VECTOR(N-1 downto 0); clk : in STD_LOGIC; clr : in STD_LOGIC; q : out STD_LOGIC_VECTOR(N-1 downto 0) ); end reg;

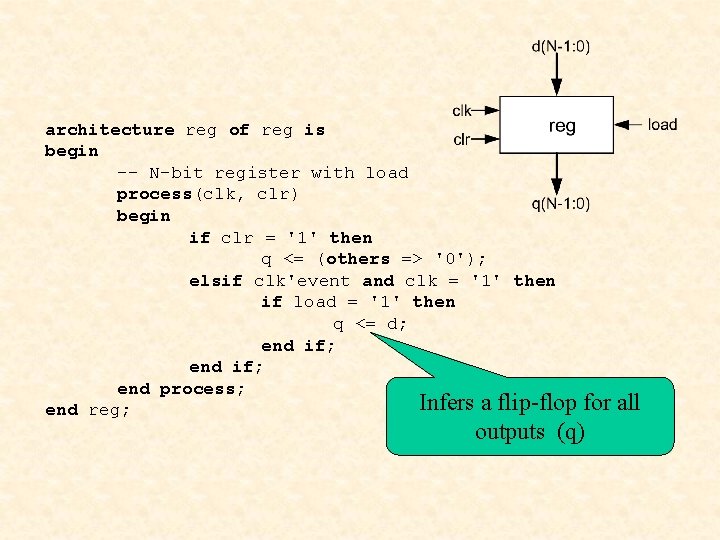

architecture reg of reg is begin -- N-bit register with load process(clk, clr) begin if clr = '1' then q <= (others => '0'); elsif clk'event and clk = '1' then if load = '1' then q <= d; end if; end process; Infers a flip-flop end reg; for all outputs (q)

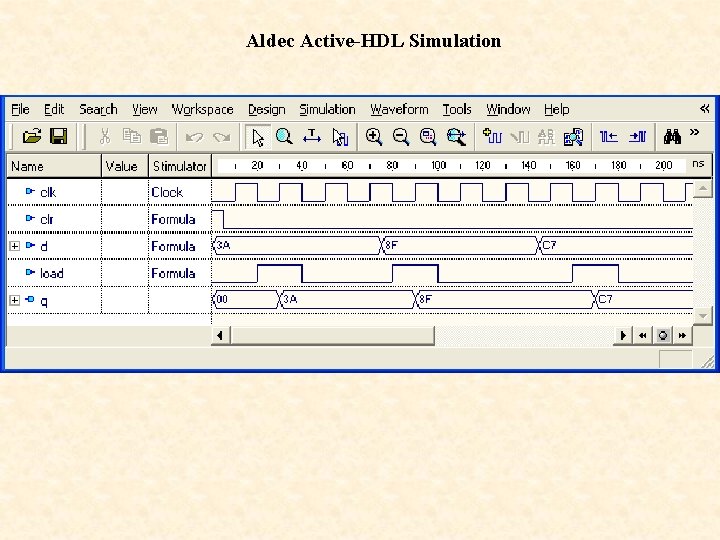

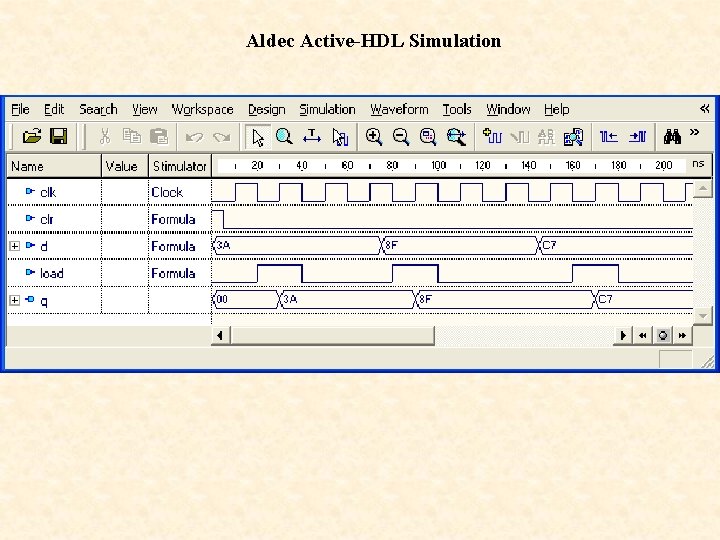

Aldec Active-HDL Simulation

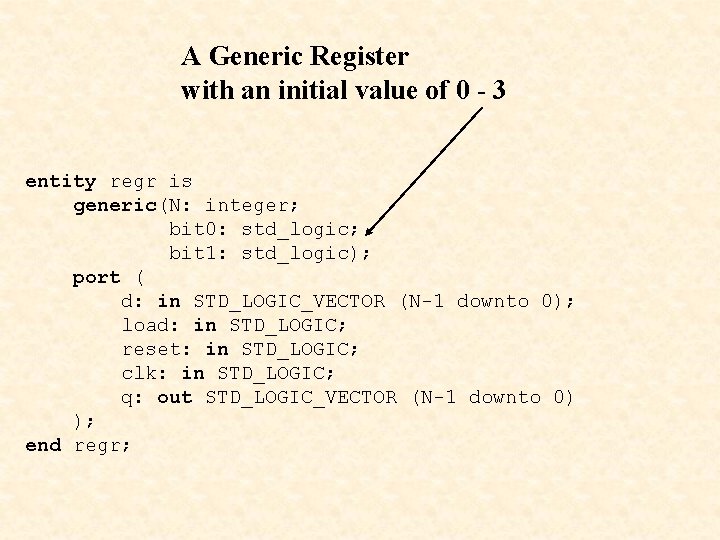

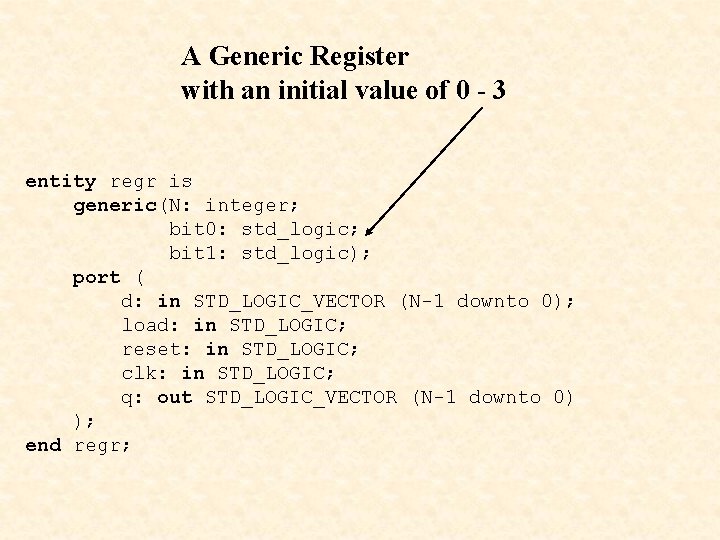

A Generic Register with an initial value of 0 - 3 entity regr is generic(N: integer; bit 0: std_logic; bit 1: std_logic); port ( d: in STD_LOGIC_VECTOR (N-1 downto 0); load: in STD_LOGIC; reset: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (N-1 downto 0) ); end regr;

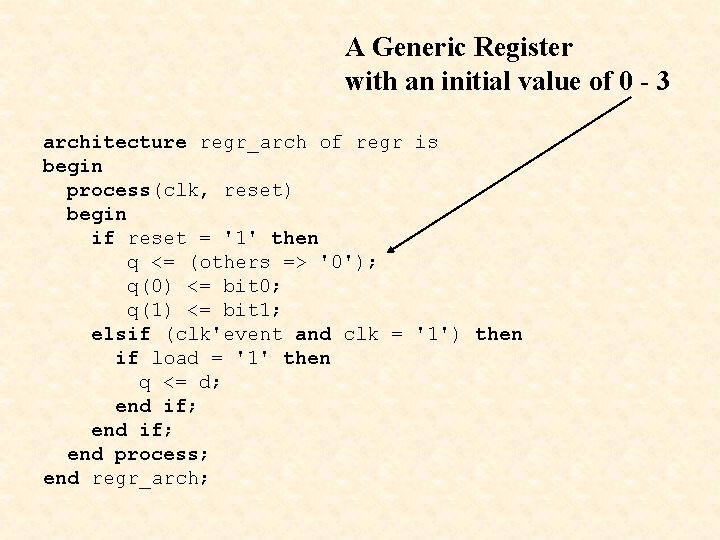

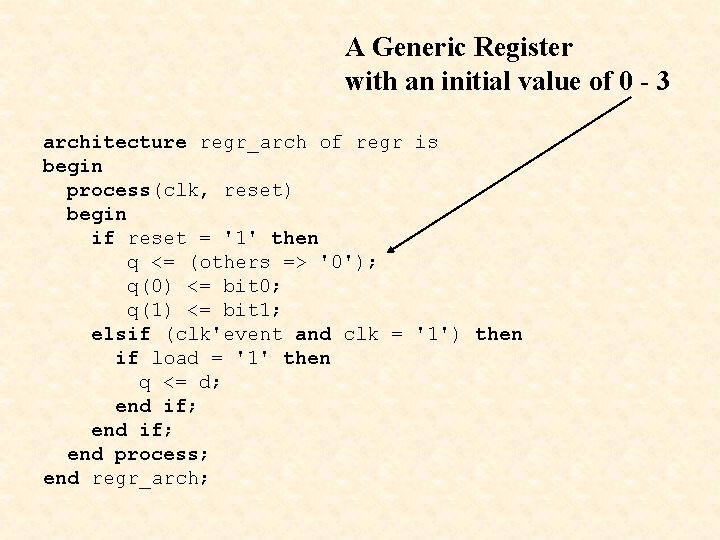

A Generic Register with an initial value of 0 - 3 architecture regr_arch of regr is begin process(clk, reset) begin if reset = '1' then q <= (others => '0'); q(0) <= bit 0; q(1) <= bit 1; elsif (clk'event and clk = '1') then if load = '1' then q <= d; end if; end process; end regr_arch;