80386 Microprocessor Course Outcome Apply the basic knowledge

80386 Microprocessor Course Outcome Apply the basic knowledge of Microprocessor to Computer System Architecture

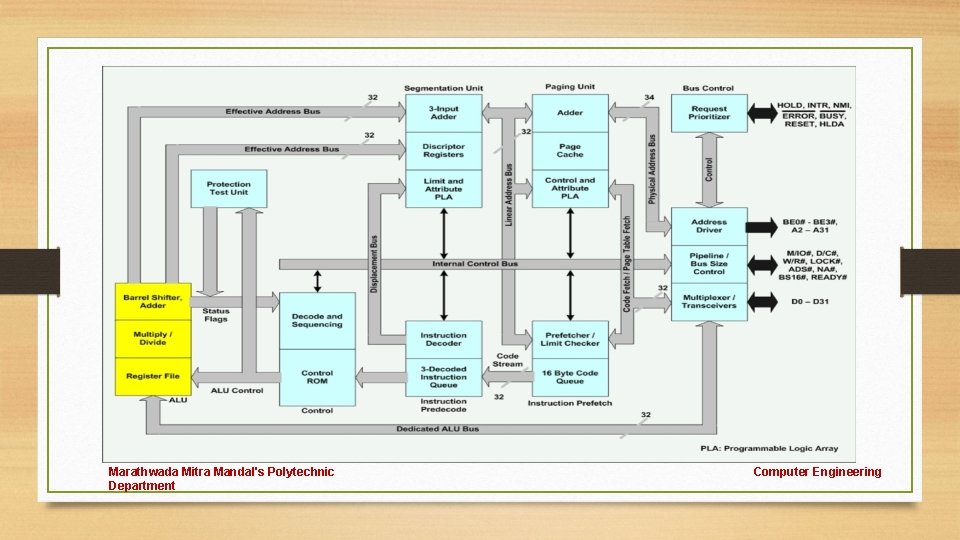

Architecture & Signal description Of 80386 Central Processing Unit Execution Unit Instruction Unit Memory Management Unit Bus Interface Unit Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

Execution unit & Instruction Unit • The EU has 8 general purpose and 8 special purpose registers, used for handling data or calculating offset addresses. • The IU decodes the opcode bytes received from 16 -byte instruction code queue and arranges them into a 3 -instr decoded- instruction queue, after decoding them so as to pass it to the control section for deriving the necessary control signals. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

The Memory Management unit (MMU) • Segmentation Unit • It allows the use of two address components, Segment and Offset for revocability and sharing of code and data • Max. 4 Gb segments • Paging Unit • It organizes the physical Memory in terms of pages of 4 Kb size each. It works under the control of segmentation unit Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

Bus control Unit • • It controls the access of the bus It has a prioritize to resolve the priority of the various bus requests. The address driver drives the bus enable and address signals A 0 -A 31 The pipeline and dynamic bus sizing units handle the related control signals • The Data buffers interface the internal data bus with the system bus Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

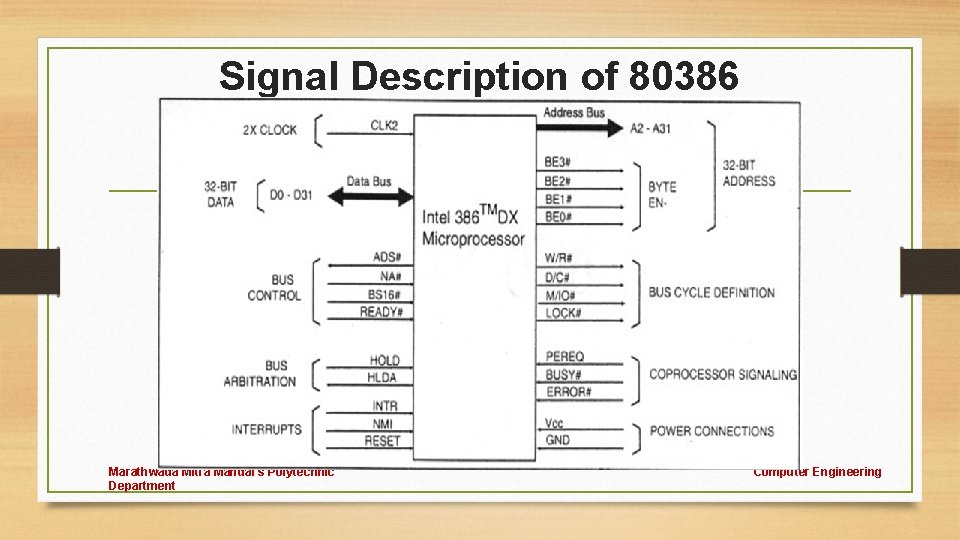

Signal Description of 80386 Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

• W/R#: The write / read output distinguishes the write and read cycles from one another. • D/C#: This data / control output pin distinguishes between a data transfer cycle from a machine control cycle like interrupt acknowledge. • M/IO#: This output pin differentiates between the memory and I/O cycles. • LOCK#: The LOCK# output pin enables the CPU to prevent the other bus masters from gaining the control of the system bus. • NA#: The next address input pin, if activated, allows address pipelining, during 80386 bus cycles. • ADS#: The address status output pin indicates that the address bus and bus cycle definition pins( W/R#, D/C#, M/IO#, BE 0# to BE 3# ) are carrying the respective valid signals. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

• READY#: The ready signals indicates to the CPU that the previous bus cycle has been terminated and the bus is ready for the next cycle. The signal is used to insert WAIT states in a bus cycle and is useful for interfacing of slow devices with CPU. • BS 16#: The bus size – 16 input pin allows the interfacing of 16 bit devices with the 32 bit wide 80386 data bus. Successive 16 bit bus cycles may be executed to read a 32 bit data from a peripheral. • HOLD: The bus hold input pin enables the other bus masters to gain control of the system bus if it is asserted. • HLDA: The bus hold acknowledge output indicates that a valid bus hold request has been received and the bus has been relinquished by the CPU. • BUSY#: The busy input signal indicates to the CPU that the coprocessor is busy with the allocated task. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

• ERROR#: The error input pin indicates to the CPU that the coprocessor has encountered an error while executing its instruction. • PEREQ: The processor extension request output signal indicates to the CPU to fetch a data word for the coprocessor. • INTR: This interrupt pin is a mask able interrupt, that can be masked using the IF of the flag register. • NMI: A valid request signal at the non-mask able interrupt request input pin internally generates a nonmask able interrupt of type 2. • RESET: A high at this input pin suspends the current operation and restart the execution from the starting location. • N / C: No connection pins are expected to be left open while connecting the 80386 in the circuit. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

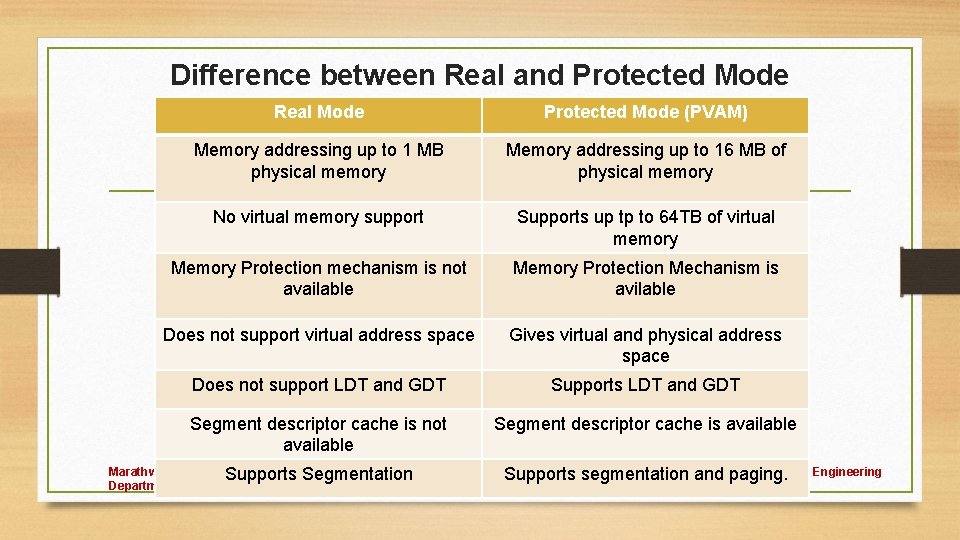

Difference between Real and Protected Mode Real Mode Protected Mode (PVAM) Memory addressing up to 1 MB physical memory Memory addressing up to 16 MB of physical memory No virtual memory support Supports up tp to 64 TB of virtual memory Memory Protection mechanism is not available Memory Protection Mechanism is avilable Does not support virtual address space Gives virtual and physical address space Does not support LDT and GDT Supports LDT and GDT Segment descriptor cache is not available Segment descriptor cache is available Marathwada Mitra Mandal's Polytechnic Supports Segmentation Department Computer Engineering Supports segmentation and paging.

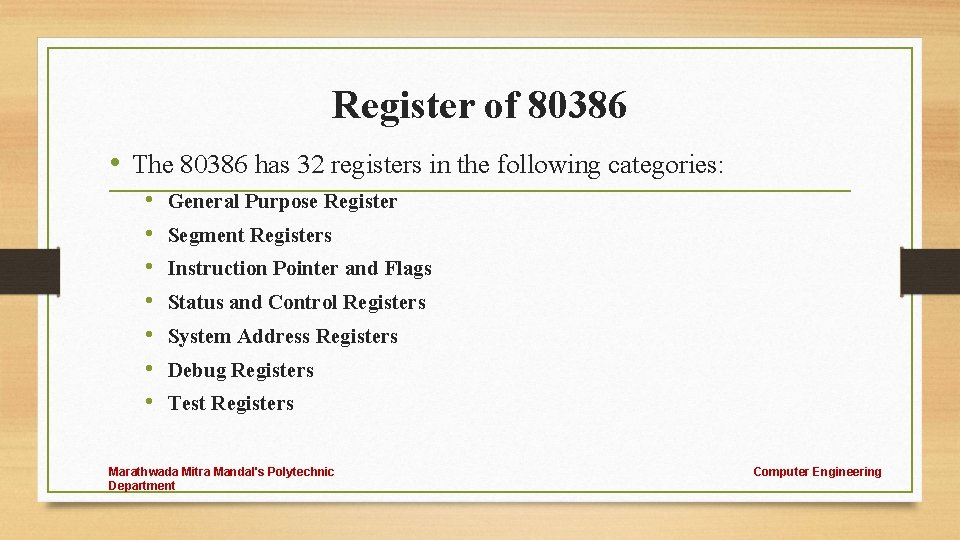

Register of 80386 • The 80386 has 32 registers in the following categories: • • General Purpose Register Segment Registers Instruction Pointer and Flags Status and Control Registers System Address Registers Debug Registers Test Registers Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

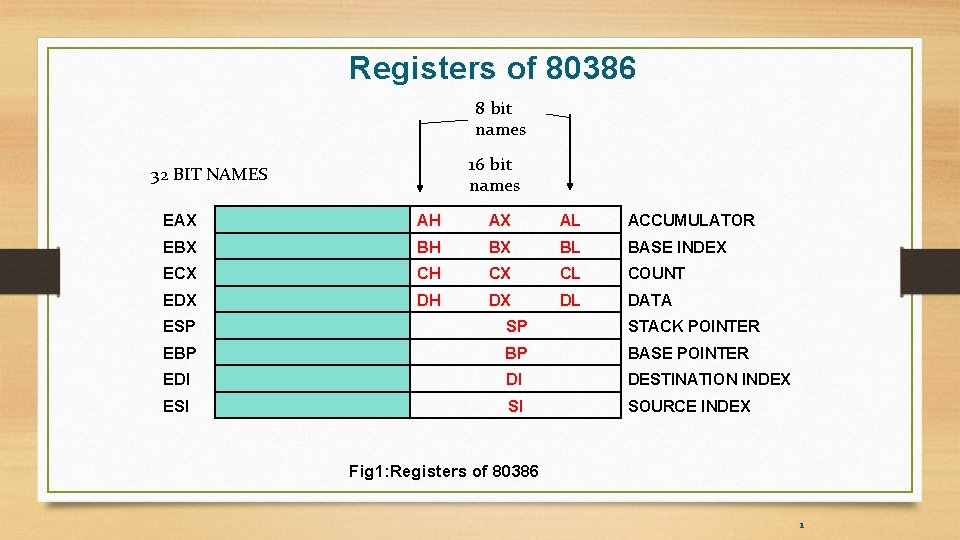

Registers of 80386 8 bit names 16 bit names 32 BIT NAMES EAX AH AX AL ACCUMULATOR EBX BH BX BL BASE INDEX ECX CH CX CL COUNT EDX DH DX DL DATA ESP SP STACK POINTER EBP BP BASE POINTER EDI DI DESTINATION INDEX ESI SI SOURCE INDEX Fig 1: Registers of 80386 1

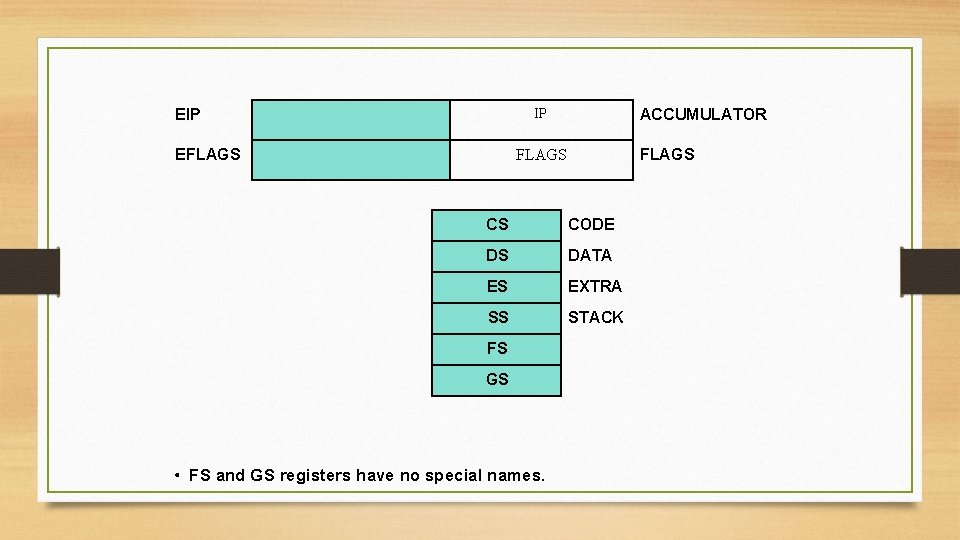

EIP ACCUMULATOR IP EFLAGS CS CODE DS DATA ES EXTRA SS STACK FS GS • FS and GS registers have no special names.

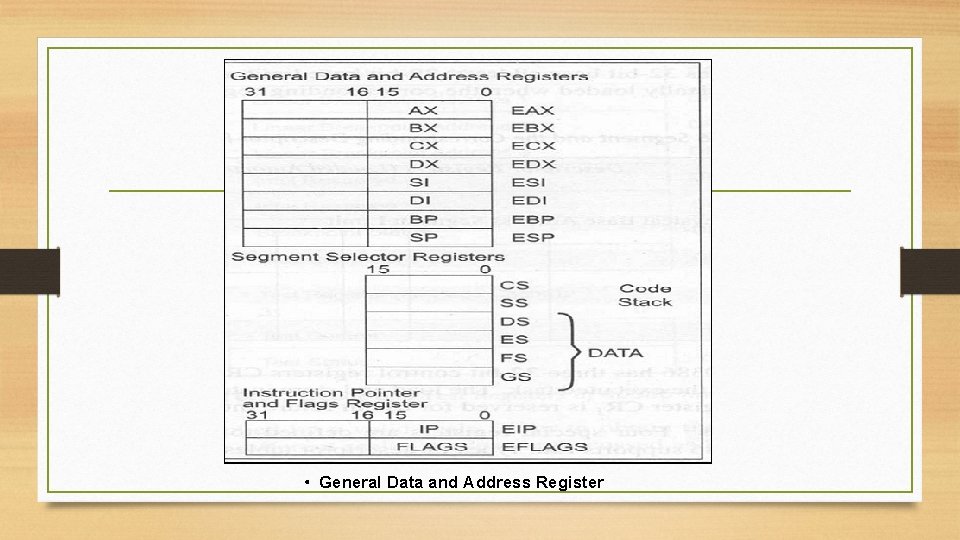

• General Data and Address Register

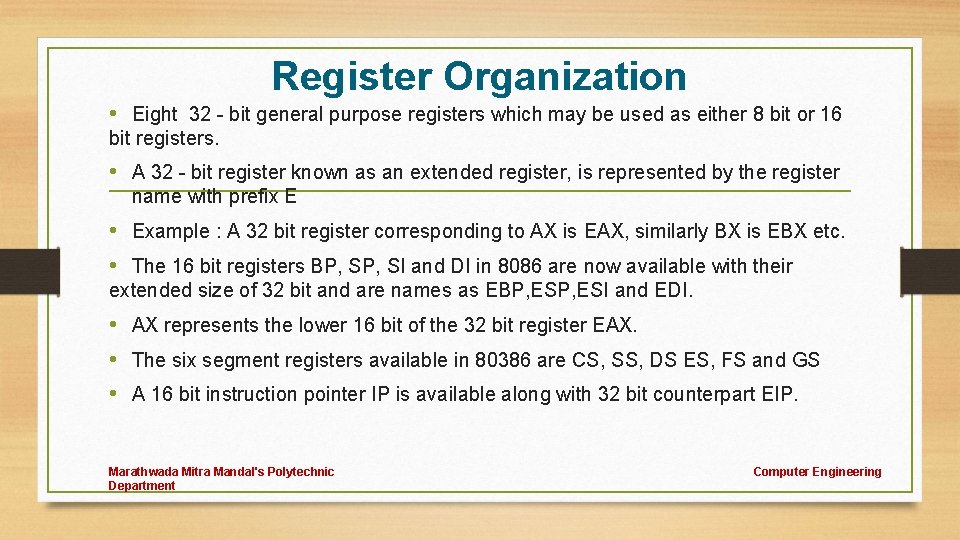

Register Organization • Eight 32 - bit general purpose registers which may be used as either 8 bit or 16 bit registers. • A 32 - bit register known as an extended register, is represented by the register name with prefix E • Example : A 32 bit register corresponding to AX is EAX, similarly BX is EBX etc. • The 16 bit registers BP, SI and DI in 8086 are now available with their extended size of 32 bit and are names as EBP, ESI and EDI. • AX represents the lower 16 bit of the 32 bit register EAX. • The six segment registers available in 80386 are CS, SS, DS ES, FS and GS • A 16 bit instruction pointer IP is available along with 32 bit counterpart EIP. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

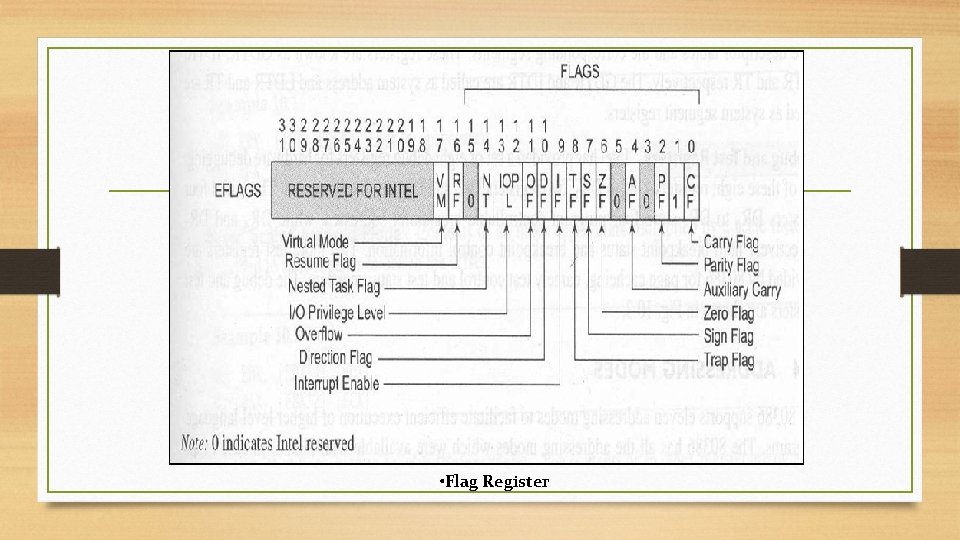

• Flag Register

Flags • C (Carry) – It holds the carry after calculations • P (Parity) – Parity is a logic 0 for odd parity and a logic 1 for even parity. Parity is a count of ones in a number expressed as even or odd. • A (Auxiliary carry) –Carry occurs bits positions 3 and 5 of the results. • Z (Zero) - The zero f lag shows that the result of an arithmetic or logical operation is zero. When Z = 1, the result is zero. When Z = 0, the result was nonzero. • T (Trap) – Enables trapping through an on-chip debugging facility. • S (Sign) - The sign f lag holds the arithmetic sign after an arithmetic or a logical operation. If S =1 the sign bit is set and the result is negative. If S = 0, the sign bit is not set and the result is positive. • I (Interrupt) - The interrupt f lag controls the operations of the INTR(Interrupt request) input pint. If I =1, the INTR pin is enabled; if I =0, the INTR Computer Engineering pin is disabled. Marathwada Mitra Mandal's Polytechnic Department

Flags • VM (Virtual mode) - If this f lag set, the 80386 enters the virtual mode within the protected mode. In this mode, if any privileged instruction is executed, an exception 13 is generated. • RF(resume) – The resume f lag is used with debugging to control the resumption of execution after the next instruction. • NT (nested task) – The nested task f lag is used to indicated that the current task is nested within another task in protected mode operation. This f lag is when the task I nested by software. • IOPL (I/O Privilege level) – IOPL is used in protected mode operation to select the privilege level for I. /O devices. IF the current privilege level is higher or more trusted than the IOPL, I/O executed without hindrance. If the IOPL is lower than the current privilege level, an interrupt occurs. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

Features of 80386 microprocessor • 8, 16, 32 -Bit Data Types • 8 General Purpose 32 -Bit Registers • Very Large Address Space • 4 Gigabyte Physical • 64 Terabyte Virtual • 4 Gigabyte Maximum Segment Size • Integrated Memory Management Unit • Virtual Memory Support • Optional On-Chip Paging • 4 Levels of Protection • Fully Compatible with 80286 Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

Features of 80386 microprocessor • Object Code Compatible with All 8086 Family Microprocessors • Virtual 8086 Mode Allows Running of 8086 Software in a Protected and Paged System • Hardware Debugging Support • Optimized for System Performance • Pipelined Instruction Execution • On-Chip Address Translation Caches • 20, 25 and 33 MHz Clock • 40, 50 and 66 Megabytes/Sec Bus Bandwidth • Numeric Support via Intel 387 TM DX Math Coprocessor Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

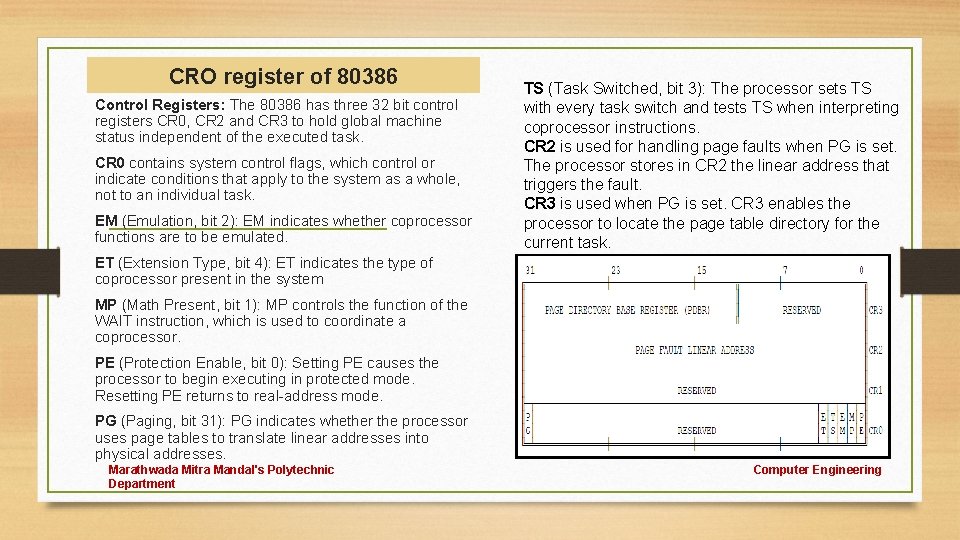

CRO register of 80386 Control Registers: The 80386 has three 32 bit control registers CR 0, CR 2 and CR 3 to hold global machine status independent of the executed task. CR 0 contains system control flags, which control or indicate conditions that apply to the system as a whole, not to an individual task. EM (Emulation, bit 2): EM indicates whether coprocessor functions are to be emulated. TS (Task Switched, bit 3): The processor sets TS with every task switch and tests TS when interpreting coprocessor instructions. CR 2 is used for handling page faults when PG is set. The processor stores in CR 2 the linear address that triggers the fault. CR 3 is used when PG is set. CR 3 enables the processor to locate the page table directory for the current task. ET (Extension Type, bit 4): ET indicates the type of coprocessor present in the system MP (Math Present, bit 1): MP controls the function of the WAIT instruction, which is used to coordinate a coprocessor. PE (Protection Enable, bit 0): Setting PE causes the processor to begin executing in protected mode. Resetting PE returns to real-address mode. PG (Paging, bit 31): PG indicates whether the processor uses page tables to translate linear addresses into physical addresses. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

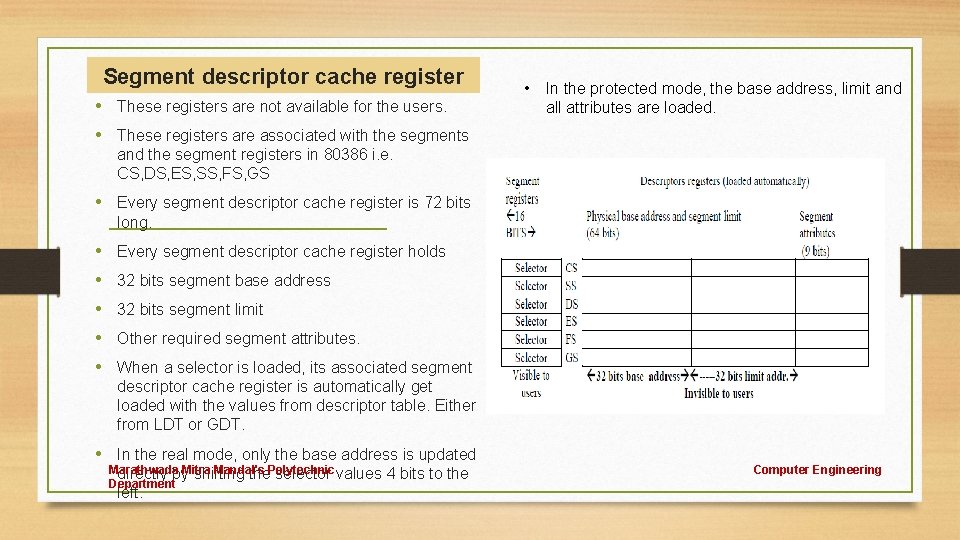

Segment descriptor cache register • These registers are not available for the users. • In the protected mode, the base address, limit and all attributes are loaded. • These registers are associated with the segments and the segment registers in 80386 i. e. CS, DS, ES, SS, FS, GS • Every segment descriptor cache register is 72 bits long. • Every segment descriptor cache register holds • 32 bits segment base address • 32 bits segment limit • Other required segment attributes. • When a selector is loaded, its associated segment descriptor cache register is automatically get loaded with the values from descriptor table. Either from LDT or GDT. • In the real mode, only the base address is updated Marathwada Mitra Mandal's Polytechnic directly by shifting the selector values 4 bits to the Department left. Computer Engineering

- Slides: 23