Shift Registers 91509 L 26 Shift Registers Copyright

- Slides: 11

Shift Registers 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 1

Class 25 – Shift Registers o Multiplication by 2 (division by 2) Shift Register topology o Material from section 7 -6 of text o 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 2

Effect of a shift operation o o A single shift is multiplication by 2 Consider the operation 6 x 2 = 12 n n n o 0110 x 0010 0000 0110. Will skip last 2 rows of terms of 0 s 01100 Note that this result is just a shift by 1 position. 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 3

Multiplication by shift o o Reference base 10. To multiply or divide by 10 you just move the decimal point, or in scientific notation, adjust the exponent. In base 2 you can move the binary point n n o Right by 1 position to multiply by 2 Left by 1 position to divide by 2 Or shift the binary number on a fixed binary point n Left by 1 position to multiply by 2 o n 1110. x 2 11100. Right by 1 position to divide by 2 o 11100. ¸ 2 1110. 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 4

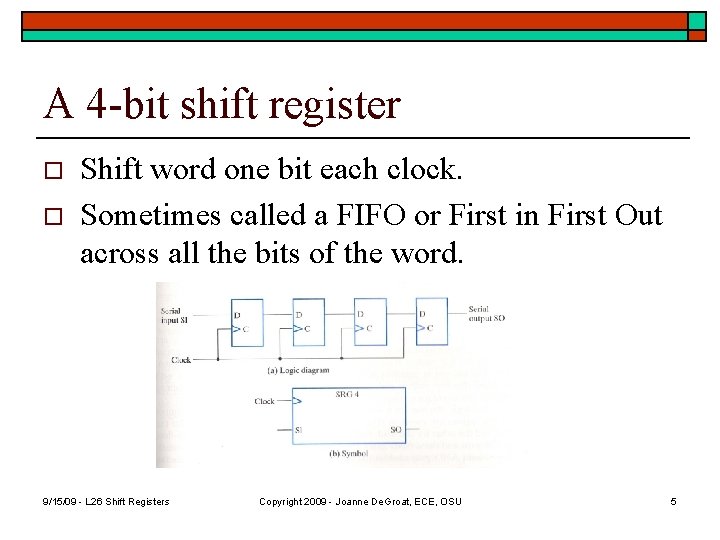

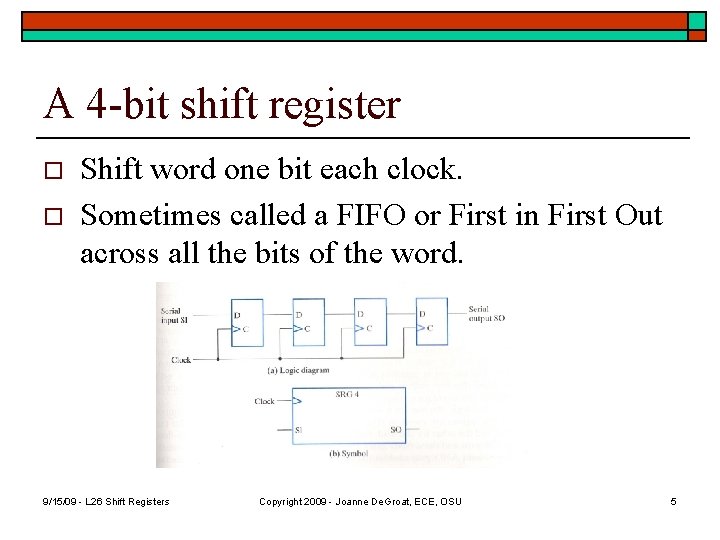

A 4 -bit shift register o o Shift word one bit each clock. Sometimes called a FIFO or First in First Out across all the bits of the word. 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 5

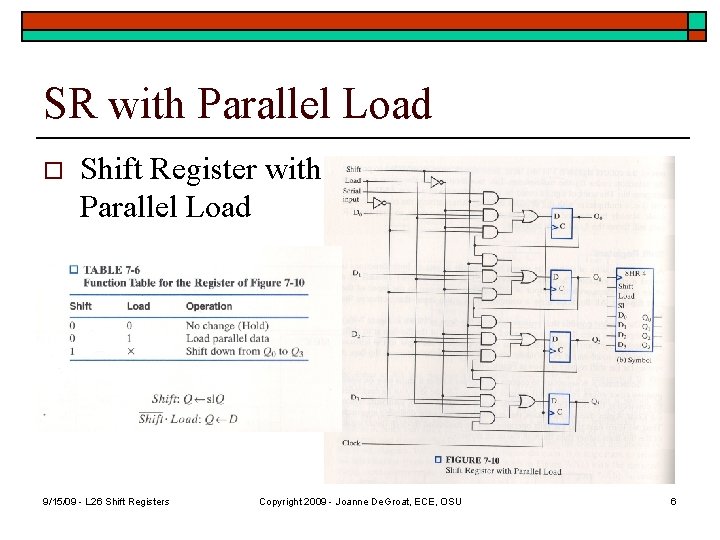

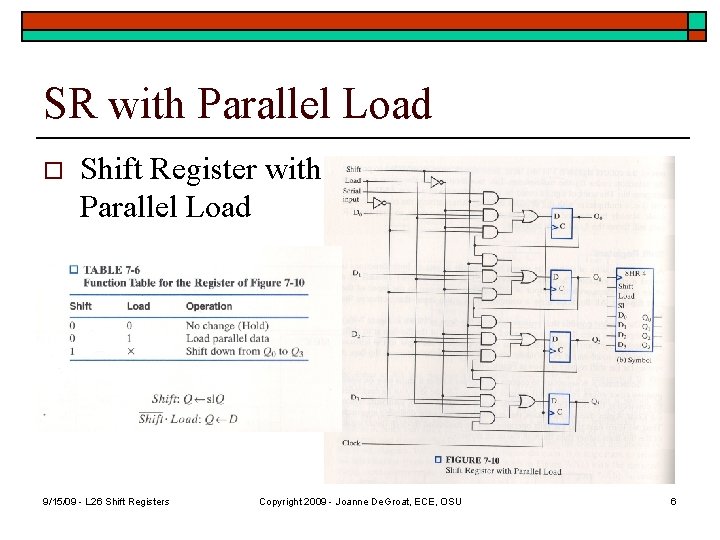

SR with Parallel Load o Shift Register with Parallel Load 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 6

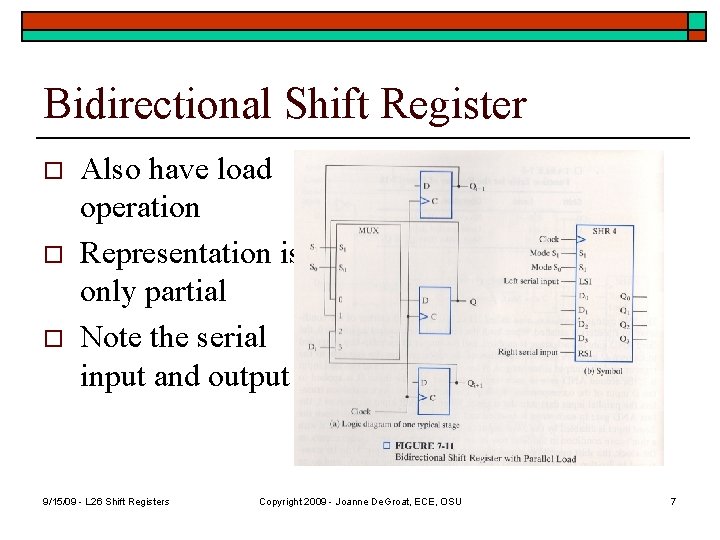

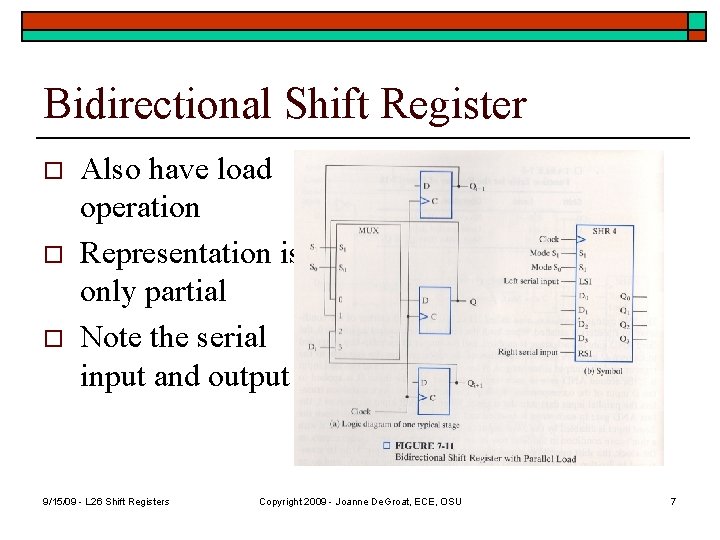

Bidirectional Shift Register o o o Also have load operation Representation is only partial Note the serial input and output 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 7

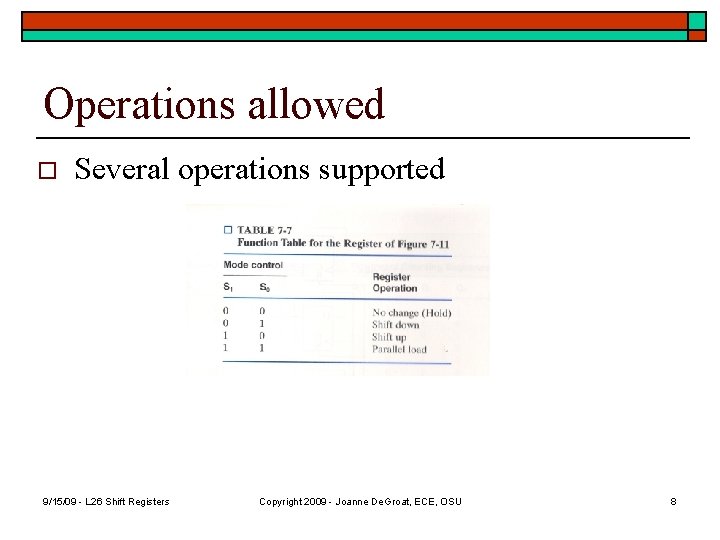

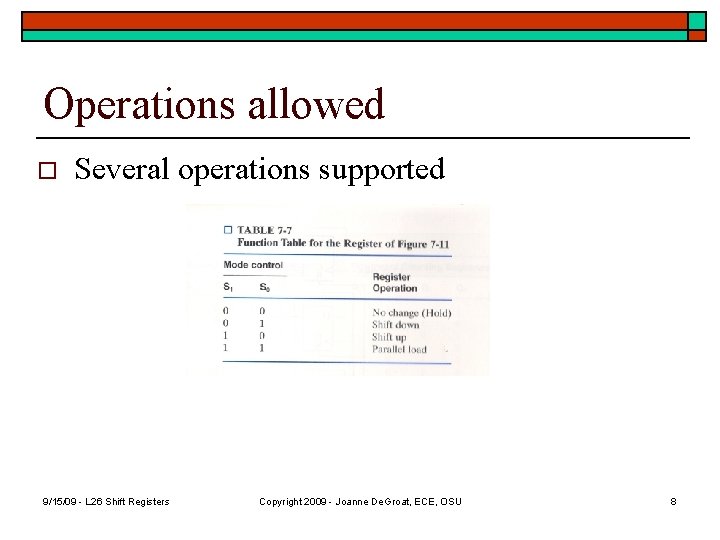

Operations allowed o Several operations supported 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 8

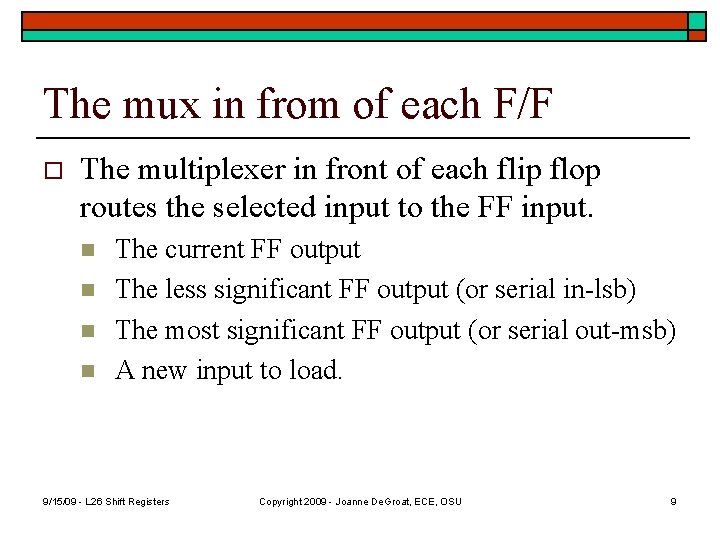

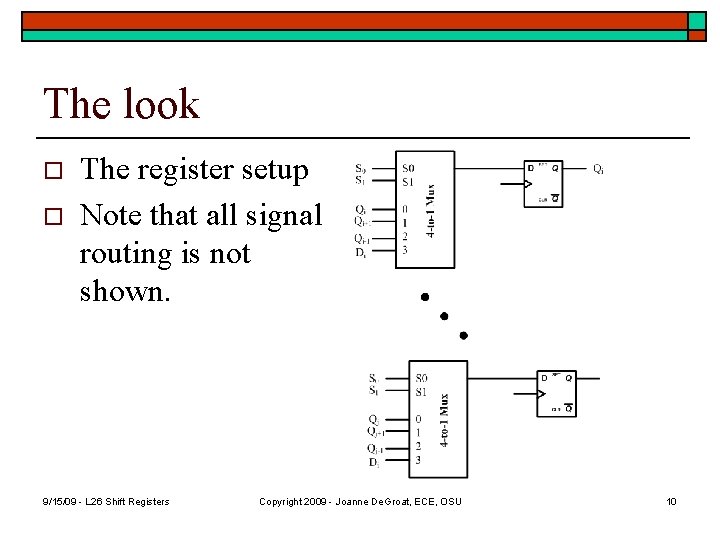

The mux in from of each F/F o The multiplexer in front of each flip flop routes the selected input to the FF input. n n The current FF output The less significant FF output (or serial in-lsb) The most significant FF output (or serial out-msb) A new input to load. 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 9

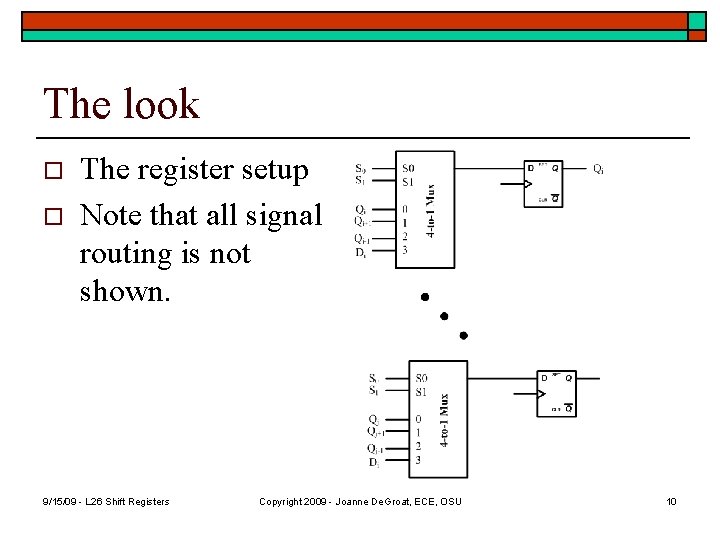

The look o o The register setup Note that all signal routing is not shown. 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 10

Class 25 assignment o o Covered part of section 7 -6 Problems for hand in n o Problems for practice n o Nothing new Reading for next class: counters from 7 -6 9/15/09 - L 26 Shift Registers Copyright 2009 - Joanne De. Groat, ECE, OSU 11