Universidad Autnoma de Nuevo Len Facultad de Ingeniera

- Slides: 72

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Diseño de Sistemas Secuenciales síncronos De mis maestros he aprendido mucho; De mis colegas, más; Y de mis alumnos aun más Noviembre de 2015 JAGG Sistemas Digitales Electrónica Digital I

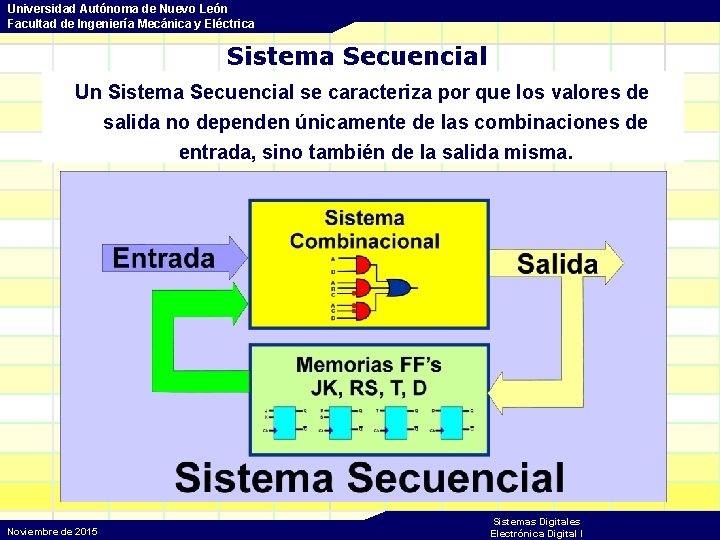

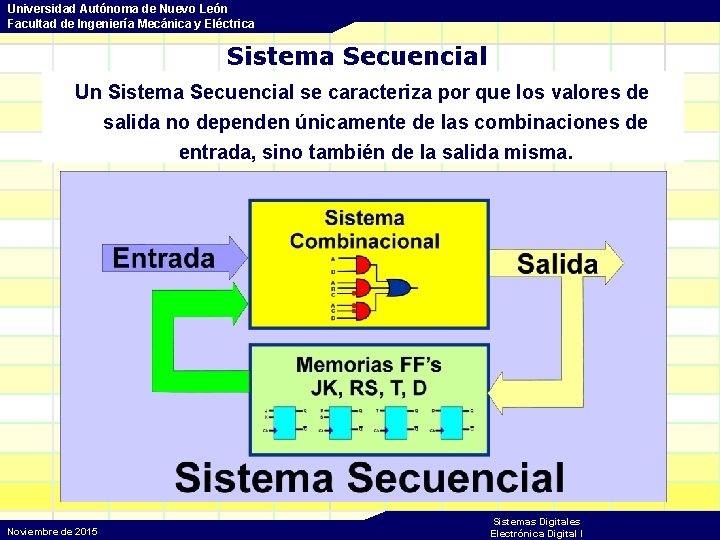

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Sistema Secuencial Un Sistema Secuencial se caracteriza por que los valores de salida no dependen únicamente de las combinaciones de entrada, sino también de la salida misma. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

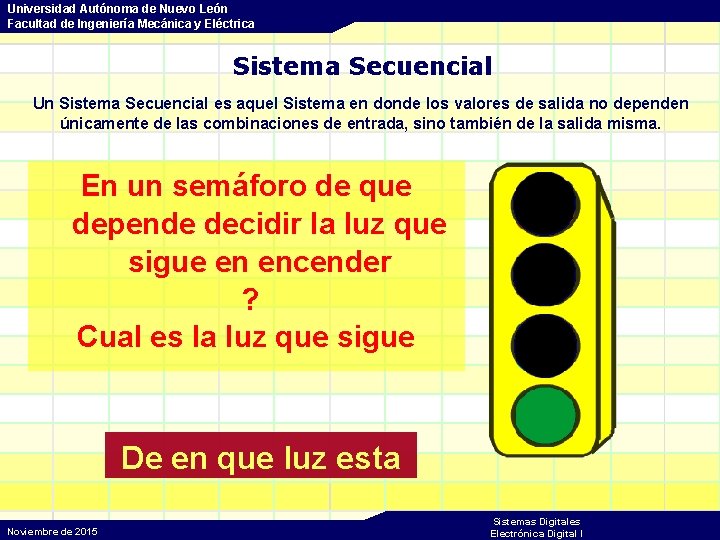

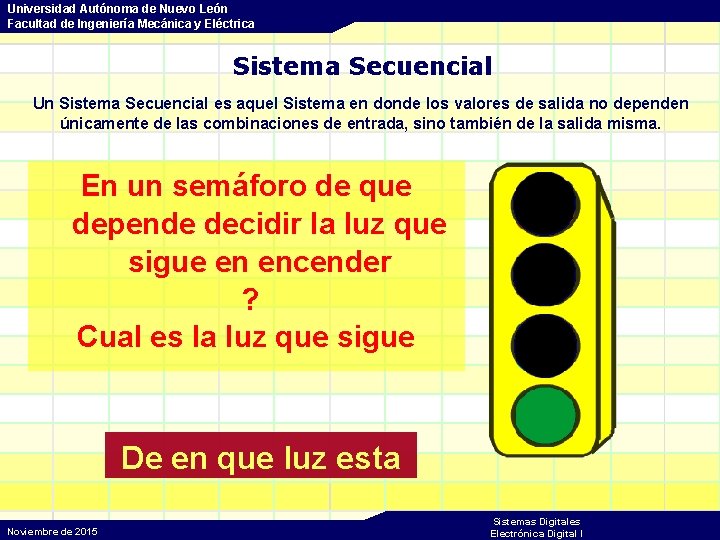

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Sistema Secuencial Un Sistema Secuencial es aquel Sistema en donde los valores de salida no dependen únicamente de las combinaciones de entrada, sino también de la salida misma. En un semáforo de que depende decidir la luz que sigue en encender ? Cual es la luz que sigue De en que luz esta Noviembre de 2015 Sistemas Digitales Electrónica Digital I

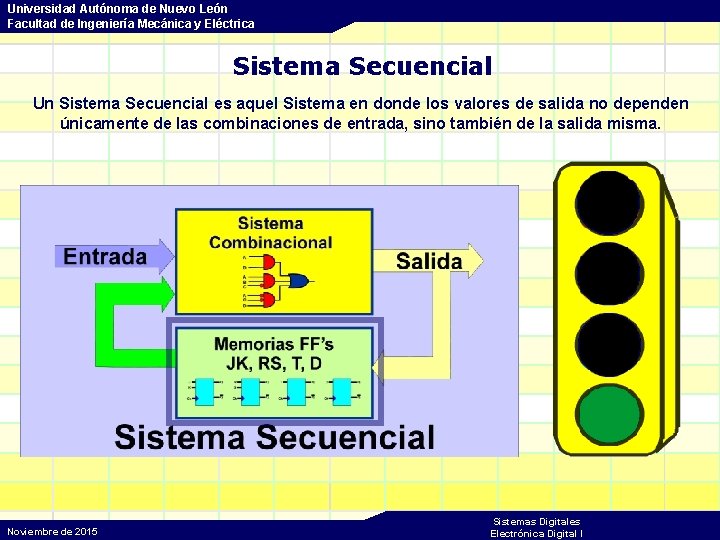

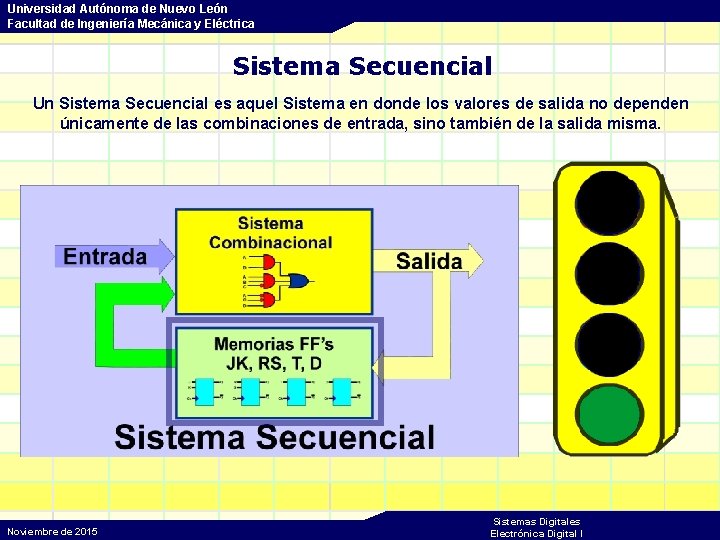

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Sistema Secuencial Un Sistema Secuencial es aquel Sistema en donde los valores de salida no dependen únicamente de las combinaciones de entrada, sino también de la salida misma. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica clasificación • Asíncrono: que no depende de una señal de sincronía depende solo de un cambio de entrada. • Síncrono en donde los cambios de estado dependen de una señal de sincronía de los Flip Flops llamada reloj, Ck o Clk. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

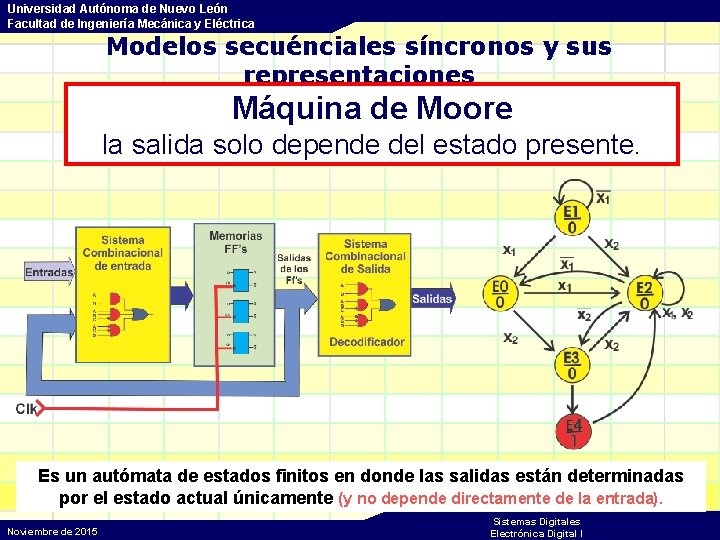

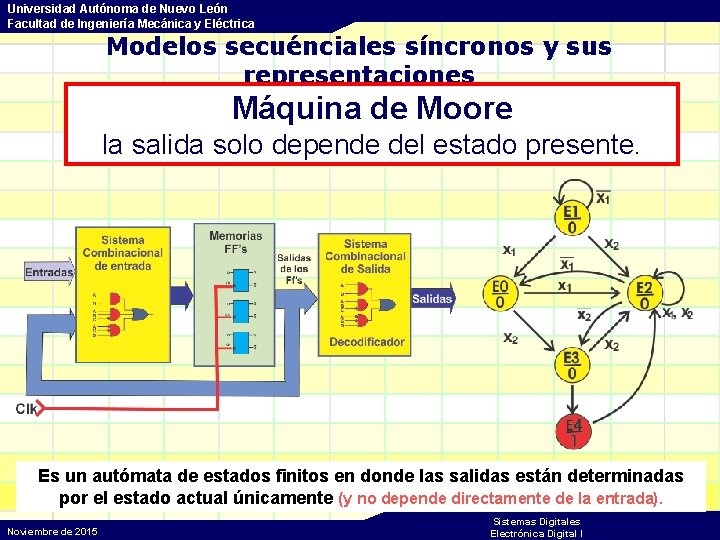

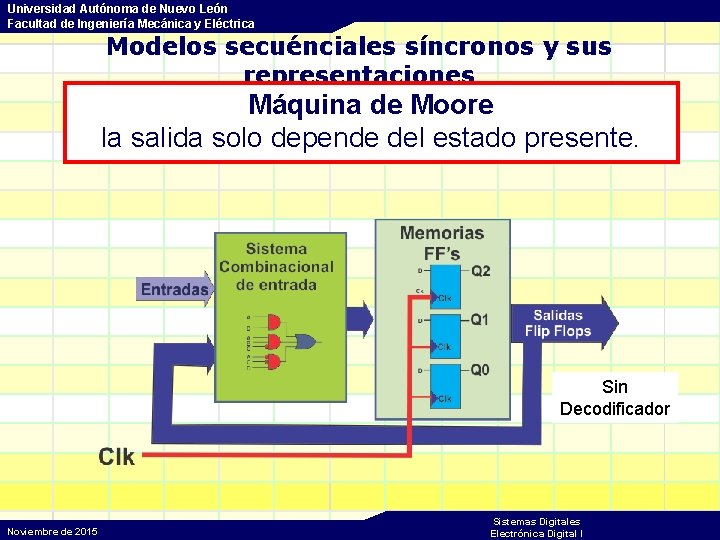

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Modelos secuénciales síncronos y sus representaciones Máquina de Moore la salida solo depende del estado presente. Es un autómata de estados finitos en donde las salidas están determinadas por el estado actual únicamente (y no depende directamente de la entrada). Noviembre de 2015 Sistemas Digitales Electrónica Digital I

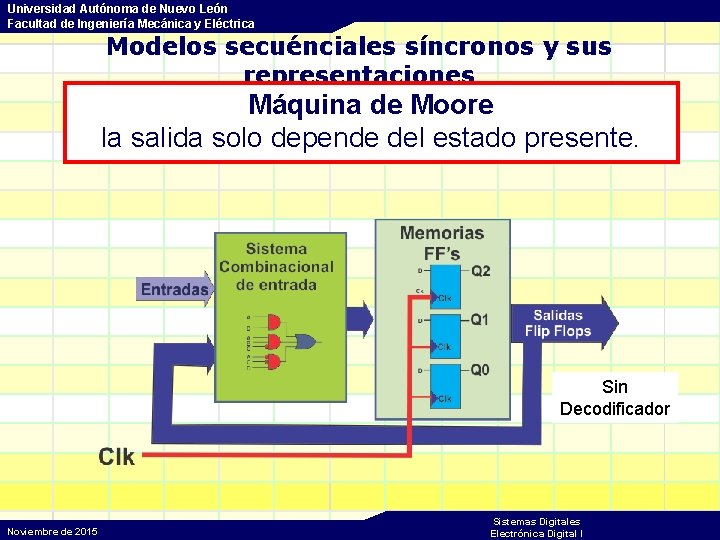

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Modelos secuénciales síncronos y sus representaciones Máquina de Moore la salida solo depende del estado presente. Sin Decodificador Noviembre de 2015 Sistemas Digitales Electrónica Digital I

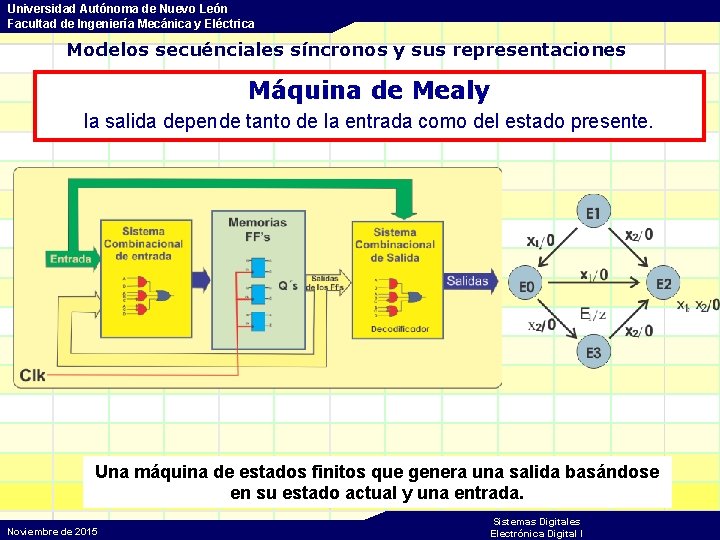

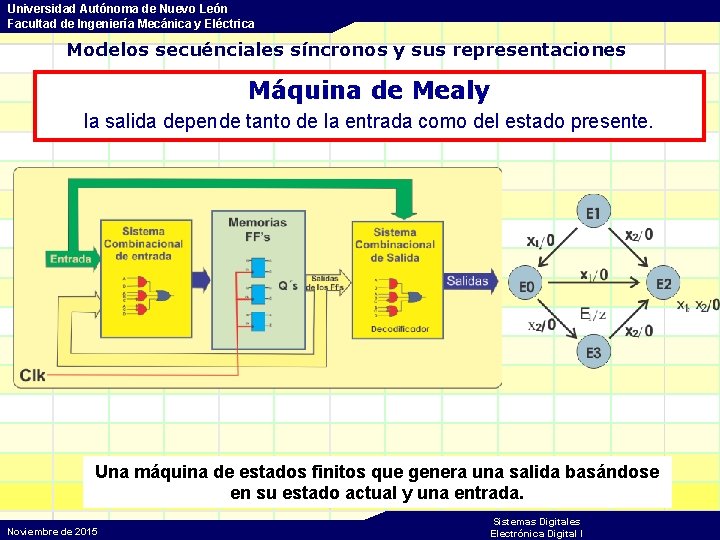

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Modelos secuénciales síncronos y sus representaciones Máquina de Mealy la salida depende tanto de la entrada como del estado presente. Una máquina de estados finitos que genera una salida basándose en su estado actual y una entrada. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Cual es parte más difícil de la solución de un problema Describirlo, Plantearlo, Identificarlo Noviembre de 2015 Sistemas Digitales Electrónica Digital I

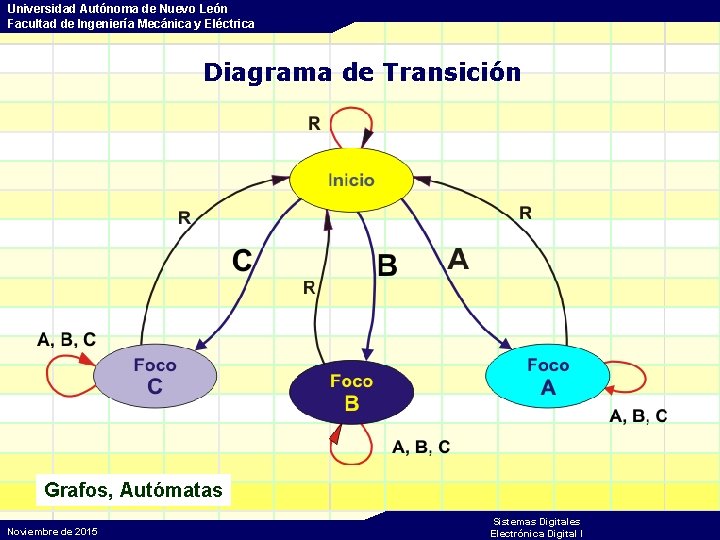

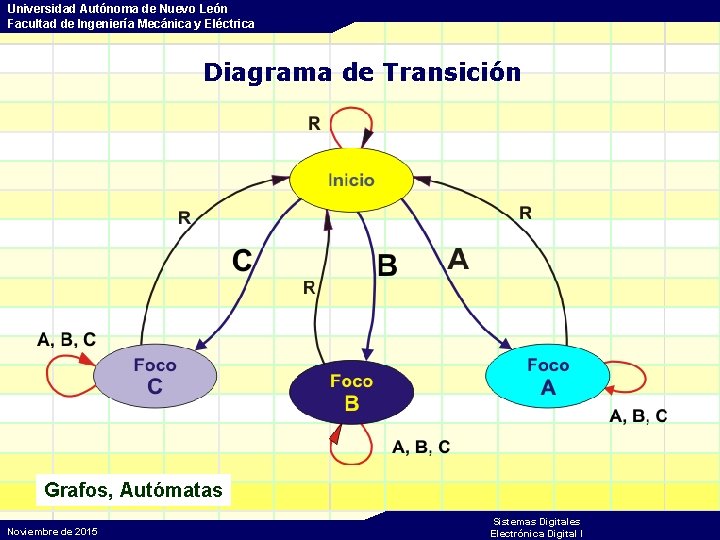

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Diagrama de Transición Grafos, Autómatas Noviembre de 2015 Sistemas Digitales Electrónica Digital I

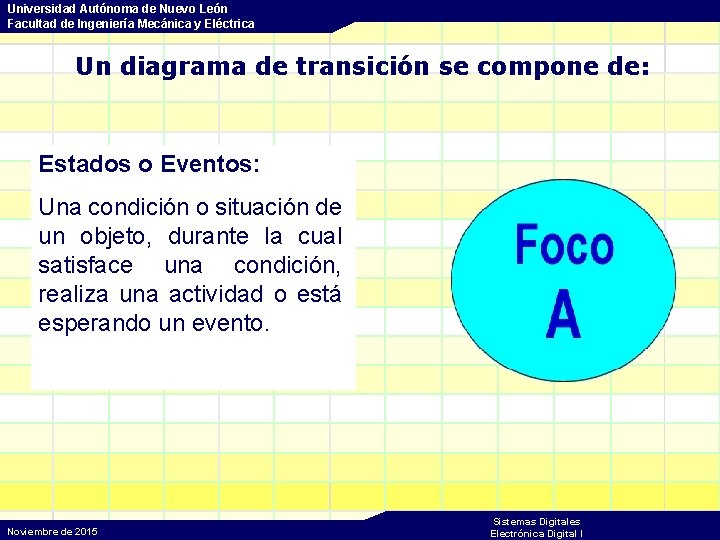

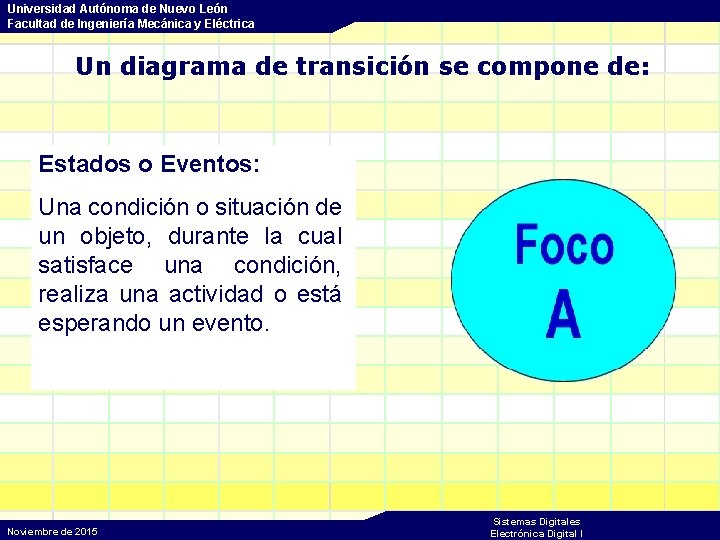

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Un diagrama de transición se compone de: Estados o Eventos: Una condición o situación de un objeto, durante la cual satisface una condición, realiza una actividad o está esperando un evento. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

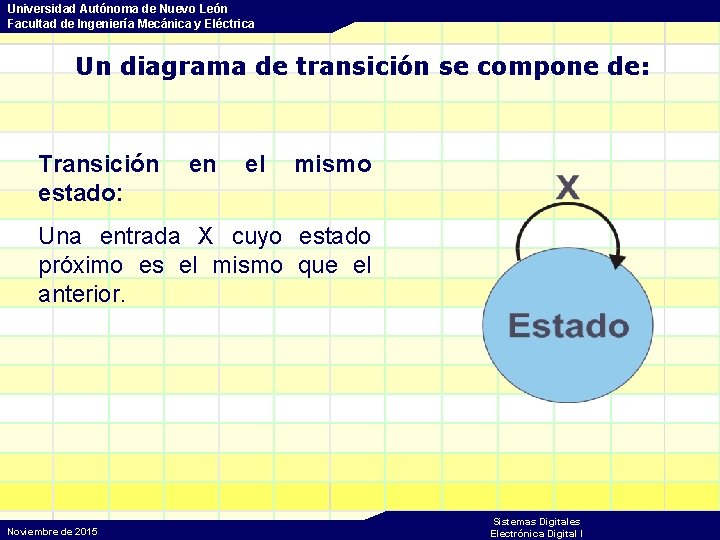

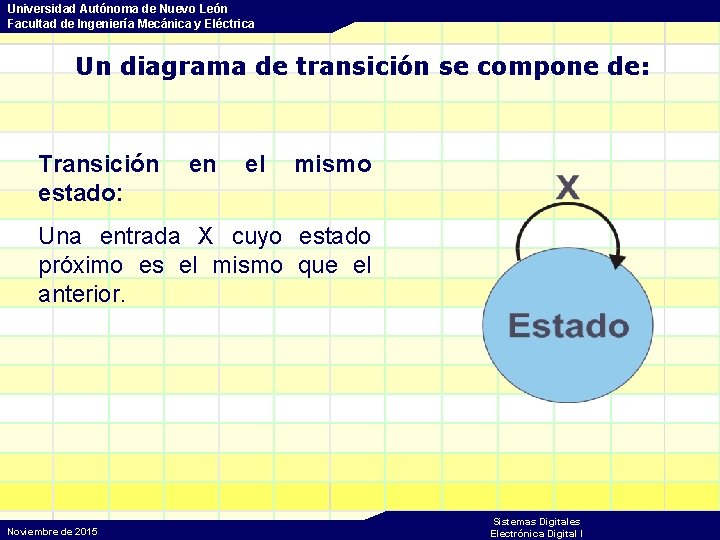

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Un diagrama de transición se compone de: Transición estado: en el mismo Una entrada X cuyo estado próximo es el mismo que el anterior. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

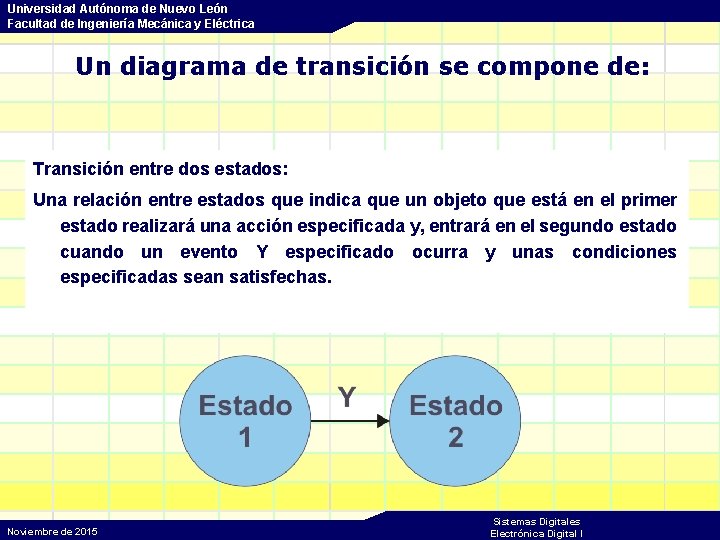

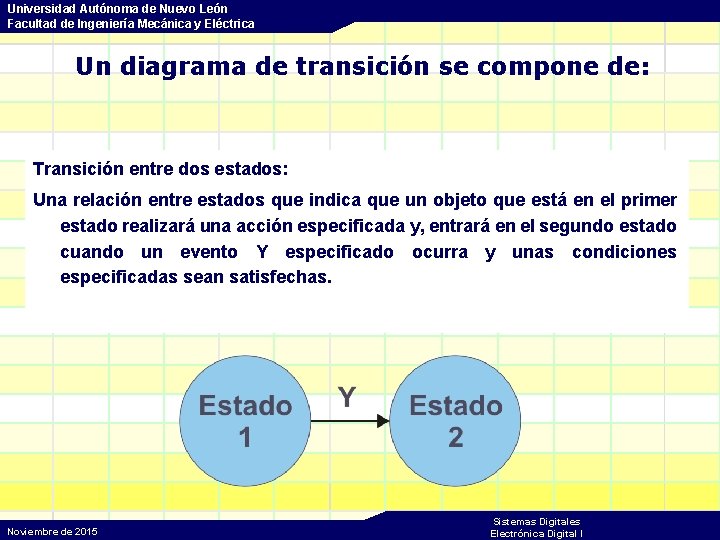

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Un diagrama de transición se compone de: Transición entre dos estados: Una relación entre estados que indica que un objeto que está en el primer estado realizará una acción especificada y, entrará en el segundo estado cuando un evento Y especificado ocurra y unas condiciones especificadas sean satisfechas. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

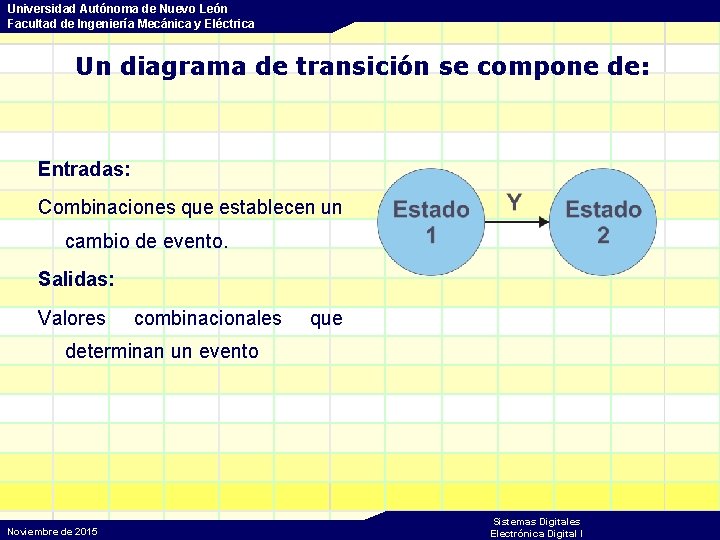

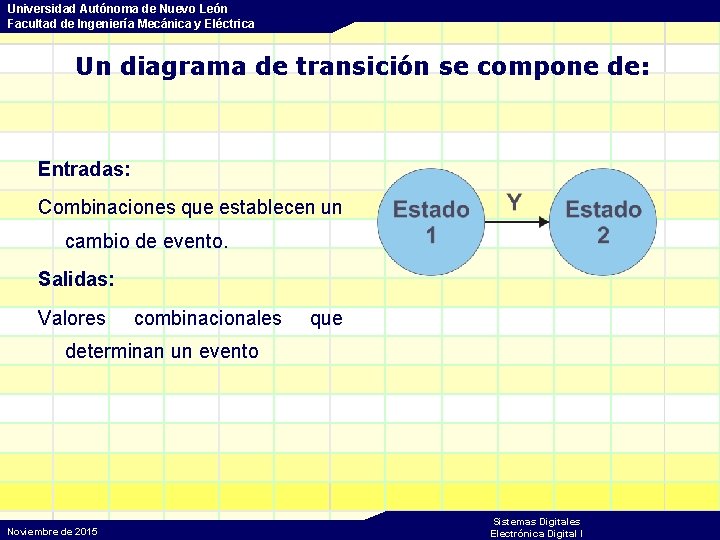

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Un diagrama de transición se compone de: Entradas: Combinaciones que establecen un cambio de evento. Salidas: Valores combinacionales que determinan un evento Noviembre de 2015 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Método tradicional de Diseño Secuencial síncrono 1. - Especificar el Sistema (Diagrama de Transición). 2. - Determinar la cantidad de Flip Flops. 3. - Asignar los valores a los estados. 4. - Determinar las entradas y salidas. a) Entrada de sincronía reloj. b) Entradas combinacionales. c) Salidas combinacionales. d) Salidas registradas (FF’s). 5. - Construir una Tabla de Estados. 6. - Minimizar. 7. - Diagrama Esquemático. 8. - Implementación. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

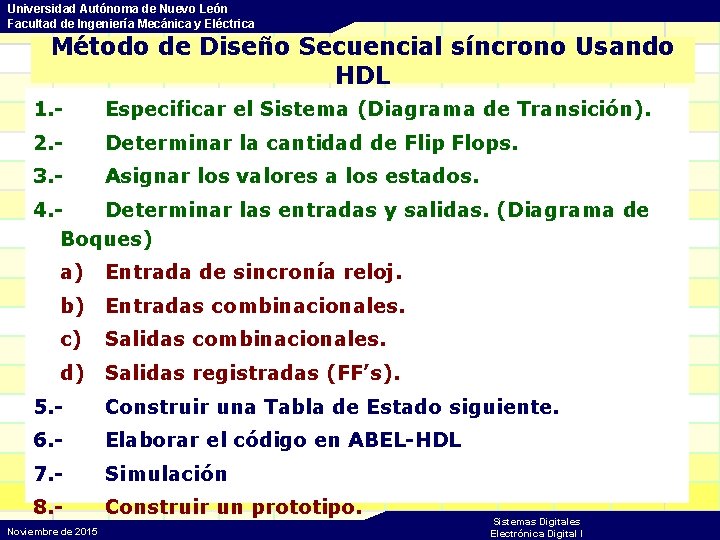

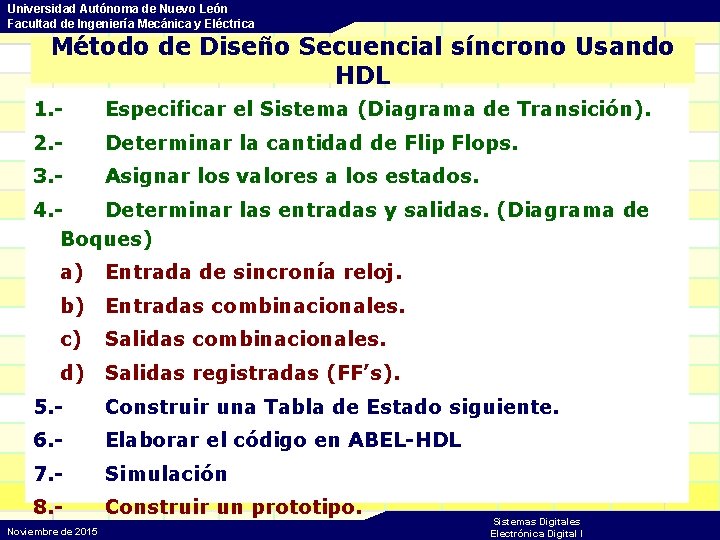

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Método de Diseño Secuencial síncrono Usando HDL 1. - Especificar el Sistema (Diagrama de Transición). 2. - Determinar la cantidad de Flip Flops. 3. - Asignar los valores a los estados. 4. Determinar las entradas y salidas. (Diagrama de Boques) a) Entrada de sincronía reloj. b) Entradas combinacionales. c) Salidas combinacionales. d) Salidas registradas (FF’s). 5. - Construir una Tabla de Estado siguiente. 6. - Elaborar el código en ABEL-HDL 7. - Simulación 8. - Construir un prototipo. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

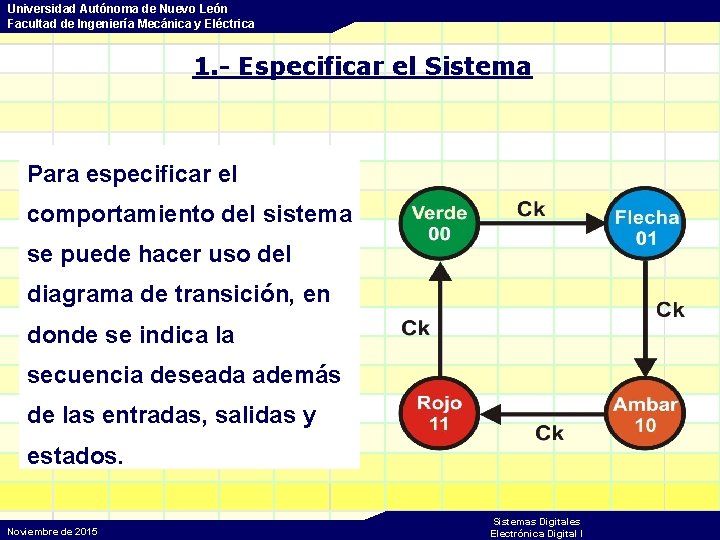

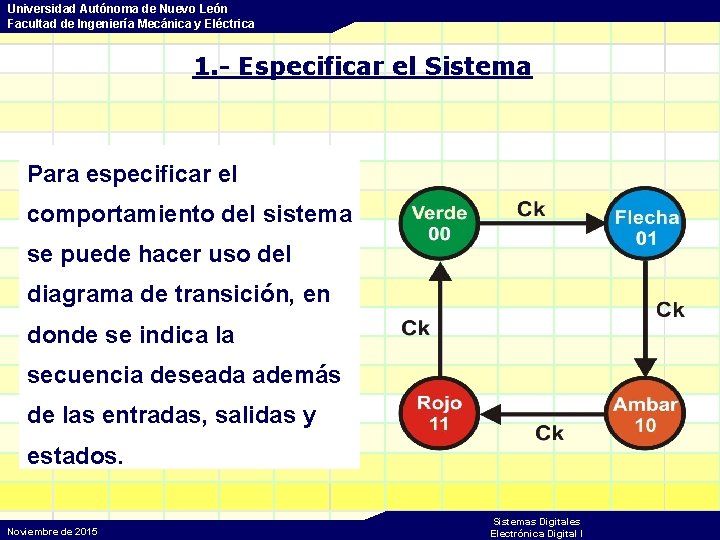

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 1. - Especificar el Sistema Para especificar el comportamiento del sistema se puede hacer uso del diagrama de transición, en donde se indica la secuencia deseada además de las entradas, salidas y estados. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

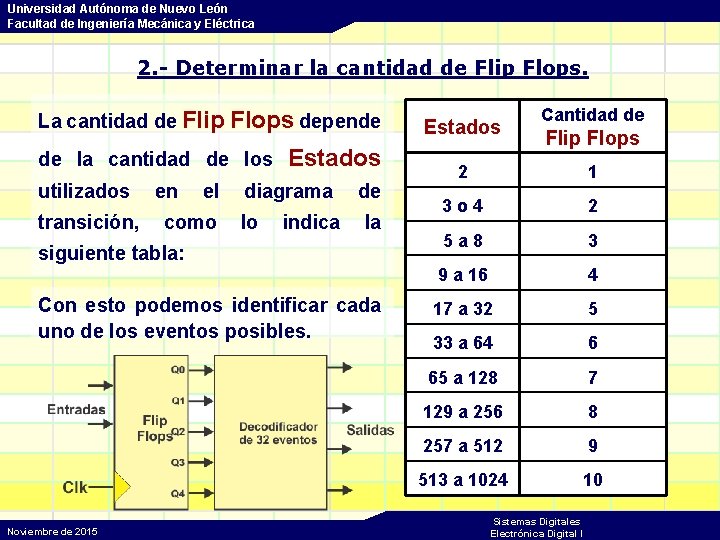

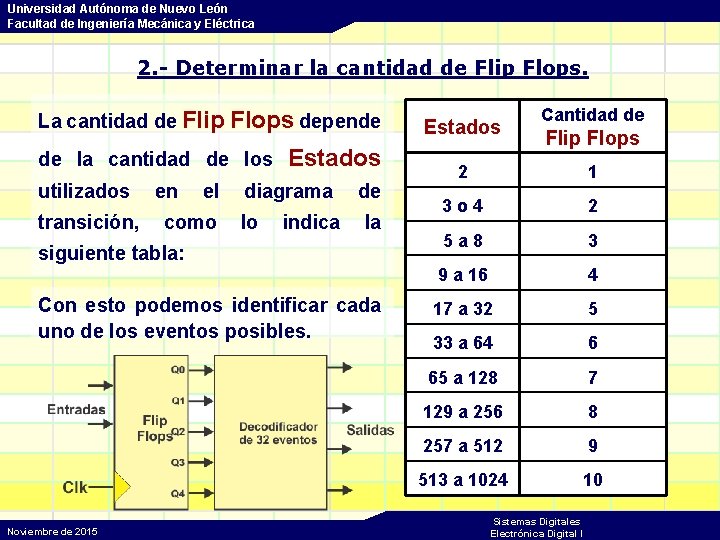

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 2. - Determinar la cantidad de Flip Flops. La cantidad de Flip Flops depende de la cantidad de los utilizados transición, en el como Estados diagrama lo indica de la siguiente tabla: Con esto podemos identificar cada uno de los eventos posibles. Noviembre de 2015 Estados Cantidad de Flip Flops 2 1 3 o 4 2 5 a 8 3 9 a 16 4 17 a 32 5 33 a 64 6 65 a 128 7 129 a 256 8 257 a 512 9 513 a 1024 10 Sistemas Digitales Electrónica Digital I

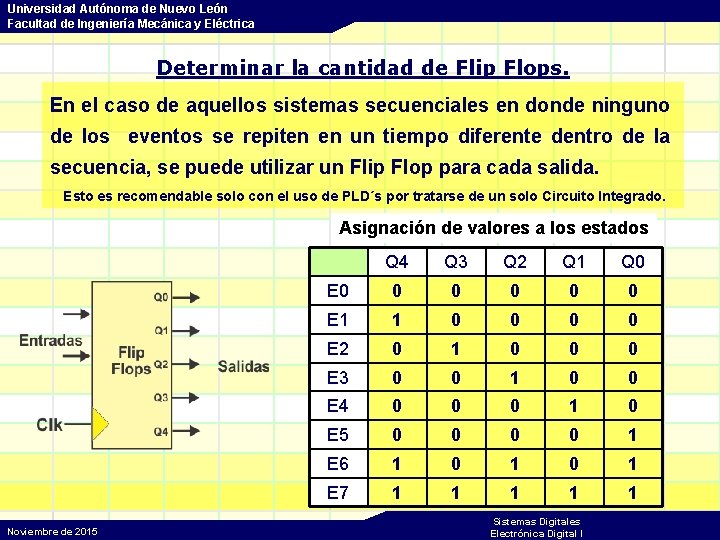

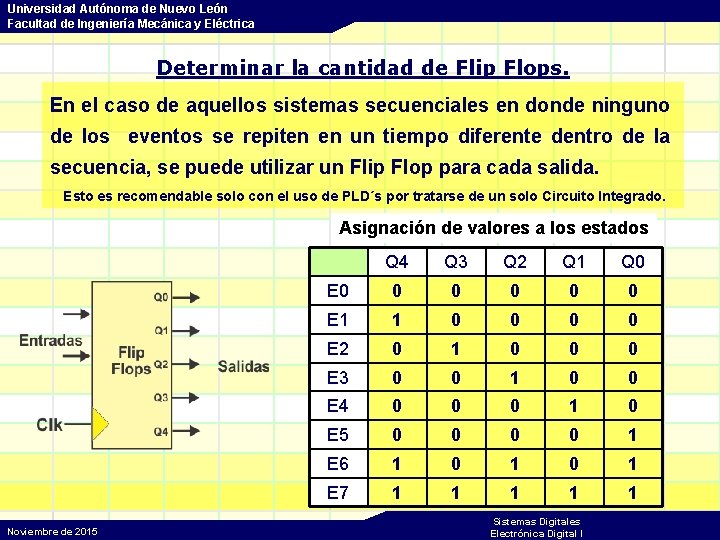

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Determinar la cantidad de Flip Flops. En el caso de aquellos sistemas secuenciales en donde ninguno de los eventos se repiten en un tiempo diferente dentro de la secuencia, se puede utilizar un Flip Flop para cada salida. Esto es recomendable solo con el uso de PLD´s por tratarse de un solo Circuito Integrado. Asignación de valores a los estados Noviembre de 2015 Q 4 Q 3 Q 2 Q 1 Q 0 E 0 0 0 E 1 1 0 0 E 2 0 1 0 0 0 E 3 0 0 1 0 0 E 4 0 0 0 1 0 E 5 0 0 1 E 6 1 0 1 E 7 1 1 1 Sistemas Digitales Electrónica Digital I

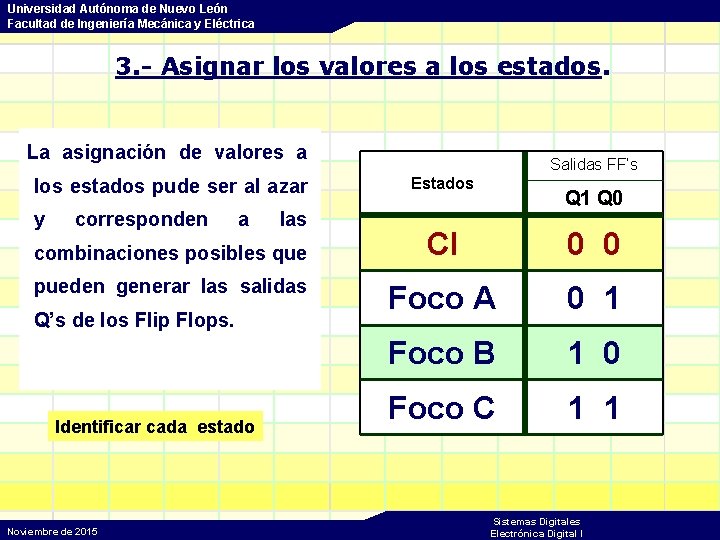

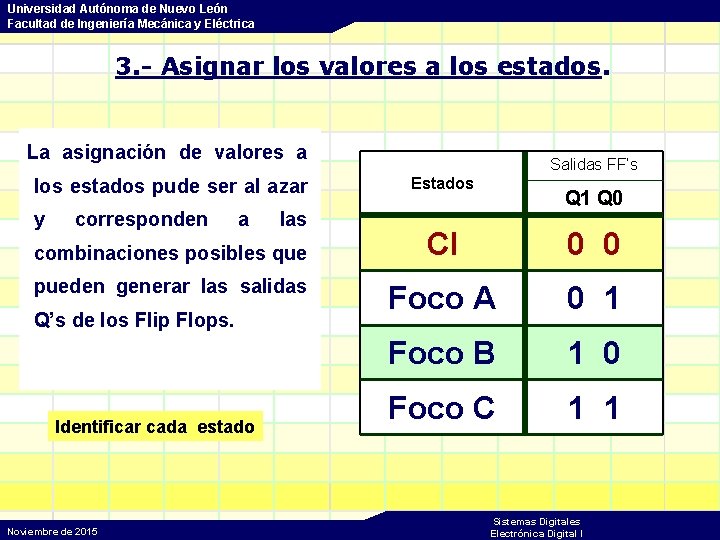

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 3. - Asignar los valores a los estados. La asignación de valores a los estados pude ser al azar y corresponden a las combinaciones posibles que pueden generar las salidas Q’s de los Flip Flops. Identificar cada estado Noviembre de 2015 Salidas FF’s Estados Q 1 Q 0 CI 0 0 Foco A 0 1 Foco B 1 0 Foco C 1 1 Sistemas Digitales Electrónica Digital I

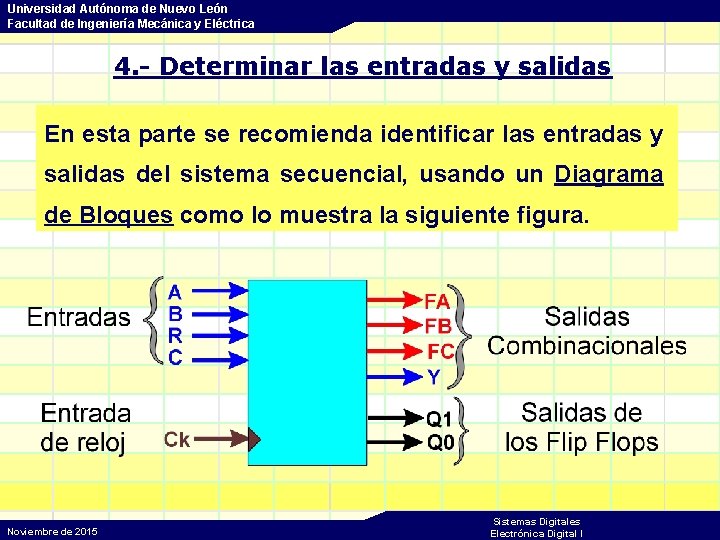

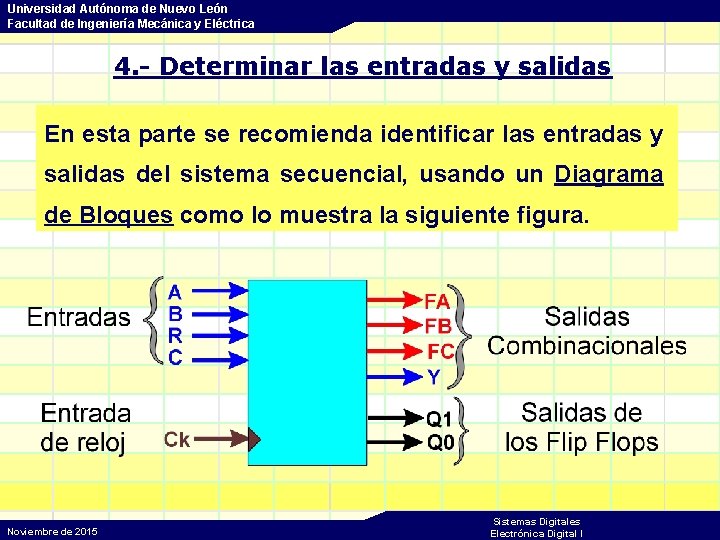

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 4. - Determinar las entradas y salidas En esta parte se recomienda identificar las entradas y salidas del sistema secuencial, usando un Diagrama de Bloques como lo muestra la siguiente figura. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

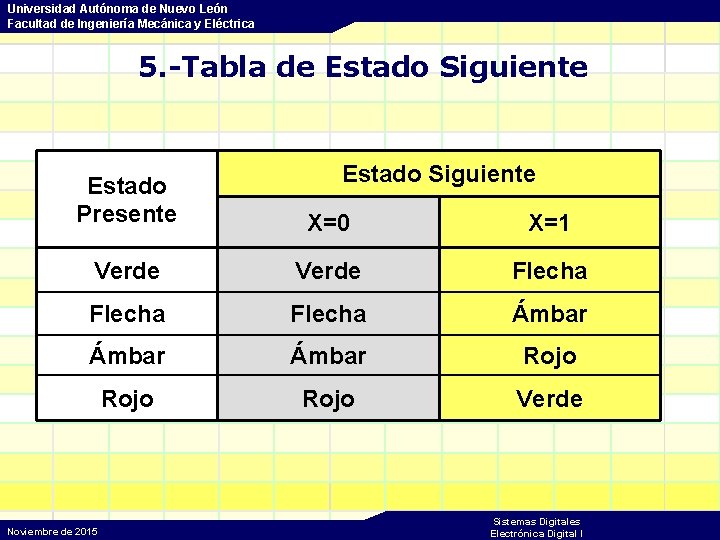

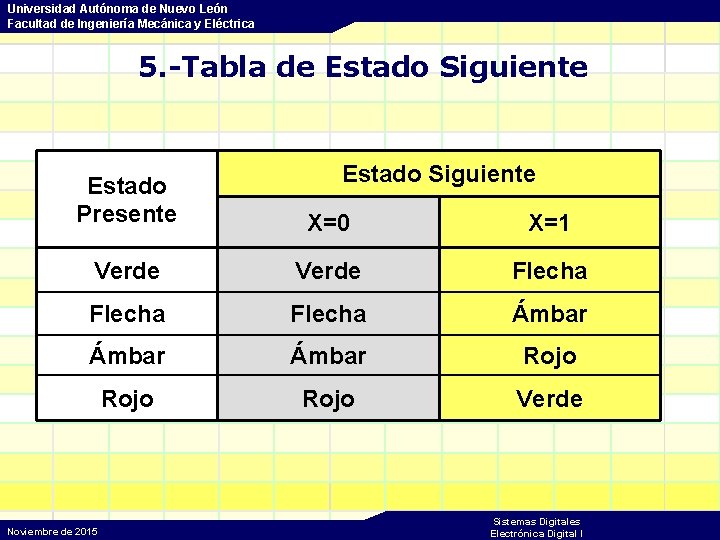

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 5. -Tabla de Estado Siguiente Estado Presente X=0 X=1 Verde Flecha Ámbar Rojo Verde Noviembre de 2015 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 6. - Código en ABEL-HDL Codificación en ABEL-HDL a) Entradas y salidas b) Sincronización de los Flip Flops c) Asignación de valores a los estados d) Definir la secuencia (state_diagram o Truth_table) e) Elaborar el Test_Vectors Noviembre de 2015 Sistemas Digitales Electrónica Digital I

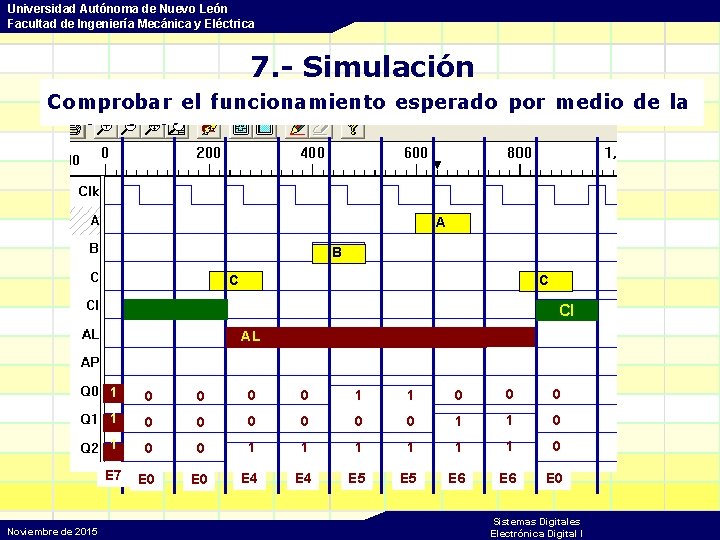

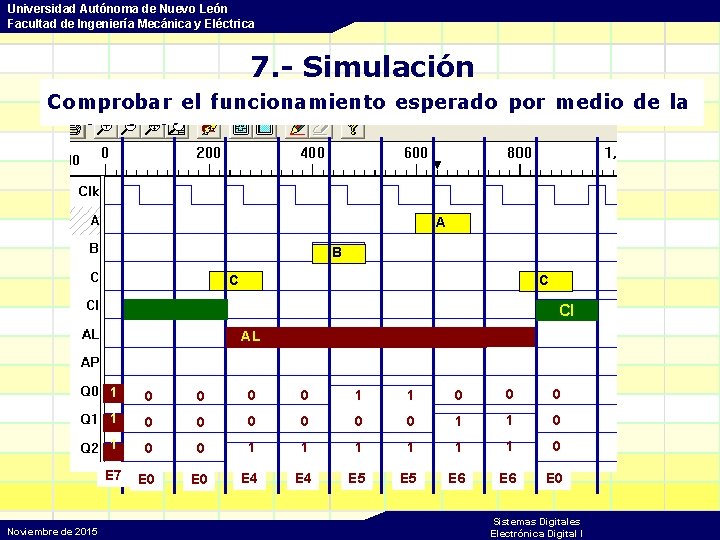

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 7. - Simulación Comprobar el funcionamiento esperado por medio de la simulación A B C C CI AL Noviembre de 2015 1 0 0 1 1 0 0 0 1 1 0 0 1 1 1 0 E 7 E 0 E 4 E 5 E 6 E 0 Sistemas Digitales Electrónica Digital I

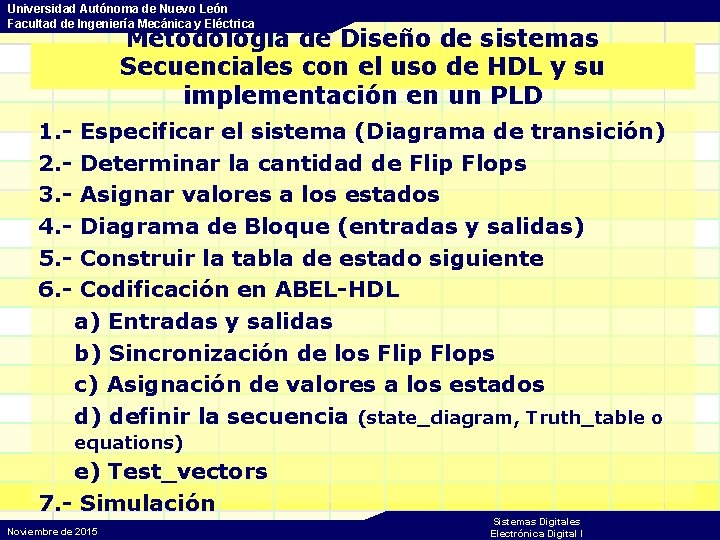

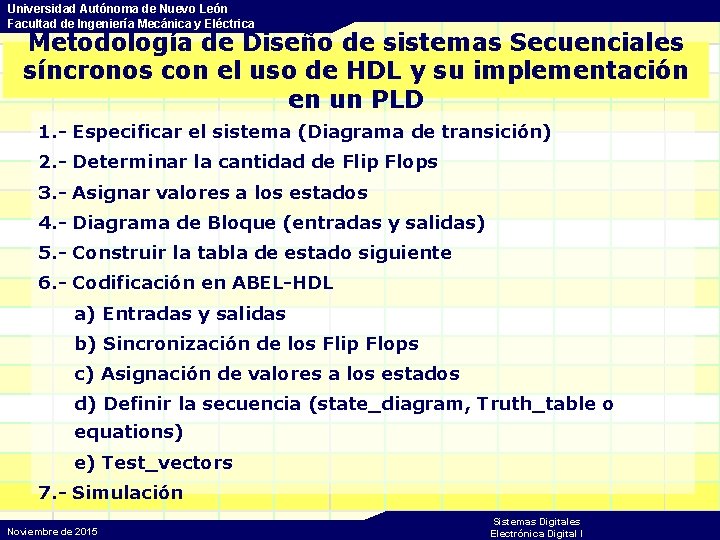

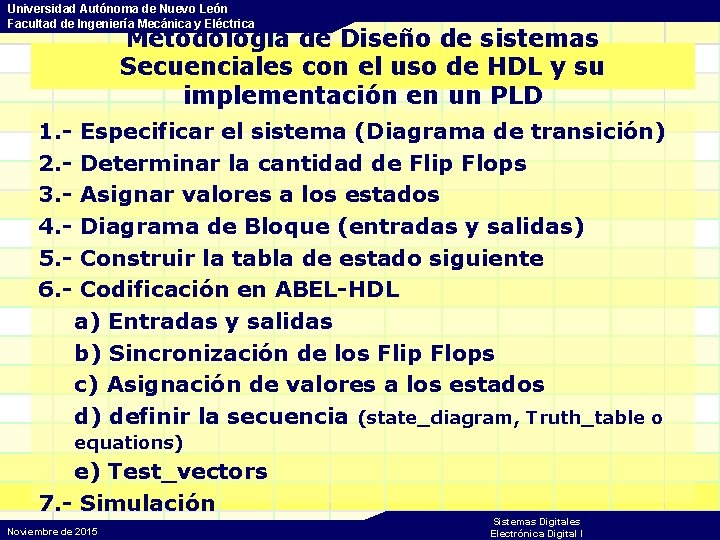

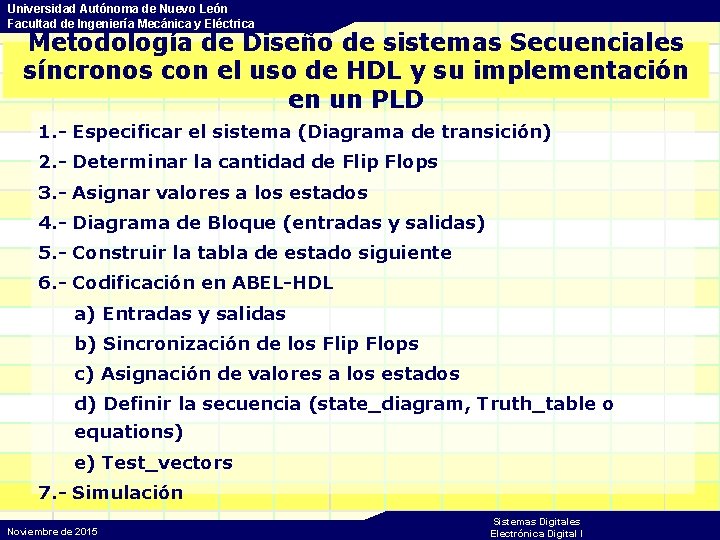

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Metodología de Diseño de sistemas Secuenciales con el uso de HDL y su implementación en un PLD 1. 2. 3. 4. 5. 6. - Especificar el sistema (Diagrama de transición) Determinar la cantidad de Flip Flops Asignar valores a los estados Diagrama de Bloque (entradas y salidas) Construir la tabla de estado siguiente Codificación en ABEL-HDL a) Entradas y salidas b) Sincronización de los Flip Flops c) Asignación de valores a los estados d) definir la secuencia (state_diagram, Truth_table o equations) e) Test_vectors 7. - Simulación Noviembre de 2015 Sistemas Digitales Electrónica Digital I

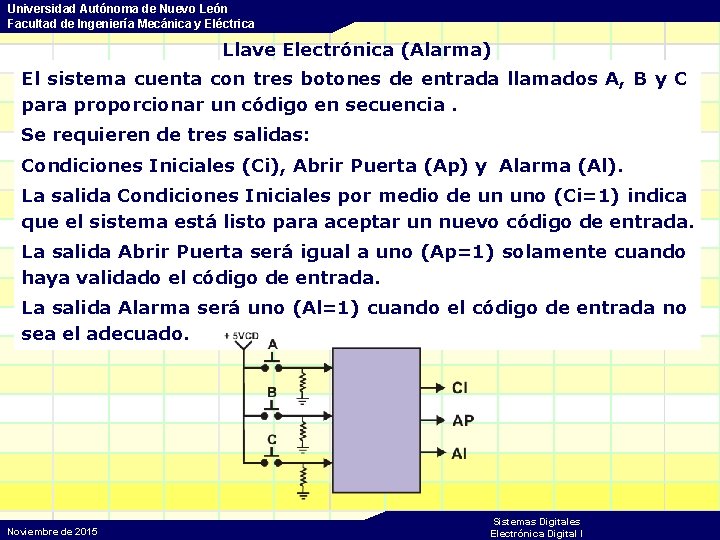

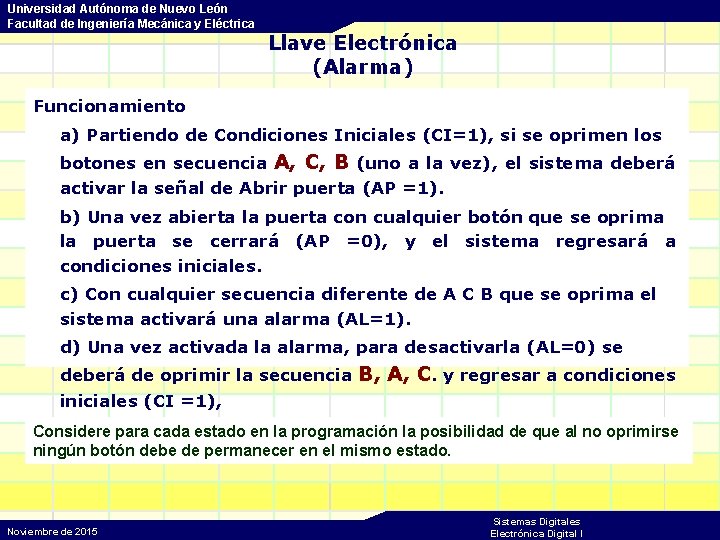

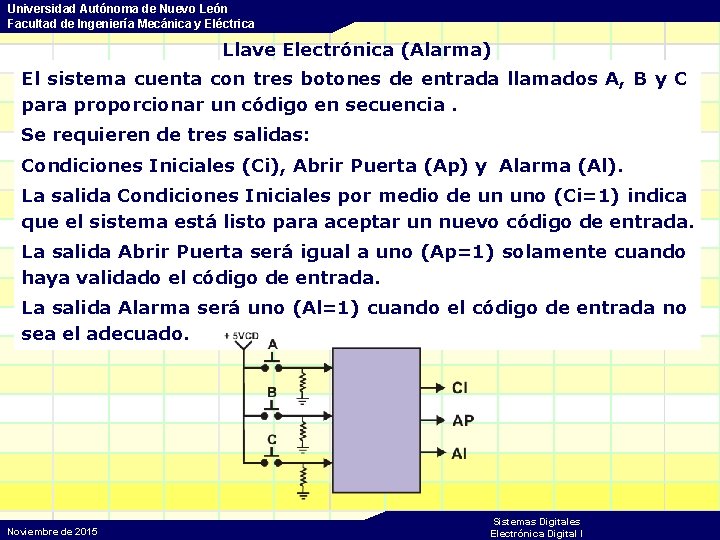

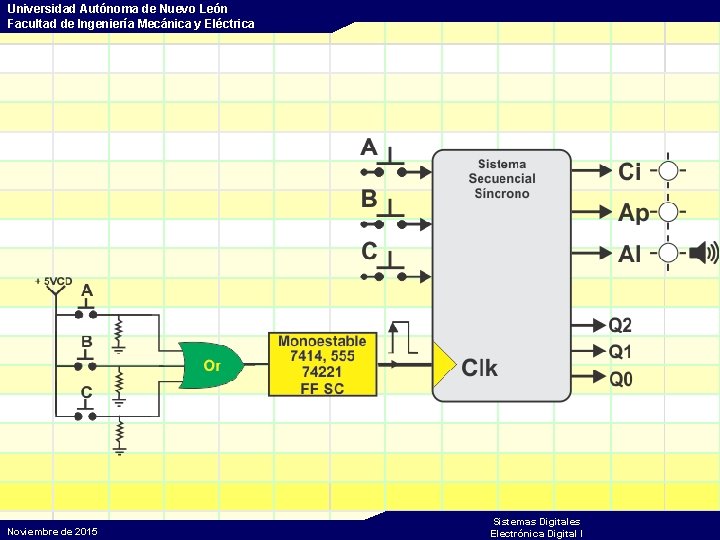

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Llave Electrónica (Alarma) El sistema cuenta con tres botones de entrada llamados A, B y C para proporcionar un código en secuencia. Se requieren de tres salidas: Condiciones Iniciales (Ci), Abrir Puerta (Ap) y Alarma (Al). La salida Condiciones Iniciales por medio de un uno (Ci=1) indica que el sistema está listo para aceptar un nuevo código de entrada. La salida Abrir Puerta será igual a uno (Ap=1) solamente cuando haya validado el código de entrada. La salida Alarma será uno (Al=1) cuando el código de entrada no sea el adecuado. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

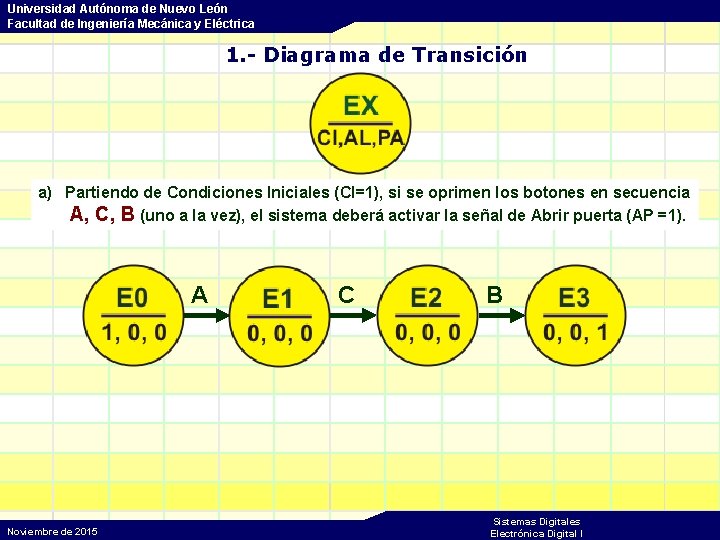

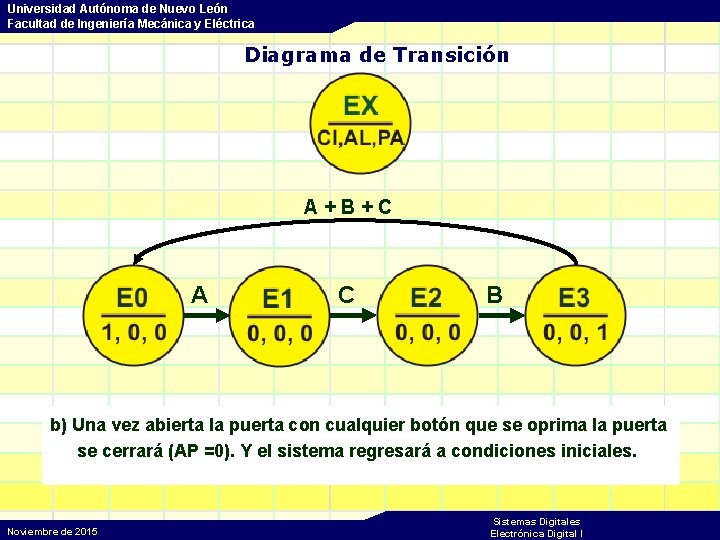

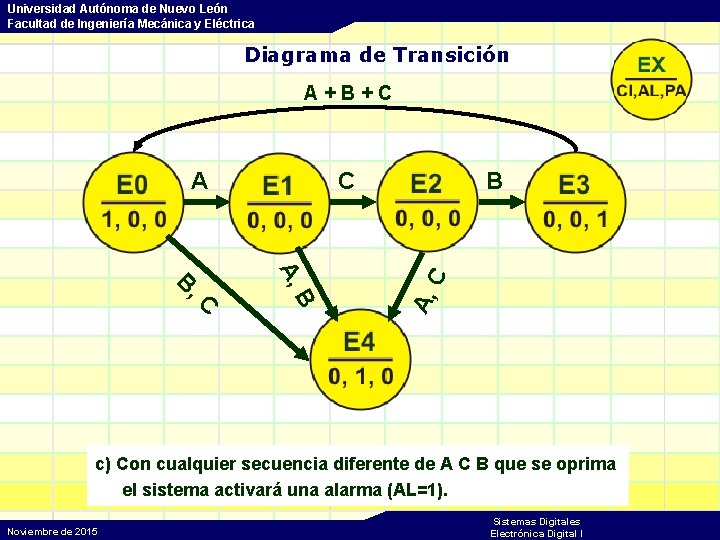

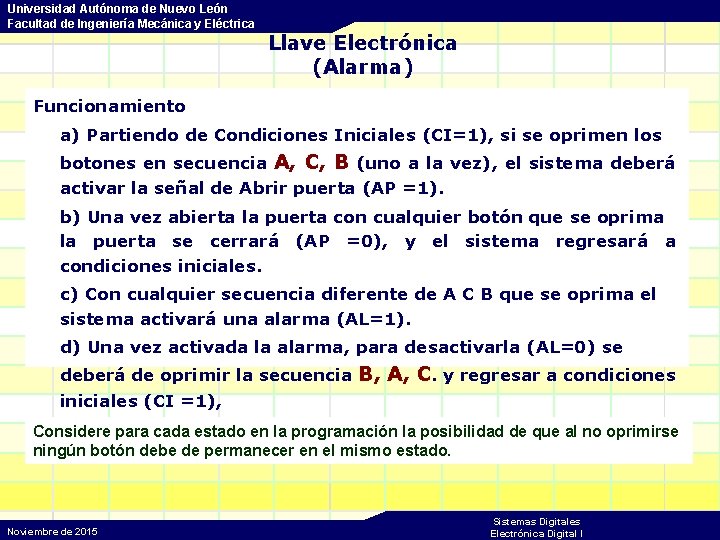

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Llave Electrónica (Alarma) Funcionamiento a) Partiendo de Condiciones Iniciales (CI=1), si se oprimen los botones en secuencia A, C, B (uno a la vez), el sistema deberá activar la señal de Abrir puerta (AP =1). b) Una vez abierta la puerta con cualquier botón que se oprima la puerta se cerrará (AP =0), y el sistema regresará a condiciones iniciales. c) Con cualquier secuencia diferente de A C B que se oprima el sistema activará una alarma (AL=1). d) Una vez activada la alarma, para desactivarla (AL=0) se deberá de oprimir la secuencia B, A, C. y regresar a condiciones iniciales (CI =1), Considere para cada estado en la programación la posibilidad de que al no oprimirse ningún botón debe de permanecer en el mismo estado. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

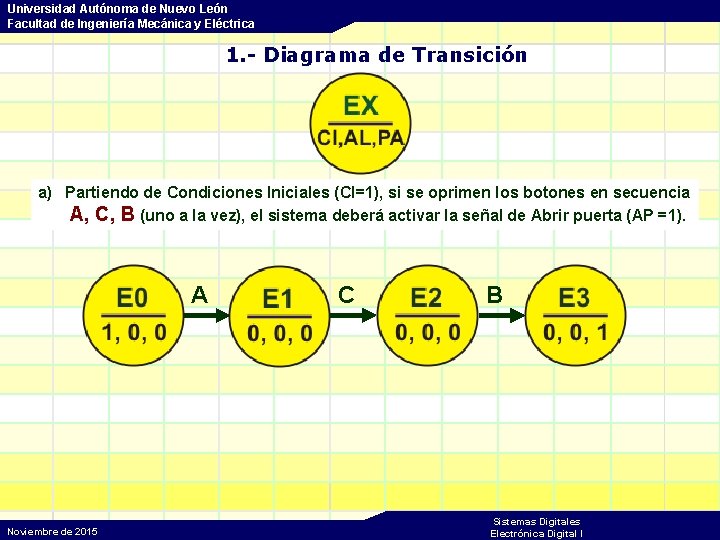

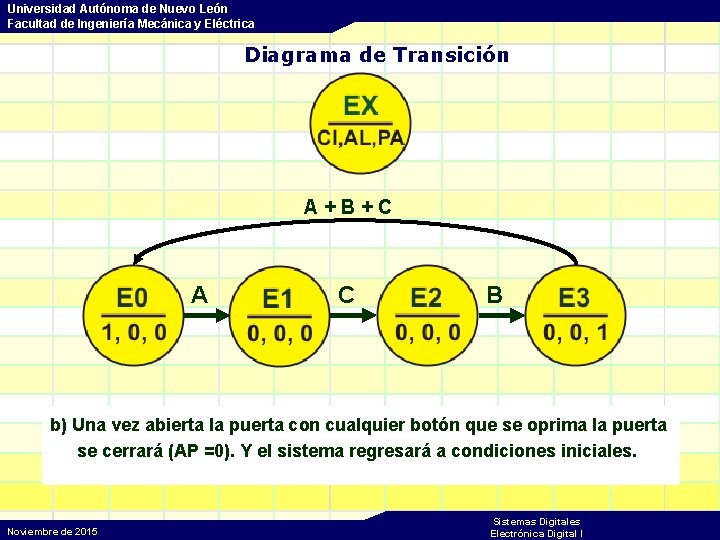

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 1. - Diagrama de Transición a) Partiendo de Condiciones Iniciales (CI=1), si se oprimen los botones en secuencia A, C, B (uno a la vez), el sistema deberá activar la señal de Abrir puerta (AP =1). A Noviembre de 2015 C B Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Diagrama de Transición A+B+C A C B b) Una vez abierta la puerta con cualquier botón que se oprima la puerta se cerrará (AP =0). Y el sistema regresará a condiciones iniciales. Noviembre de 2015 Sistemas Digitales Electrónica Digital I

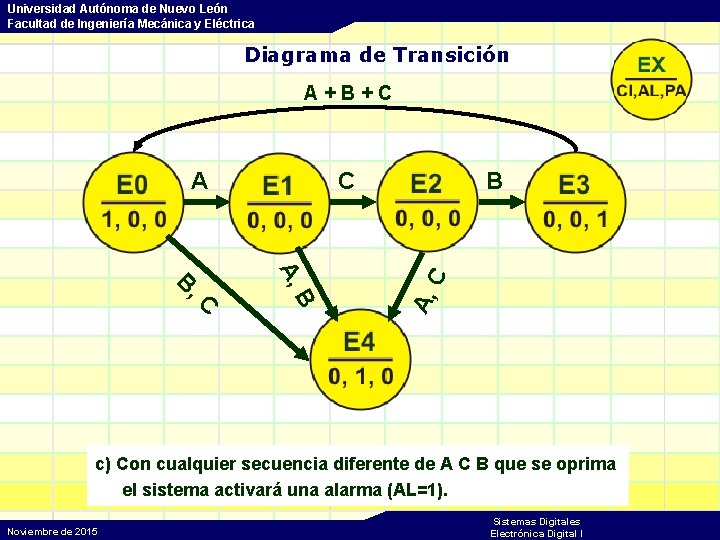

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Diagrama de Transición A+B+C C B , C B A, B C A, A c) Con cualquier secuencia diferente de A C B que se oprima el sistema activará una alarma (AL=1). Noviembre de 2015 Sistemas Digitales Electrónica Digital I

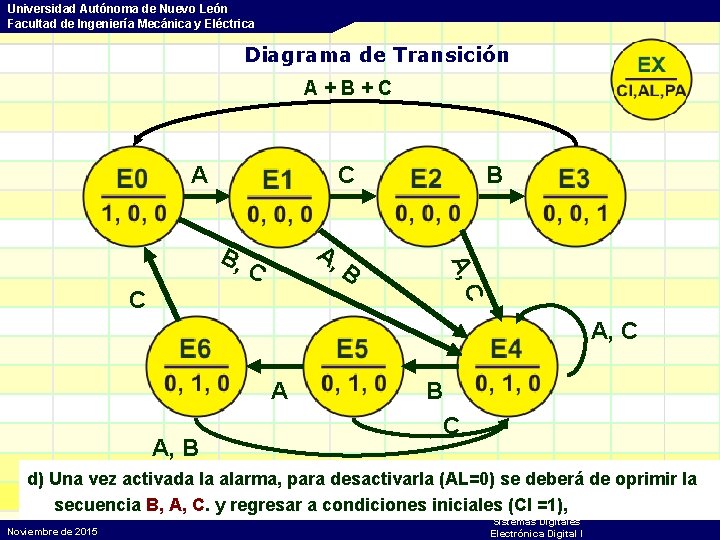

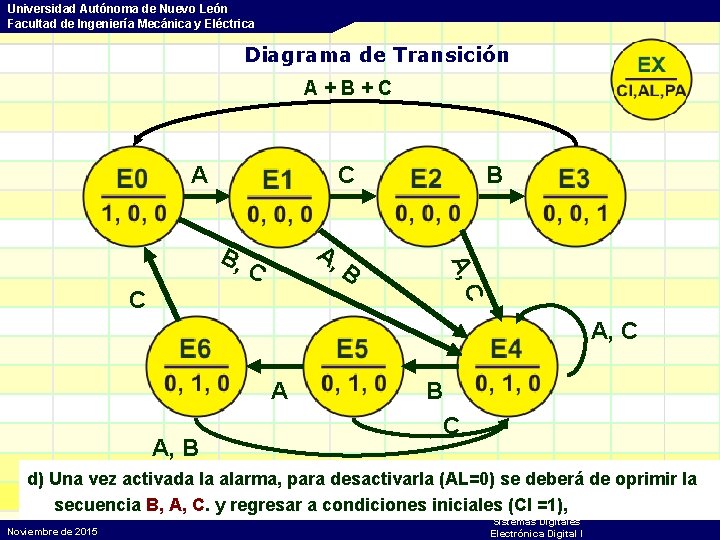

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Diagrama de Transición A+B+C A C A, C B A, B C C A, C A A, B B C d) Una vez activada la alarma, para desactivarla (AL=0) se deberá de oprimir la secuencia B, A, C. y regresar a condiciones iniciales (CI =1), Noviembre de 2015 Sistemas Digitales Electrónica Digital I

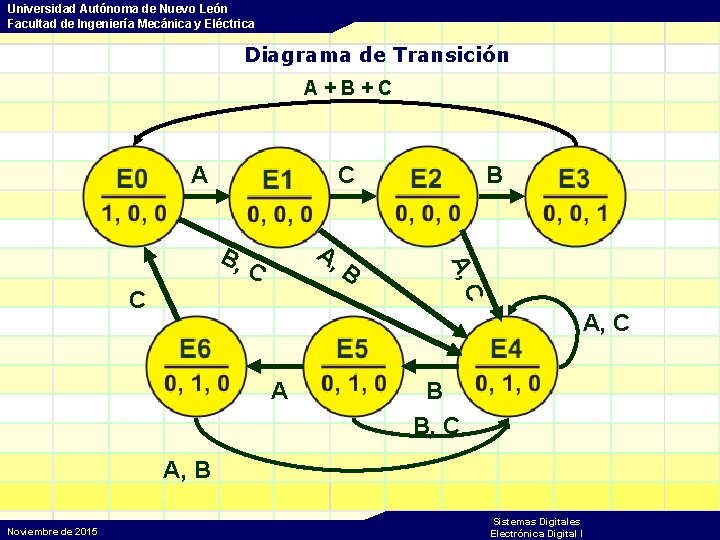

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Diagrama de Transición A+B+C A C A, C C C B A, C A B B, C A, B Noviembre de 2015 Sistemas Digitales Electrónica Digital I

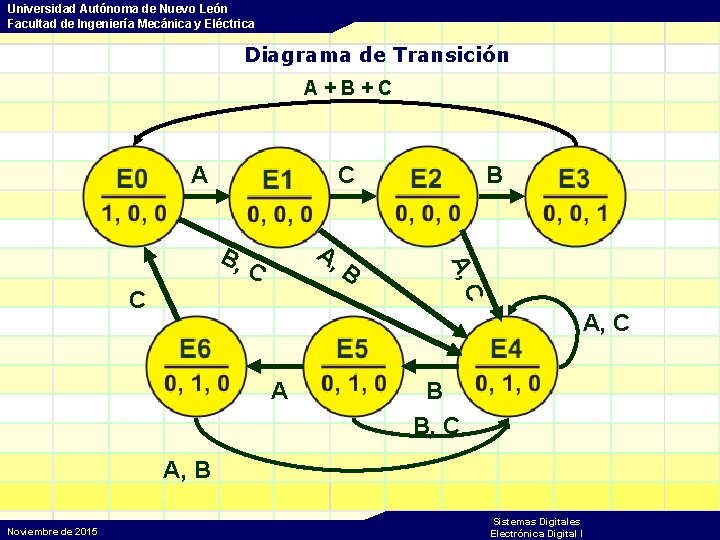

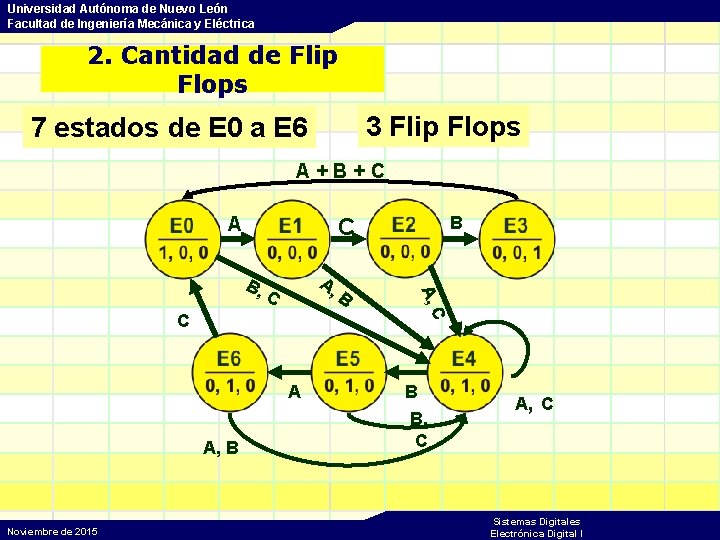

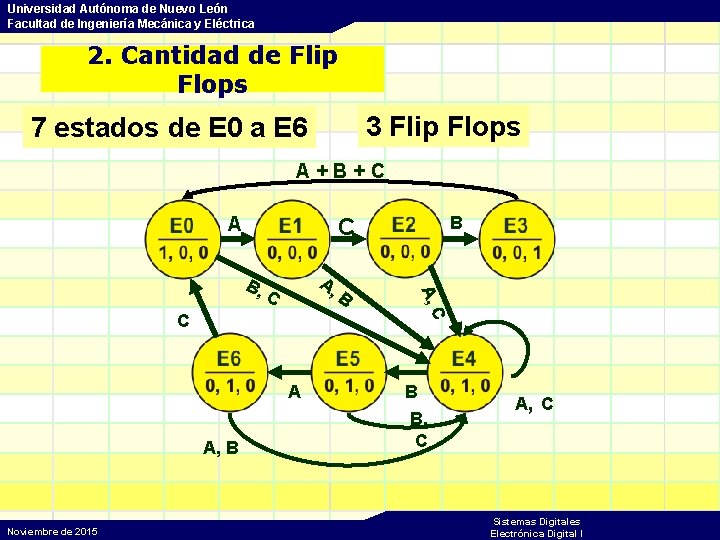

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 2. Cantidad de Flip Flops 3 Flip Flops 7 estados de E 0 a E 6 A+B+C A B C A, C B A, B, C C A A, B Noviembre de 2015 B B, C A, C Sistemas Digitales Electrónica Digital I

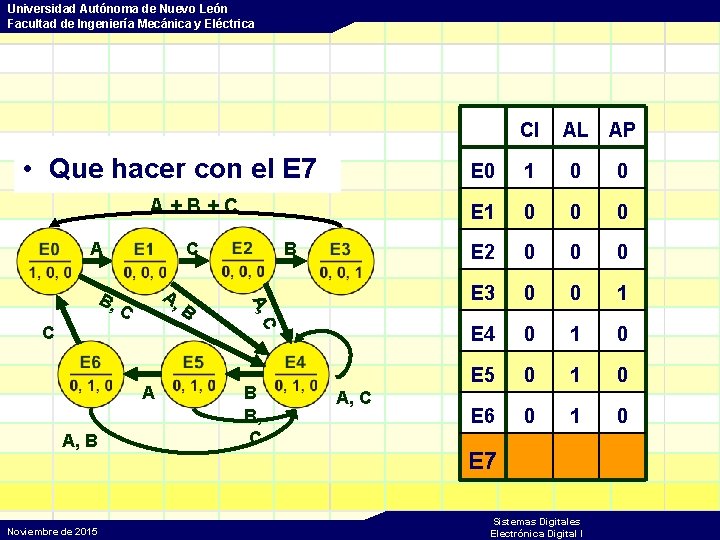

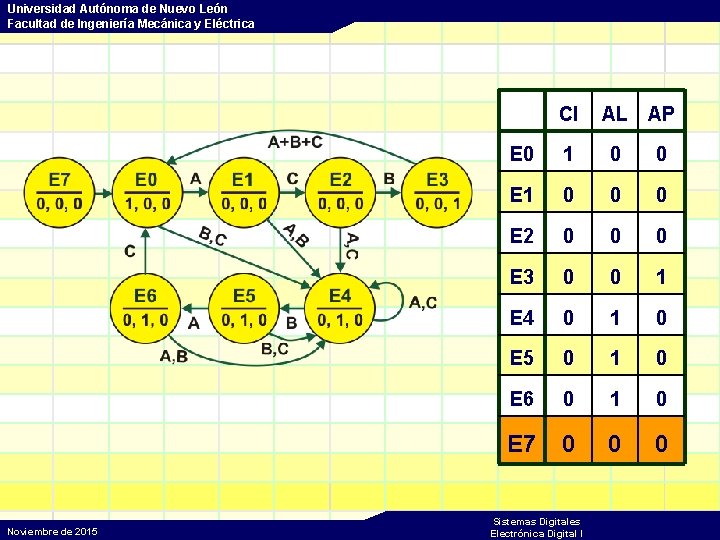

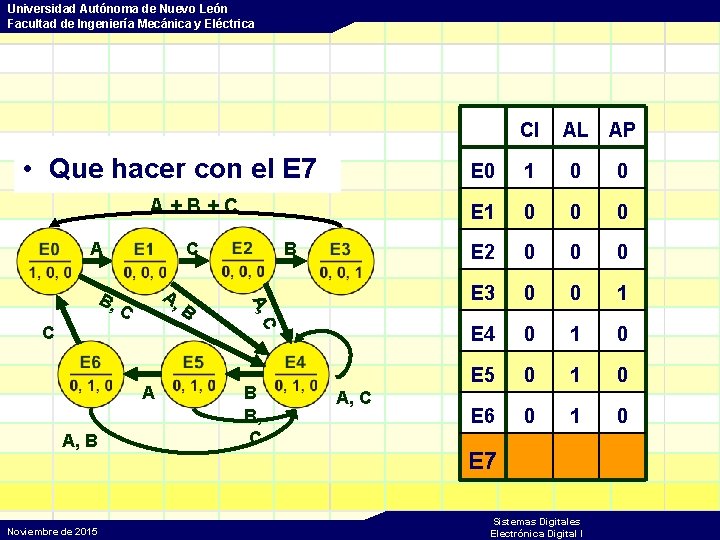

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica CI • Que hacer con el E 7 A+B+C A A, C B A, B C C C A A, B Noviembre de 2015 B B, C AL AP E 0 1 0 0 E 1 0 0 0 E 2 0 0 0 E 3 0 0 1 E 4 0 1 0 E 5 0 1 0 E 6 0 1 0 E 7 Sistemas Digitales Electrónica Digital I

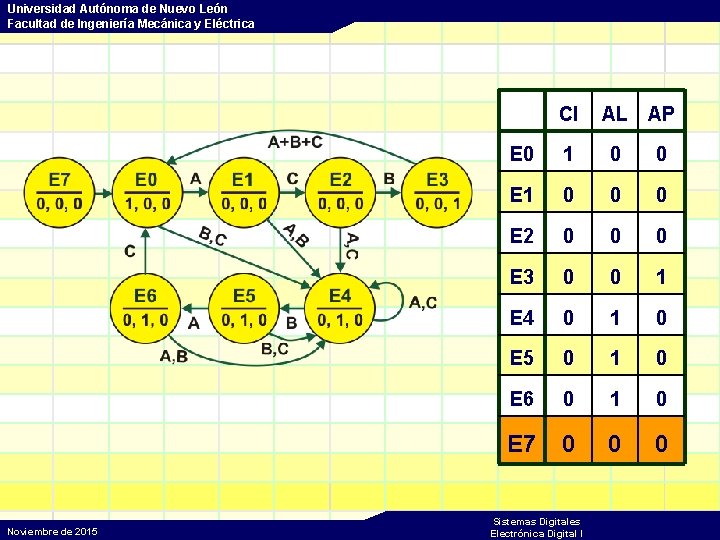

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica CI Noviembre de 2015 AL AP E 0 1 0 0 E 1 0 0 0 E 2 0 0 0 E 3 0 0 1 E 4 0 1 0 E 5 0 1 0 E 6 0 1 0 E 7 0 0 0 Sistemas Digitales Electrónica Digital I

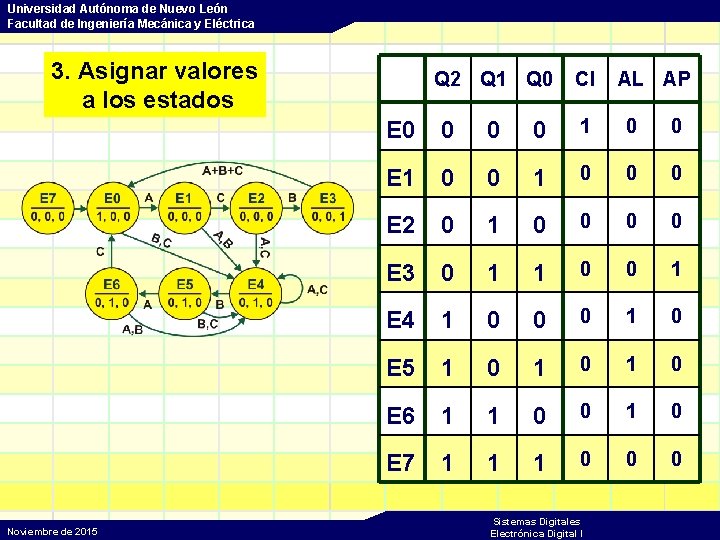

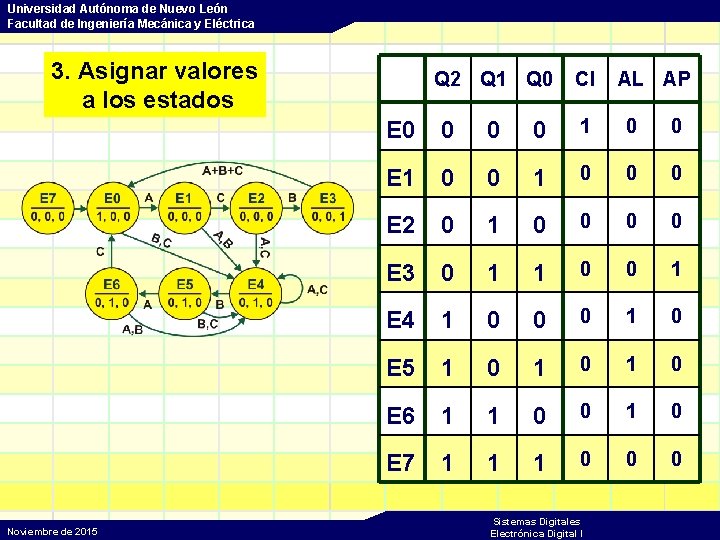

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 3. Asignar valores a los estados Noviembre de 2015 Q 2 Q 1 Q 0 CI AL AP E 0 0 1 0 0 E 1 0 0 0 E 2 0 1 0 0 E 3 0 1 1 0 0 1 E 4 1 0 0 0 1 0 E 5 1 0 1 0 E 6 1 1 0 0 1 0 E 7 1 1 1 0 0 0 Sistemas Digitales Electrónica Digital I

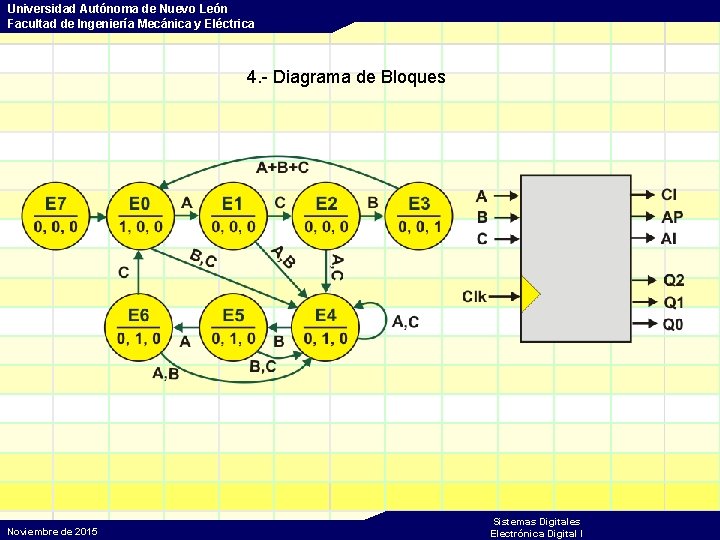

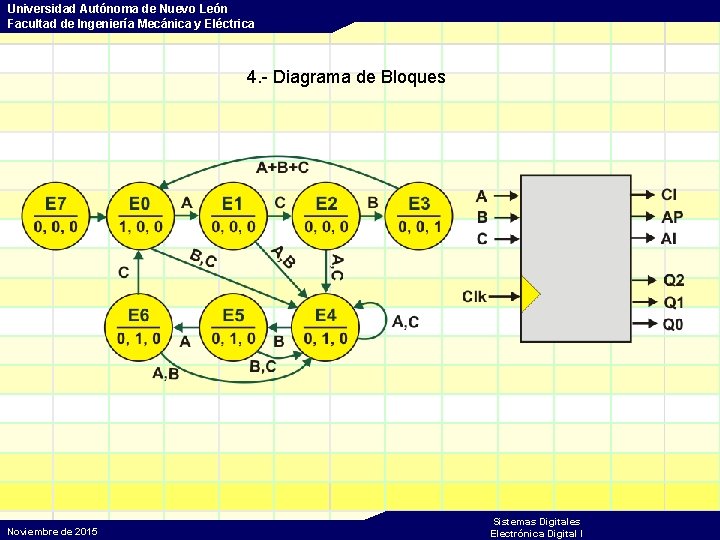

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 4. - Diagrama de Bloques Noviembre de 2015 Sistemas Digitales Electrónica Digital I

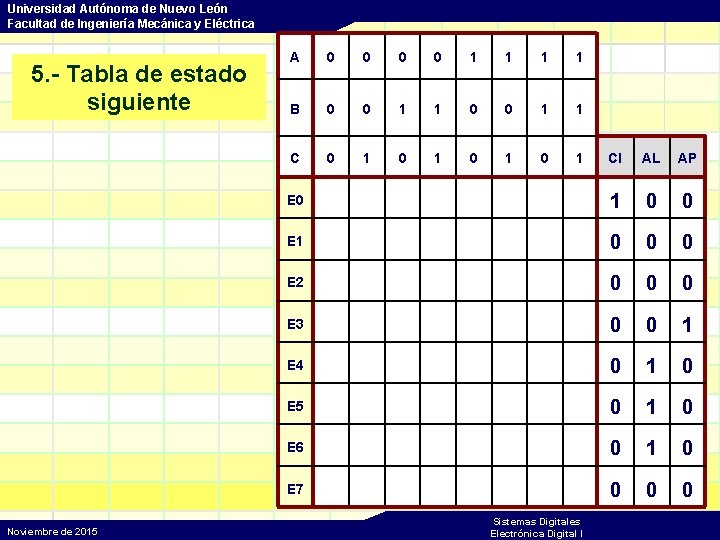

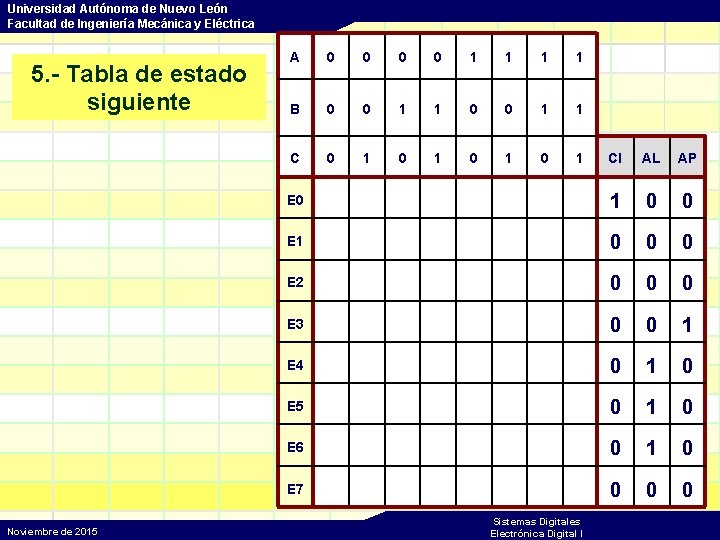

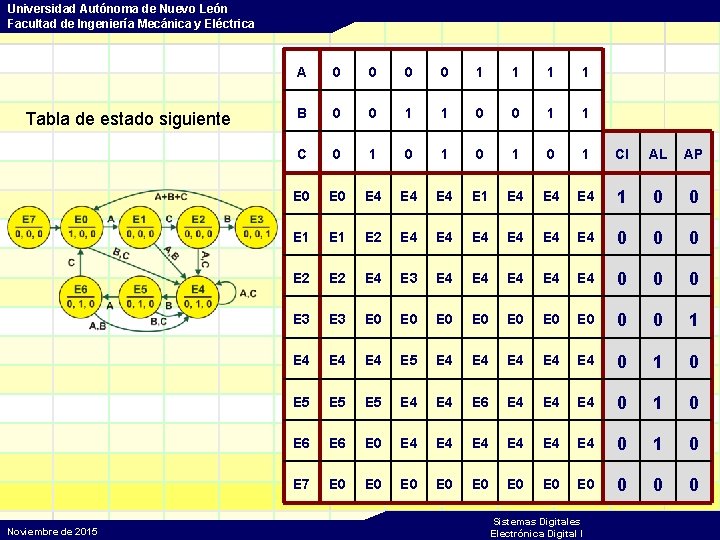

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 5. - Tabla de estado siguiente Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL AP E 0 1 0 0 E 1 0 0 0 E 2 0 0 0 E 3 0 0 1 E 4 0 1 0 E 5 0 1 0 E 6 0 1 0 E 7 0 0 0 Sistemas Digitales Electrónica Digital I

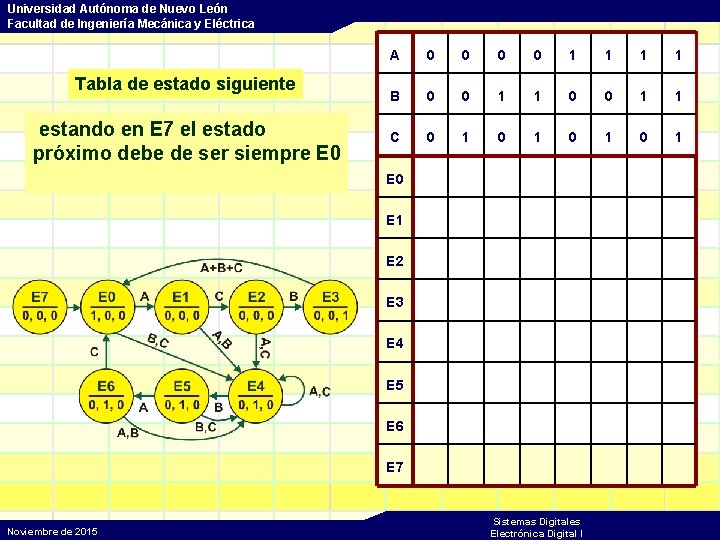

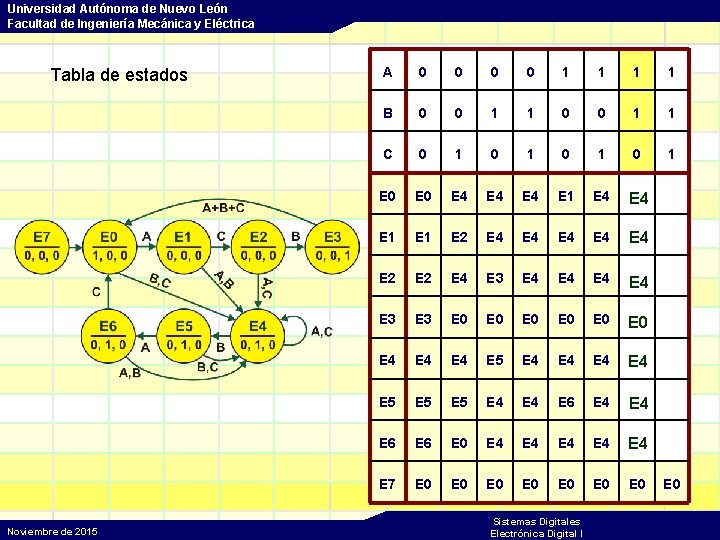

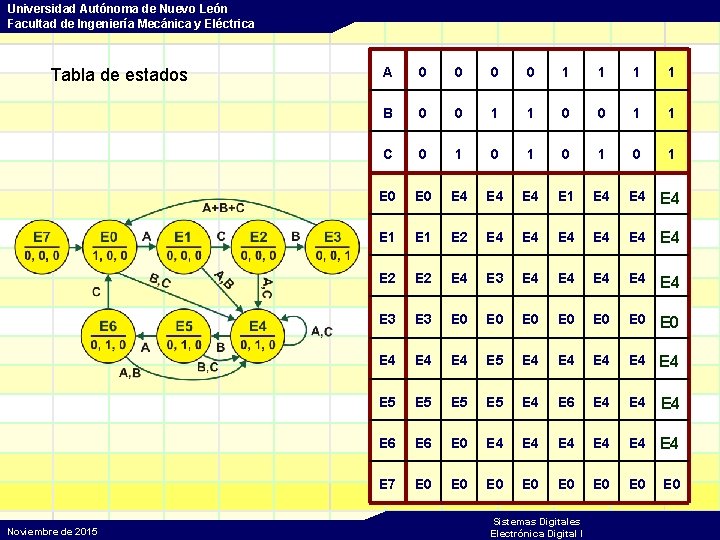

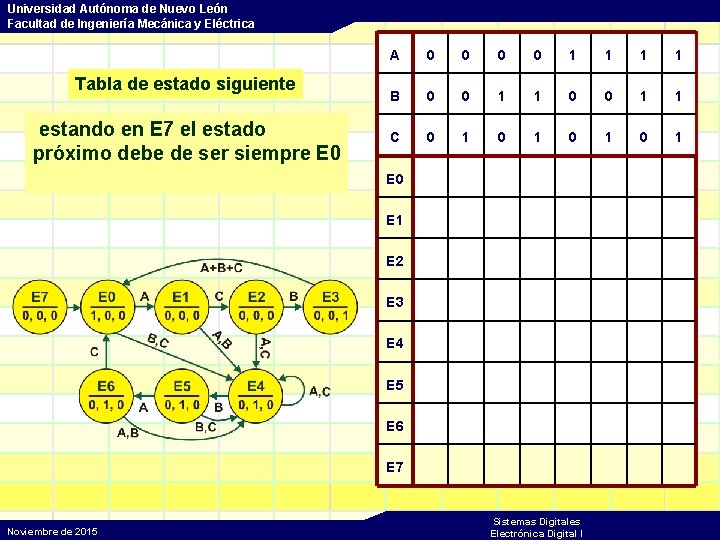

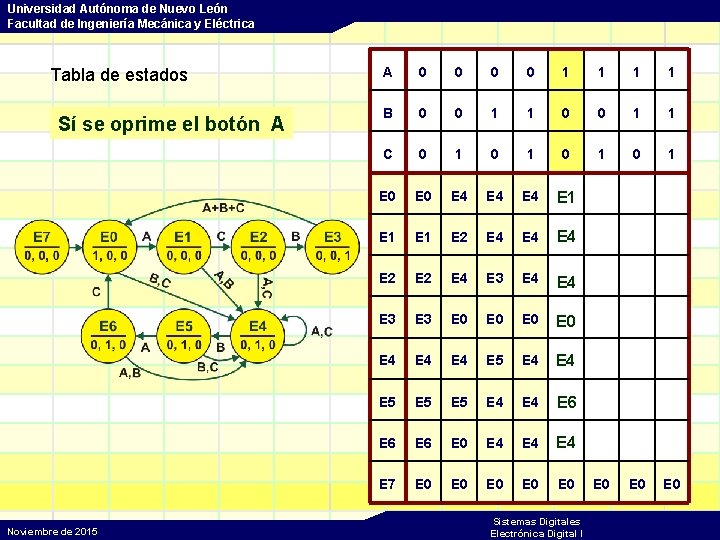

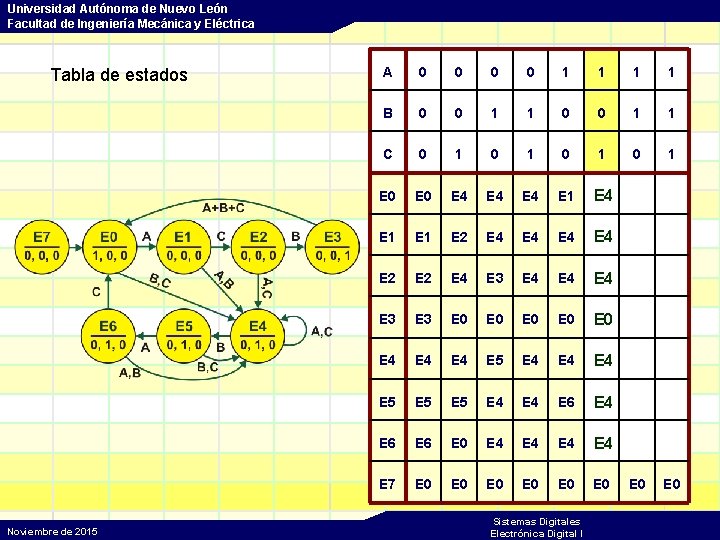

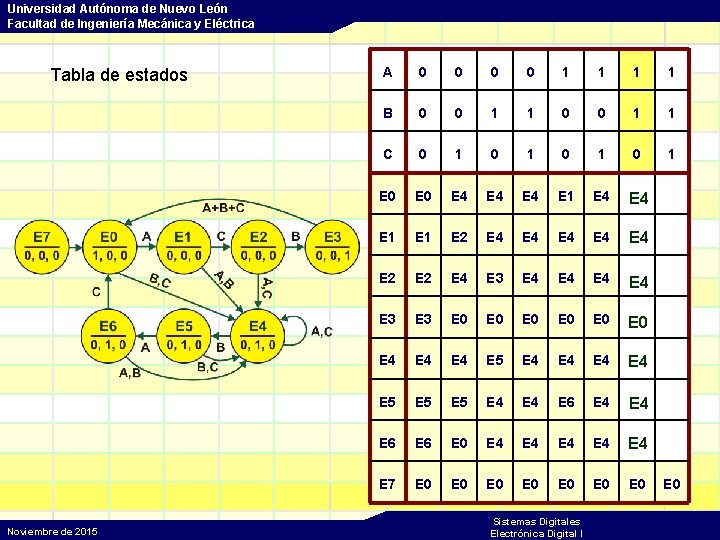

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estado siguiente estando en E 7 el estado próximo debe de ser siempre E 0 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 1 E 2 E 3 E 4 E 5 E 6 E 7 Noviembre de 2015 Sistemas Digitales Electrónica Digital I

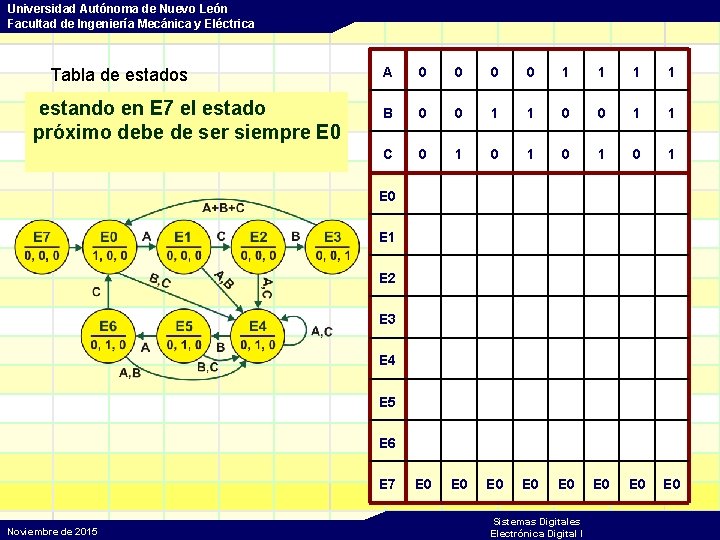

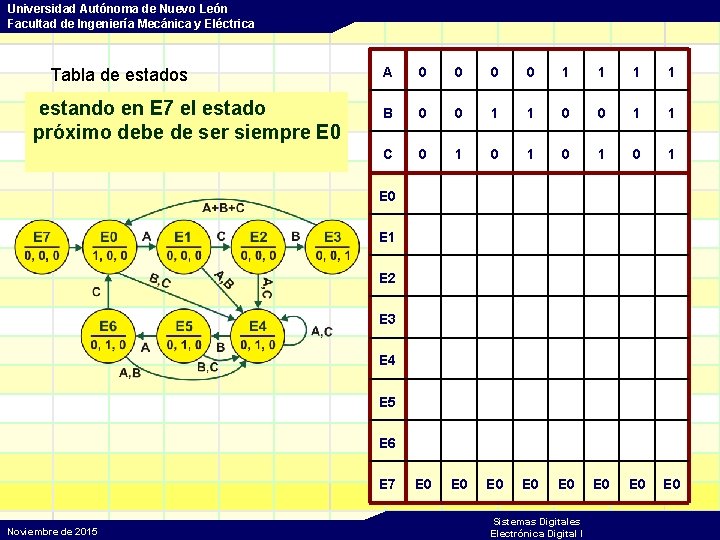

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados estando en E 7 el estado próximo debe de ser siempre E 0 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 0 E 0 E 1 E 2 E 3 E 4 E 5 E 6 E 7 Noviembre de 2015 Sistemas Digitales Electrónica Digital I

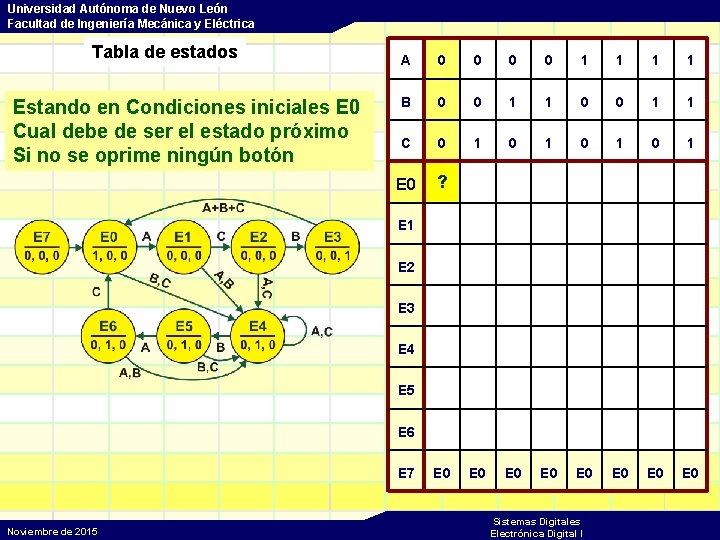

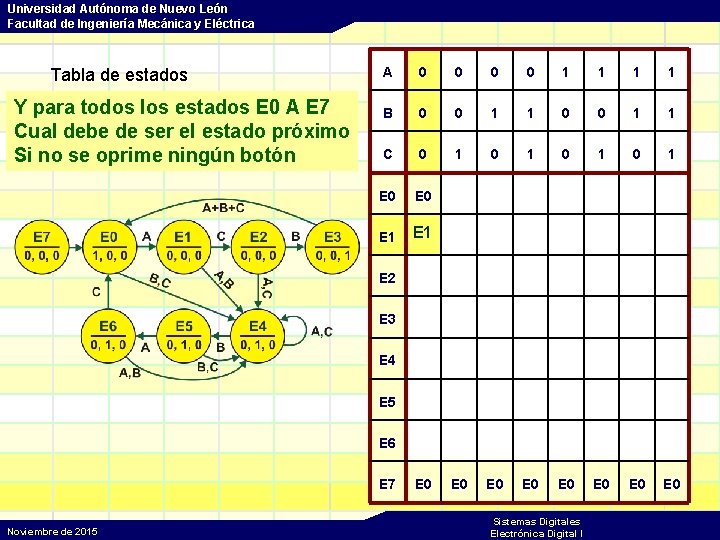

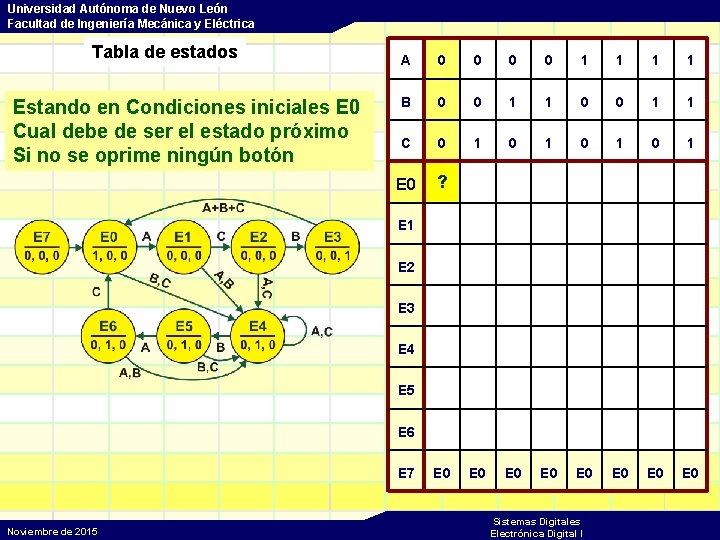

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Estando en Condiciones iniciales E 0 Cual debe de ser el estado próximo Si no se oprime ningún botón A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 ? E 0 E 0 E 1 E 2 E 3 E 4 E 5 E 6 E 7 Noviembre de 2015 E 0 Sistemas Digitales Electrónica Digital I

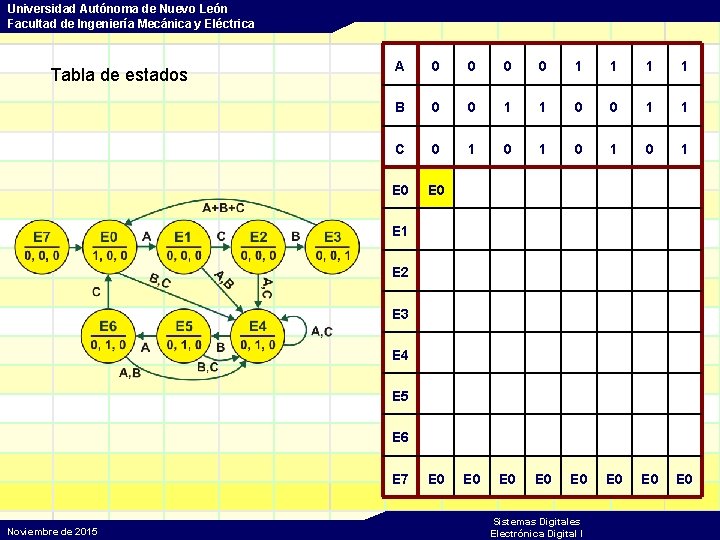

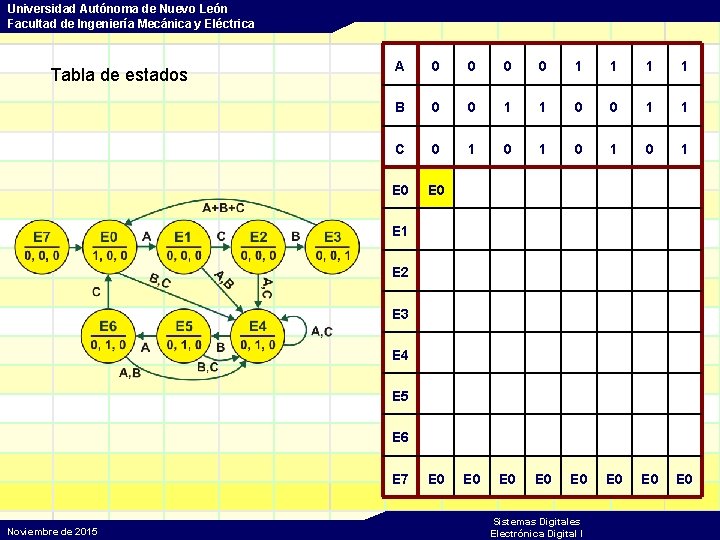

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 0 E 0 E 1 E 2 E 3 E 4 E 5 E 6 E 7 Noviembre de 2015 E 0 Sistemas Digitales Electrónica Digital I

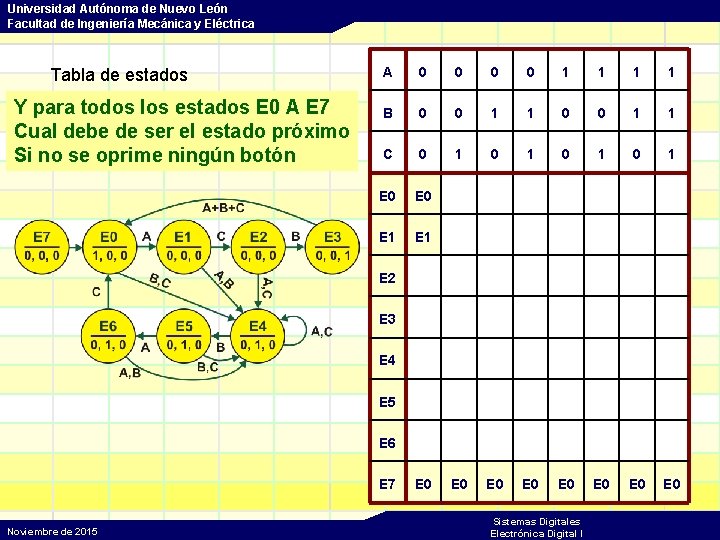

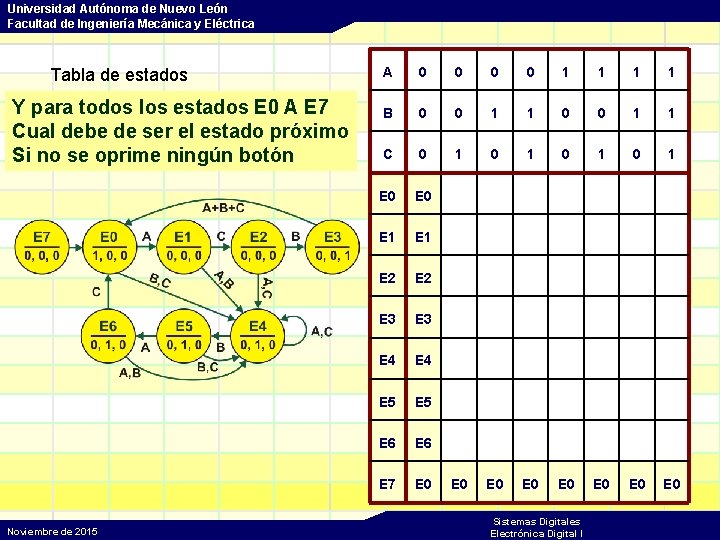

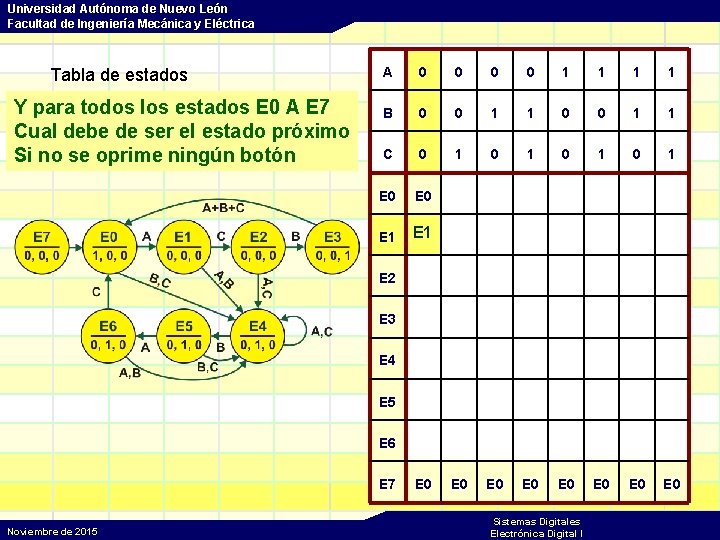

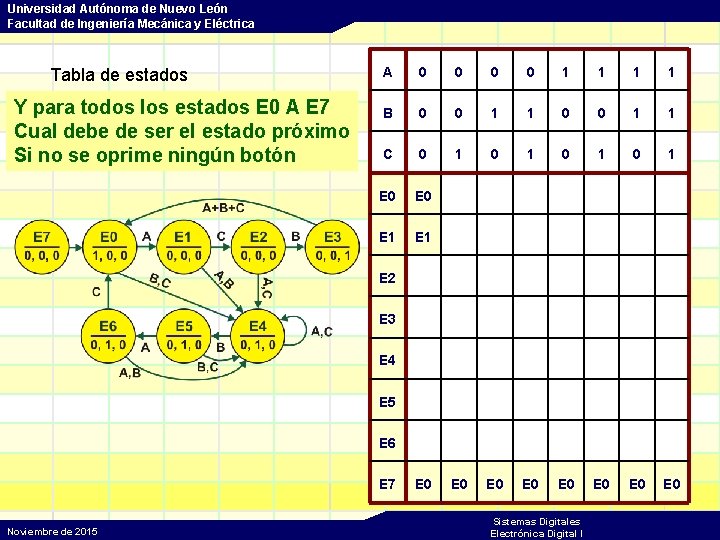

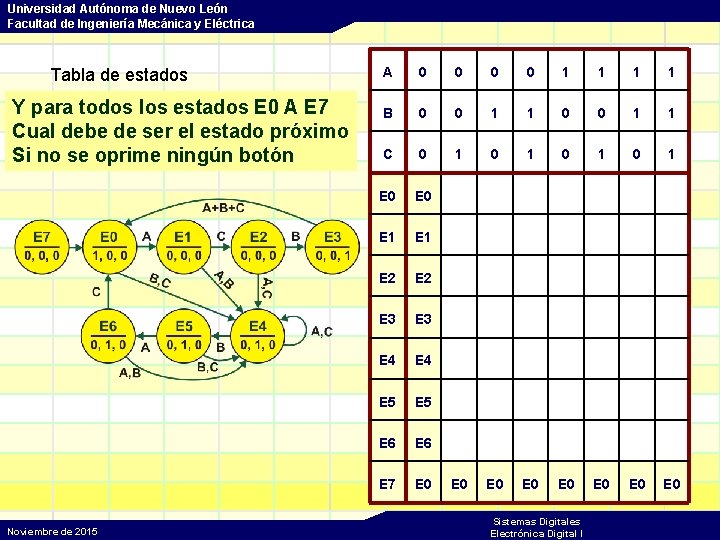

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Y para todos los estados E 0 A E 7 Cual debe de ser el estado próximo Si no se oprime ningún botón A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 0 E 0 E 0 E 2 E 3 E 4 E 5 E 6 E 7 Noviembre de 2015 E 0 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Y para todos los estados E 0 A E 7 Cual debe de ser el estado próximo Si no se oprime ningún botón A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 0 E 0 E 0 E 2 E 3 E 4 E 5 E 6 E 7 Noviembre de 2015 E 0 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Y para todos los estados E 0 A E 7 Cual debe de ser el estado próximo Si no se oprime ningún botón Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 1 E 2 E 3 E 4 E 5 E 6 E 7 E 0 E 0 Sistemas Digitales Electrónica Digital I

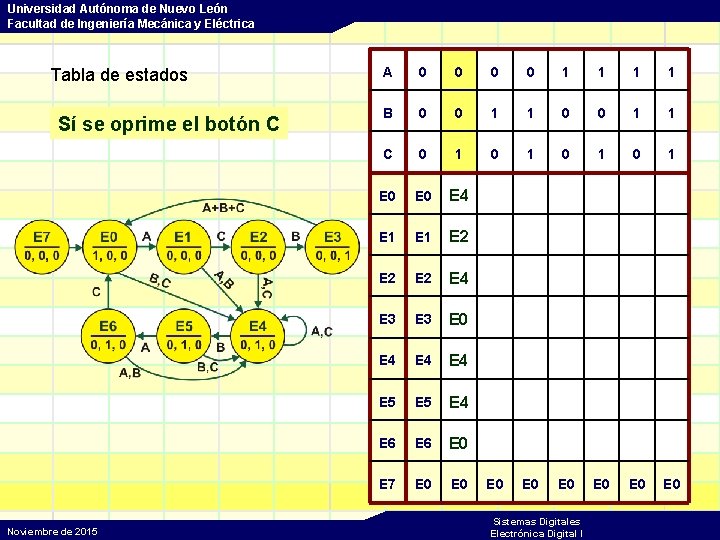

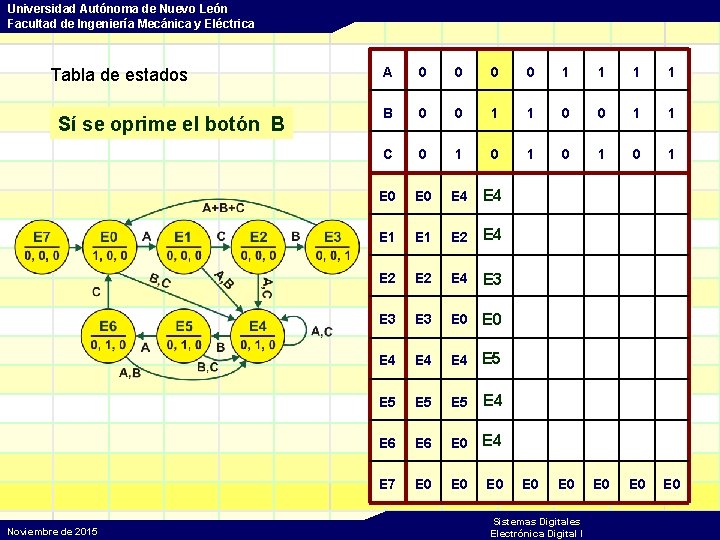

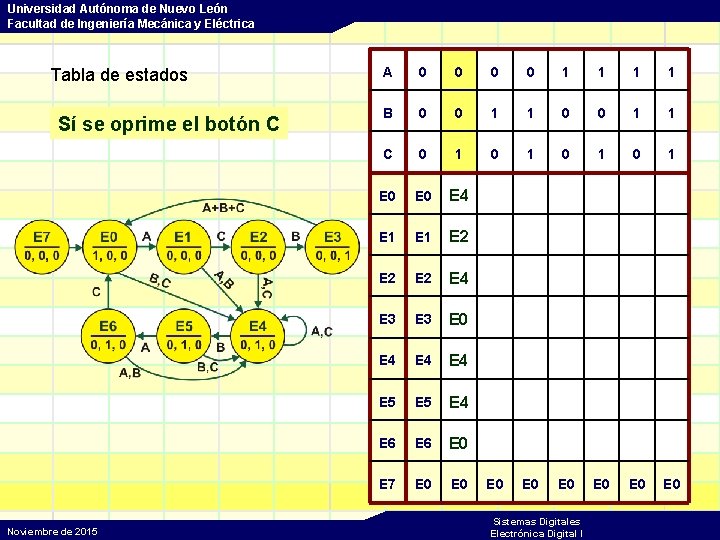

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Sí se oprime el botón C Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 4 E 1 E 2 E 2 E 4 E 3 E 0 E 4 E 4 E 5 E 4 E 6 E 0 E 7 E 0 E 0 Sistemas Digitales Electrónica Digital I

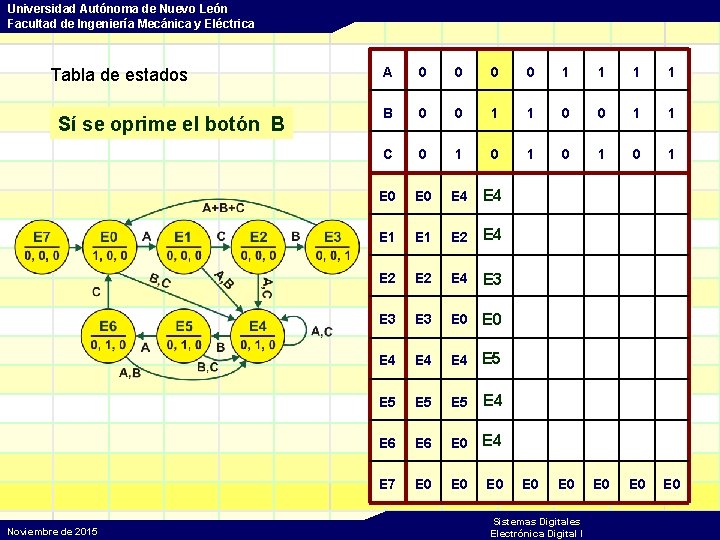

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Sí se oprime el botón B Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 4 E 1 E 2 E 4 E 3 E 3 E 0 E 4 E 4 E 5 E 5 E 4 E 6 E 0 E 4 E 7 E 0 E 0 Sistemas Digitales Electrónica Digital I

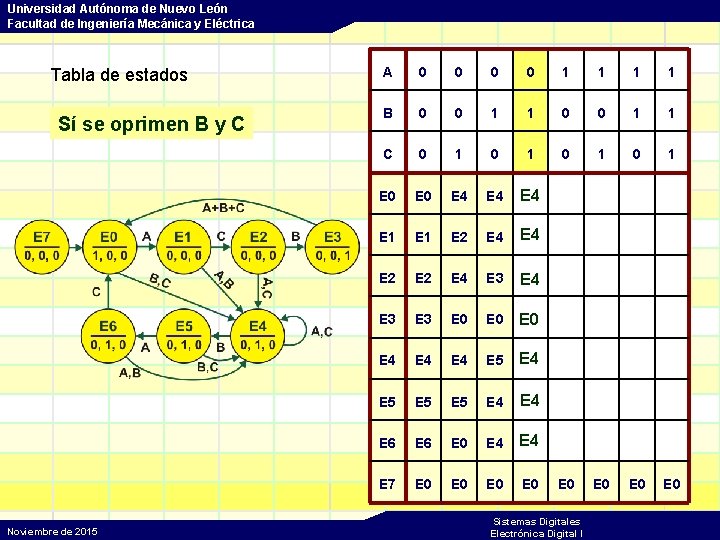

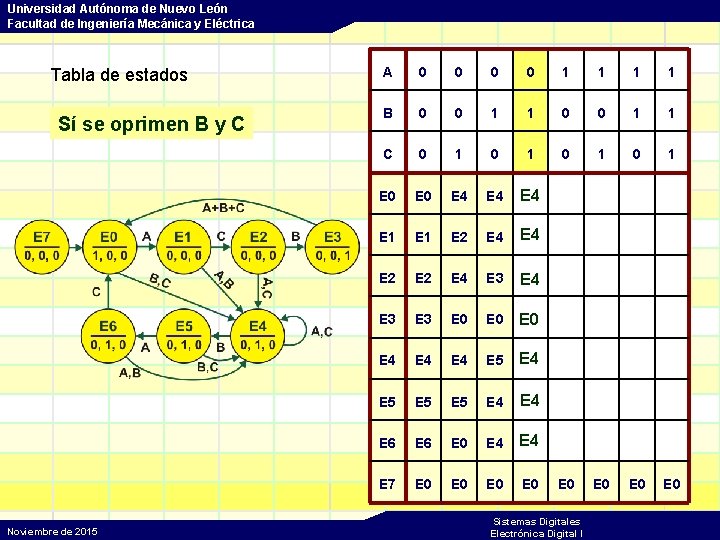

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Sí se oprimen B y C Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 4 E 4 E 1 E 2 E 4 E 3 E 3 E 0 E 0 E 4 E 4 E 5 E 5 E 4 E 6 E 0 E 4 E 7 E 0 E 0 Sistemas Digitales Electrónica Digital I

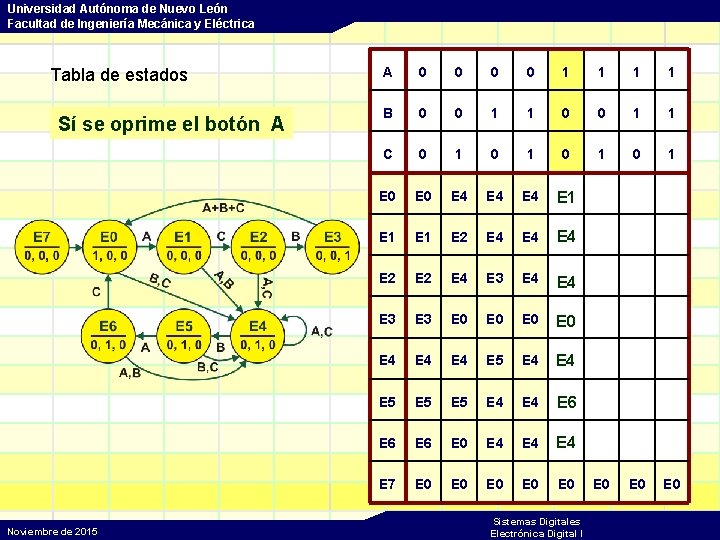

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Sí se oprime el botón A Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 4 E 4 E 1 E 1 E 2 E 4 E 4 E 2 E 4 E 3 E 0 E 0 E 4 E 4 E 5 E 5 E 4 E 6 E 6 E 0 E 4 E 4 E 7 E 0 E 0 Sistemas Digitales Electrónica Digital I

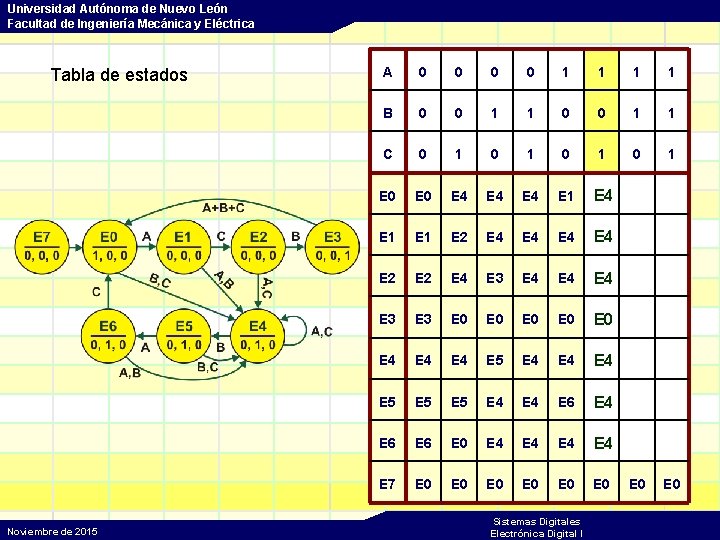

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 4 E 4 E 1 E 1 E 2 E 4 E 4 E 2 E 4 E 3 E 4 E 4 E 3 E 0 E 0 E 0 E 4 E 4 E 4 E 5 E 5 E 4 E 6 E 0 E 4 E 4 E 7 E 0 E 0 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 4 E 4 E 1 E 2 E 4 E 4 E 4 E 2 E 4 E 3 E 4 E 4 E 3 E 0 E 0 E 0 E 4 E 4 E 5 E 5 E 4 E 4 E 6 E 6 E 0 E 4 E 4 E 4 E 7 E 0 E 0 Sistemas Digitales Electrónica Digital I E 0

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estados Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 4 E 4 E 4 E 1 E 1 E 2 E 4 E 4 E 4 E 2 E 4 E 3 E 4 E 4 E 4 E 3 E 0 E 0 E 4 E 4 E 5 E 4 E 4 E 4 E 5 E 5 E 4 E 6 E 0 E 4 E 4 E 4 E 7 E 0 E 0 Sistemas Digitales Electrónica Digital I E 4 E 0

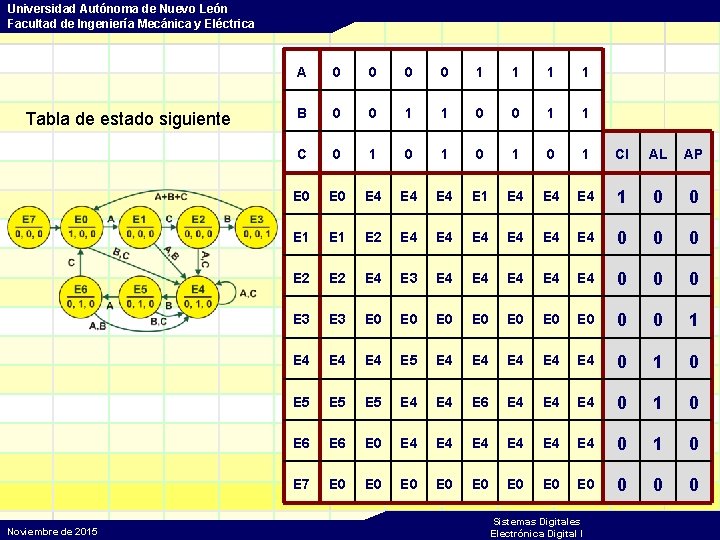

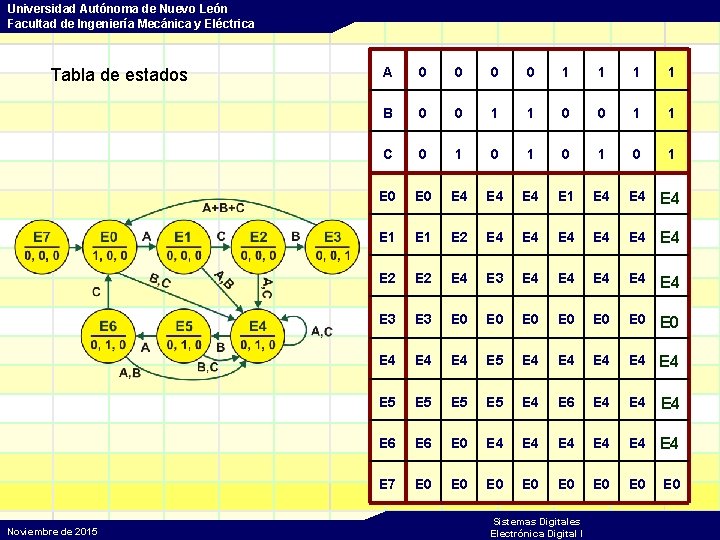

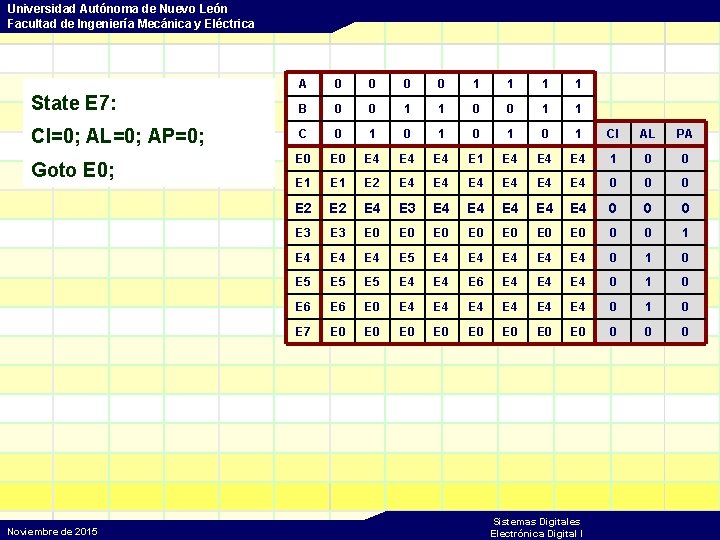

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Tabla de estado siguiente Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL AP E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 Sistemas Digitales Electrónica Digital I

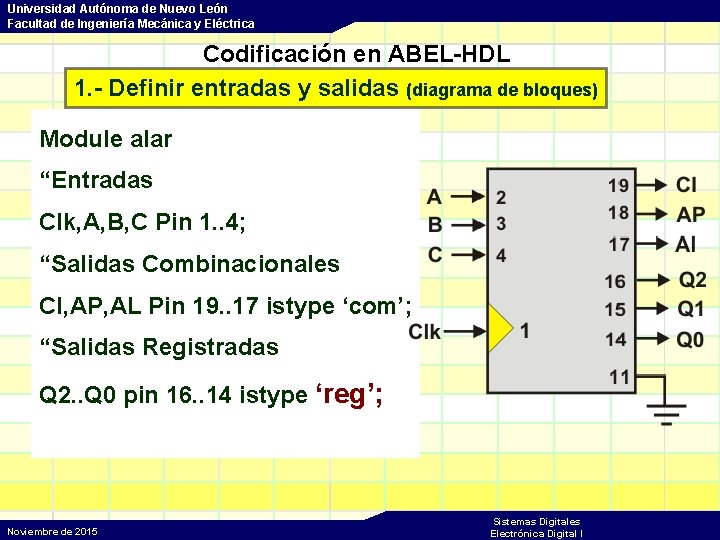

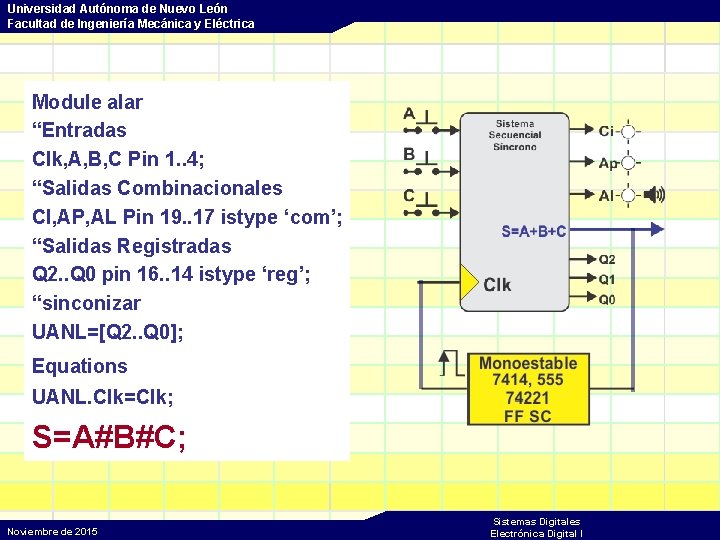

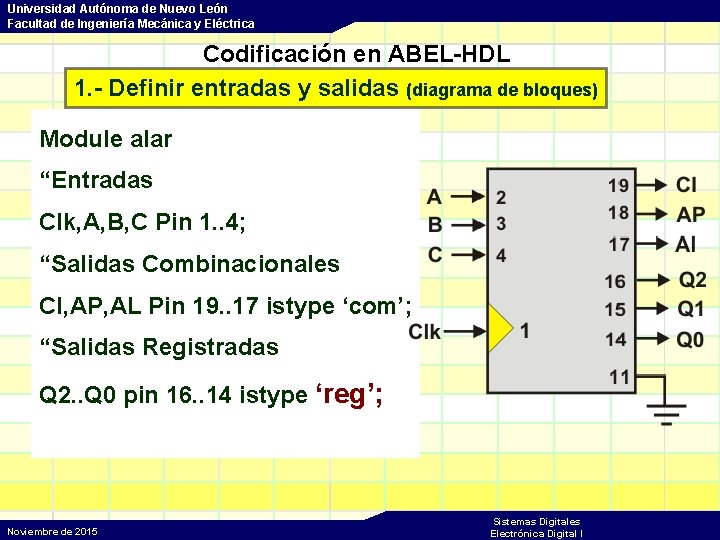

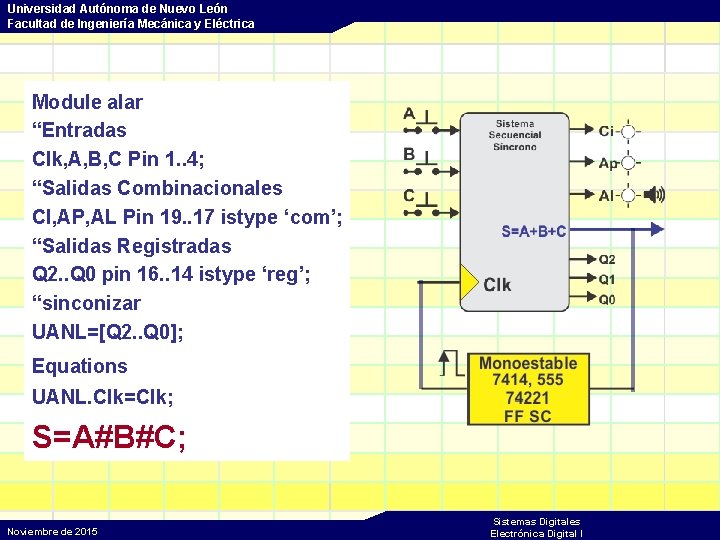

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Codificación en ABEL-HDL 1. - Definir entradas y salidas (diagrama de bloques) Module alar “Entradas Clk, A, B, C Pin 1. . 4; “Salidas Combinacionales CI, AP, AL Pin 19. . 17 istype ‘com’; “Salidas Registradas Q 2. . Q 0 pin 16. . 14 istype ‘reg’; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

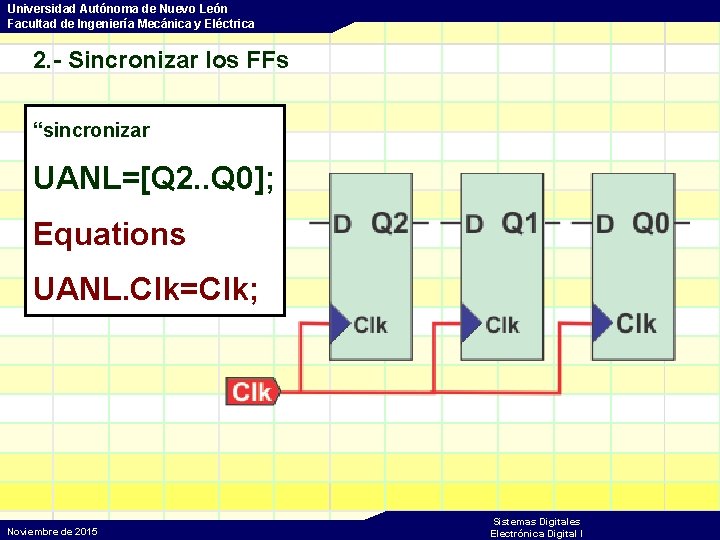

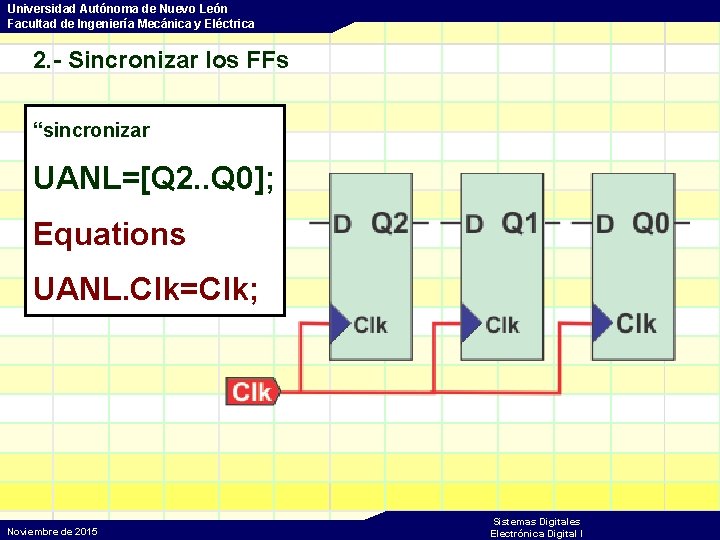

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 2. - Sincronizar los FFs “sincronizar UANL=[Q 2. . Q 0]; Equations UANL. Clk=Clk; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

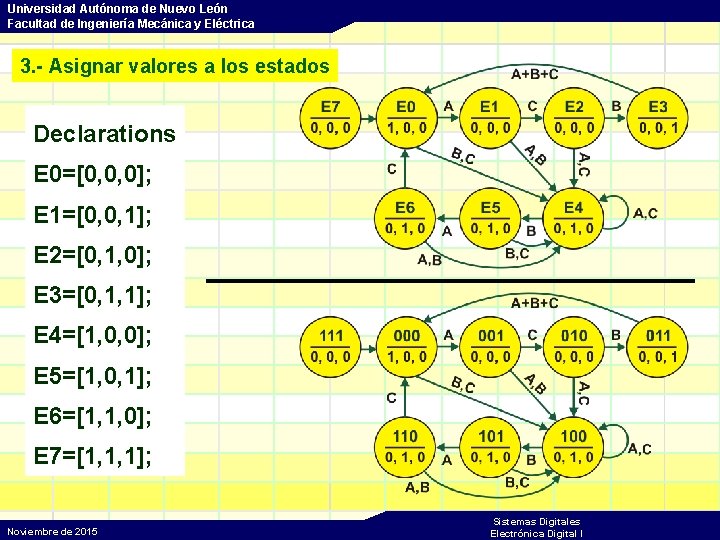

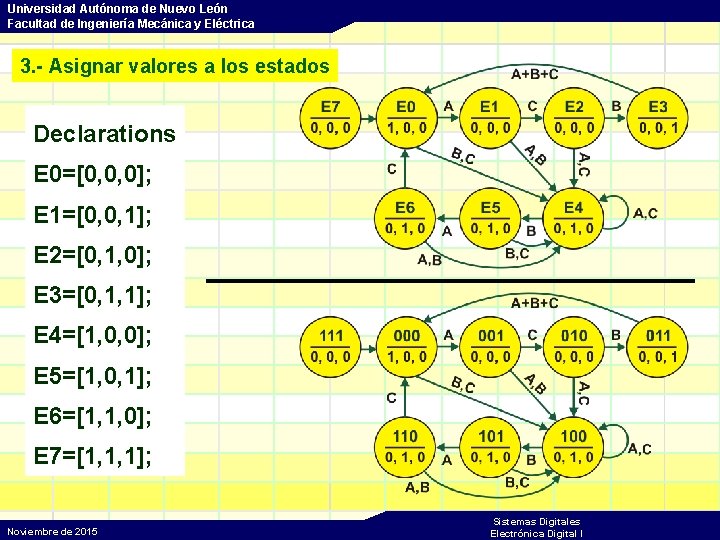

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 3. - Asignar valores a los estados Declarations E 0=[0, 0, 0]; E 1=[0, 0, 1]; E 2=[0, 1, 0]; E 3=[0, 1, 1]; E 4=[1, 0, 0]; E 5=[1, 0, 1]; E 6=[1, 1, 0]; E 7=[1, 1, 1]; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

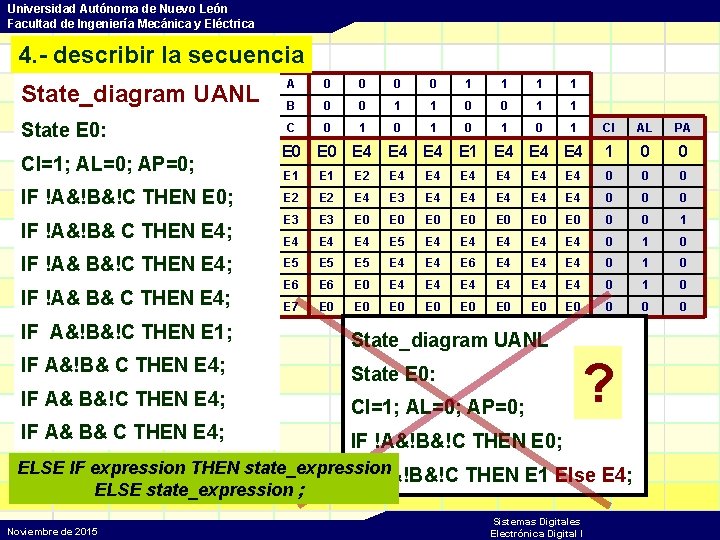

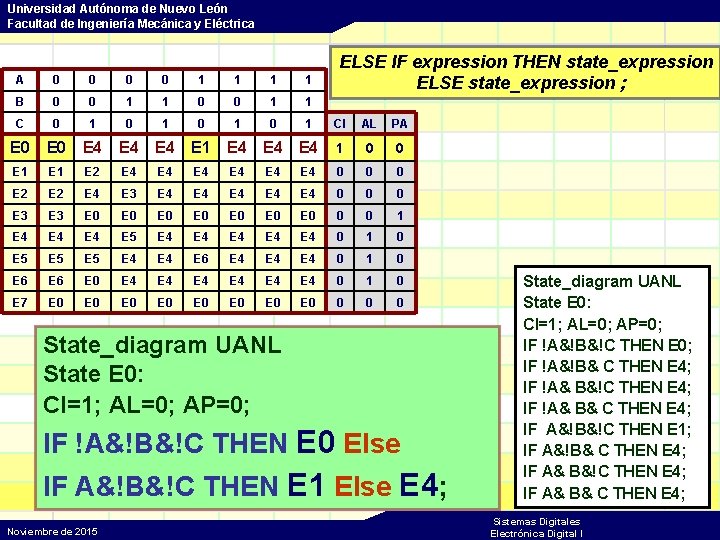

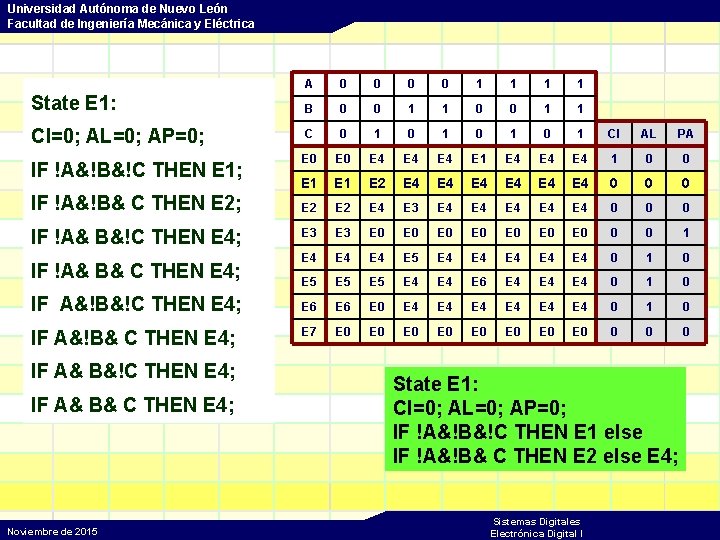

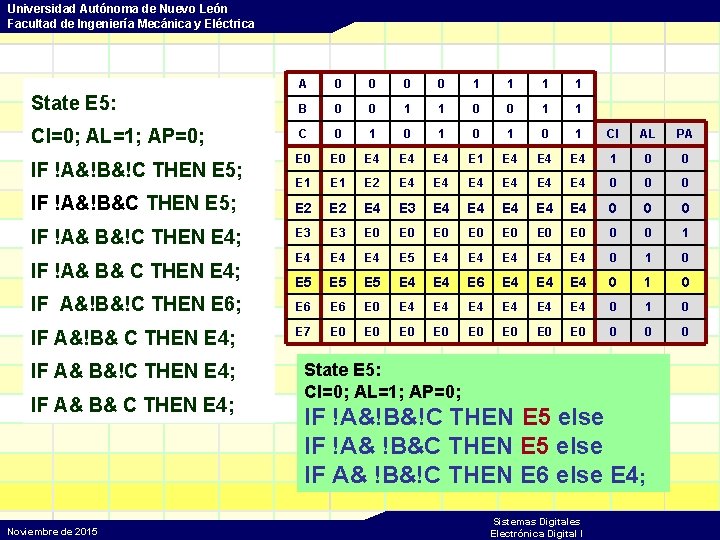

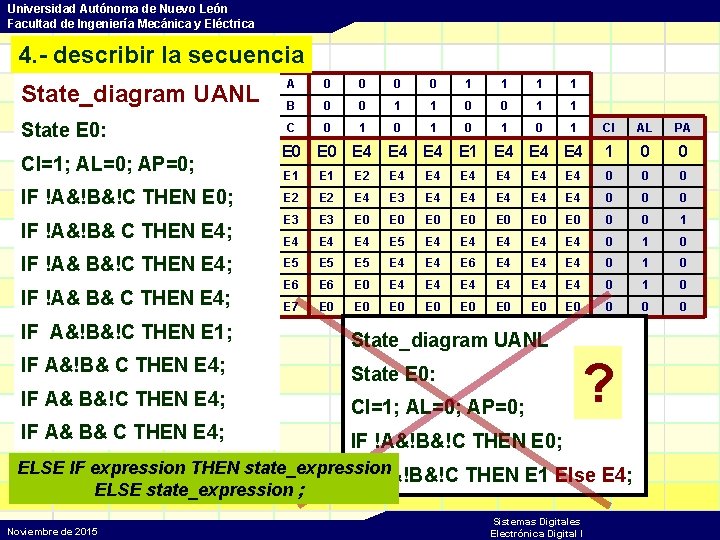

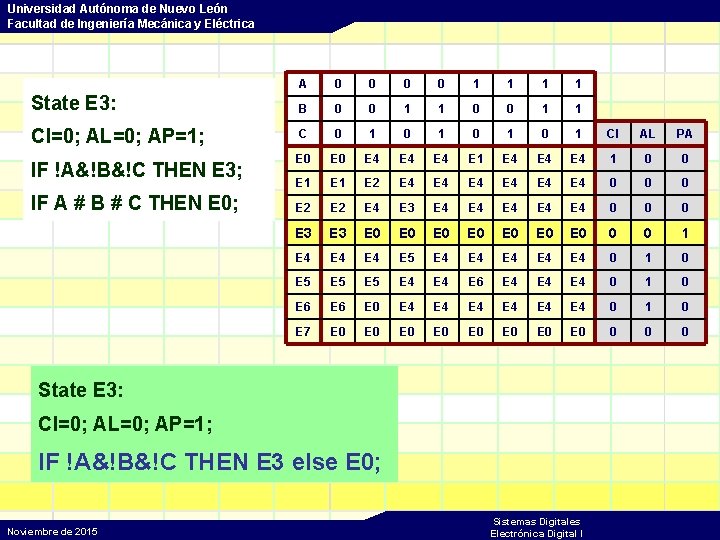

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 4. - describir la secuencia State_diagram UANL A 0 0 1 1 B 0 0 1 1 State E 0: C 0 1 0 1 CI=1; AL=0; AP=0; IF !A&!B&!C THEN E 0; IF !A&!B& C THEN E 4; IF !A& B&!C THEN E 4; IF !A& B& C THEN E 4; CI AL PA E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 IF A&!B&!C THEN E 1; State_diagram UANL IF A&!B& C THEN E 4; State E 0: IF A& B&!C THEN E 4; CI=1; AL=0; AP=0; IF A& B& C THEN E 4; IF !A&!B&!C THEN E 0; ? ELSE IF expression THEN state_expression IF A&!B&!C THEN E 1 Else E 4; ELSE state_expression ; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

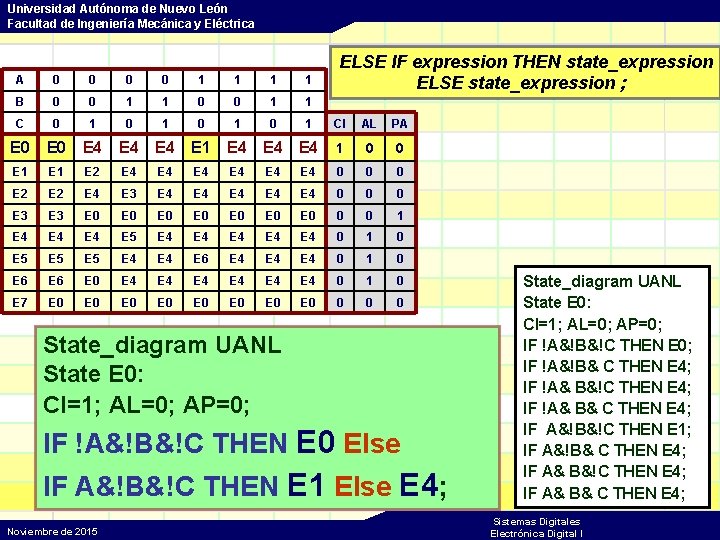

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 E 0 E 4 E 4 E 1 E 1 E 2 E 4 E 4 E 2 E 4 E 3 E 3 E 0 E 4 E 4 E 5 E 6 E 7 ELSE IF expression THEN state_expression ELSE state_expression ; CI AL PA E 4 1 0 0 E 4 E 4 0 0 0 E 0 E 0 E 0 0 0 1 E 5 E 4 E 4 E 4 0 1 0 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 0 E 0 0 State_diagram UANL State E 0: CI=1; AL=0; AP=0; IF !A&!B&!C THEN E 0 Else IF A&!B&!C THEN E 1 Else E 4; Noviembre de 2015 State_diagram UANL State E 0: CI=1; AL=0; AP=0; IF !A&!B&!C THEN E 0; IF !A&!B& C THEN E 4; IF !A& B&!C THEN E 4; IF !A& B& C THEN E 4; IF A&!B&!C THEN E 1; IF A&!B& C THEN E 4; IF A& B&!C THEN E 4; IF A& B& C THEN E 4; Sistemas Digitales Electrónica Digital I

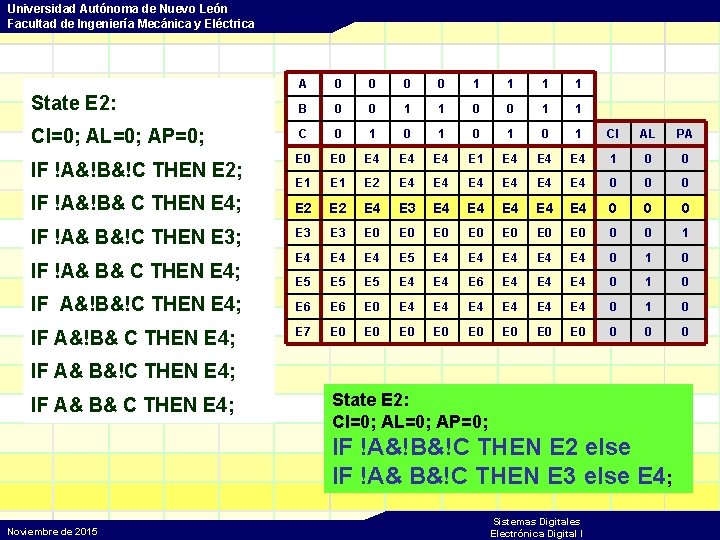

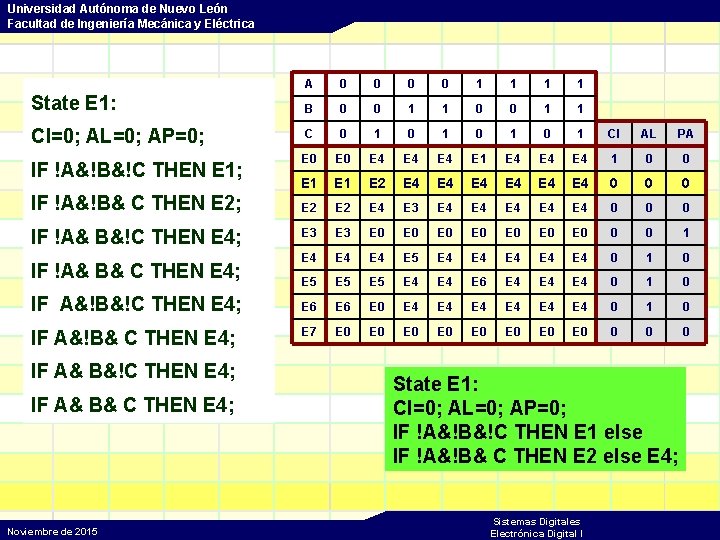

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL PA E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 IF !A&!B& C THEN E 2; E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 IF !A& B&!C THEN E 4; E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 State E 1: CI=0; AL=0; AP=0; IF !A&!B&!C THEN E 1; IF !A& B& C THEN E 4; IF A&!B&!C THEN E 4; IF A&!B& C THEN E 4; IF A& B&!C THEN E 4; IF A& B& C THEN E 4; Noviembre de 2015 State E 1: CI=0; AL=0; AP=0; IF !A&!B&!C THEN E 1 else IF !A&!B& C THEN E 2 else E 4; Sistemas Digitales Electrónica Digital I

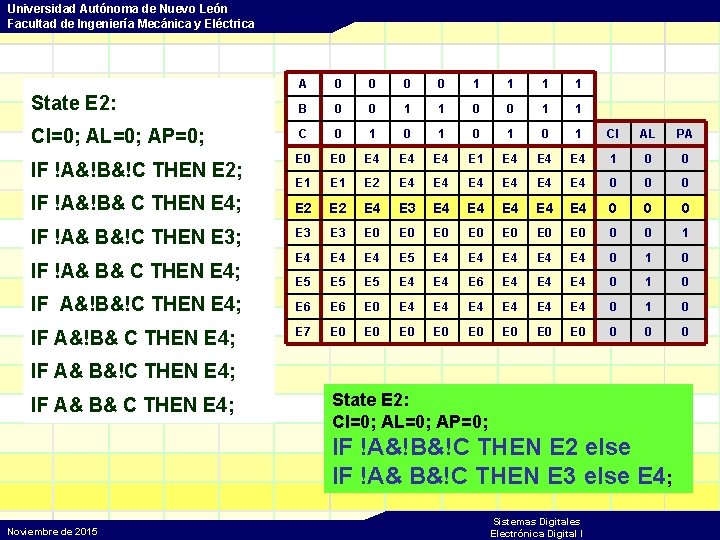

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL PA E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 IF !A&!B& C THEN E 4; E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 IF !A& B&!C THEN E 3; E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 State E 2: CI=0; AL=0; AP=0; IF !A&!B&!C THEN E 2; IF !A& B& C THEN E 4; IF A&!B&!C THEN E 4; IF A&!B& C THEN E 4; IF A& B&!C THEN E 4; IF A& B& C THEN E 4; State E 2: CI=0; AL=0; AP=0; IF !A&!B&!C THEN E 2 else IF !A& B&!C THEN E 3 else E 4; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

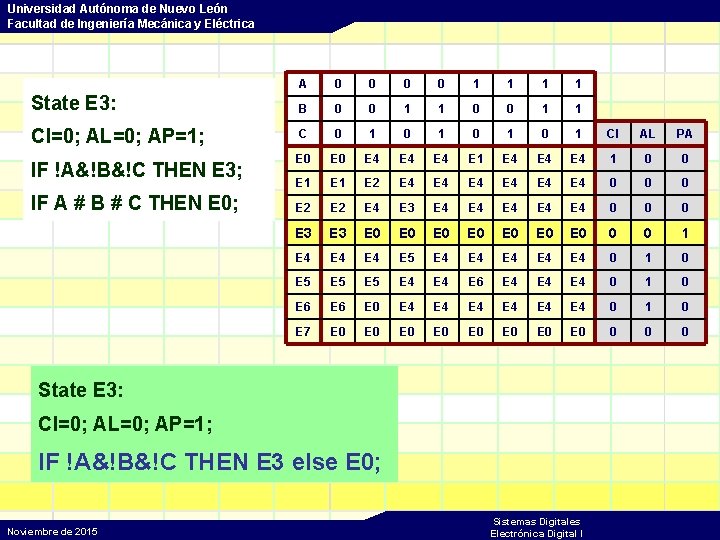

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica State E 3: CI=0; AL=0; AP=1; IF !A&!B&!C THEN E 3; IF A # B # C THEN E 0; A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL PA E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 State E 3: CI=0; AL=0; AP=1; IF !A&!B&!C THEN E 3 else E 0; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

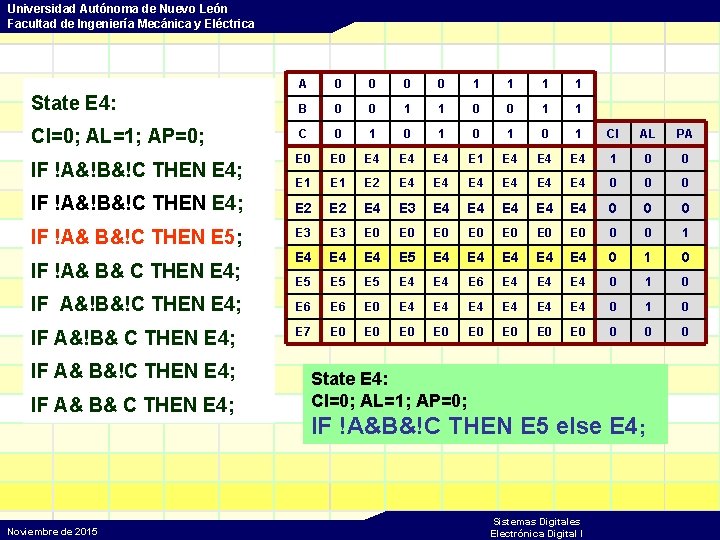

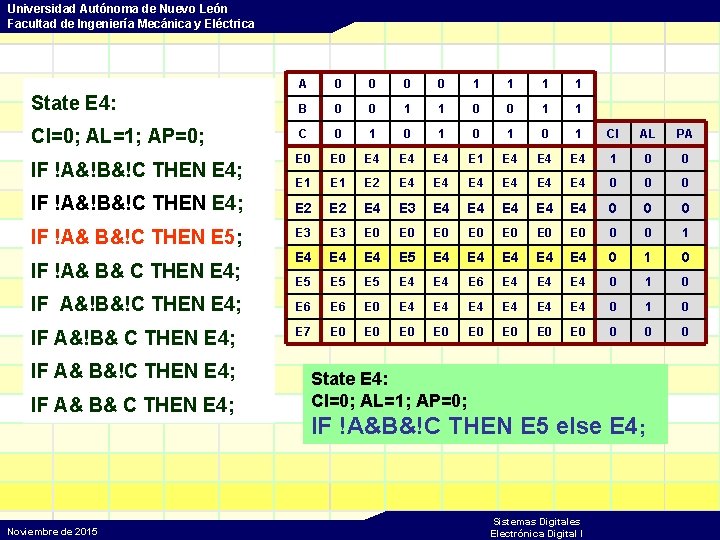

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL PA E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 IF !A&!B&!C THEN E 4; E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 IF !A& B&!C THEN E 5; E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 State E 4: CI=0; AL=1; AP=0; IF !A&!B&!C THEN E 4; IF !A& B& C THEN E 4; IF A&!B&!C THEN E 4; IF A&!B& C THEN E 4; IF A& B&!C THEN E 4; IF A& B& C THEN E 4; Noviembre de 2015 State E 4: CI=0; AL=1; AP=0; IF !A&B&!C THEN E 5 else E 4; Sistemas Digitales Electrónica Digital I

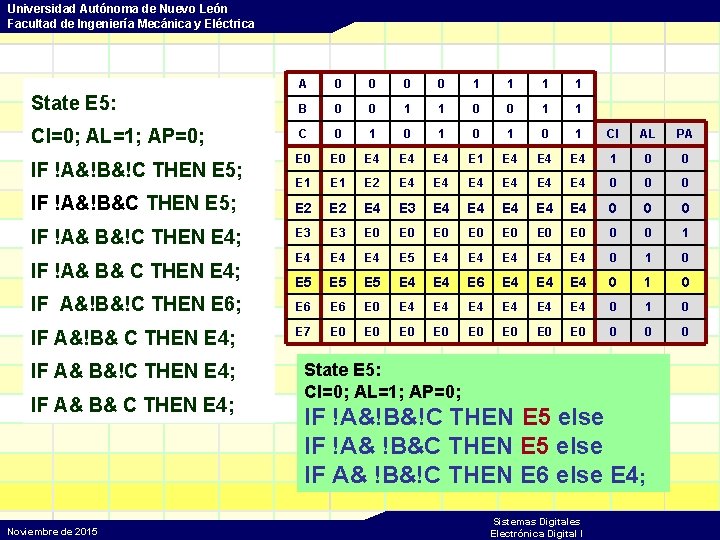

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL PA E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 IF !A&!B&C THEN E 5; E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 IF !A& B&!C THEN E 4; E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 State E 5: CI=0; AL=1; AP=0; IF !A&!B&!C THEN E 5; IF !A& B& C THEN E 4; IF A&!B&!C THEN E 6; IF A&!B& C THEN E 4; IF A& B&!C THEN E 4; IF A& B& C THEN E 4; Noviembre de 2015 State E 5: CI=0; AL=1; AP=0; IF !A&!B&!C THEN E 5 else IF !A& !B&C THEN E 5 else IF A& !B&!C THEN E 6 else E 4; Sistemas Digitales Electrónica Digital I

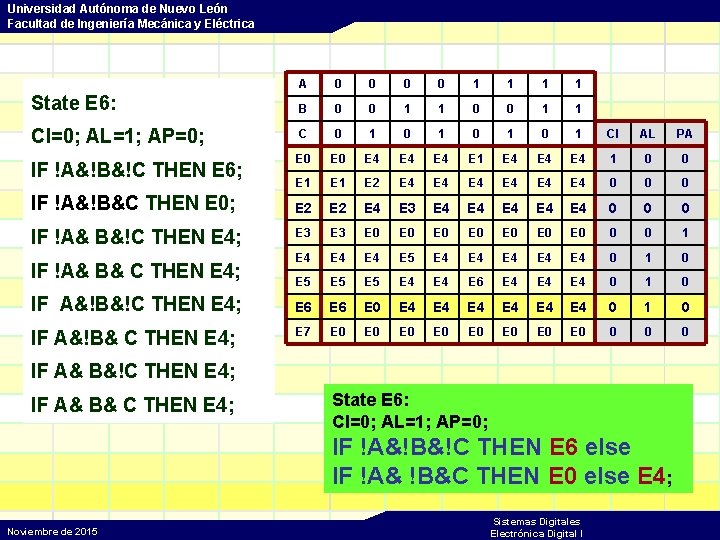

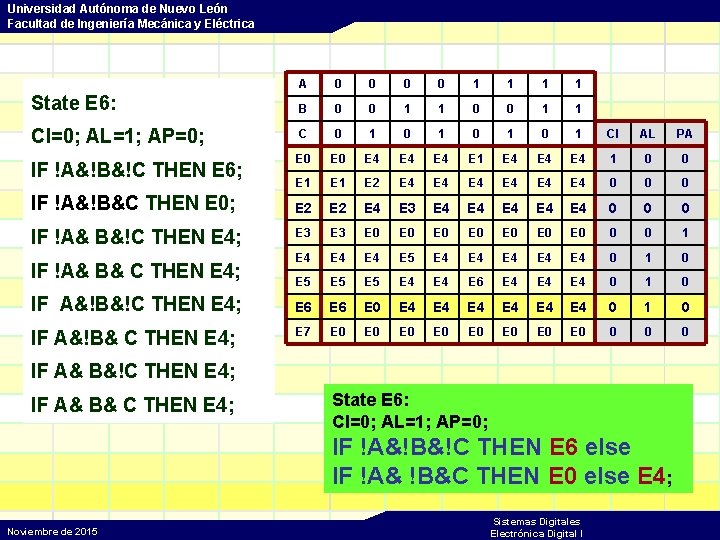

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL PA E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 IF !A&!B&C THEN E 0; E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 IF !A& B&!C THEN E 4; E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 State E 6: CI=0; AL=1; AP=0; IF !A&!B&!C THEN E 6; IF !A& B& C THEN E 4; IF A&!B&!C THEN E 4; IF A&!B& C THEN E 4; IF A& B&!C THEN E 4; IF A& B& C THEN E 4; State E 6: CI=0; AL=1; AP=0; IF !A&!B&!C THEN E 6 else IF !A& !B&C THEN E 0 else E 4; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

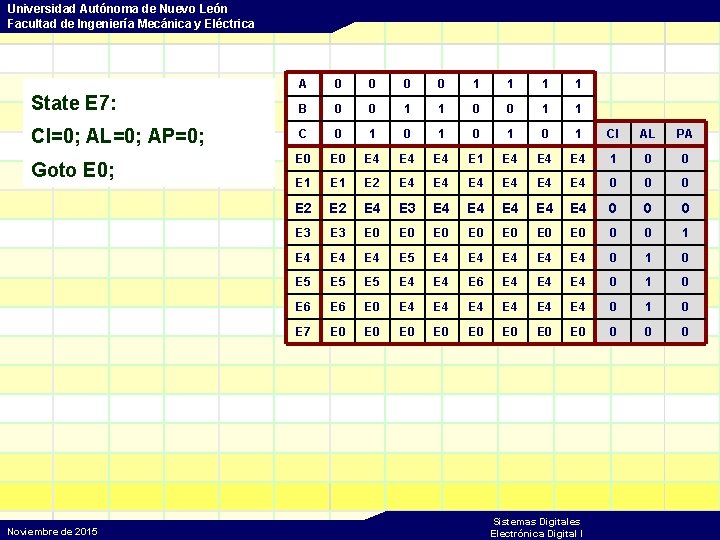

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica State E 7: CI=0; AL=0; AP=0; Goto E 0; Noviembre de 2015 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 CI AL PA E 0 E 4 E 4 E 1 E 4 E 4 1 0 0 E 1 E 2 E 4 E 4 E 4 0 0 0 E 2 E 4 E 3 E 4 E 4 E 4 0 0 0 E 3 E 0 E 0 0 0 1 E 4 E 4 E 5 E 4 E 4 E 4 0 1 0 E 5 E 5 E 4 E 6 E 4 E 4 0 1 0 E 6 E 0 E 4 E 4 E 4 0 1 0 E 7 E 0 E 0 0 0 0 Sistemas Digitales Electrónica Digital I

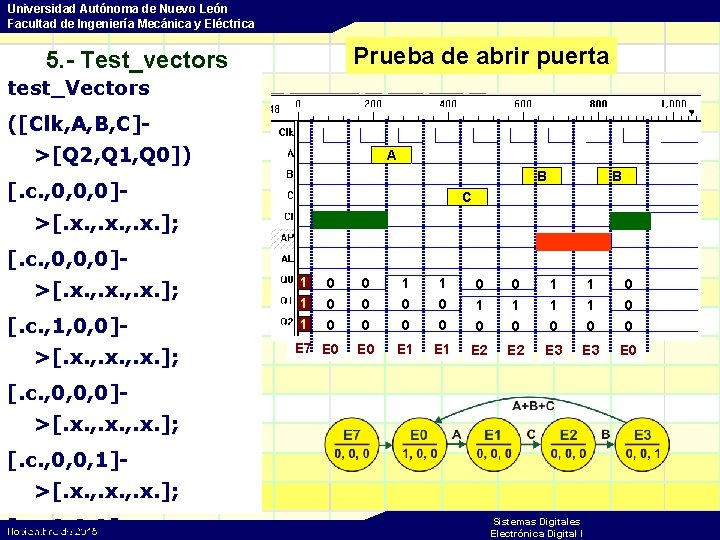

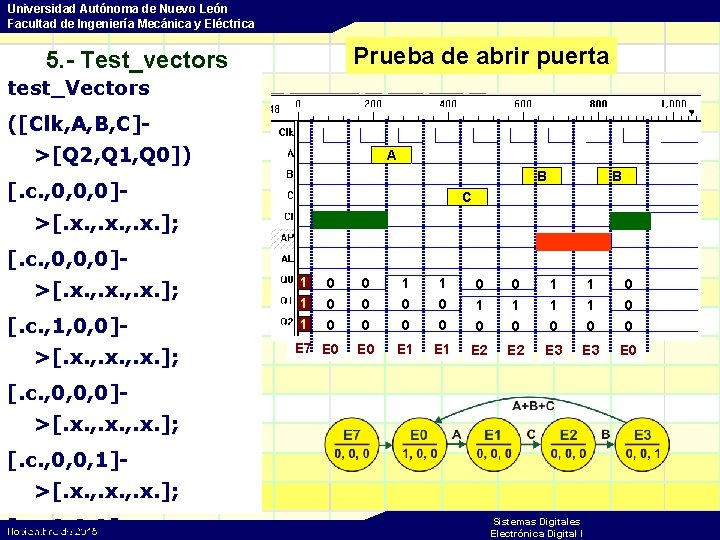

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Prueba de abrir puerta 5. - Test_vectors test_Vectors ([Clk, A, B, C]>[Q 2, Q 1, Q 0]) A B [. c. , 0, 0, 0]- B C >[. x. , . x. ]; [. c. , 0, 0, 0]>[. x. , . x. ]; [. c. , 1, 0, 0]>[. x. , . x. ]; 1 0 0 1 1 0 0 0 0 1 0 1 0 0 0 E 1 E 2 E 3 E 0 E 7 E 0 [. c. , 0, 0, 0]>[. x. , . x. ]; [. c. , 0, 0, 1]>[. x. , . x. ]; [. c. , 0, 0, 0]- Noviembre de 2015 Sistemas Digitales Electrónica Digital I

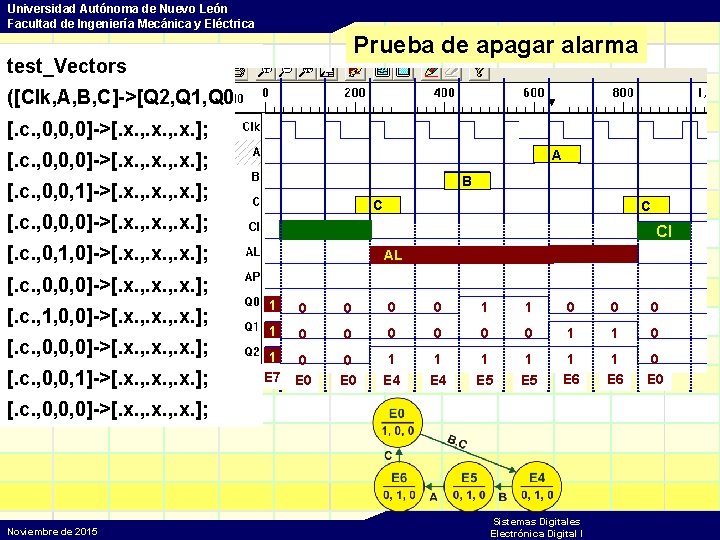

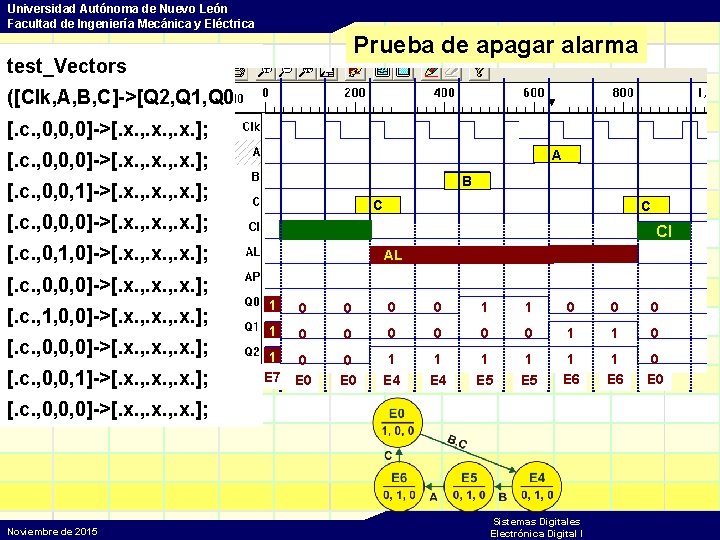

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Prueba de apagar alarma test_Vectors ([Clk, A, B, C]->[Q 2, Q 1, Q 0]) [. c. , 0, 0, 0]->[. x. , . x. ]; A [. c. , 0, 0, 0]->[. x. , . x. ]; B [. c. , 0, 0, 1]->[. x. , . x. ]; C [. c. , 0, 0, 0]->[. x. , . x. ]; C CI [. c. , 0, 1, 0]->[. x. , . x. ]; AL [. c. , 0, 0, 0]->[. x. , . x. ]; [. c. , 1, 0, 0]->[. x. , . x. ]; [. c. , 0, 0, 1]->[. x. , . x. ]; 1 0 0 1 1 0 0 0 1 1 0 0 E 0 1 E 4 1 E 5 1 E 6 0 E 0 1 0 E 7 E 0 [. c. , 0, 0, 0]->[. x. , . x. ]; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

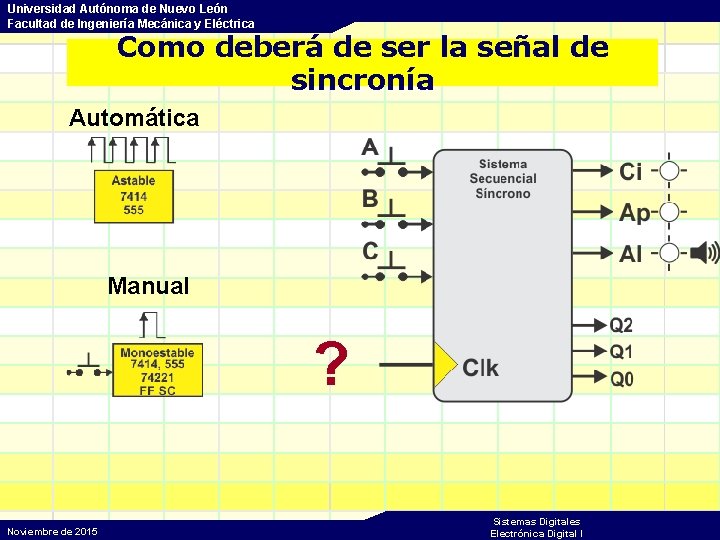

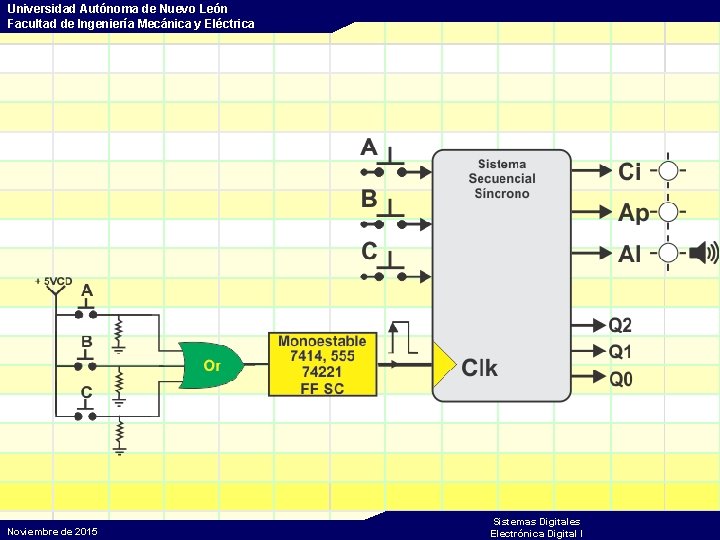

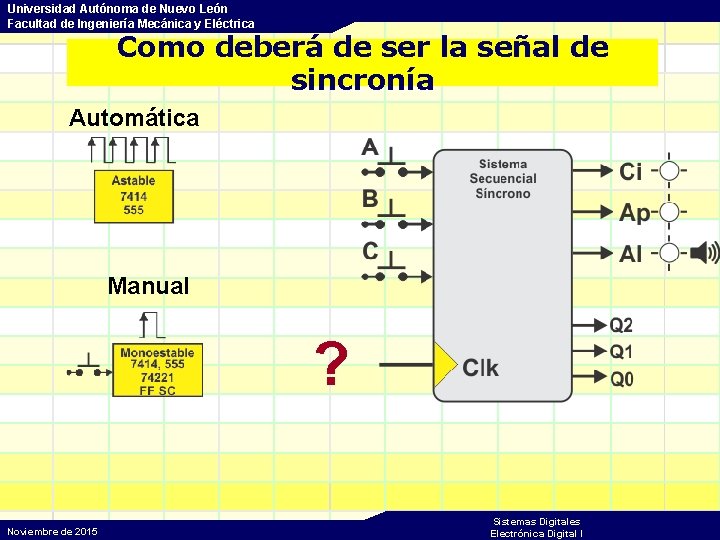

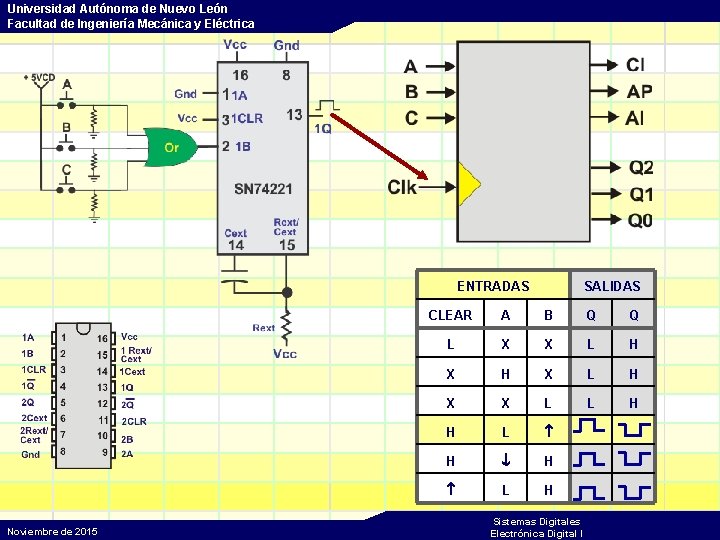

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Como deberá de ser la señal de sincronía Automática Manual ? Noviembre de 2015 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Noviembre de 2015 Sistemas Digitales Electrónica Digital I

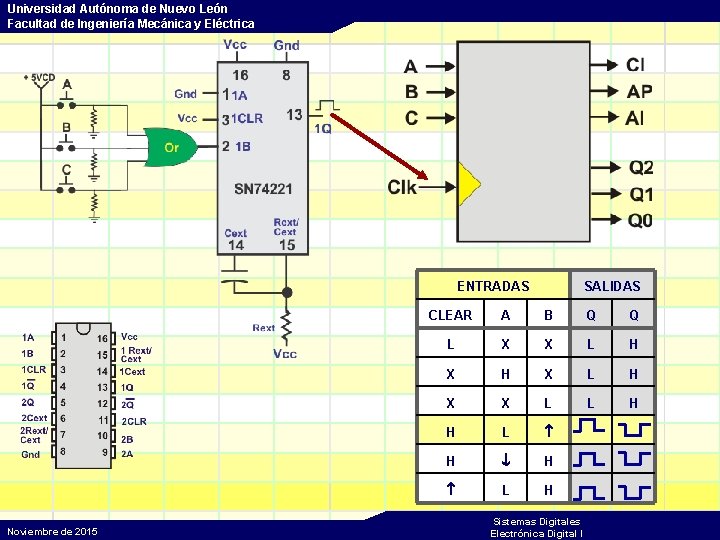

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica ENTRADAS Noviembre de 2015 SALIDAS CLEAR A B Q Q L X X L H X X L L H H L H Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Module alar “Entradas Clk, A, B, C Pin 1. . 4; “Salidas Combinacionales CI, AP, AL Pin 19. . 17 istype ‘com’; “Salidas Registradas Q 2. . Q 0 pin 16. . 14 istype ‘reg’; “sinconizar UANL=[Q 2. . Q 0]; Equations UANL. Clk=Clk; S=A#B#C; Noviembre de 2015 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Metodología de Diseño de sistemas Secuenciales síncronos con el uso de HDL y su implementación en un PLD 1. - Especificar el sistema (Diagrama de transición) 2. - Determinar la cantidad de Flip Flops 3. - Asignar valores a los estados 4. - Diagrama de Bloque (entradas y salidas) 5. - Construir la tabla de estado siguiente 6. - Codificación en ABEL-HDL a) Entradas y salidas b) Sincronización de los Flip Flops c) Asignación de valores a los estados d) Definir la secuencia (state_diagram, Truth_table o equations) e) Test_vectors 7. - Simulación Noviembre de 2015 Sistemas Digitales Electrónica Digital I