Universidad Autnoma de Nuevo Len Facultad de Ingeniera

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica test_vectors ([Clk, AD]->D) Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica test_vectors ([Clk, AD]->D)](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-74.jpg)

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica [7, ^HF]: >[0, Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica [7, ^HF]: >[0,](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-78.jpg)

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Truth_table ([D, U]->[Rck]) Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Truth_table ([D, U]->[Rck])](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-79.jpg)

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truth_table ([D, U]->[Rck]) Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truth_table ([D, U]->[Rck])](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-82.jpg)

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truth_table ([D, U]: Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truth_table ([D, U]:](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-84.jpg)

- Slides: 103

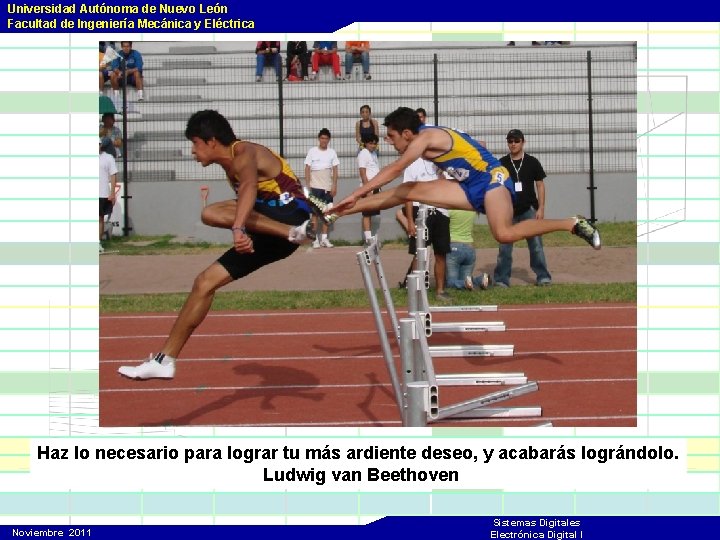

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Haz lo necesario para lograr tu más ardiente deseo, y acabarás lográndolo. Ludwig van Beethoven Noviembre 2011 Sistemas Digitales Electrónica Digital I

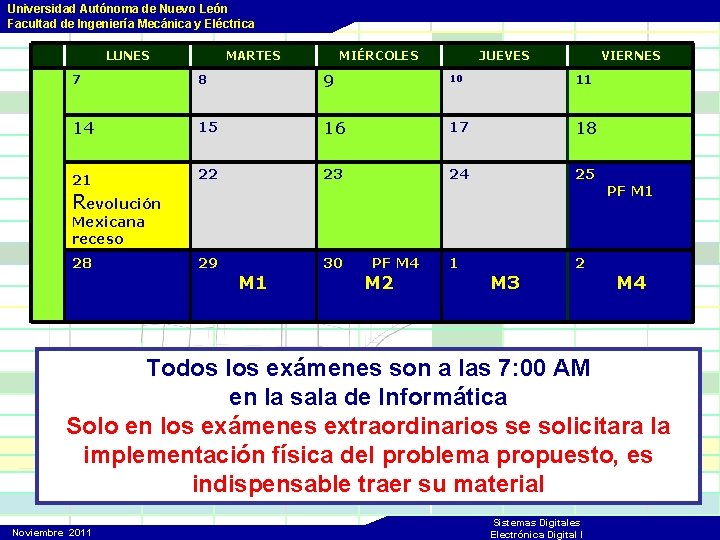

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica LUNES MARTES MIÉRCOLES JUEVES VIERNES 7 8 9 10 11 14 15 16 17 18 21 22 23 24 25 29 30 1 2 Revolución PF M 1 Mexicana receso 28 M 1 PF M 4 M 2 M 3 M 4 Todos los exámenes son a las 7: 00 AM en la sala de Informática Solo en los exámenes extraordinarios se solicitara la implementación física del problema propuesto, es indispensable traer su material Noviembre 2011 Sistemas Digitales Electrónica Digital I

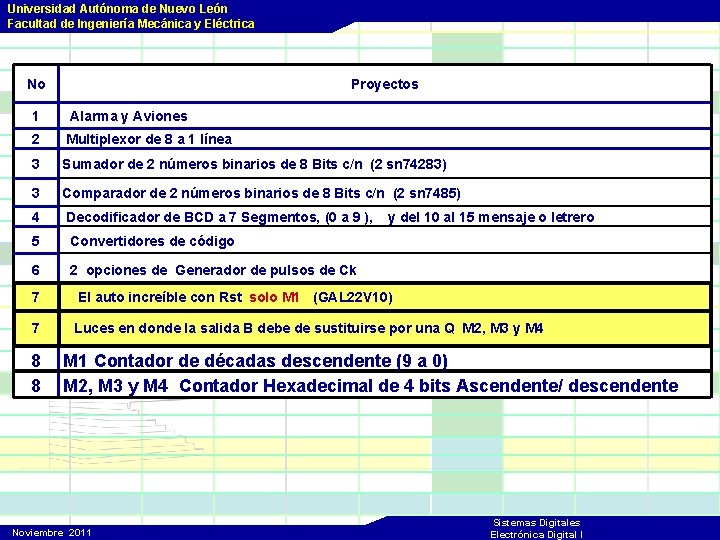

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica No Proyectos 1 Alarma y Aviones 2 Multiplexor de 8 a 1 línea 3 Sumador de 2 números binarios de 8 Bits c/n (2 sn 74283) 3 Comparador de 2 números binarios de 8 Bits c/n (2 sn 7485) 4 Decodificador de BCD a 7 Segmentos, (0 a 9 ), 5 Convertidores de código 6 2 opciones de Generador de pulsos de Ck y del 10 al 15 mensaje o letrero 7 El auto increíble con Rst solo M 1 (GAL 22 V 10) 7 Luces en donde la salida B debe de sustituirse por una Q M 2, M 3 y M 4 8 8 M 1 Contador de décadas descendente (9 a 0) M 2, M 3 y M 4 Contador Hexadecimal de 4 bits Ascendente/ descendente Noviembre 2011 Sistemas Digitales Electrónica Digital I

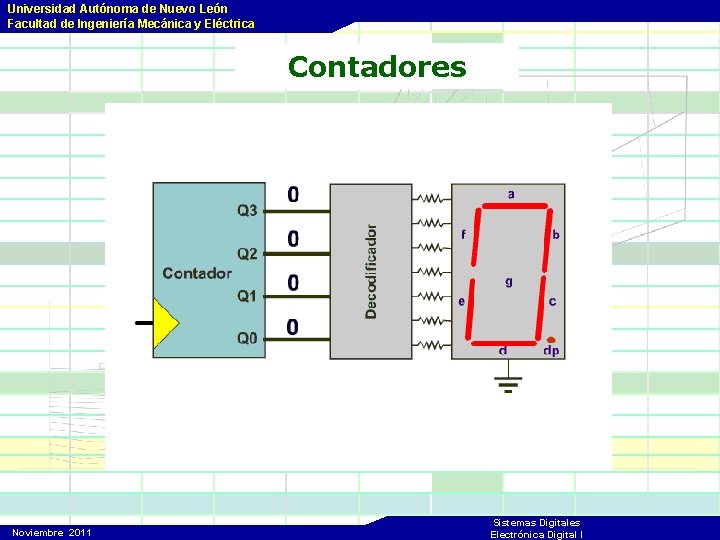

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contadores Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador (counter en inglés) Es un circuito digital secuencial construido a partir de Flip Flops y compuertas lógicas capaz de: • Realizar el cómputo (conteo) de los pulsos que recibe en la entrada de sincronía (Clk). • Actuar como divisor de frecuencia. Habitualmente, el conteo se realiza en un código binario, que con frecuencia será el binario natural o el BCD natural (contador de décadas). Los contadores se pueden clasificar en: • Binarios (n bit´s) • Décadas (0 a 9) • Especiales Pueden ser ascendentes (UP) y/o descendentes (DOWN) Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Bit’s Conteo Ascendente Conteo Descendente 1 0 a 1 1 a 0 Los contadores binarios pueden 2 0 a 3 3 a 0 ser clasificados por: 3 0 a 7 7 a 0 1. - El número de bit’s 4 0 a 15 15 a 0 5 0 a 31 31 a 0 6 0 a 63 63 a 0 7 0 a 127 a 0 8 0 a 255 a 0 9 0 a 511 a 0 Contadores Binarios 2. - El número máximo de estados (Módulo del contador) 10 0 a 1023 a 0 Noviembre 2011 Sistemas Digitales Electrónica Digital I

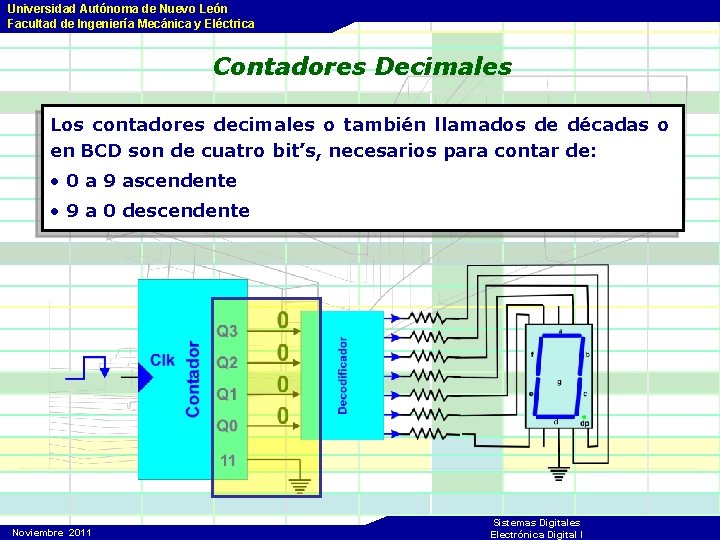

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contadores Decimales Los contadores decimales o también llamados de décadas o en BCD son de cuatro bit’s, necesarios para contar de: • 0 a 9 ascendente • 9 a 0 descendente Noviembre 2011 Sistemas Digitales Electrónica Digital I

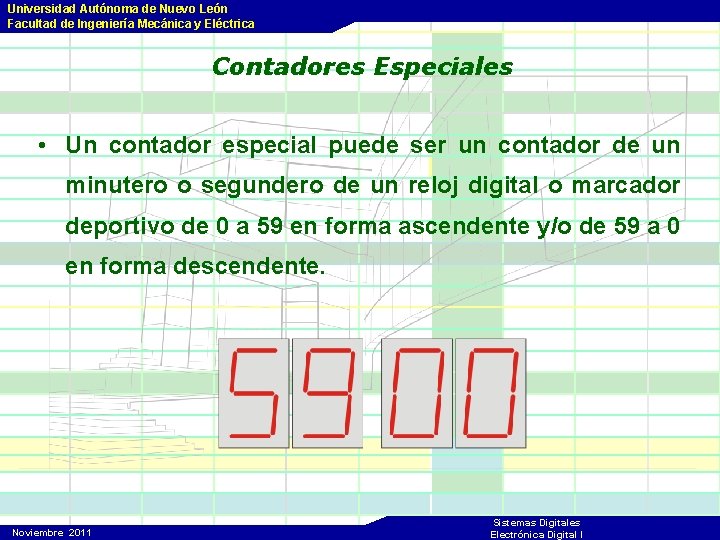

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contadores Especiales • Un contador especial puede ser un contador de un minutero o segundero de un reloj digital o marcador deportivo de 0 a 59 en forma ascendente y/o de 59 a 0 en forma descendente. Noviembre 2011 Sistemas Digitales Electrónica Digital I

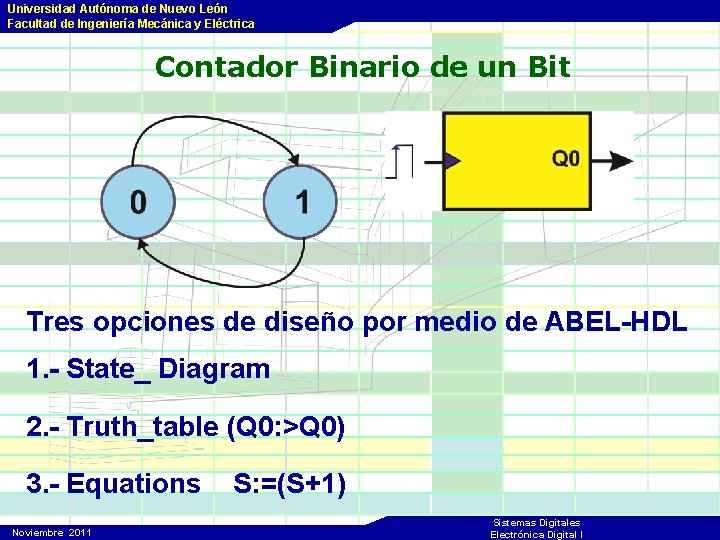

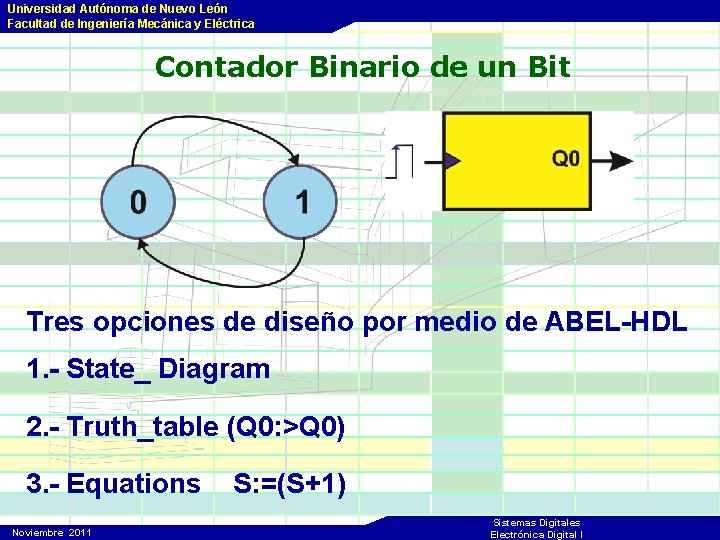

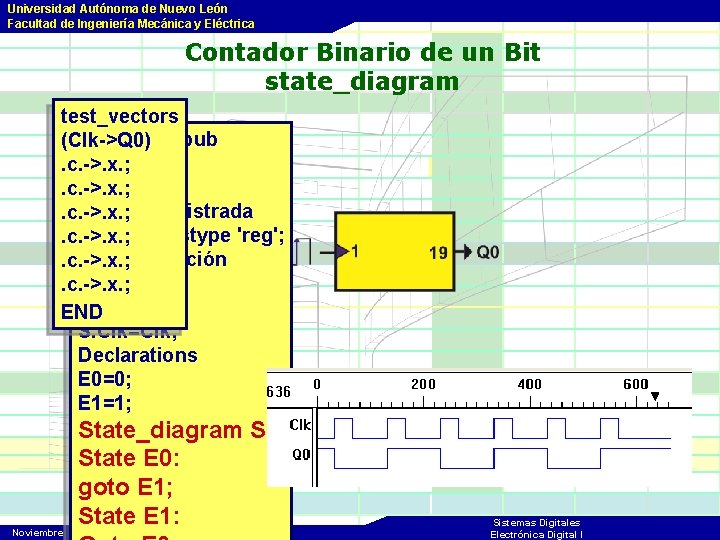

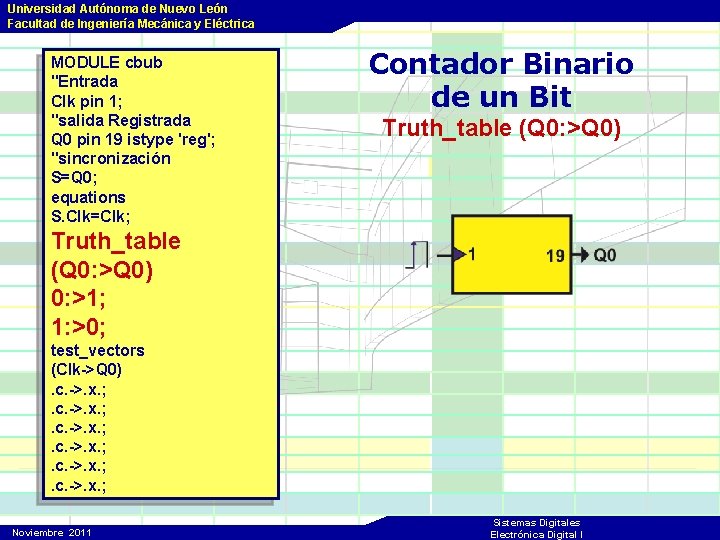

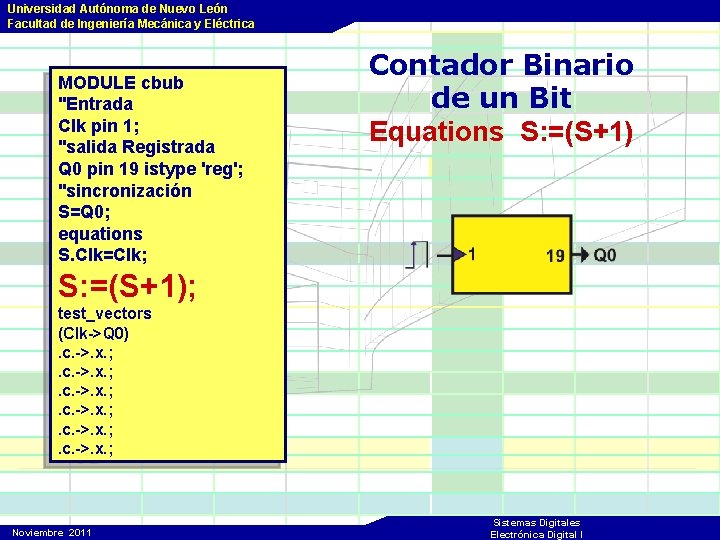

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario de un Bit Tres opciones de diseño por medio de ABEL-HDL 1. - State_ Diagram 2. - Truth_table (Q 0: >Q 0) 3. - Equations Noviembre 2011 S: =(S+1) Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario de un Bit state_diagram test_vectors MODULE cbub (Clk->Q 0) "Entrada. c. ->. x. ; Clk pin 1; . c. ->. x. ; "salida Registrada. c. ->. x. ; Q 0 pin 19 istype 'reg'; . c. ->. x. ; "sincronización. c. ->. x. ; S=Q 0; . c. ->. x. ; equations END S. Clk=Clk; Declarations E 0=0; E 1=1; State_diagram S State E 0: goto E 1; State E 1: Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE cbub "Entrada Clk pin 1; "salida Registrada Q 0 pin 19 istype 'reg'; "sincronización S=Q 0; equations S. Clk=Clk; Contador Binario de un Bit Truth_table (Q 0: >Q 0) 0: >1; 1: >0; test_vectors (Clk->Q 0). c. ->. x. ; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE cbub "Entrada Clk pin 1; "salida Registrada Q 0 pin 19 istype 'reg'; "sincronización S=Q 0; equations S. Clk=Clk; Contador Binario de un Bit Equations S: =(S+1); test_vectors (Clk->Q 0). c. ->. x. ; Noviembre 2011 Sistemas Digitales Electrónica Digital I

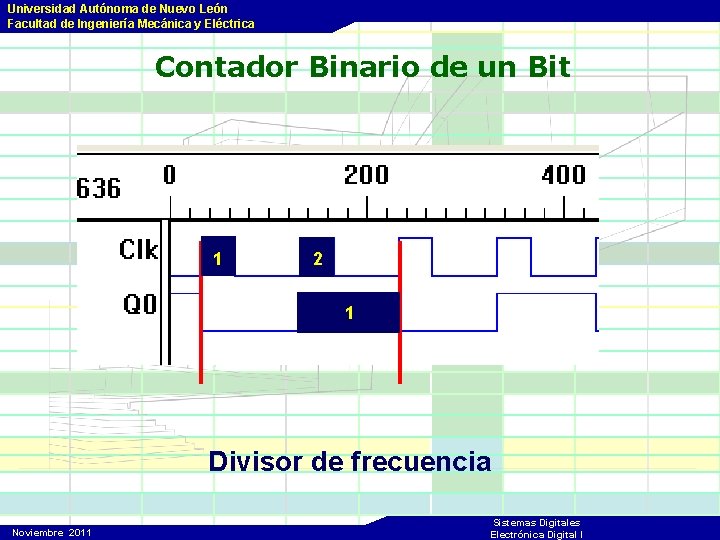

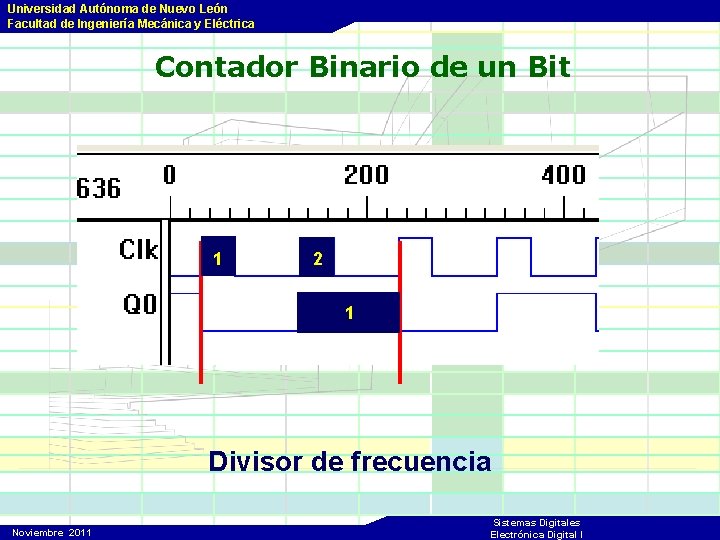

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario de un Bit 1 2 1 Divisor de frecuencia Noviembre 2011 Sistemas Digitales Electrónica Digital I

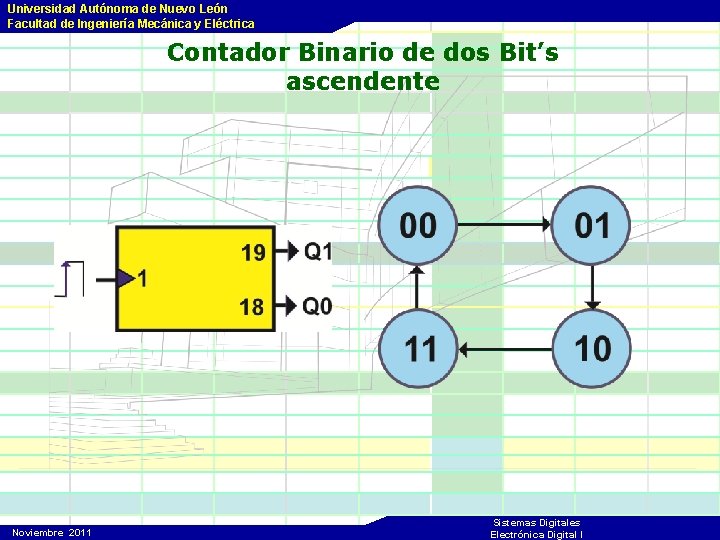

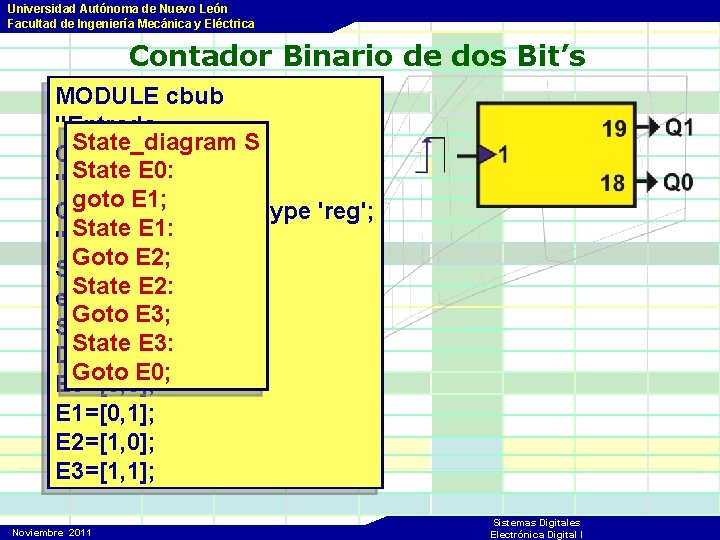

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario de dos Bit’s ascendente Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario de dos Bit’s MODULE cbub "Entrada State_diagram S Clk pin 1; State E 0: "salida Registrada goto E 1; Q 1, Q 0 pin 19, 18 istype 'reg'; State E 1: "sincronización Goto E 2; S=[Q 1, Q 0]; State E 2: equations Goto E 3; S. Clk=Clk; State E 3: Declarations Goto E 0; E 0=[0, 0]; E 1=[0, 1]; E 2=[1, 0]; E 3=[1, 1]; Noviembre 2011 Sistemas Digitales Electrónica Digital I

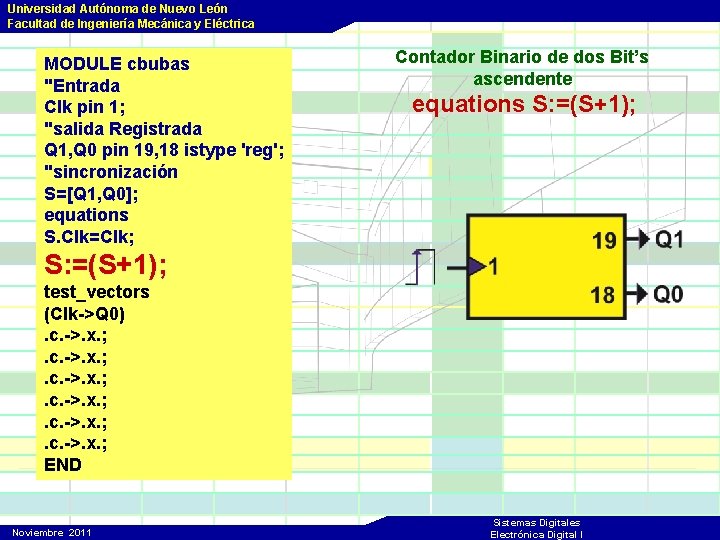

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE cbubas "Entrada Clk pin 1; "salida Registrada Q 1, Q 0 pin 19, 18 istype 'reg'; "sincronización S=[Q 1, Q 0]; equations S. Clk=Clk; Contador Binario de dos Bit’s ascendente Truth_Table ([Q 1, Q 0] : >[Q 1, Q 0]) Truth_Table ([Q 1, Q 0] (S: >S) : >[Q 1, Q 0]) [0, 0]: >[0, 1]; 0: >1; [0, 1]: >[1, 0]; 1: >2; [1, 0]: >[1, 1]; 2: >3; [1, 1]: >[0, 0]; 3: >0; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE cbubas "Entrada Clk pin 1; "salida Registrada Q 1, Q 0 pin 19, 18 istype 'reg'; "sincronización S=[Q 1, Q 0]; equations S. Clk=Clk; Contador Binario de dos Bit’s ascendente equations S: =(S+1); test_vectors (Clk->Q 0). c. ->. x. ; END Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica test_vectors (Clk->Q 0). c. ->. x. ; END Noviembre 2011 Contador Binario de dos Bit’s ascendente 1 0 0 1 1 1 0 1 0 1 3 0 1 2 3 Sistemas Digitales Electrónica Digital I

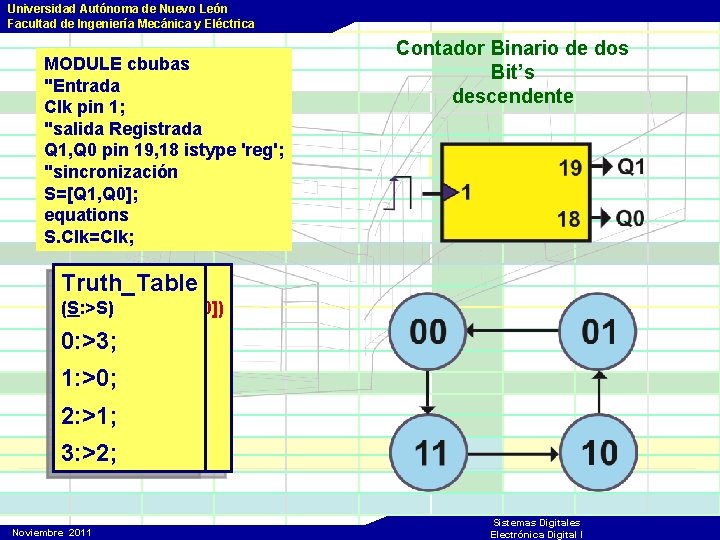

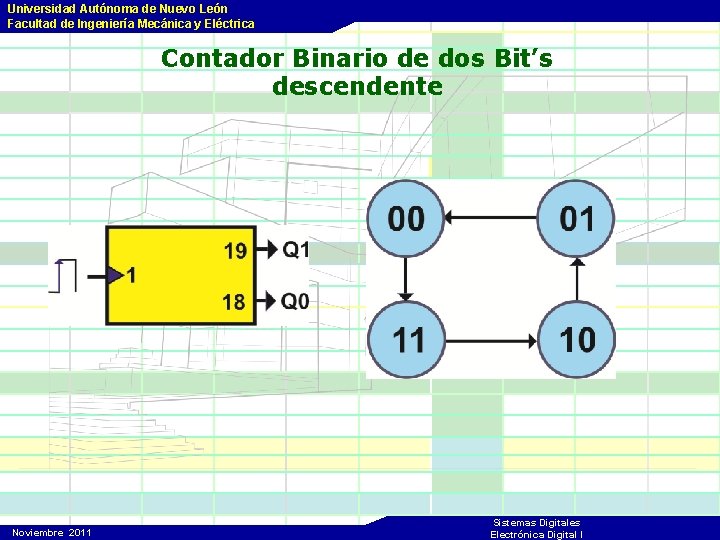

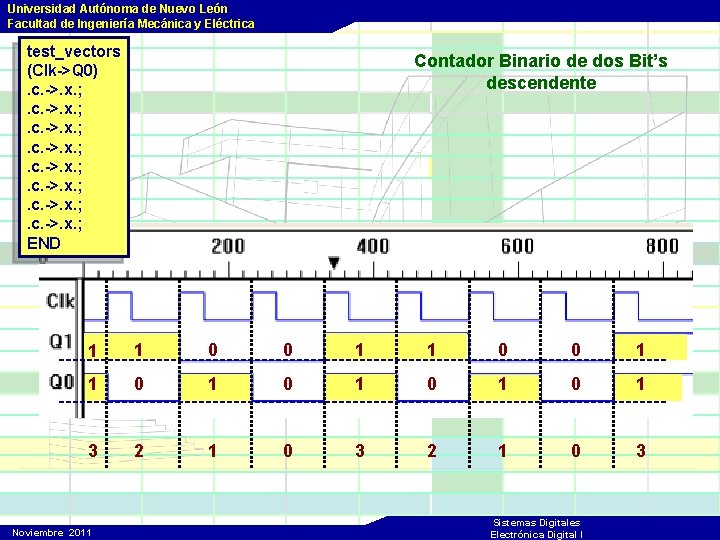

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario de dos Bit’s descendente Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario de dos Bit’s descendente State_diagram S State E 0: goto E 3; State E 1: Goto E 0; State E 2: Goto E 1; State E 3: Goto E 2; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE cbubas "Entrada Clk pin 1; "salida Registrada Q 1, Q 0 pin 19, 18 istype 'reg'; "sincronización S=[Q 1, Q 0]; equations S. Clk=Clk; Contador Binario de dos Bit’s descendente Truth_Table ([Q 1, Q 0] (S: >S) : >[Q 1, Q 0]) [0, 0]: >[1, 1]; 0: >3; [0, 1]: >[0, 0]; 1: >0; [1, 0]: >[0, 1]; 2: >1; [1, 1]: >[1, 0]; 3: >2; Noviembre 2011 Sistemas Digitales Electrónica Digital I

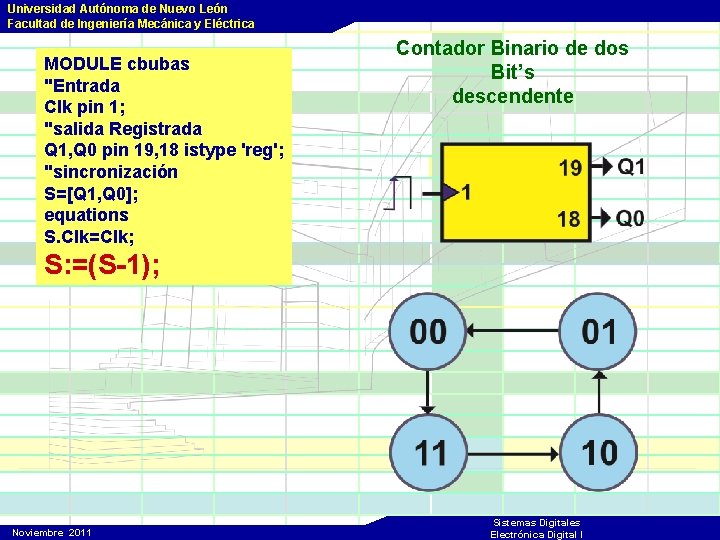

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE cbubas "Entrada Clk pin 1; "salida Registrada Q 1, Q 0 pin 19, 18 istype 'reg'; "sincronización S=[Q 1, Q 0]; equations S. Clk=Clk; Contador Binario de dos Bit’s descendente S: =(S-1); Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica test_vectors (Clk->Q 0). c. ->. x. ; END Contador Binario de dos Bit’s descendente 1 1 0 0 1 1 0 1 0 1 3 2 1 0 3 Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario ascendente de 0 a 15 (4 Bit´s) Noviembre 2011 Sistemas Digitales Electrónica Digital I

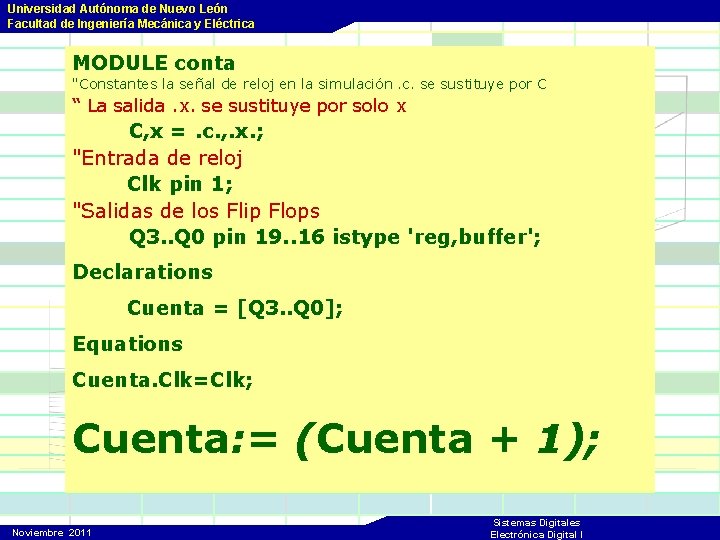

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE conta "Constantes la señal de reloj en la simulación. c. se sustituye por C “ La salida. x. se sustituye por solo x C, x =. c. , . x. ; "Entrada de reloj Clk pin 1; "Salidas de los Flip Flops Q 3. . Q 0 pin 19. . 16 istype 'reg, buffer'; Declarations Cuenta = [Q 3. . Q 0]; Equations Cuenta. Clk=Clk; Cuenta: = (Cuenta + 1); Noviembre 2011 Sistemas Digitales Electrónica Digital I

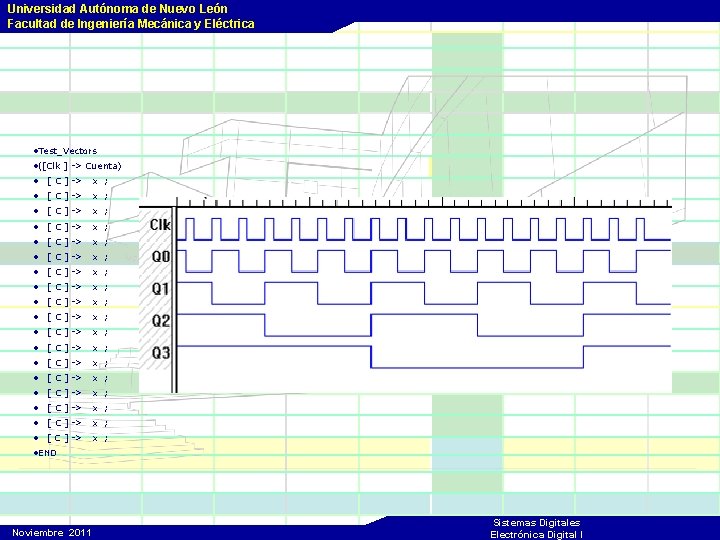

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica • Test_Vectors • ([Clk ] -> Cuenta) • [ C ] -> x ; • [ C ] -> x ; • [ C ] -> x ; • [ C ] -> x ; • [ C ] -> x ; • END Noviembre 2011 Sistemas Digitales Electrónica Digital I

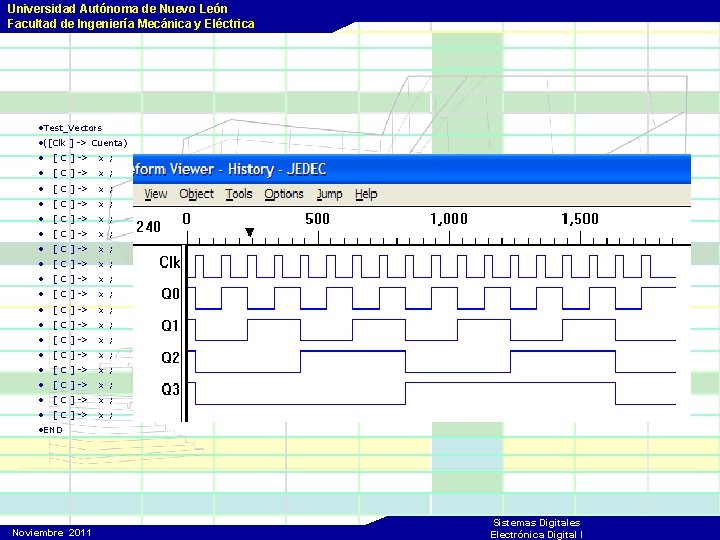

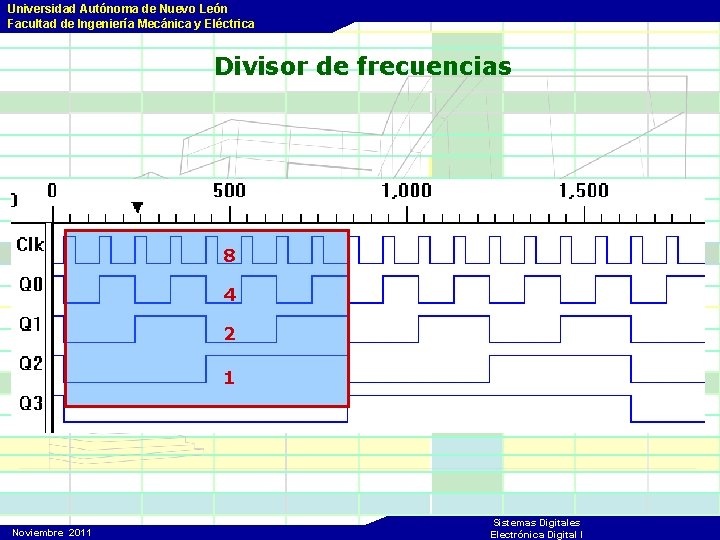

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Divisor de frecuencias 8 4 2 1 Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Divisor de frecuencias 16 Noviembre 2011 8 Clk/2 4 Clk/4 2 Clk/8 1 Clk/16 Sistemas Digitales Electrónica Digital I

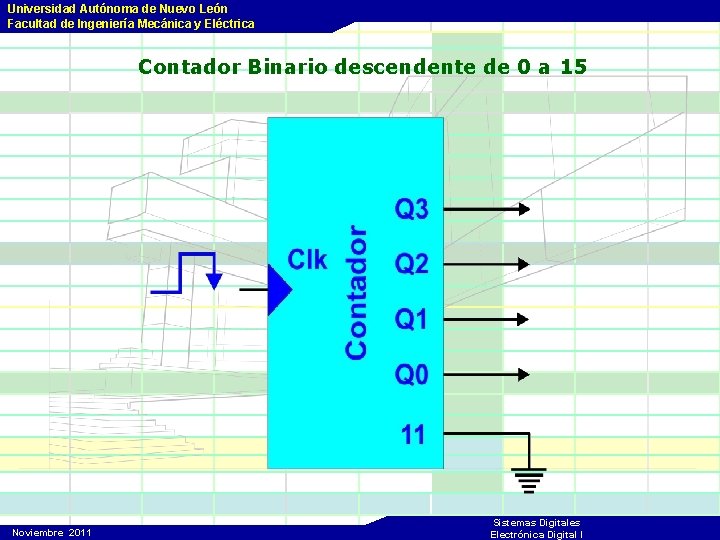

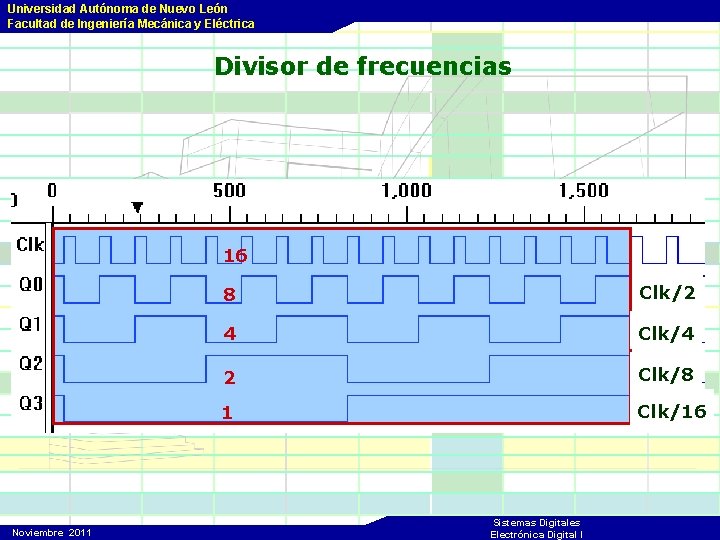

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador Binario descendente de 0 a 15 Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE conta "Constantes la señal de reloj en la simulación. c. se sustituye por C “ La salida. x. se sustituye por solo x C, x =. c. , . x. ; "Entrada de reloj Clk pin 1; "Salidas de los Flip Flops Q 3. . Q 0 pin 19. . 16 istype 'reg'; Declarations Cuenta = [Q 3. . Q 0]; Equations Cuenta. Clk=Clk; Cuenta: = (Cuenta - 1); Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica • Test_Vectors • ([Clk ] -> Cuenta) • [ C ] -> x ; • [ C ] -> x ; • [ C ] -> x ; • [ C ] -> x ; • [ C ] -> x ; • END Noviembre 2011 Sistemas Digitales Electrónica Digital I

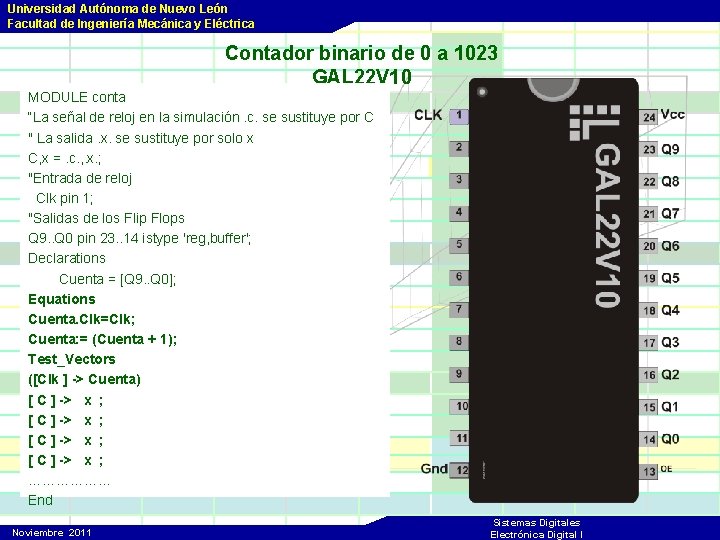

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador binario de 0 a 1023 GAL 22 V 10 MODULE conta “La señal de reloj en la simulación. c. se sustituye por C " La salida. x. se sustituye por solo x C, x =. c. , . x. ; "Entrada de reloj Clk pin 1; "Salidas de los Flip Flops Q 9. . Q 0 pin 23. . 14 istype 'reg, buffer'; Declarations Cuenta = [Q 9. . Q 0]; Equations Cuenta. Clk=Clk; Cuenta: = (Cuenta + 1); Test_Vectors ([Clk ] -> Cuenta) [ C ] -> x ; ……………… End Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Noviembre 2011 Sistemas Digitales Electrónica Digital I

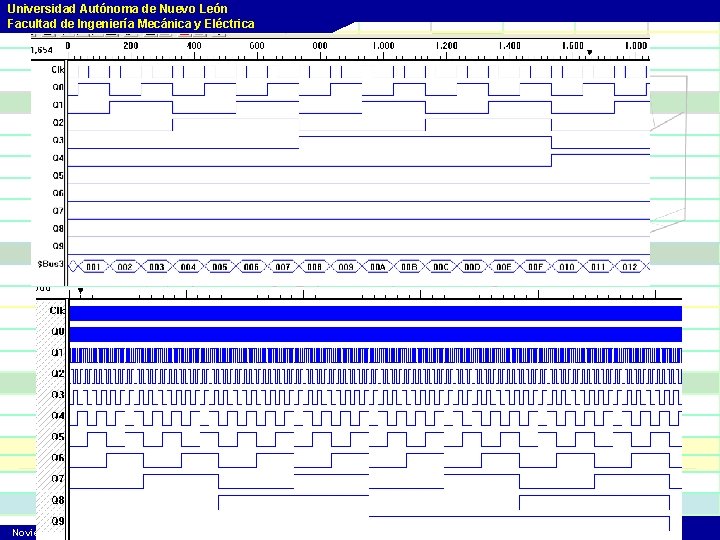

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador binario de dos bit’s Que contenga una entrada X de modo que: a) Si X=0 se ascendente b) Si X=1 sea descendente Noviembre 2011 Sistemas Digitales Electrónica Digital I

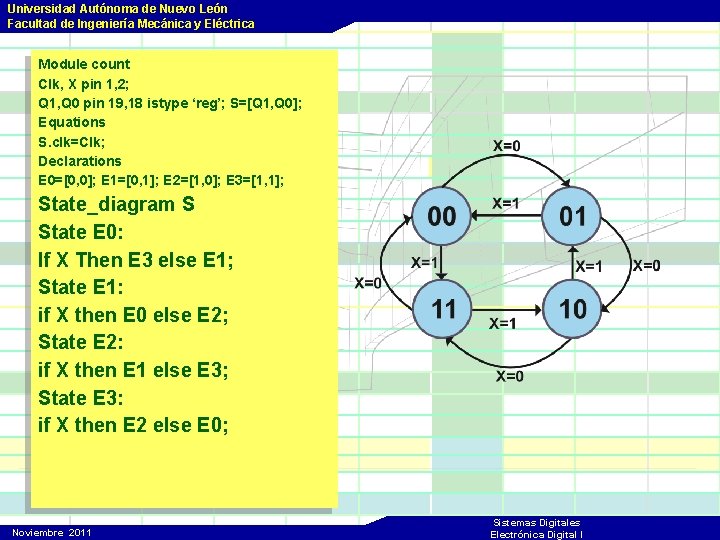

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Module count Clk, X pin 1, 2; Q 1, Q 0 pin 19, 18 istype ‘reg’; S=[Q 1, Q 0]; Equations S. clk=Clk; Declarations E 0=[0, 0]; E 1=[0, 1]; E 2=[1, 0]; E 3=[1, 1]; State_diagram S State E 0: If X Then E 3 else E 1; State E 1: if X then E 0 else E 2; State E 2: if X then E 1 else E 3; State E 3: if X then E 2 else E 0; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Module count Clk, X pin 1, 2; Q 1, Q 0 pin 19, 18 istype ‘reg’; S=[Q 1, Q 0]; Equations S. clk=Clk; Truth_table ([X, Q 1, Q 0] : >[Q 1, Q 0]) [0, 0, 0]: >[0, 1]; [0, 0, 1]: >[1, 0]; [0, 1, 0]: >[1, 1]; [0, 1, 1]: >[0, 0]; [1, 0, 0]: >[1, 1]; [1, 0, 1]: >[0, 0]; [1, 1, 0]: >[0, 1]; [1, 1, 1]: >[1, 0]; Truth_table ([X, S] : >[S]) [0, 0]: >[1]; [0, 1]: >[2]; [0, 2]: >[3]; [0, 3]: >[0]; [1, 0]: >[3]; [1, 1]: >[0]; [1, 2]: >[1]; [1, 3]: >[2]; End Noviembre 2011 Sistemas Digitales Electrónica Digital I

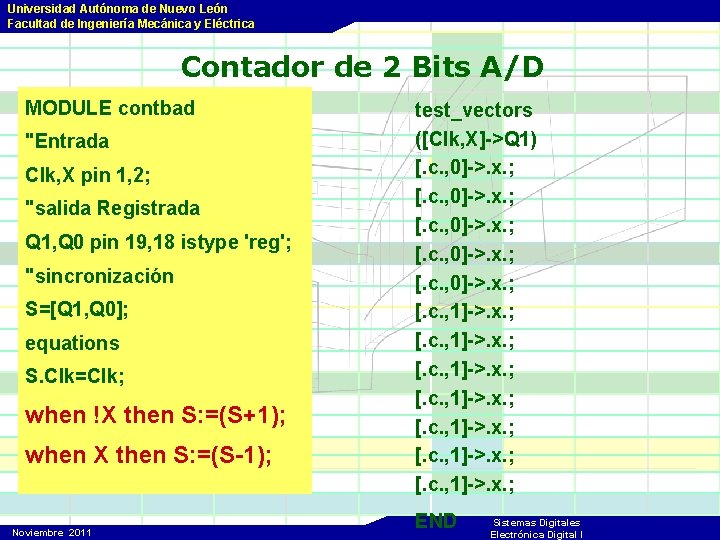

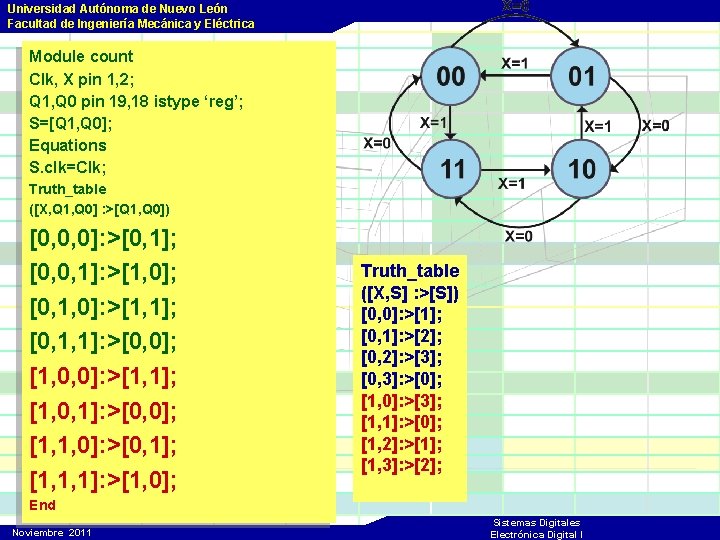

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 2 Bits A/D MODULE contbad "Entrada Clk, X pin 1, 2; "salida Registrada Q 1, Q 0 pin 19, 18 istype 'reg'; "sincronización S=[Q 1, Q 0]; equations S. Clk=Clk; when !X then S: =(S+1); when X then S: =(S-1); Noviembre 2011 test_vectors ([Clk, X]->Q 1) [. c. , 0]->. x. ; [. c. , 1]->. x. ; END Sistemas Digitales Electrónica Digital I

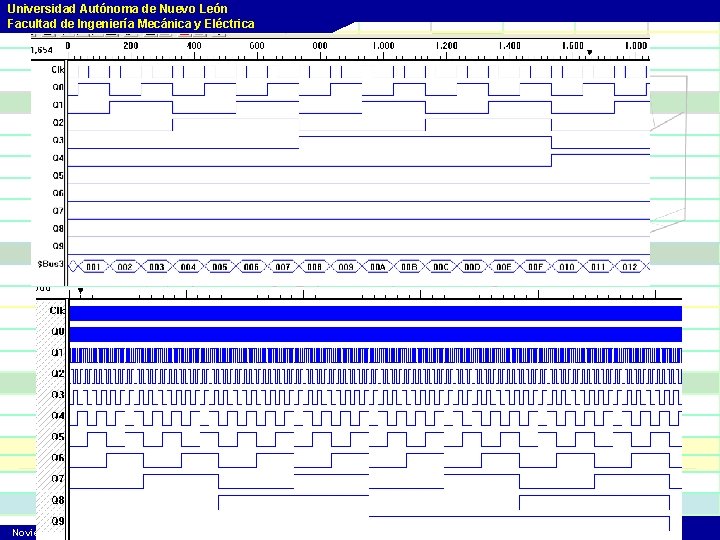

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Simulación test_vectors ([Clk, X]->Q 0) [. c. , 0]->. x. ; [. c. , 1]->. x. ; [. c. , 0]->. x. ; Noviembre 2011 Ascendente Descendente Sistemas Digitales Electrónica Digital I

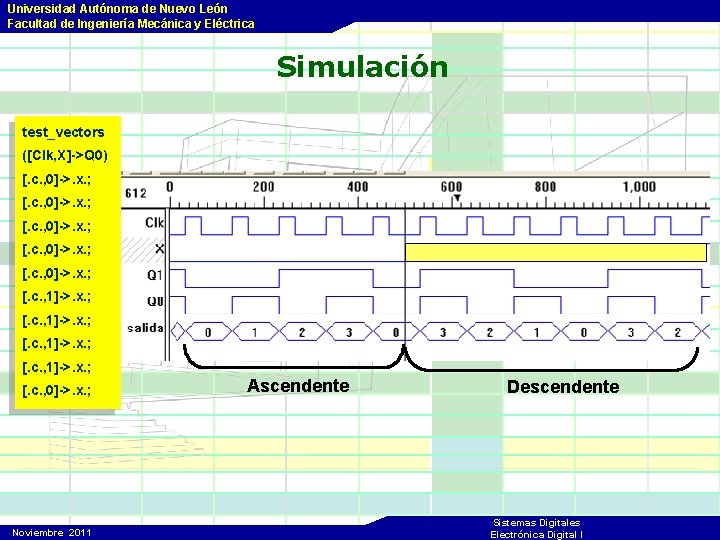

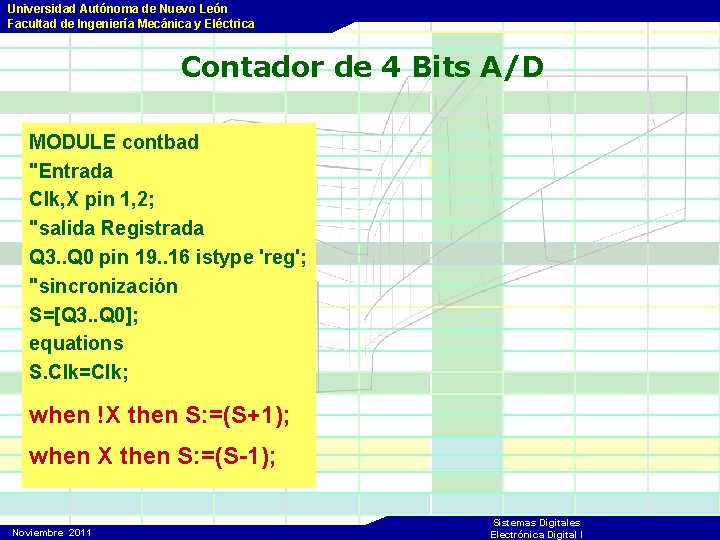

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 4 Bits A/D MODULE contbad "Entrada Clk, X pin 1, 2; "salida Registrada Q 3. . Q 0 pin 19. . 16 istype 'reg'; "sincronización S=[Q 3. . Q 0]; equations S. Clk=Clk; when !X then S: =(S+1); when X then S: =(S-1); Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 4 Bits A/D Noviembre 2011 Sistemas Digitales Electrónica Digital I

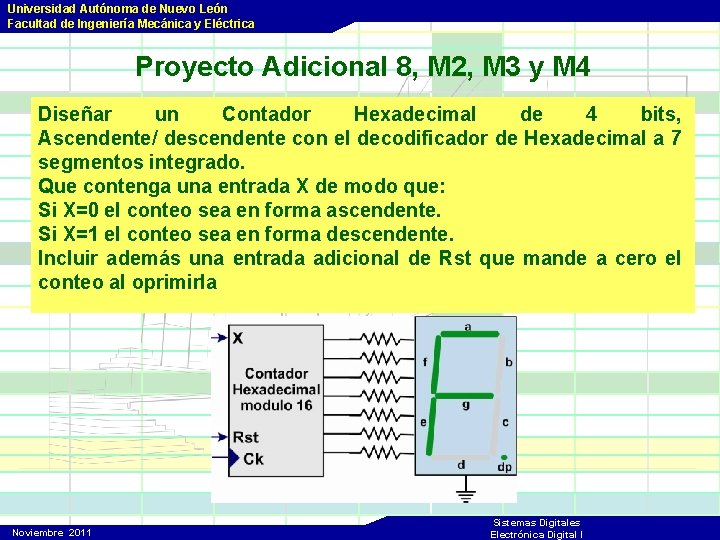

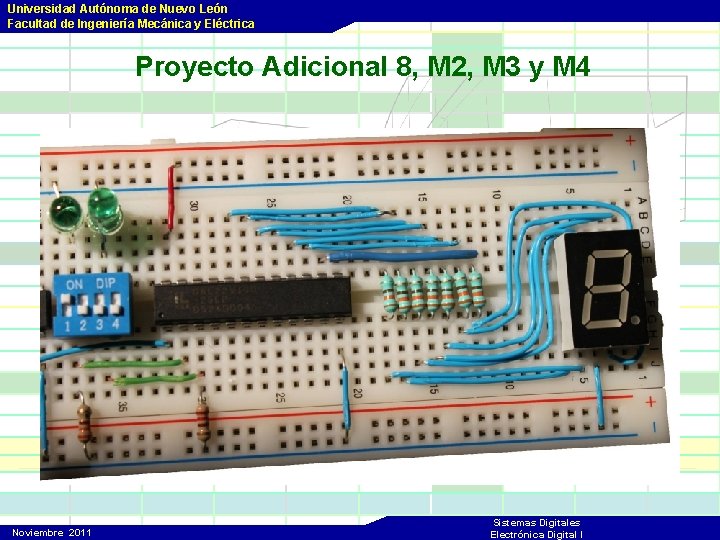

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Proyecto Adicional 8, M 2, M 3 y M 4 Diseñar un Contador Hexadecimal de 4 bits, Ascendente/ descendente con el decodificador de Hexadecimal a 7 segmentos integrado. Que contenga una entrada X de modo que: Si X=0 el conteo sea en forma ascendente. Si X=1 el conteo sea en forma descendente. Incluir además una entrada adicional de Rst que mande a cero el conteo al oprimirla Noviembre 2011 Sistemas Digitales Electrónica Digital I

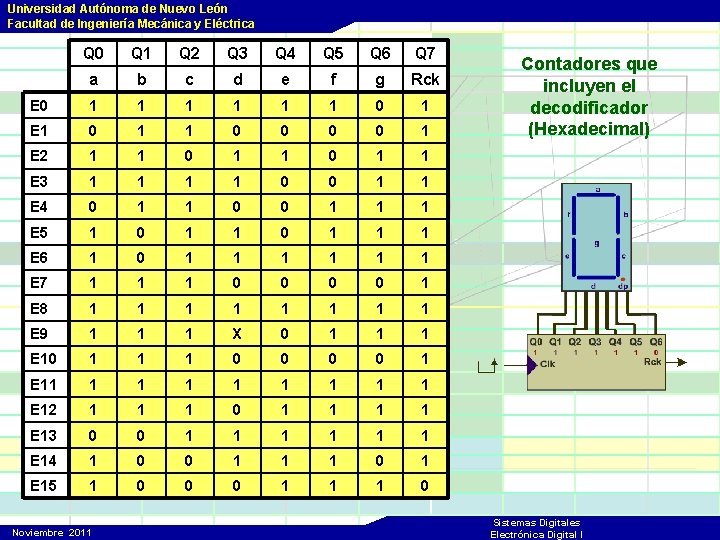

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Q 0 Q 1 Q 2 Q 3 Q 4 Q 5 Q 6 Q 7 a b c d e f g Rck E 0 1 1 1 0 1 E 1 0 1 1 0 0 1 E 2 1 1 0 1 1 E 3 1 1 0 0 1 1 E 4 0 1 1 0 0 1 1 1 E 5 1 0 1 1 1 E 6 1 0 1 1 1 E 7 1 1 1 0 0 1 E 8 1 1 1 1 E 9 1 1 1 X 0 1 1 1 E 10 1 1 1 0 0 1 E 11 1 1 1 1 E 12 1 1 1 0 1 1 E 13 0 0 1 1 1 E 14 1 0 0 1 1 1 0 1 E 15 1 0 0 0 1 1 1 0 Noviembre 2011 Contadores que incluyen el decodificador (Hexadecimal) Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Proyecto Adicional 8, M 2, M 3 y M 4 Noviembre 2011 Sistemas Digitales Electrónica Digital I

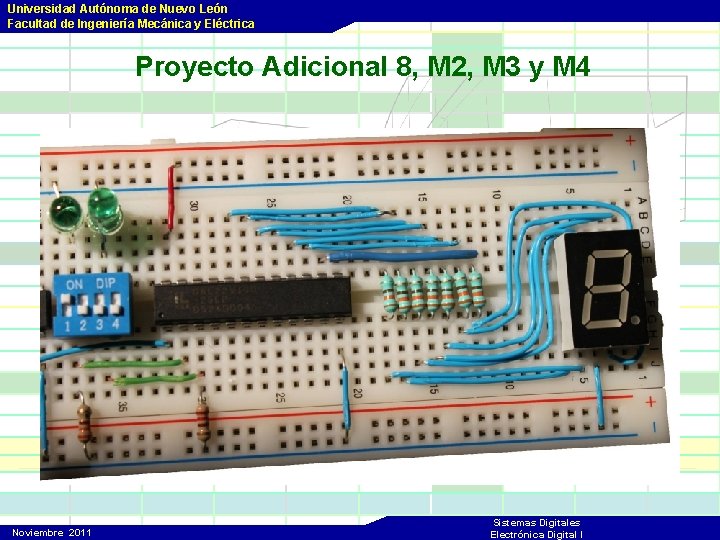

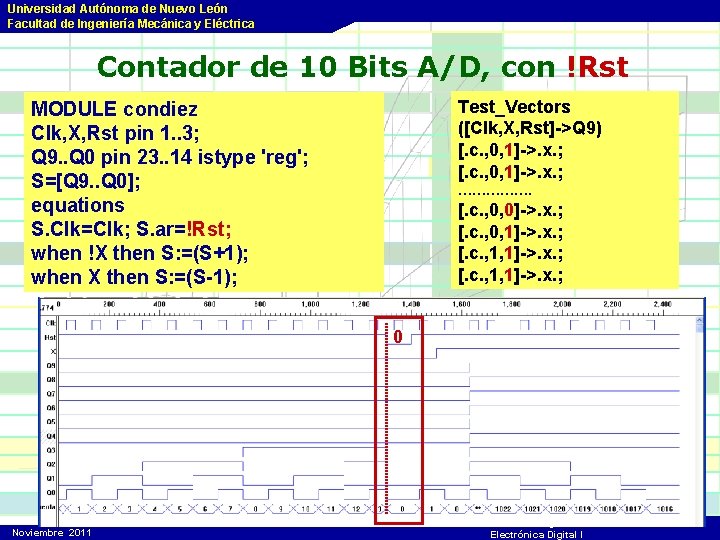

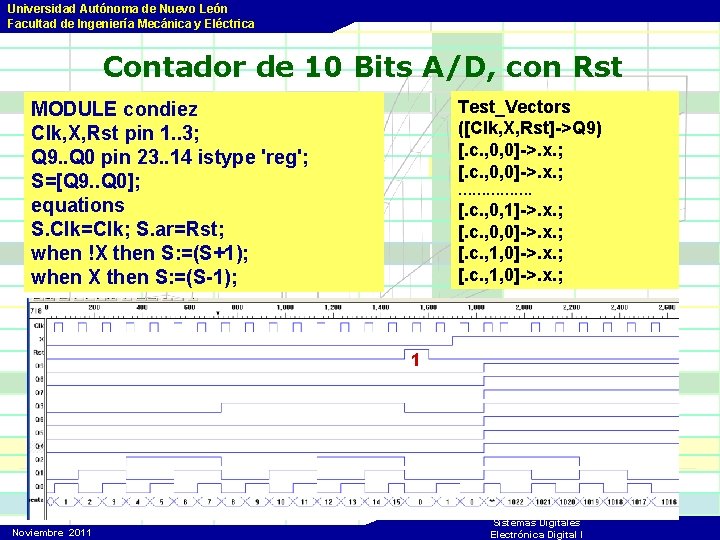

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 10 Bits A/D, con Rst Test_Vectors ([Clk, X, Rst]->Q 9) [. c. , 0, 0]->. x. ; MODULE condiez Clk, X, Rst pin 1. . 3; Q 9. . Q 0 pin 23. . 14 istype 'reg'; S=[Q 9. . Q 0]; equations S. Clk=Clk; S. ar=Rst; when !X then S: =(S+1); when X then S: =(S-1); ……………. [. c. , 0, 1]->. x. ; [. c. , 0, 0]->. x. ; [. c. , 1, 0]->. x. ; 1 Noviembre 2011 Sistemas Digitales Electrónica Digital I

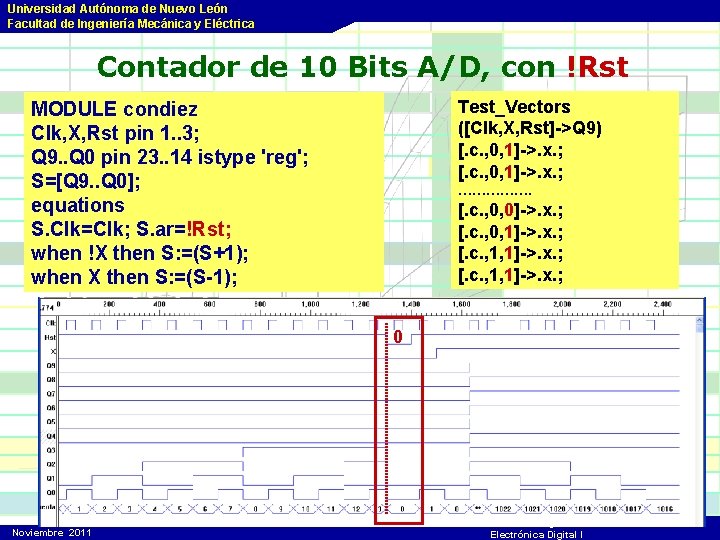

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 10 Bits A/D, con !Rst Test_Vectors ([Clk, X, Rst]->Q 9) [. c. , 0, 1]->. x. ; MODULE condiez Clk, X, Rst pin 1. . 3; Q 9. . Q 0 pin 23. . 14 istype 'reg'; S=[Q 9. . Q 0]; equations S. Clk=Clk; S. ar=!Rst; when !X then S: =(S+1); when X then S: =(S-1); ……………. [. c. , 0, 0]->. x. ; [. c. , 0, 1]->. x. ; [. c. , 1, 1]->. x. ; 0 Noviembre 2011 Sistemas Digitales Electrónica Digital I

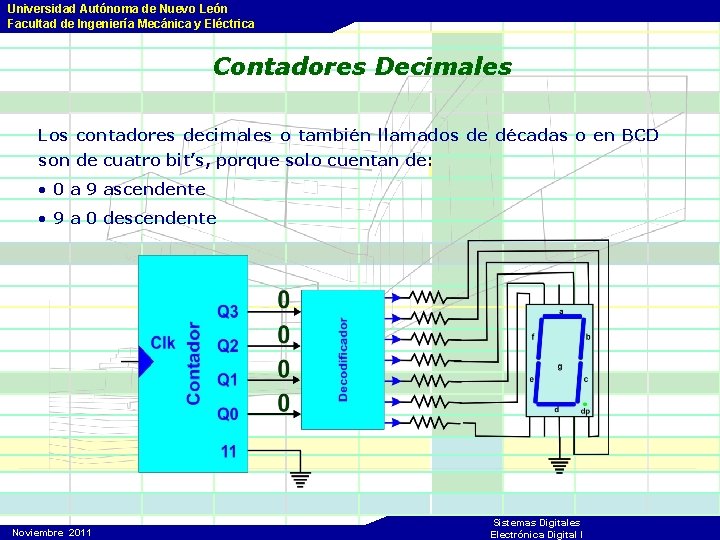

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contadores Decimales Los contadores decimales o también llamados de décadas o en BCD son de cuatro bit’s, porque solo cuentan de: • 0 a 9 ascendente • 9 a 0 descendente Noviembre 2011 Sistemas Digitales Electrónica Digital I

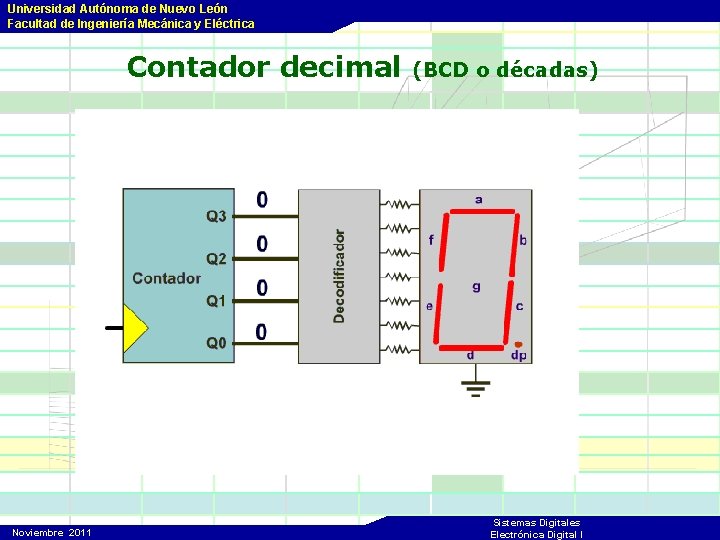

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador decimal Noviembre 2011 (BCD o décadas) Sistemas Digitales Electrónica Digital I

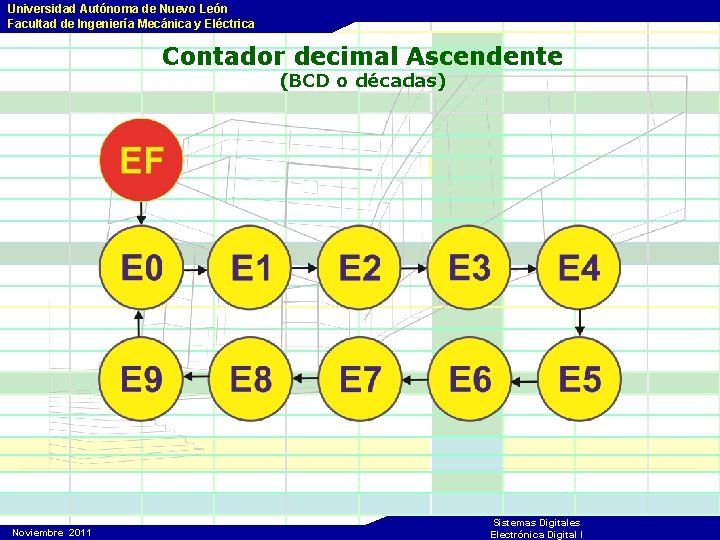

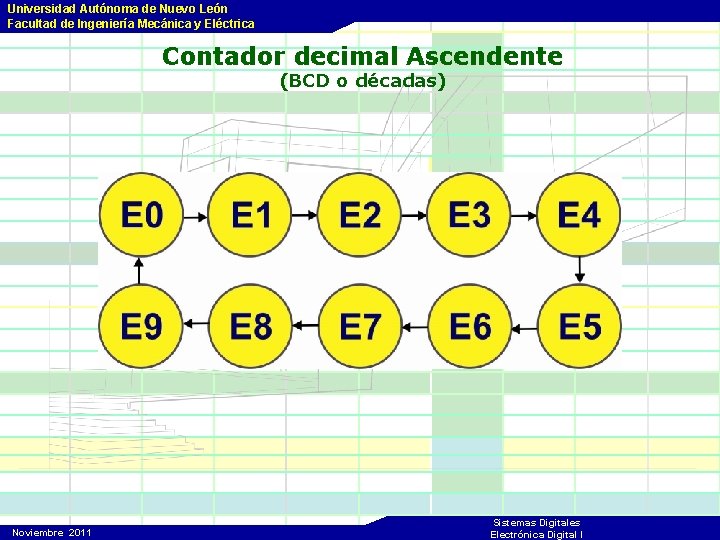

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador decimal Ascendente (BCD o décadas) Noviembre 2011 Sistemas Digitales Electrónica Digital I

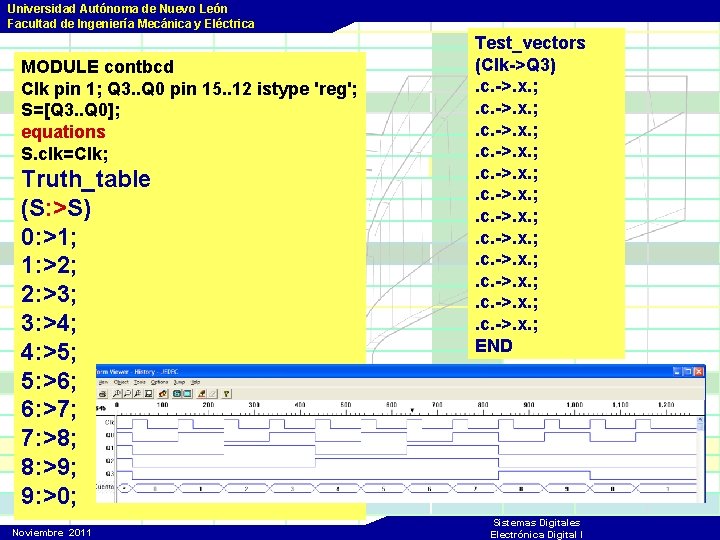

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE contbcd Clk pin 1; Q 3. . Q 0 pin 15. . 12 istype 'reg'; S=[Q 3. . Q 0]; equations S. clk=Clk; Truth_table (S: >S) 0: >1; 1: >2; 2: >3; 3: >4; 4: >5; 5: >6; 6: >7; 7: >8; 8: >9; 9: >0; Noviembre 2011 Test_vectors (Clk->Q 3). c. ->. x. ; END Sistemas Digitales Electrónica Digital I

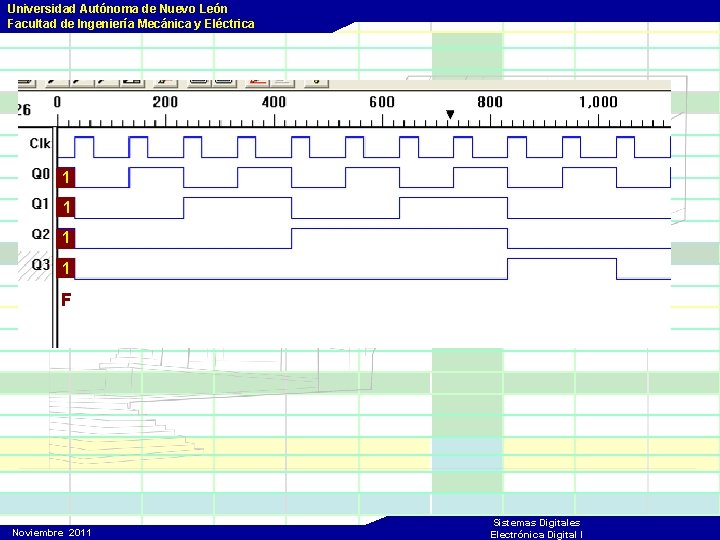

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador decimal Ascendente (BCD o décadas) Noviembre 2011 Sistemas Digitales Electrónica Digital I

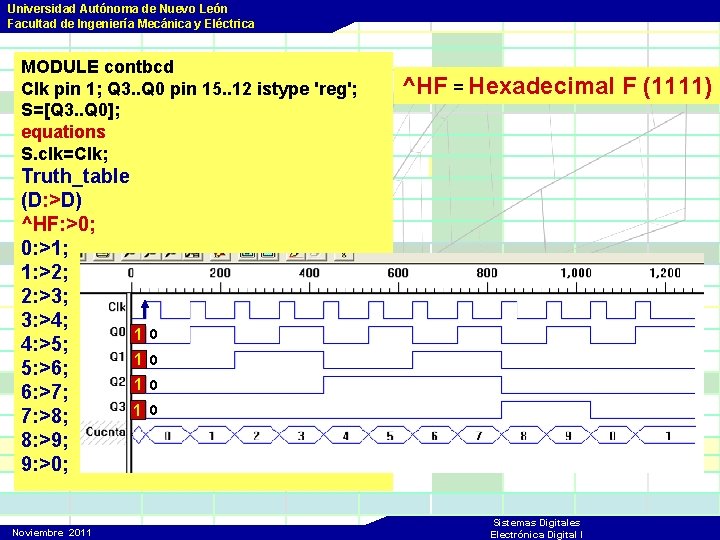

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE contbcd Clk pin 1; Q 3. . Q 0 pin 15. . 12 istype 'reg'; S=[Q 3. . Q 0]; equations S. clk=Clk; Truth_table (D: >D) ^HF: >0; 0: >1; 1: >2; 2: >3; 3: >4; 1 4: >5; 1 5: >6; 1 6: >7; 1 7: >8; 8: >9; 9: >0; Noviembre 2011 ^HF = Hexadecimal F (1111) 0 0 Sistemas Digitales Electrónica Digital I

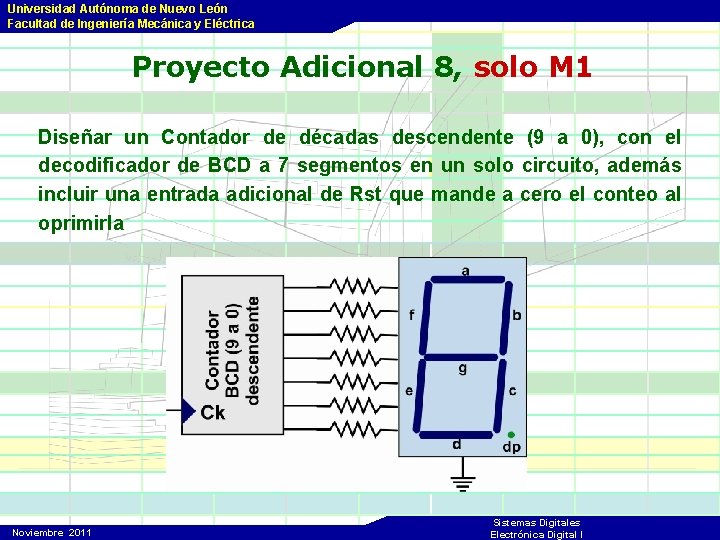

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Proyecto Adicional 8, solo M 1 Diseñar un Contador de décadas descendente (9 a 0), con el decodificador de BCD a 7 segmentos en un solo circuito, además incluir una entrada adicional de Rst que mande a cero el conteo al oprimirla Noviembre 2011 Sistemas Digitales Electrónica Digital I

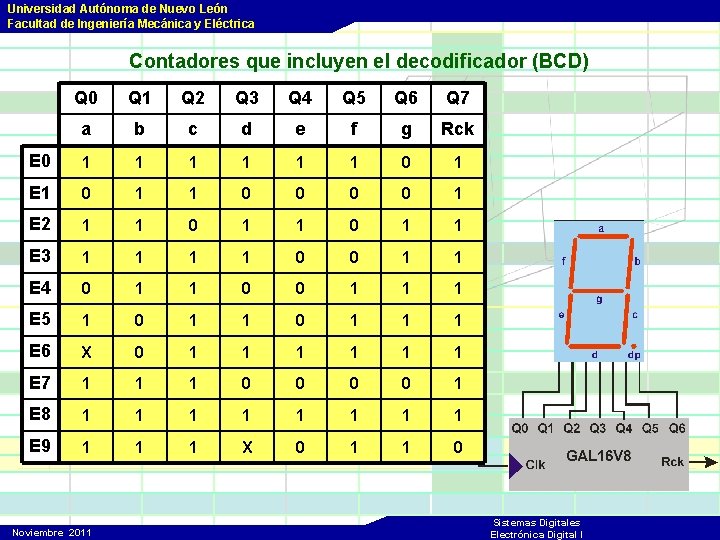

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contadores que incluyen el decodificador (BCD) Q 0 Q 1 Q 2 Q 3 Q 4 Q 5 Q 6 Q 7 a b c d e f g Rck E 0 1 1 1 0 1 E 1 0 1 1 0 0 1 E 2 1 1 0 1 1 E 3 1 1 0 0 1 1 E 4 0 1 1 0 0 1 1 1 E 5 1 0 1 1 1 E 6 X 0 1 1 1 E 7 1 1 1 0 0 1 E 8 1 1 1 1 E 9 1 1 1 X 0 1 1 0 Noviembre 2011 Sistemas Digitales Electrónica Digital I

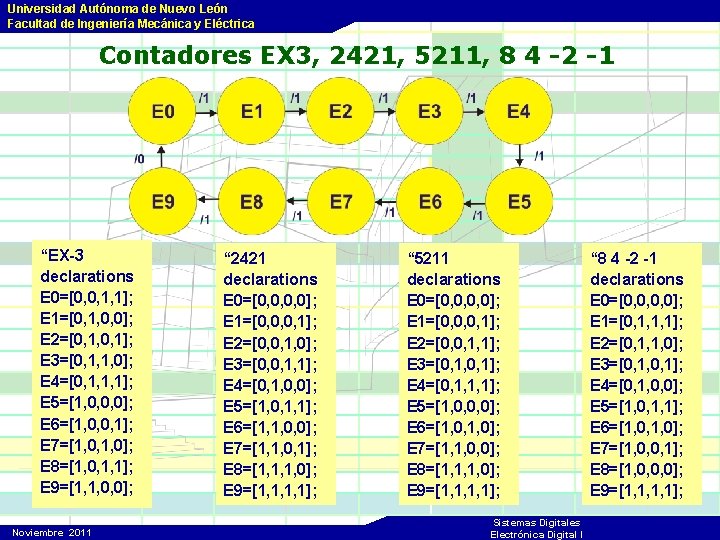

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contadores EX 3, 2421, 5211, 8 4 -2 -1 “EX-3 declarations E 0=[0, 0, 1, 1]; E 1=[0, 1, 0, 0]; E 2=[0, 1, 0, 1]; E 3=[0, 1, 1, 0]; E 4=[0, 1, 1, 1]; E 5=[1, 0, 0, 0]; E 6=[1, 0, 0, 1]; E 7=[1, 0, 1, 0]; E 8=[1, 0, 1, 1]; E 9=[1, 1, 0, 0]; Noviembre 2011 “ 2421 declarations E 0=[0, 0, 0, 0]; E 1=[0, 0, 0, 1]; E 2=[0, 0, 1, 0]; E 3=[0, 0, 1, 1]; E 4=[0, 1, 0, 0]; E 5=[1, 0, 1, 1]; E 6=[1, 1, 0, 0]; E 7=[1, 1, 0, 1]; E 8=[1, 1, 1, 0]; E 9=[1, 1, 1, 1]; “ 5211 declarations E 0=[0, 0, 0, 0]; E 1=[0, 0, 0, 1]; E 2=[0, 0, 1, 1]; E 3=[0, 1, 0, 1]; E 4=[0, 1, 1, 1]; E 5=[1, 0, 0, 0]; E 6=[1, 0, 1, 0]; E 7=[1, 1, 0, 0]; E 8=[1, 1, 1, 0]; E 9=[1, 1, 1, 1]; Sistemas Digitales Electrónica Digital I “ 8 4 -2 -1 declarations E 0=[0, 0, 0, 0]; E 1=[0, 1, 1, 1]; E 2=[0, 1, 1, 0]; E 3=[0, 1, 0, 1]; E 4=[0, 1, 0, 0]; E 5=[1, 0, 1, 1]; E 6=[1, 0, 1, 0]; E 7=[1, 0, 0, 1]; E 8=[1, 0, 0, 0]; E 9=[1, 1, 1, 1];

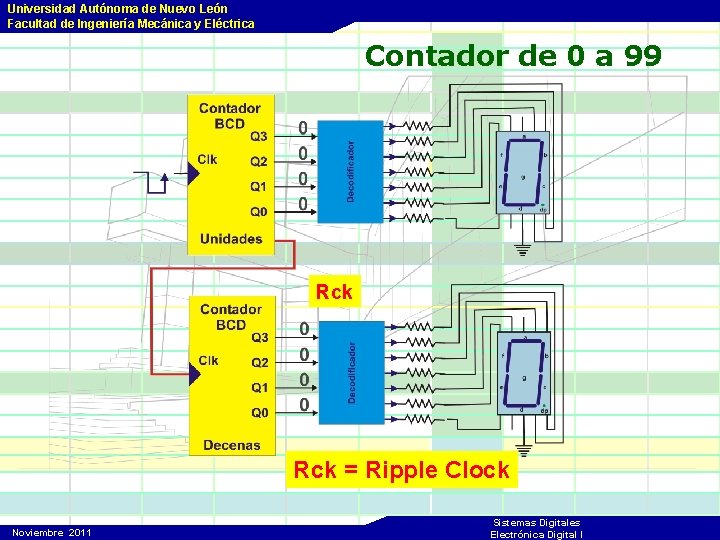

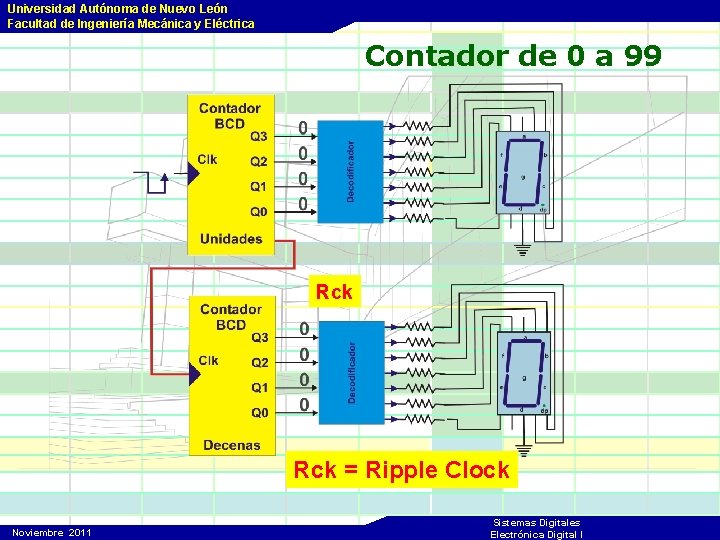

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 0 a 99 Rck = Ripple Clock Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Noviembre 2011 Ck Q 3 Q 2 Q 1 Q 0 Rck 0 0 0 1 1 2 0 0 1 3 0 0 1 1 1 4 0 1 0 0 1 5 0 1 1 6 0 1 1 0 1 7 0 1 1 8 1 0 0 0 1 9 1 0 0 0 0 1 Sistemas Digitales Electrónica Digital I 1 0 1

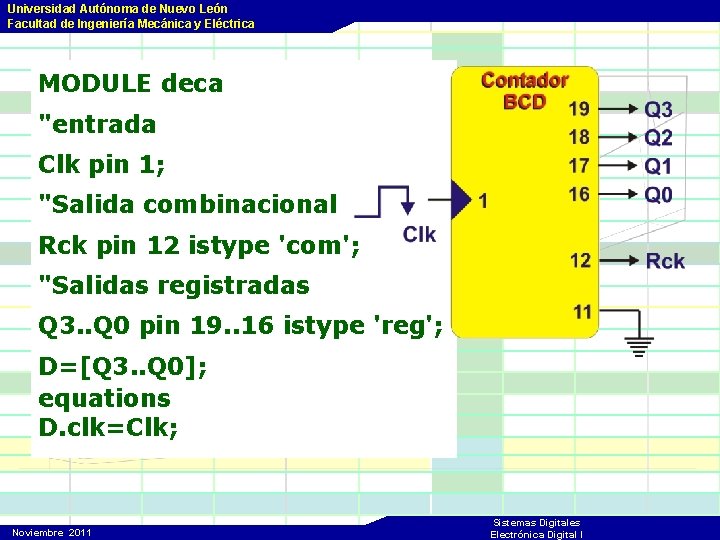

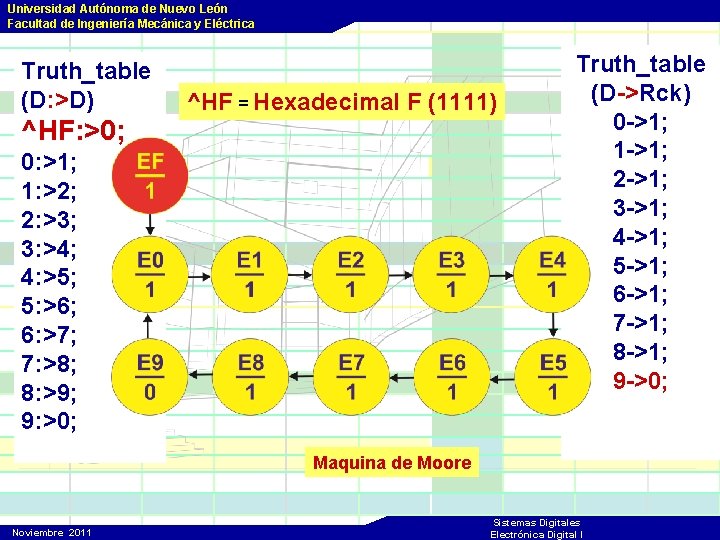

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE deca "entrada Clk pin 1; "Salida combinacional Rck pin 12 istype 'com'; "Salidas registradas Q 3. . Q 0 pin 19. . 16 istype 'reg'; D=[Q 3. . Q 0]; equations D. clk=Clk; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Truth_table (D: >D) 0: >1; 1: >2; 2: >3; 3: >4; 4: >5; 5: >6; 6: >7; 7: >8; 8: >9; 9: >0; Noviembre 2011 Truth_table (D->Rck) 0 ->1; 1 ->1; 2 ->1; 3 ->1; 4 ->1; 5 ->1; 6 ->1; 7 ->1; 8 ->1; 9 ->0; Sistemas Digitales Electrónica Digital I

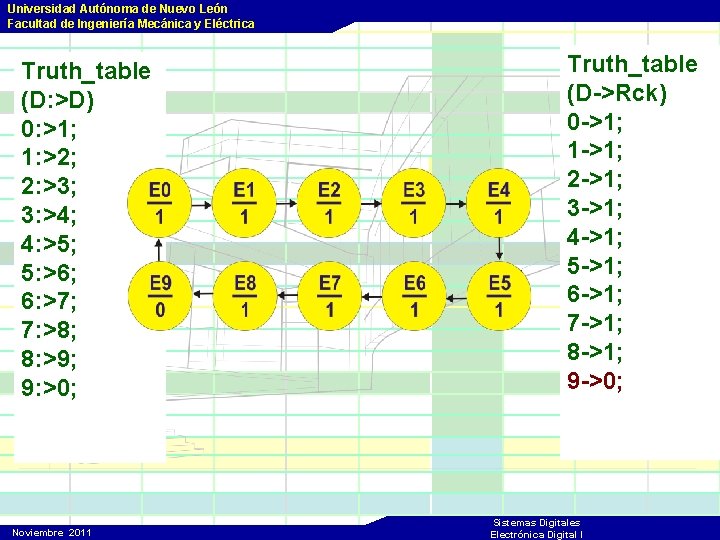

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 1 1 F Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Truth_table (D: >D) ^HF: >0; ^HF = Hexadecimal F (1111) 0: >1; 1: >2; 2: >3; 3: >4; 4: >5; 5: >6; 6: >7; 7: >8; 8: >9; 9: >0; Truth_table (D->Rck) 0 ->1; 1 ->1; 2 ->1; 3 ->1; 4 ->1; 5 ->1; 6 ->1; 7 ->1; 8 ->1; 9 ->0; Maquina de Moore Noviembre 2011 Sistemas Digitales Electrónica Digital I

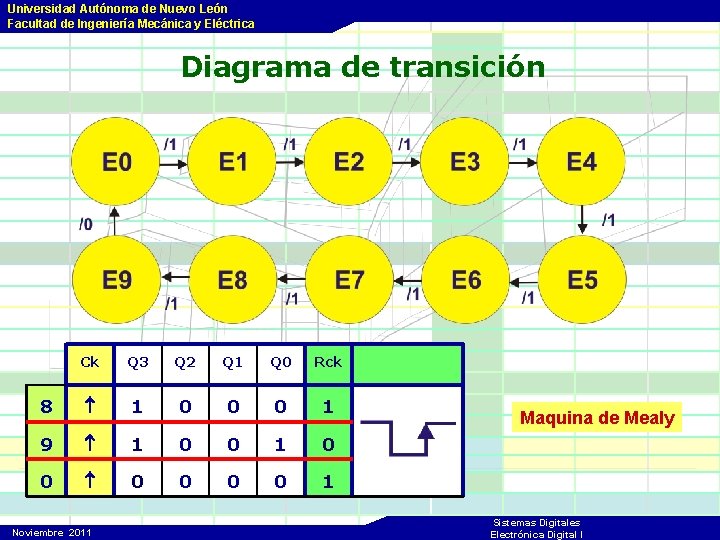

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Diagrama de transición Ck Q 3 Q 2 Q 1 Q 0 Rck 8 1 0 0 0 1 9 1 0 0 0 0 1 Noviembre 2011 Maquina de Mealy Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE deca "entrada Clk pin 1; "Salida combinacional Rck pin 12 istype 'com'; "Salidas registradas Q 3. . Q 0 pin 19. . 16 istype 'reg'; D=[Q 3. . Q 0]; equations D. clk=Clk; Noviembre 2011 Sistemas Digitales Electrónica Digital I

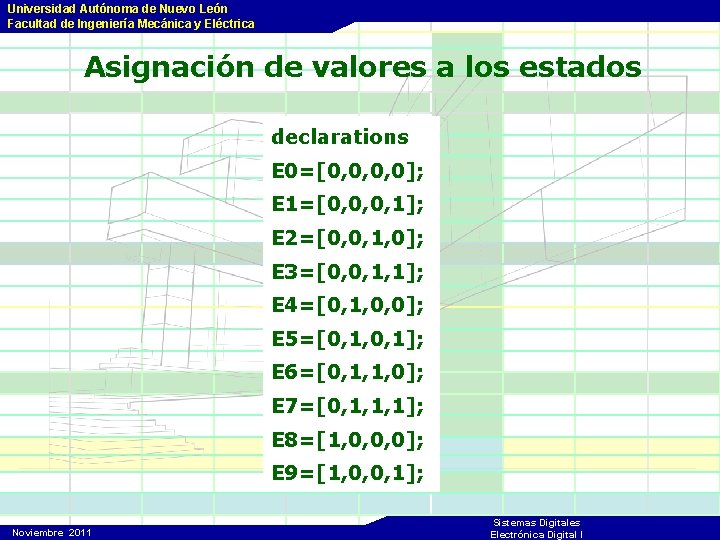

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Asignación de valores a los estados declarations E 0=[0, 0, 0, 0]; E 1=[0, 0, 0, 1]; E 2=[0, 0, 1, 0]; E 3=[0, 0, 1, 1]; E 4=[0, 1, 0, 0]; E 5=[0, 1, 0, 1]; E 6=[0, 1, 1, 0]; E 7=[0, 1, 1, 1]; E 8=[1, 0, 0, 0]; E 9=[1, 0, 0, 1]; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Máquina de Mealy state_diagram D State E 0: goto E 1 with Rck=1; state E 1: goto E 2 with Rck=1; state E 2: goto E 3 with Rck=1; state E 3: goto E 4 with Rck=1; state E 4: goto E 5 with Rck=1; Noviembre 2011 state E 5: goto E 6 with state E 6: goto E 7 with state E 7: goto E 8 with state E 8: goto E 9 with state E 9: Rck=1; goto E 0 with Rck=0; Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica test_vectors (Clk->D). c. ->. x. ; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Máquina de Moore Truth_table (D->Rck) 0 ->1; 1 ->1; 2 ->1; 3 ->1; 4 ->1; 5 ->1; 6 ->1; 7 ->1; 8 ->1; 9 ->0; Noviembre 2011 Máquina de Mealy Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica test_vectors (Clk->D). c. ->. x. ; END Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Noviembre 2011 Sistemas Digitales Electrónica Digital I

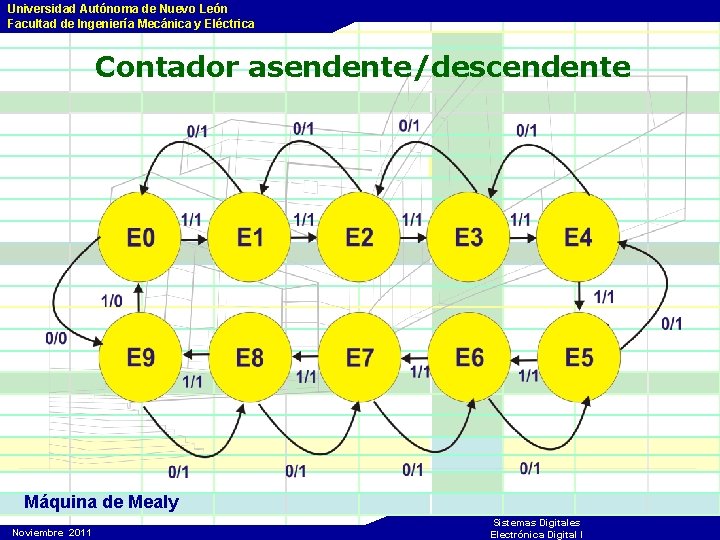

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador asendente/descendente Máquina de Mealy Noviembre 2011 Sistemas Digitales Electrónica Digital I

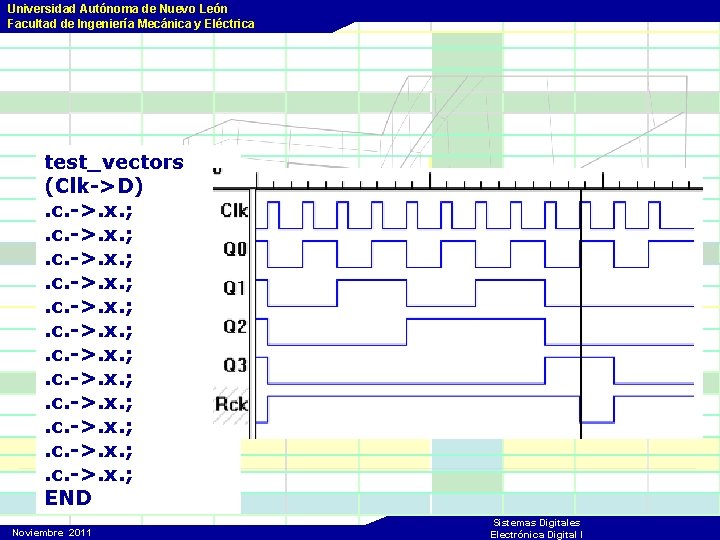

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica MODULE adbcd "entradas Clk, AD pin 1, 2; "salida Combinacional Rck pin 12 istype 'com'; "salidas Registradas Q 3. . Q 0 pin 19. . 16 istype 'reg'; D=[Q 3. . Q 0]; equations D. clk=Clk; Noviembre 2011 Sistemas Digitales Electrónica Digital I

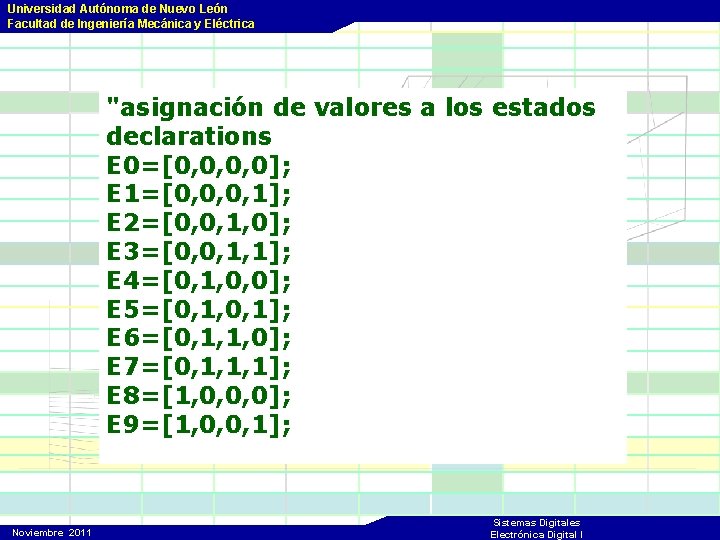

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica "asignación de valores a los estados declarations E 0=[0, 0, 0, 0]; E 1=[0, 0, 0, 1]; E 2=[0, 0, 1, 0]; E 3=[0, 0, 1, 1]; E 4=[0, 1, 0, 0]; E 5=[0, 1, 0, 1]; E 6=[0, 1, 1, 0]; E 7=[0, 1, 1, 1]; E 8=[1, 0, 0, 0]; E 9=[1, 0, 0, 1]; Noviembre 2011 Sistemas Digitales Electrónica Digital I

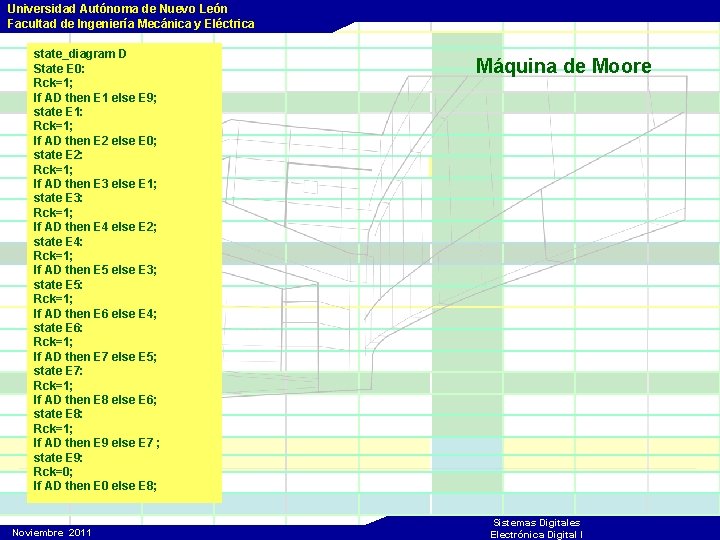

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica state_diagram D State E 0: If AD then E 1; If !AD Then E 9 with Rck=0; state E 1: If AD then E 2 else E 0 with Rck=1; state E 2: If AD then E 3 else E 1 with Rck=1; state E 3: If AD then E 4 else E 2 with Rck=1; state E 4: If AD then E 5 else E 3 with Rck=1; state E 5: If AD then E 6 else E 4 with Rck=1; state E 6: If AD then E 7 else E 5 with Rck=1; state E 7: If AD then E 8 else E 6 with Rck=1; state E 8: If AD then E 9 else E 7 with Rck=1; state E 9: If AD then E 0 with Rck=0; if !AD Then E 8 with Rck=1; Noviembre 2011 Máquina de Mealy Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica state_diagram D State E 0: Rck=1; If AD then E 1 else E 9; state E 1: Rck=1; If AD then E 2 else E 0; state E 2: Rck=1; If AD then E 3 else E 1; state E 3: Rck=1; If AD then E 4 else E 2; state E 4: Rck=1; If AD then E 5 else E 3; state E 5: Rck=1; If AD then E 6 else E 4; state E 6: Rck=1; If AD then E 7 else E 5; state E 7: Rck=1; If AD then E 8 else E 6; state E 8: Rck=1; If AD then E 9 else E 7 ; state E 9: Rck=0; If AD then E 0 else E 8; Noviembre 2011 Máquina de Moore Sistemas Digitales Electrónica Digital I

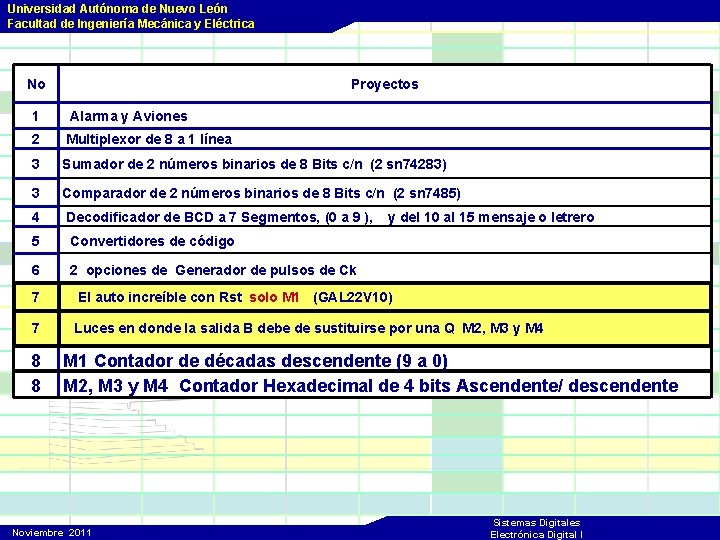

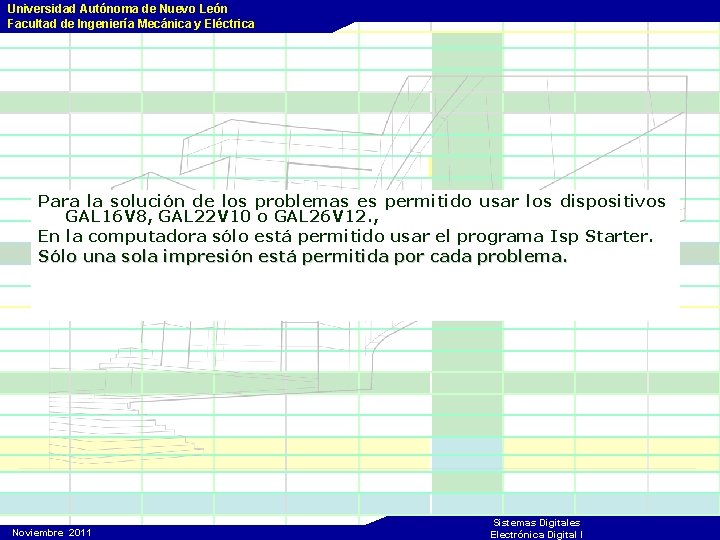

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica testvectors Clk ADD Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica test_vectors ([Clk, AD]->D)](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-74.jpg)

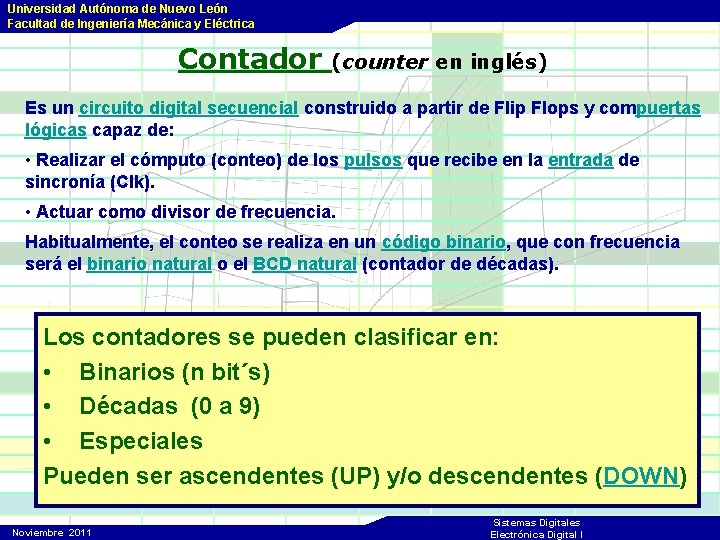

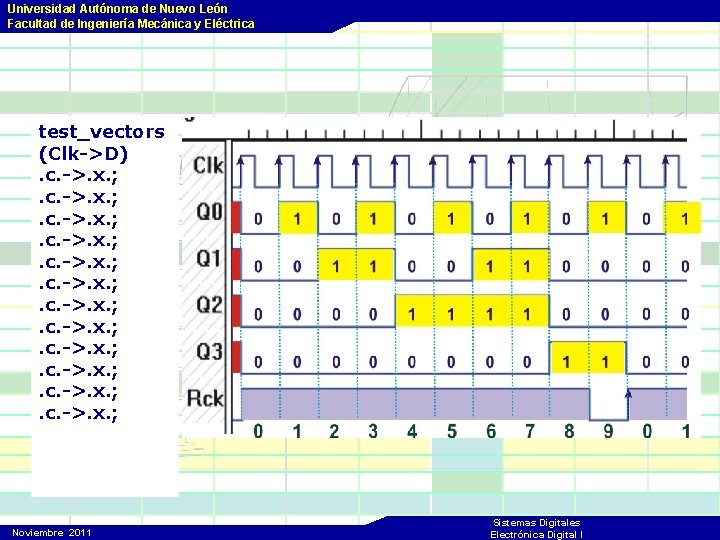

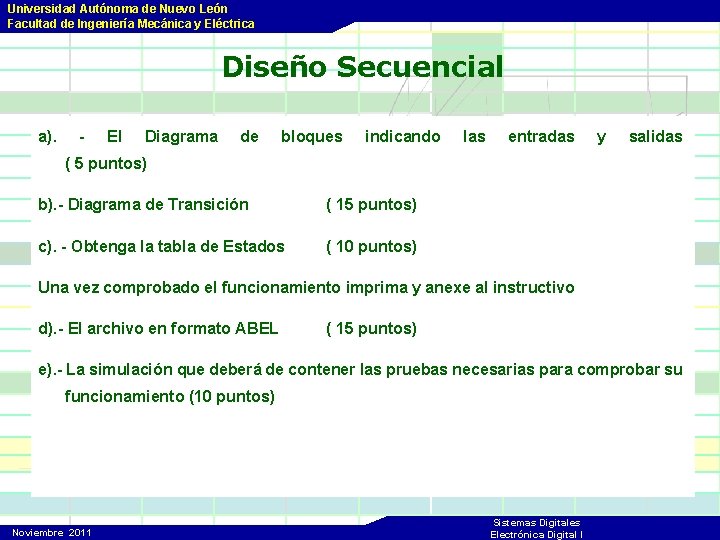

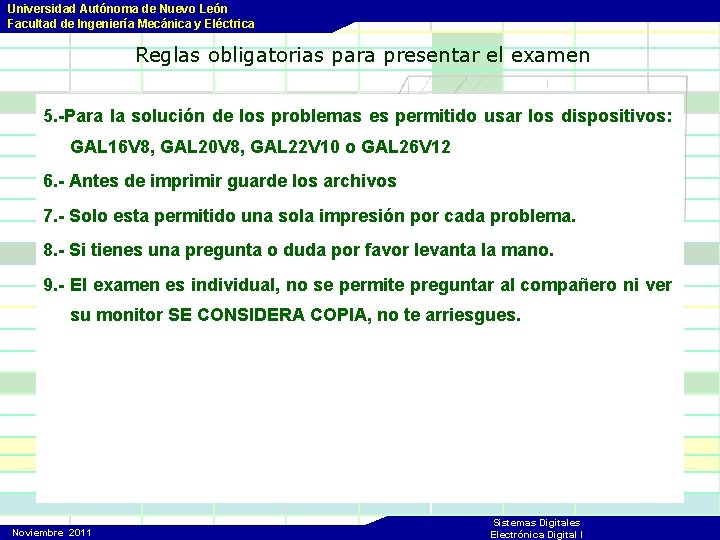

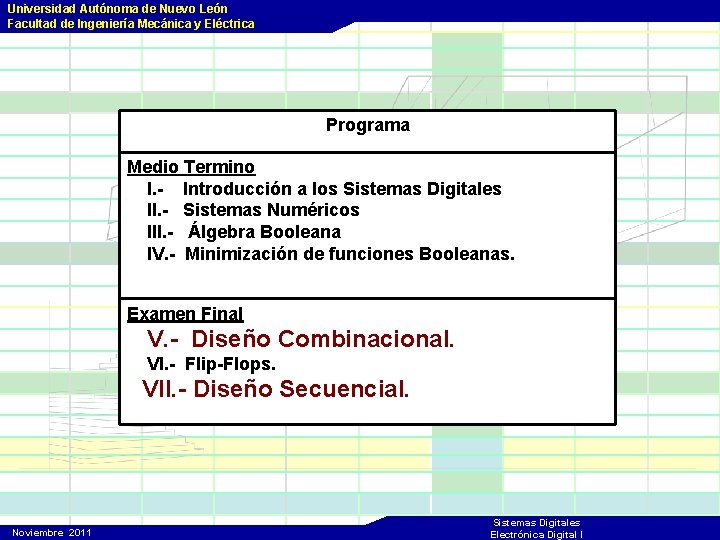

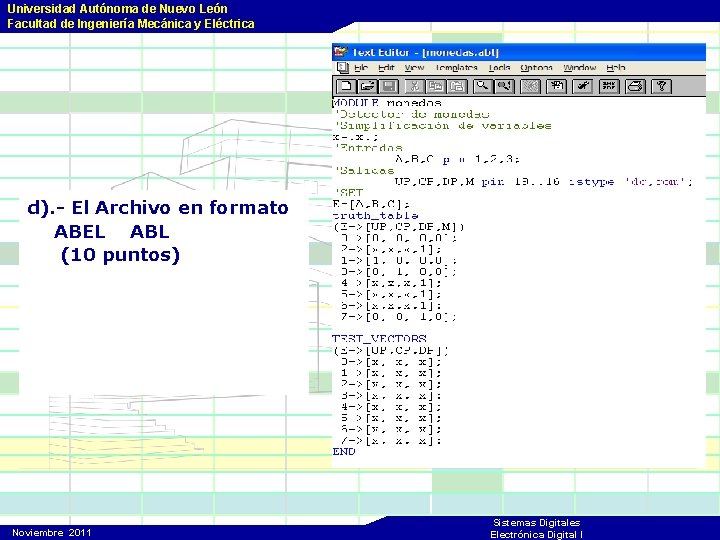

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica test_vectors ([Clk, AD]->D) [. c. , 1]->. x. ; [. c. , 0]->. x. ; [. c. , 0]->. x. ; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Noviembre 2011 Sistemas Digitales Electrónica Digital I

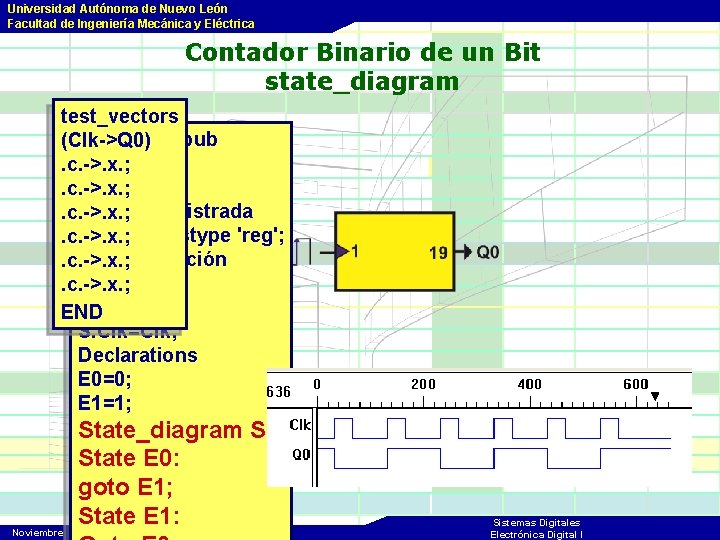

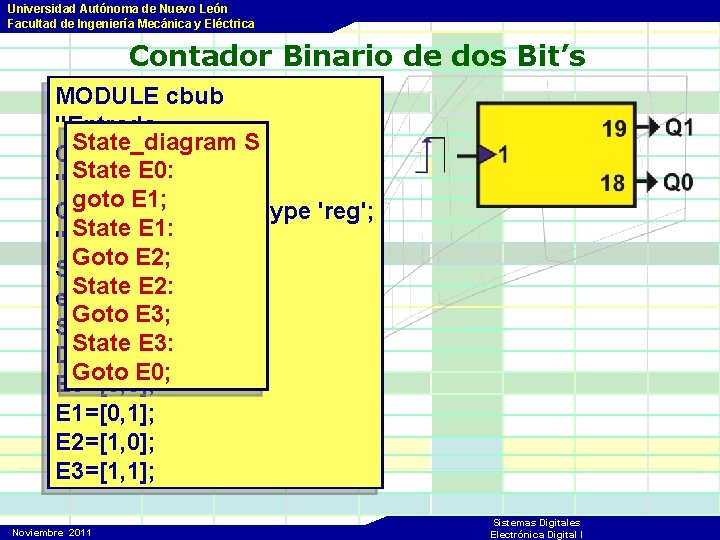

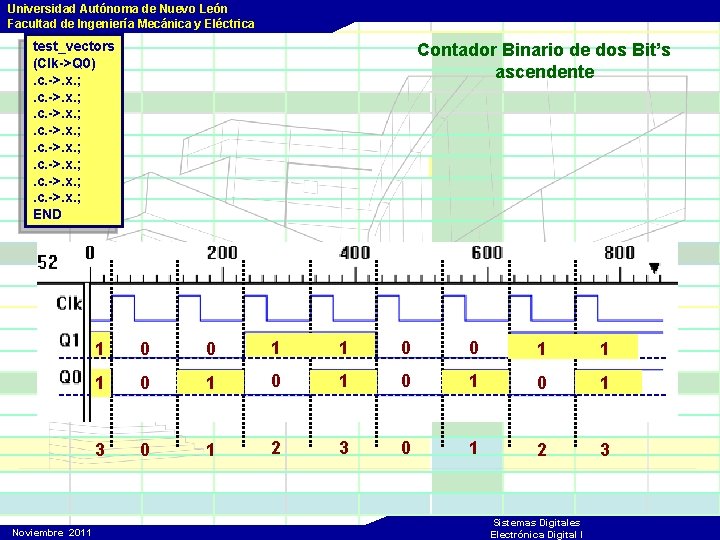

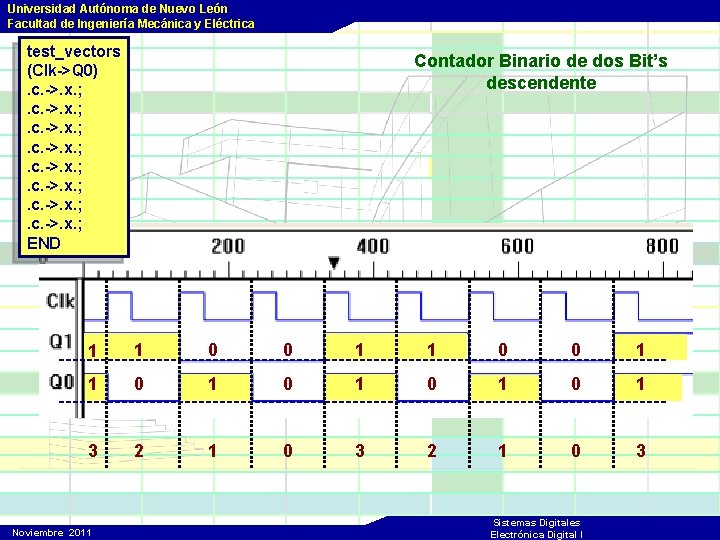

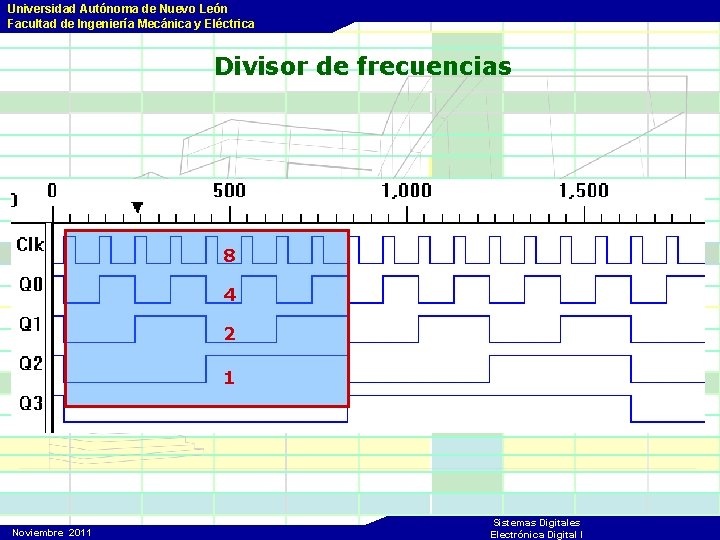

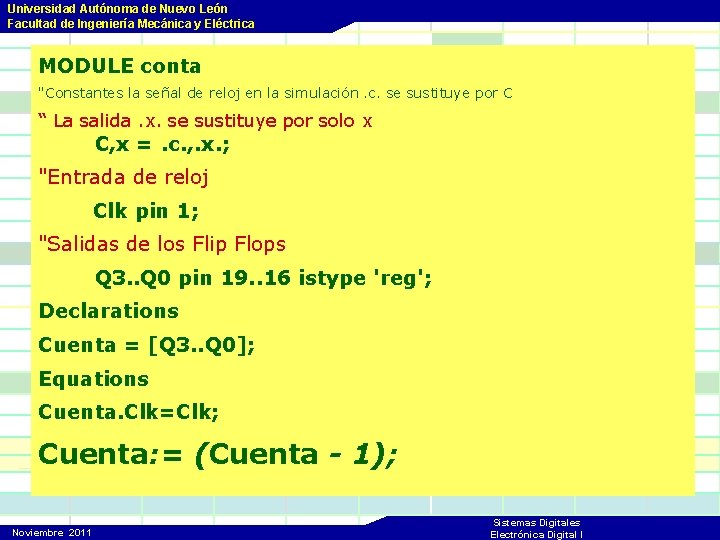

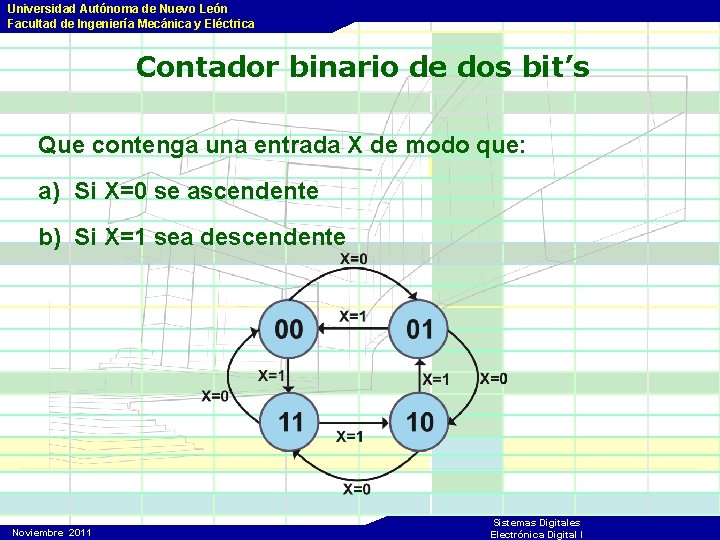

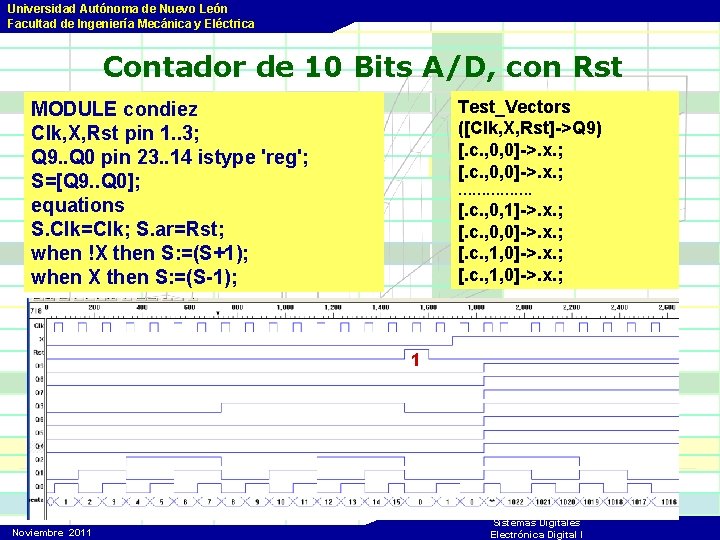

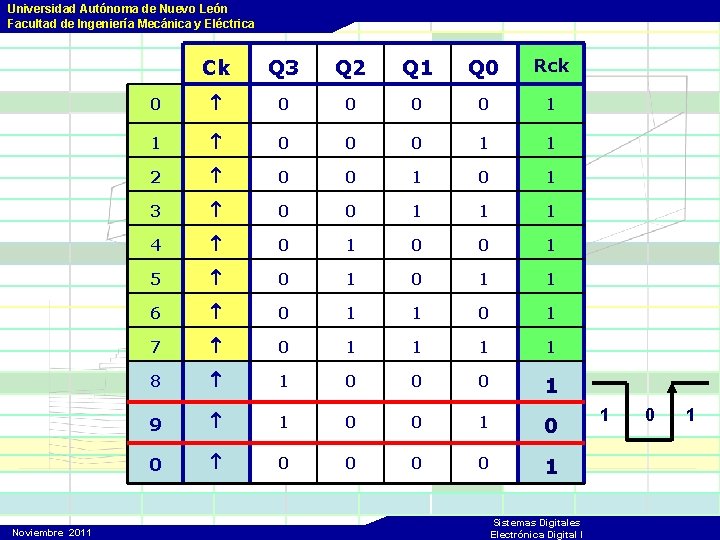

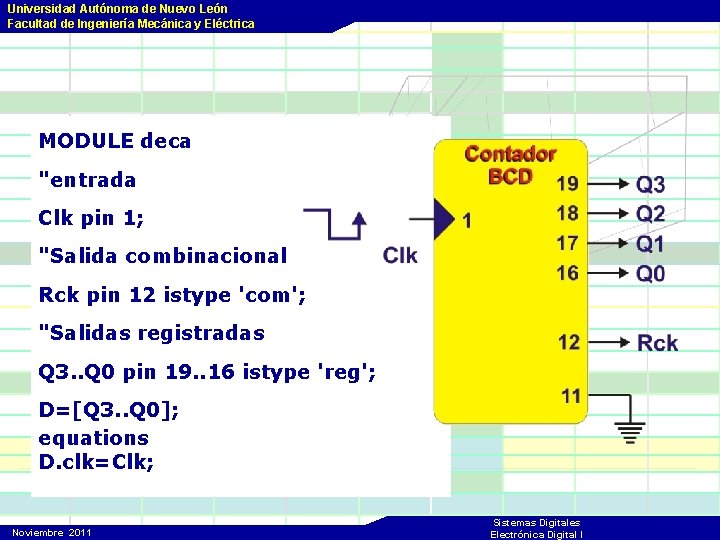

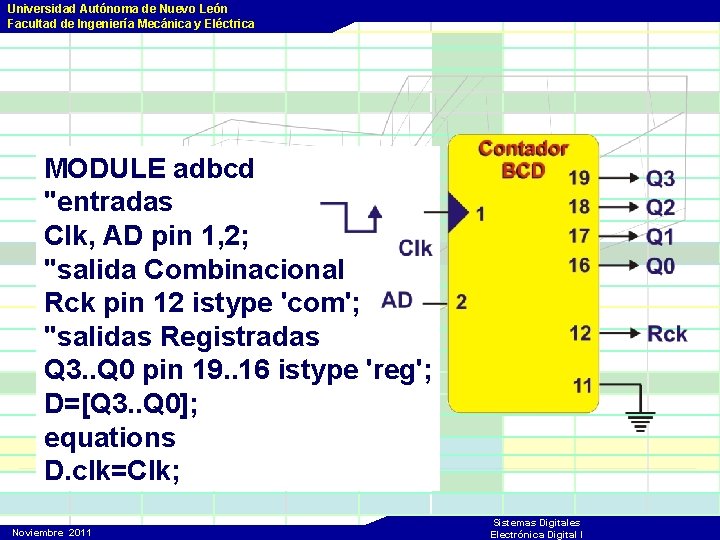

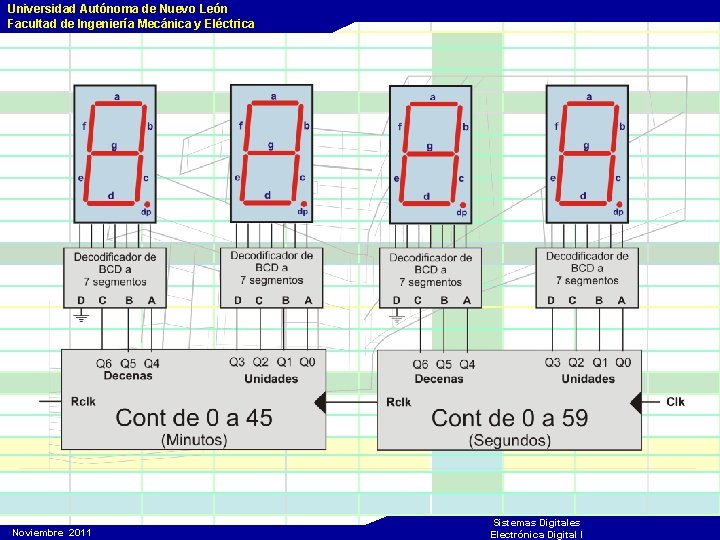

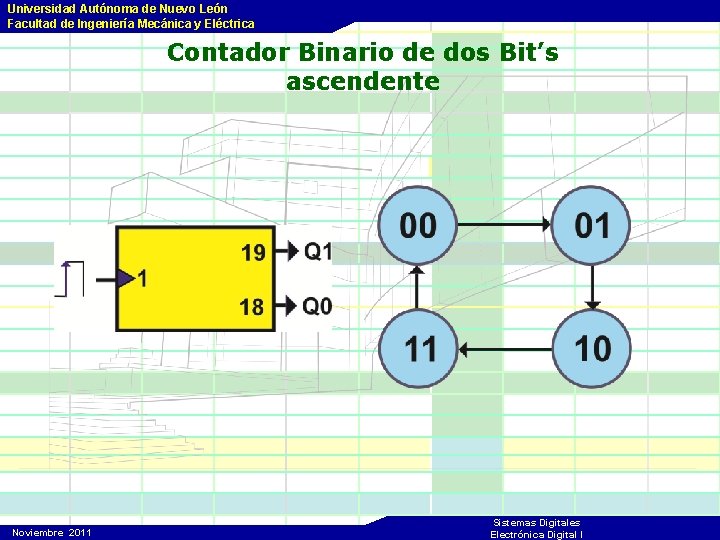

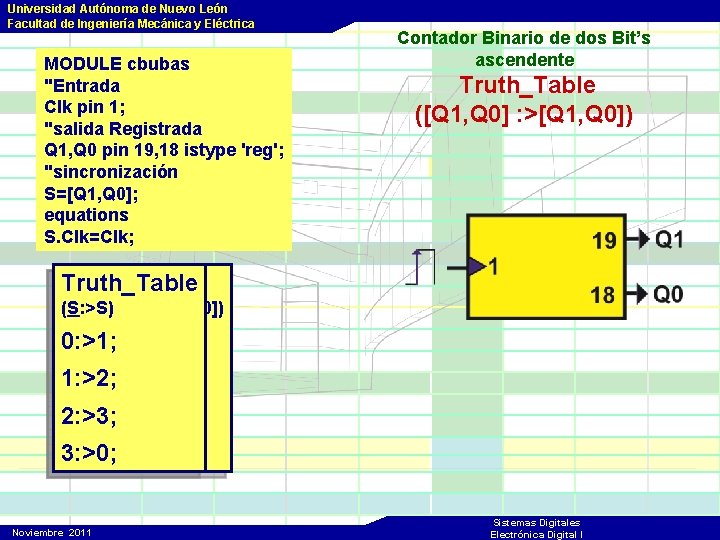

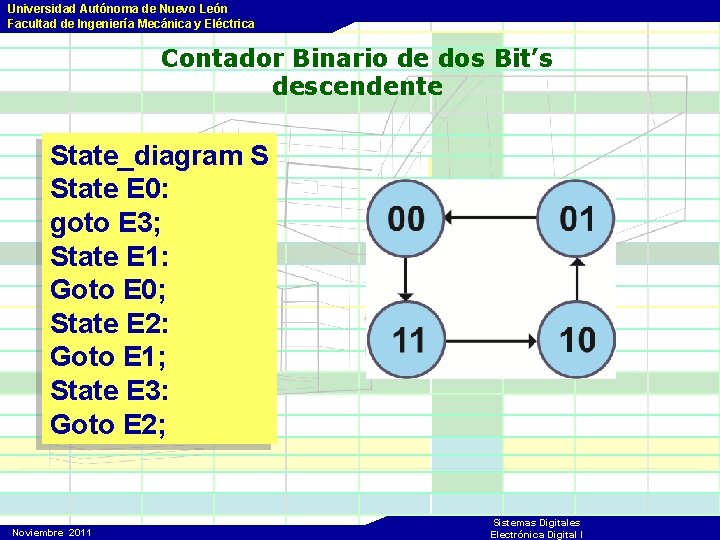

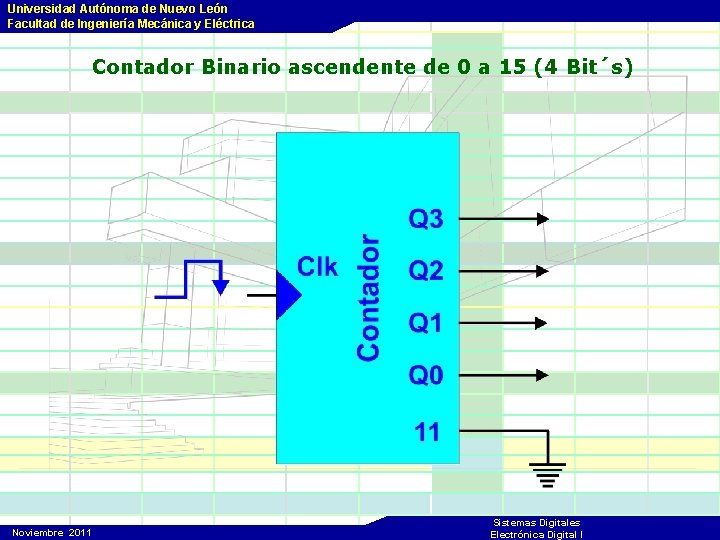

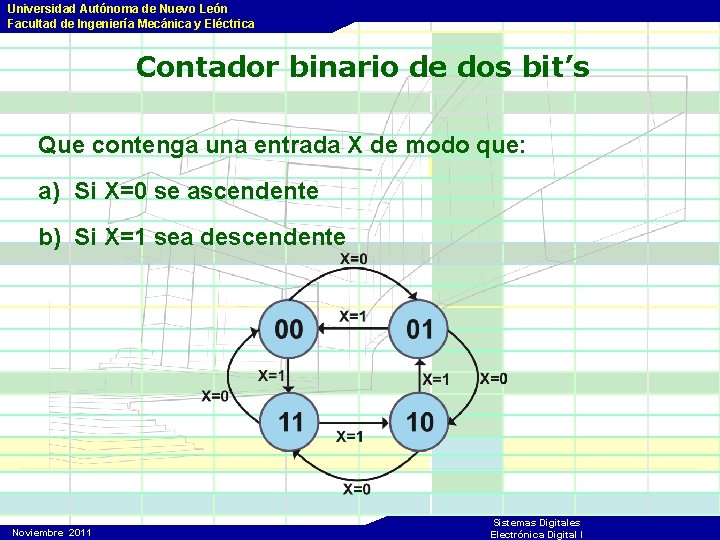

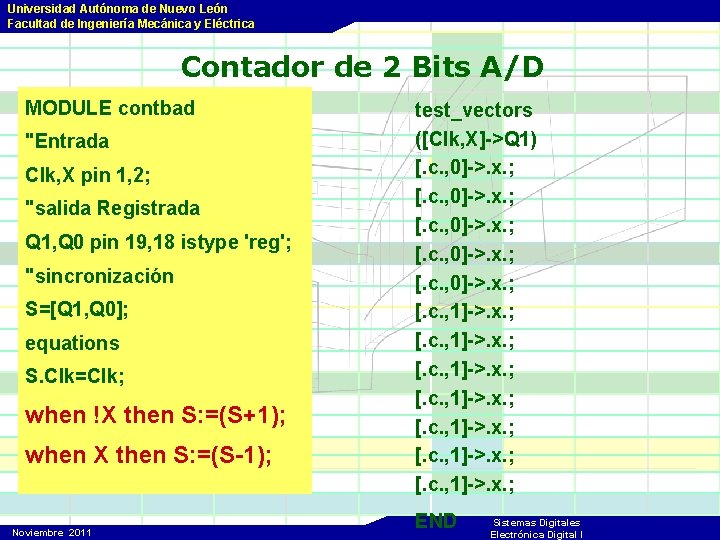

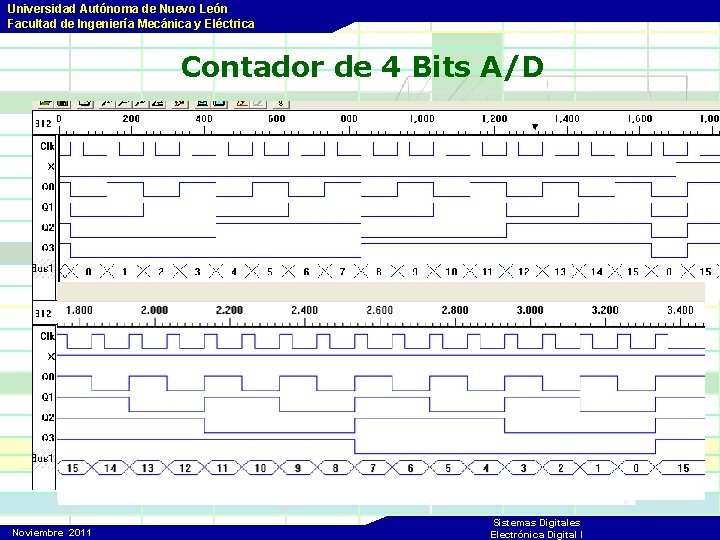

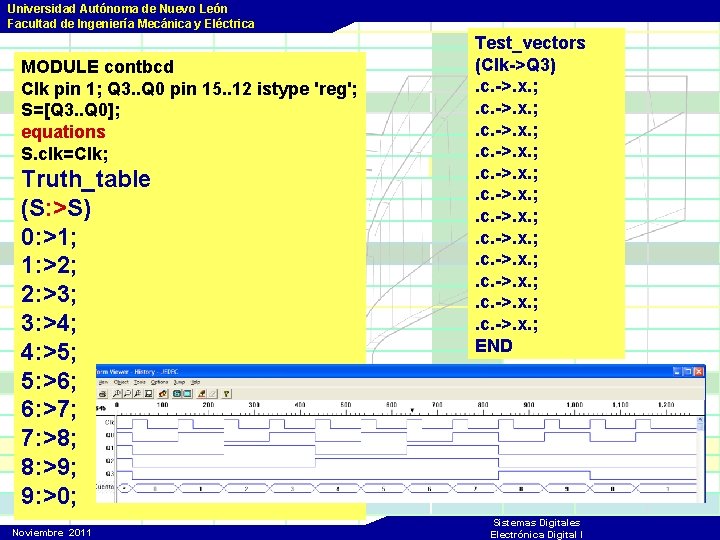

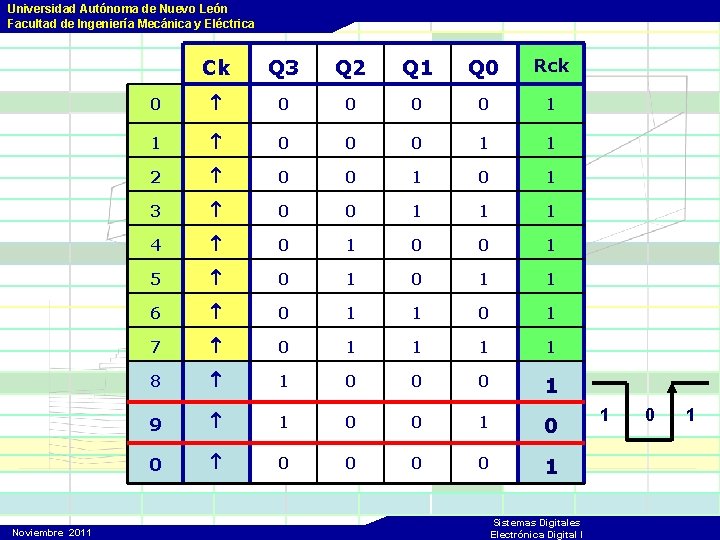

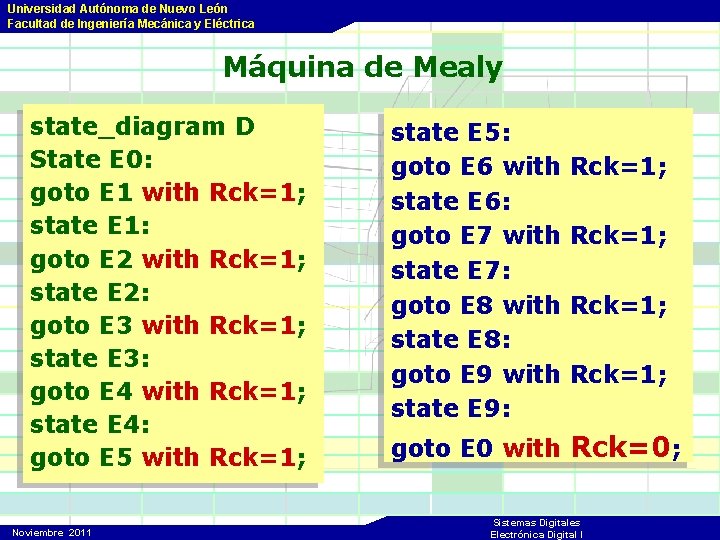

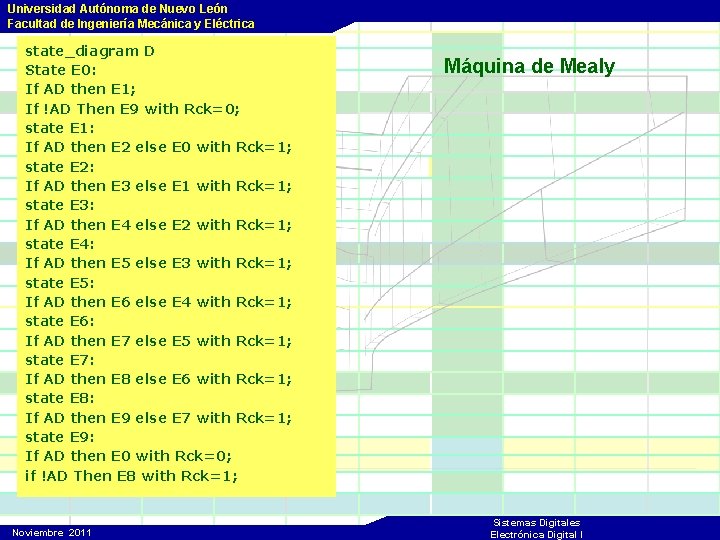

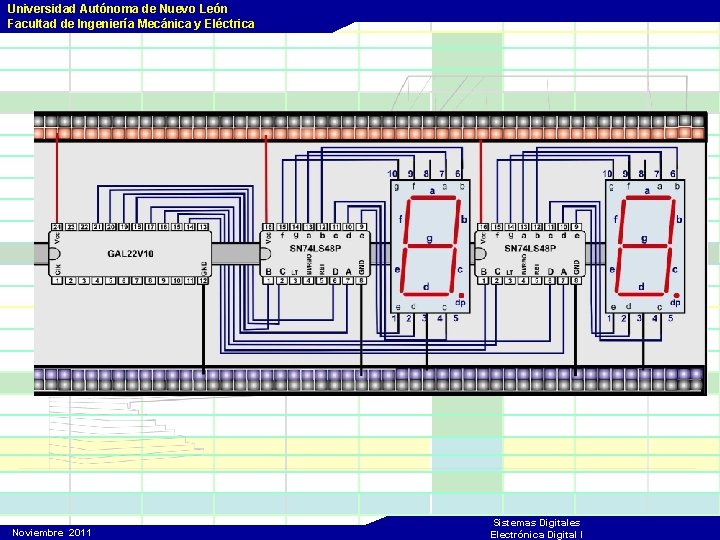

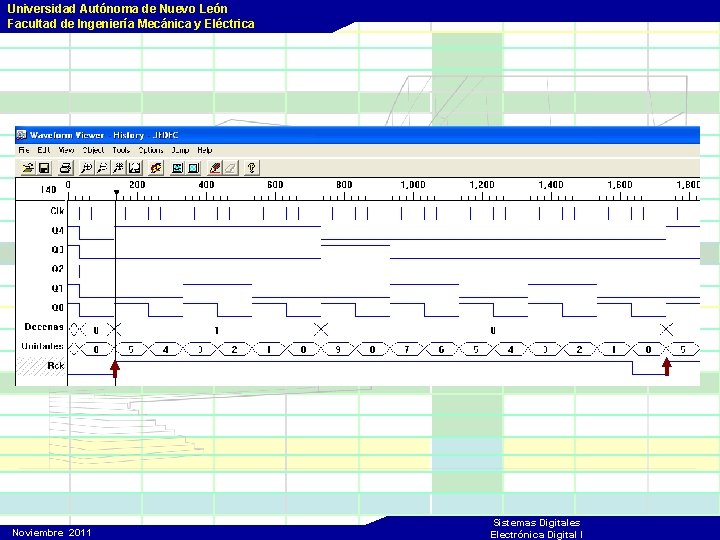

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 0 a 59 ascendente MODULE cnn "entrada Clk pin 1; “Salida Rck pin 12 istype ‘com’; "Salidas registradas Q 6. . Q 0 pin 19. . 13 istype 'reg'; D=[Q 6. . Q 4]; U=[Q 3. . Q 0]; equations D. clk=Clk; U. Clk=Clk; Noviembre 2011 Sistemas Digitales Electrónica Digital I

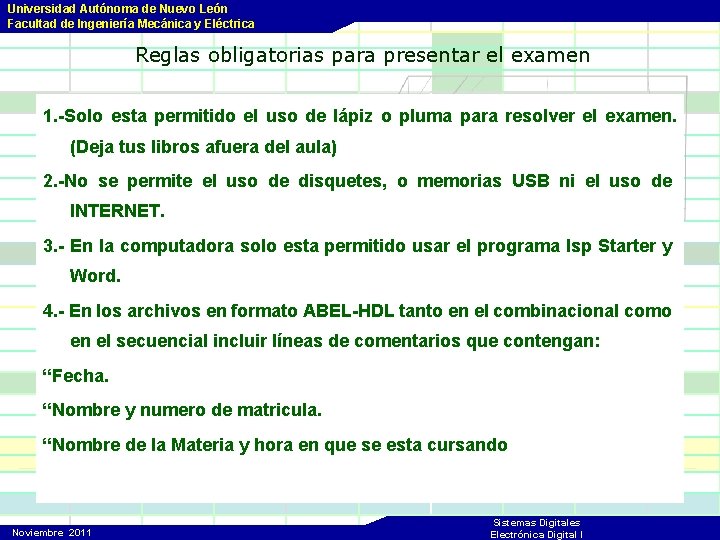

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 7 HF 0 Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica [7, ^HF]: >[0,](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-78.jpg)

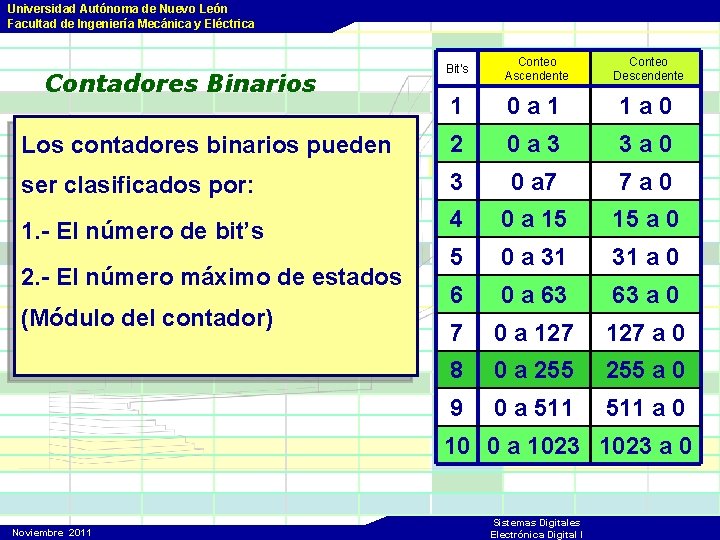

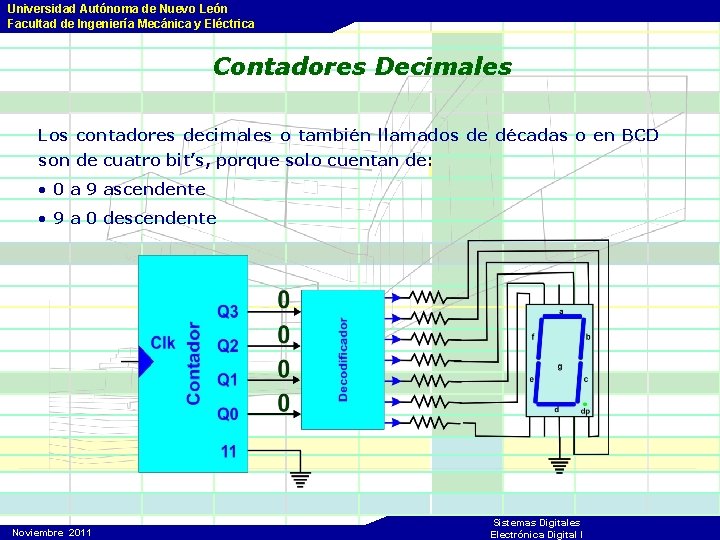

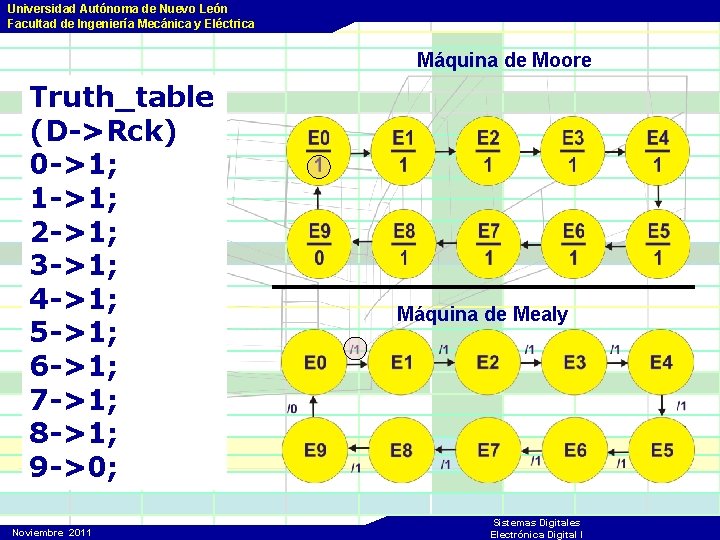

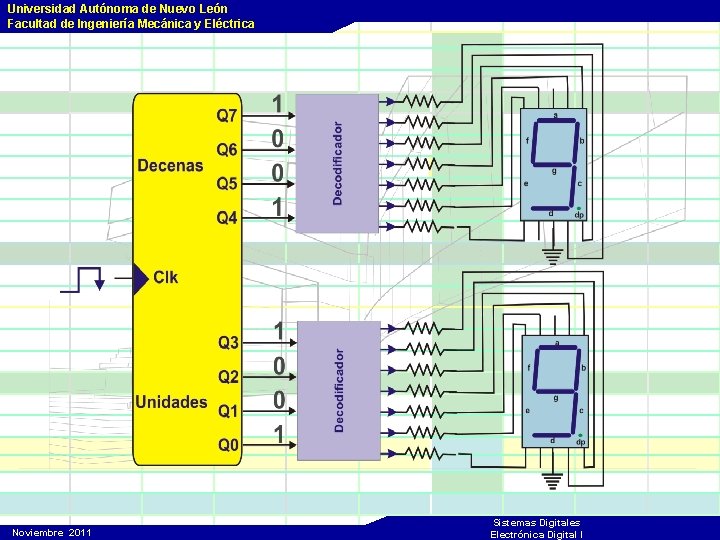

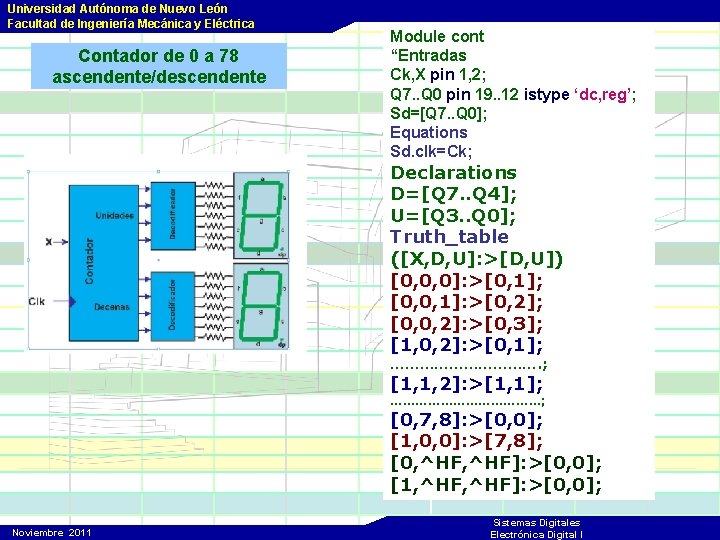

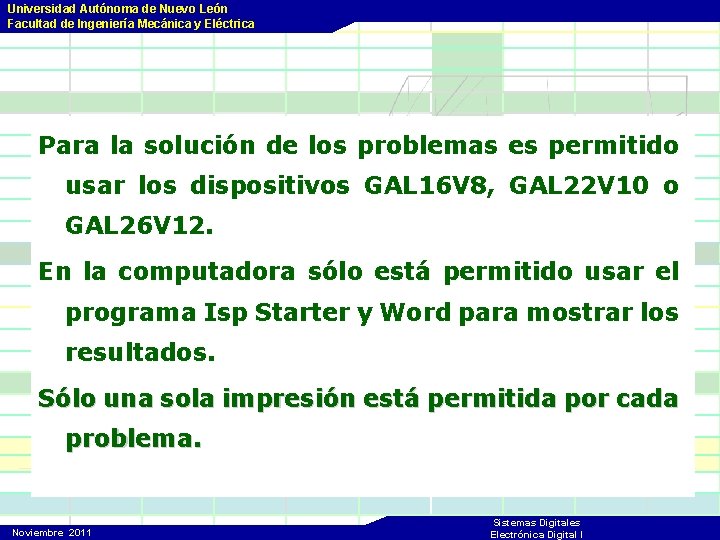

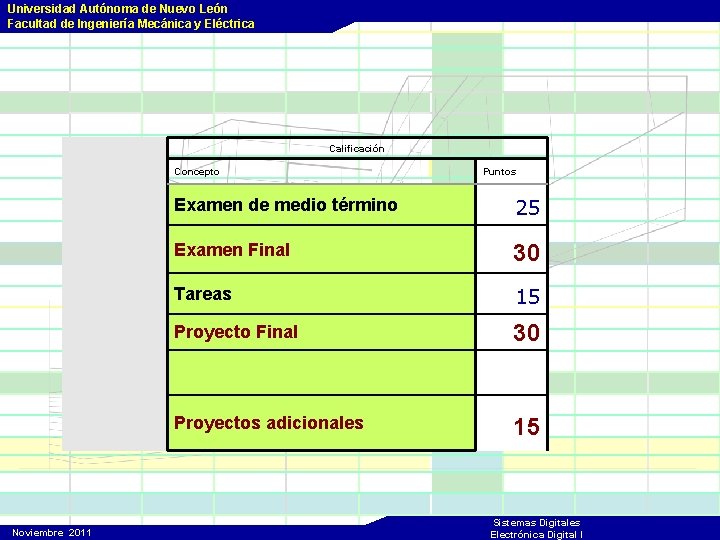

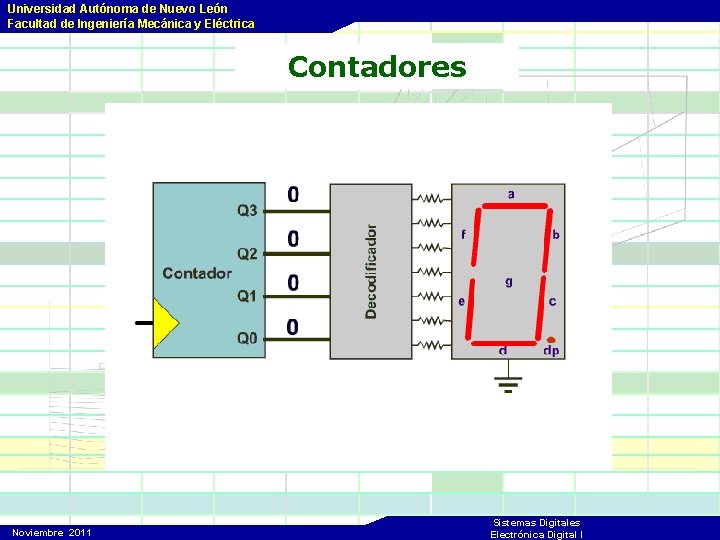

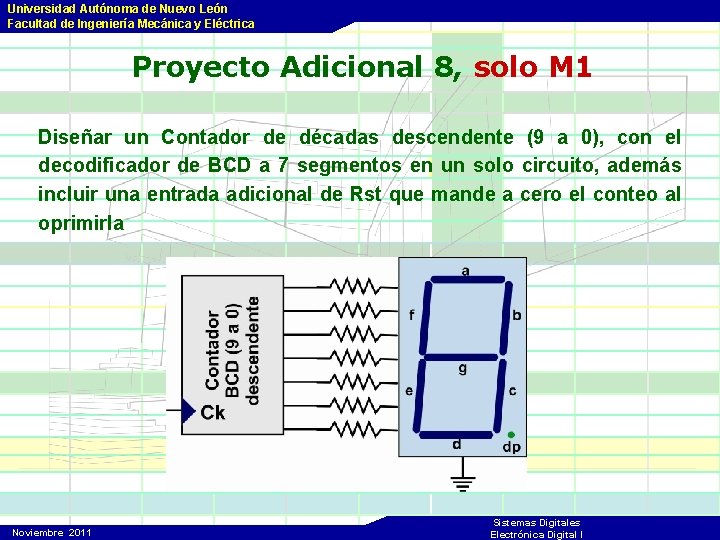

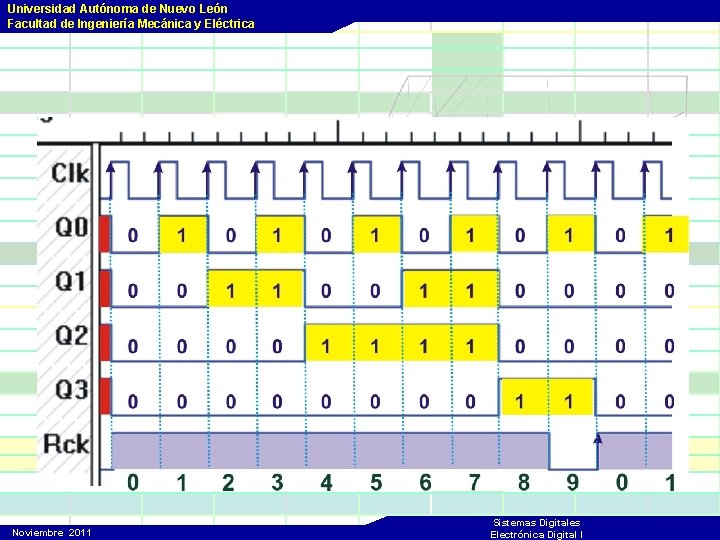

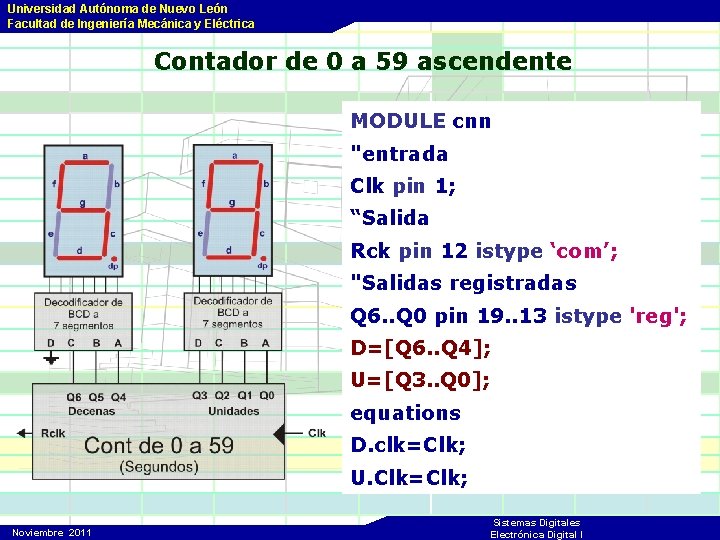

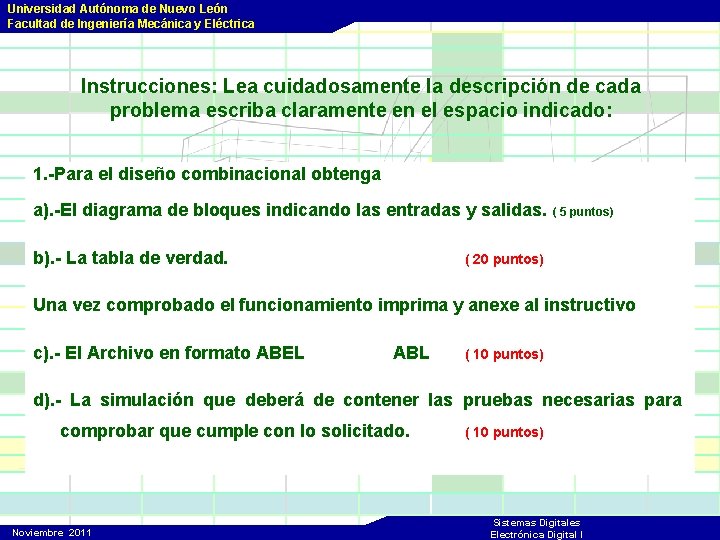

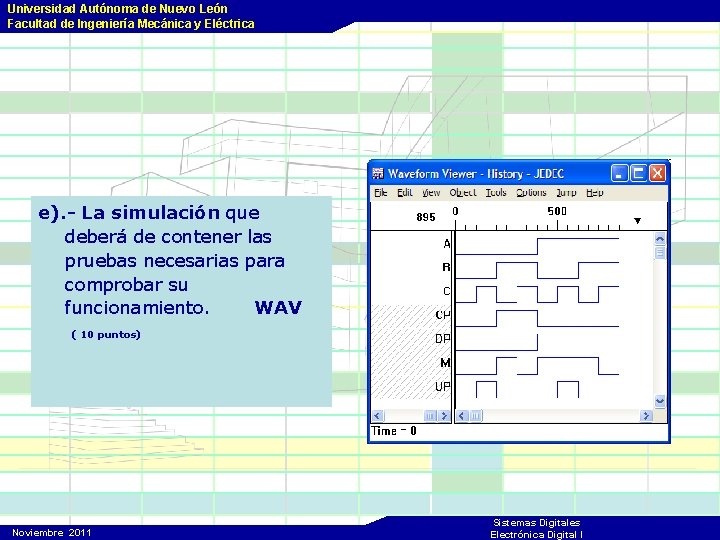

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica [7, ^HF]: >[0, 0]; Decenas 7 Unidades F 1 0 1 0 Clk Noviembre 2011 truth_table ([D, U]: >[D, U]) [7, ^HF]: >[0, 0]; [0, 0]: >[0, 1]; [0, 1]: >[0, 2]; [0, 2]: >[0, 3]; [0, 3]: >[0, 4]; [0, 4]: >[0, 5]; [0, 5]: >[0, 6]; [0, 6]: >[0, 7]; [0, 7]: >[0, 8]; [0, 8]: >[0, 9]; [0, 9]: >[1, 0]; [1, 0]: >[1, 1]; [1, 1]: >[1, 2]; [1, 2]: >[1, 3]; ………………… [5, 8]: >[5, 9]; [5, 9]: >[0, 0]; Sistemas Digitales Electrónica Digital I

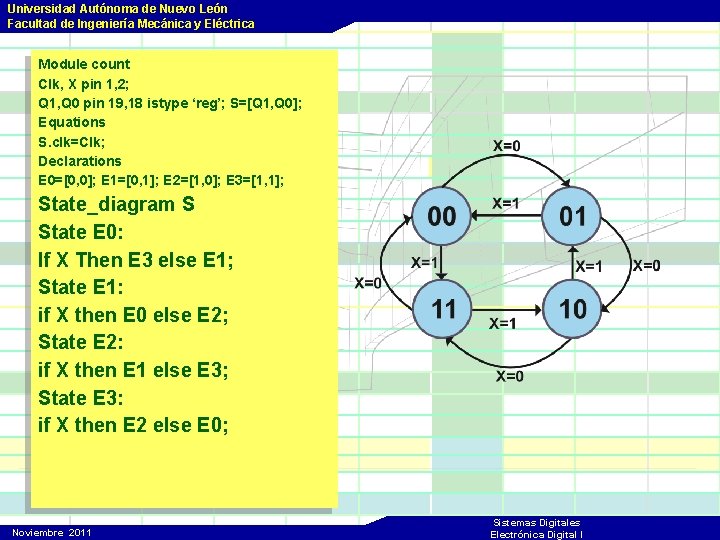

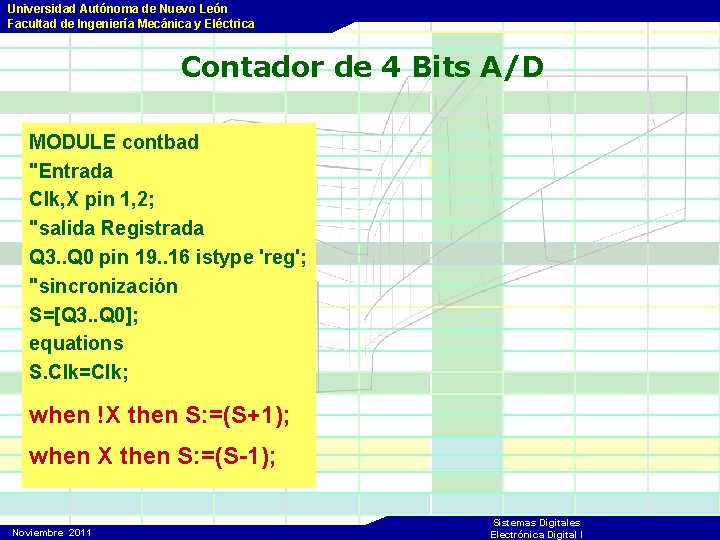

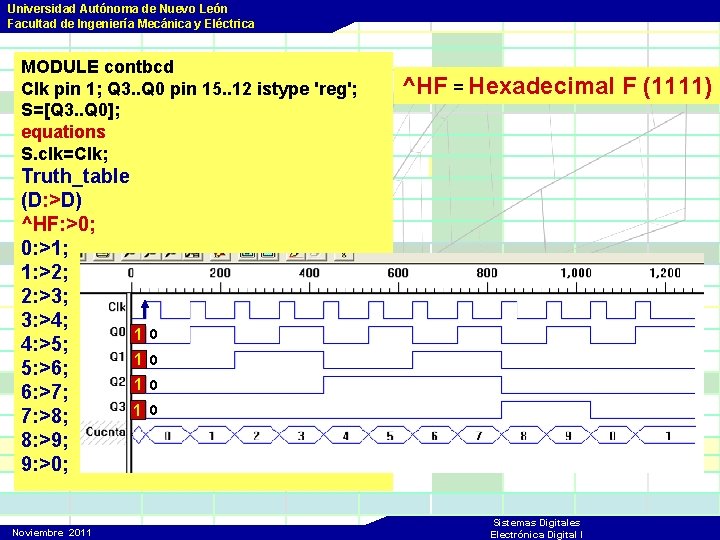

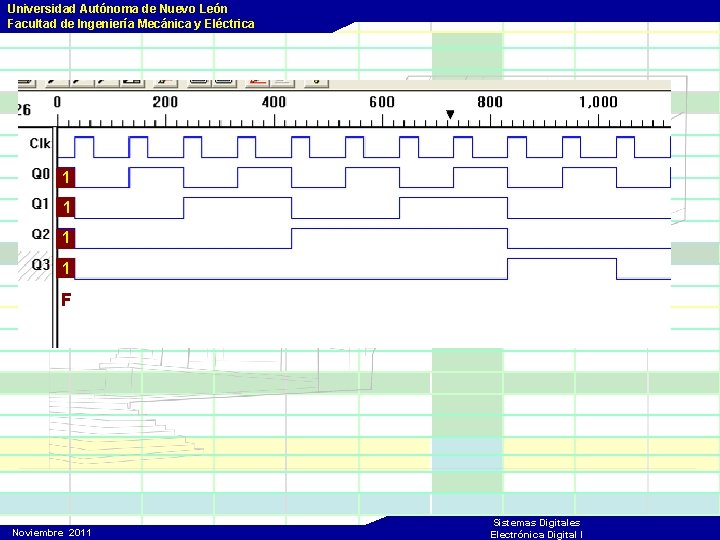

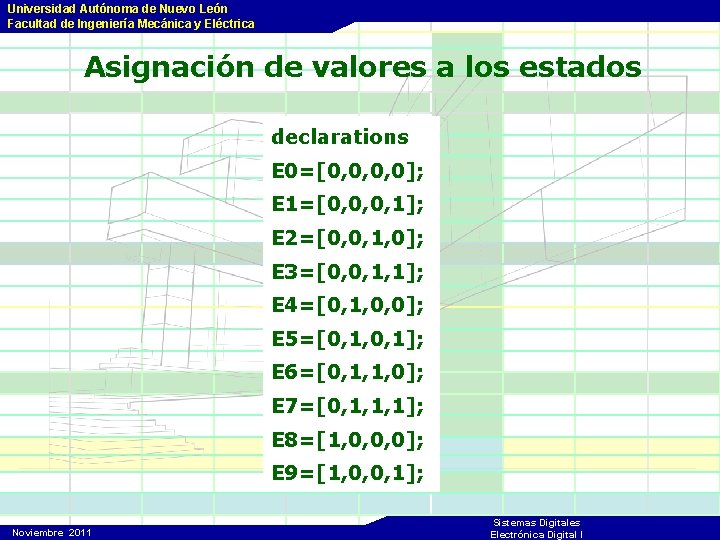

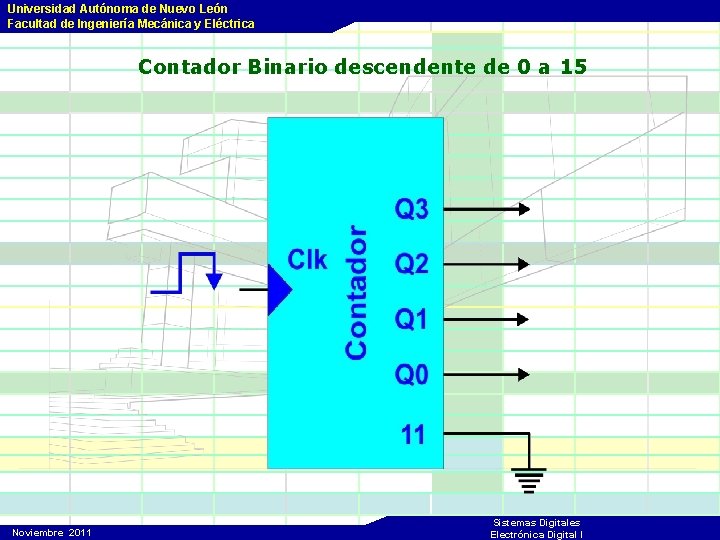

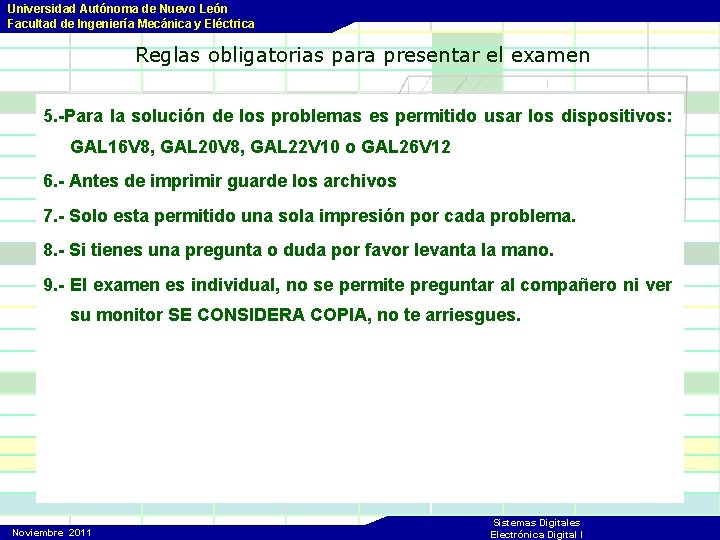

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Truthtable D URck Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Truth_table ([D, U]->[Rck])](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-79.jpg)

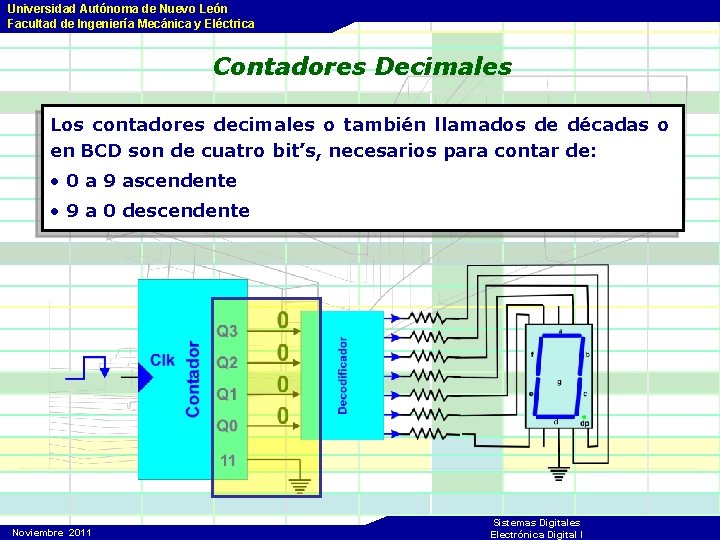

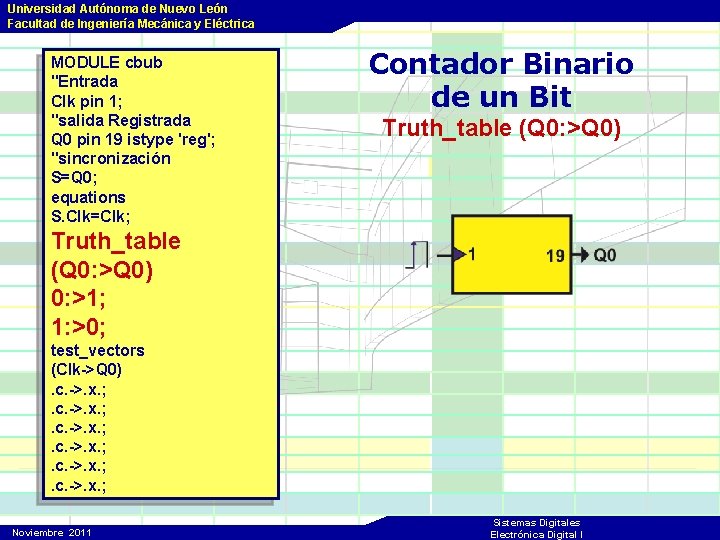

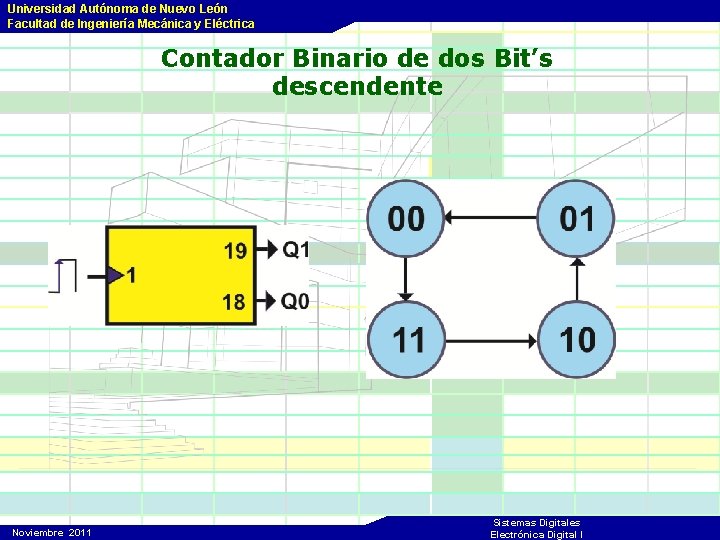

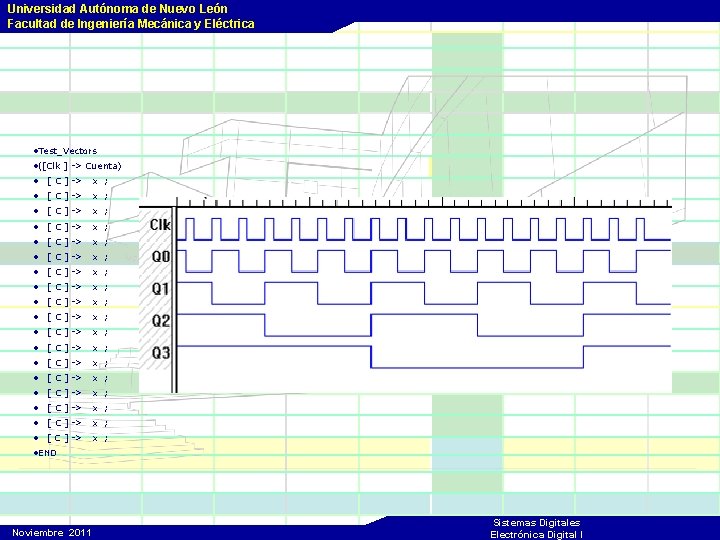

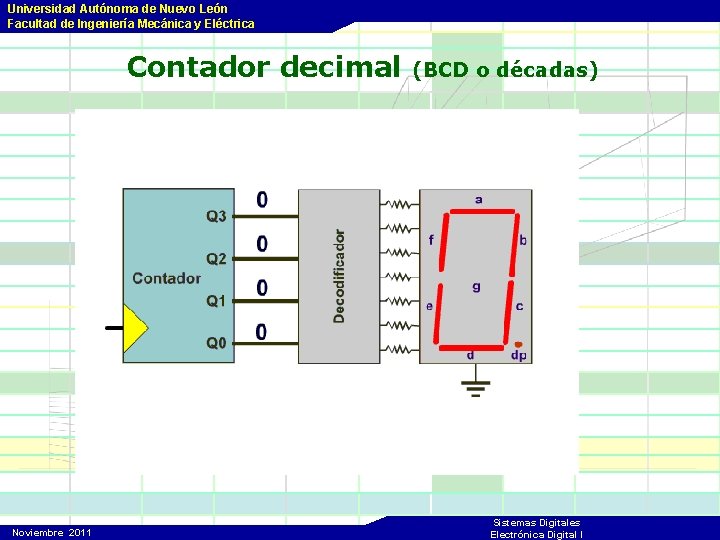

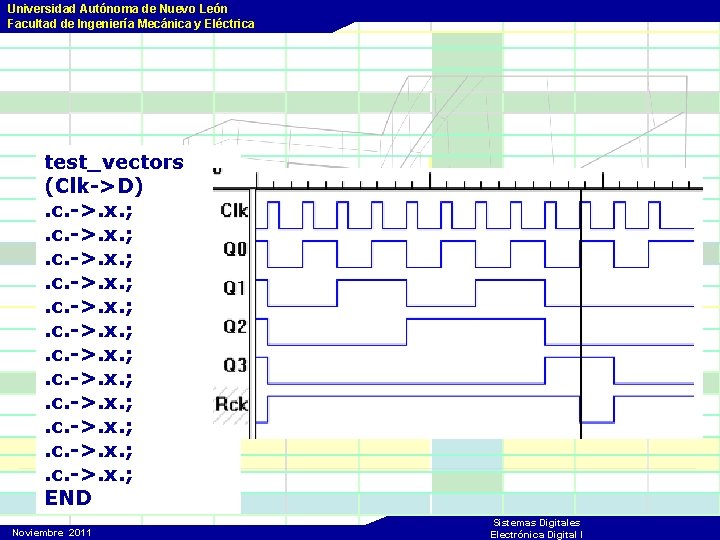

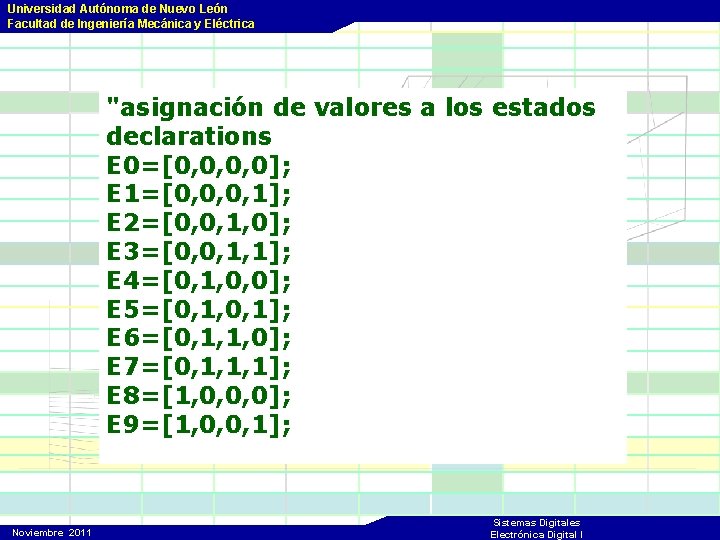

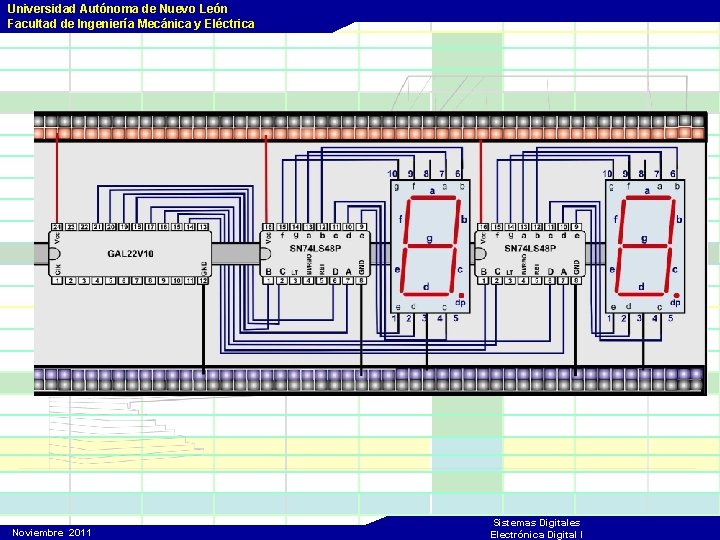

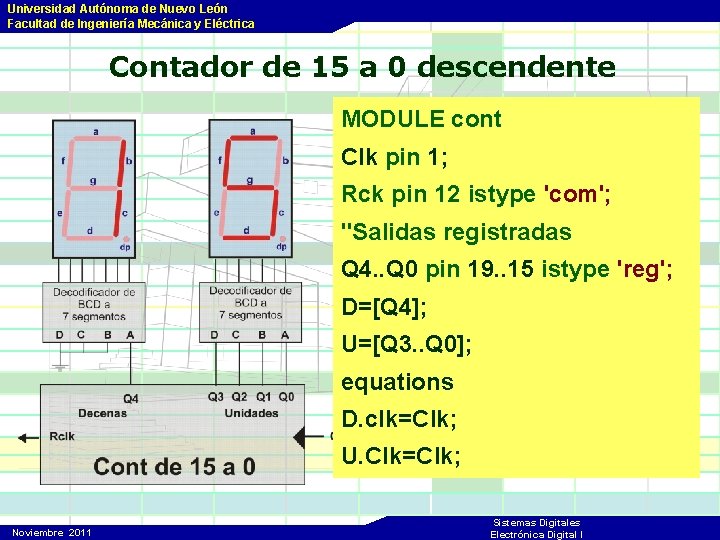

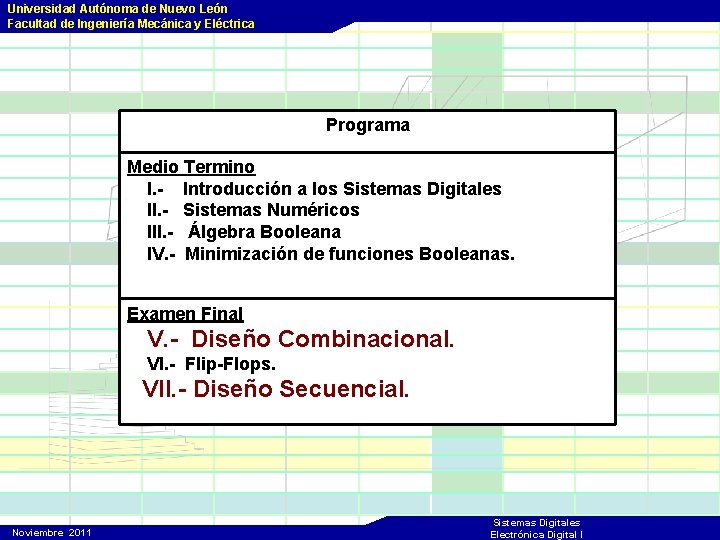

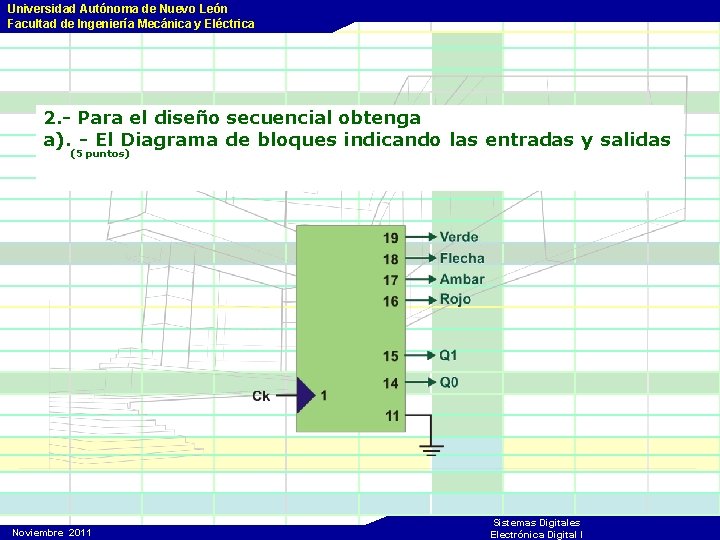

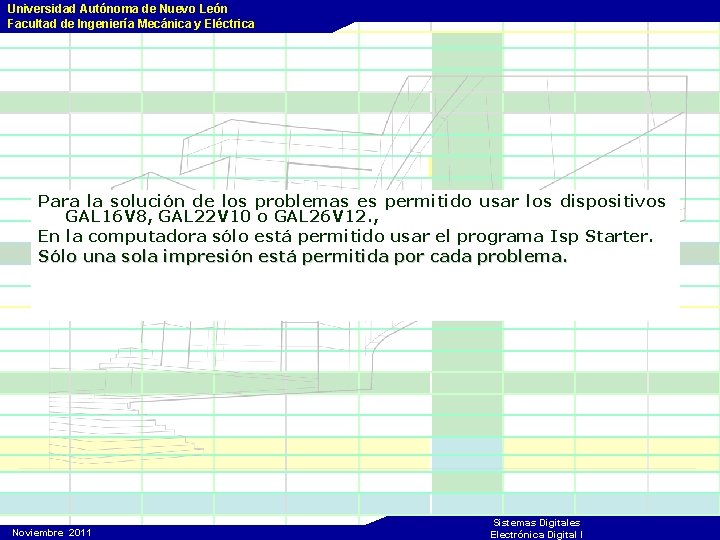

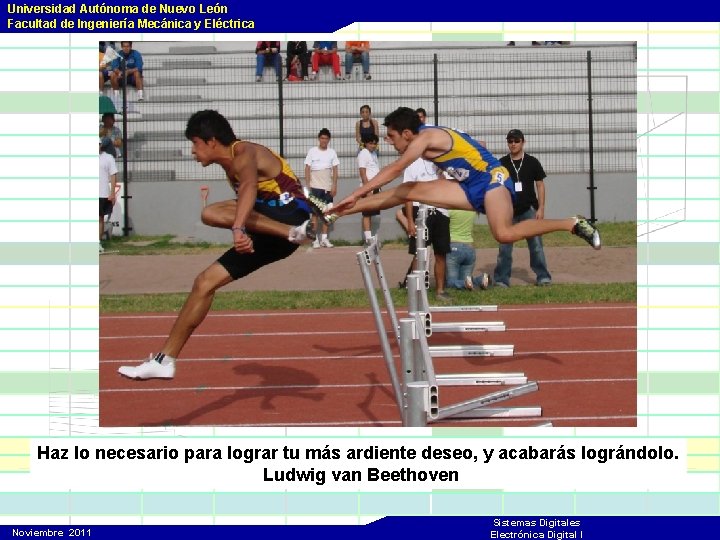

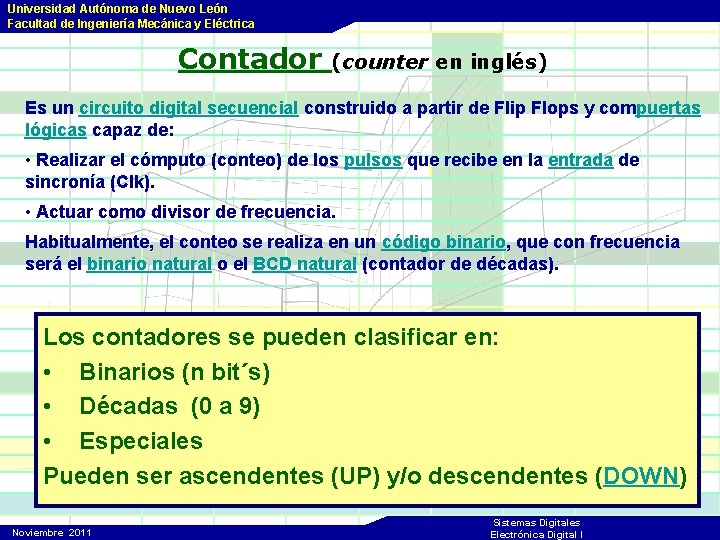

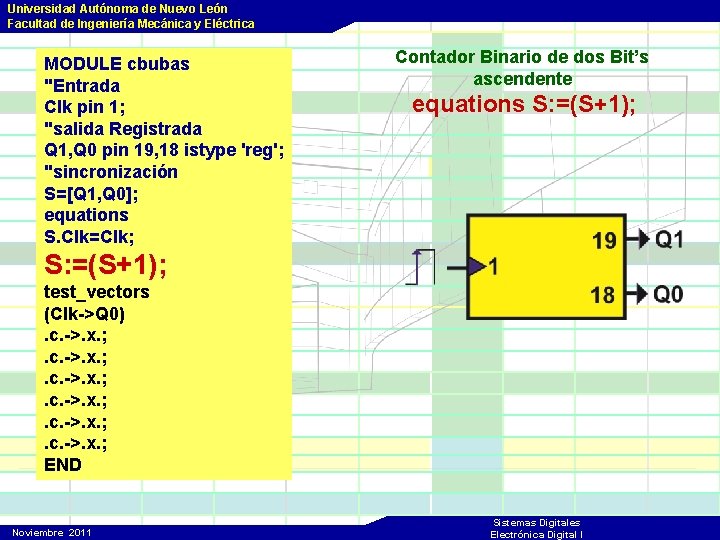

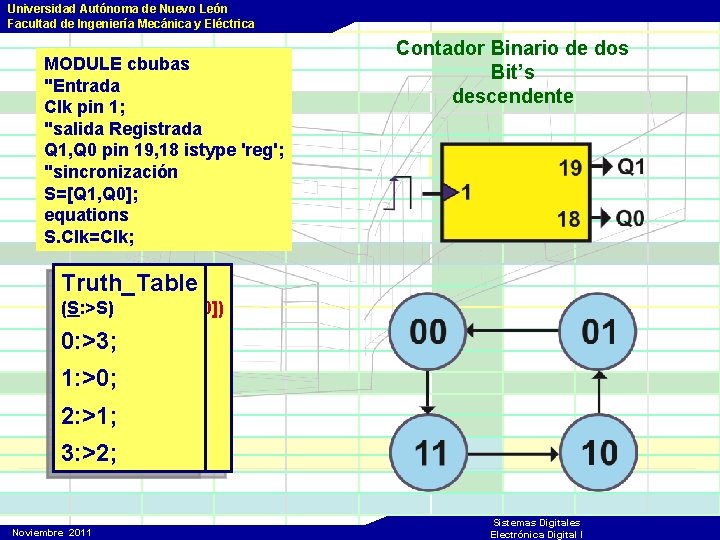

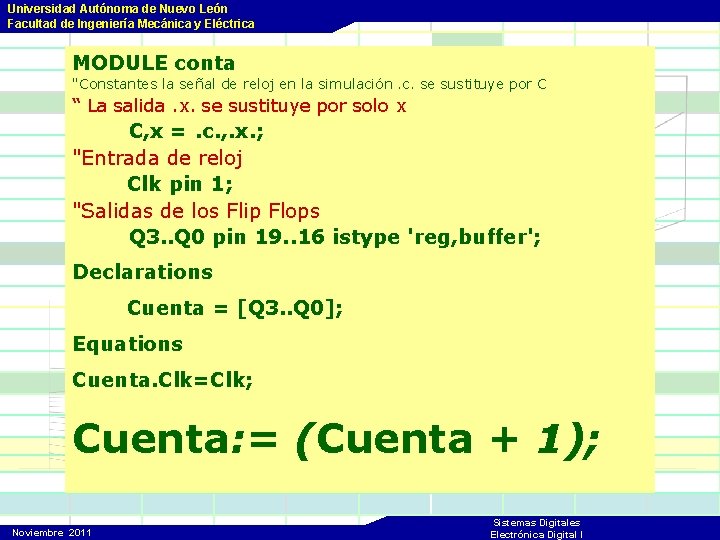

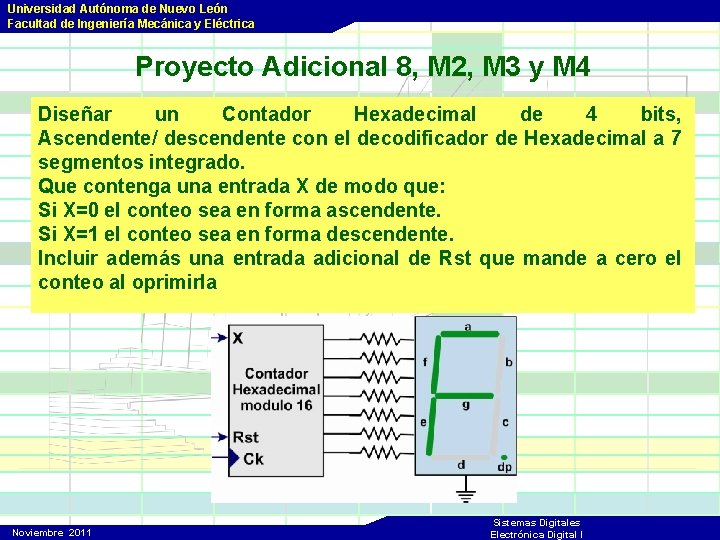

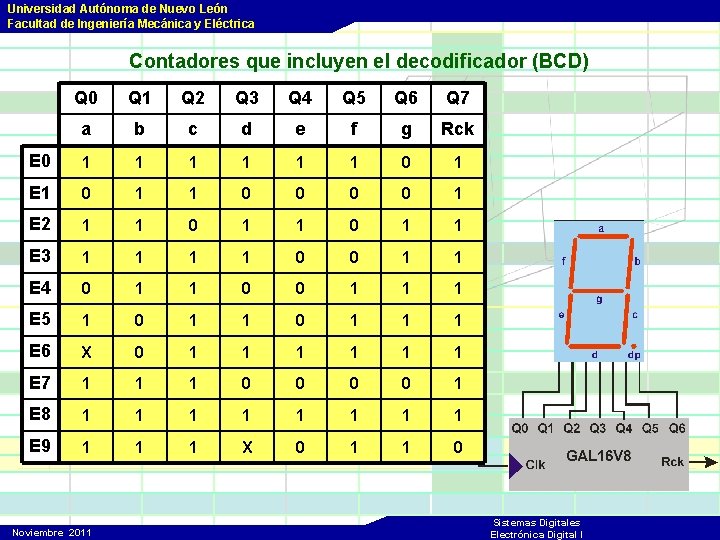

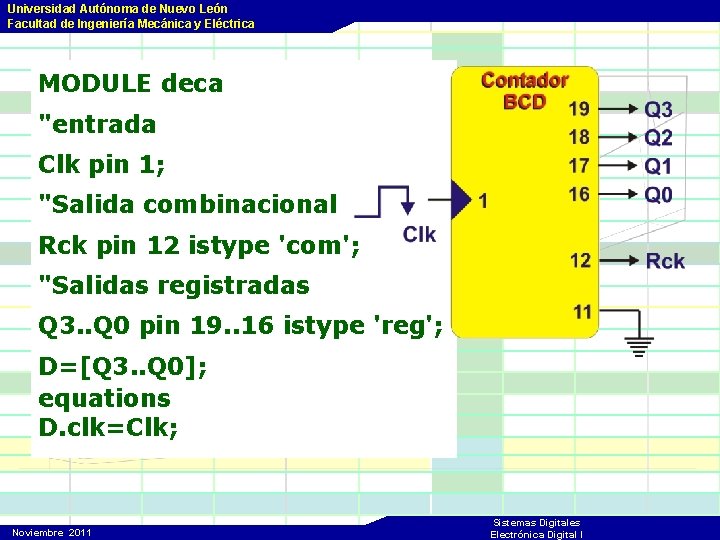

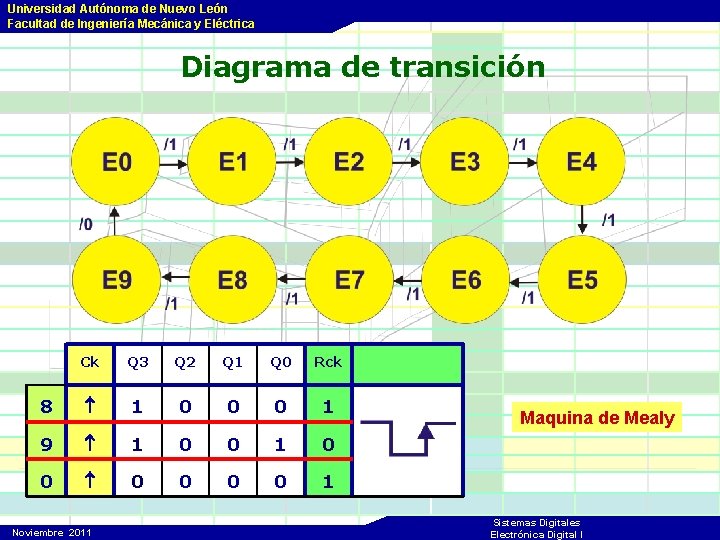

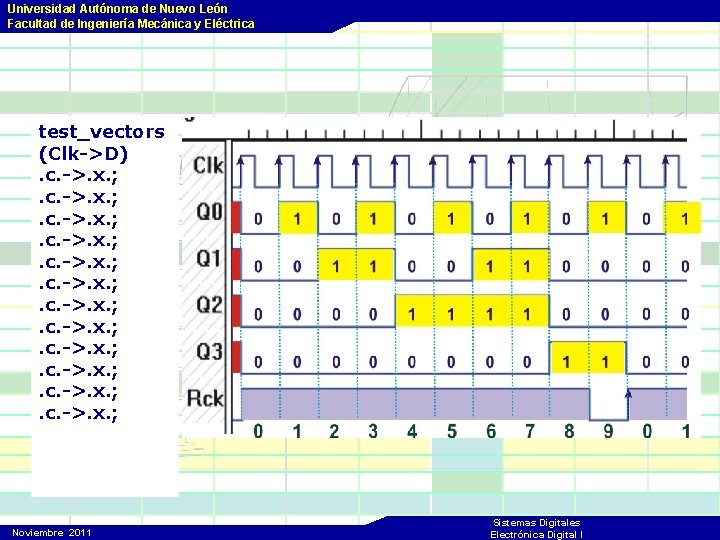

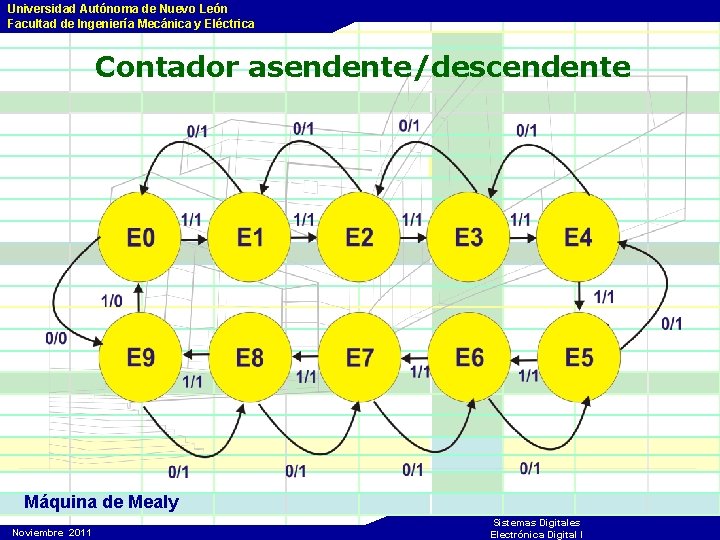

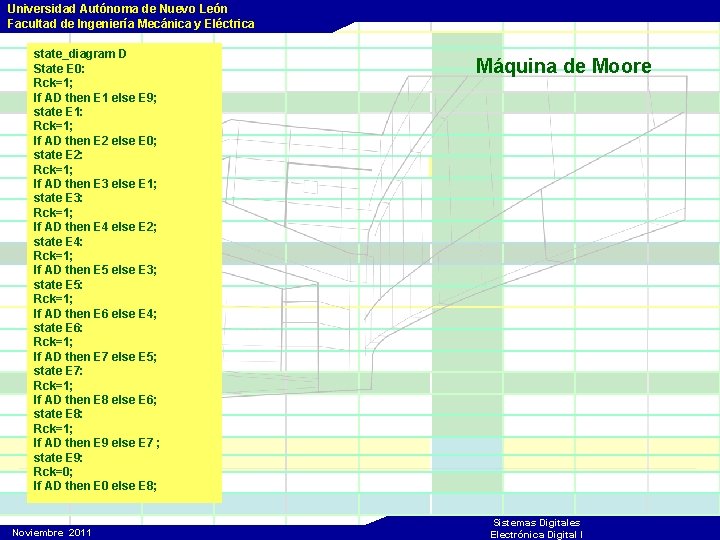

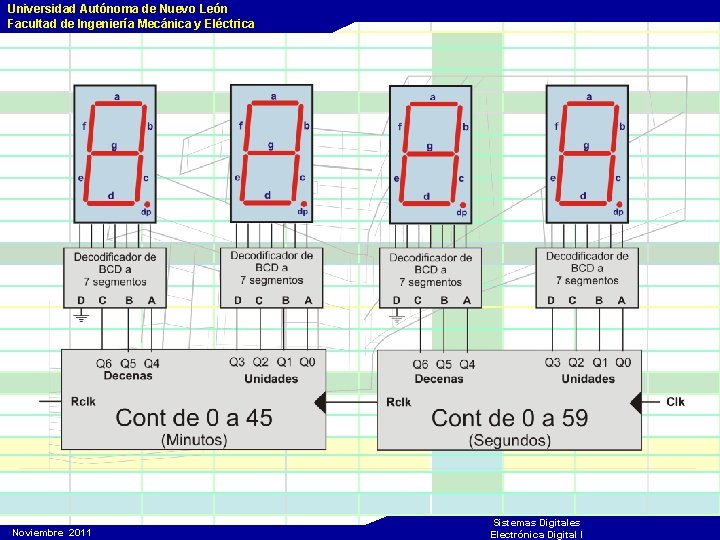

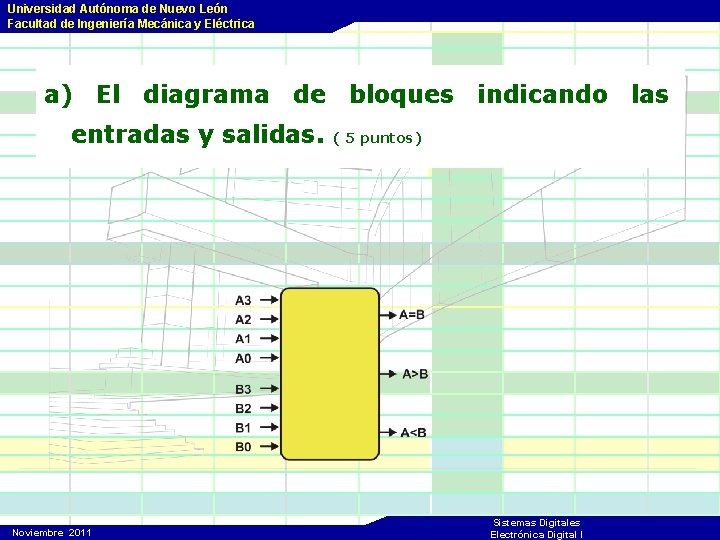

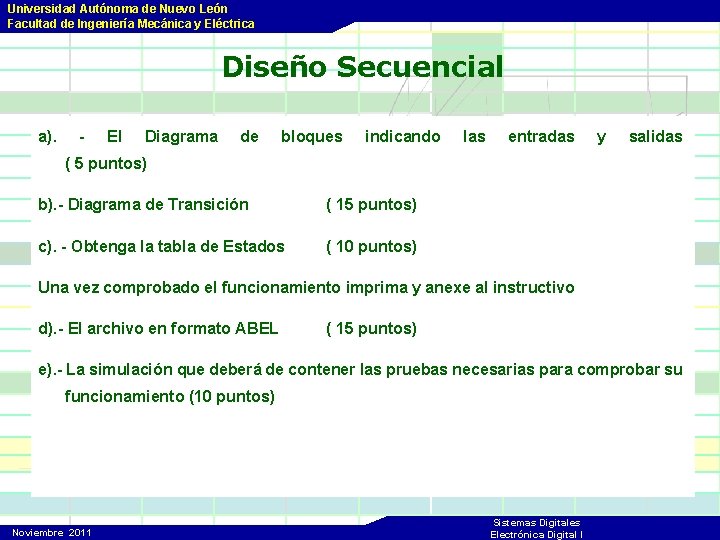

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Truth_table ([D, U]->[Rck]) [5, 9]->1; Todo lo no listado en Truth_table la salida toma el valor de cero test_vectors (Clk->Rck). c. ->. x. ; Noviembre 2011 Sistemas Digitales Electrónica Digital I

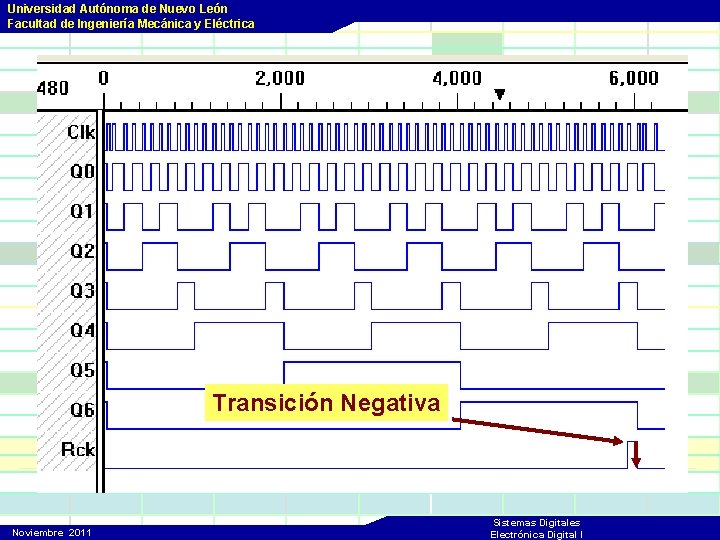

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Transición Negativa Noviembre 2011 Sistemas Digitales Electrónica Digital I

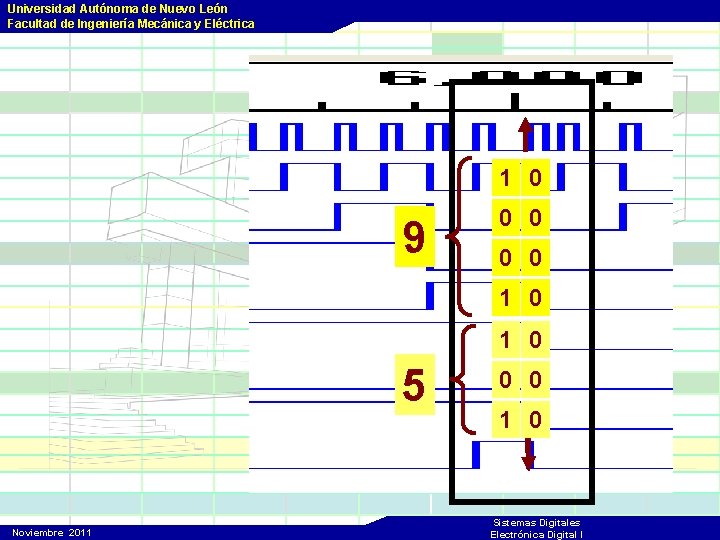

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 1 0 9 0 0 1 0 5 Noviembre 2011 0 0 1 0 Sistemas Digitales Electrónica Digital I

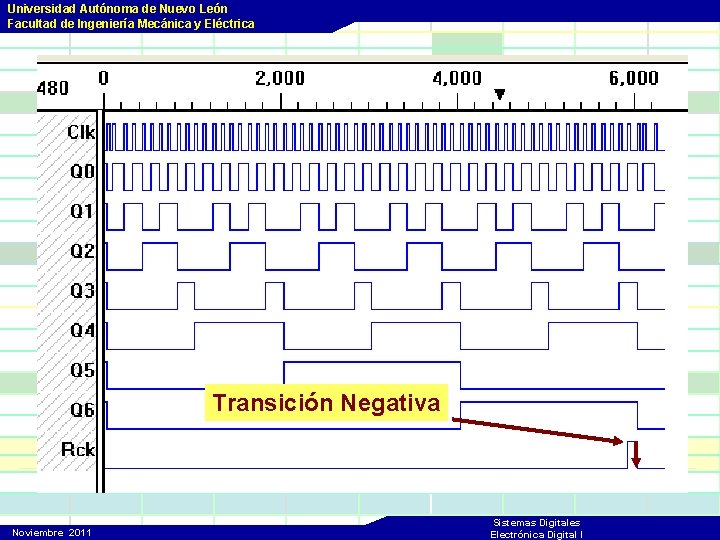

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truthtable D URck Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truth_table ([D, U]->[Rck])](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-82.jpg)

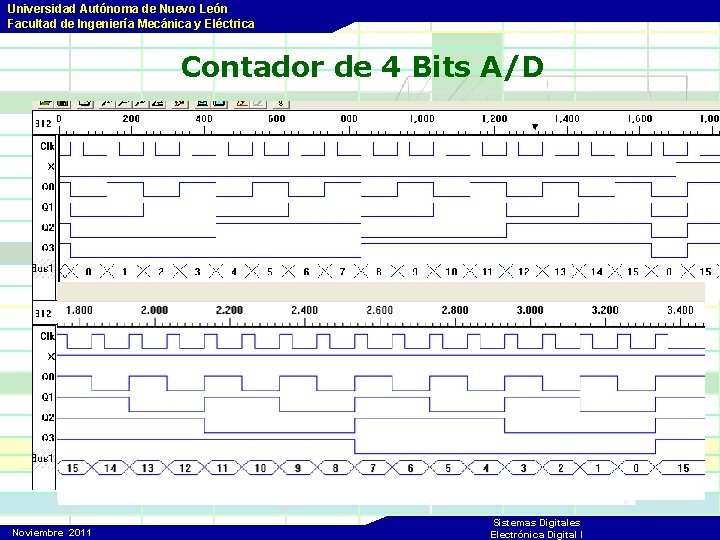

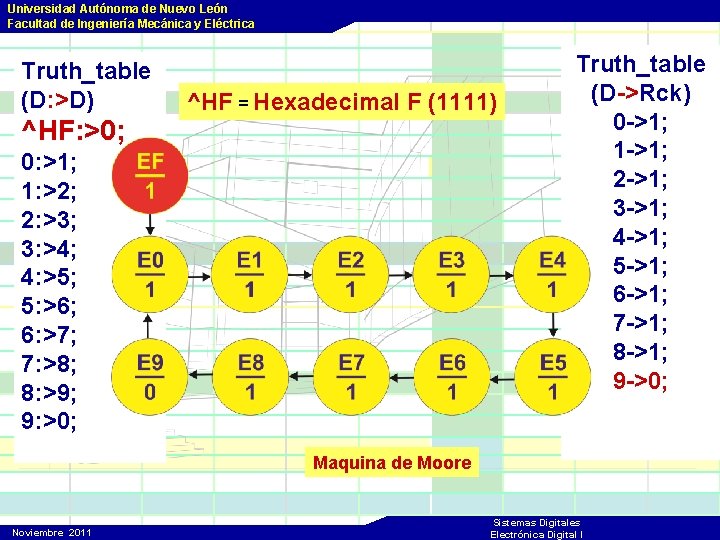

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truth_table ([D, U]->[Rck]) [0, 0]->[1]; [0, 1]->[1]; [0, 2]->[1]; [0, 3]->[1]; [0, 4]->[1]; [0, 5]->[1]; [0, 6]->[1]; --------[5, 4]->[1]; Transición Positiva [5, 5]->[1]; [5, 6]->[1]; [5, 7]->[1]; [5, 8]->[1]; [5, 9]->[0]; Noviembre 2011 Sistemas Digitales Electrónica Digital I

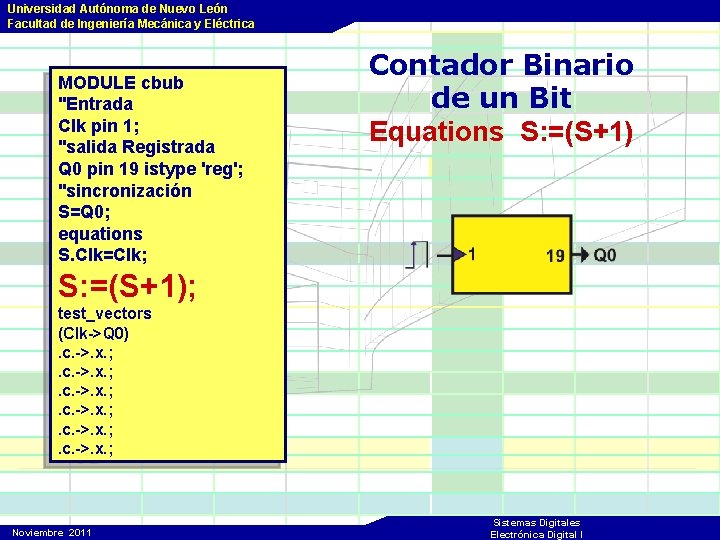

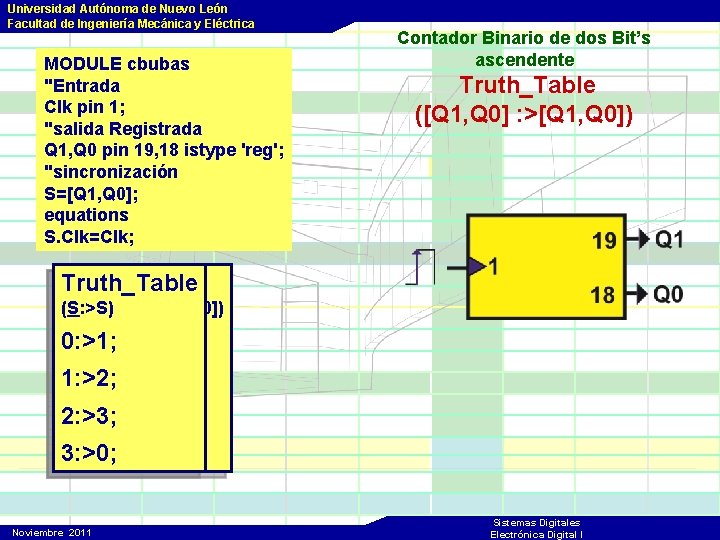

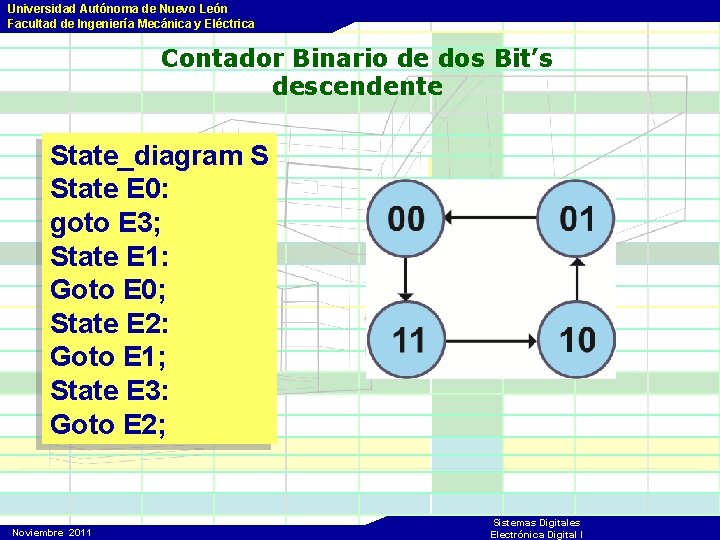

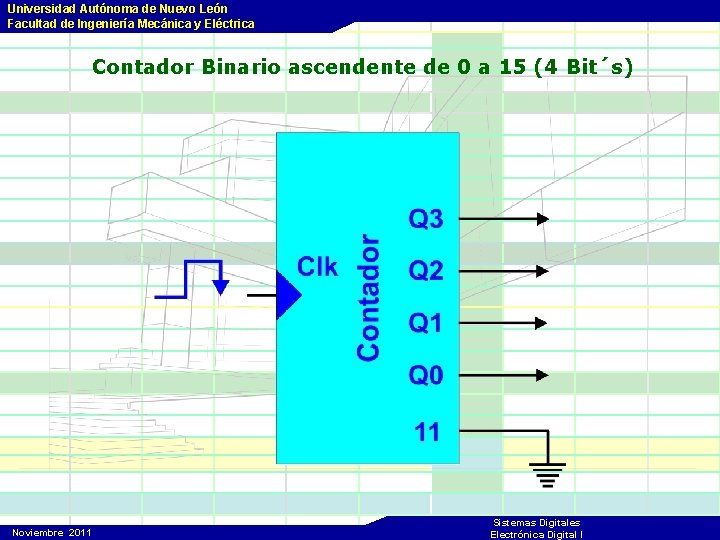

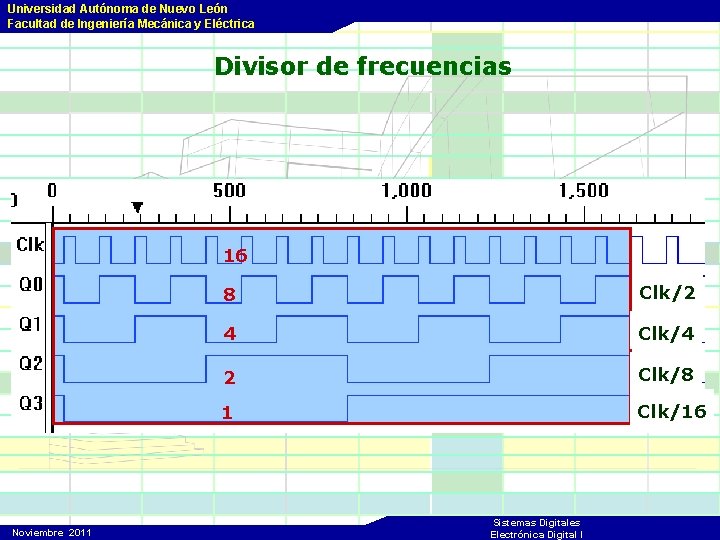

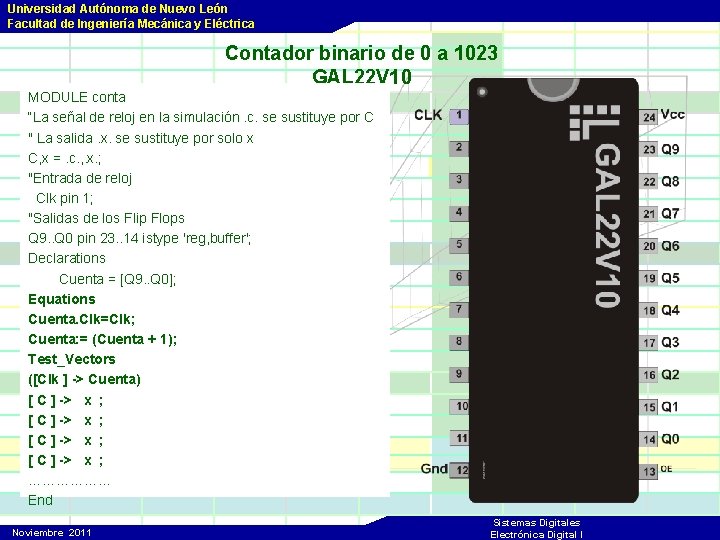

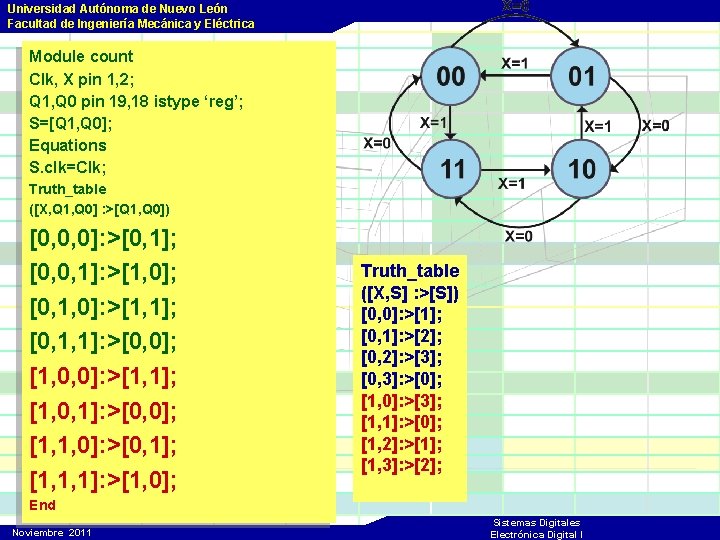

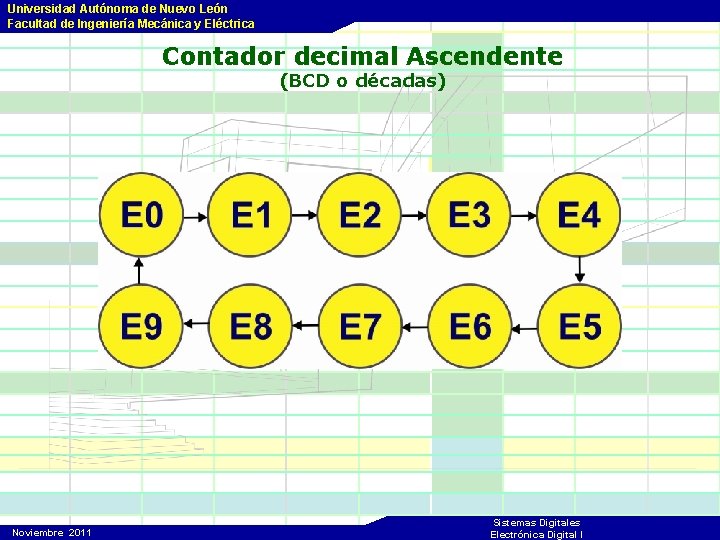

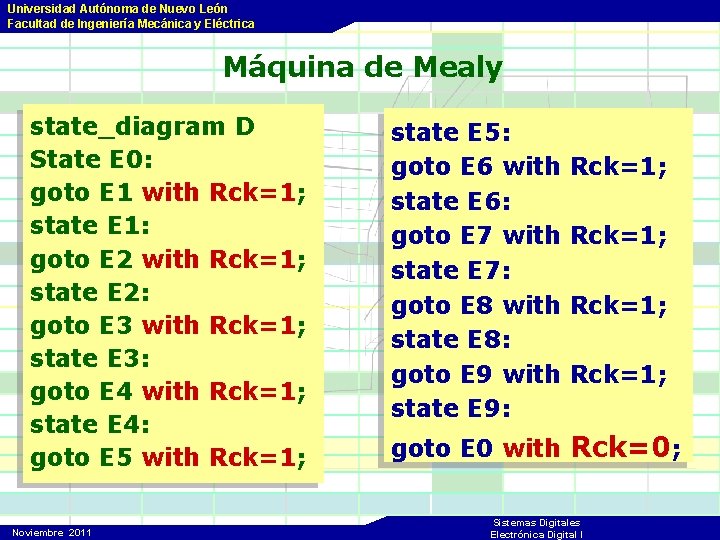

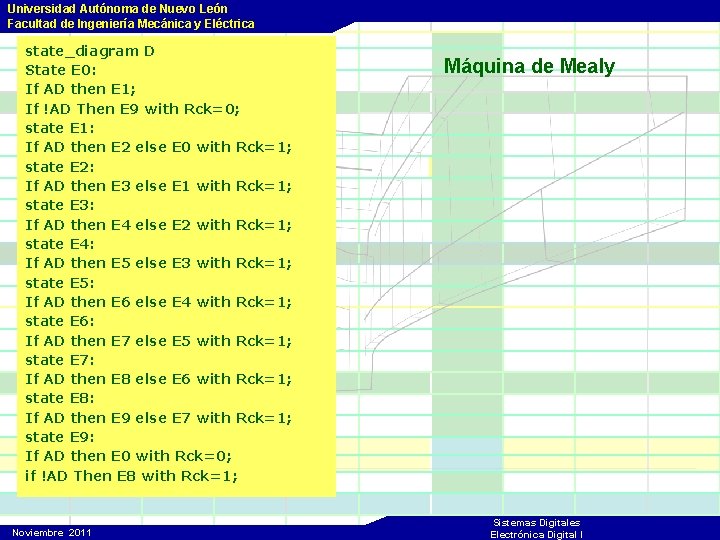

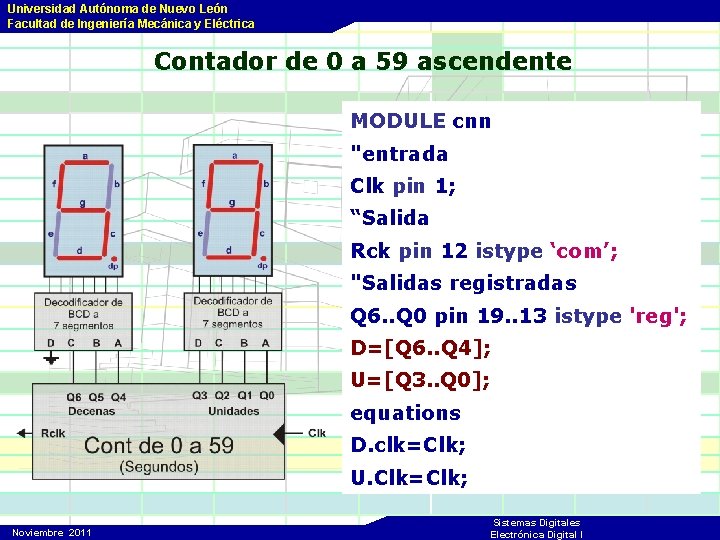

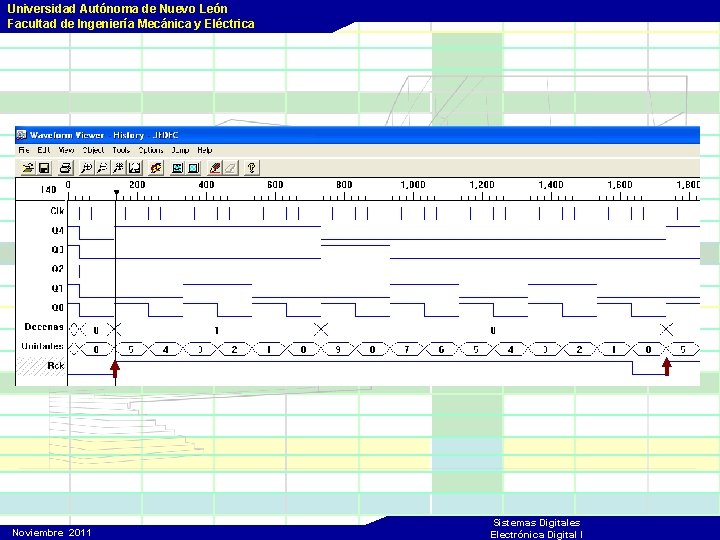

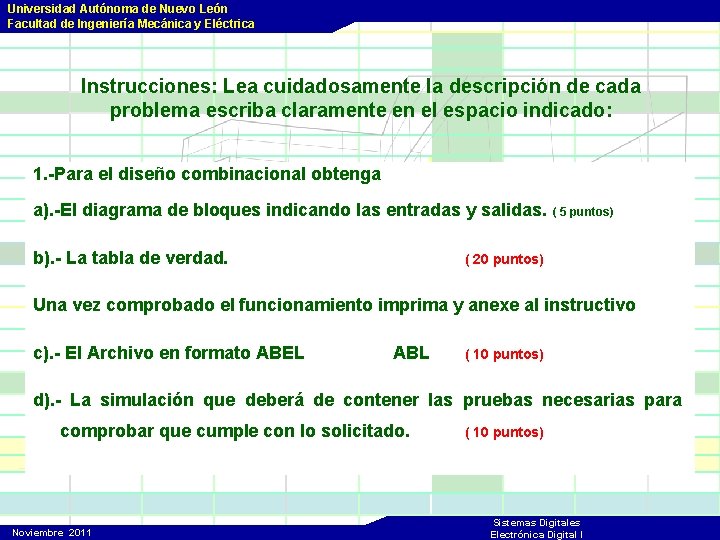

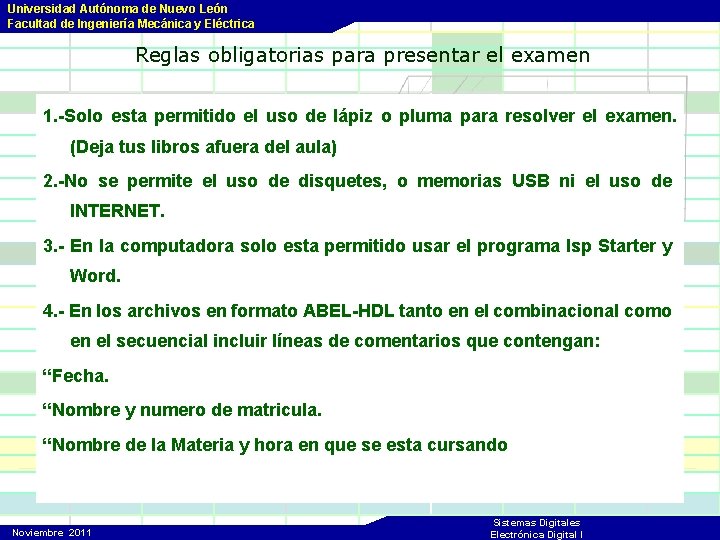

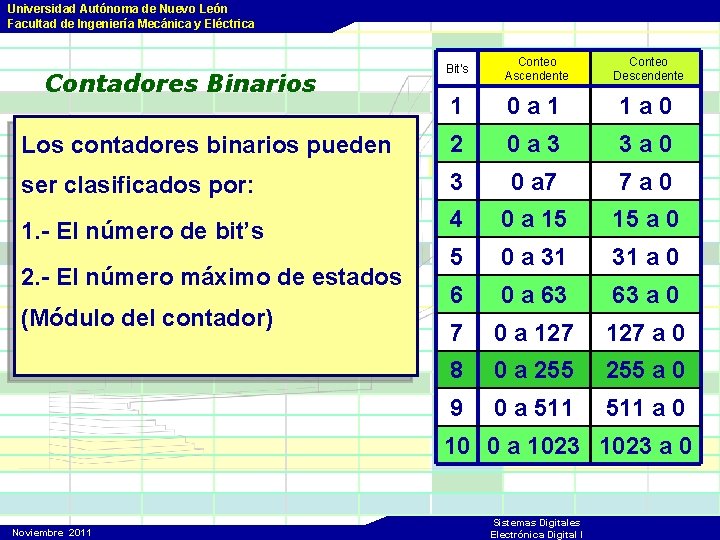

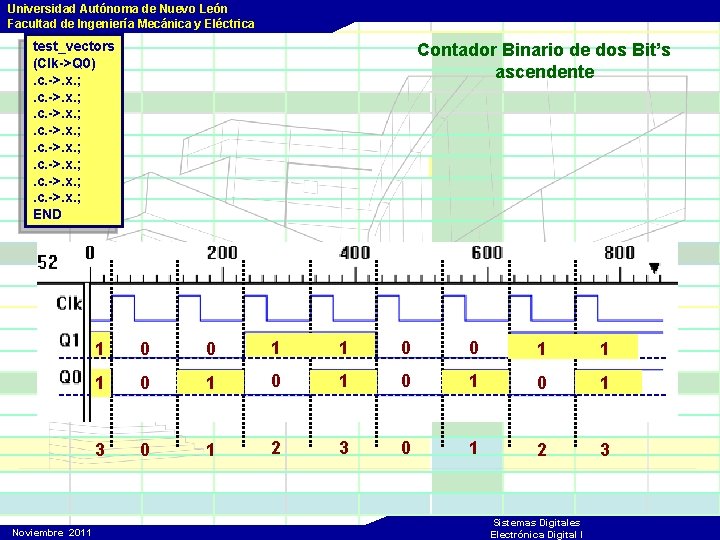

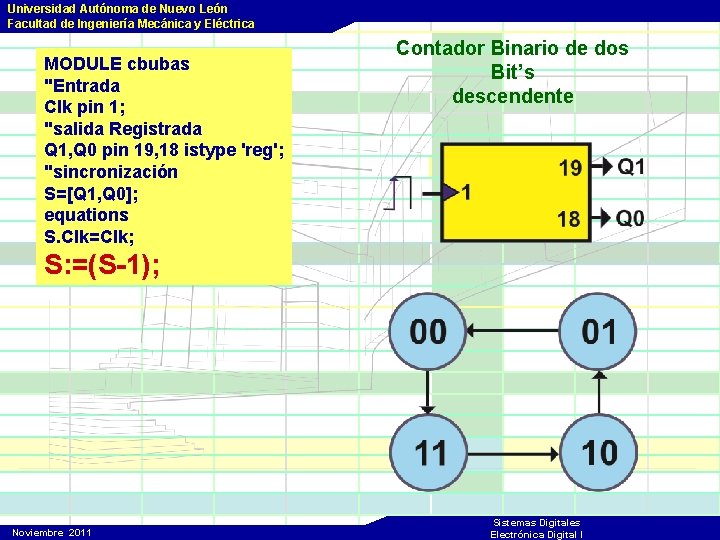

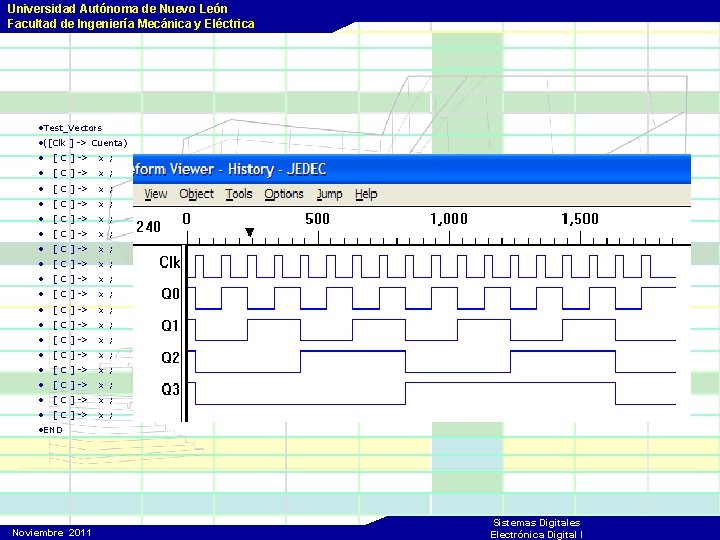

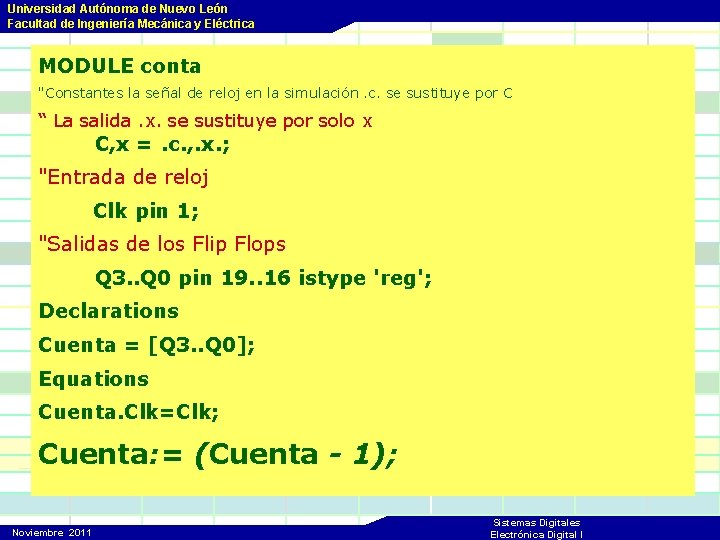

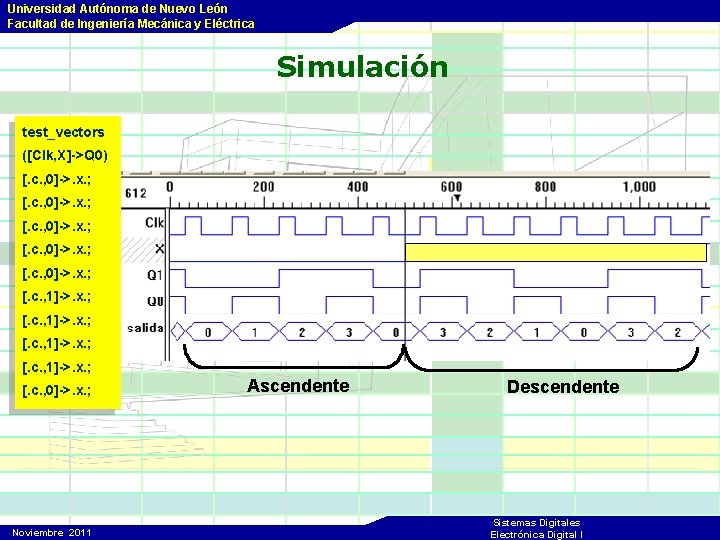

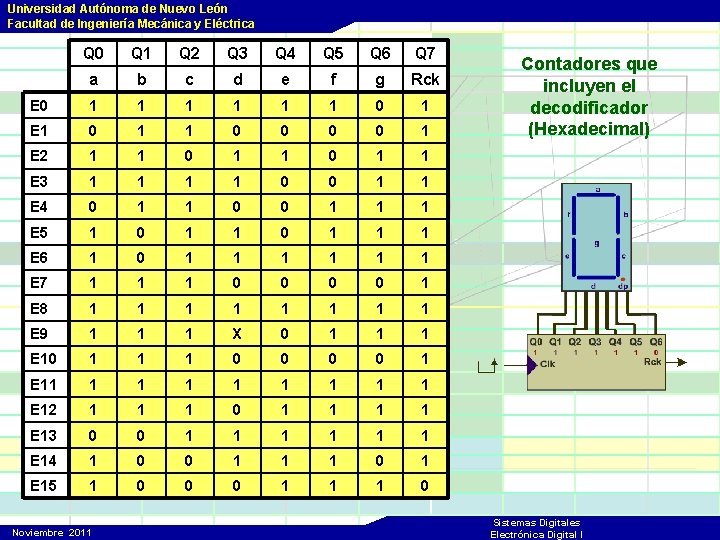

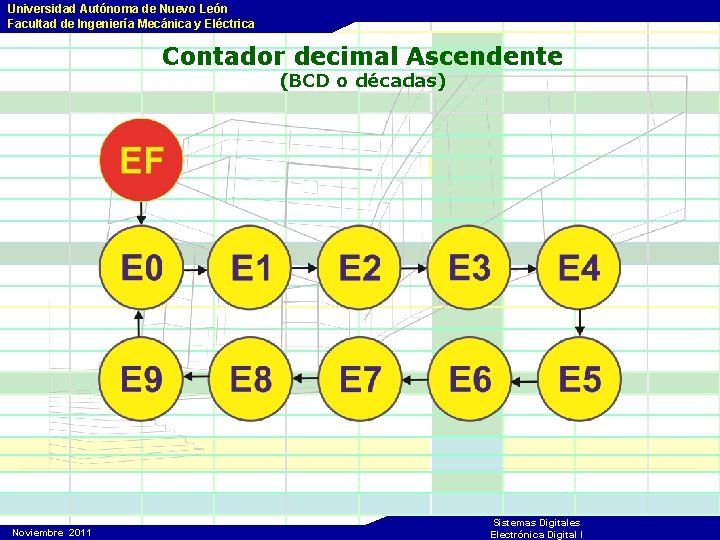

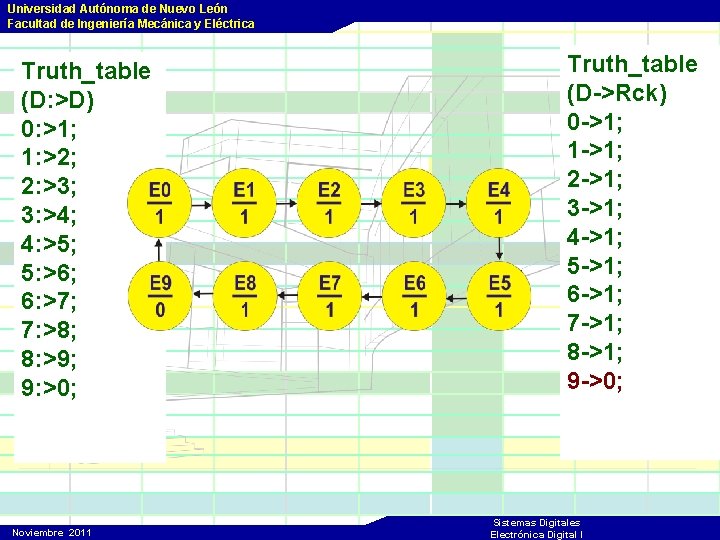

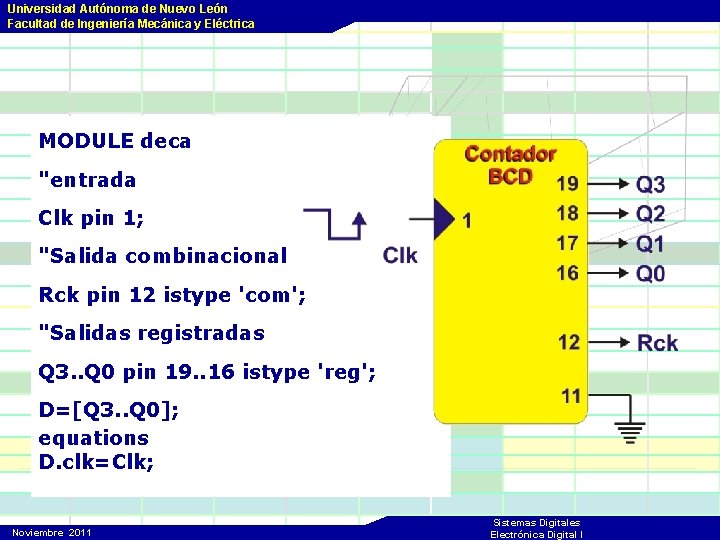

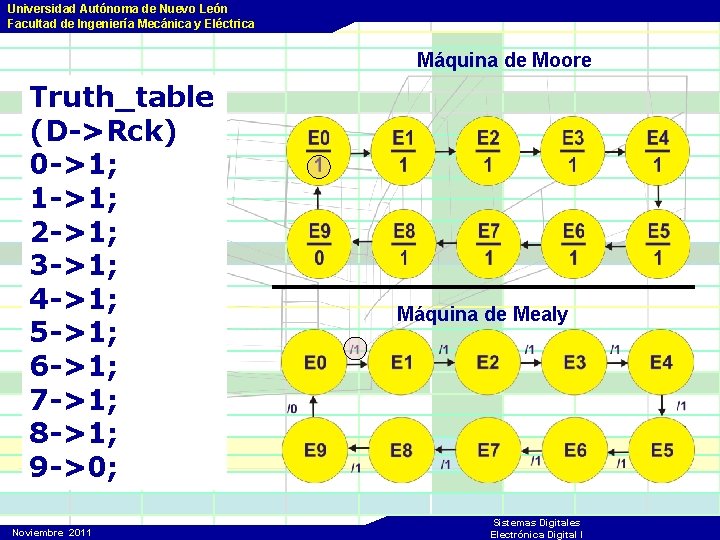

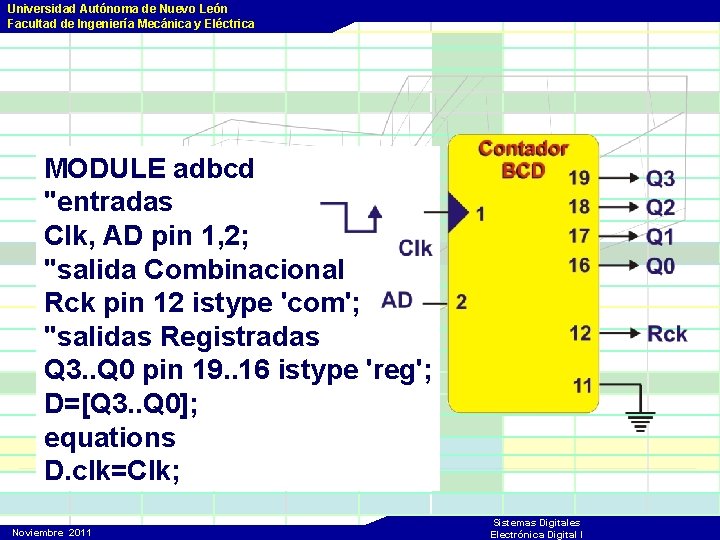

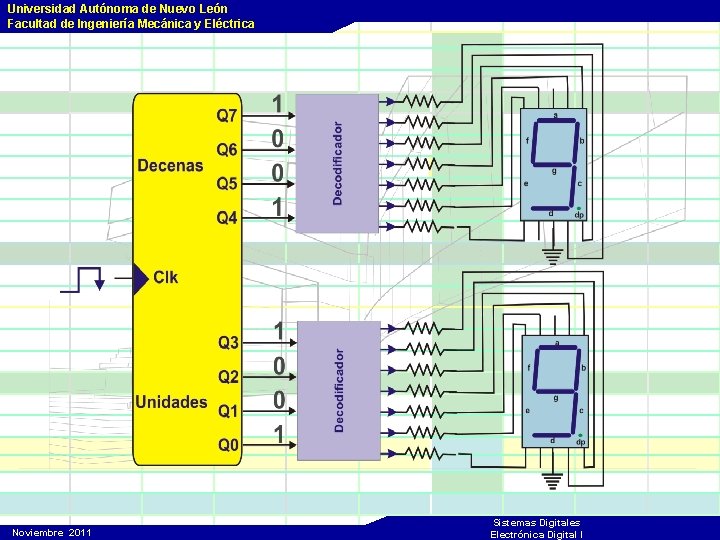

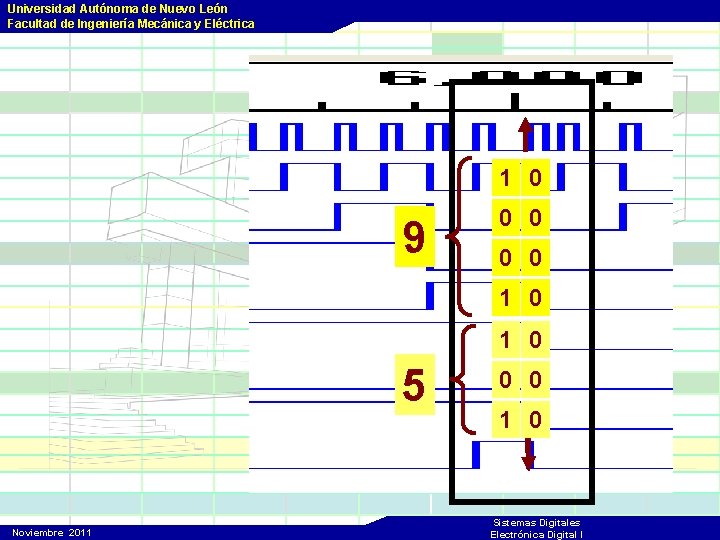

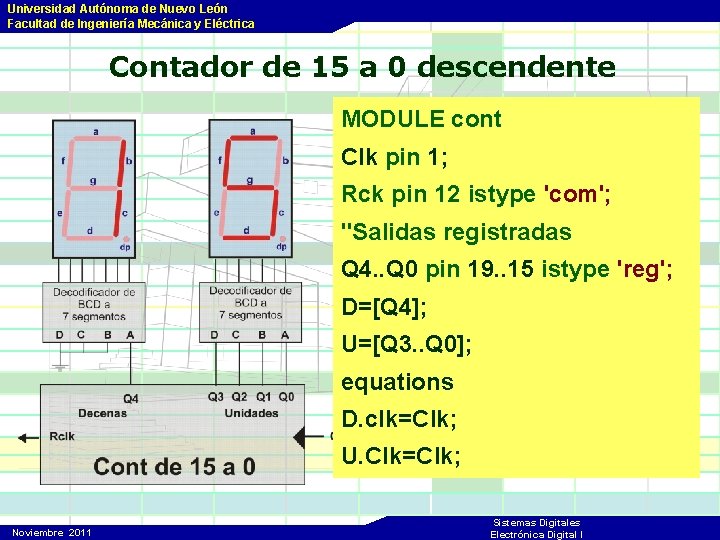

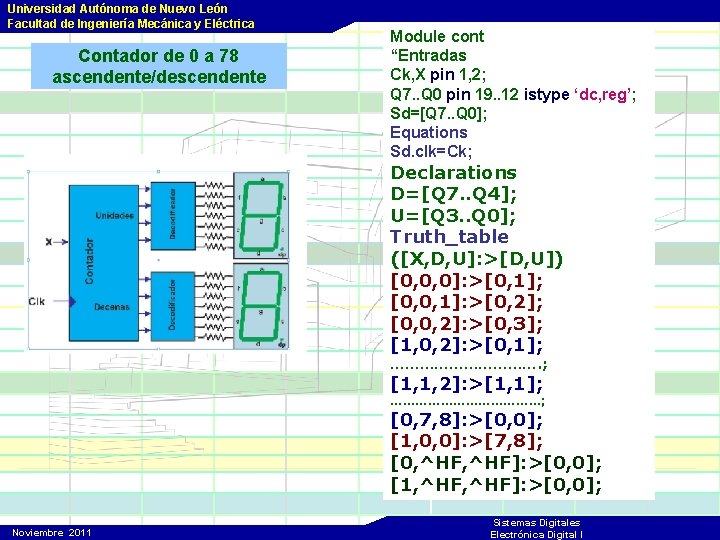

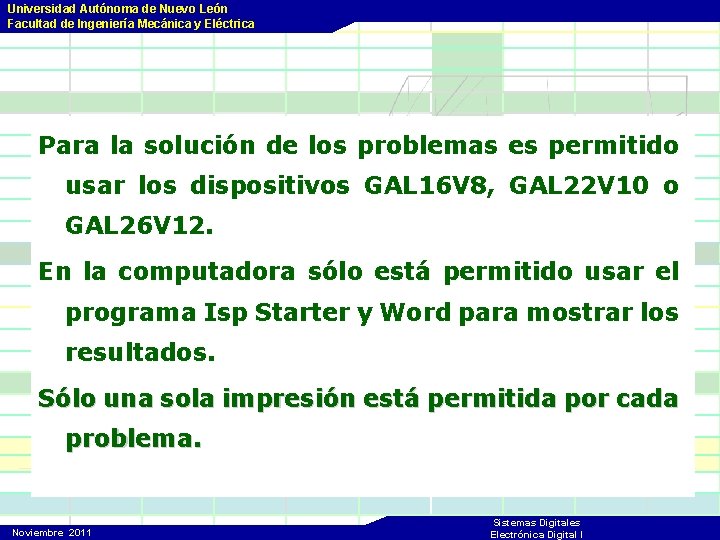

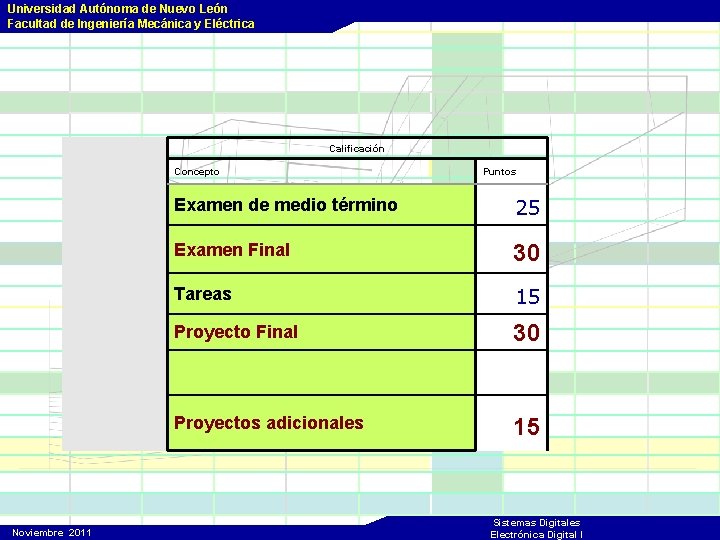

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 15 a 0 descendente MODULE cont Clk pin 1; Rck pin 12 istype 'com'; "Salidas registradas Q 4. . Q 0 pin 19. . 15 istype 'reg'; D=[Q 4]; U=[Q 3. . Q 0]; equations D. clk=Clk; U. Clk=Clk; Noviembre 2011 Sistemas Digitales Electrónica Digital I

![Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truthtable D U Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truth_table ([D, U]:](https://slidetodoc.com/presentation_image_h2/9ffc01b3151bd4b93a416a21da3b6d52/image-84.jpg)

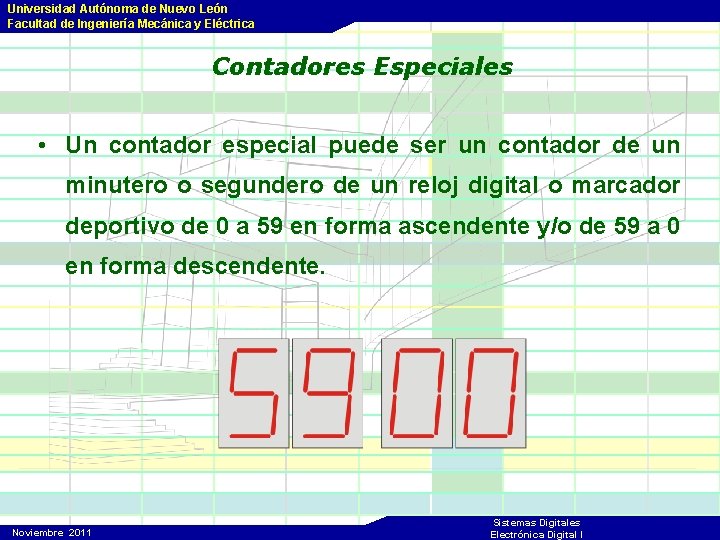

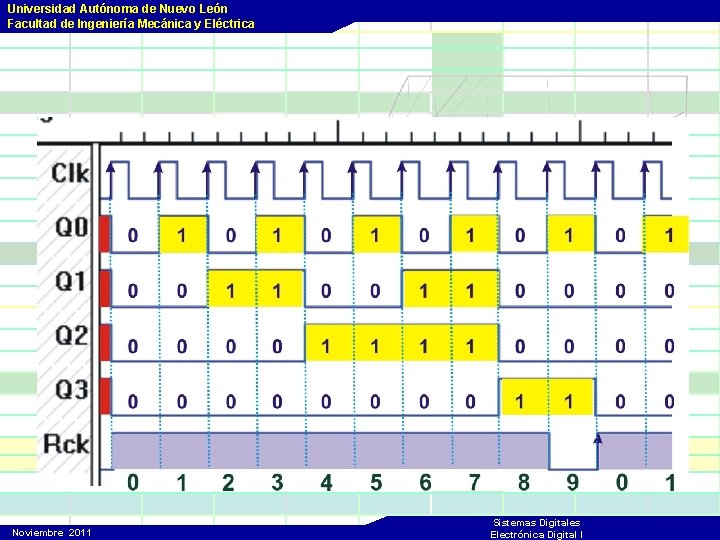

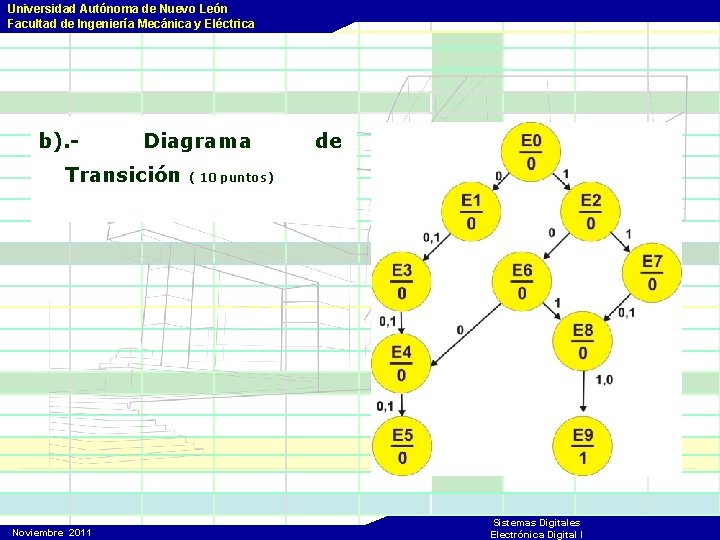

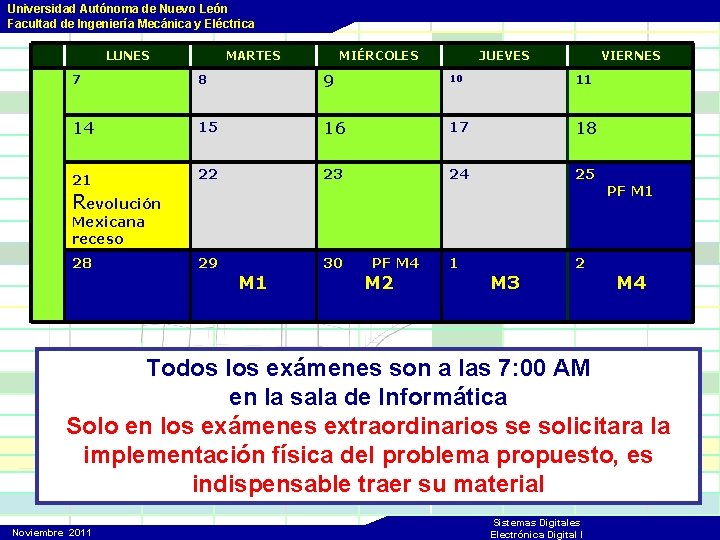

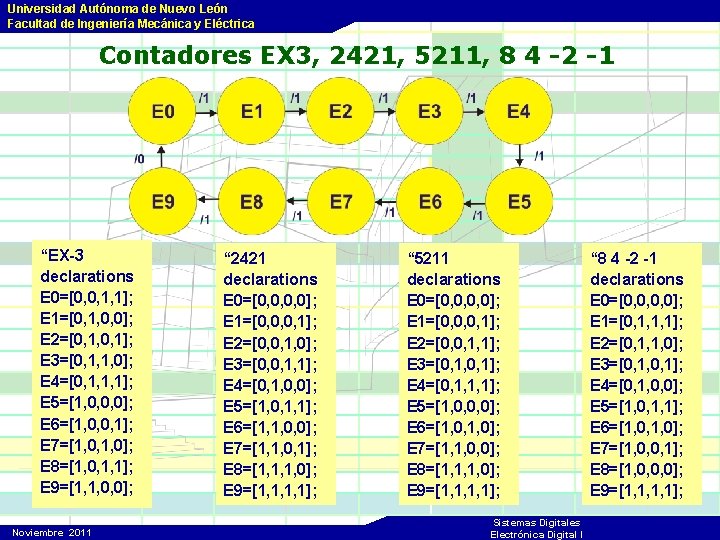

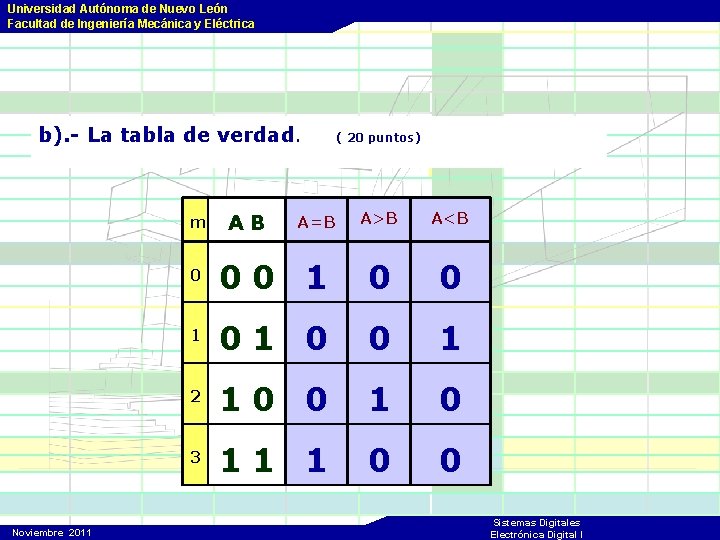

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica truth_table ([D, U]: >[D, U]) [1, ^HF]: >[0, 0]; [0, 0]: >[1, 5]; [0, 1]: >[0, 0]; [0, 2]: >[0, 1]; [0, 3]: >[0, 2]; [0, 4]: >[0, 3]; [0, 5]: >[0, 4]; [0, 6]: >[0, 5]; [0, 7]: >[0, 6]; [0, 8]: >[0, 7]; [0, 9]: >[0, 8]; [1, 0]: >[0, 9]; [1, 1]: >[1, 0]; [1, 2]: >[1, 1]; [1, 3]: >[1, 2]; [1, 4]: >[1, 3]; [1, 5]: >[1, 4]; Noviembre 2011 “tabla para Rck truth_table ([D, U]->[Rck]) [0, 0]->[0]; [0, 1]->[1]; [0, 2]->[1]; [0, 3]->[1]; [0, 4]->[1]; [0, 5]->[1]; [0, 6]->[1]; [0, 7]->[1]; [0, 8]->[1]; [0, 9]->[1]; [1, 0]->[1]; [1, 1]->[1]; [1, 2]->[1]; [1, 3]->[1]; [1, 4]->[1]; [1, 5]->[1]; TEST_VECTORS ([Clk]->[D, U, Rck]) [. c. ]->[. x. , . x. , . x. ]; [. c. ]->[. x. , . x. ]; END Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Contador de 0 a 78 ascendente/descendente Module cont “Entradas Ck, X pin 1, 2; Q 7. . Q 0 pin 19. . 12 istype ‘dc, reg’; Sd=[Q 7. . Q 0]; Equations Sd. clk=Ck; Declarations D=[Q 7. . Q 4]; U=[Q 3. . Q 0]; Truth_table ([X, D, U]: >[D, U]) [0, 0, 0]: >[0, 1]; [0, 0, 1]: >[0, 2]; [0, 0, 2]: >[0, 3]; [1, 0, 2]: >[0, 1]; ……………. ; [1, 1, 2]: >[1, 1]; ………………; [0, 7, 8]: >[0, 0]; [1, 0, 0]: >[7, 8]; [0, ^HF]: >[0, 0]; [1, ^HF]: >[0, 0]; Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Programa Medio Termino I. - Introducción a los Sistemas Digitales II. - Sistemas Numéricos III. - Álgebra Booleana IV. - Minimización de funciones Booleanas. Examen Final V. - Diseño Combinacional. VI. - Flip-Flops. VII. - Diseño Secuencial. Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Instrucciones: Lea cuidadosamente la descripción de cada problema escriba claramente en el espacio indicado: 1. -Para el diseño combinacional obtenga a). -El diagrama de bloques indicando las entradas y salidas. b). - La tabla de verdad. ( 5 puntos) ( 20 puntos) Una vez comprobado el funcionamiento imprima y anexe al instructivo c). - El Archivo en formato ABEL ABL ( 10 puntos) d). - La simulación que deberá de contener las pruebas necesarias para comprobar que cumple con lo solicitado. Noviembre 2011 ( 10 puntos) Sistemas Digitales Electrónica Digital I

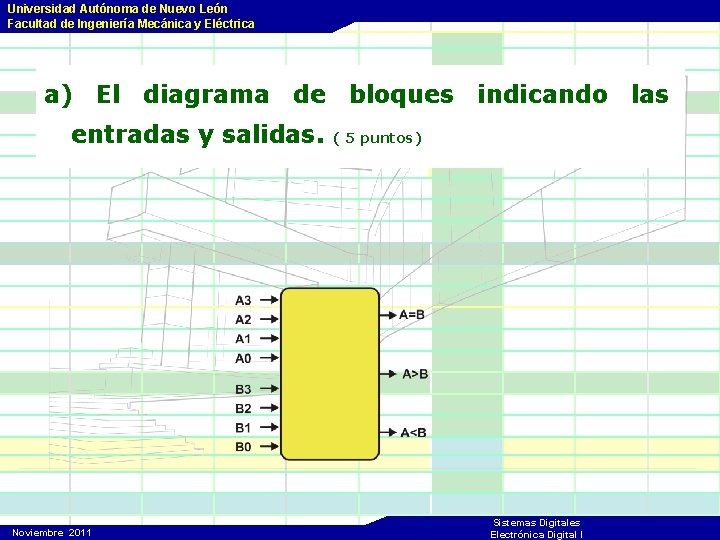

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica a) El diagrama de bloques indicando las entradas y salidas. Noviembre 2011 ( 5 puntos) Sistemas Digitales Electrónica Digital I

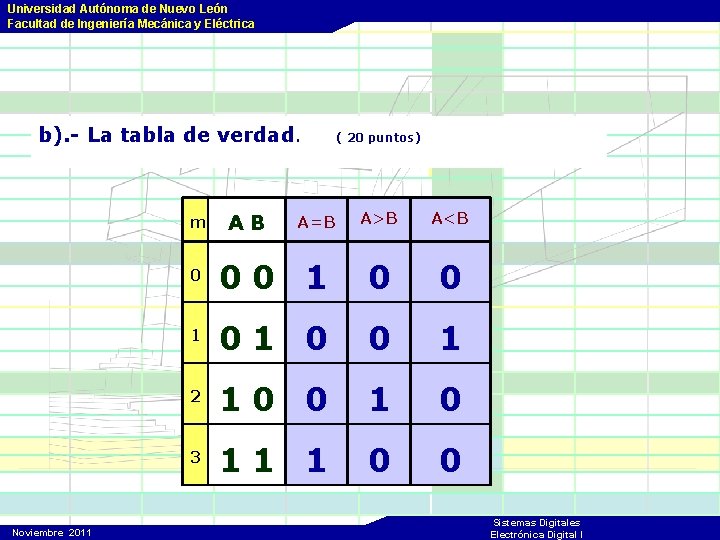

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica b). - La tabla de verdad. m Noviembre 2011 AB A=B ( 20 puntos) A>B A<B 0 00 1 01 0 0 1 2 10 0 1 0 3 11 1 0 0 Sistemas Digitales Electrónica Digital I

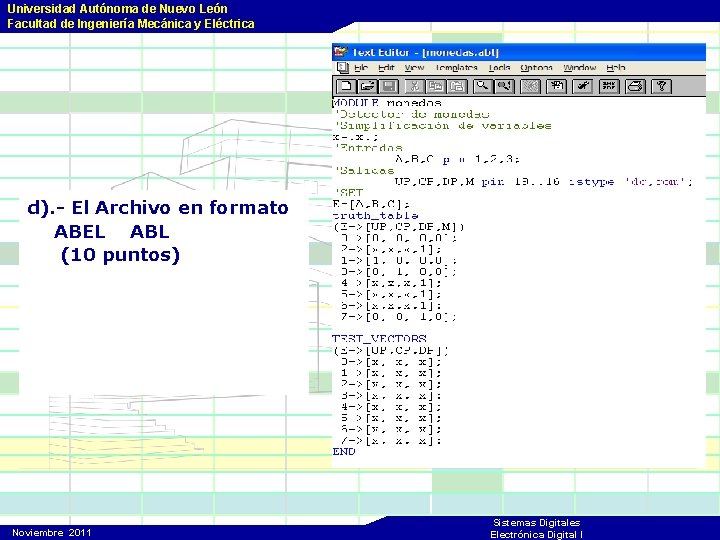

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica d). - El Archivo en formato ABEL ABL (10 puntos) Noviembre 2011 Sistemas Digitales Electrónica Digital I

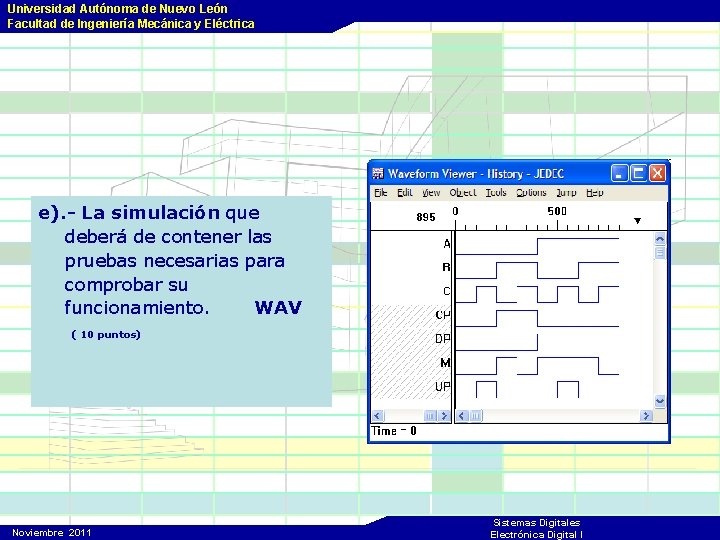

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica e). - La simulación que deberá de contener las pruebas necesarias para comprobar su funcionamiento. WAV ( 10 puntos) Noviembre 2011 Sistemas Digitales Electrónica Digital I

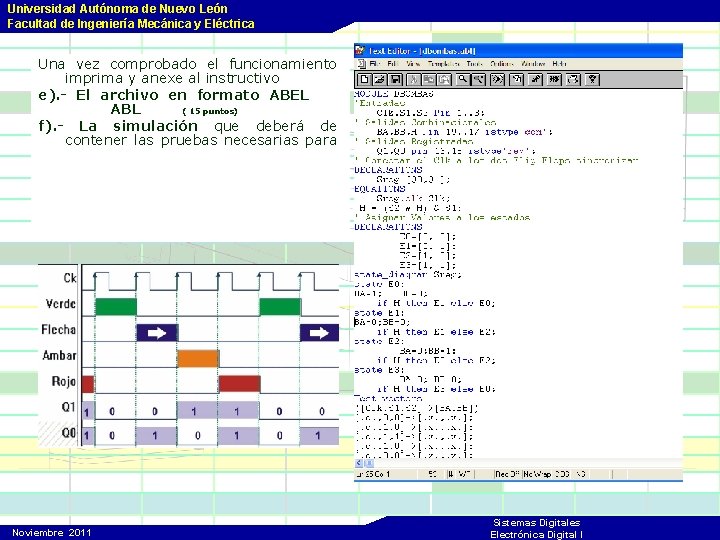

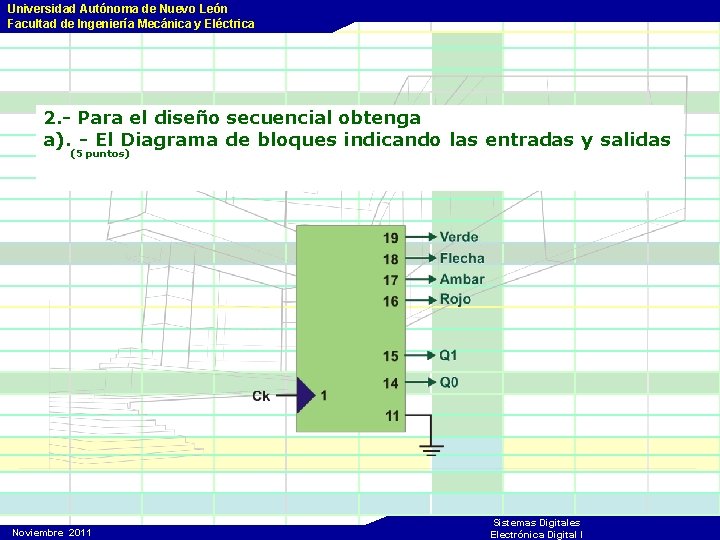

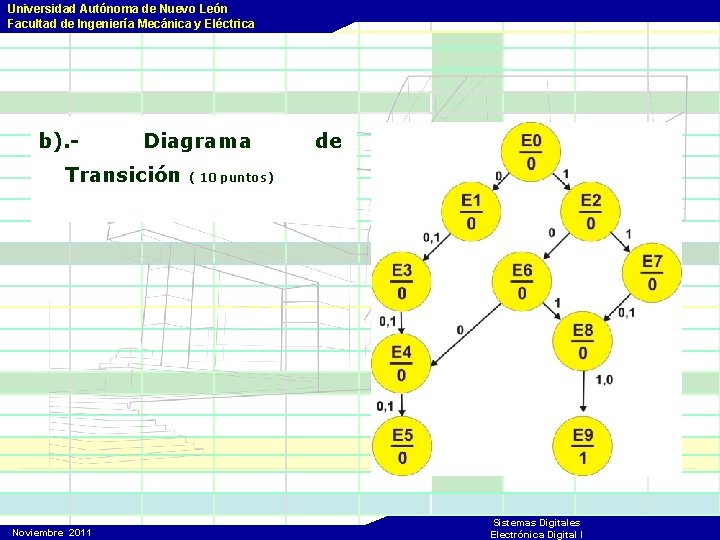

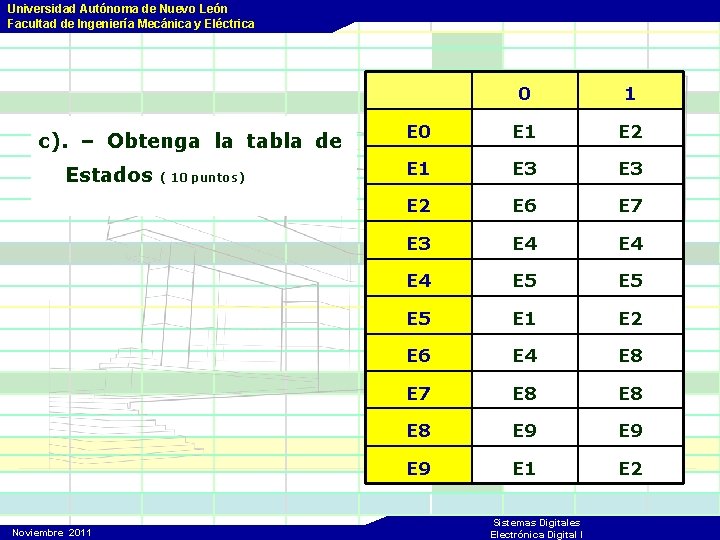

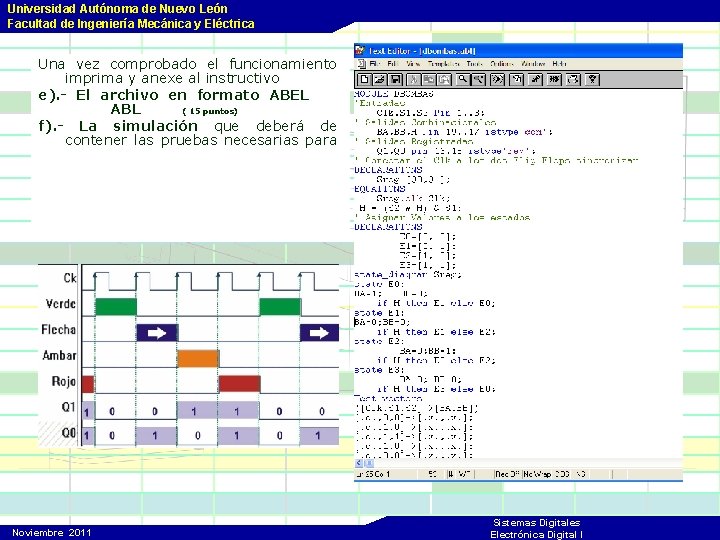

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Diseño Secuencial a). - El Diagrama de bloques indicando las entradas y salidas ( 5 puntos) b). - Diagrama de Transición ( 15 puntos) c). - Obtenga la tabla de Estados ( 10 puntos) Una vez comprobado el funcionamiento imprima y anexe al instructivo d). - El archivo en formato ABEL ( 15 puntos) e). - La simulación que deberá de contener las pruebas necesarias para comprobar su funcionamiento (10 puntos) Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Para la solución de los problemas es permitido usar los dispositivos GAL 16 V 8, GAL 22 V 10 o GAL 26 V 12. En la computadora sólo está permitido usar el programa Isp Starter y Word para mostrar los resultados. Sólo una sola impresión está permitida por cada problema. Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica 2. - Para el diseño secuencial obtenga a). - El Diagrama de bloques indicando las entradas y salidas (5 puntos) Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica b). - Diagrama Transición Noviembre 2011 de ( 10 puntos) Sistemas Digitales Electrónica Digital I

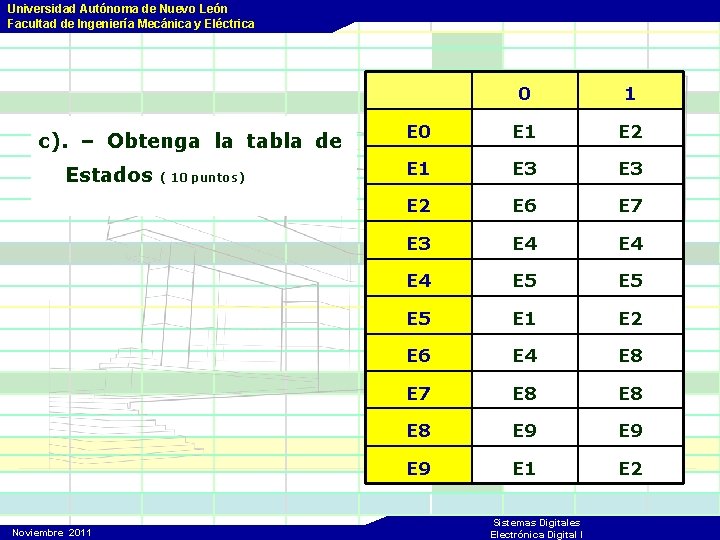

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica c). – Obtenga la tabla de Estados Noviembre 2011 ( 10 puntos) 0 1 E 0 E 1 E 2 E 1 E 3 E 2 E 6 E 7 E 3 E 4 E 4 E 5 E 5 E 1 E 2 E 6 E 4 E 8 E 7 E 8 E 8 E 9 E 9 E 1 E 2 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Una vez comprobado el funcionamiento imprima y anexe al instructivo e). - El archivo en formato ABEL ABL ( 15 puntos) f). - La simulación que deberá de contener las pruebas necesarias para Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Para la solución de los problemas es permitido usar los dispositivos GAL 16 V 8, GAL 22 V 10 o GAL 26 V 12. , En la computadora sólo está permitido usar el programa Isp Starter. Sólo una sola impresión está permitida por cada problema. Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Reglas obligatorias para presentar el examen 1. -Solo esta permitido el uso de lápiz o pluma para resolver el examen. (Deja tus libros afuera del aula) 2. -No se permite el uso de disquetes, o memorias USB ni el uso de INTERNET. 3. - En la computadora solo esta permitido usar el programa Isp Starter y Word. 4. - En los archivos en formato ABEL-HDL tanto en el combinacional como en el secuencial incluir líneas de comentarios que contengan: “Fecha. “Nombre y numero de matricula. “Nombre de la Materia y hora en que se esta cursando Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Reglas obligatorias para presentar el examen 5. -Para la solución de los problemas es permitido usar los dispositivos: GAL 16 V 8, GAL 20 V 8, GAL 22 V 10 o GAL 26 V 12 6. - Antes de imprimir guarde los archivos 7. - Solo esta permitido una sola impresión por cada problema. 8. - Si tienes una pregunta o duda por favor levanta la mano. 9. - El examen es individual, no se permite preguntar al compañero ni ver su monitor SE CONSIDERA COPIA, no te arriesgues. Noviembre 2011 Sistemas Digitales Electrónica Digital I

Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica Calificación Concepto Noviembre 2011 Puntos Examen de medio término 25 Examen Final 30 Tareas 15 Proyecto Final 30 Proyectos adicionales 15 Sistemas Digitales Electrónica Digital I