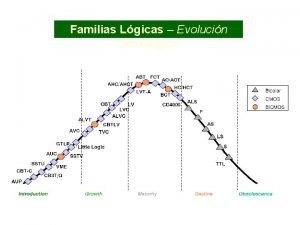

Tecnologa de las Familias Lgicas Resea Histrica En

- Slides: 49

Tecnología de las Familias Lógicas

Reseña Histórica En 1940, la primer computadora electrónica digital (ENIAC) tenia cerca de 18. 000 válvulas, para un número similar de compuertas lógicas A fines de los 50, la invención del diodo semiconductor y los transistores bipolares, permitieron el desarrollo de computadoras mas chicas, rápidas y mayor capacidad de computo En los 60, la invención del Circuito Integrado (IC, Integrated Circuit), permitió incluir en una misma pastilla (IC) múltiples diodos, transistores, y otros componentes ICTP FPGA-VHDL 2

Familia Lógica Es una colección de diferentes circuitos integrados con sus entradas y salidas, construidos con la misma tecnología pero que tienen distinta funcionalidad lógica Circuitos integrados de una misma tecnología se pueden conectar entre sí Circuitos integrados de distintas tecnología puede que no se puedan conectar entre sí Familia Lógica Complementary Metal-Oxide Semiconductor Filed Effect Transistor (CMOS) Familia Lógica Bipolar Transistor Logic (TTL) ICTP FPGA-VHDL 3

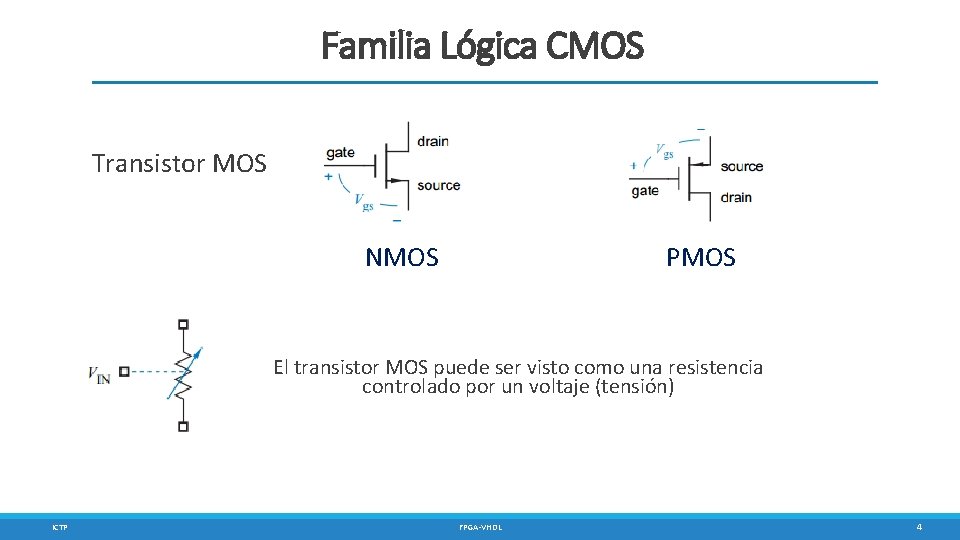

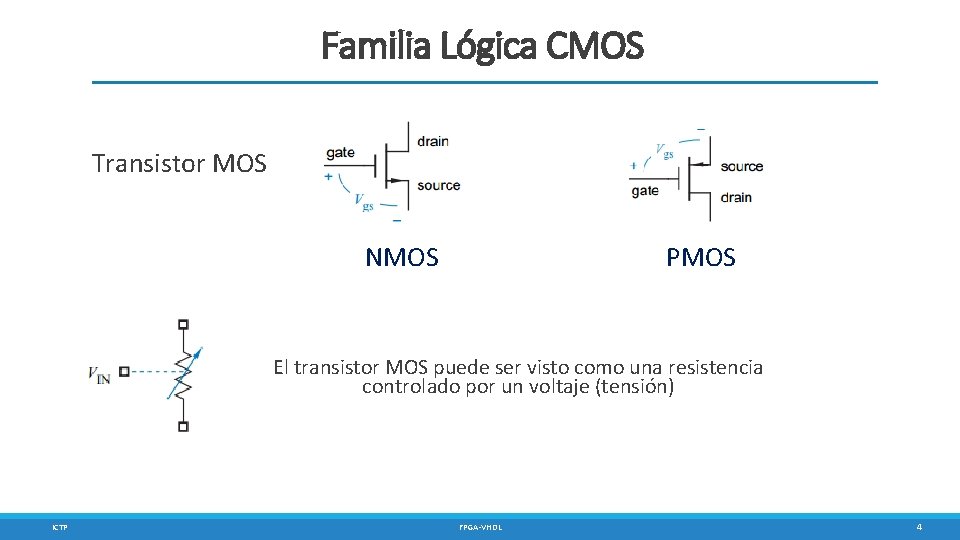

Familia Lógica CMOS Transistor MOS NMOS PMOS El transistor MOS puede ser visto como una resistencia controlado por un voltaje (tensión) ICTP FPGA-VHDL 4

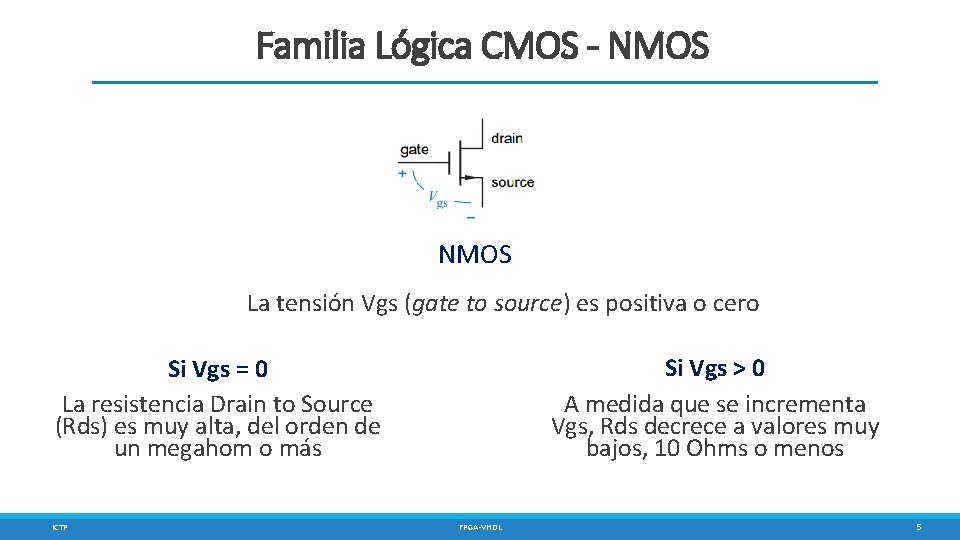

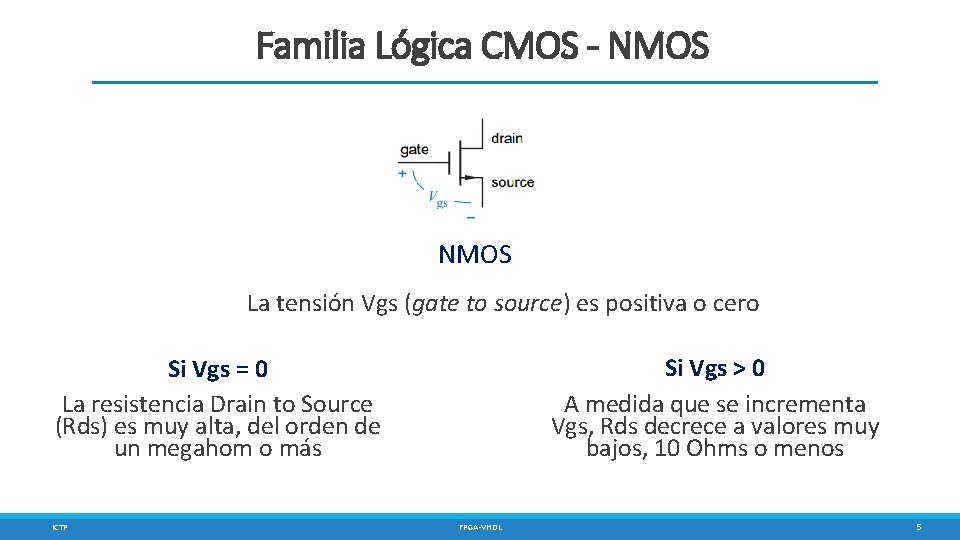

Familia Lógica CMOS - NMOS La tensión Vgs (gate to source) es positiva o cero Si Vgs > 0 A medida que se incrementa Vgs, Rds decrece a valores muy bajos, 10 Ohms o menos Si Vgs = 0 La resistencia Drain to Source (Rds) es muy alta, del orden de un megahom o más ICTP FPGA-VHDL 5

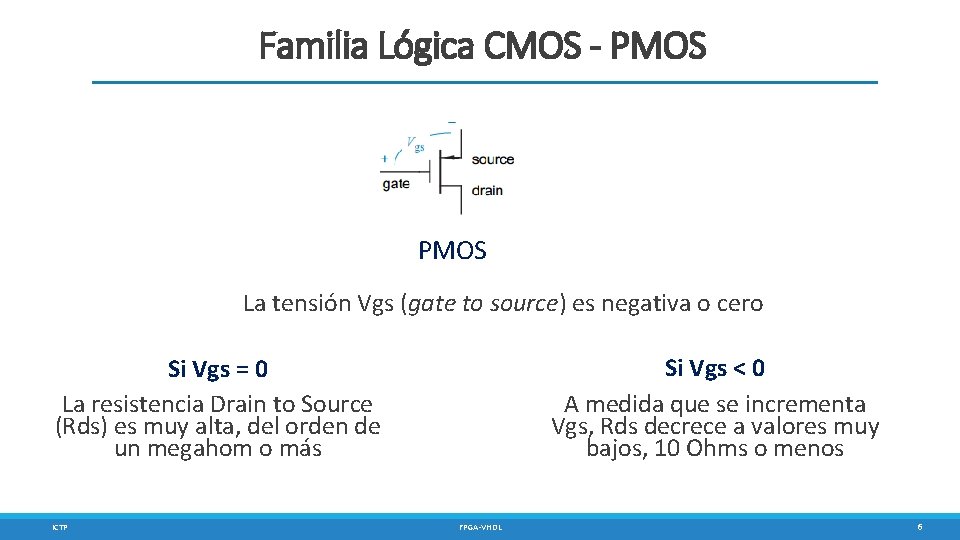

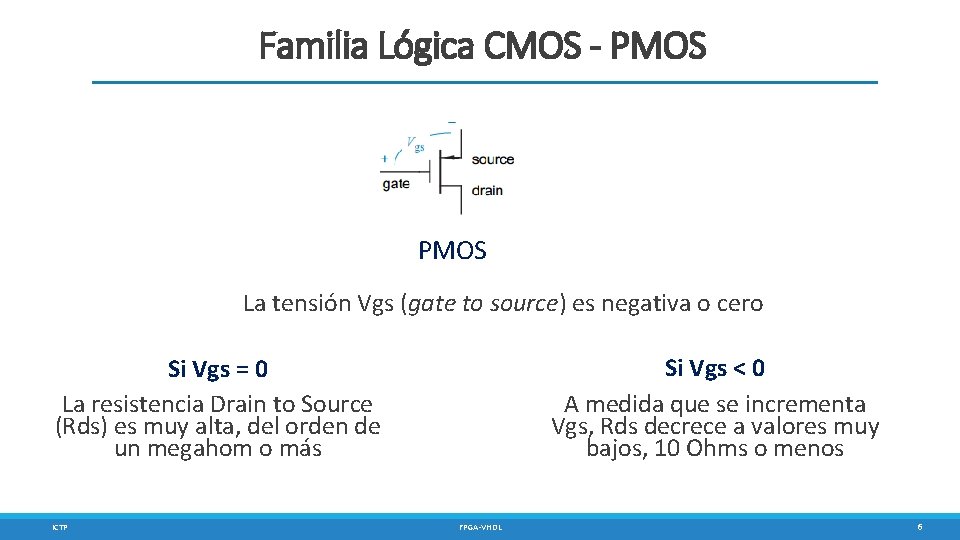

Familia Lógica CMOS - PMOS La tensión Vgs (gate to source) es negativa o cero Si Vgs < 0 A medida que se incrementa Vgs, Rds decrece a valores muy bajos, 10 Ohms o menos Si Vgs = 0 La resistencia Drain to Source (Rds) es muy alta, del orden de un megahom o más ICTP FPGA-VHDL 6

Familia Lógica CMOS – Muy Baja Corriente Independientemente del voltaje aplicado a Vgs, no hay corriente que fluya desde el gate a source o desde gate a drain La resistencia entre el gate y los otros terminales (source o drain) es extremadamente alta Por ende la corriente que fluya a través de la resistencia es muy pequeña , típicamente del orden de los microamperes (µA, 10 -6 A), y es llamada corriente de perdida (leakage current) ICTP FPGA-VHDL 7

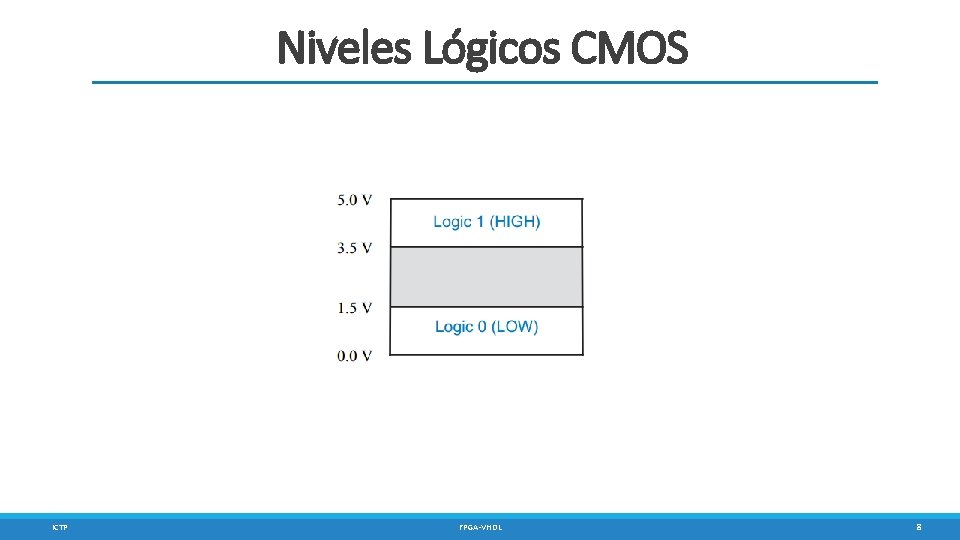

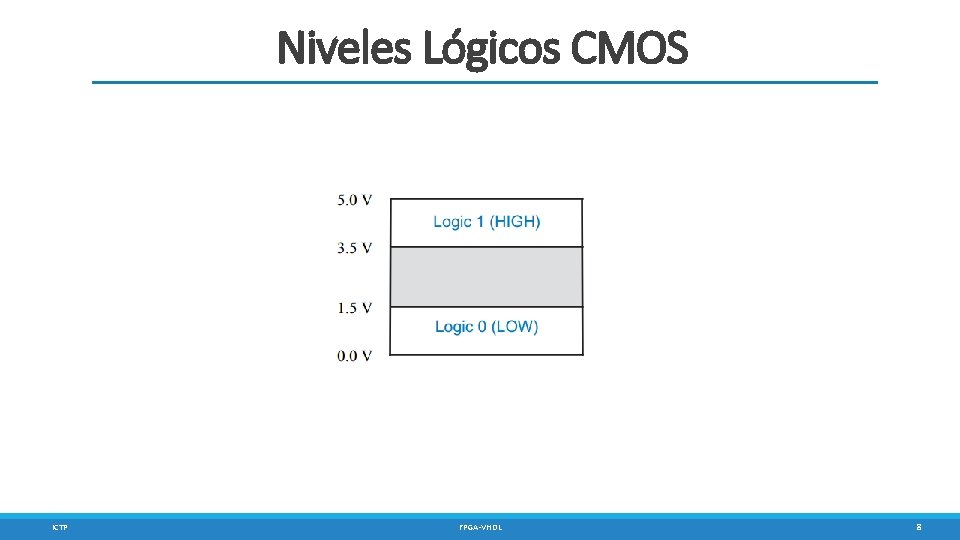

Niveles Lógicos CMOS ICTP FPGA-VHDL 8

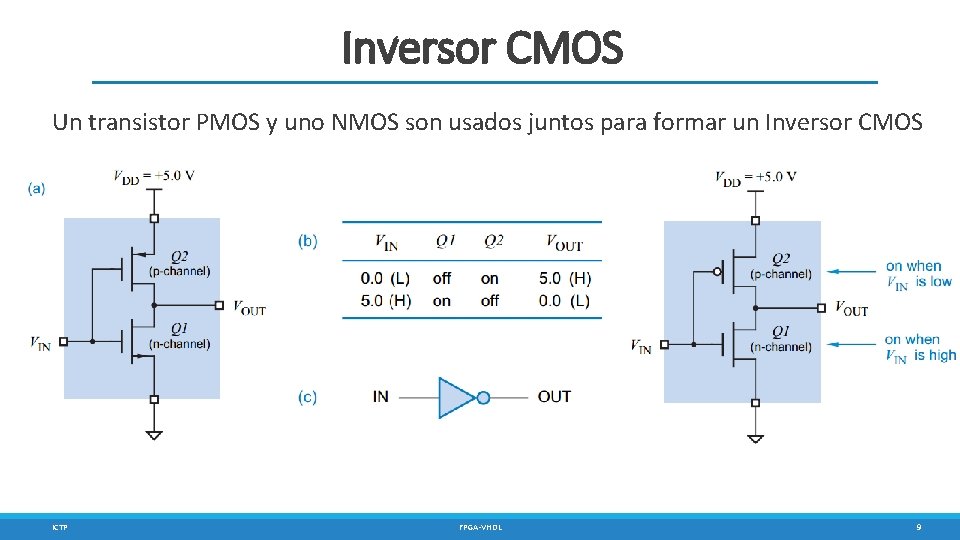

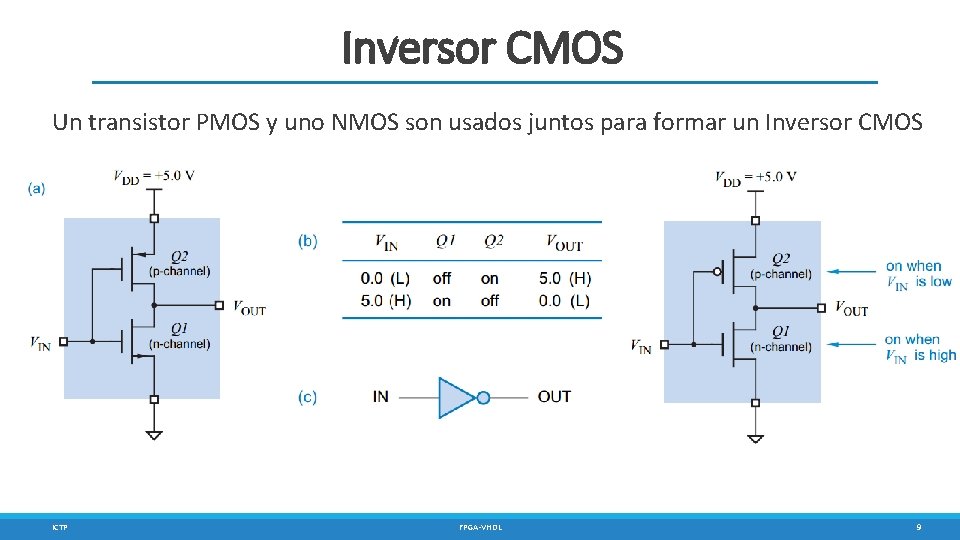

Inversor CMOS Un transistor PMOS y uno NMOS son usados juntos para formar un Inversor CMOS ICTP FPGA-VHDL 9

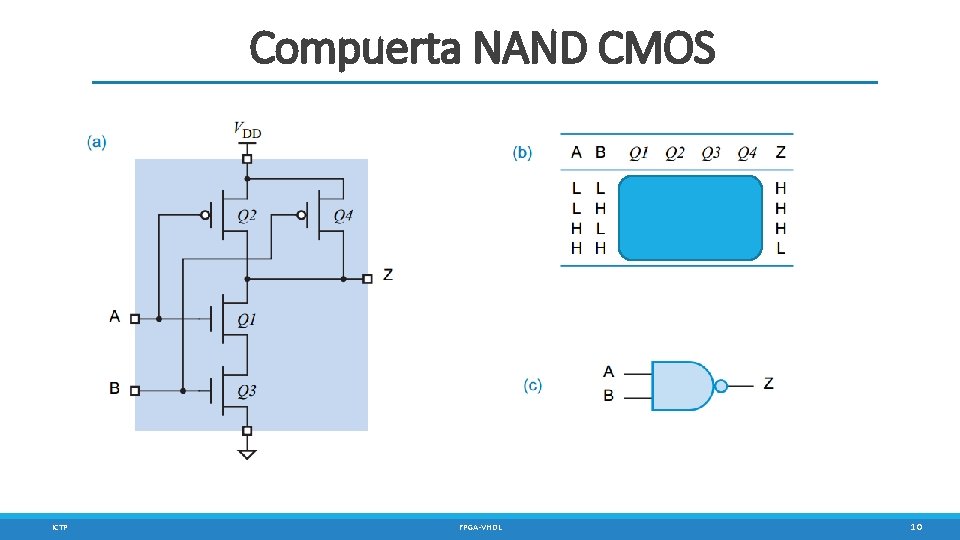

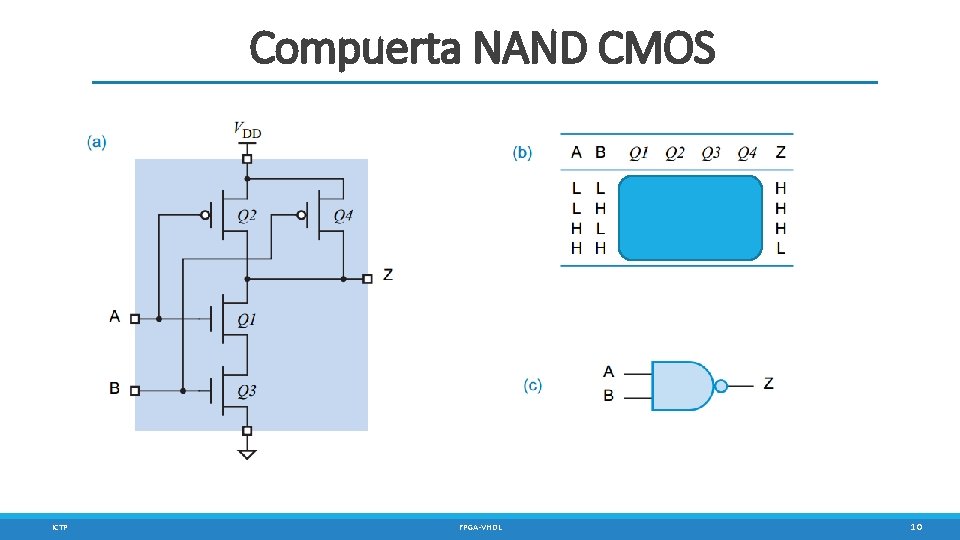

Compuerta NAND CMOS ICTP FPGA-VHDL 10

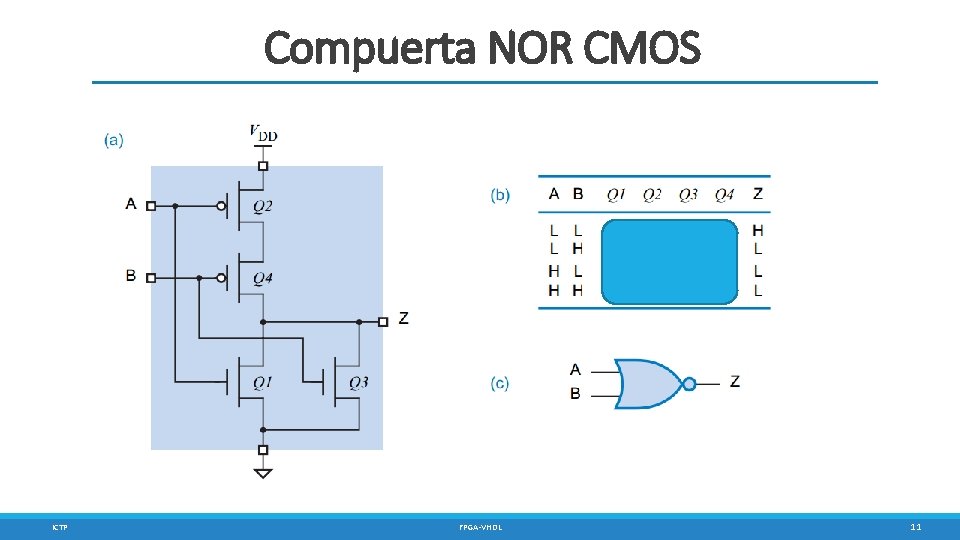

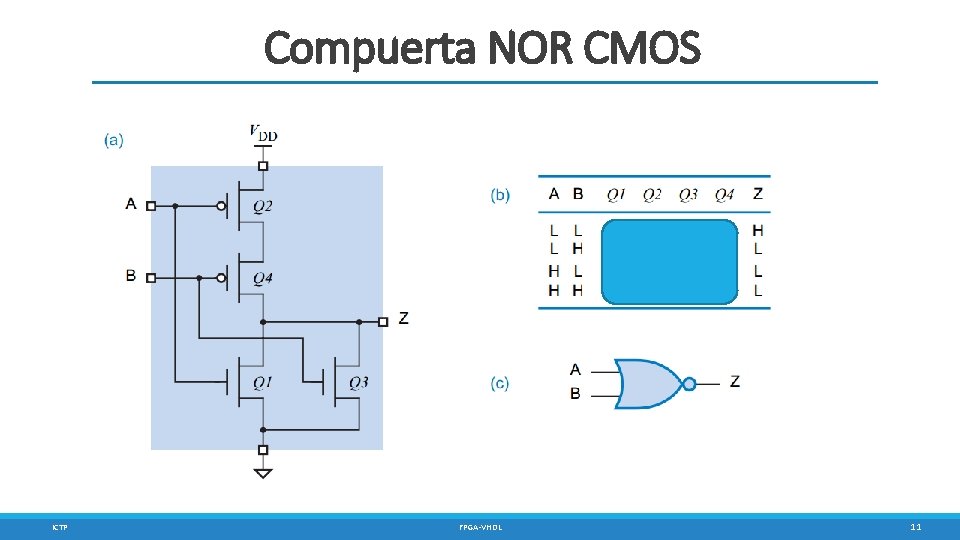

Compuerta NOR CMOS ICTP FPGA-VHDL 11

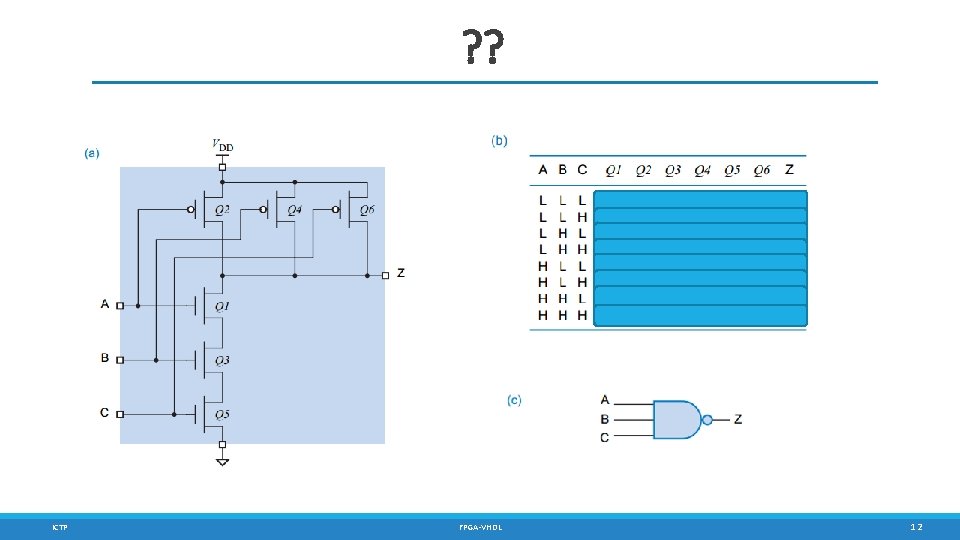

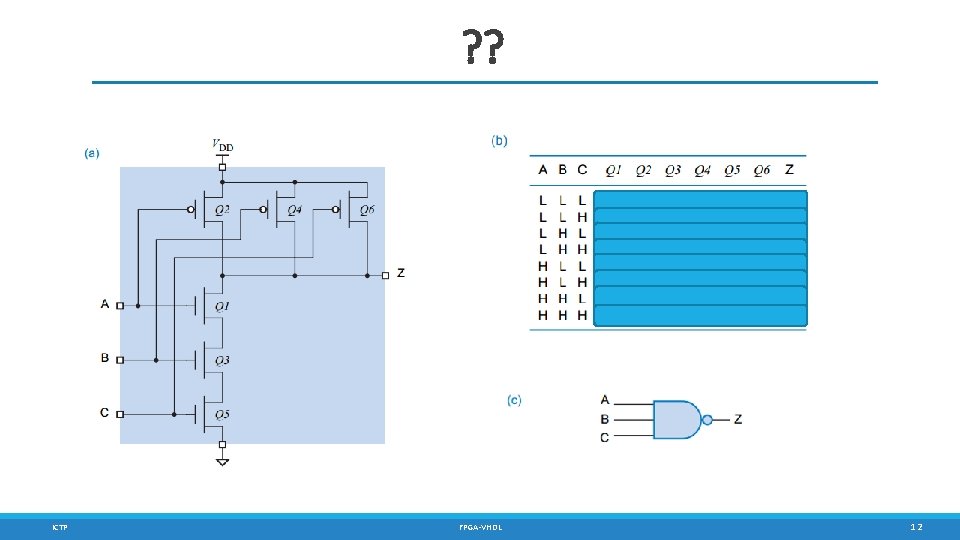

? ? ICTP FPGA-VHDL 12

Parámetros Eléctricos y de Tiempo ICTP FPGA-VHDL 13

Fan In – Fan Out El número de entradas que puede tener una compuerta de una familia lógica es llamada cargabilidad de entrada (fan in) El número de entradas que puede son conectadas a una determinada salida de una familia lógica es llamada cargabilidad de salida (fan out) ICTP FPGA-VHDL 14

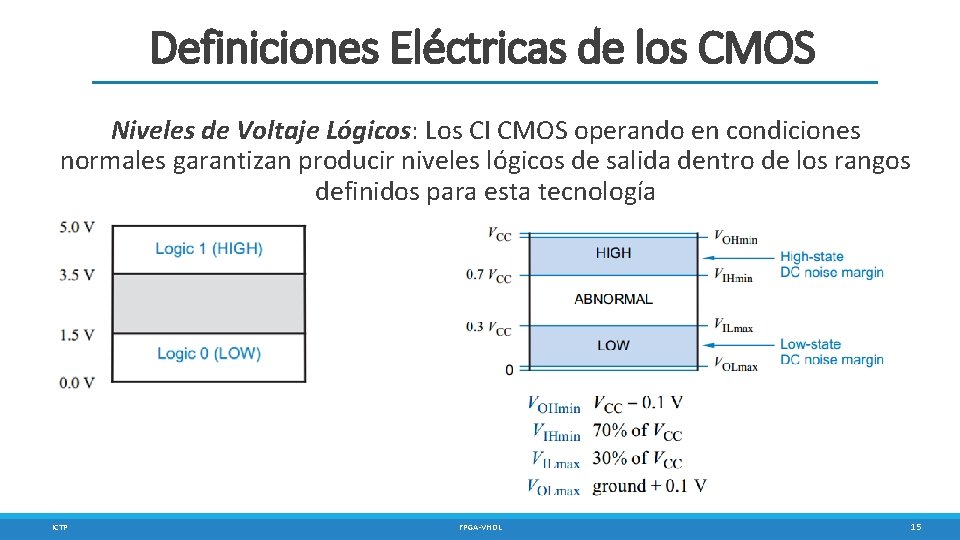

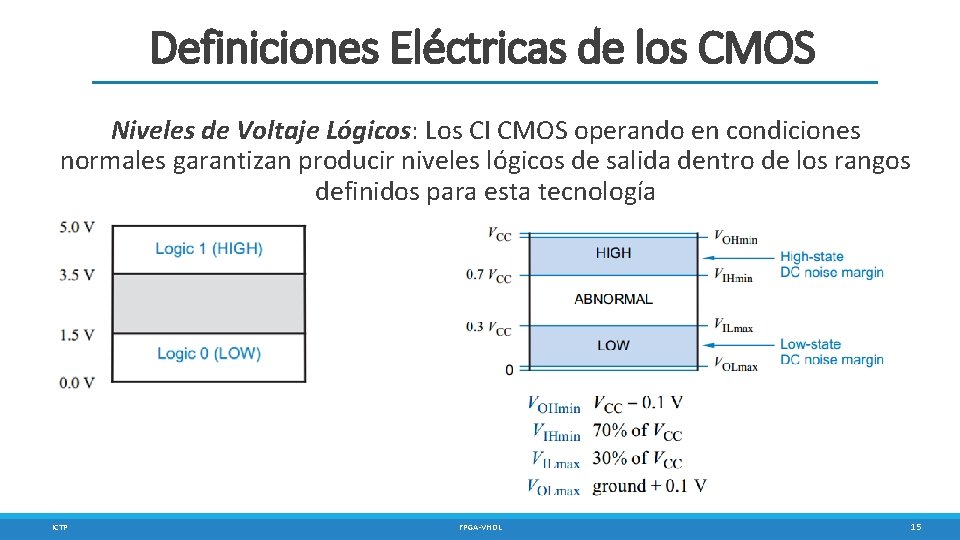

Definiciones Eléctricas de los CMOS Niveles de Voltaje Lógicos: Los CI CMOS operando en condiciones normales garantizan producir niveles lógicos de salida dentro de los rangos definidos para esta tecnología ICTP FPGA-VHDL 15

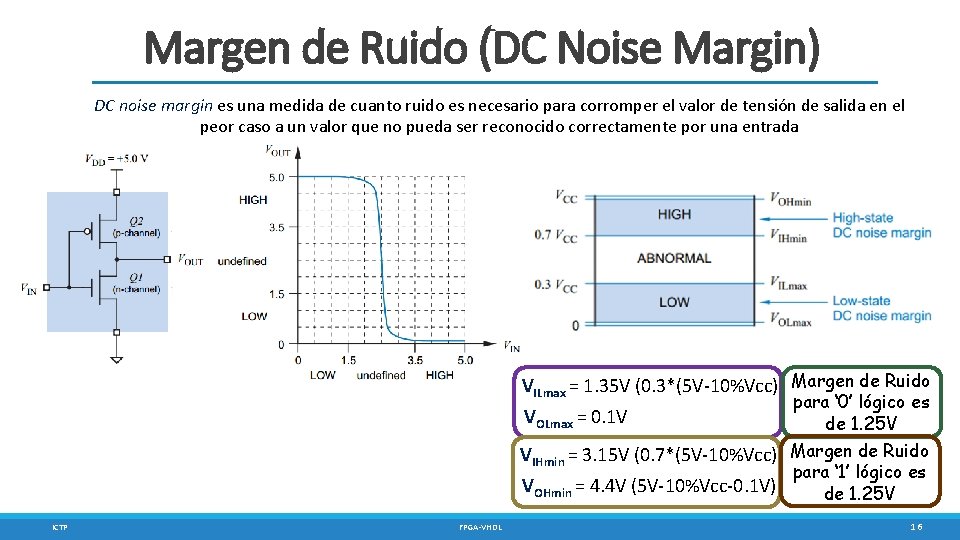

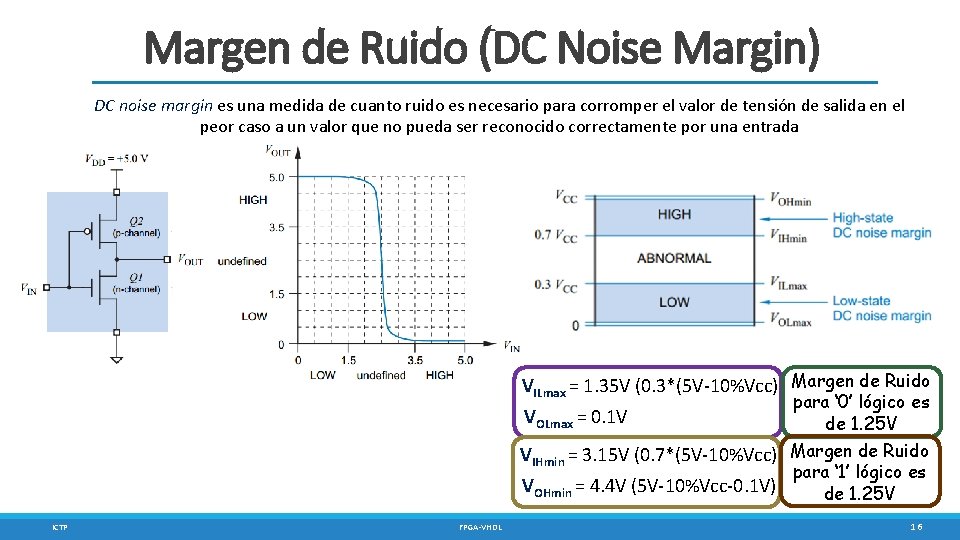

Margen de Ruido (DC Noise Margin) DC noise margin es una medida de cuanto ruido es necesario para corromper el valor de tensión de salida en el peor caso a un valor que no pueda ser reconocido correctamente por una entrada VILmax = 1. 35 V (0. 3*(5 V-10%Vcc) Margen de Ruido para ‘ 0’ lógico es de 1. 25 V VIHmin = 3. 15 V (0. 7*(5 V-10%Vcc) Margen de Ruido para ‘ 1’ lógico es VOHmin = 4. 4 V (5 V-10%Vcc-0. 1 V) de 1. 25 V VOLmax = 0. 1 V ICTP FPGA-VHDL 16

Ruido (Noise) Hay diversas fuentes de ruido que pueden generar problemas en el funcionamiento de un sistema digital. Entre las principales fuentes de ruido se destacan: § Campos magnéticos/eléctricos § Perturbaciones en la fuente de voltaje § Rayos cósmicos § Conmutación de varias señales lógicas al mismo tiempo § Rebote de señales debido a una adaptación de impedancias no correcta entre la salida del CI y la pista del circuito impreso ICTP FPGA-VHDL 17

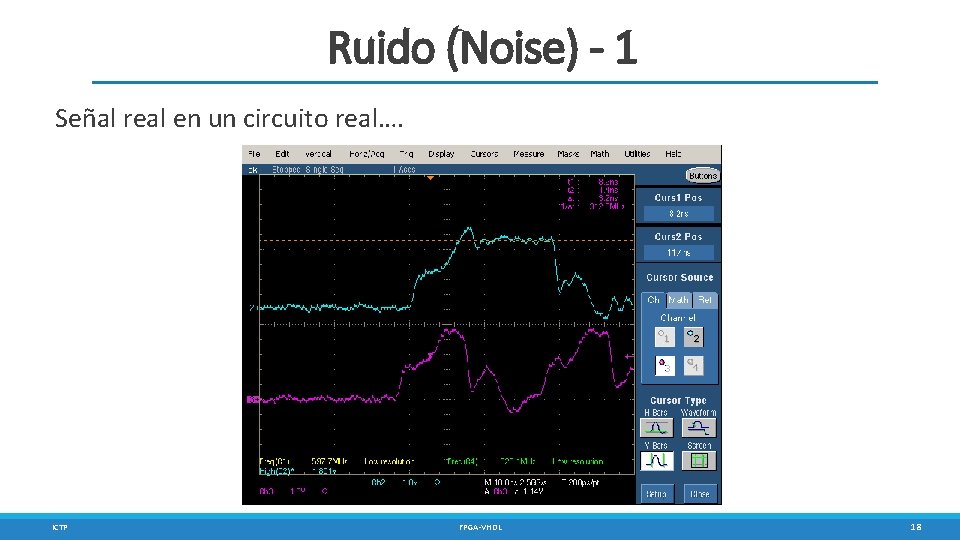

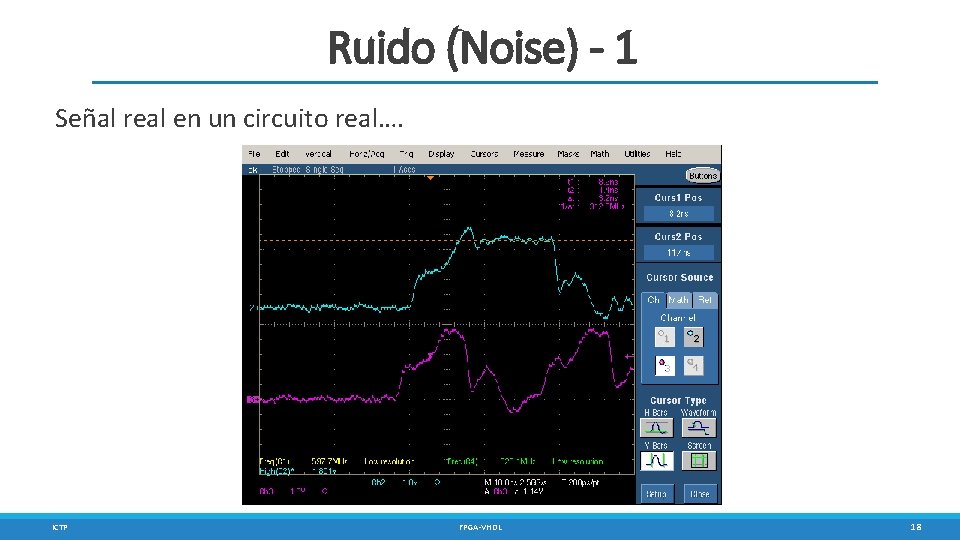

Ruido (Noise) - 1 Señal real en un circuito real…. ICTP FPGA-VHDL 18

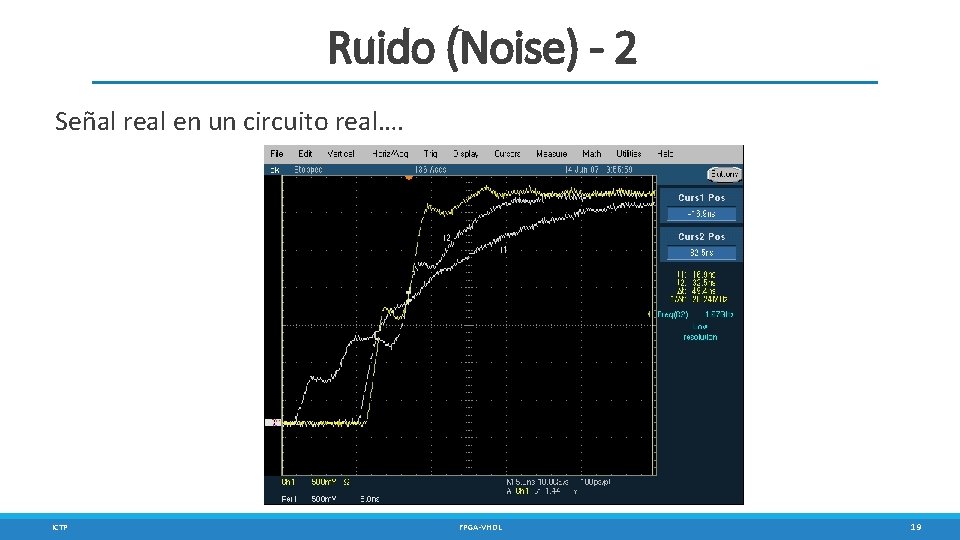

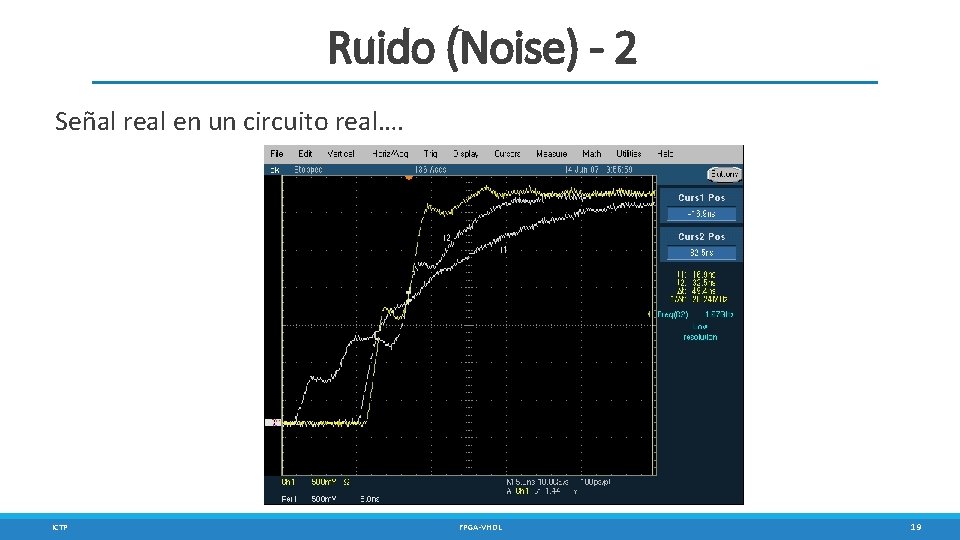

Ruido (Noise) - 2 Señal real en un circuito real…. ICTP FPGA-VHDL 19

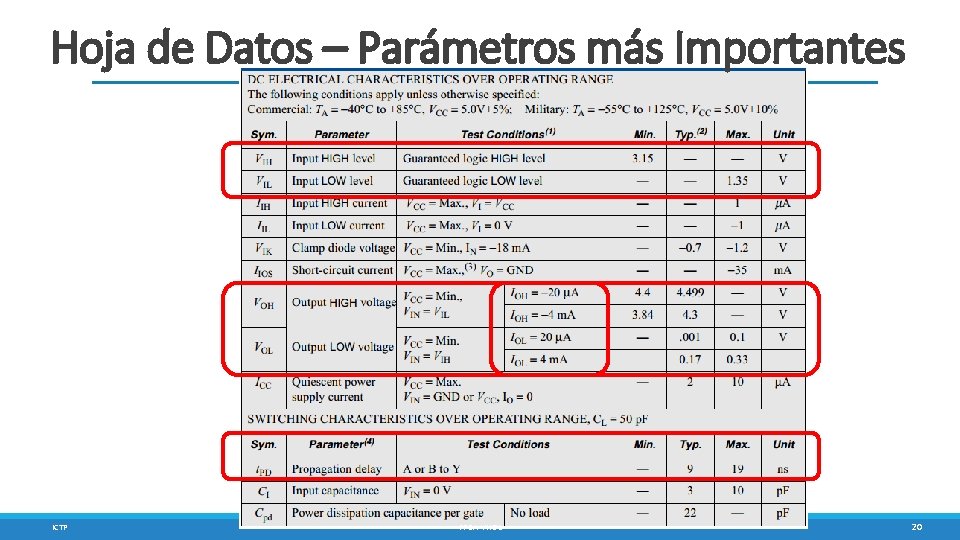

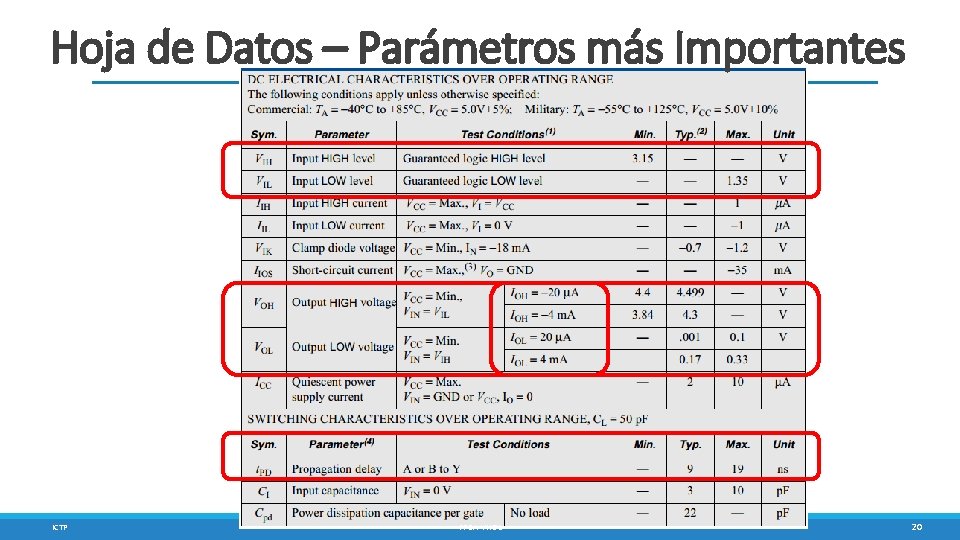

Hoja de Datos – Parámetros más Importantes ICTP FPGA-VHDL 20

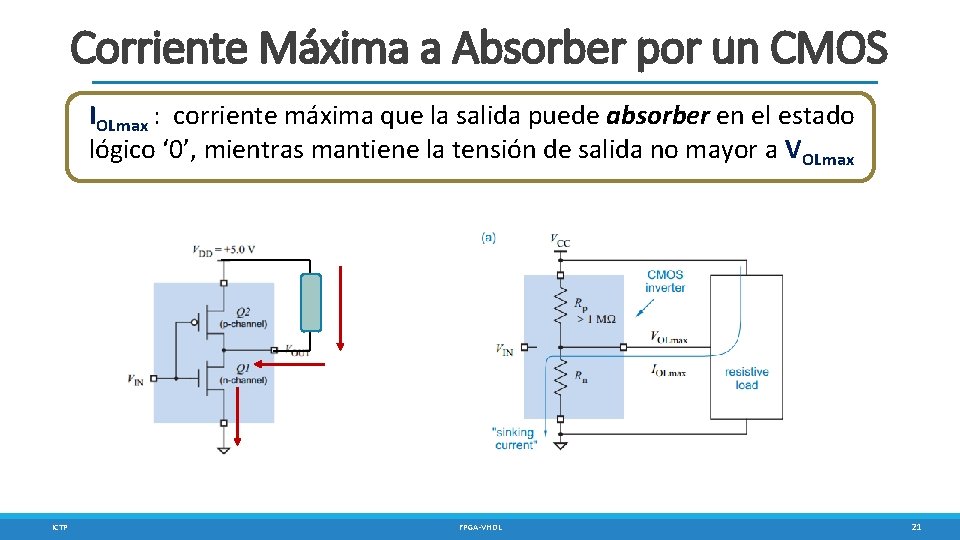

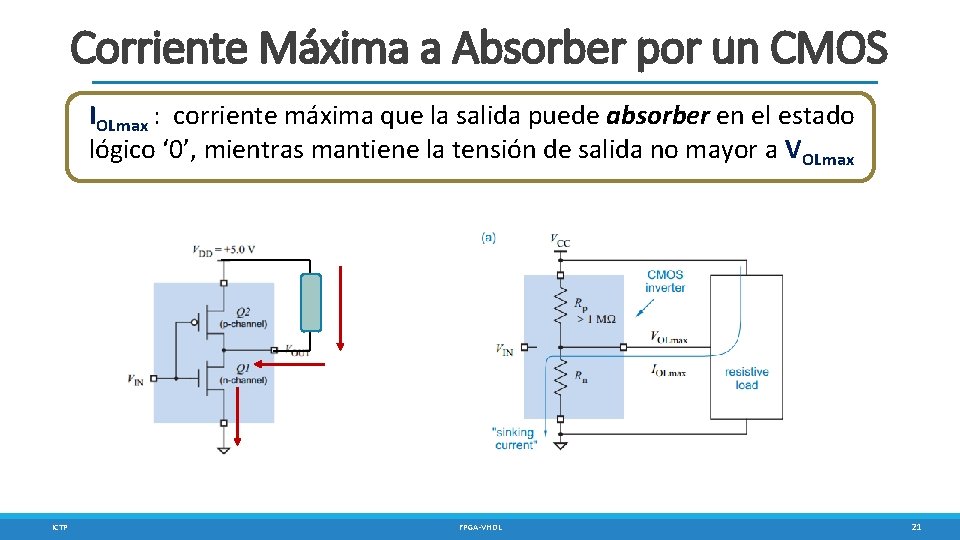

Corriente Máxima a Absorber por un CMOS IOLmax : corriente máxima que la salida puede absorber en el estado lógico ‘ 0’, mientras mantiene la tensión de salida no mayor a VOLmax ICTP FPGA-VHDL 21

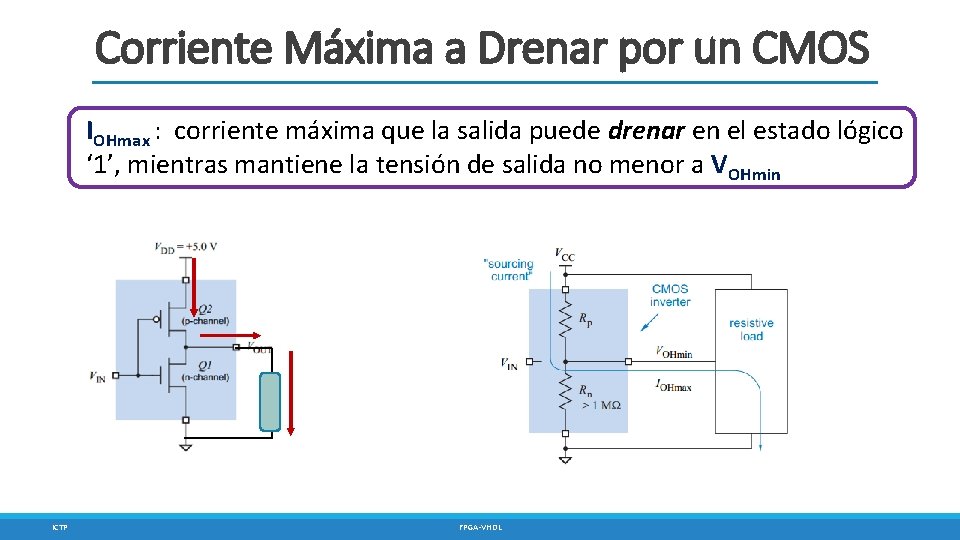

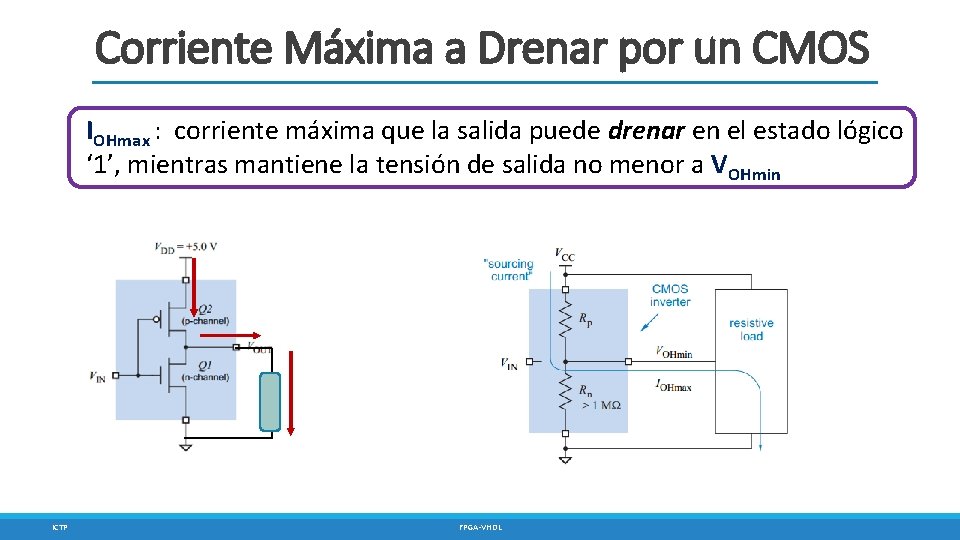

Corriente Máxima a Drenar por un CMOS IOHmax : corriente máxima que la salida puede drenar en el estado lógico ‘ 1’, mientras mantiene la tensión de salida no menor a VOHmin 22 ICTP FPGA-VHDL

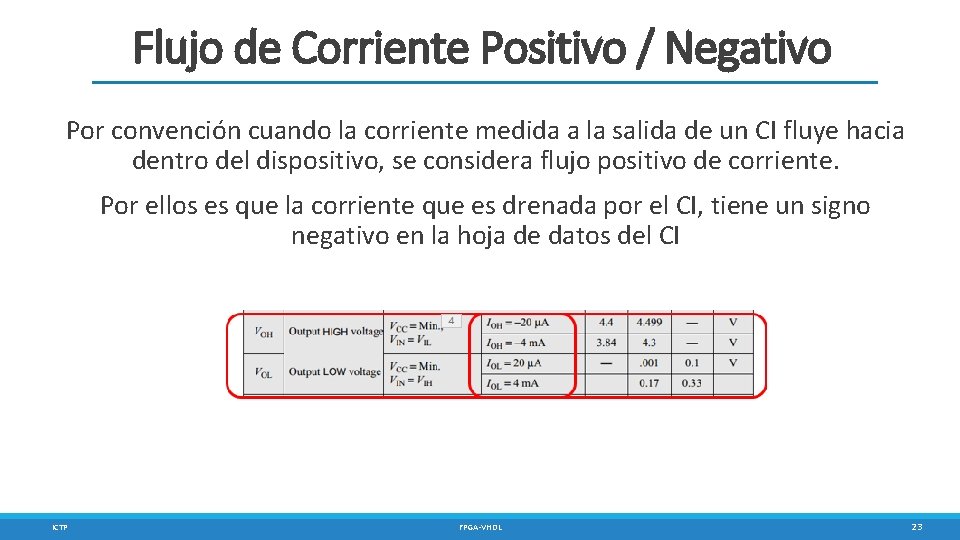

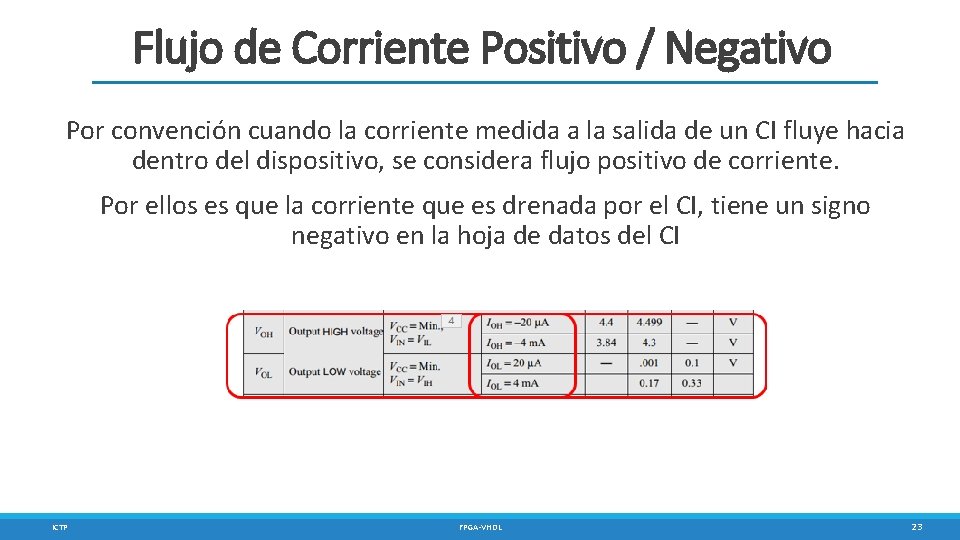

Flujo de Corriente Positivo / Negativo Por convención cuando la corriente medida a la salida de un CI fluye hacia dentro del dispositivo, se considera flujo positivo de corriente. Por ellos es que la corriente que es drenada por el CI, tiene un signo negativo en la hoja de datos del CI ICTP FPGA-VHDL 23

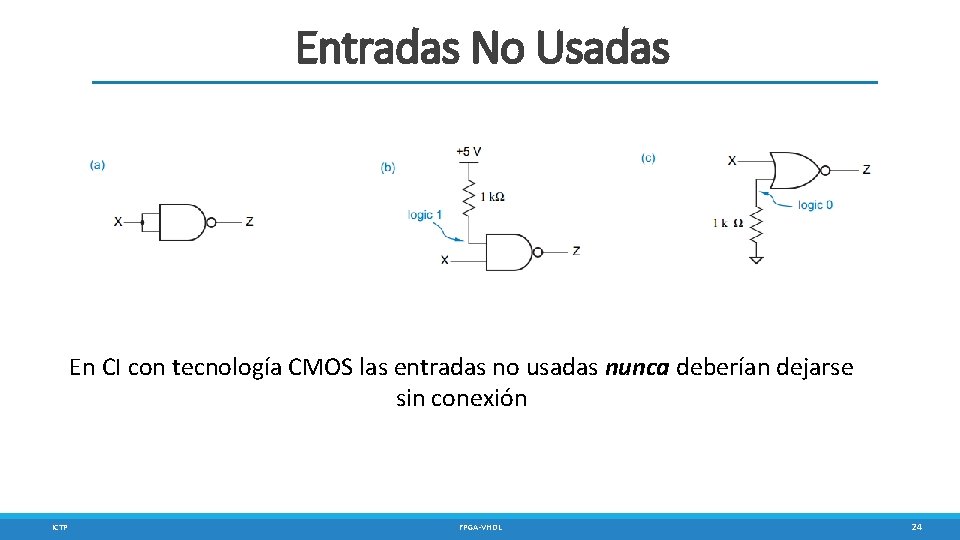

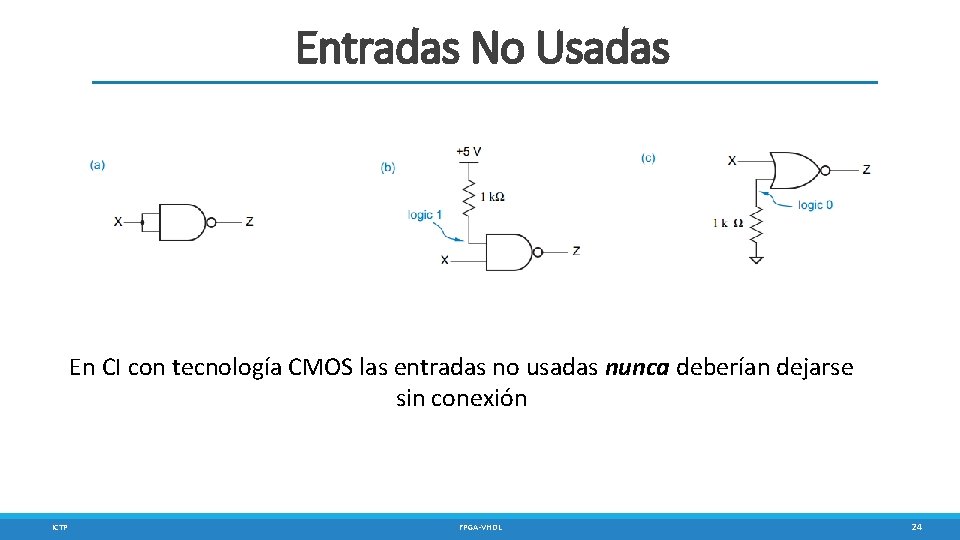

Entradas No Usadas En CI con tecnología CMOS las entradas no usadas nunca deberían dejarse sin conexión ICTP FPGA-VHDL 24

Descarga Electrostática (ESD) Electrostatic Discharge (ESD) es un fenómeno eléctrico que hace que circule una corriente eléctrica repentina y momentánea entre dos objetos de distinto potencial eléctrico. Esta corriente eléctrica es indeseada y pueden causar daño irreparable al CI y/o al equipo electrónico ICTP FPGA-VHDL 25

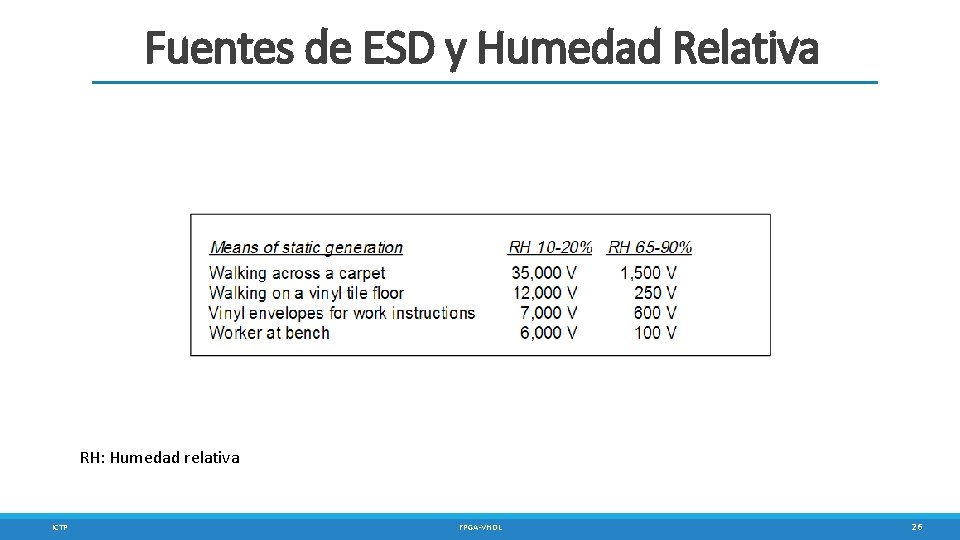

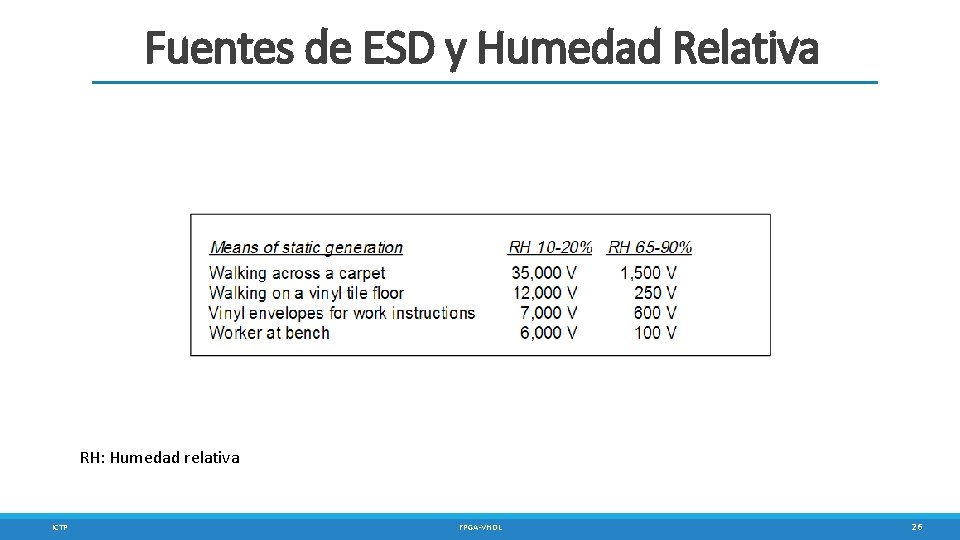

Fuentes de ESD y Humedad Relativa RH: Humedad relativa ICTP FPGA-VHDL 26

Protección y Prevención de ESD ICTP FPGA-VHDL 27

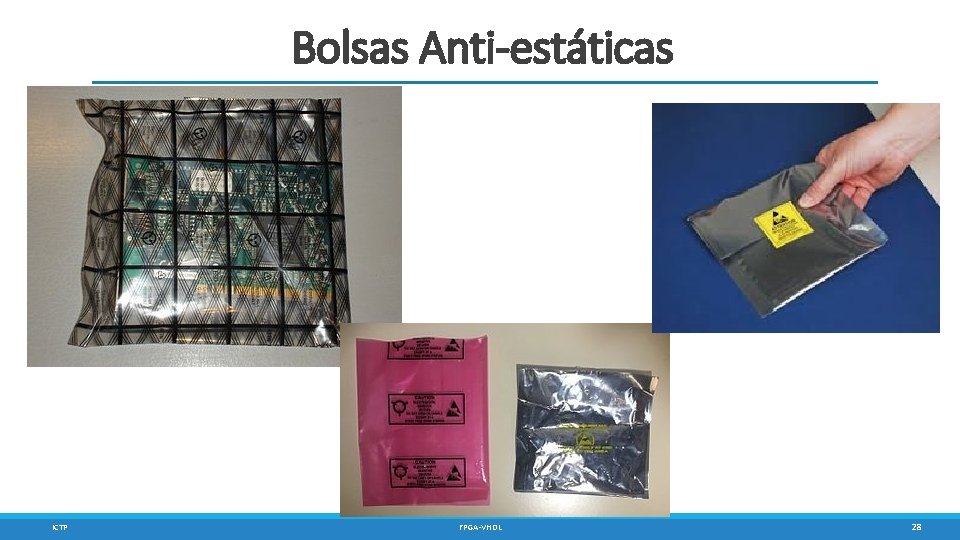

Bolsas Anti-estáticas ICTP FPGA-VHDL 28

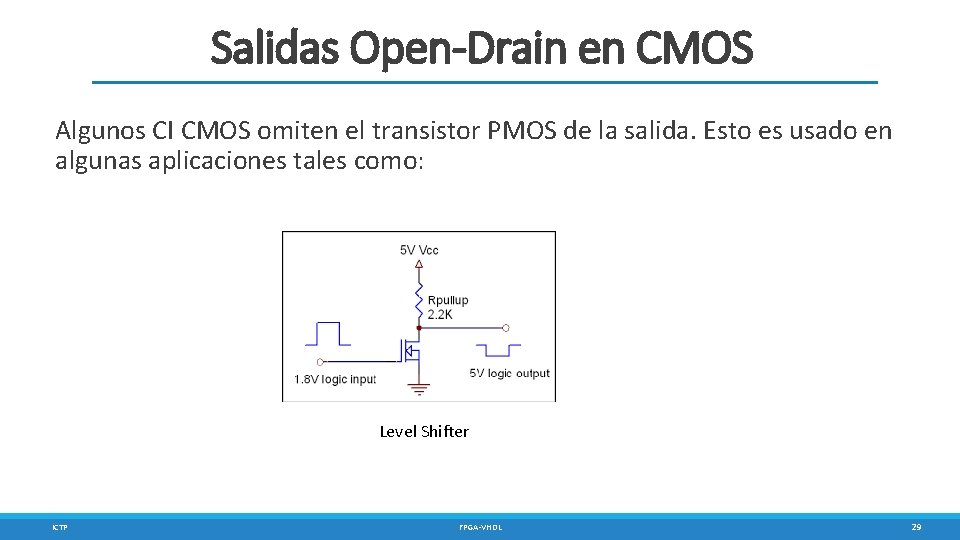

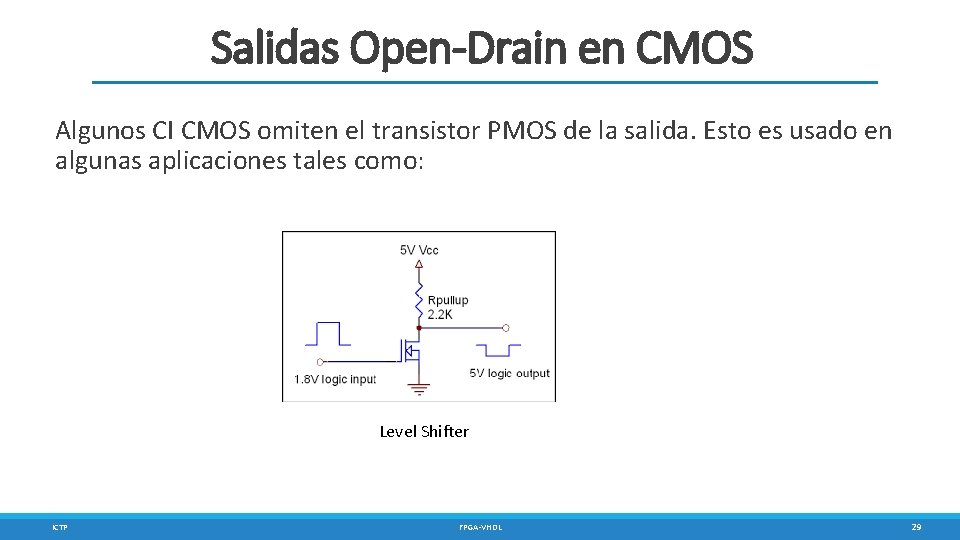

Salidas Open-Drain en CMOS Algunos CI CMOS omiten el transistor PMOS de la salida. Esto es usado en algunas aplicaciones tales como: Level Shifter ICTP FPGA-VHDL 29

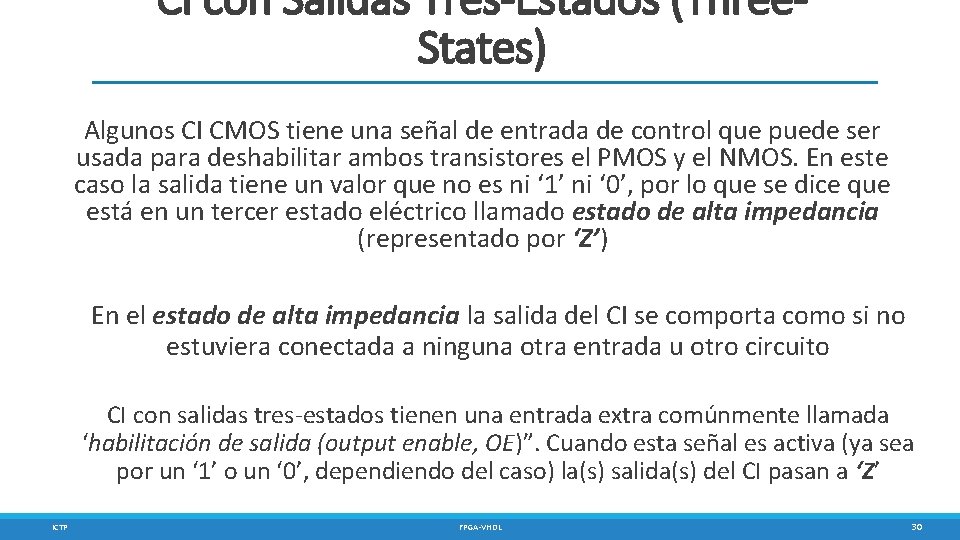

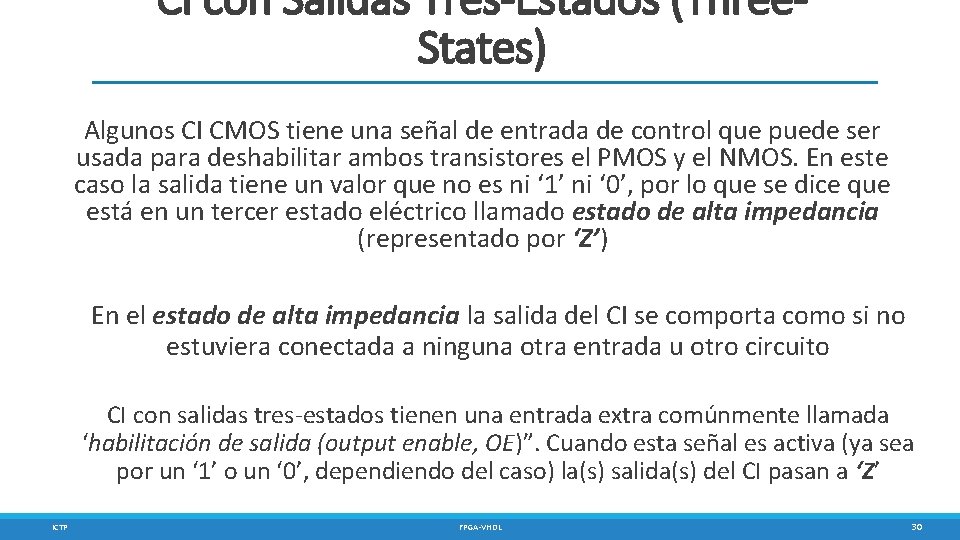

CI con Salidas Tres-Estados (Three. States) Algunos CI CMOS tiene una señal de entrada de control que puede ser usada para deshabilitar ambos transistores el PMOS y el NMOS. En este caso la salida tiene un valor que no es ni ‘ 1’ ni ‘ 0’, por lo que se dice que está en un tercer estado eléctrico llamado estado de alta impedancia (representado por ‘Z’) En el estado de alta impedancia la salida del CI se comporta como si no estuviera conectada a ninguna otra entrada u otro circuito CI con salidas tres-estados tienen una entrada extra comúnmente llamada ‘habilitación de salida (output enable, OE)”. Cuando esta señal es activa (ya sea por un ‘ 1’ o un ‘ 0’, dependiendo del caso) la(s) salida(s) del CI pasan a ‘Z’ ICTP FPGA-VHDL 30

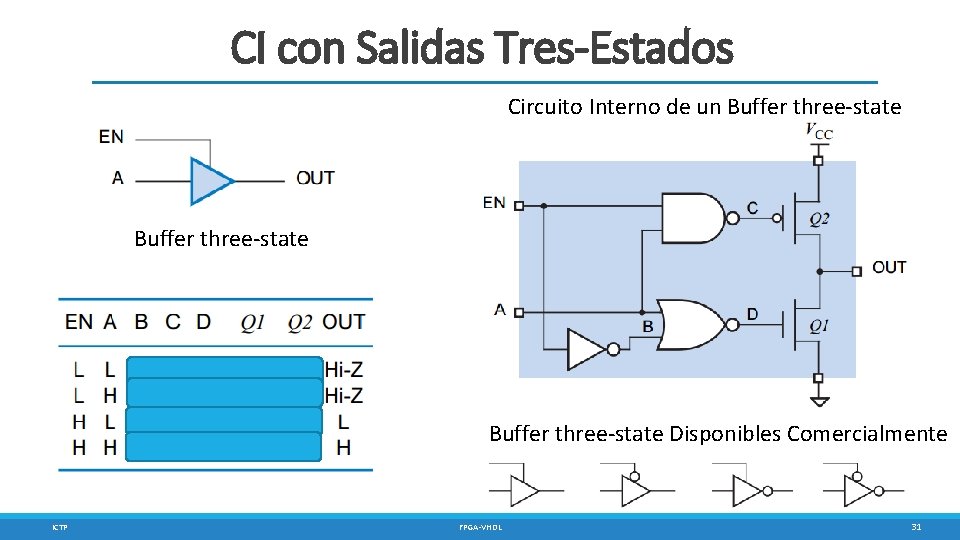

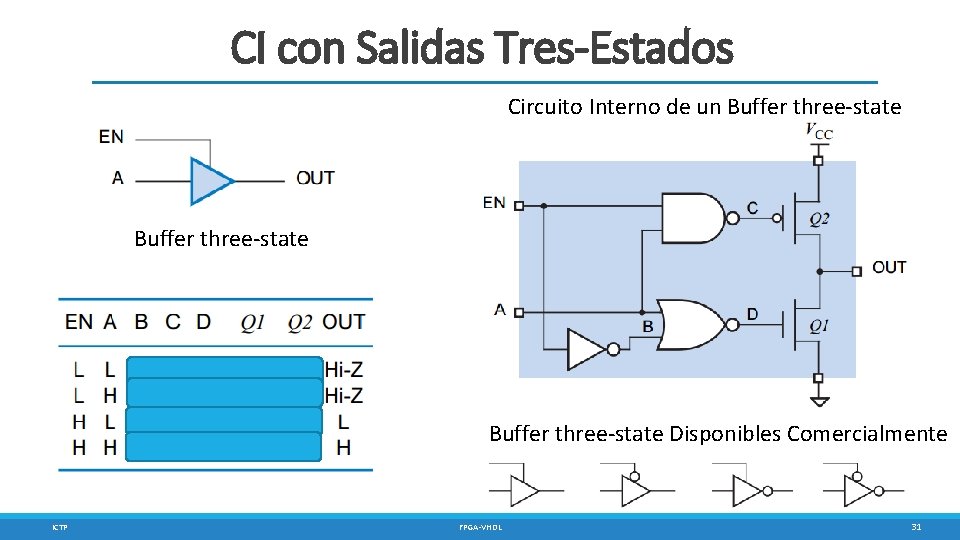

CI con Salidas Tres-Estados Circuito Interno de un Buffer three-state Disponibles Comercialmente ICTP FPGA-VHDL 31

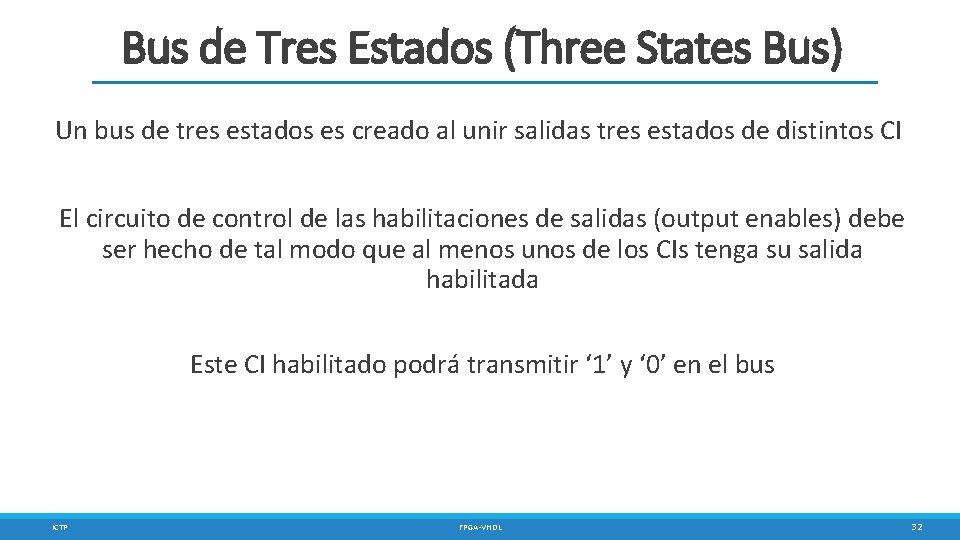

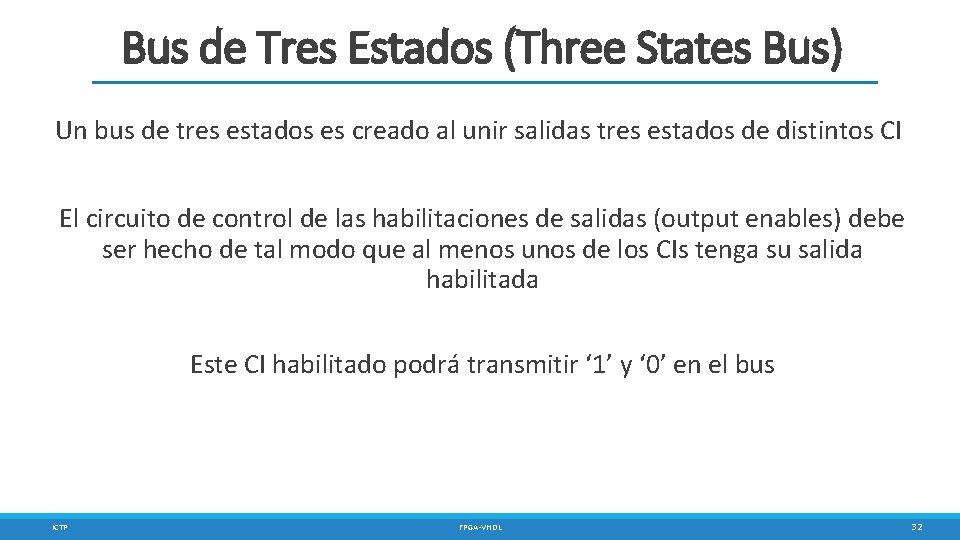

Bus de Tres Estados (Three States Bus) Un bus de tres estados es creado al unir salidas tres estados de distintos CI El circuito de control de las habilitaciones de salidas (output enables) debe ser hecho de tal modo que al menos unos de los CIs tenga su salida habilitada Este CI habilitado podrá transmitir ‘ 1’ y ‘ 0’ en el bus ICTP FPGA-VHDL 32

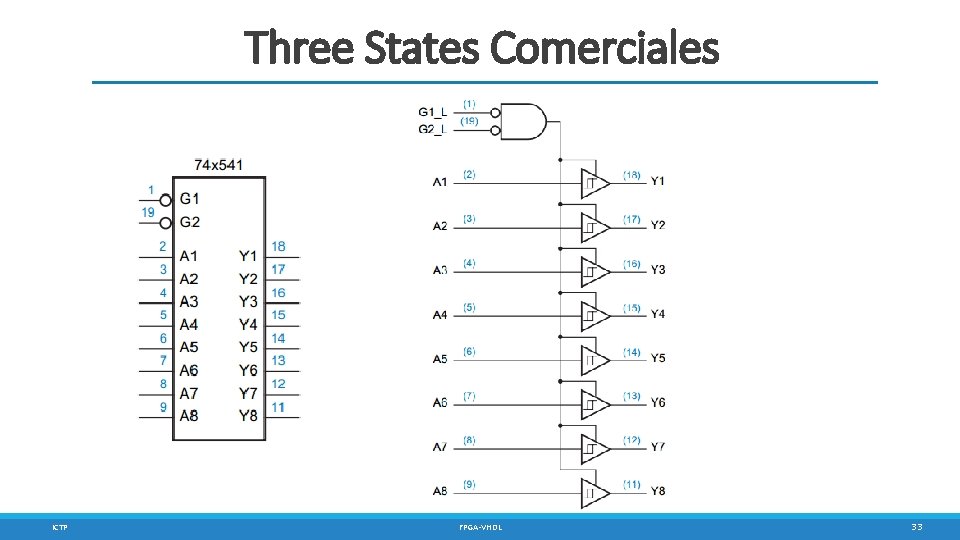

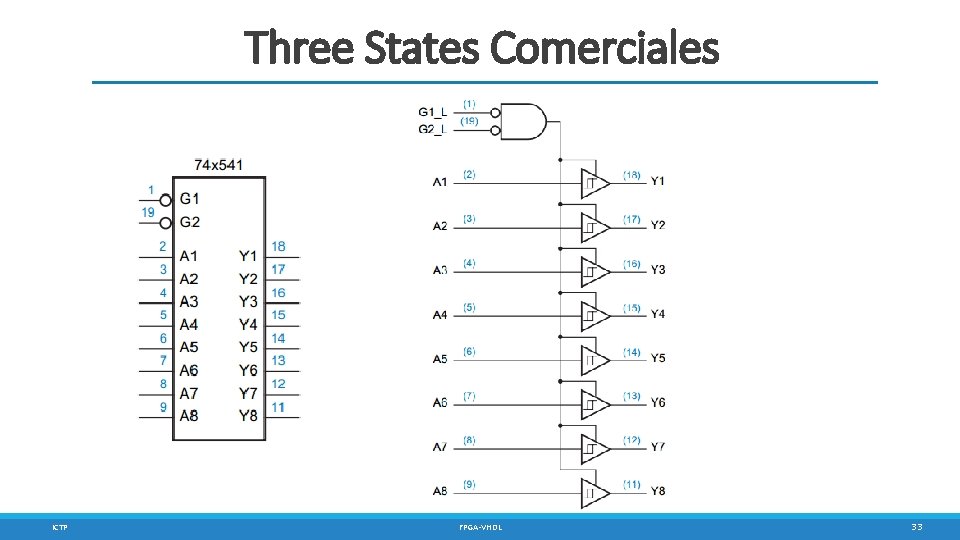

Three States Comerciales ICTP FPGA-VHDL 33

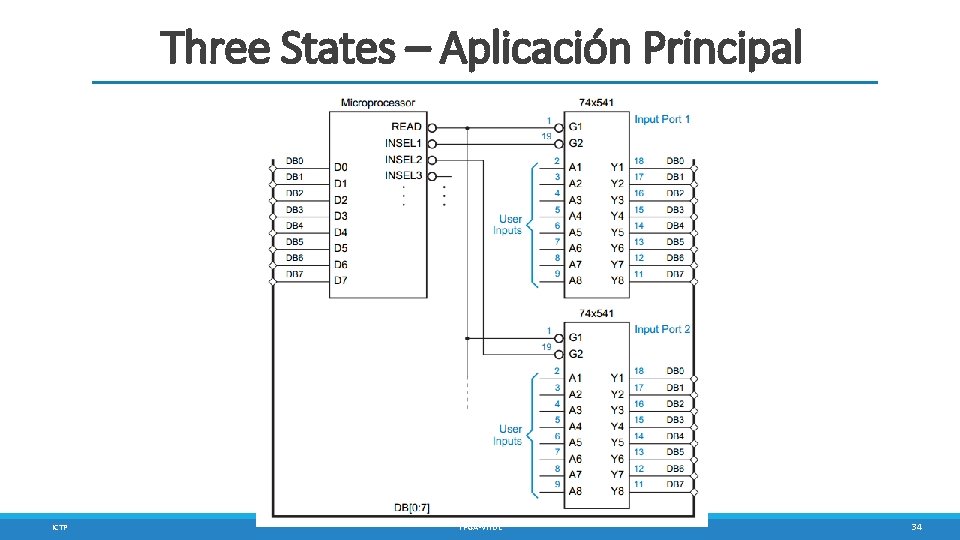

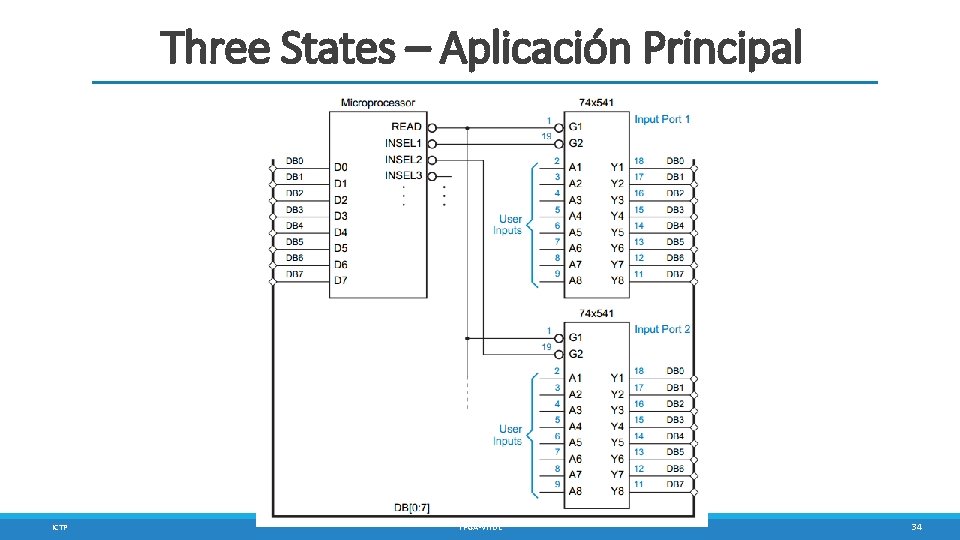

Three States – Aplicación Principal ICTP FPGA-VHDL 34

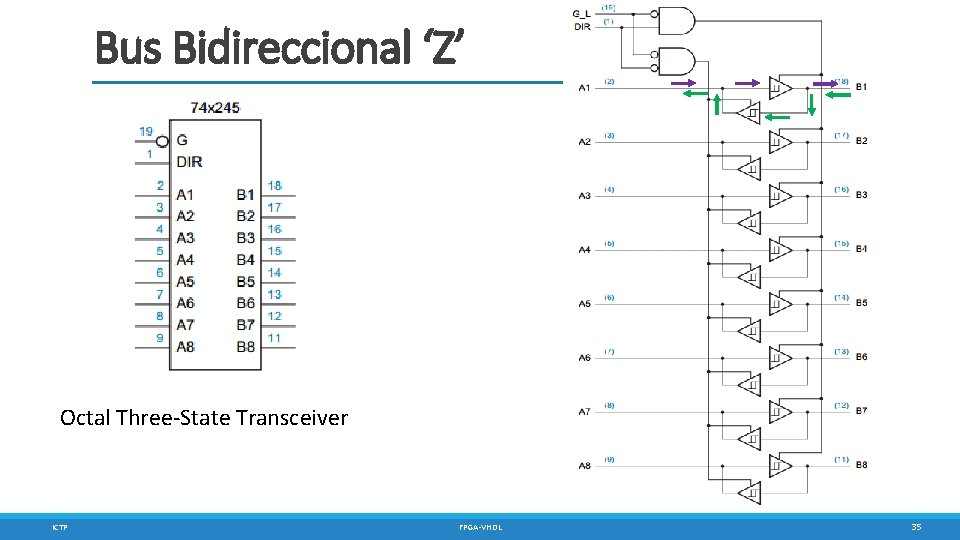

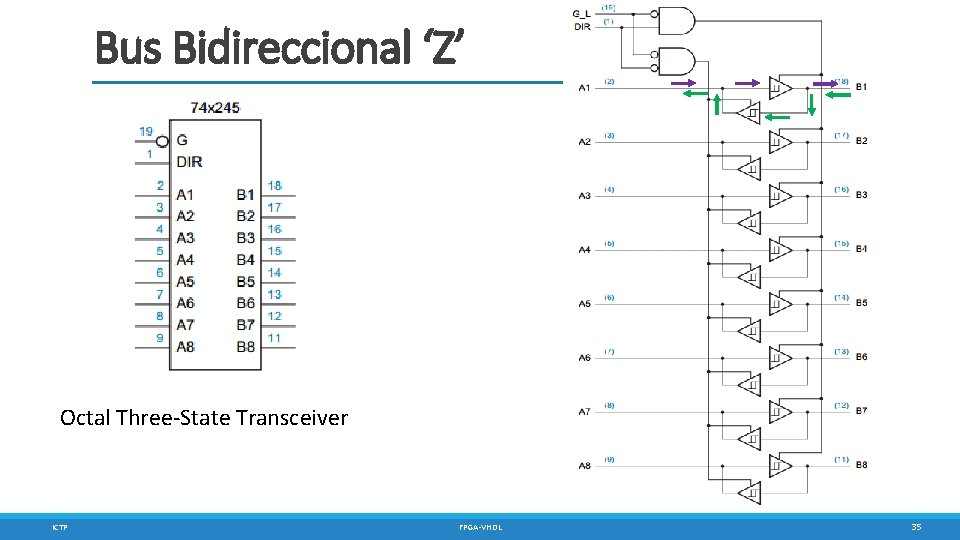

Bus Bidireccional ‘Z’ Octal Three-State Transceiver ICTP FPGA-VHDL 35

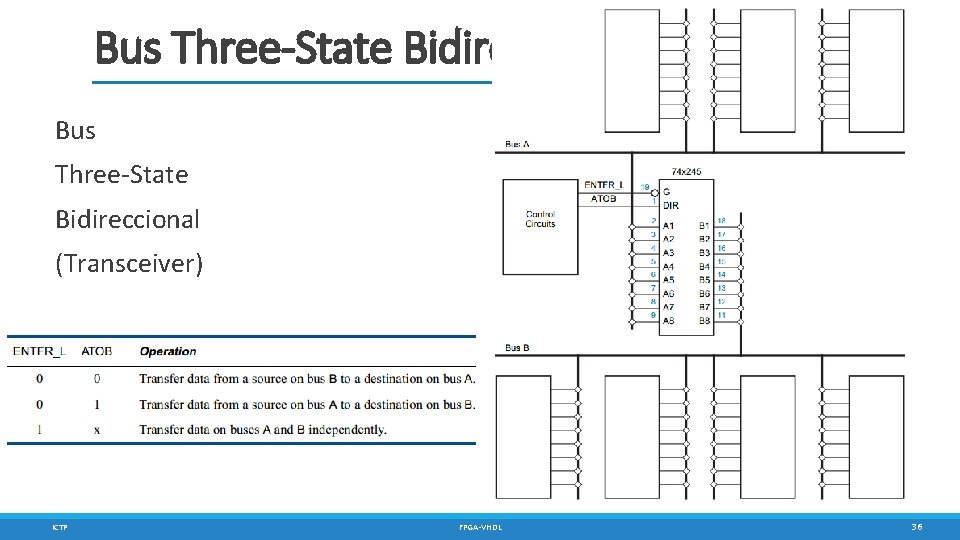

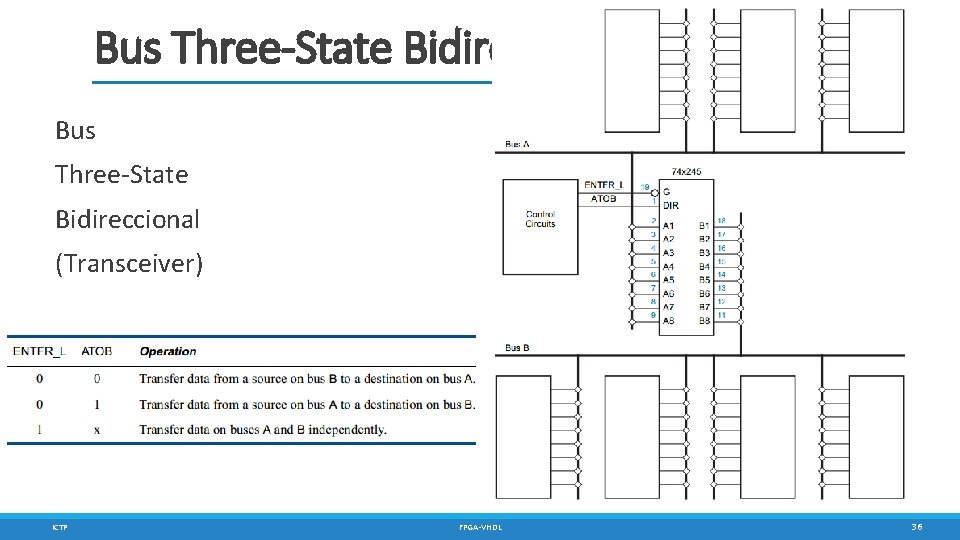

Bus Three-State Bidireccional (Transceiver) ICTP FPGA-VHDL 36

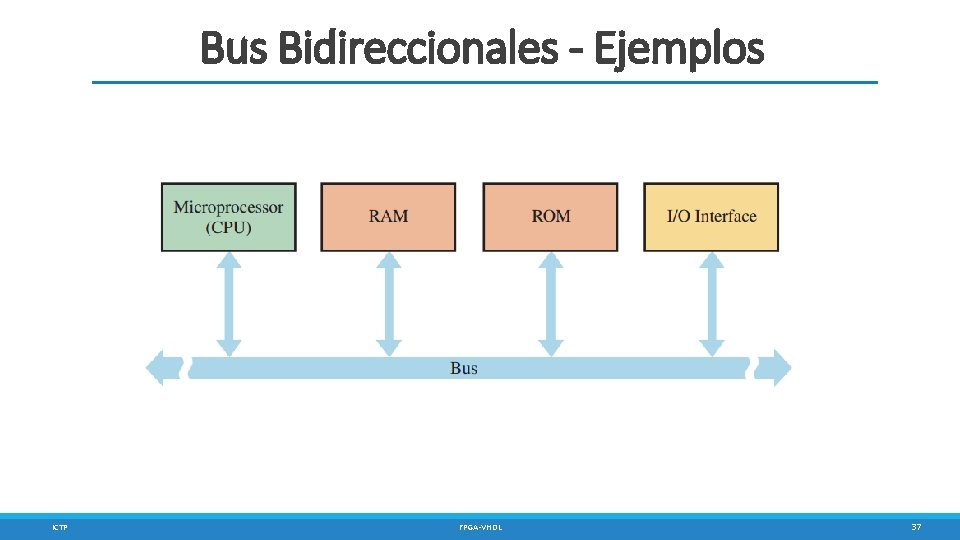

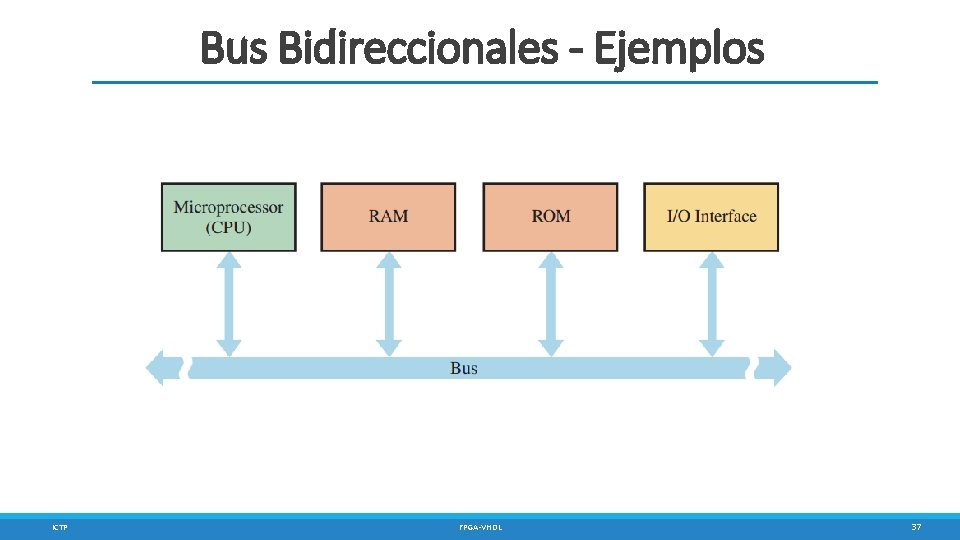

Bus Bidireccionales - Ejemplos ICTP FPGA-VHDL 37

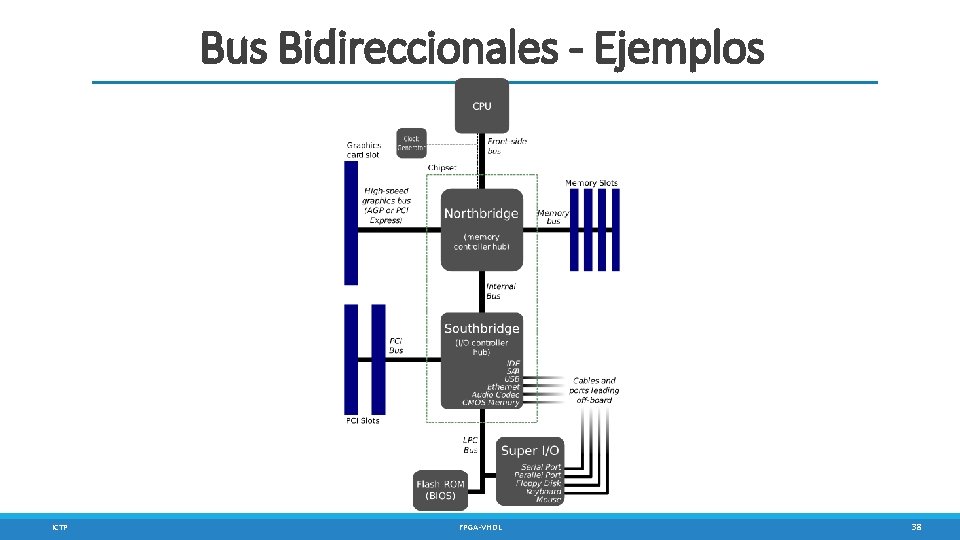

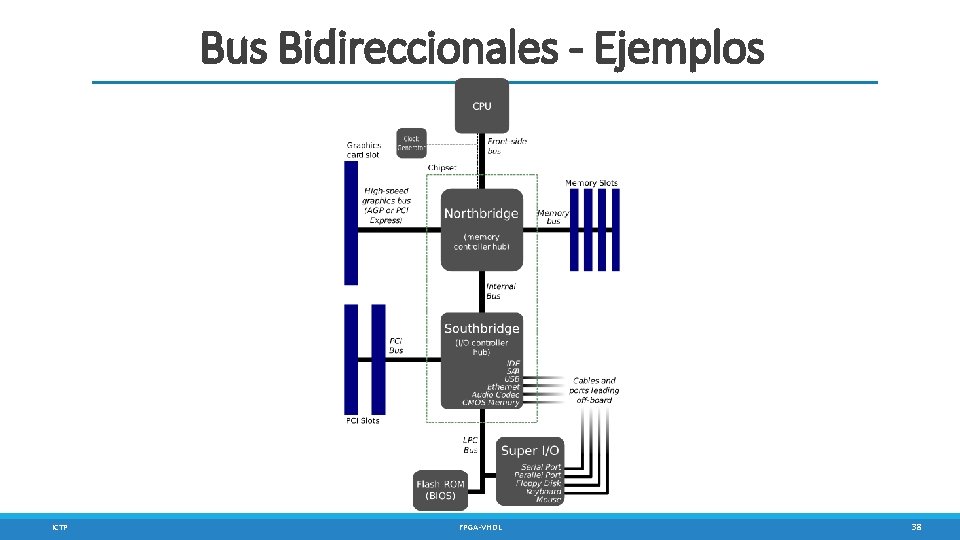

Bus Bidireccionales - Ejemplos ICTP FPGA-VHDL 38

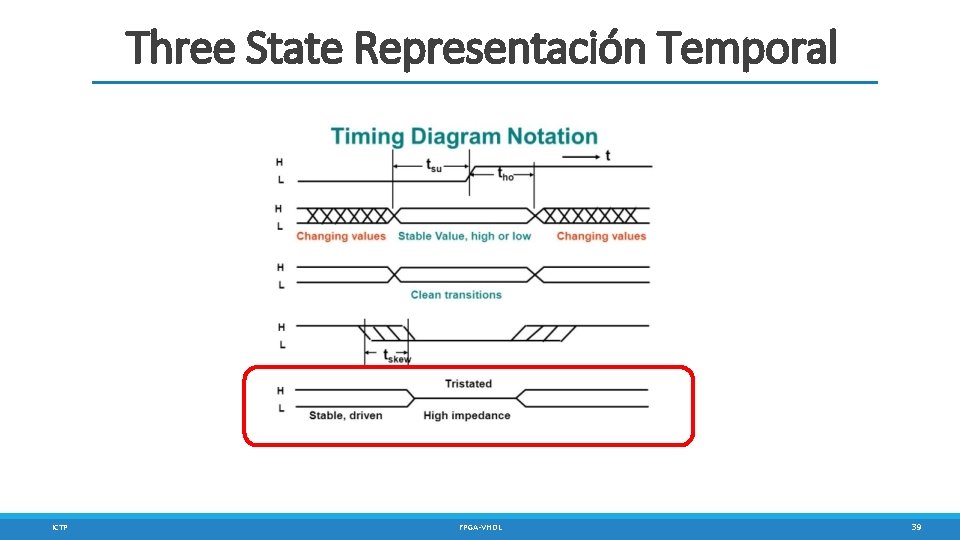

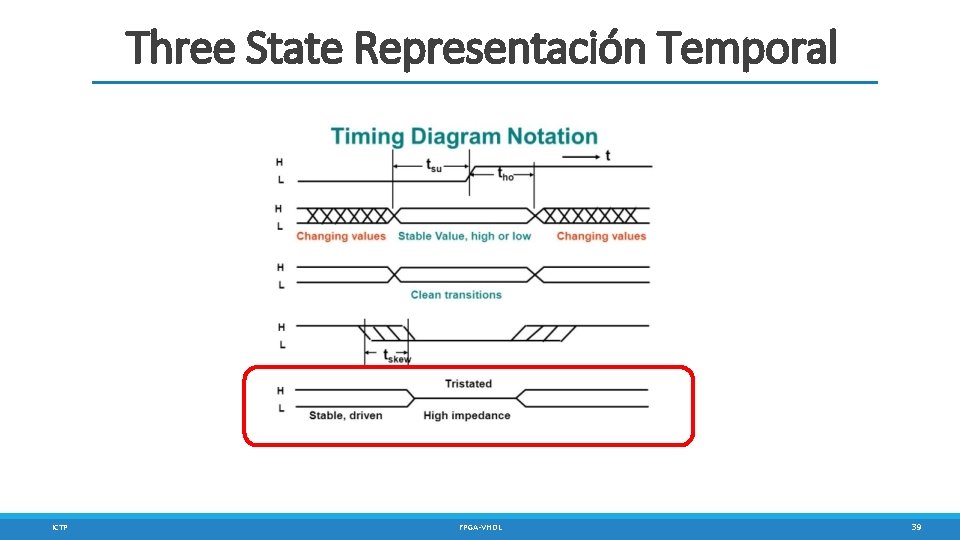

Three State Representación Temporal ICTP FPGA-VHDL 39

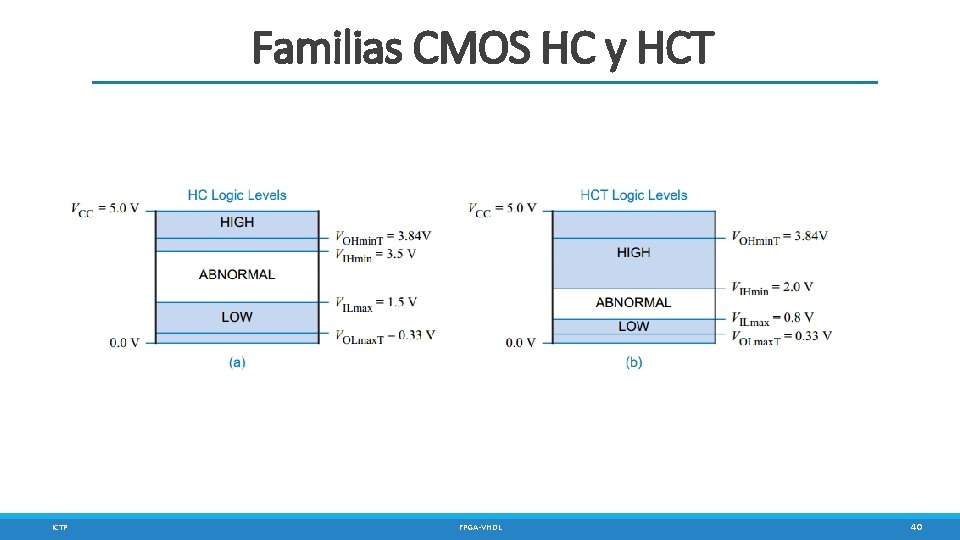

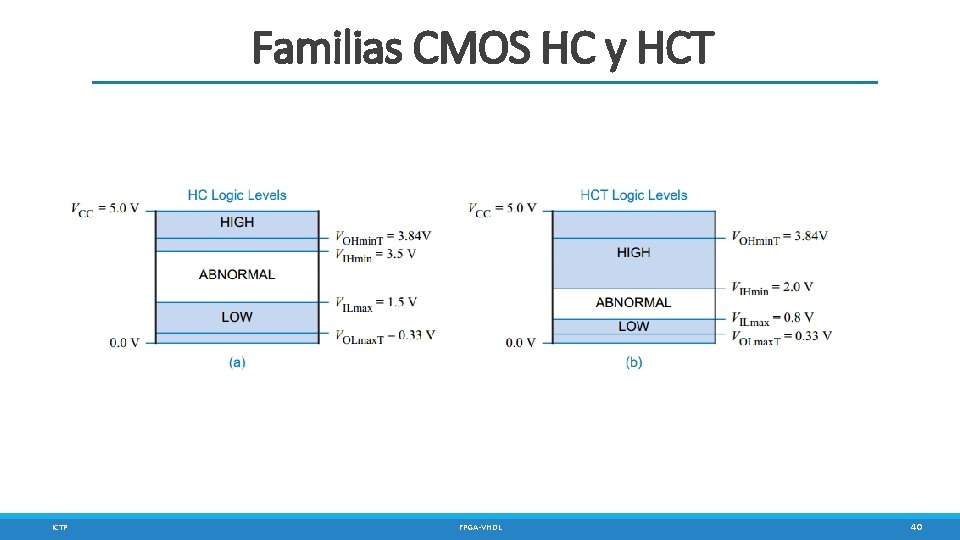

Familias CMOS HC y HCT ICTP FPGA-VHDL 40

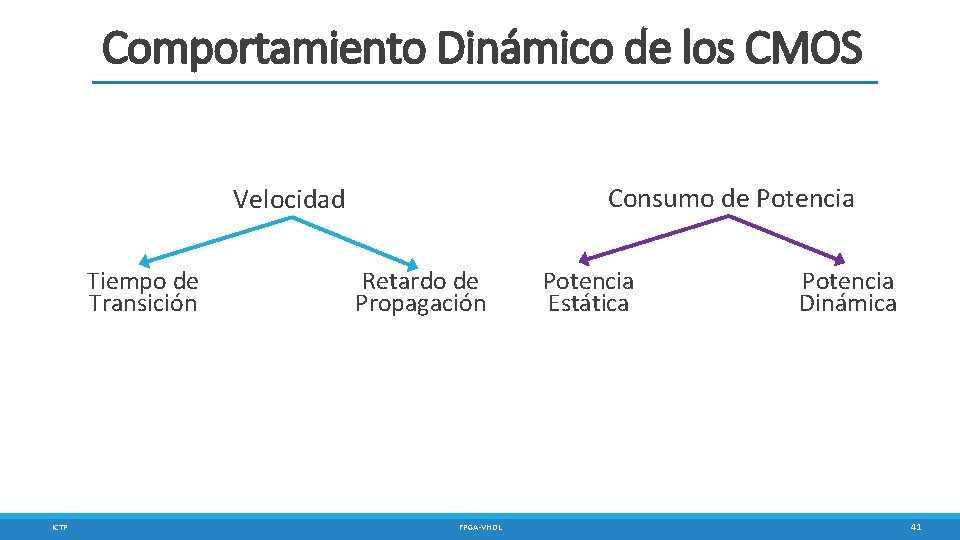

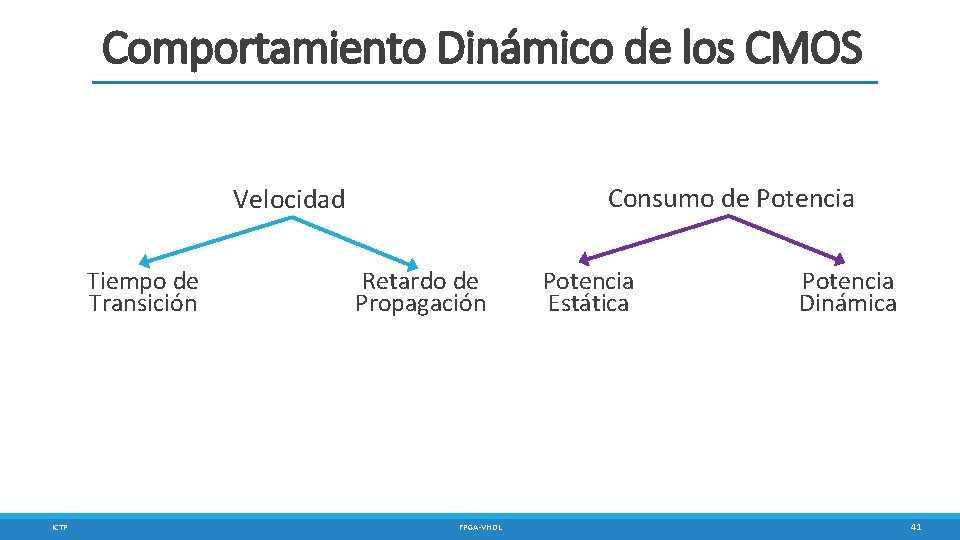

Comportamiento Dinámico de los CMOS Consumo de Potencia Velocidad Tiempo de Transición ICTP Retardo de Propagación FPGA-VHDL Potencia Estática Potencia Dinámica 41

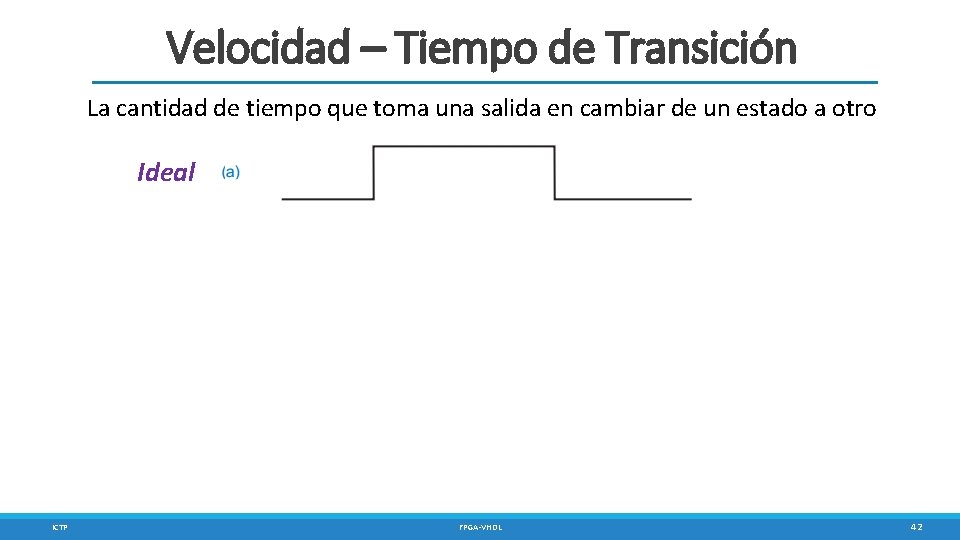

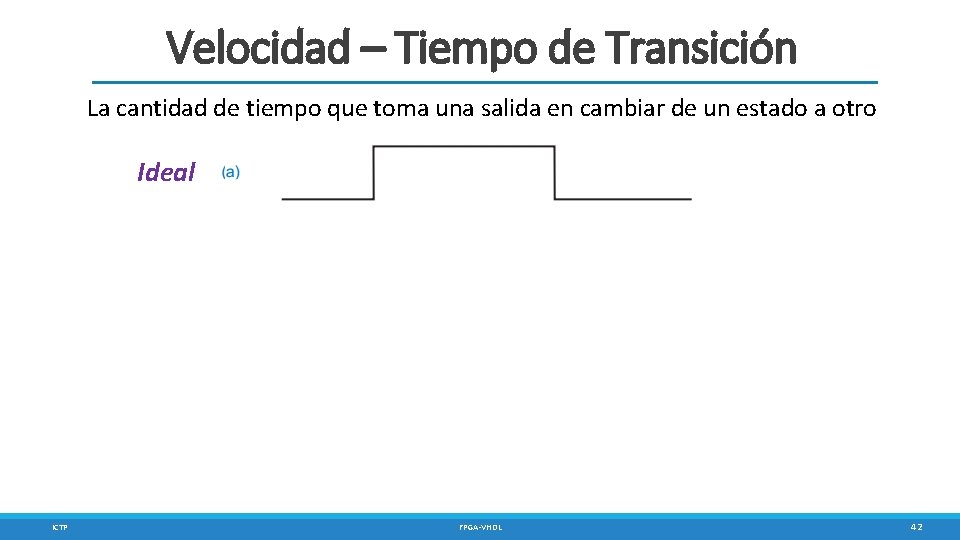

Velocidad – Tiempo de Transición La cantidad de tiempo que toma una salida en cambiar de un estado a otro Ideal Real Mediciones tr 0 ->1 tiempo de subida (rise time) ICTP FPGA-VHDL tf t 1 ->0 tiempo de bajada (fall time) 42

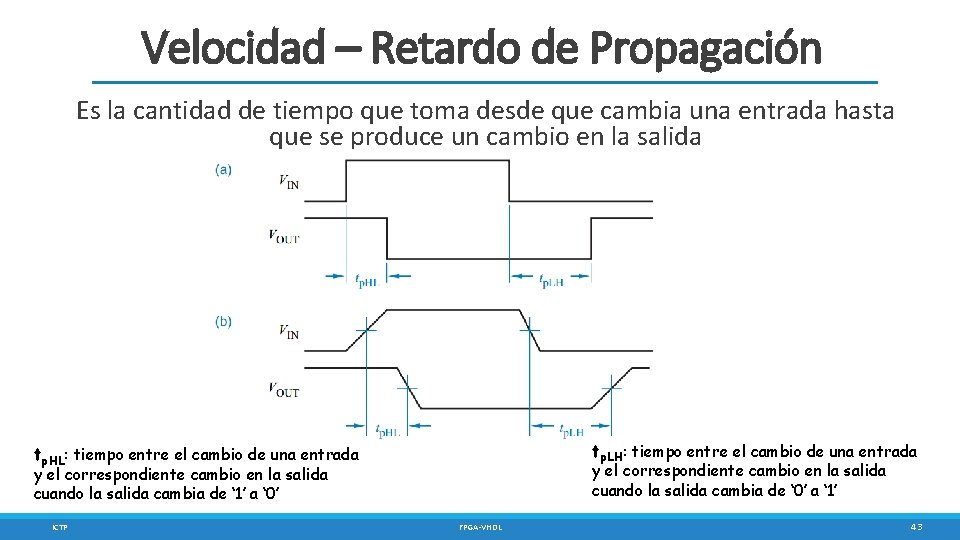

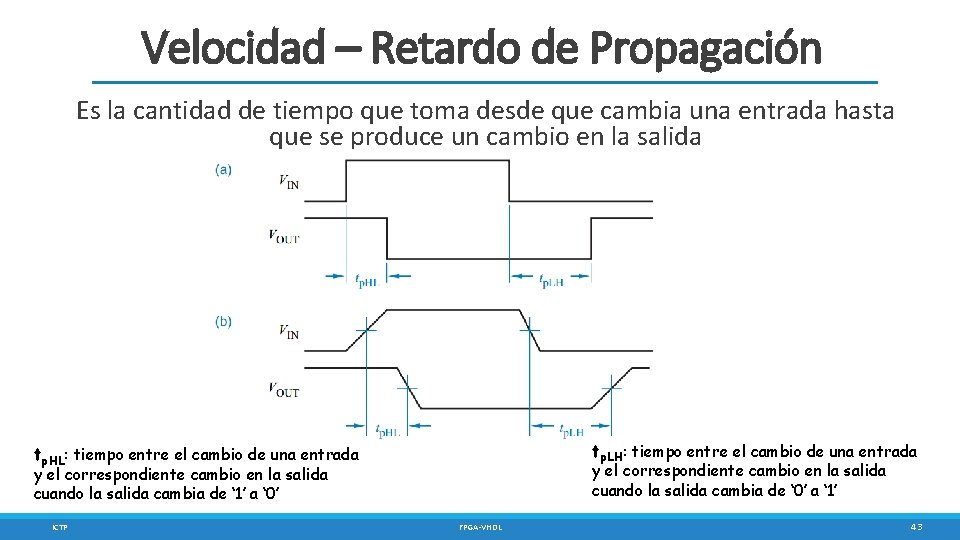

Velocidad – Retardo de Propagación Es la cantidad de tiempo que toma desde que cambia una entrada hasta que se produce un cambio en la salida tp. LH: tiempo entre el cambio de una entrada tp. HL: tiempo entre el cambio de una entrada y el correspondiente cambio en la salida cuando la salida cambia de ‘ 0’ a ‘ 1’ y el correspondiente cambio en la salida cuando la salida cambia de ‘ 1’ a ‘ 0’ ICTP FPGA-VHDL 43

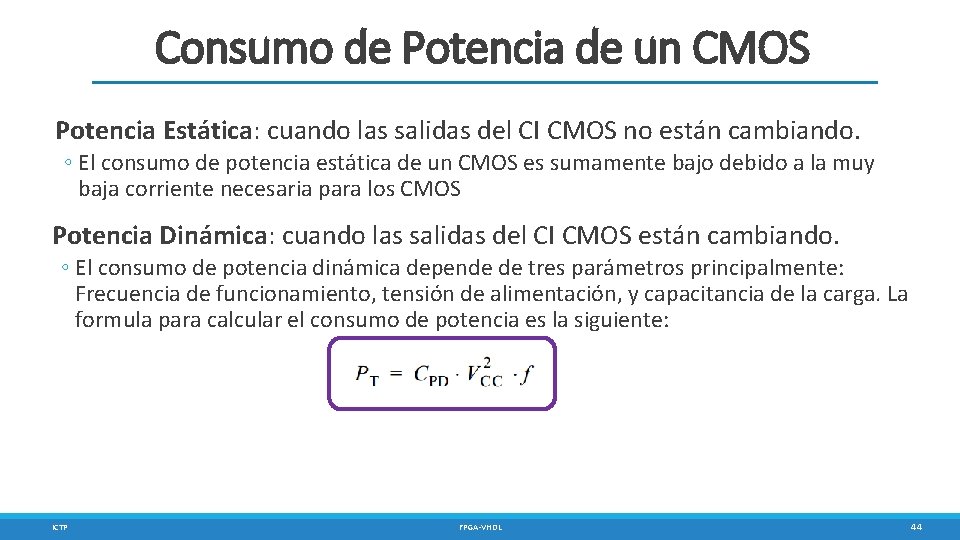

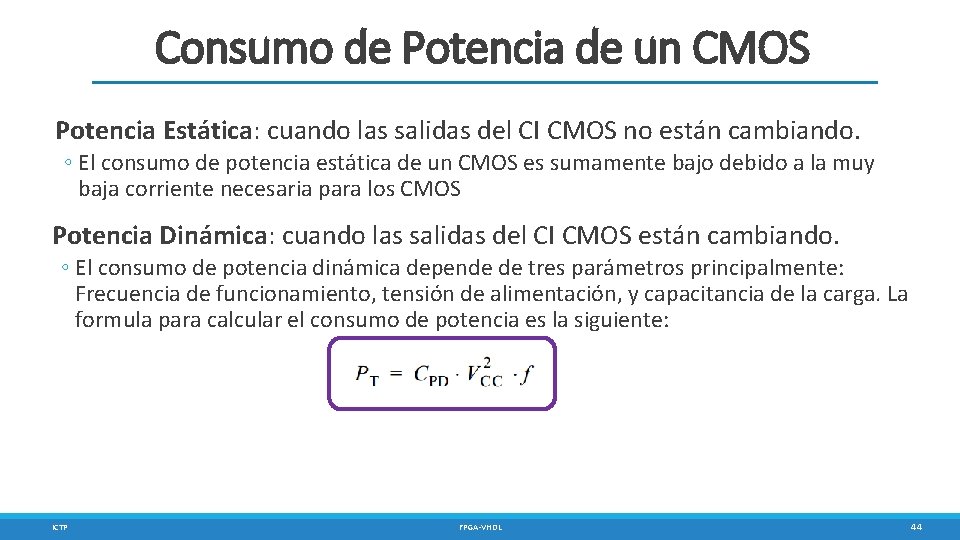

Consumo de Potencia de un CMOS Potencia Estática: cuando las salidas del CI CMOS no están cambiando. ◦ El consumo de potencia estática de un CMOS es sumamente bajo debido a la muy baja corriente necesaria para los CMOS Potencia Dinámica: cuando las salidas del CI CMOS están cambiando. ◦ El consumo de potencia dinámica depende de tres parámetros principalmente: Frecuencia de funcionamiento, tensión de alimentación, y capacitancia de la carga. La formula para calcular el consumo de potencia es la siguiente: ICTP FPGA-VHDL 44

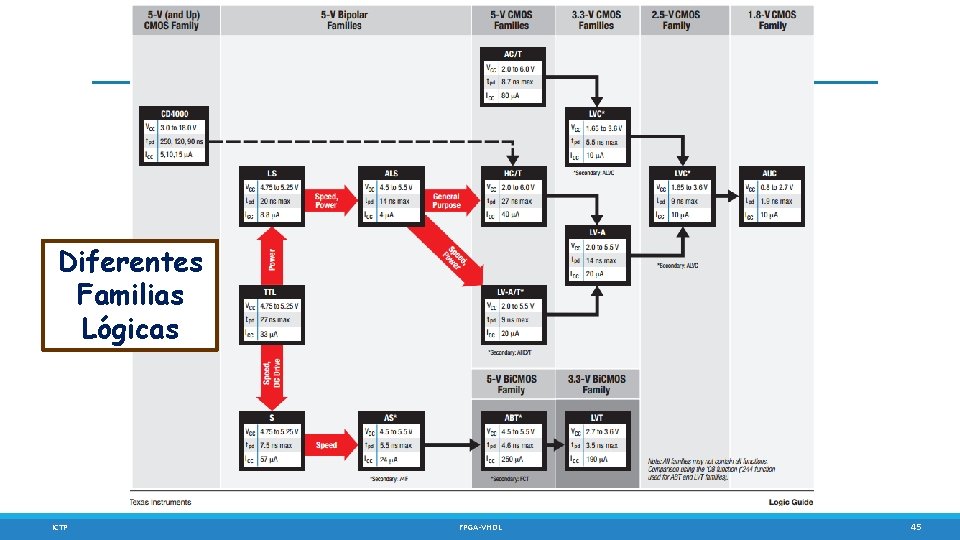

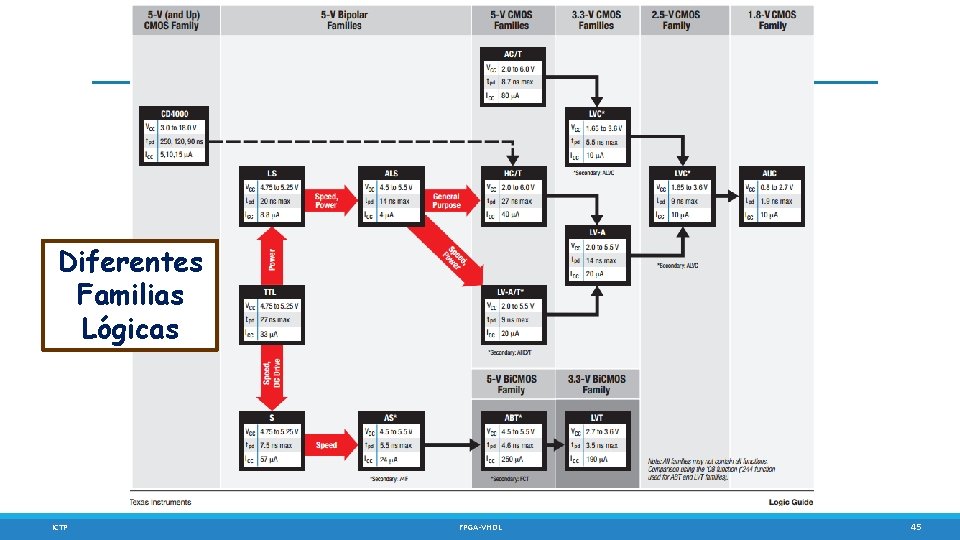

Diferentes Familias Lógicas ICTP FPGA-VHDL 45

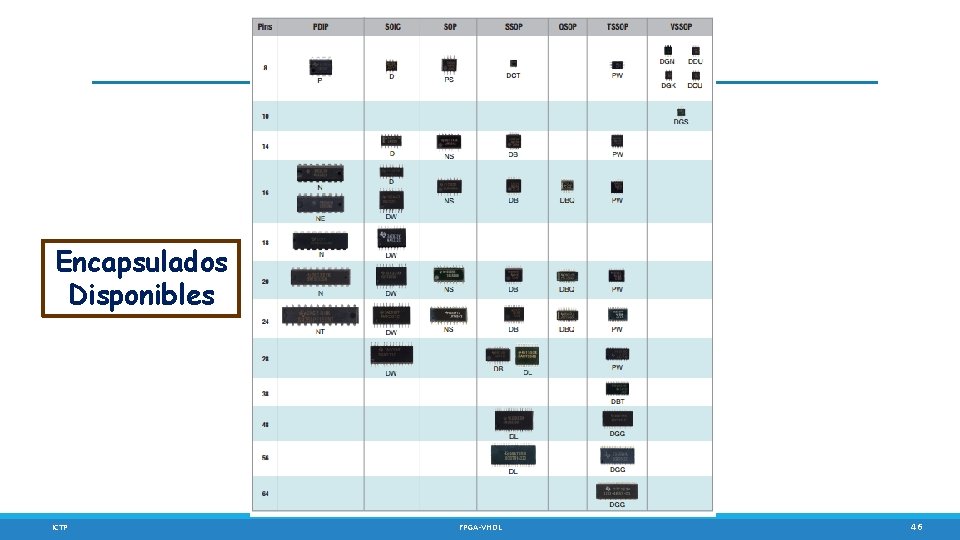

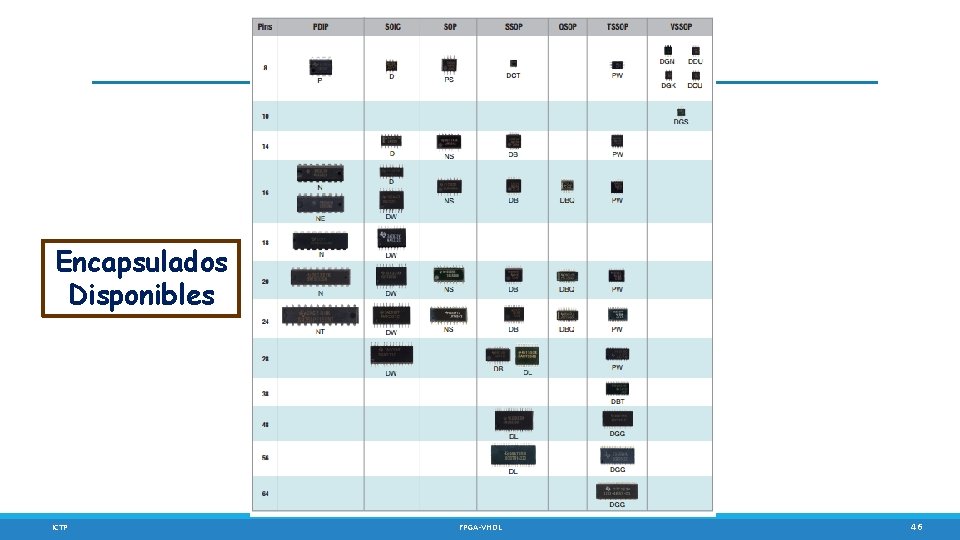

Encapsulados Disponibles ICTP FPGA-VHDL 46

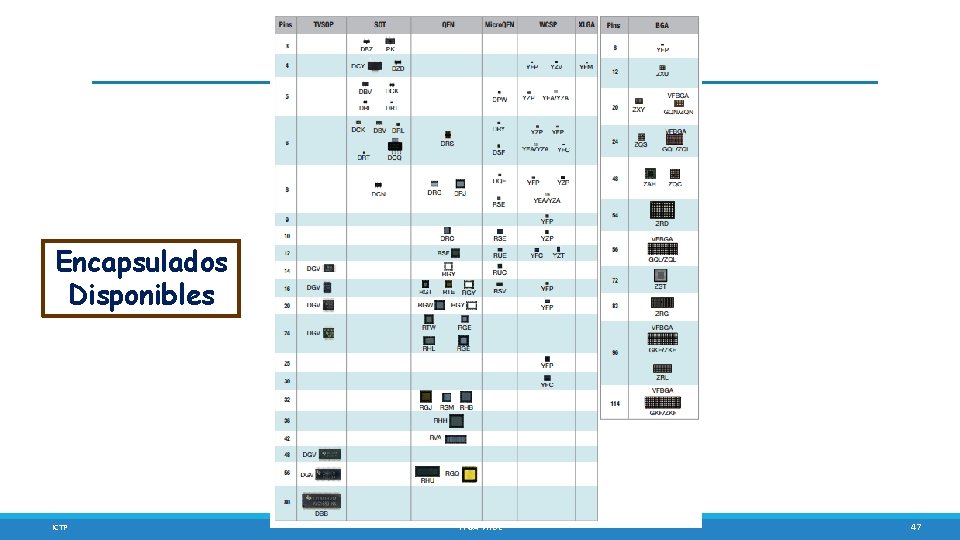

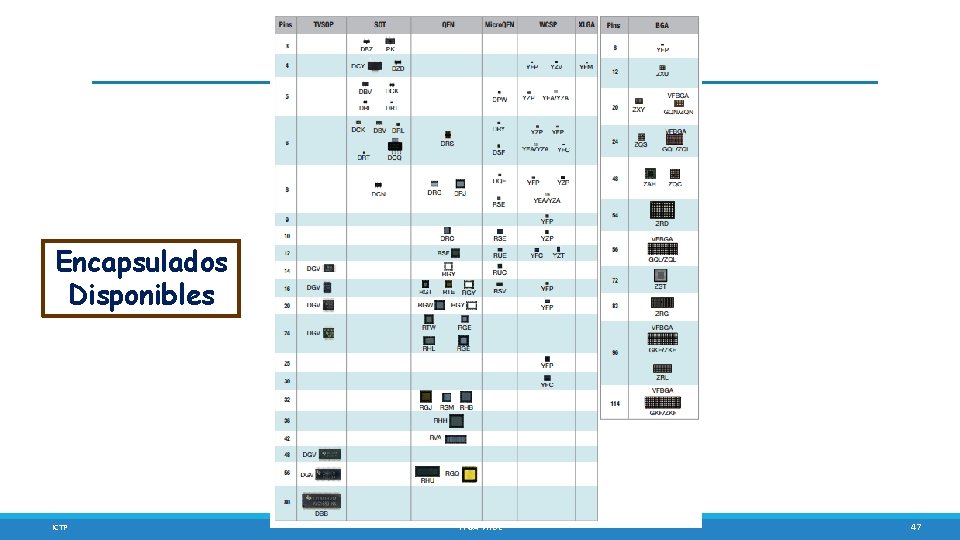

Encapsulados Disponibles ICTP FPGA-VHDL 47

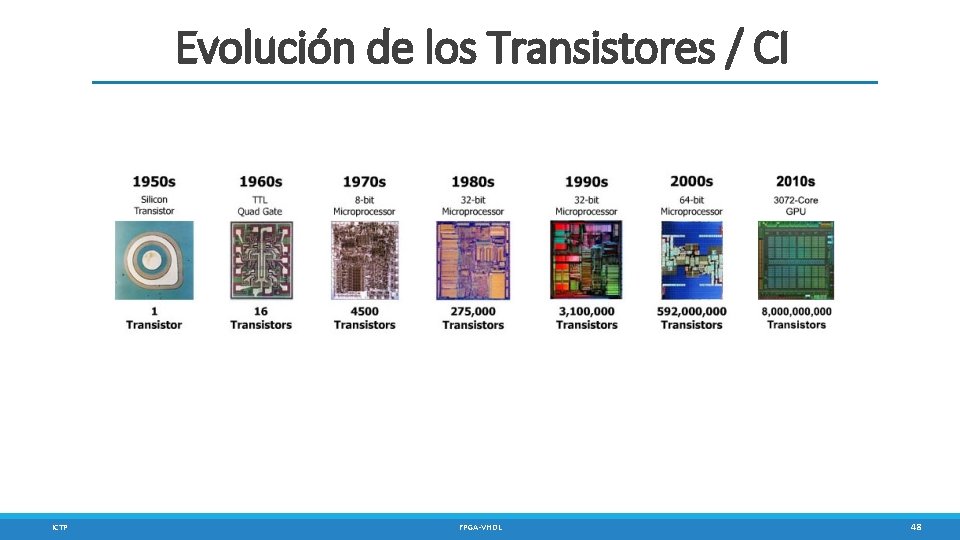

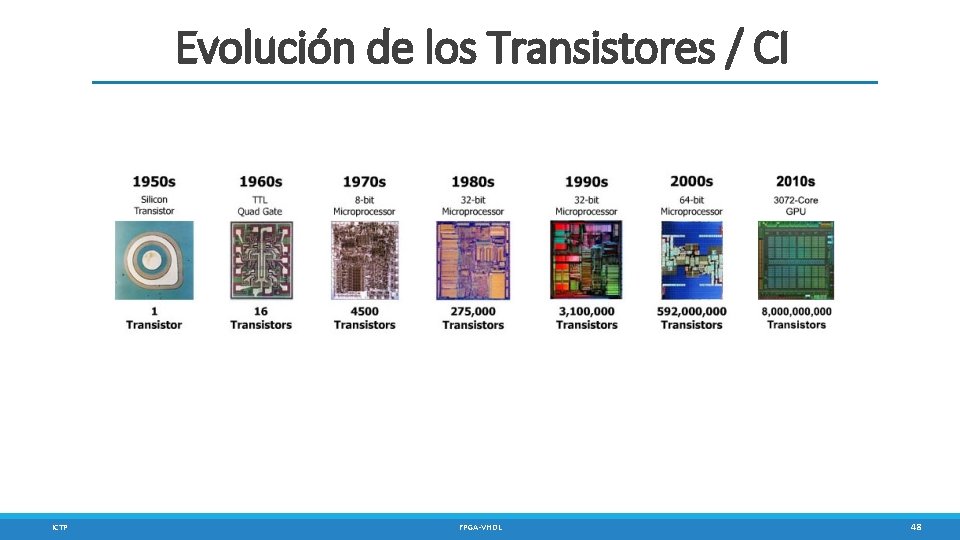

Evolución de los Transistores / CI ICTP FPGA-VHDL 48

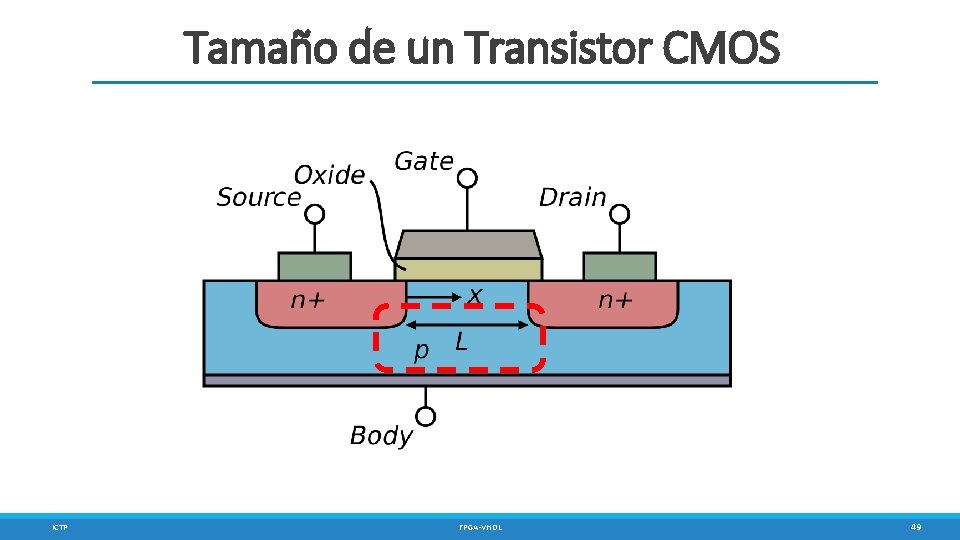

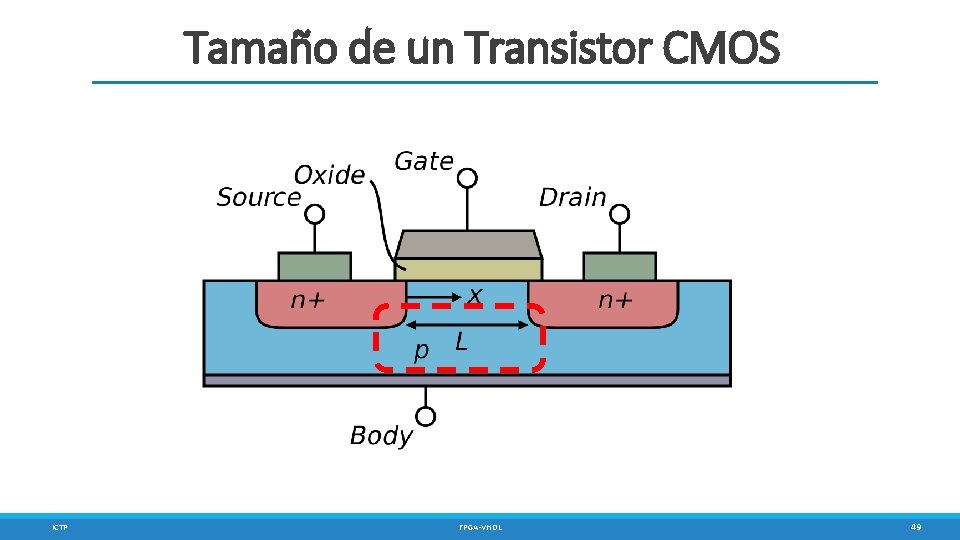

Tamaño de un Transistor CMOS ICTP FPGA-VHDL 49

Histrica

Histrica Que es tecnologa

Que es tecnologa Tecnologa

Tecnologa Plasmidos

Plasmidos Tecnologa en alimentos

Tecnologa en alimentos Tema 1 las familias y las comunidades

Tema 1 las familias y las comunidades Resea orientation

Resea orientation Reemployment

Reemployment Programa resea

Programa resea Programa resea

Programa resea Cuáles son los deberes de la familia cristiana

Cuáles son los deberes de la familia cristiana Benditas sean todas las familias de la tierra

Benditas sean todas las familias de la tierra Caracterización de las familias en colombia

Caracterización de las familias en colombia Familia

Familia Hora santa por las familias mfc

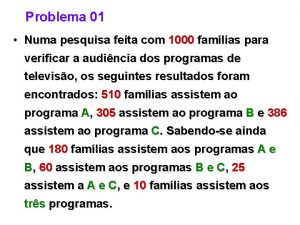

Hora santa por las familias mfc Se encuesta a 150 familias

Se encuesta a 150 familias Familia y vivienda saludable

Familia y vivienda saludable Programa de apoyo a familias para el autoconsumo

Programa de apoyo a familias para el autoconsumo Numa pesquisa feita com 1000 famílias

Numa pesquisa feita com 1000 famílias Que es la familia incompleta

Que es la familia incompleta Instrumentos de cuerda percutida

Instrumentos de cuerda percutida Coral y falso coral diferencias

Coral y falso coral diferencias Particolarità della prima declinazione in latino

Particolarità della prima declinazione in latino Familias disfuncionales neurotigénicas

Familias disfuncionales neurotigénicas Familias interculturales

Familias interculturales Red iberoamericana de trabajo con familias

Red iberoamericana de trabajo con familias Fortaleciendo familias en la fe

Fortaleciendo familias en la fe Familia evitadora de conflictos

Familia evitadora de conflictos Infoeduca familias

Infoeduca familias Programa de familias y viviendas saludables

Programa de familias y viviendas saludables Familias de microcontroladores

Familias de microcontroladores Familias fusionadas

Familias fusionadas Bienvenidos familias

Bienvenidos familias Familias disgregadas

Familias disgregadas Lanbidez familias profesionales

Lanbidez familias profesionales Lanbidez familias profesionales

Lanbidez familias profesionales Familias uniformadas

Familias uniformadas Familias en accion palmira

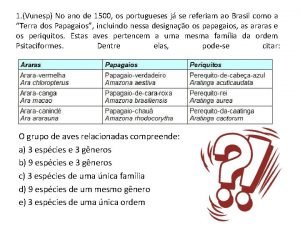

Familias en accion palmira Vunesp no ano de 1500

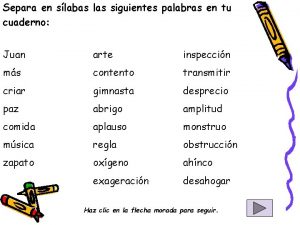

Vunesp no ano de 1500 Palabras en silabas

Palabras en silabas Diferencias entre las niif completas y las niif para pymes

Diferencias entre las niif completas y las niif para pymes Bioarticion

Bioarticion Linea de tiempo de las generaciones de las computadoras

Linea de tiempo de las generaciones de las computadoras Las palabras no se pueden recoger

Las palabras no se pueden recoger Las misiones se hacen

Las misiones se hacen Generacion de computadoras

Generacion de computadoras Edad de la historia

Edad de la historia Obligaciones y contratos mercantiles

Obligaciones y contratos mercantiles Cuáles son las edades en las que se divide la prehistoria

Cuáles son las edades en las que se divide la prehistoria Materi las asetilin

Materi las asetilin