Slide 1 8 State Machines also called Finite

- Slides: 53

Slide 1 8. State Machines (also called Finite State Machines (FSM), Automaton)

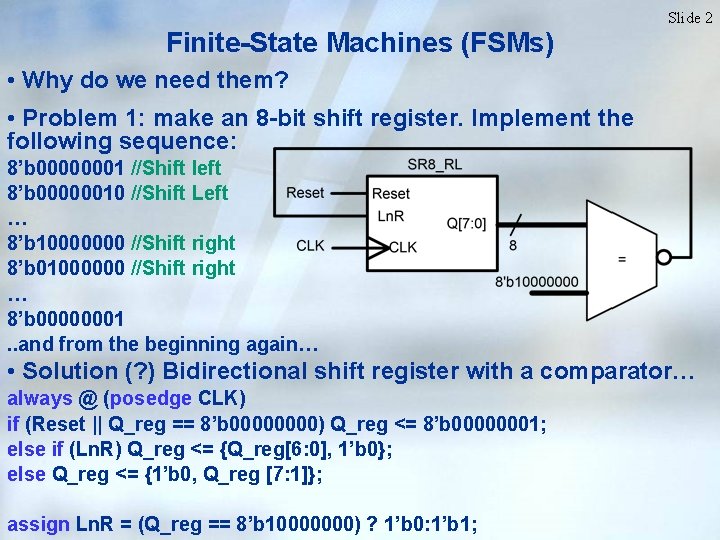

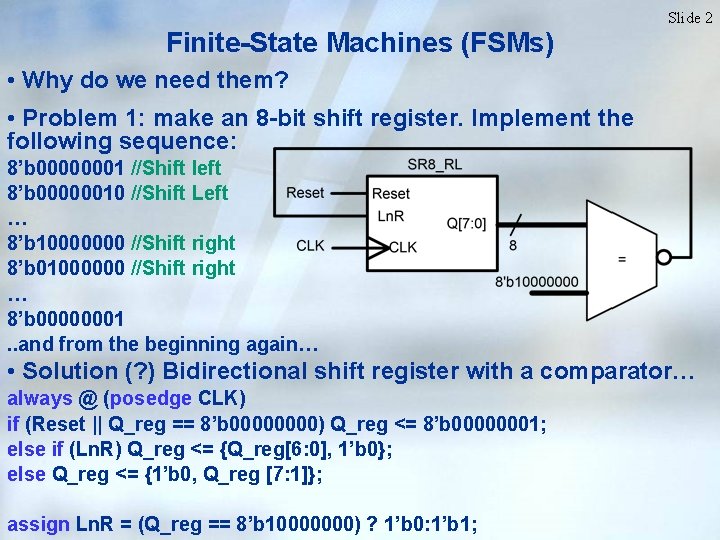

Slide 2 Finite-State Machines (FSMs) • Why do we need them? • Problem 1: make an 8 -bit shift register. Implement the following sequence: 8’b 00000001 //Shift left 8’b 00000010 //Shift Left … 8’b 10000000 //Shift right 8’b 01000000 //Shift right … 8’b 00000001. . and from the beginning again… • Solution (? ) Bidirectional shift register with a comparator… always @ (posedge CLK) if (Reset || Q_reg == 8’b 0000) Q_reg <= 8’b 00000001; else if (Ln. R) Q_reg <= {Q_reg[6: 0], 1’b 0}; else Q_reg <= {1’b 0, Q_reg [7: 1]}; assign Ln. R = (Q_reg == 8’b 10000000) ? 1’b 0: 1’b 1;

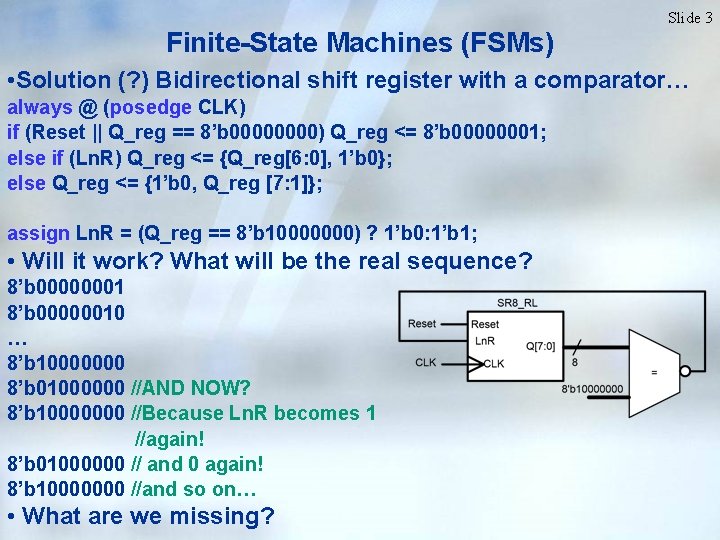

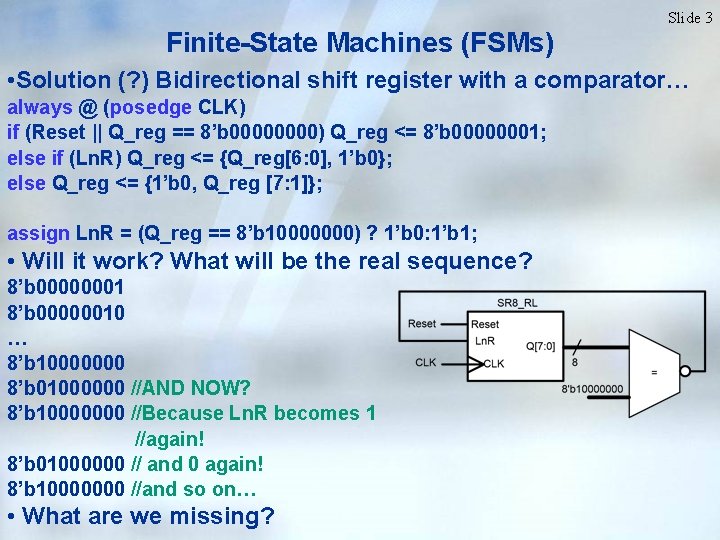

Slide 3 Finite-State Machines (FSMs) • Solution (? ) Bidirectional shift register with a comparator… always @ (posedge CLK) if (Reset || Q_reg == 8’b 0000) Q_reg <= 8’b 00000001; else if (Ln. R) Q_reg <= {Q_reg[6: 0], 1’b 0}; else Q_reg <= {1’b 0, Q_reg [7: 1]}; assign Ln. R = (Q_reg == 8’b 10000000) ? 1’b 0: 1’b 1; • Will it work? What will be the real sequence? 8’b 00000001 8’b 00000010 … 8’b 10000000 8’b 01000000 //AND NOW? 8’b 10000000 //Because Ln. R becomes 1 //again! 8’b 01000000 // and 0 again! 8’b 10000000 //and so on… • What are we missing?

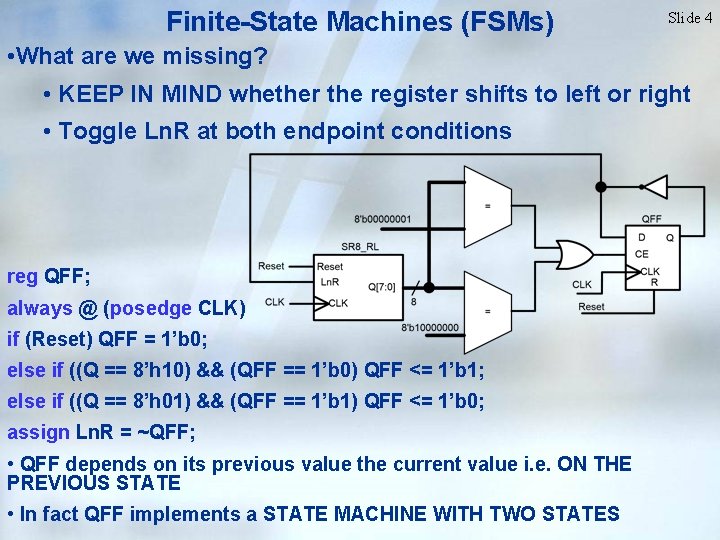

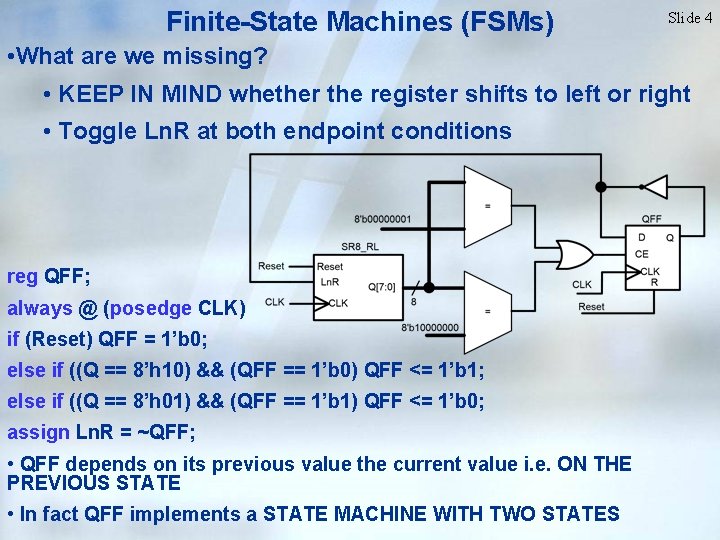

Finite-State Machines (FSMs) Slide 4 • What are we missing? • KEEP IN MIND whether the register shifts to left or right • Toggle Ln. R at both endpoint conditions reg QFF; always @ (posedge CLK) if (Reset) QFF = 1’b 0; else if ((Q == 8’h 10) && (QFF == 1’b 0) QFF <= 1’b 1; else if ((Q == 8’h 01) && (QFF == 1’b 1) QFF <= 1’b 0; assign Ln. R = ~QFF; • QFF depends on its previous value the current value i. e. ON THE PREVIOUS STATE • In fact QFF implements a STATE MACHINE WITH TWO STATES

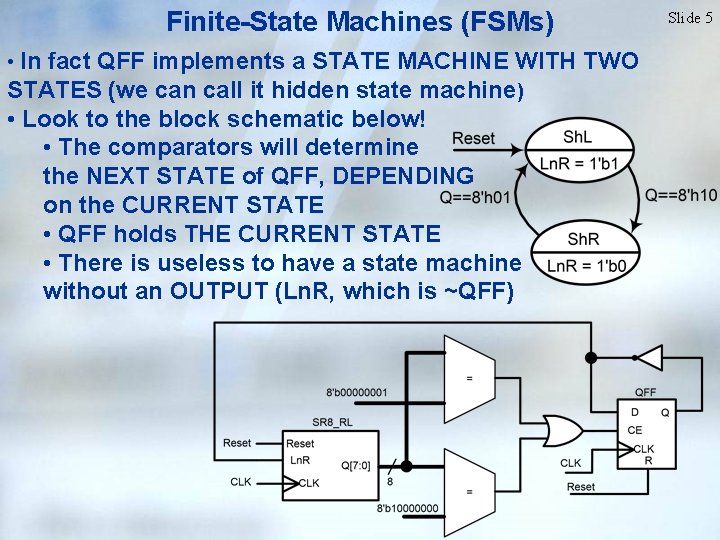

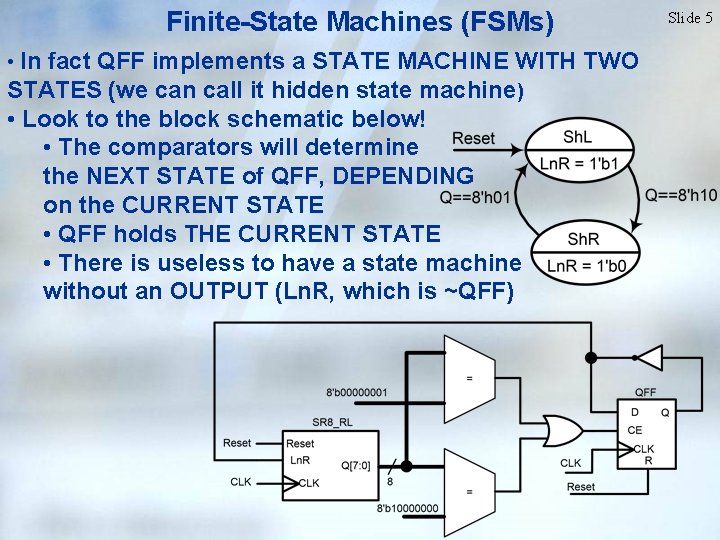

Finite-State Machines (FSMs) • In fact QFF implements a STATE MACHINE WITH TWO STATES (we can call it hidden state machine) • Look to the block schematic below! • The comparators will determine the NEXT STATE of QFF, DEPENDING on the CURRENT STATE • QFF holds THE CURRENT STATE • There is useless to have a state machine without an OUTPUT (Ln. R, which is ~QFF) Slide 5

Slide 6 Finite-State Machines (FSMs) • Problem 2: make a 4 -bit counter, that counts in the following sequence: 1. Count up to 12 2. Count down to 5 3. Count up to 7 and hold counting until Reset becomes active • In other words, imagine it as a task: 1. Go up to the 12 th floor to take some papers from an office 2. Then go down to the 5 th floor to leave the papers to be signed 3. Afterwards go up to the 7 th floor and wait for… • Cannot be done by simply pressing the elevator buttons 12, 5 and 7! • We have here four STATES to keep in mind: • Counting up to 12 • Counting down to 5 • Counting up to 7 • Hold counting at 7 • Think about a two-bit counter that holds the current state

Slide 7 Finite-State Machines (FSMs) • Think about a two-bit counter that holds the current state reg [1: 0] cntst; always @ (posedge CLK) if (Reset) cntst <= 2’b 00; else if ( ((cnt == 4’h. C) && (cntst == 2’b 00)) || //are the conditions OK? ((cnt == 4’h 5) && (cntst == 2’b 01)) || //Check them ((cnt == 4’h 7) && (cntst == 2’b 10)) ) //using simulation! cntst<=cntst+ 2’b 01; //correct conditions are: 4’h. B, 4’h 6 !!! //NOT EVEN THE PREVIOUS PROBLEM/SOLUTION IS CORRECT!!! GO BACK //AFTER FINISHING THIS ONE ! always @ (cntst) begin case (cntst) 2’b 00: begin CE = 1’b 1; Un. D = 1’b 1; end 2’b 01: begin CE = 1’b 1; Un. D = 1’b 0; end … 2’b 11: CE = 1’b 0;

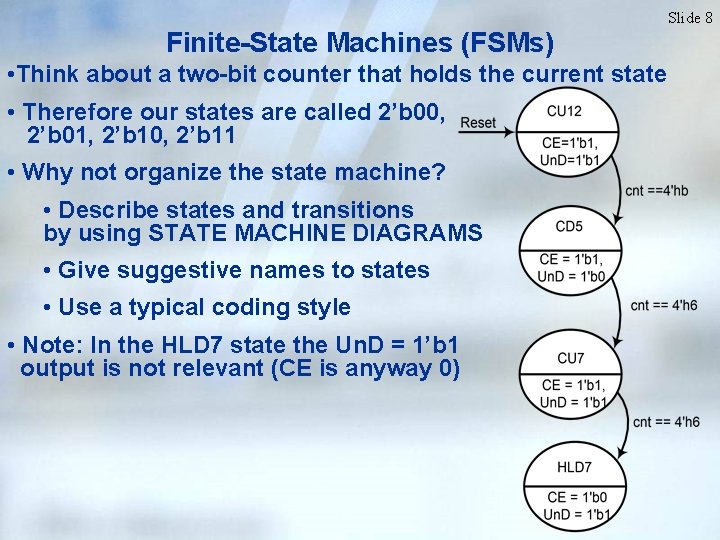

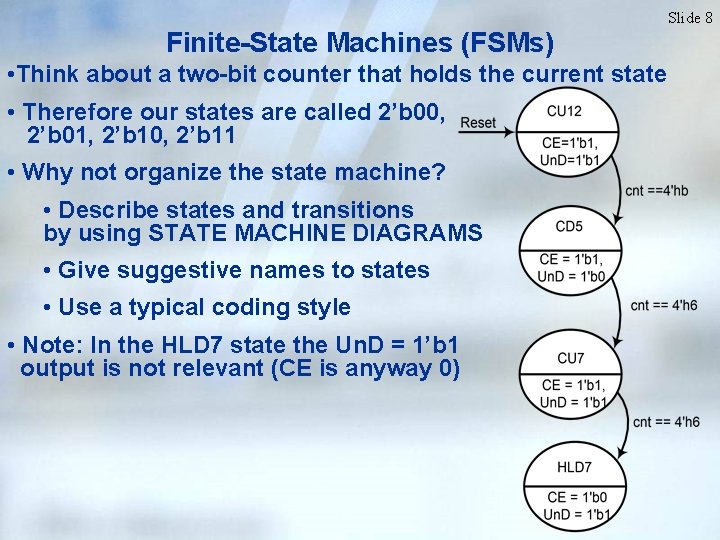

Slide 8 Finite-State Machines (FSMs) • Think about a two-bit counter that holds the current state • Therefore our states are called 2’b 00, 2’b 01, 2’b 10, 2’b 11 • Why not organize the state machine? • Describe states and transitions by using STATE MACHINE DIAGRAMS • Give suggestive names to states • Use a typical coding style • Note: In the HLD 7 state the Un. D = 1’b 1 output is not relevant (CE is anyway 0)

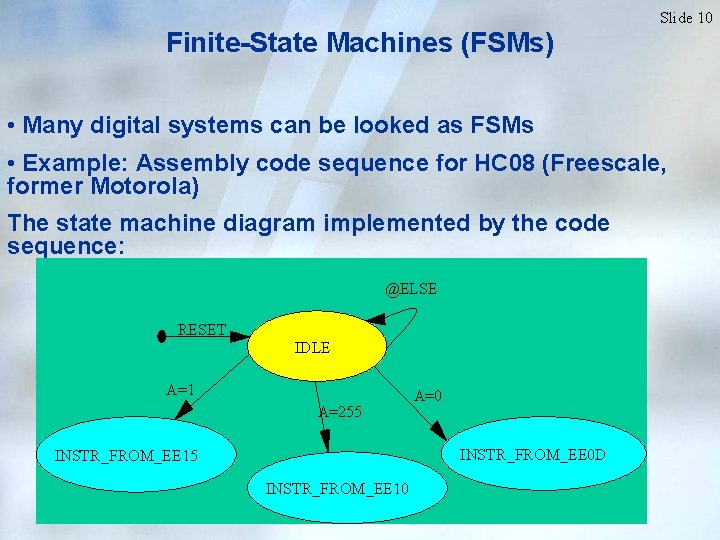

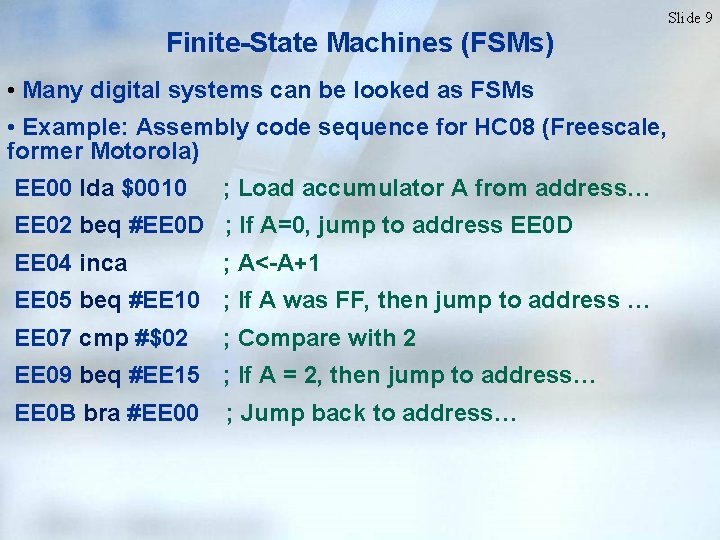

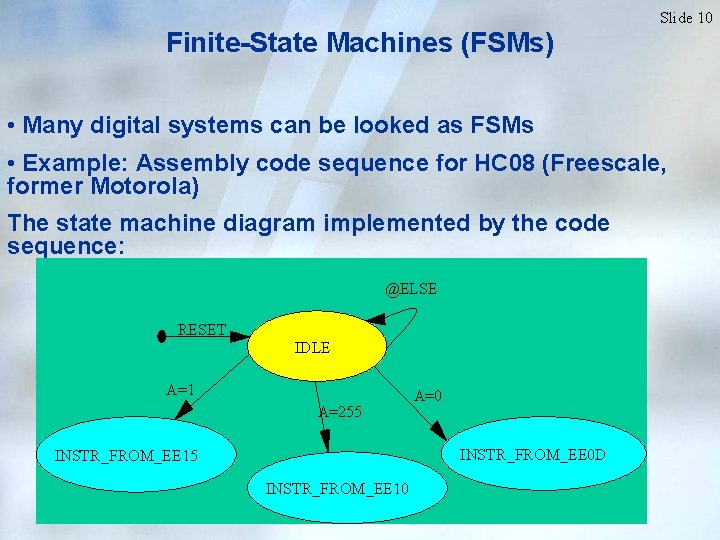

Slide 9 Finite-State Machines (FSMs) • Many digital systems can be looked as FSMs • Example: Assembly code sequence for HC 08 (Freescale, former Motorola) EE 00 lda $0010 ; Load accumulator A from address… EE 02 beq #EE 0 D ; If A=0, jump to address EE 0 D EE 04 inca ; A<-A+1 EE 05 beq #EE 10 ; If A was FF, then jump to address … EE 07 cmp #$02 ; Compare with 2 EE 09 beq #EE 15 ; If A = 2, then jump to address… EE 0 B bra #EE 00 ; Jump back to address…

Slide 10 Finite-State Machines (FSMs) • Many digital systems can be looked as FSMs • Example: Assembly code sequence for HC 08 (Freescale, former Motorola) The state machine diagram implemented by the code sequence: @ELSE RESET IDLE A=1 A=255 A=0 INSTR_FROM_EE 0 D INSTR_FROM_EE 15 INSTR_FROM_EE 10

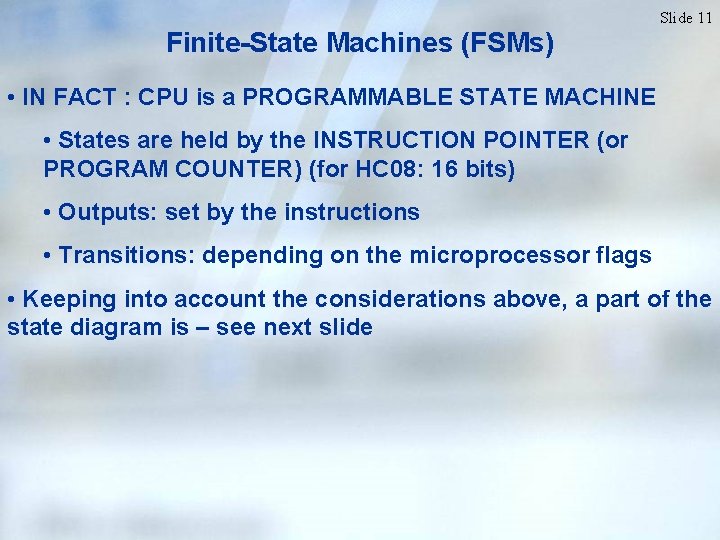

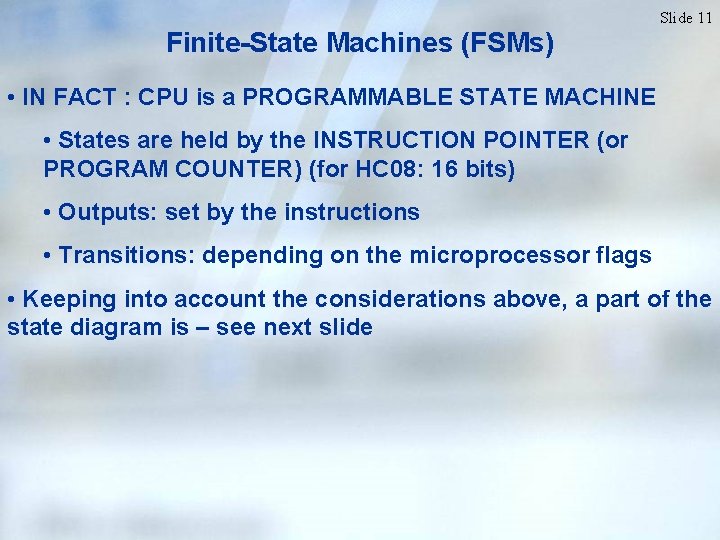

Slide 11 Finite-State Machines (FSMs) • IN FACT : CPU is a PROGRAMMABLE STATE MACHINE • States are held by the INSTRUCTION POINTER (or PROGRAM COUNTER) (for HC 08: 16 bits) • Outputs: set by the instructions • Transitions: depending on the microprocessor flags • Keeping into account the considerations above, a part of the state diagram is – see next slide

Keeping into account the considerations above, a part of the state diagram is: RESET EE 00 PC=PC+2 1 EE 02 PC<=PC+(A=0) AND 11 + (A=0) A=0 A=0 EE 0 D INSTRUCTION EE 04 A<=A+1 PC<=PC+1 1 EE 05 PC<=PC+(A=0) AND 11 + (A=0) AND A=0 Z=0 EE 10 INSTRUCTION A=0 EE 07 Z<='1' when A=2 ELSE '0' 1 EE 09 PC<=PC+(Z=1) AND 12 + (Z=0) Z=1 EE 15 INSTRUCTION Slide 12

Slide 13 Finite-State Machines (FSMs) • Notes: • The state machine diagram above can be described in many ways, depending on the level of abstractization • Each state (instruction) represents in fact a colloection of states/operations for the CPU: • Fetch • Instruction decode • Execute • Some of the operations above can be implemented in Pipeline!

Slide 14 Finite-State Machines (FSMs) • For State machines implemented by CPUs: • Low execution speed: some of the instructions need several clock periods, at a clock speed of 4. . 20 MHZ • But flexible – easy to change the algorithm • For state machines implemented on FPGAs or ASICs: • Very fast (A decision can be taken in a single clock period, at a clock frequency of 50. . 200 MHz • But rigid – changing the algorithm to be implemented may need to redesign the state machine • Therefore: design the state machine to be as readable as possible!

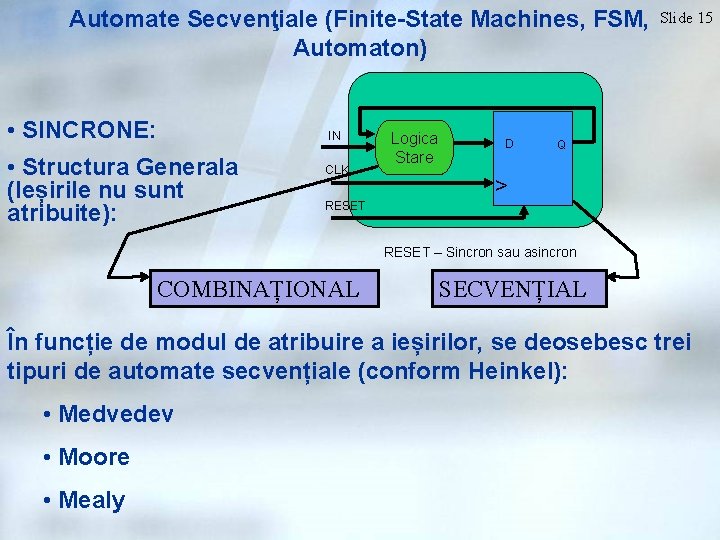

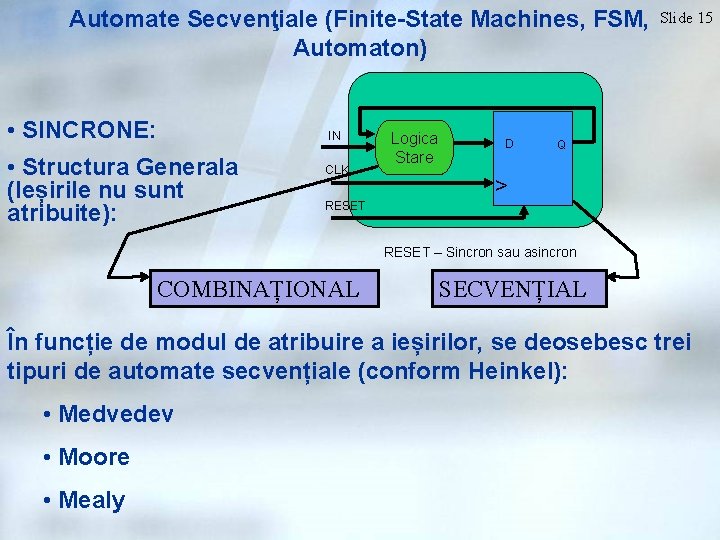

Automate Secvenţiale (Finite-State Machines, FSM, Automaton) • SINCRONE: IN • Structura Generala (Ieșirile nu sunt atribuite): CLK Logica Stare D Slide 15 Q > RESET – Sincron sau asincron COMBINAȚIONAL SECVENȚIAL În funcție de modul de atribuire a ieșirilor, se deosebesc trei tipuri de automate secvențiale (conform Heinkel): • Medvedev • Moore • Mealy

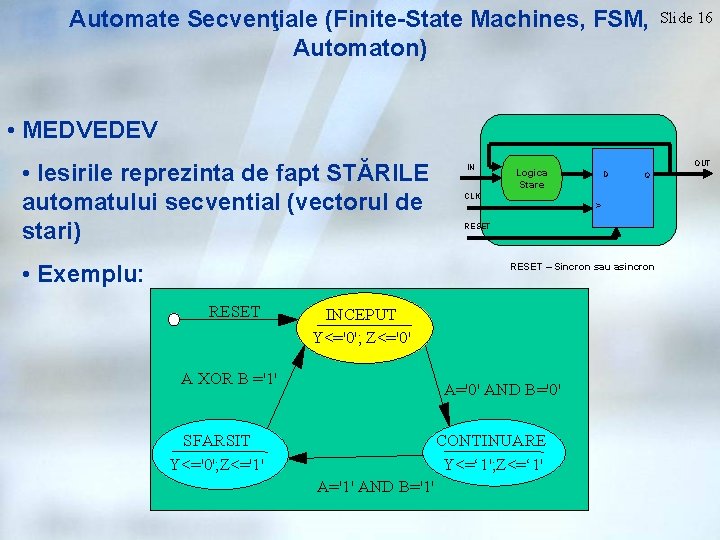

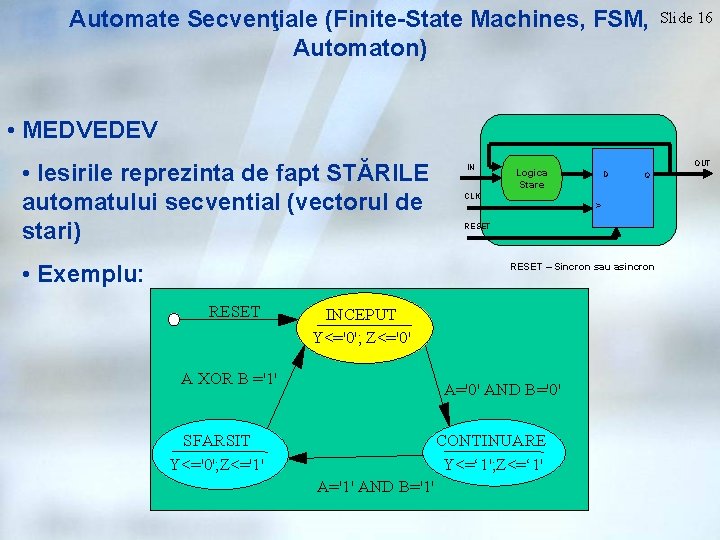

Automate Secvenţiale (Finite-State Machines, FSM, Automaton) Slide 16 • MEDVEDEV • Iesirile reprezinta de fapt STĂRILE automatului secvential (vectorul de stari) • Exemplu: IN OUT Logica Stare CLK D Q > RESET – Sincron sau asincron RESET INCEPUT Y<='0'; Z<='0' A XOR B ='1' A='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' SFARSIT Y<='0'; Z<='1' AND B='1'

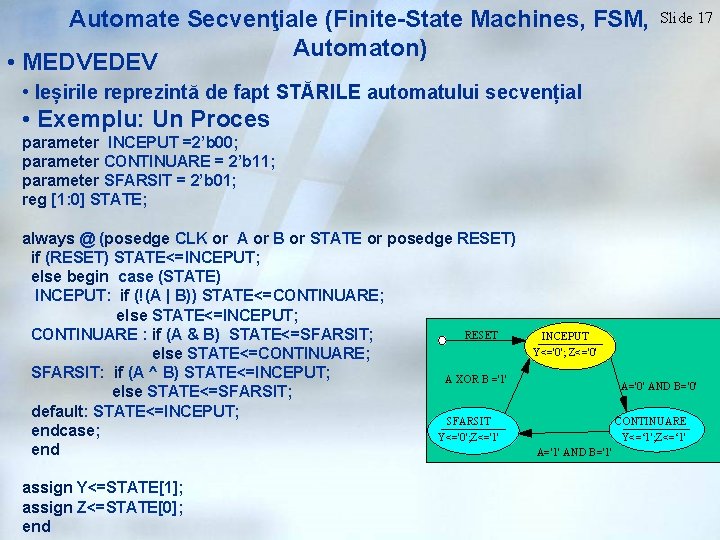

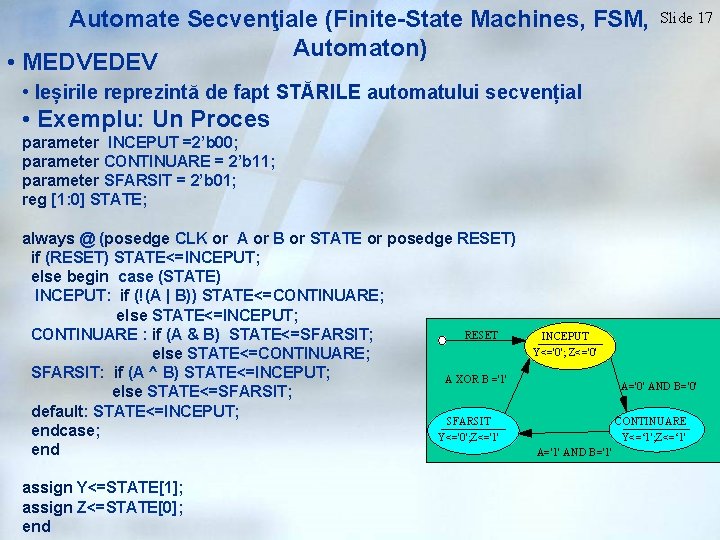

Automate Secvenţiale (Finite-State Machines, FSM, Automaton) • MEDVEDEV Slide 17 • Ieșirile reprezintă de fapt STĂRILE automatului secvențial • Exemplu: Un Proces parameter INCEPUT =2’b 00; parameter CONTINUARE = 2’b 11; parameter SFARSIT = 2’b 01; reg [1: 0] STATE; always @ (posedge CLK or A or B or STATE or posedge RESET) if (RESET) STATE<=INCEPUT; else begin case (STATE) INCEPUT: if (!(A | B)) STATE<=CONTINUARE; else STATE<=INCEPUT; RESET CONTINUARE : if (A & B) STATE<=SFARSIT; else STATE<=CONTINUARE; SFARSIT: if (A ^ B) STATE<=INCEPUT; A XOR B ='1' else STATE<=SFARSIT; default: STATE<=INCEPUT; SFARSIT endcase; Y<='0'; Z<='1' end assign Y<=STATE[1]; assign Z<=STATE[0]; end INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

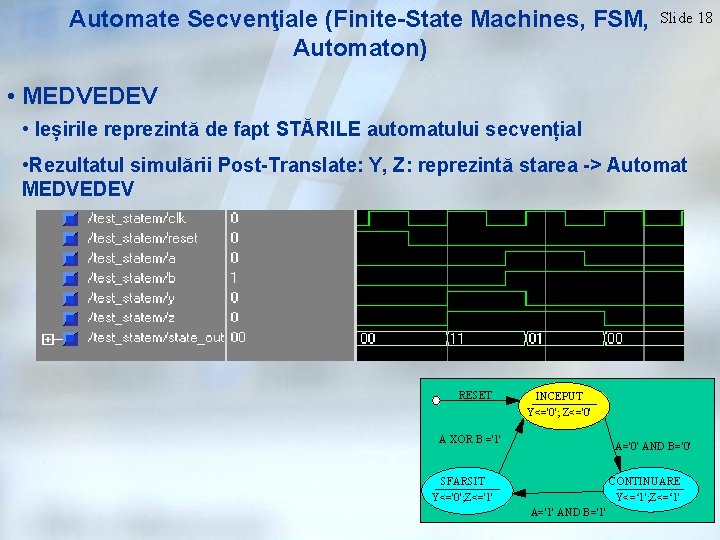

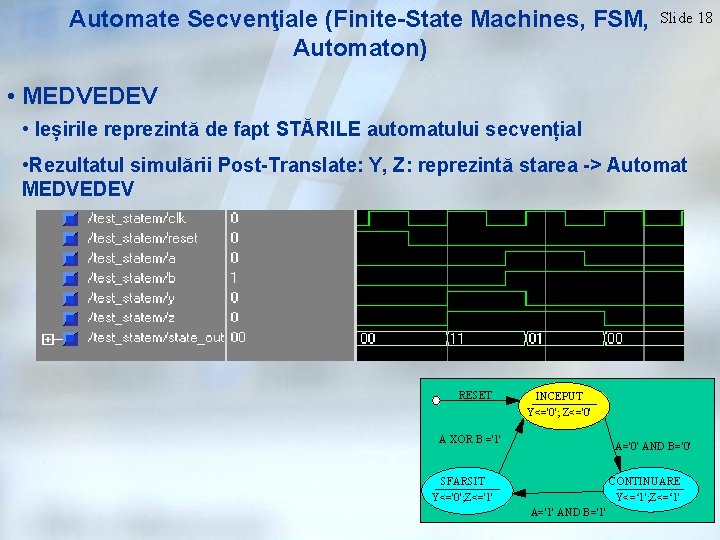

Automate Secvenţiale (Finite-State Machines, FSM, Automaton) Slide 18 • MEDVEDEV • Ieșirile reprezintă de fapt STĂRILE automatului secvențial • Rezultatul simulării Post-Translate: Y, Z: reprezintă starea -> Automat MEDVEDEV RESET INCEPUT Y<='0'; Z<='0' A XOR B ='1' A='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' SFARSIT Y<='0'; Z<='1' AND B='1'

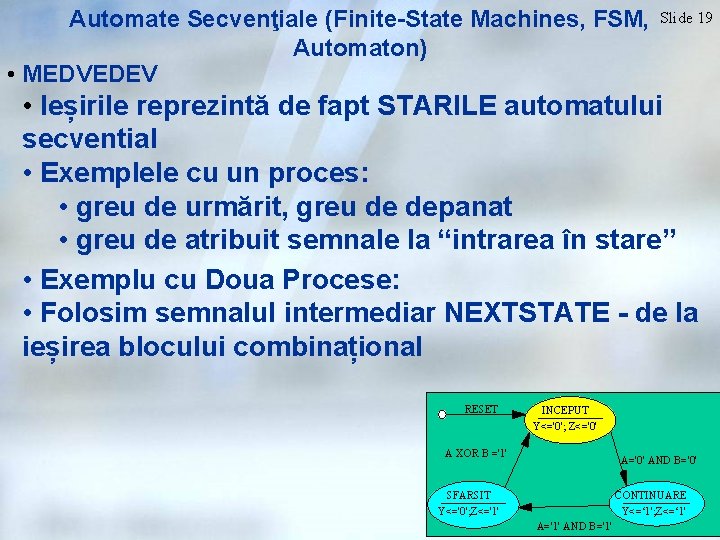

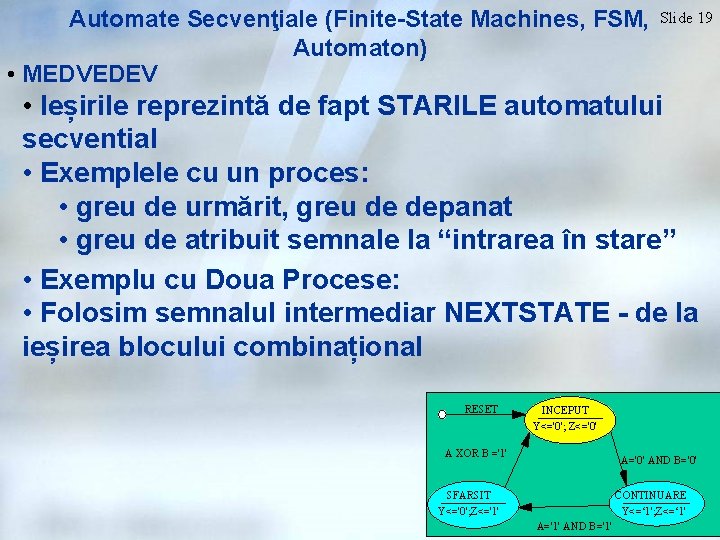

Automate Secvenţiale (Finite-State Machines, FSM, Automaton) • MEDVEDEV Slide 19 • Ieșirile reprezintă de fapt STARILE automatului secvential • Exemplele cu un proces: • greu de urmărit, greu de depanat • greu de atribuit semnale la “intrarea în stare” • Exemplu cu Doua Procese: • Folosim semnalul intermediar NEXTSTATE - de la ieșirea blocului combinațional RESET INCEPUT Y<='0'; Z<='0' A XOR B ='1' A='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' SFARSIT Y<='0'; Z<='1' AND B='1'

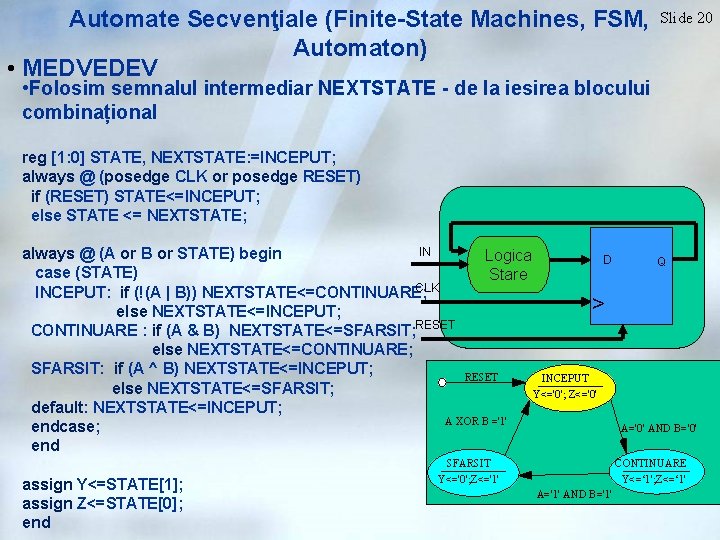

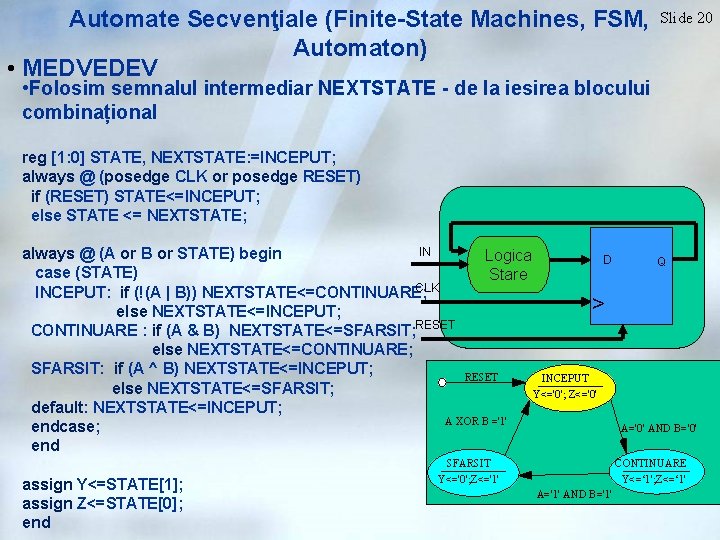

Automate Secvenţiale (Finite-State Machines, FSM, Automaton) • MEDVEDEV Slide 20 • Folosim semnalul intermediar NEXTSTATE - de la iesirea blocului combinațional reg [1: 0] STATE, NEXTSTATE: =INCEPUT; always @ (posedge CLK or posedge RESET) if (RESET) STATE<=INCEPUT; else STATE <= NEXTSTATE; IN always @ (A or B or STATE) begin Logica D case (STATE) Stare CLK INCEPUT: if (!(A | B)) NEXTSTATE<=CONTINUARE; > else NEXTSTATE<=INCEPUT; CONTINUARE : if (A & B) NEXTSTATE<=SFARSIT; RESET else NEXTSTATE<=CONTINUARE; SFARSIT: if (A ^ B) NEXTSTATE<=INCEPUT; RESET INCEPUT else NEXTSTATE<=SFARSIT; Y<='0'; Z<='0' default: NEXTSTATE<=INCEPUT; A XOR B ='1' endcase; end assign Y<=STATE[1]; assign Z<=STATE[0]; end Q A='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' SFARSIT Y<='0'; Z<='1' AND B='1'

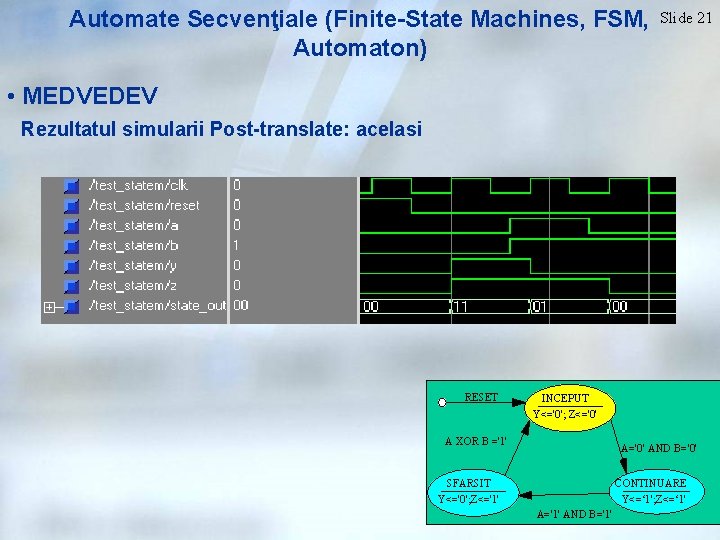

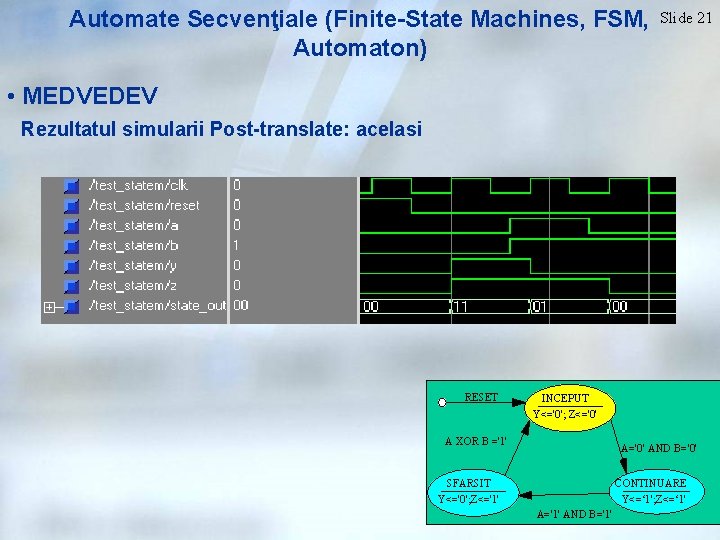

Automate Secvenţiale (Finite-State Machines, FSM, Automaton) Slide 21 • MEDVEDEV Rezultatul simularii Post-translate: acelasi RESET INCEPUT Y<='0'; Z<='0' A XOR B ='1' A='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' SFARSIT Y<='0'; Z<='1' AND B='1'

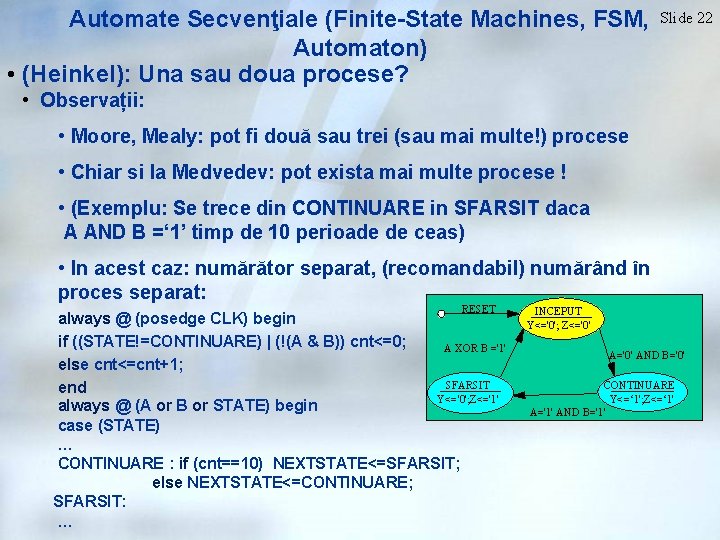

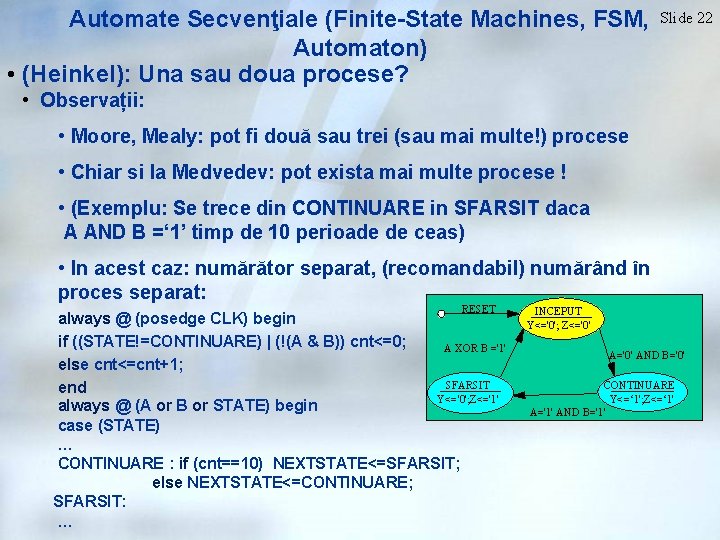

Automate Secvenţiale (Finite-State Machines, FSM, Automaton) • (Heinkel): Una sau doua procese? Slide 22 • Observații: • Moore, Mealy: pot fi două sau trei (sau mai multe!) procese • Chiar si la Medvedev: pot exista mai multe procese ! • (Exemplu: Se trece din CONTINUARE in SFARSIT daca A AND B =‘ 1’ timp de 10 perioade de ceas) • In acest caz: numărător separat, (recomandabil) numărând în proces separat: RESET always @ (posedge CLK) begin if ((STATE!=CONTINUARE) | (!(A & B)) cnt<=0; A XOR B ='1' else cnt<=cnt+1; SFARSIT end Y<='0'; Z<='1' always @ (A or B or STATE) begin case (STATE) … CONTINUARE : if (cnt==10) NEXTSTATE<=SFARSIT; else NEXTSTATE<=CONTINUARE; SFARSIT: … INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

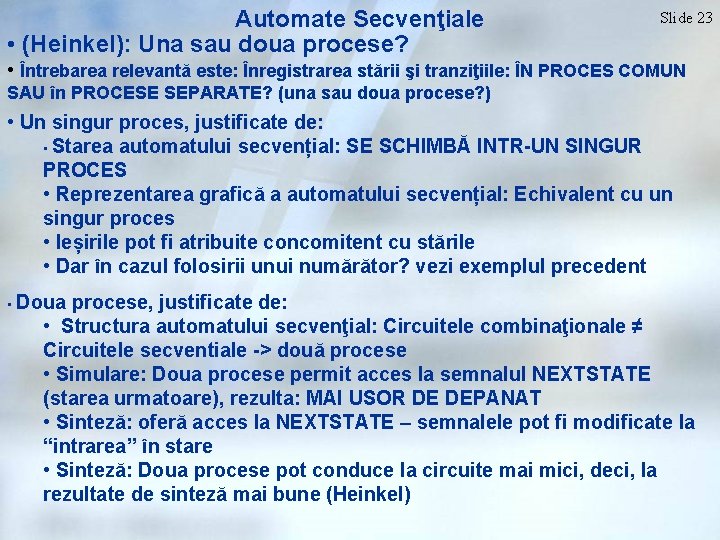

Automate Secvenţiale • (Heinkel): Una sau doua procese? Slide 23 • Întrebarea relevantă este: Înregistrarea stării şi tranziţiile: ÎN PROCES COMUN SAU în PROCESE SEPARATE? (una sau doua procese? ) • Un singur proces, justificate de: • Starea automatului secvențial: SE SCHIMBĂ INTR-UN SINGUR PROCES • Reprezentarea grafică a automatului secvențial: Echivalent cu un singur proces • Ieșirile pot fi atribuite concomitent cu stările • Dar în cazul folosirii unui numărător? vezi exemplul precedent • Doua procese, justificate de: • Structura automatului secvenţial: Circuitele combinaţionale ≠ Circuitele secventiale -> două procese • Simulare: Doua procese permit acces la semnalul NEXTSTATE (starea urmatoare), rezulta: MAI USOR DE DEPANAT • Sinteză: oferă acces la NEXTSTATE – semnalele pot fi modificate la “intrarea” în stare • Sinteză: Doua procese pot conduce la circuite mai mici, deci, la rezultate de sinteză mai bune (Heinkel)

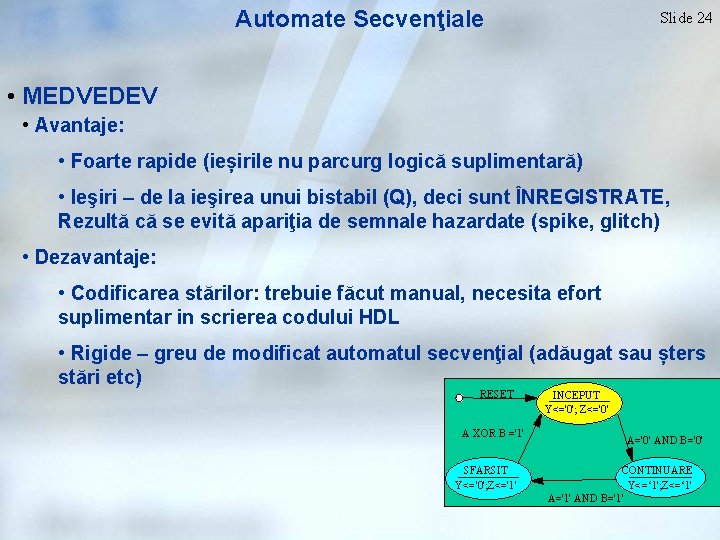

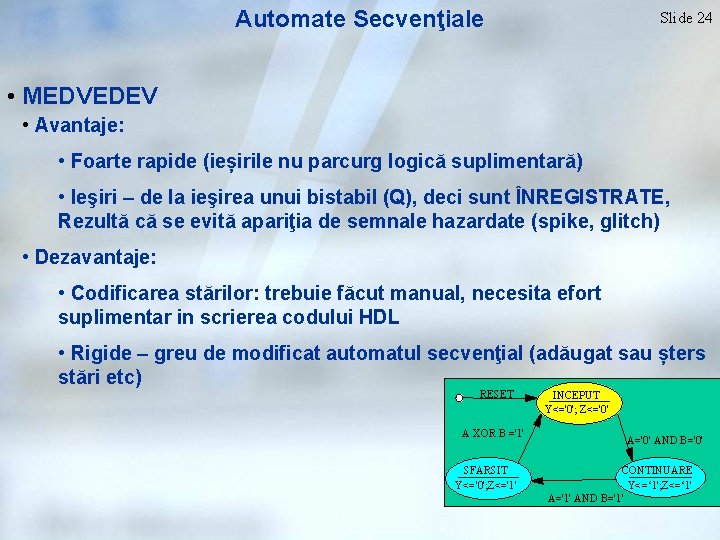

Automate Secvenţiale Slide 24 • MEDVEDEV • Avantaje: • Foarte rapide (ieșirile nu parcurg logică suplimentară) • Ieşiri – de la ieşirea unui bistabil (Q), deci sunt ÎNREGISTRATE, Rezultă că se evită apariţia de semnale hazardate (spike, glitch) • Dezavantaje: • Codificarea stărilor: trebuie făcut manual, necesita efort suplimentar in scrierea codului HDL • Rigide – greu de modificat automatul secvenţial (adăugat sau șters stări etc) RESET A XOR B ='1' SFARSIT Y<='0'; Z<='1' INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

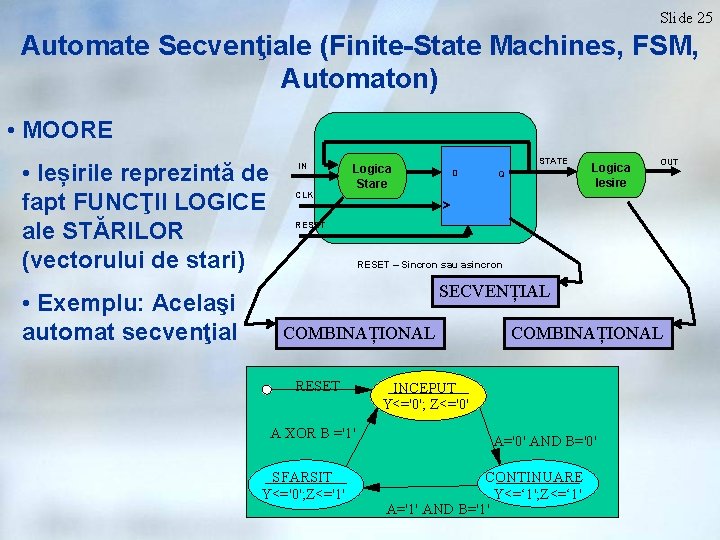

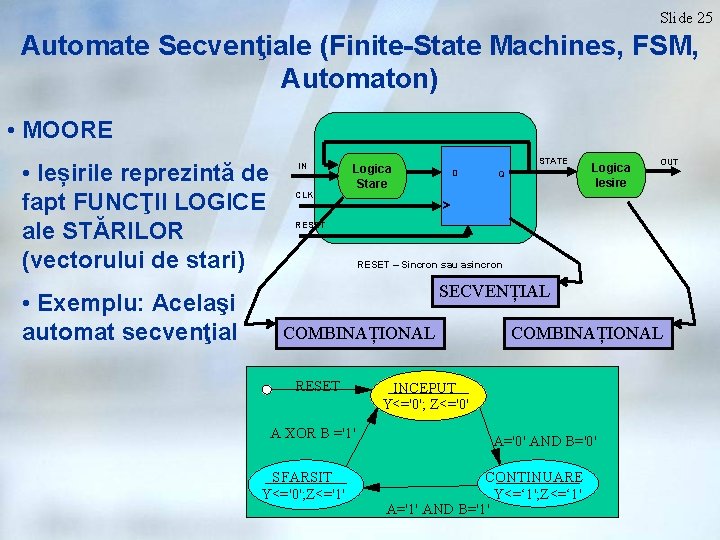

Slide 25 Automate Secvenţiale (Finite-State Machines, FSM, Automaton) • MOORE • Ieșirile reprezintă de fapt FUNCŢII LOGICE ale STĂRILOR (vectorului de stari) • Exemplu: Acelaşi automat secvenţial IN CLK STATE Logica Stare D Q Logica Iesire OUT > RESET – Sincron sau asincron SECVENȚIAL COMBINAȚIONAL RESET A XOR B ='1' SFARSIT Y<='0'; Z<='1' COMBINAȚIONAL INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

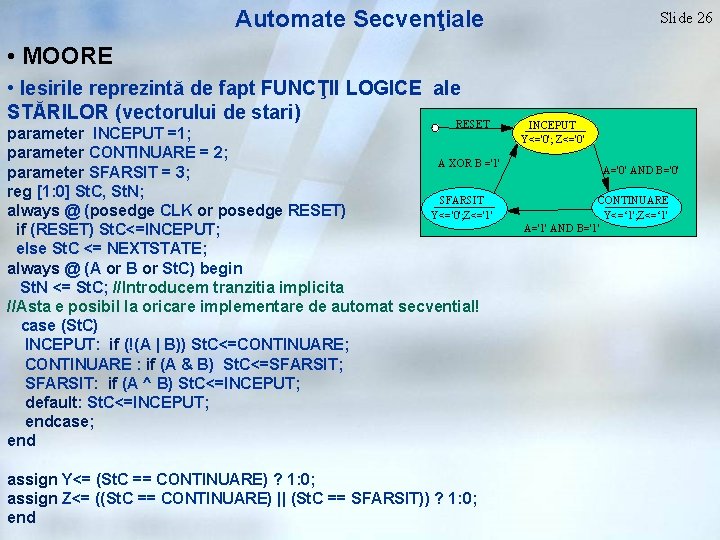

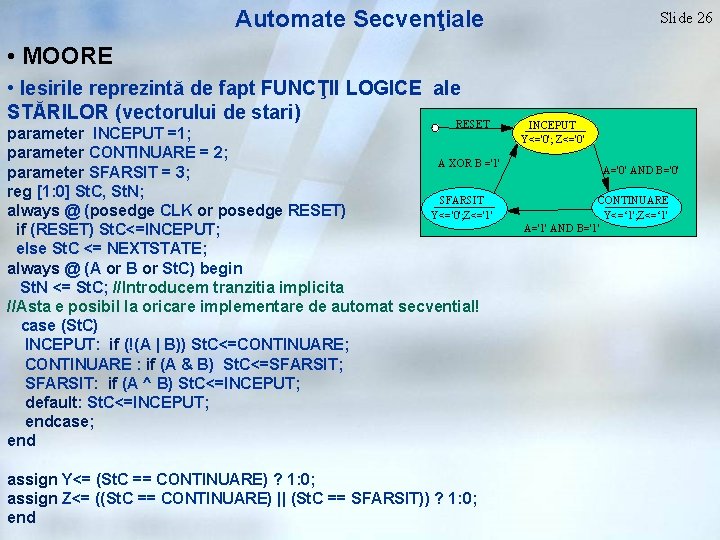

Automate Secvenţiale Slide 26 • MOORE • Iesirile reprezintă de fapt FUNCŢII LOGICE ale STĂRILOR (vectorului de stari) RESET parameter INCEPUT =1; parameter CONTINUARE = 2; A XOR B ='1' parameter SFARSIT = 3; reg [1: 0] St. C, St. N; SFARSIT always @ (posedge CLK or posedge RESET) Y<='0'; Z<='1' if (RESET) St. C<=INCEPUT; else St. C <= NEXTSTATE; always @ (A or B or St. C) begin St. N <= St. C; //Introducem tranzitia implicita //Asta e posibil la oricare implementare de automat secvential! case (St. C) INCEPUT: if (!(A | B)) St. C<=CONTINUARE; CONTINUARE : if (A & B) St. C<=SFARSIT; SFARSIT: if (A ^ B) St. C<=INCEPUT; default: St. C<=INCEPUT; endcase; end assign Y<= (St. C == CONTINUARE) ? 1: 0; assign Z<= ((St. C == CONTINUARE) || (St. C == SFARSIT)) ? 1: 0; end INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

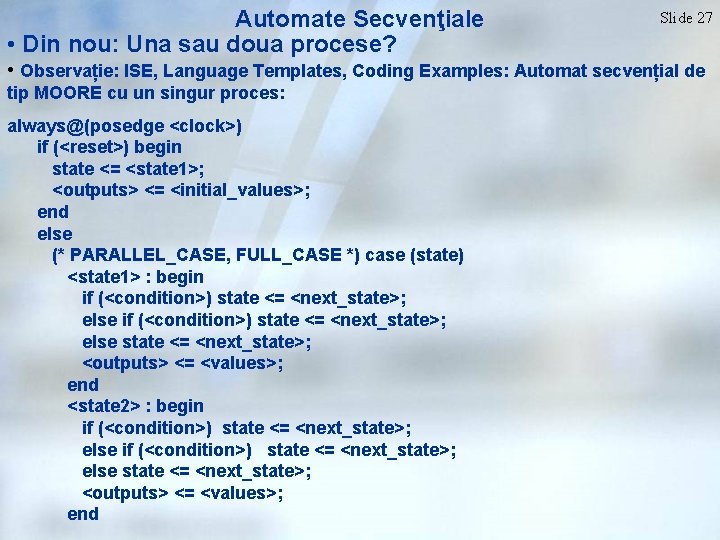

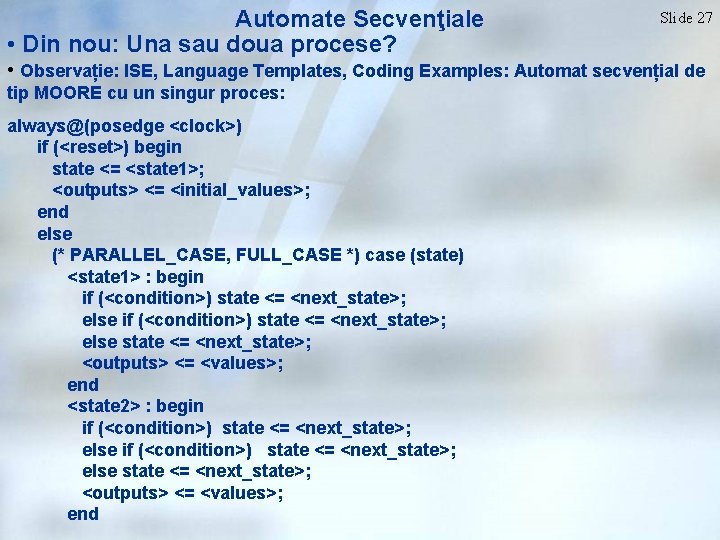

Automate Secvenţiale • Din nou: Una sau doua procese? Slide 27 • Observație: ISE, Language Templates, Coding Examples: Automat secvențial de tip MOORE cu un singur proces: always@(posedge <clock>) if (<reset>) begin state <= <state 1>; <outputs> <= <initial_values>; end else (* PARALLEL_CASE, FULL_CASE *) case (state) <state 1> : begin if (<condition>) state <= <next_state>; else state <= <next_state>; <outputs> <= <values>; end <state 2> : begin if (<condition>) state <= <next_state>; else state <= <next_state>; <outputs> <= <values>; end

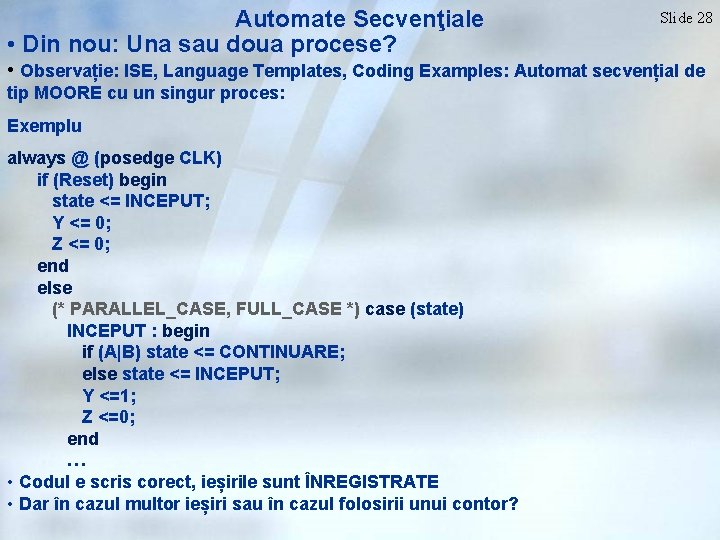

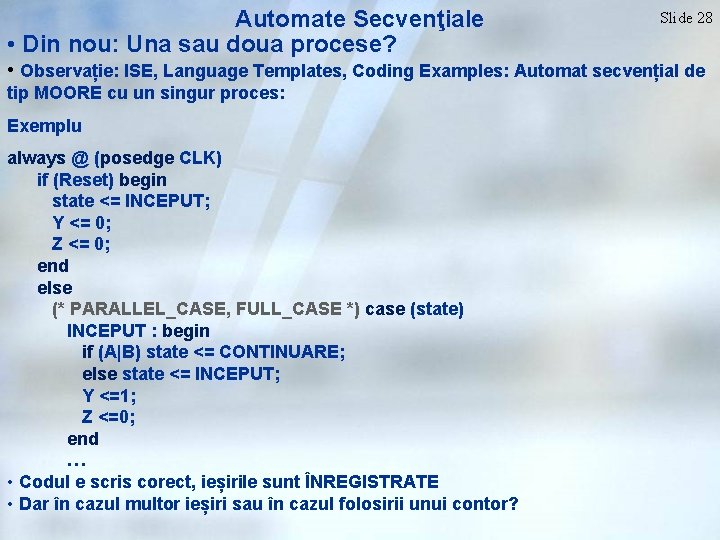

Automate Secvenţiale • Din nou: Una sau doua procese? Slide 28 • Observație: ISE, Language Templates, Coding Examples: Automat secvențial de tip MOORE cu un singur proces: Exemplu always @ (posedge CLK) if (Reset) begin state <= INCEPUT; Y <= 0; Z <= 0; end else (* PARALLEL_CASE, FULL_CASE *) case (state) INCEPUT : begin if (A|B) state <= CONTINUARE; else state <= INCEPUT; Y <=1; Z <=0; end … • Codul e scris corect, ieșirile sunt ÎNREGISTRATE • Dar în cazul multor ieșiri sau în cazul folosirii unui contor?

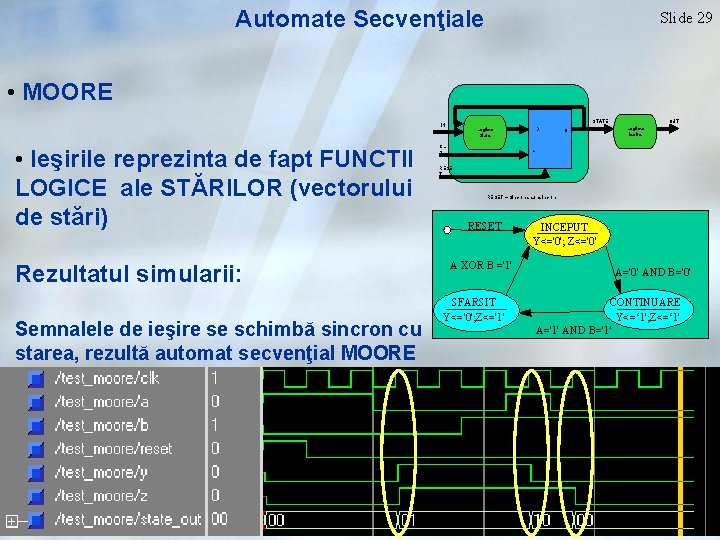

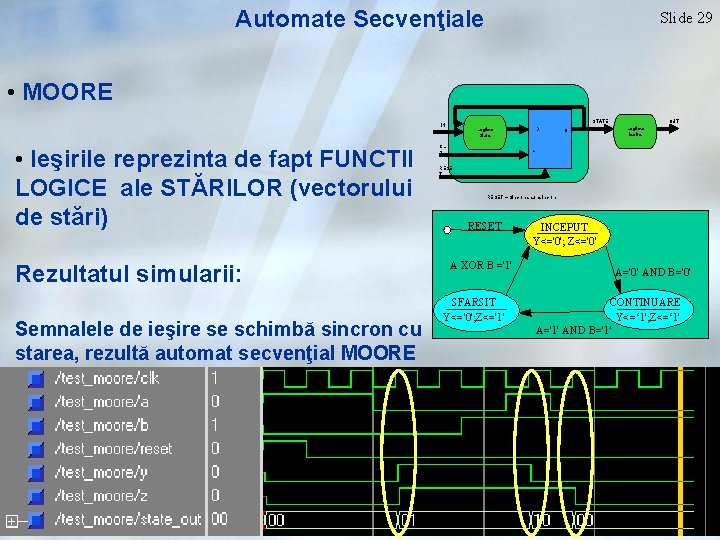

Automate Secvenţiale Slide 29 • MOORE STATE IN • Ieşirile reprezinta de fapt FUNCTII LOGICE ale STĂRILOR (vectorului de stări) Rezultatul simularii: Semnalele de ieşire se schimbă sincron cu starea, rezultă automat secvenţial MOORE Logica Stare CL K D Q OUT Logica Iesire > RESE T RESET – Sincron sau asincron RESET A XOR B ='1' SFARSIT Y<='0'; Z<='1' INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

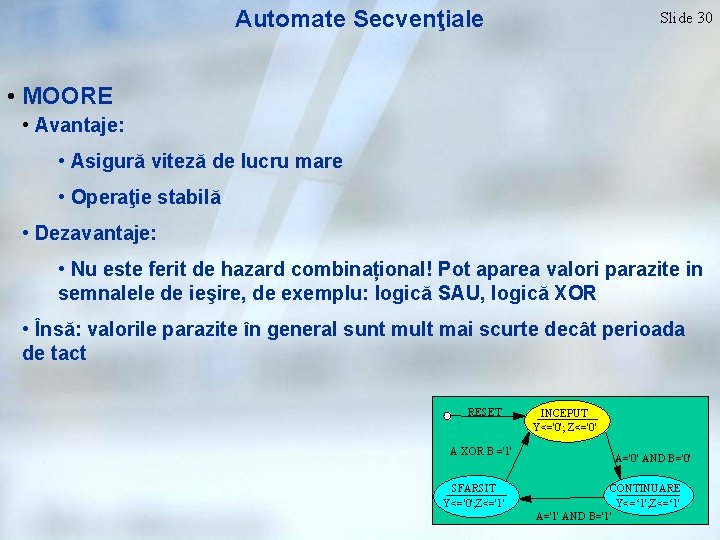

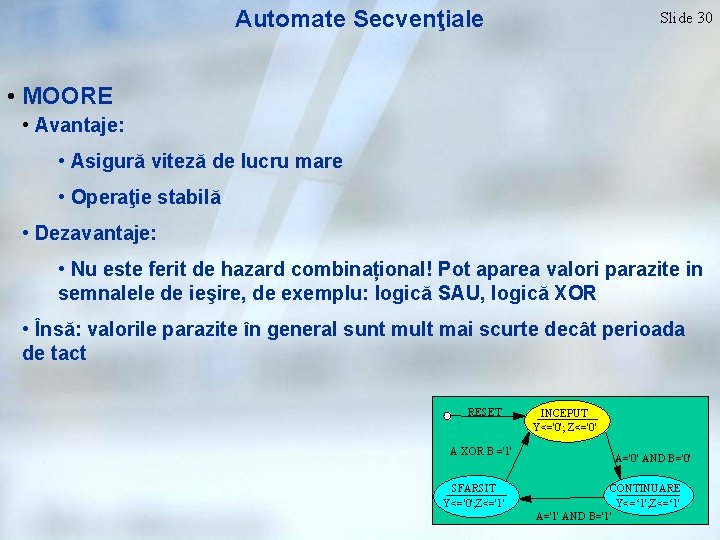

Automate Secvenţiale Slide 30 • MOORE • Avantaje: • Asigură viteză de lucru mare • Operaţie stabilă • Dezavantaje: • Nu este ferit de hazard combinațional! Pot aparea valori parazite in semnalele de ieşire, de exemplu: logică SAU, logică XOR • Însă: valorile parazite în general sunt mult mai scurte decât perioada de tact RESET A XOR B ='1' SFARSIT Y<='0'; Z<='1' INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

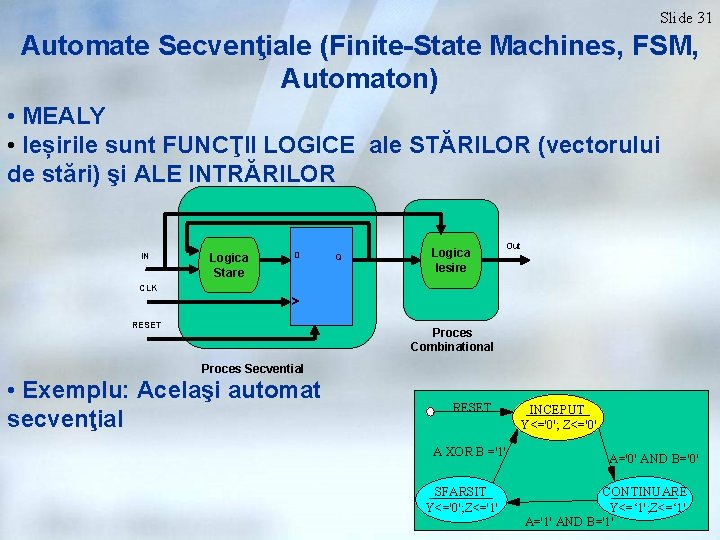

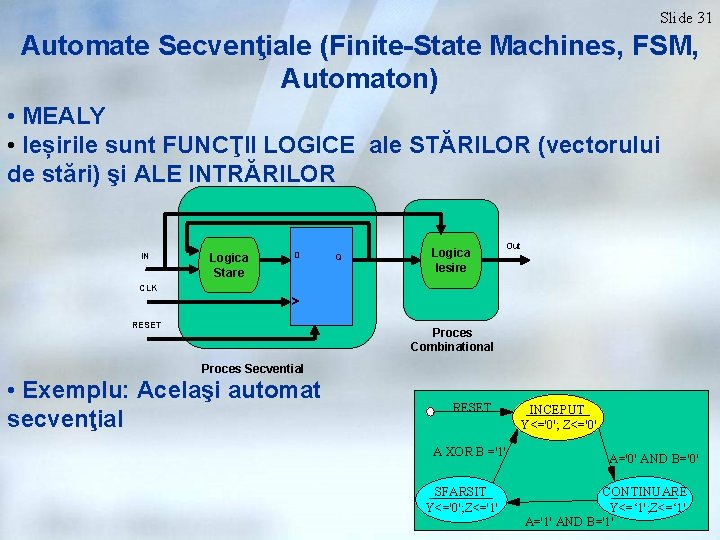

Slide 31 Automate Secvenţiale (Finite-State Machines, FSM, Automaton) • MEALY • Ieșirile sunt FUNCŢII LOGICE ale STĂRILOR (vectorului de stări) şi ALE INTRĂRILOR IN Logica Stare D Q Logica Iesire Out CLK > RESET Proces Combinational Proces Secvential • Exemplu: Acelaşi automat secvenţial RESET A XOR B ='1' SFARSIT Y<='0'; Z<='1' INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

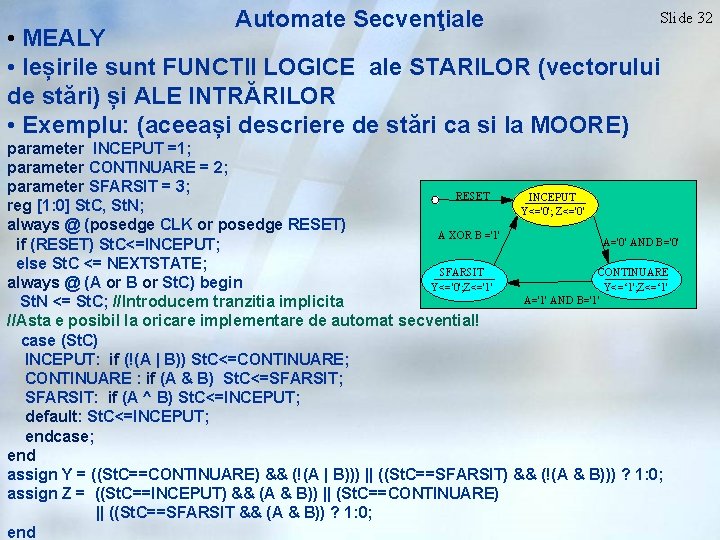

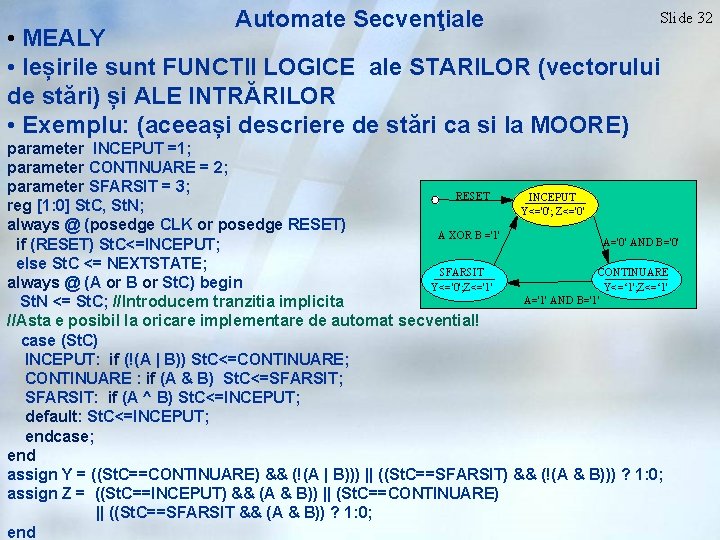

Automate Secvenţiale Slide 32 • MEALY • Ieșirile sunt FUNCTII LOGICE ale STARILOR (vectorului de stări) și ALE INTRĂRILOR • Exemplu: (aceeași descriere de stări ca si la MOORE) parameter INCEPUT =1; parameter CONTINUARE = 2; parameter SFARSIT = 3; RESET INCEPUT reg [1: 0] St. C, St. N; Y<='0'; Z<='0' always @ (posedge CLK or posedge RESET) A XOR B ='1' A='0' AND B='0' if (RESET) St. C<=INCEPUT; else St. C <= NEXTSTATE; CONTINUARE SFARSIT always @ (A or B or St. C) begin Y<='0'; Z<='1' Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1' St. N <= St. C; //Introducem tranzitia implicita //Asta e posibil la oricare implementare de automat secvential! case (St. C) INCEPUT: if (!(A | B)) St. C<=CONTINUARE; CONTINUARE : if (A & B) St. C<=SFARSIT; SFARSIT: if (A ^ B) St. C<=INCEPUT; default: St. C<=INCEPUT; endcase; end assign Y = ((St. C==CONTINUARE) && (!(A | B))) || ((St. C==SFARSIT) && (!(A & B))) ? 1: 0; assign Z = ((St. C==INCEPUT) && (A & B)) || (St. C==CONTINUARE) || ((St. C==SFARSIT && (A & B)) ? 1: 0; end

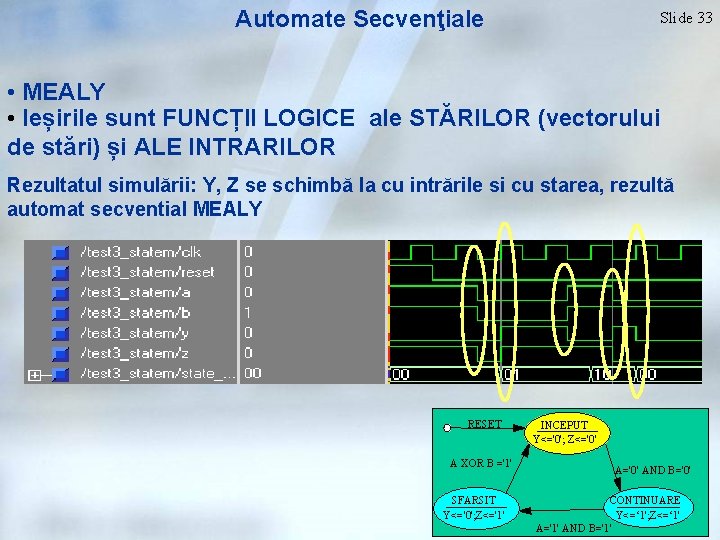

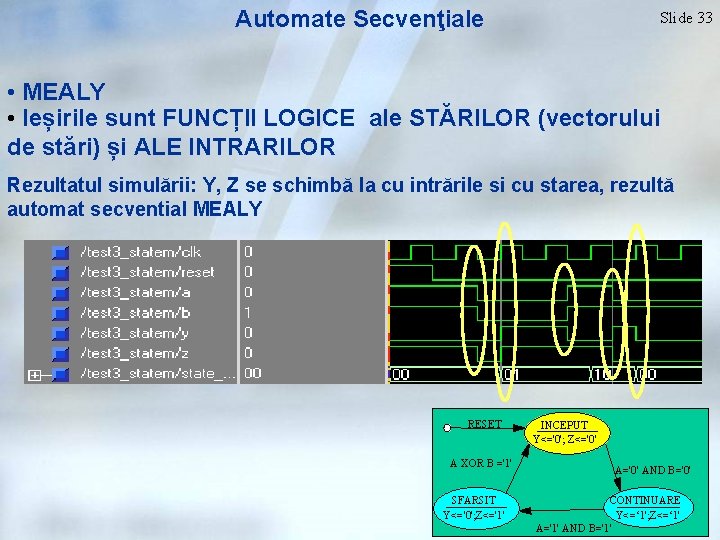

Automate Secvenţiale Slide 33 • MEALY • Ieșirile sunt FUNCȚII LOGICE ale STĂRILOR (vectorului de stări) și ALE INTRARILOR Rezultatul simulării: Y, Z se schimbă la cu intrările si cu starea, rezultă automat secvential MEALY RESET A XOR B ='1' SFARSIT Y<='0'; Z<='1' INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

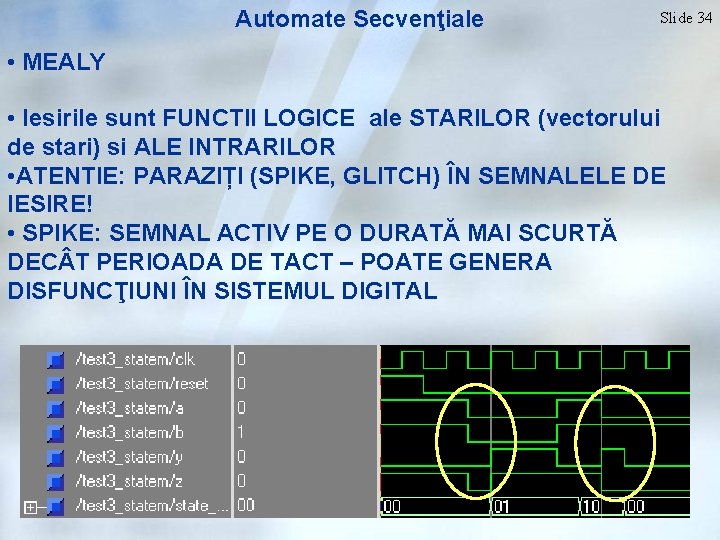

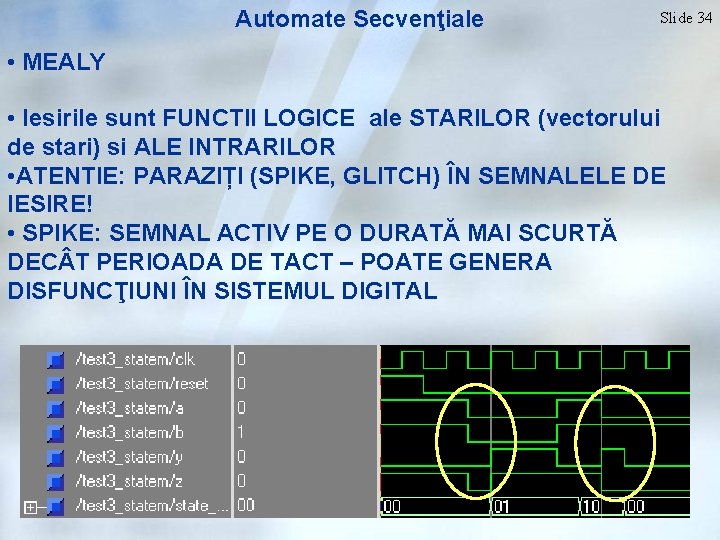

Automate Secvenţiale Slide 34 • MEALY • Iesirile sunt FUNCTII LOGICE ale STARILOR (vectorului de stari) si ALE INTRARILOR • ATENTIE: PARAZIȚI (SPIKE, GLITCH) ÎN SEMNALELE DE IESIRE! • SPIKE: SEMNAL ACTIV PE O DURATĂ MAI SCURTĂ DEC T PERIOADA DE TACT – POATE GENERA DISFUNCŢIUNI ÎN SISTEMUL DIGITAL

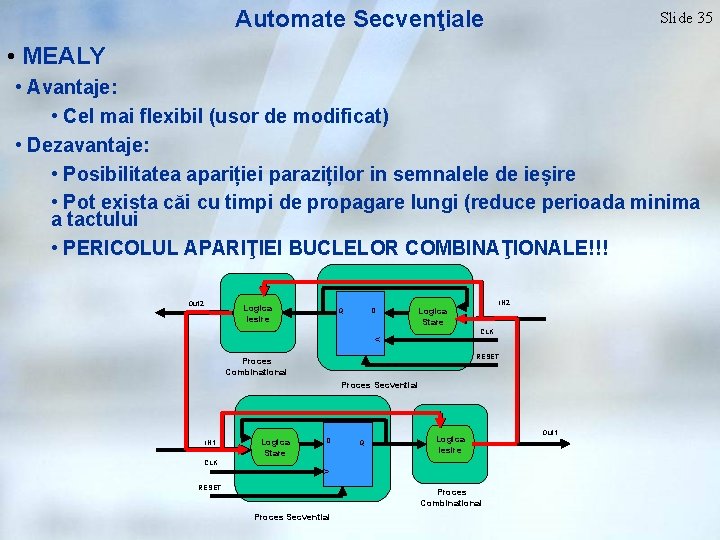

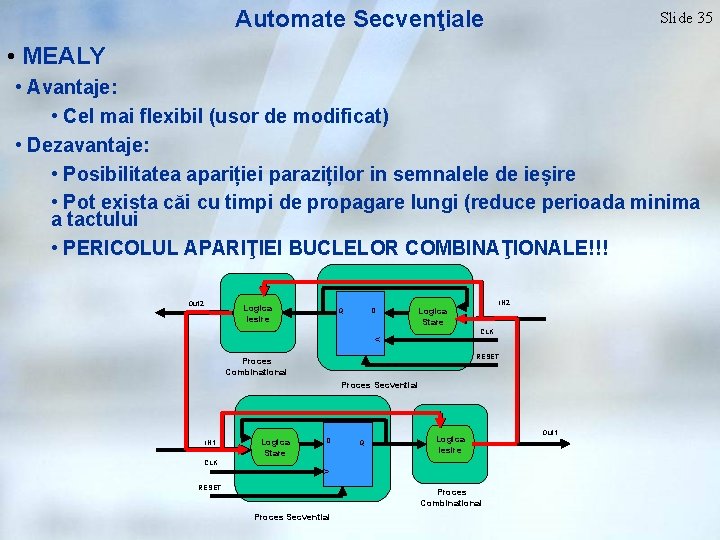

Automate Secvenţiale Slide 35 • MEALY • Avantaje: • Cel mai flexibil (usor de modificat) • Dezavantaje: • Posibilitatea apariției paraziților in semnalele de ieșire • Pot exista căi cu timpi de propagare lungi (reduce perioada minima a tactului • PERICOLUL APARIŢIEI BUCLELOR COMBINAŢIONALE!!! Out 2 Logica Iesire D Q IN 2 Logica Stare CLK < RESET Proces Combinational Proces Secvential IN 1 CLK Logica Stare D Q Logica Iesire > RESET Proces Combinational Proces Secvential Out 1

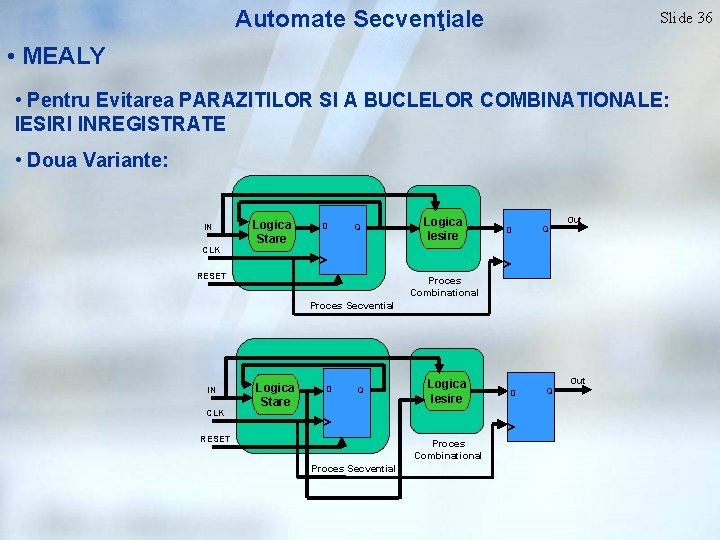

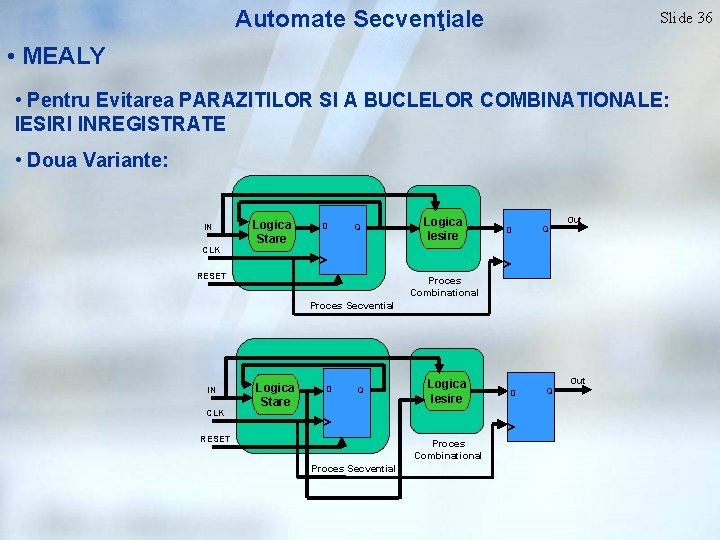

Automate Secvenţiale Slide 36 • MEALY • Pentru Evitarea PARAZITILOR SI A BUCLELOR COMBINATIONALE: IESIRI INREGISTRATE • Doua Variante: IN CLK Logica Stare D Q Logica Iesire > D Q Out > RESET Proces Combinational Proces Secvential IN CLK Logica Stare D Q Logica Iesire > RESET D > Proces Combinational Proces Secvential Out Q

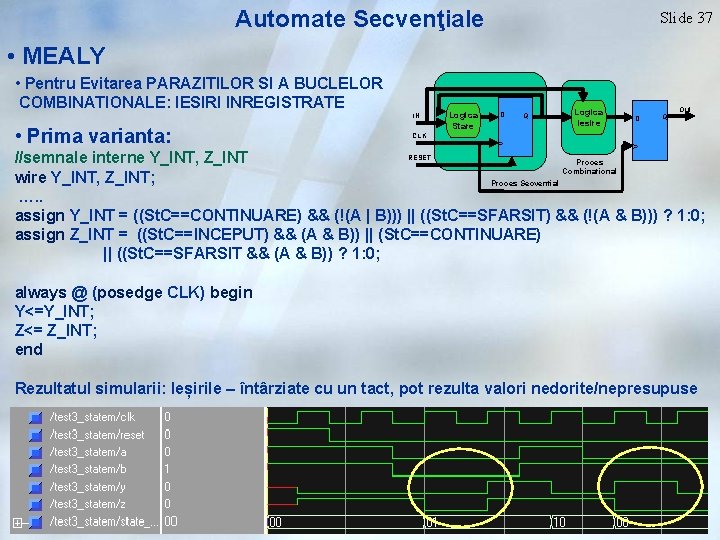

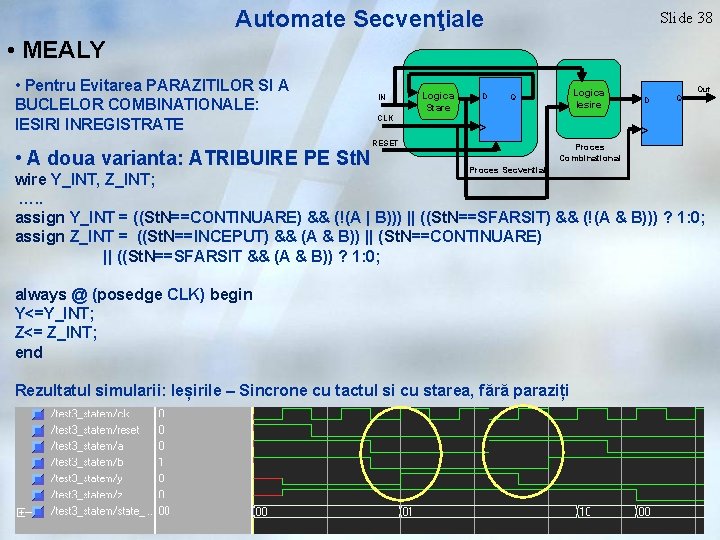

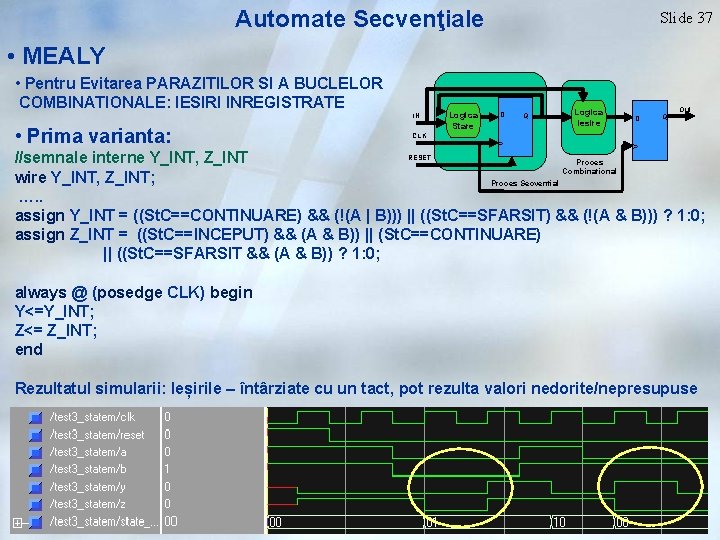

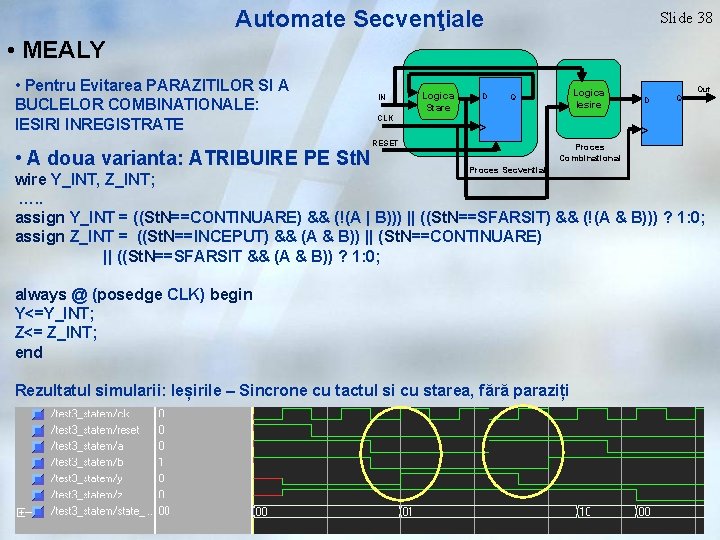

Automate Secvenţiale Slide 37 • MEALY • Pentru Evitarea PARAZITILOR SI A BUCLELOR COMBINATIONALE: IESIRI INREGISTRATE IN • Prima varianta: CLK Logica Stare D > Q Logica Iesire D Q Out > RESET //semnale interne Y_INT, Z_INT Proces Combinational wire Y_INT, Z_INT; Proces Secvential …. . assign Y_INT = ((St. C==CONTINUARE) && (!(A | B))) || ((St. C==SFARSIT) && (!(A & B))) ? 1: 0; assign Z_INT = ((St. C==INCEPUT) && (A & B)) || (St. C==CONTINUARE) || ((St. C==SFARSIT && (A & B)) ? 1: 0; always @ (posedge CLK) begin Y<=Y_INT; Z<= Z_INT; end Rezultatul simularii: Ieșirile – întârziate cu un tact, pot rezulta valori nedorite/nepresupuse

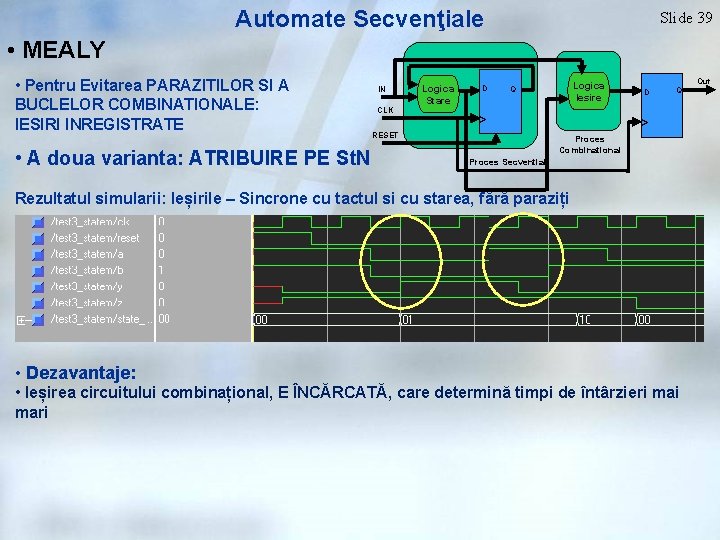

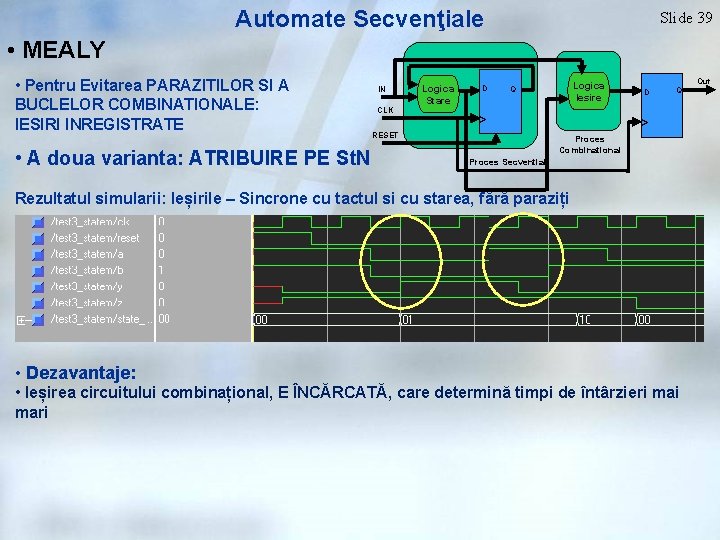

Automate Secvenţiale Slide 38 • MEALY • Pentru Evitarea PARAZITILOR SI A BUCLELOR COMBINATIONALE: IESIRI INREGISTRATE • A doua varianta: ATRIBUIRE PE St. N IN CLK Logica Stare D Logica Iesire Q > RESET Out D Q > Proces Combinational Proces Secvential wire Y_INT, Z_INT; …. . assign Y_INT = ((St. N==CONTINUARE) && (!(A | B))) || ((St. N==SFARSIT) && (!(A & B))) ? 1: 0; assign Z_INT = ((St. N==INCEPUT) && (A & B)) || (St. N==CONTINUARE) || ((St. N==SFARSIT && (A & B)) ? 1: 0; always @ (posedge CLK) begin Y<=Y_INT; Z<= Z_INT; end Rezultatul simularii: Ieșirile – Sincrone cu tactul si cu starea, fără paraziți

Automate Secvenţiale Slide 39 • MEALY • Pentru Evitarea PARAZITILOR SI A BUCLELOR COMBINATIONALE: IESIRI INREGISTRATE • A doua varianta: ATRIBUIRE PE St. N IN CLK Logica Stare D Logica Iesire Q > RESET Out D Q > Proces Combinational Proces Secvential Rezultatul simularii: Ieșirile – Sincrone cu tactul si cu starea, fără paraziți • Dezavantaje: • Ieșirea circuitului combinațional, E ÎNCĂRCATĂ, care determină timpi de întârzieri mari

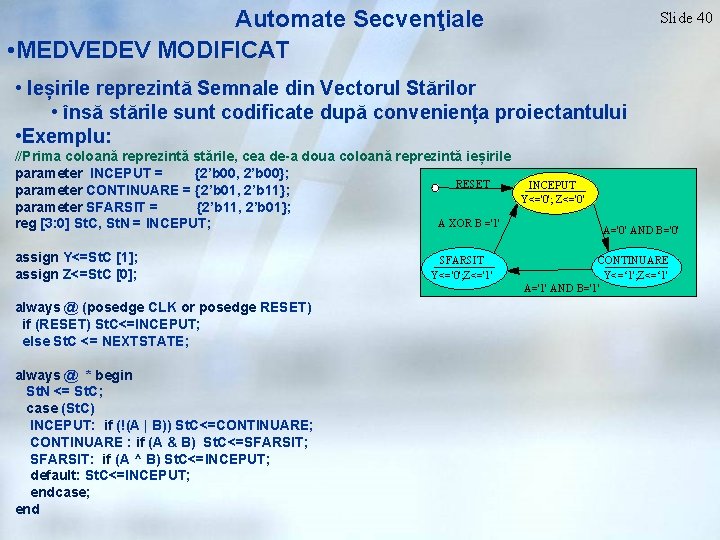

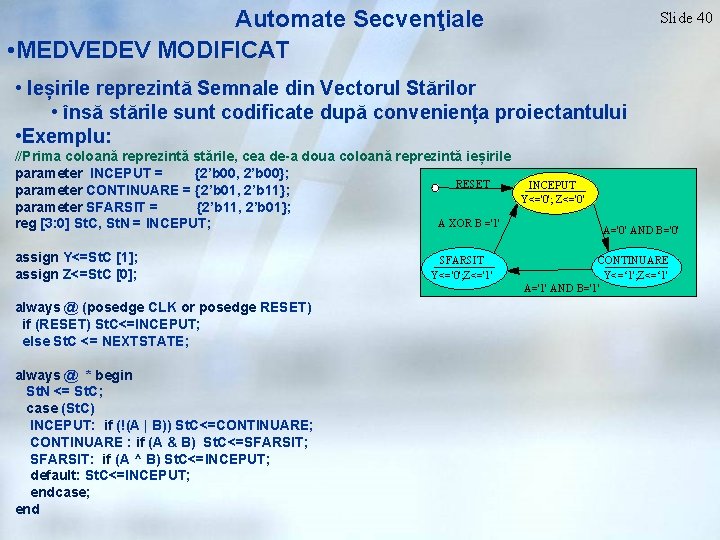

Automate Secvenţiale • MEDVEDEV MODIFICAT Slide 40 • Ieșirile reprezintă Semnale din Vectorul Stărilor • însă stările sunt codificate după conveniența proiectantului • Exemplu: //Prima coloană reprezintă stările, cea de-a doua coloană reprezintă ieșirile parameter INCEPUT = {2’b 00, 2’b 00}; RESET parameter CONTINUARE = {2’b 01, 2’b 11}; parameter SFARSIT = {2’b 11, 2’b 01}; A XOR B ='1' reg [3: 0] St. C, St. N = INCEPUT; assign Y<=St. C [1]; assign Z<=St. C [0]; always @ (posedge CLK or posedge RESET) if (RESET) St. C<=INCEPUT; else St. C <= NEXTSTATE; always @ * begin St. N <= St. C; case (St. C) INCEPUT: if (!(A | B)) St. C<=CONTINUARE; CONTINUARE : if (A & B) St. C<=SFARSIT; SFARSIT: if (A ^ B) St. C<=INCEPUT; default: St. C<=INCEPUT; endcase; end SFARSIT Y<='0'; Z<='1' INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

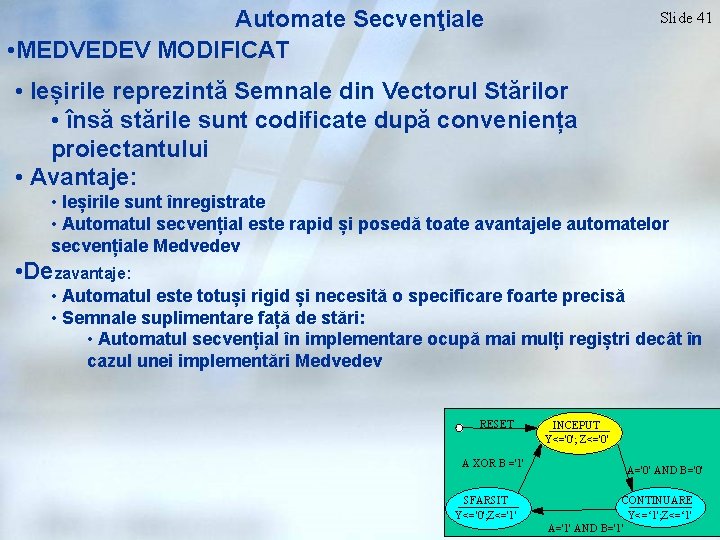

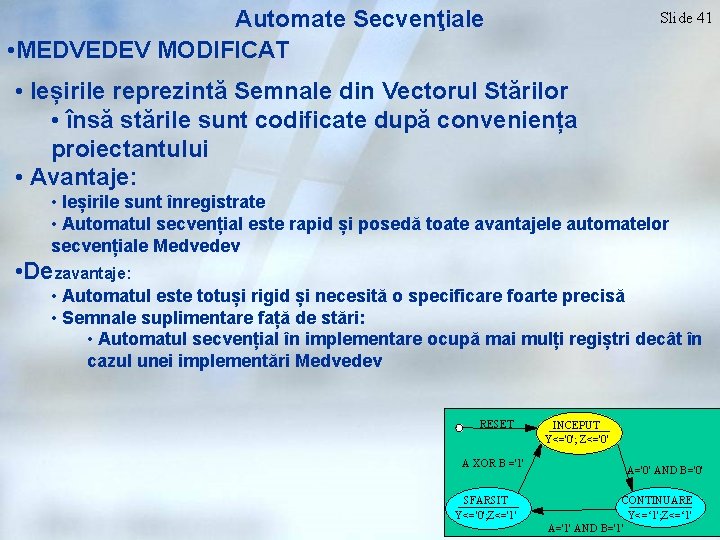

Automate Secvenţiale • MEDVEDEV MODIFICAT Slide 41 • Ieșirile reprezintă Semnale din Vectorul Stărilor • însă stările sunt codificate după conveniența proiectantului • Avantaje: • Ieșirile sunt înregistrate • Automatul secvențial este rapid și posedă toate avantajele automatelor secvențiale Medvedev • Dezavantaje: • Automatul este totuși rigid și necesită o specificare foarte precisă • Semnale suplimentare față de stări: • Automatul secvențial în implementare ocupă mai mulți regiștri decât în cazul unei implementări Medvedev RESET A XOR B ='1' SFARSIT Y<='0'; Z<='1' INCEPUT Y<='0'; Z<='0' AND B='0' CONTINUARE Y<=‘ 1'; Z<=‘ 1' A='1' AND B='1'

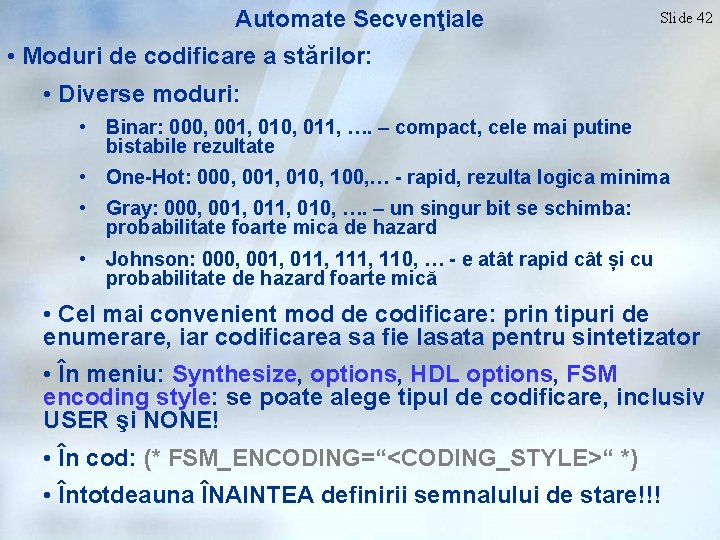

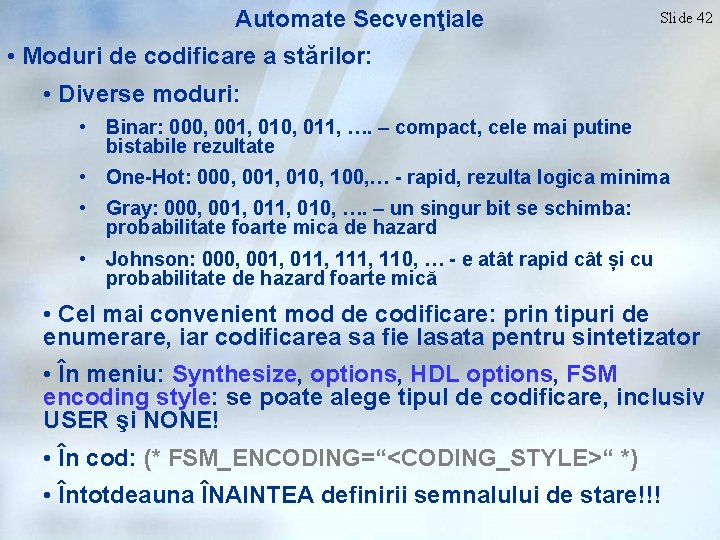

Automate Secvenţiale Slide 42 • Moduri de codificare a stărilor: • Diverse moduri: • Binar: 000, 001, 010, 011, …. – compact, cele mai putine bistabile rezultate • One-Hot: 000, 001, 010, 100, … - rapid, rezulta logica minima • Gray: 000, 001, 010, …. – un singur bit se schimba: probabilitate foarte mica de hazard • Johnson: 000, 001, 011, 110, … - e atât rapid cât și cu probabilitate de hazard foarte mică • Cel mai convenient mod de codificare: prin tipuri de enumerare, iar codificarea sa fie lasata pentru sintetizator • În meniu: Synthesize, options, HDL options, FSM encoding style: se poate alege tipul de codificare, inclusiv USER şi NONE! • În cod: (* FSM_ENCODING=“<CODING_STYLE>“ *) • Întotdeauna ÎNAINTEA definirii semnalului de stare!!!

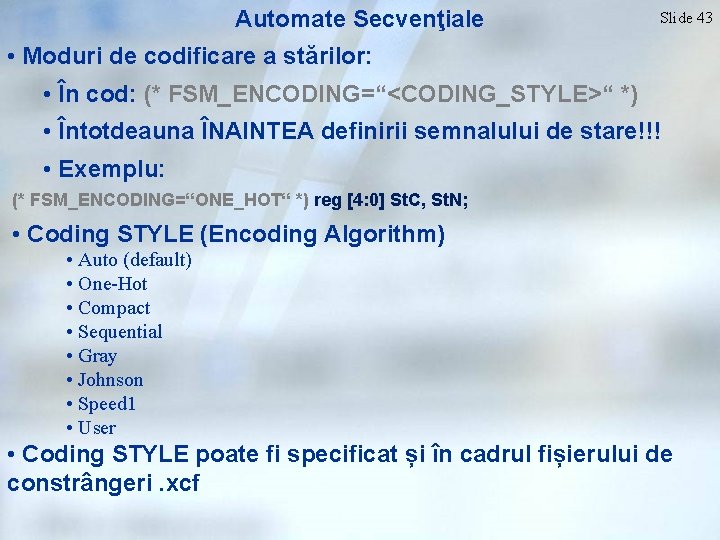

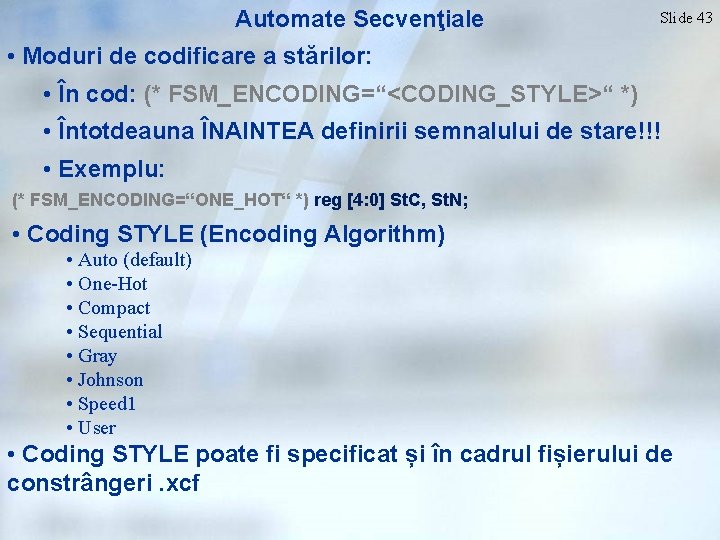

Automate Secvenţiale Slide 43 • Moduri de codificare a stărilor: • În cod: (* FSM_ENCODING=“<CODING_STYLE>“ *) • Întotdeauna ÎNAINTEA definirii semnalului de stare!!! • Exemplu: (* FSM_ENCODING=“ONE_HOT“ *) reg [4: 0] St. C, St. N; • Coding STYLE (Encoding Algorithm) • Auto (default) • One-Hot • Compact • Sequential • Gray • Johnson • Speed 1 • User • Coding STYLE poate fi specificat și în cadrul fișierului de constrângeri. xcf

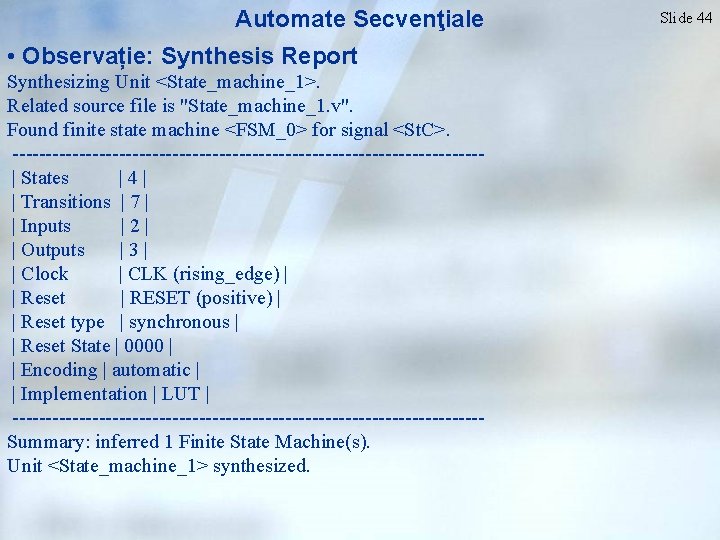

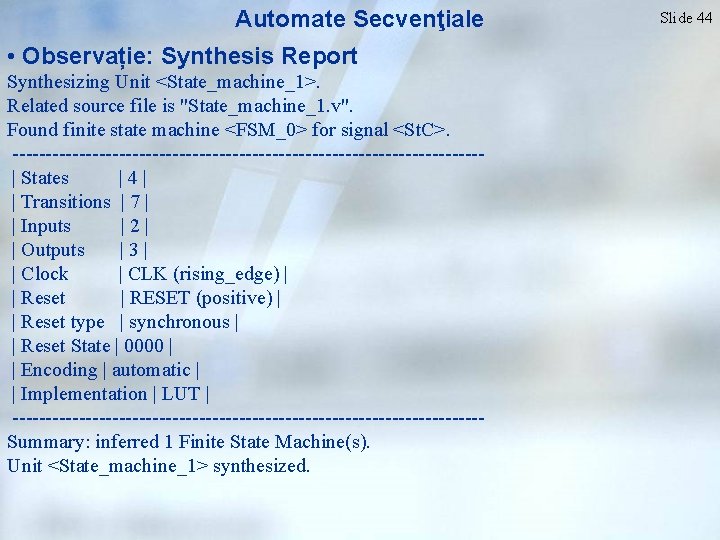

Automate Secvenţiale • Observație: Synthesis Report Synthesizing Unit <State_machine_1>. Related source file is "State_machine_1. v". Found finite state machine <FSM_0> for signal <St. C>. -----------------------------------| States |4| | Transitions | 7 | | Inputs |2| | Outputs |3| | Clock | CLK (rising_edge) | | Reset | RESET (positive) | | Reset type | synchronous | | Reset State | 0000 | | Encoding | automatic | | Implementation | LUT | -----------------------------------Summary: inferred 1 Finite State Machine(s). Unit <State_machine_1> synthesized. Slide 44

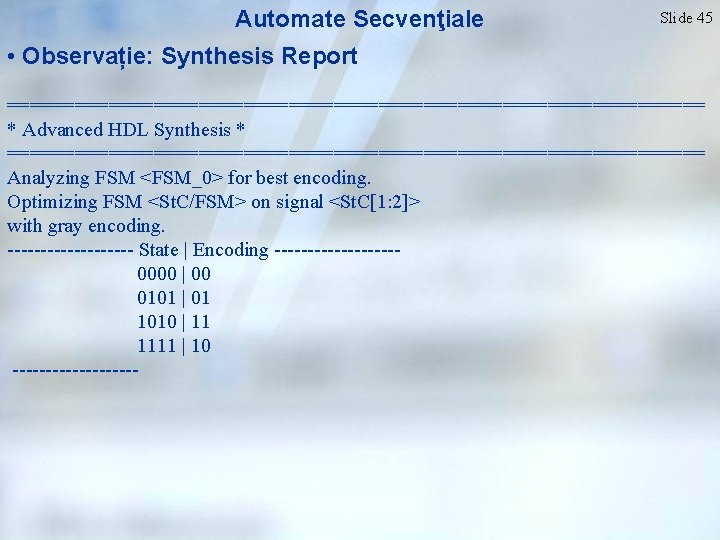

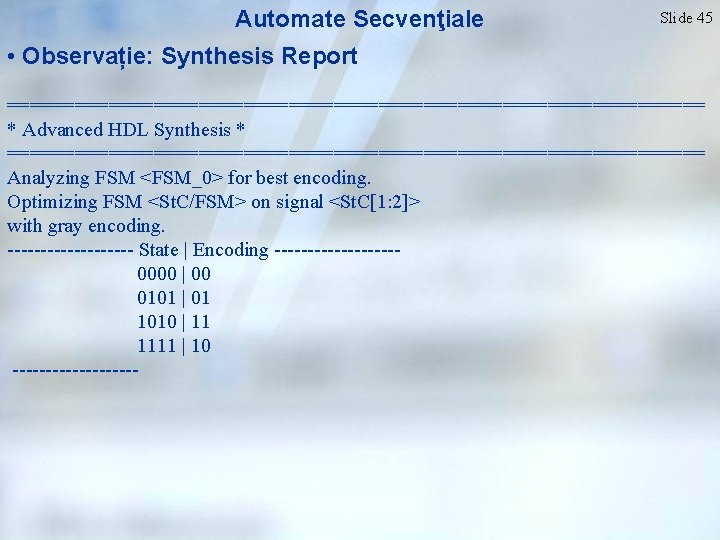

Automate Secvenţiale Slide 45 • Observație: Synthesis Report =============================== * Advanced HDL Synthesis * =============================== Analyzing FSM <FSM_0> for best encoding. Optimizing FSM <St. C/FSM> on signal <St. C[1: 2]> with gray encoding. ---------- State | Encoding ---------0000 | 00 0101 | 01 1010 | 11 1111 | 10 ----------

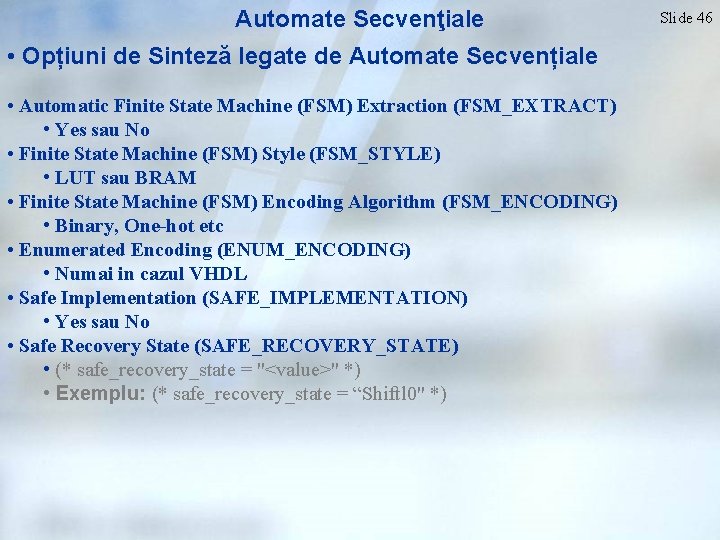

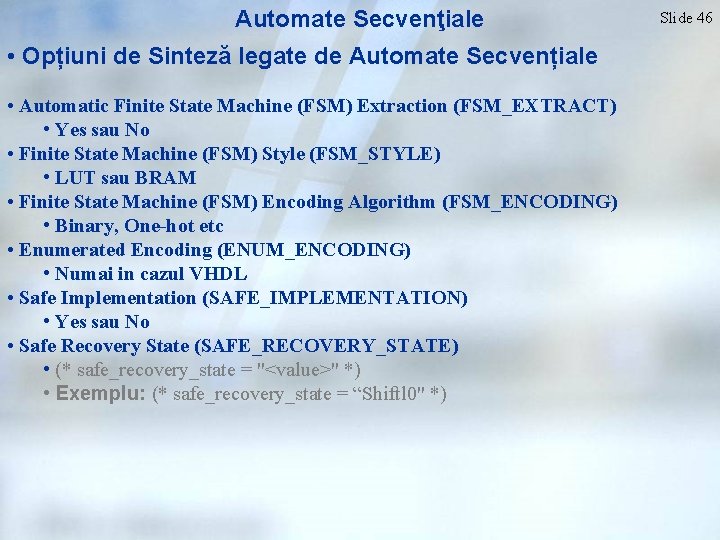

Automate Secvenţiale • Opțiuni de Sinteză legate de Automate Secvențiale • Automatic Finite State Machine (FSM) Extraction (FSM_EXTRACT) • Yes sau No • Finite State Machine (FSM) Style (FSM_STYLE) • LUT sau BRAM • Finite State Machine (FSM) Encoding Algorithm (FSM_ENCODING) • Binary, One-hot etc • Enumerated Encoding (ENUM_ENCODING) • Numai in cazul VHDL • Safe Implementation (SAFE_IMPLEMENTATION) • Yes sau No • Safe Recovery State (SAFE_RECOVERY_STATE) • (* safe_recovery_state = "<value>" *) • Exemplu: (* safe_recovery_state = “Shiftl 0" *) Slide 46

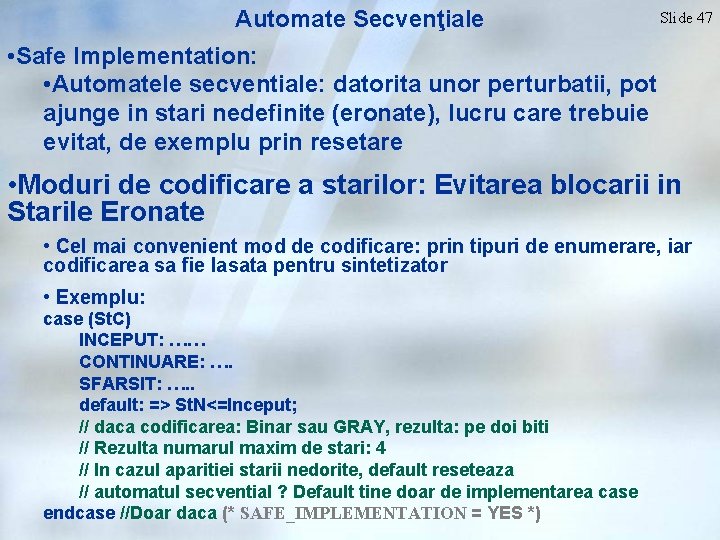

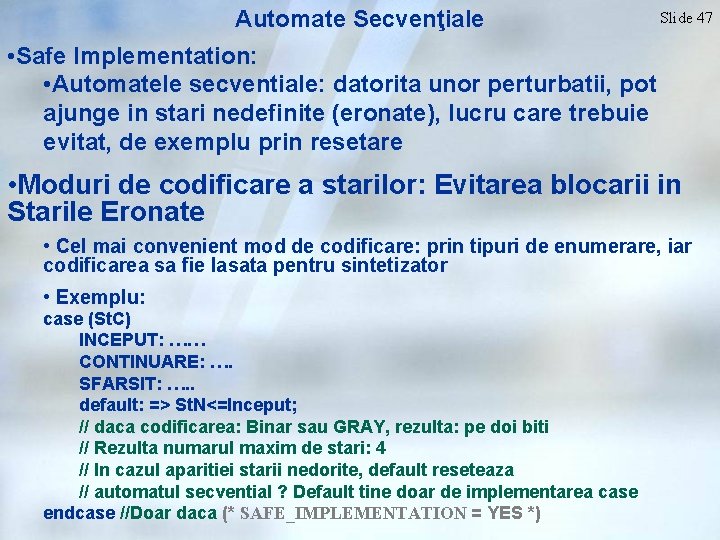

Automate Secvenţiale Slide 47 • Safe Implementation: • Automatele secventiale: datorita unor perturbatii, pot ajunge in stari nedefinite (eronate), lucru care trebuie evitat, de exemplu prin resetare • Moduri de codificare a starilor: Evitarea blocarii in Starile Eronate • Cel mai convenient mod de codificare: prin tipuri de enumerare, iar codificarea sa fie lasata pentru sintetizator • Exemplu: case (St. C) INCEPUT: …… CONTINUARE: …. SFARSIT: …. . default: => St. N<=Inceput; // daca codificarea: Binar sau GRAY, rezulta: pe doi biti // Rezulta numarul maxim de stari: 4 // In cazul aparitiei starii nedorite, default reseteaza // automatul secvential ? Default tine doar de implementarea case endcase //Doar daca (* SAFE_IMPLEMENTATION = YES *)

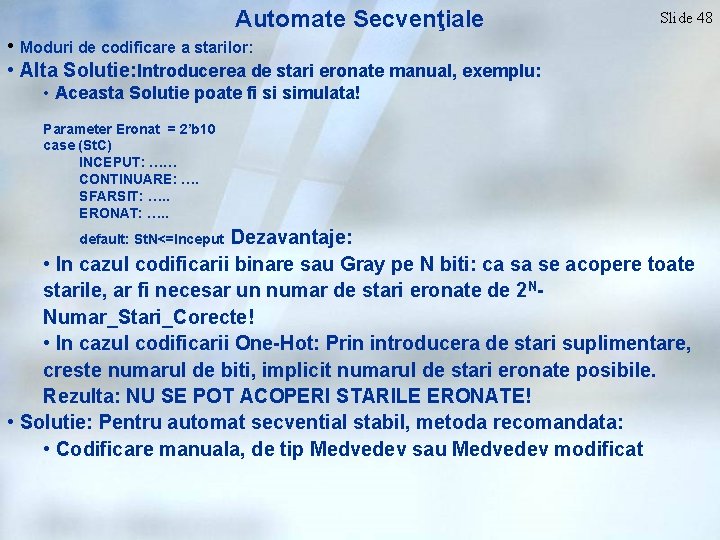

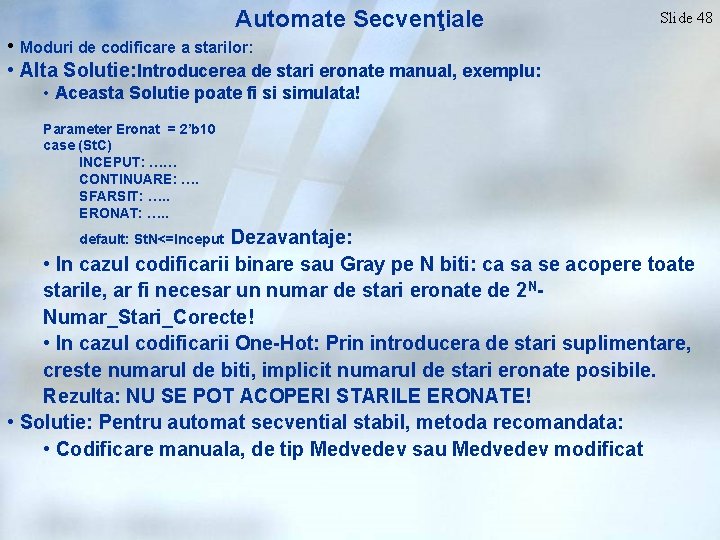

Automate Secvenţiale Slide 48 • Moduri de codificare a starilor: • Alta Solutie: Introducerea de stari eronate manual, exemplu: • Aceasta Solutie poate fi si simulata! Parameter Eronat = 2’b 10 case (St. C) INCEPUT: …… CONTINUARE: …. SFARSIT: …. . ERONAT: …. . Dezavantaje: • In cazul codificarii binare sau Gray pe N biti: ca sa se acopere toate starile, ar fi necesar un numar de stari eronate de 2 NNumar_Stari_Corecte! • In cazul codificarii One-Hot: Prin introducera de stari suplimentare, creste numarul de biti, implicit numarul de stari eronate posibile. Rezulta: NU SE POT ACOPERI STARILE ERONATE! • Solutie: Pentru automat secvential stabil, metoda recomandata: • Codificare manuala, de tip Medvedev sau Medvedev modificat default: St. N<=Inceput

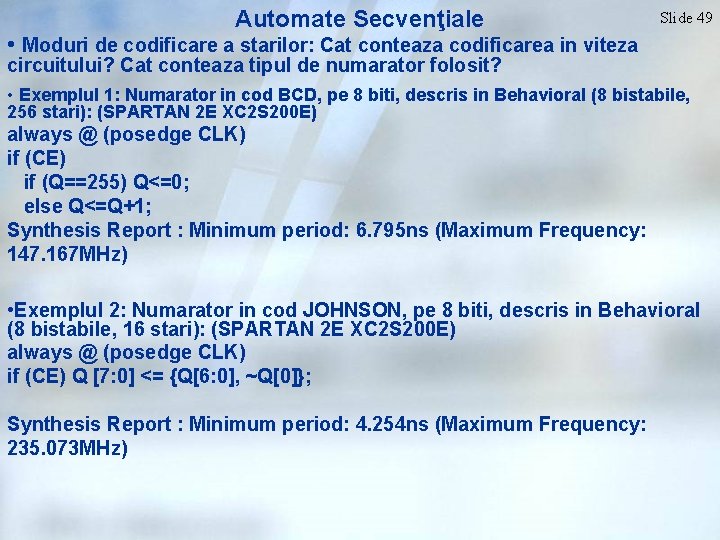

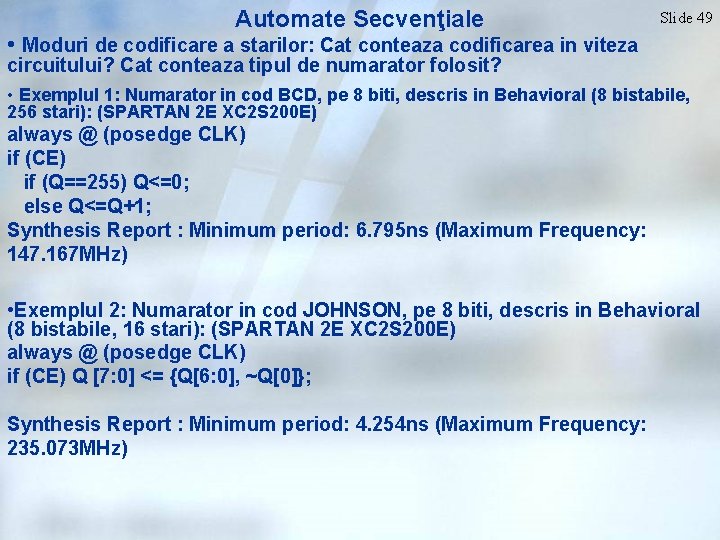

Automate Secvenţiale Slide 49 • Moduri de codificare a starilor: Cat conteaza codificarea in viteza circuitului? Cat conteaza tipul de numarator folosit? • Exemplul 1: Numarator in cod BCD, pe 8 biti, descris in Behavioral (8 bistabile, 256 stari): (SPARTAN 2 E XC 2 S 200 E) always @ (posedge CLK) if (CE) if (Q==255) Q<=0; else Q<=Q+1; Synthesis Report : Minimum period: 6. 795 ns (Maximum Frequency: 147. 167 MHz) • Exemplul 2: Numarator in cod JOHNSON, pe 8 biti, descris in Behavioral (8 bistabile, 16 stari): (SPARTAN 2 E XC 2 S 200 E) always @ (posedge CLK) if (CE) Q [7: 0] <= {Q[6: 0], ~Q[0]}; Synthesis Report : Minimum period: 4. 254 ns (Maximum Frequency: 235. 073 MHz)

Automate Secvenţiale Slide 50 • Cat conteaza tipul de codificare folosit? • Exemplul 3: Numarator in cod BINAR, pe 8 biti, descris in Behavioral (8 bistabile, 256 stari, cu insumare) always @ (posedge CLK) if (CE) Q<=Q+1; Synthesis Report : Minimum period: 4. 845 ns (Maximum Frequency: 206. 398 MHz) -Mai rapid decat Exemplul 1, insa mai incet decat Exemplul 2 -Din ce cauză?

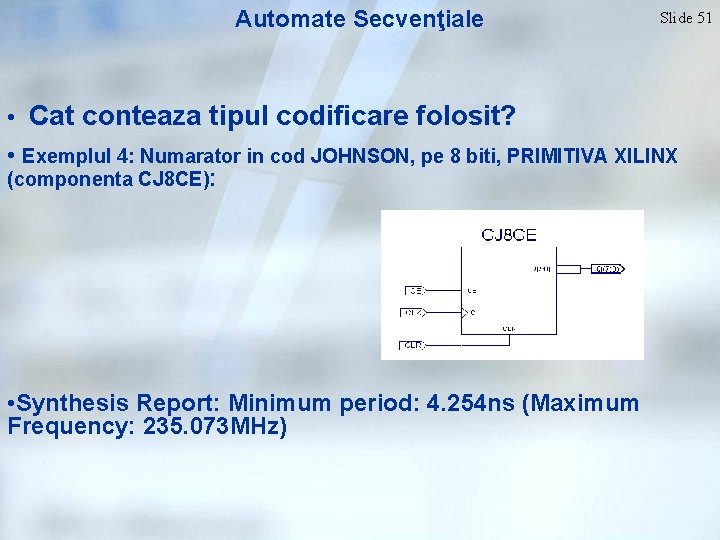

Automate Secvenţiale Slide 51 • Cat conteaza tipul codificare folosit? • Exemplul 4: Numarator in cod JOHNSON, pe 8 biti, PRIMITIVA XILINX (componenta CJ 8 CE): • Synthesis Report: Minimum period: 4. 254 ns (Maximum Frequency: 235. 073 MHz)

Automate Secvenţiale Slide 52 • Moduri de codificare a starilor: Cât contează codificarea în viteza circuitului? Cât contează tipul de numarator folosit? • Automate secventiale: • Contează modul în care sunt concepute tranzitiile (timpul de propagare prin logica combinationala care determina urmatoarea stare) • Codificarea One-HOT, Johnson: mai rapide • Numaratoare • În cod binar, descris cu behavioral: Fmax= 147. 167 MHz • În cod Johnson, descris ori cu behavioral, ori prin folosirea unei primitive XILINX: Fmax= 235. 073 MHz • În cod binar, descris simplificat: Fmax= 206. 398 MHz • În cod binar, folosind primitiva CB 8 CE: Fmax= 117. 233 MHz • Observatie: toate sintezele au fost efectuate pe Spartan IIE XC 2 S 200 E- PQ 208 -6. Pe alte componente, timpii de propagare sunt diferiti (mai mari sau mai mici)

Automate Secvenţiale Slide 53 • Concluzii: • Timpii de propagare sunt determinaţi în principal de circuitele combinaţionale • Circuite combinaţionale mai complexe şi mai multe rezultă în timpi de propagare mai mari • Codificare binară, Gray: Mai multă logică combinaţională, frecvenţă de lucru mai redusă • Gray: Doar un singur bit se schimba la o singura tranziție! Pericol de hazard mai redus • Codificare One-Hot, Johnson: mai puţine circuite combinaţionale, frecvenţă de lucru mărită