FINITE STATE MACHINES FSMs Dr Konstantinos Tatas Finite

- Slides: 62

FINITE STATE MACHINES (FSMs) Dr. Konstantinos Tatas

Finite State Machine • A generic model for sequential circuits used in sequential circuit design ACOE 161 - Digital Logic for Computers - Frederick University

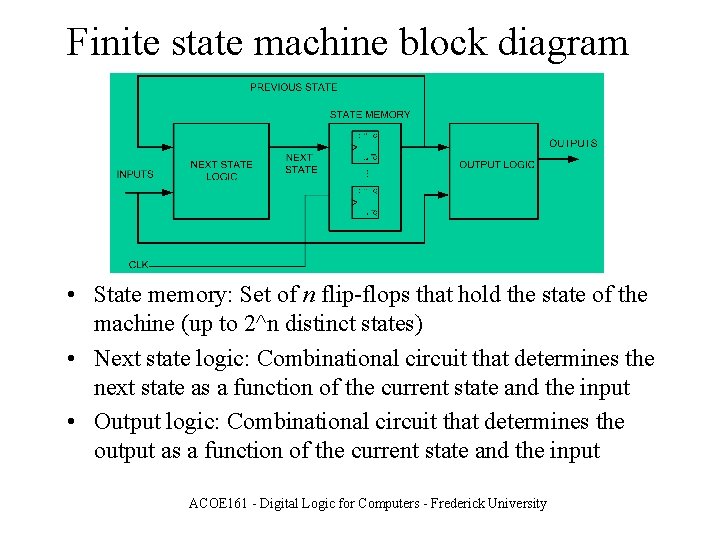

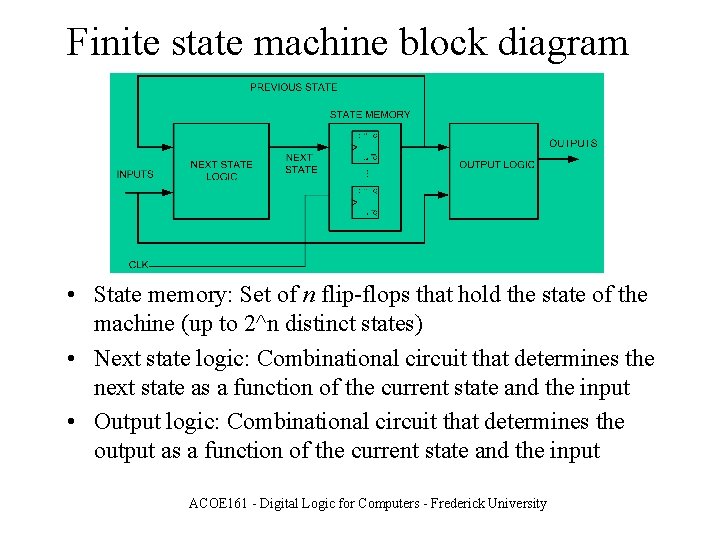

Finite state machine block diagram • State memory: Set of n flip-flops that hold the state of the machine (up to 2^n distinct states) • Next state logic: Combinational circuit that determines the next state as a function of the current state and the input • Output logic: Combinational circuit that determines the output as a function of the current state and the input ACOE 161 - Digital Logic for Computers - Frederick University

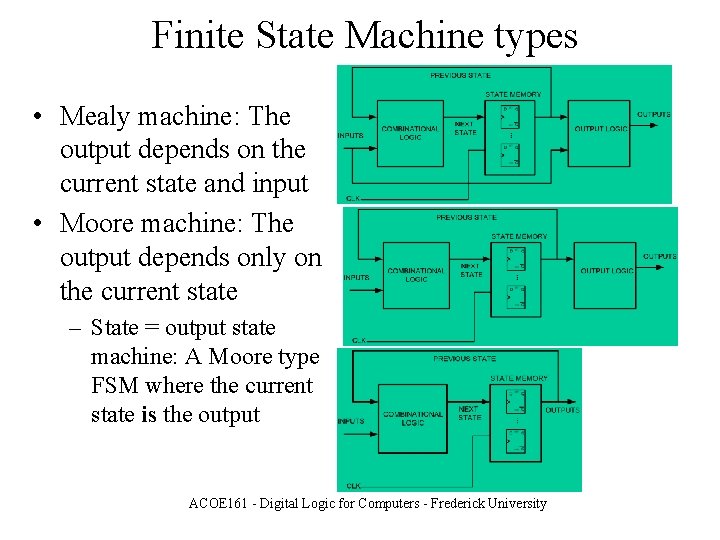

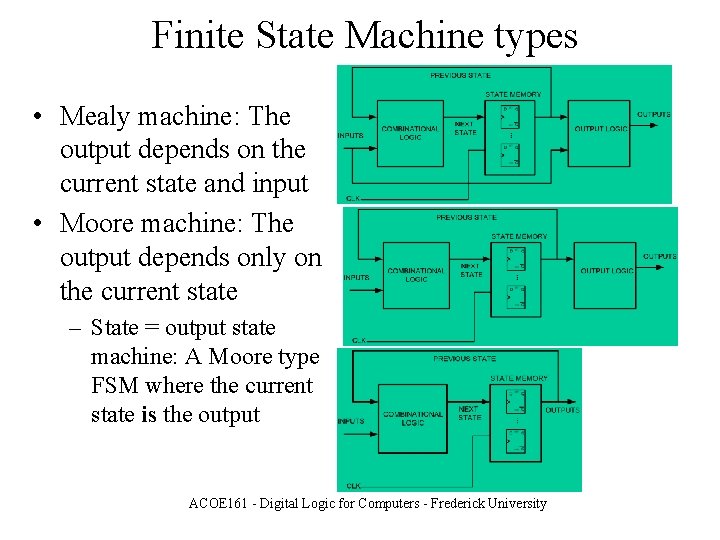

Finite State Machine types • Mealy machine: The output depends on the current state and input • Moore machine: The output depends only on the current state – State = output state machine: A Moore type FSM where the current state is the output ACOE 161 - Digital Logic for Computers - Frederick University

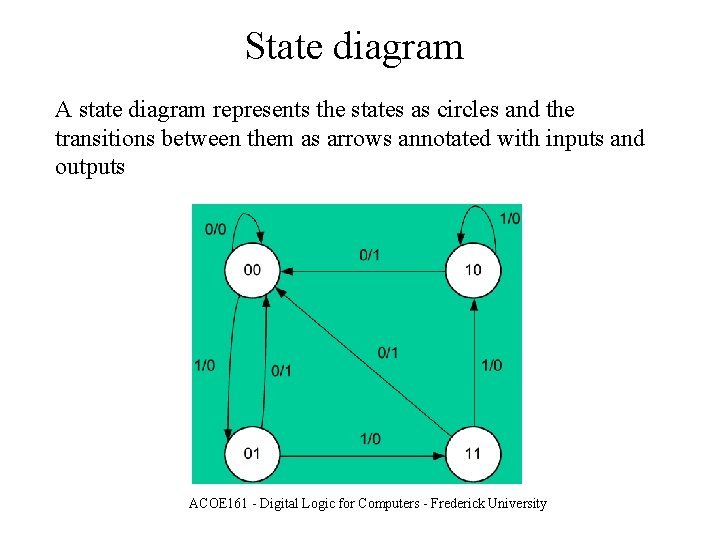

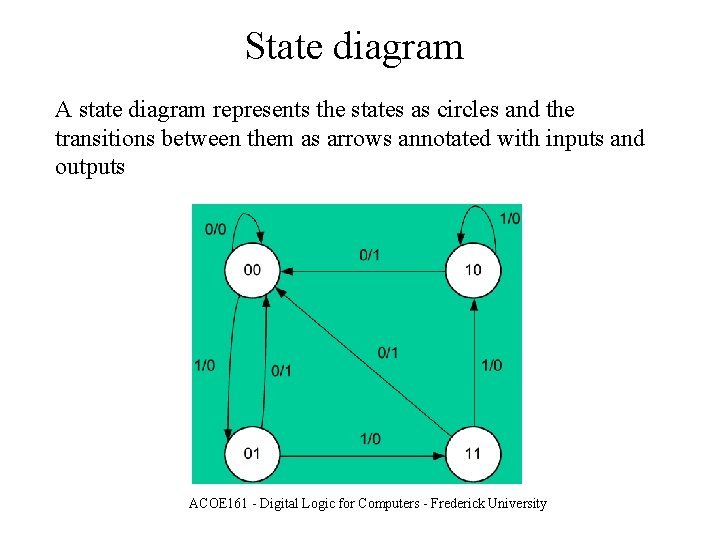

State diagram A state diagram represents the states as circles and the transitions between them as arrows annotated with inputs and outputs ACOE 161 - Digital Logic for Computers - Frederick University

Analysis of FSMs with D flip-flops • Determine the next state and output functions • Use the functions to create a state/output table that specifies every possible next state and output for any combination of current state and input ACOE 161 - Digital Logic for Computers - Frederick University

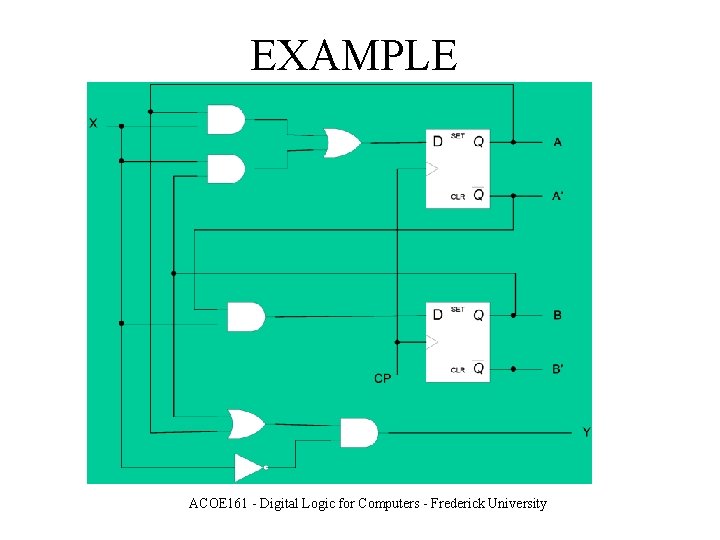

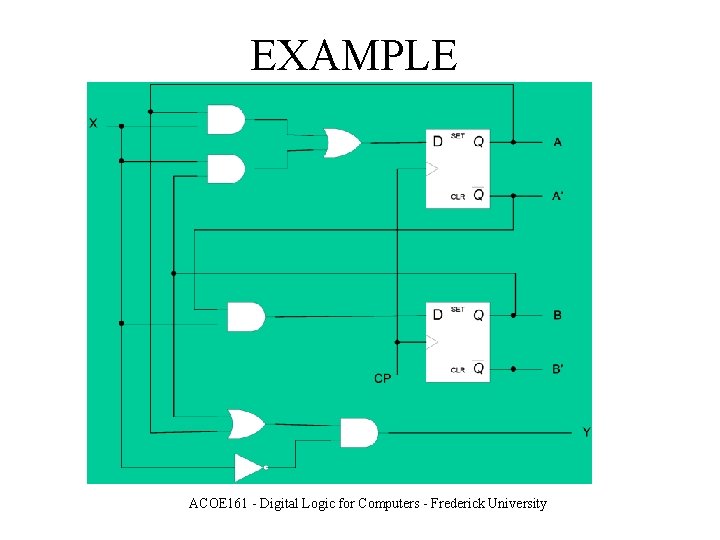

EXAMPLE ACOE 161 - Digital Logic for Computers - Frederick University

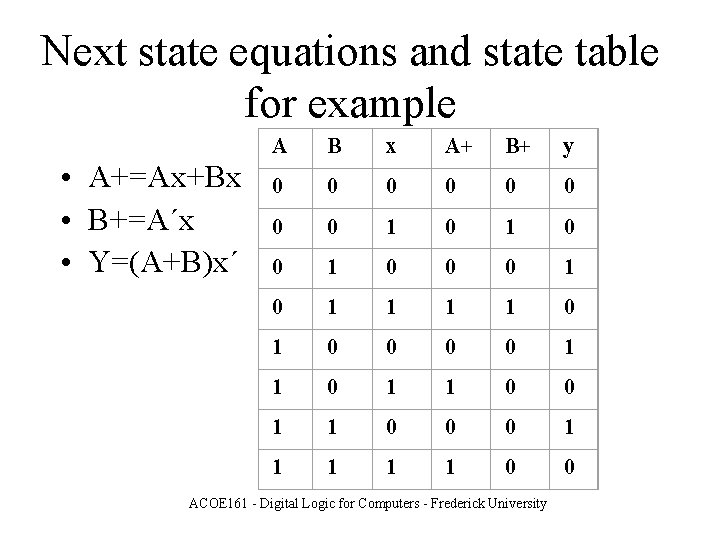

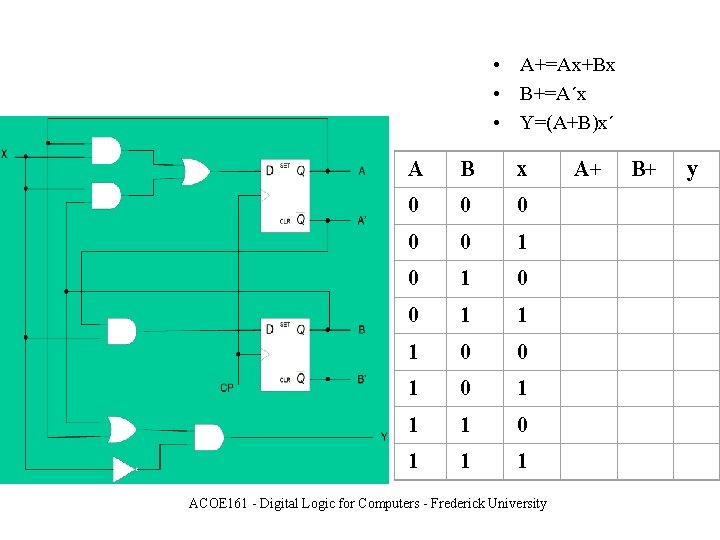

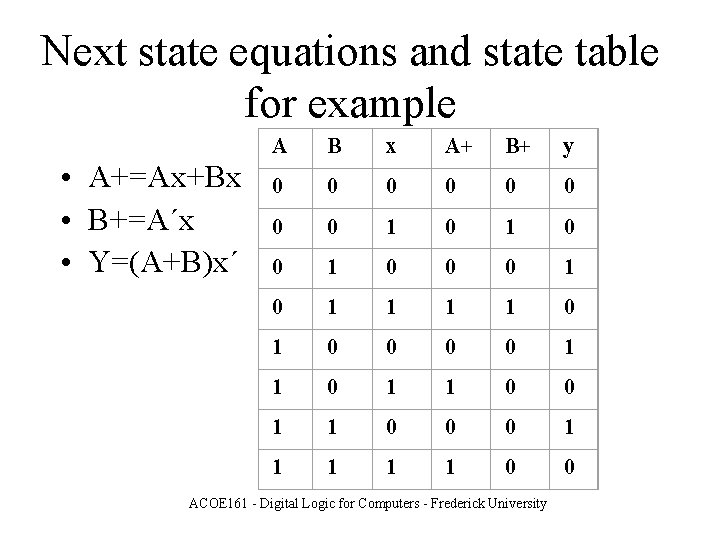

Next state equations and state table for example • A+=Ax+Bx • B+=A΄x • Y=(A+B)x΄ A B x A+ B+ y 0 0 0 0 1 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 0 1 1 1 0 0 ACOE 161 - Digital Logic for Computers - Frederick University

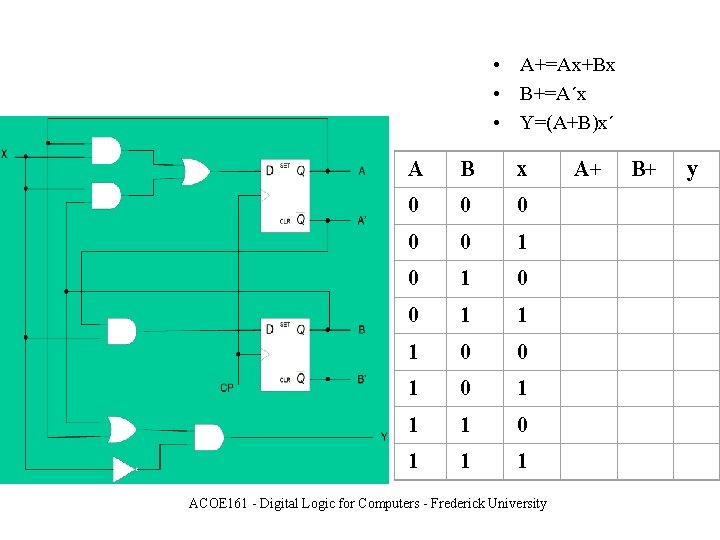

• A+=Ax+Bx • B+=A΄x • Y=(A+B)x΄ A B x 0 0 0 1 1 1 0 0 1 1 1 ACOE 161 - Digital Logic for Computers - Frederick University A+ B+ y

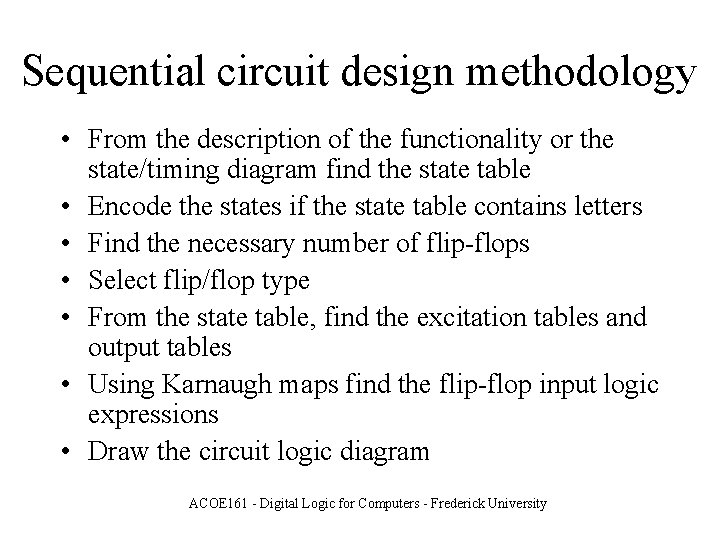

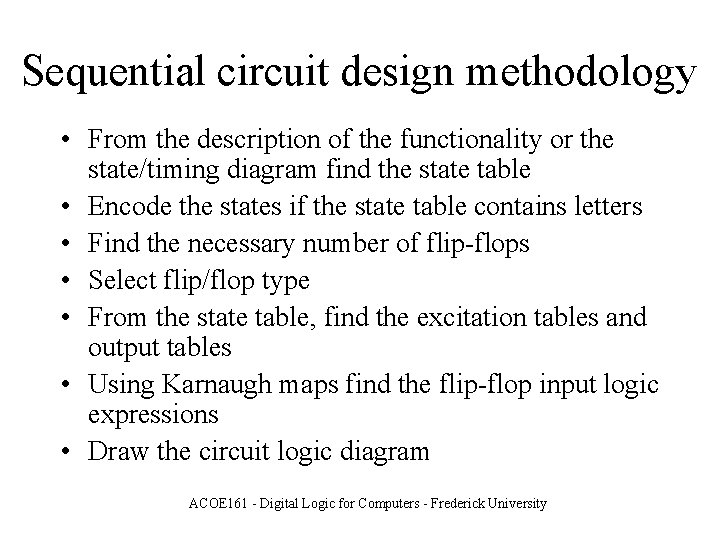

Sequential circuit design methodology • From the description of the functionality or the state/timing diagram find the state table • Encode the states if the state table contains letters • Find the necessary number of flip-flops • Select flip/flop type • From the state table, find the excitation tables and output tables • Using Karnaugh maps find the flip-flop input logic expressions • Draw the circuit logic diagram ACOE 161 - Digital Logic for Computers - Frederick University

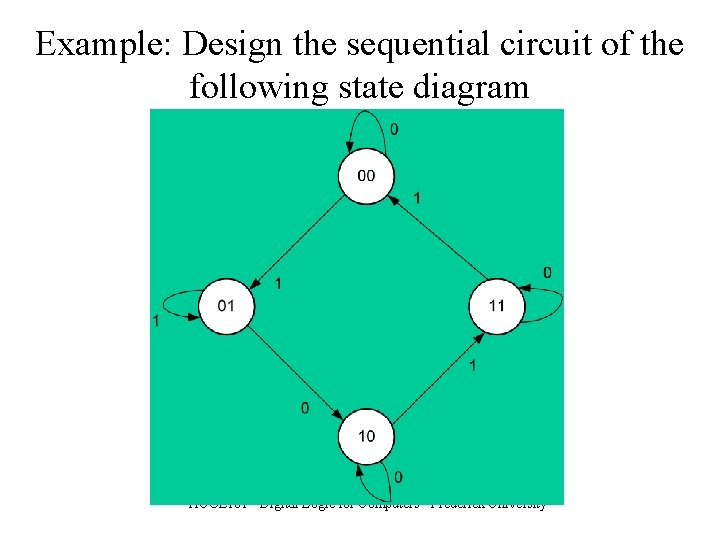

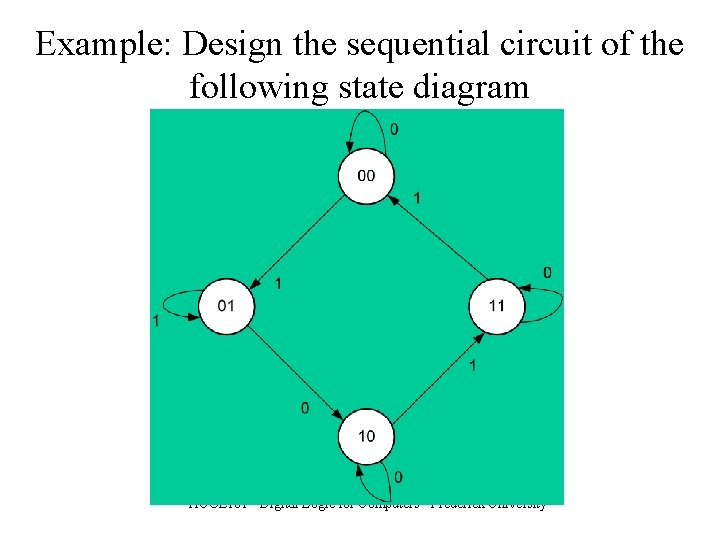

Example: Design the sequential circuit of the following state diagram ACOE 161 - Digital Logic for Computers - Frederick University

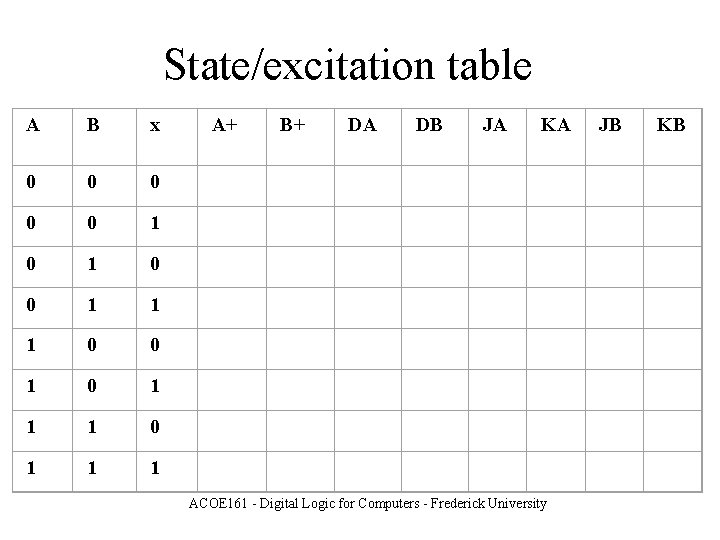

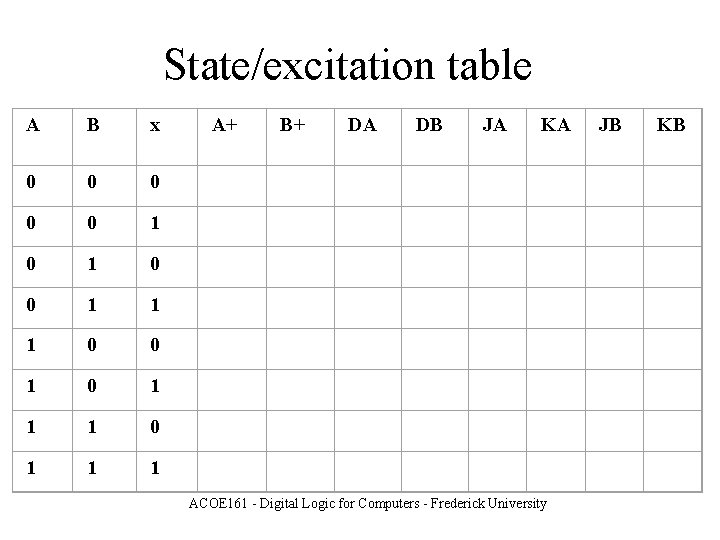

State/excitation table A B x A+ B+ DA DB JA KA JB KB 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 ACOE 161 - Digital Logic for Computers - Frederick University

Karnaugh maps for combinational circuit ACOE 161 - Digital Logic for Computers - Frederick University

Circuit logic diagram ACOE 161 - Digital Logic for Computers - Frederick University

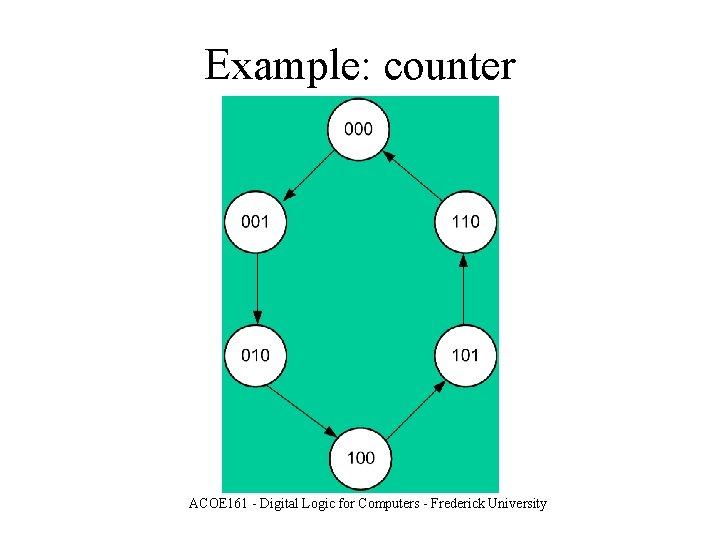

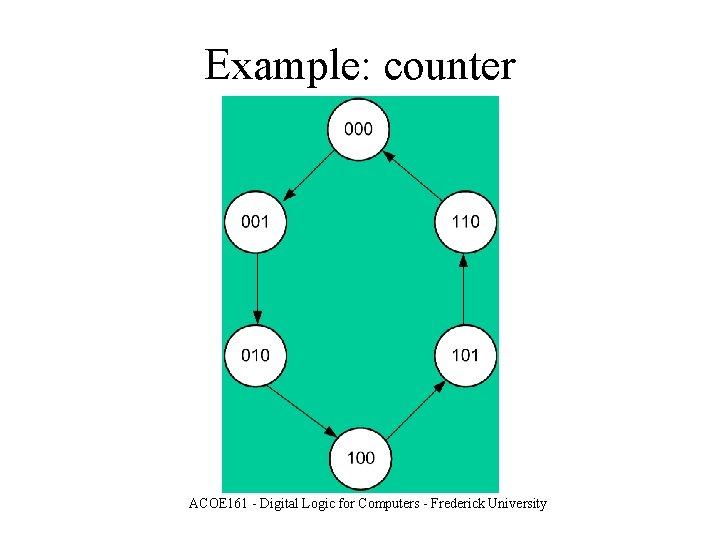

Example: counter ACOE 161 - Digital Logic for Computers - Frederick University

Self-correcting state machines • The previous example did not include two possible states “ 011” and “ 111”. If the counter unexpectedly falls into one of those states there are two possibilities: – The counter will recover by entering a valid state after a finite number of cycles (self-correcting) – The counter will stay in a non-valid state until the f/fs are reset (not self-correcting) • Finite state machines should be designed to be self correcting by assigning non-valid states to a valid next state (no don’t cares in the excitation table) ACOE 161 - Digital Logic for Computers - Frederick University

Example • Design a self-correcting one-digit BCD counter ACOE 161 - Digital Logic for Computers - Frederick University

State minimization/assignment • Often the state of the circuit is not also the output and therefore the states are named abstractly • State minimization and state assignment are then required • State minimization is the simplification of the state diagram so that a circuit with less states produces the same output sequence • State assignment is the process of assigning a binary number to each state ACOE 161 - Digital Logic for Computers - Frederick University

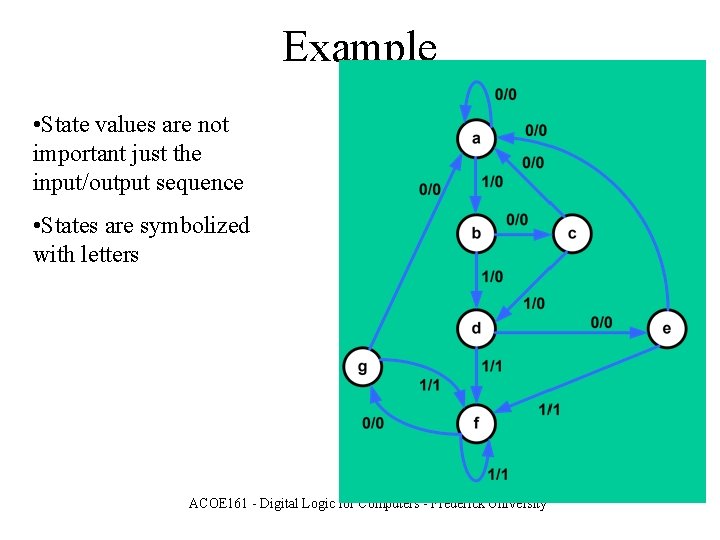

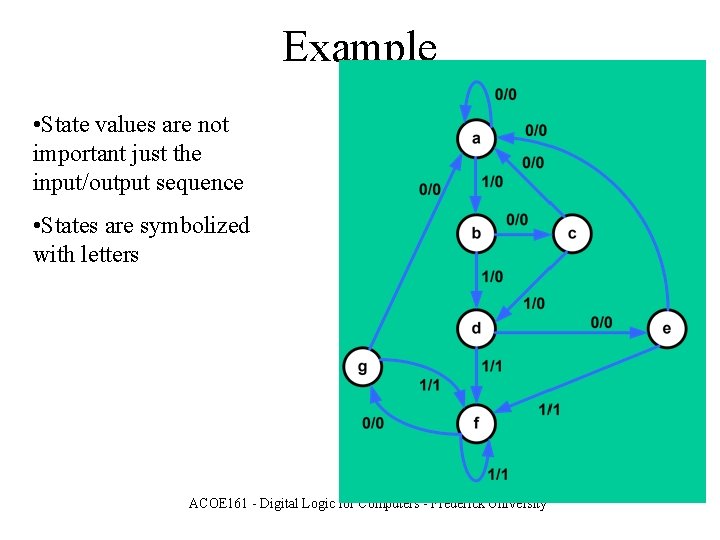

Example • State values are not important just the input/output sequence • States are symbolized with letters ACOE 161 - Digital Logic for Computers - Frederick University

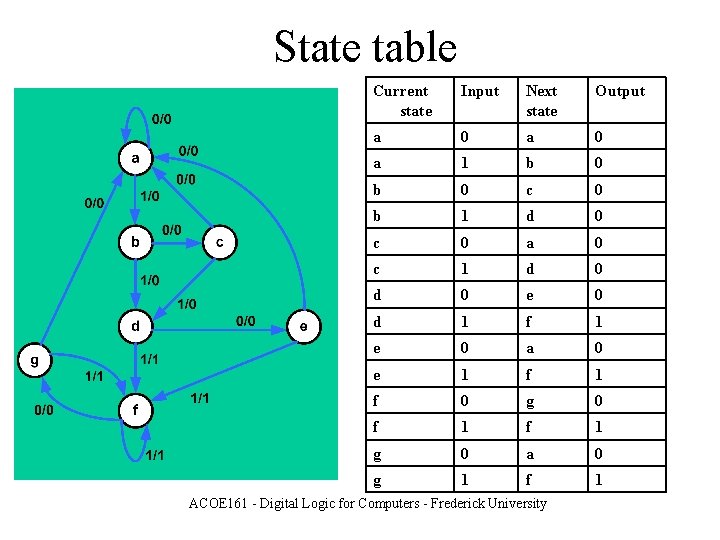

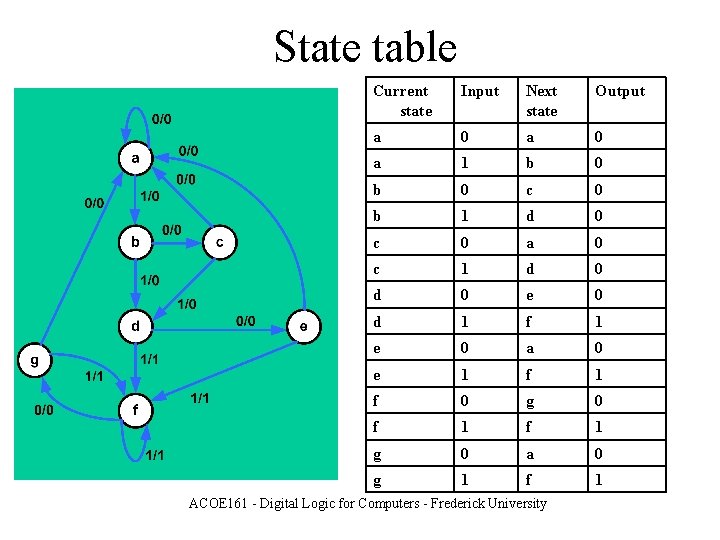

State table Current state Input Next state Output a 0 a 1 b 0 c 0 b 1 d 0 c 0 a 0 c 1 d 0 e 0 d 1 f 1 e 0 a 0 e 1 f 0 g 0 f 1 g 0 a 0 g 1 f 1 ACOE 161 - Digital Logic for Computers - Frederick University

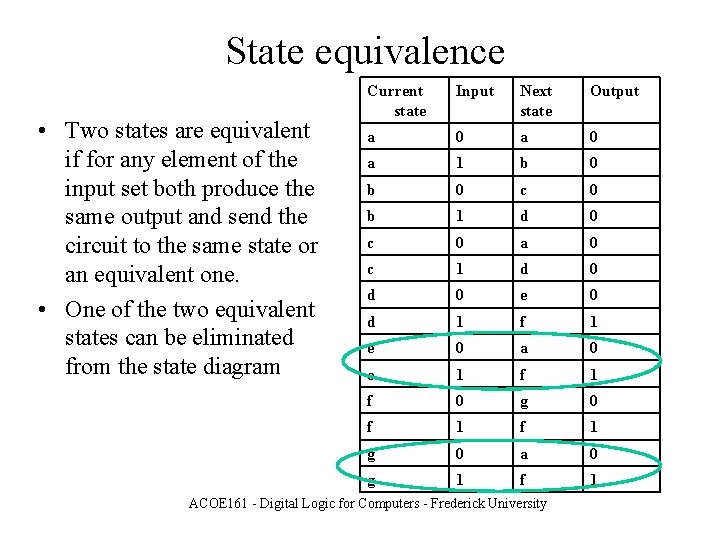

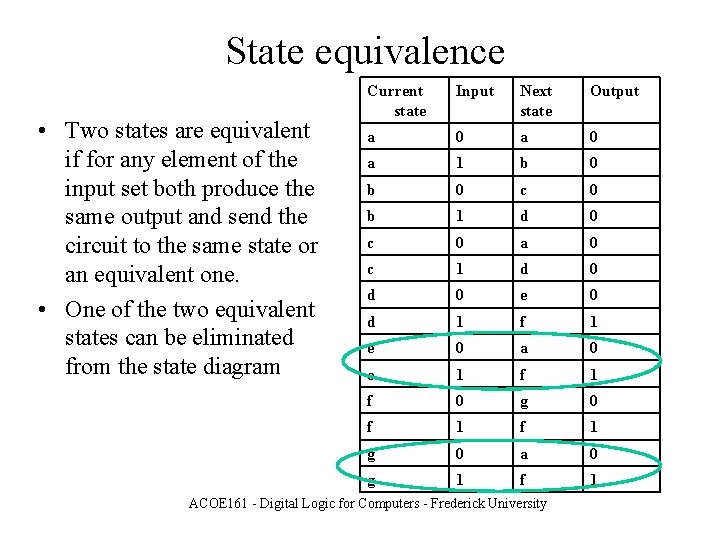

State equivalence • Two states are equivalent if for any element of the input set both produce the same output and send the circuit to the same state or an equivalent one. • One of the two equivalent states can be eliminated from the state diagram Current state Input Next state Output a 0 a 1 b 0 c 0 b 1 d 0 c 0 a 0 c 1 d 0 e 0 d 1 f 1 e 0 a 0 e 1 f 0 g 0 f 1 g 0 a 0 g 1 f 1 ACOE 161 - Digital Logic for Computers - Frederick University

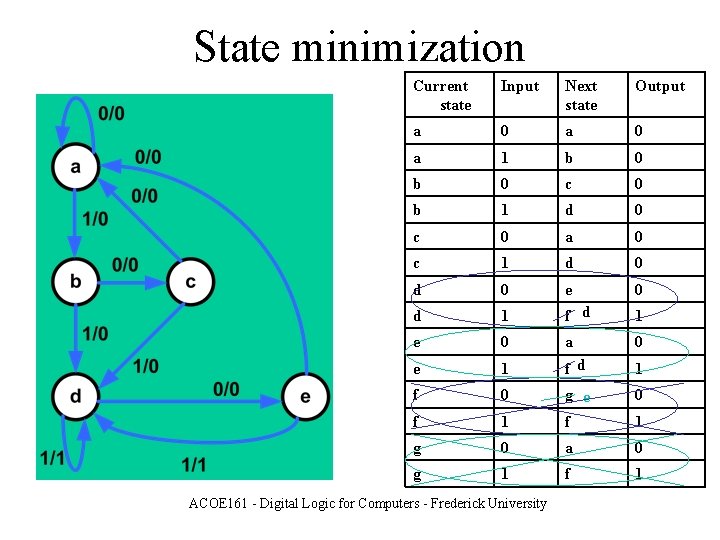

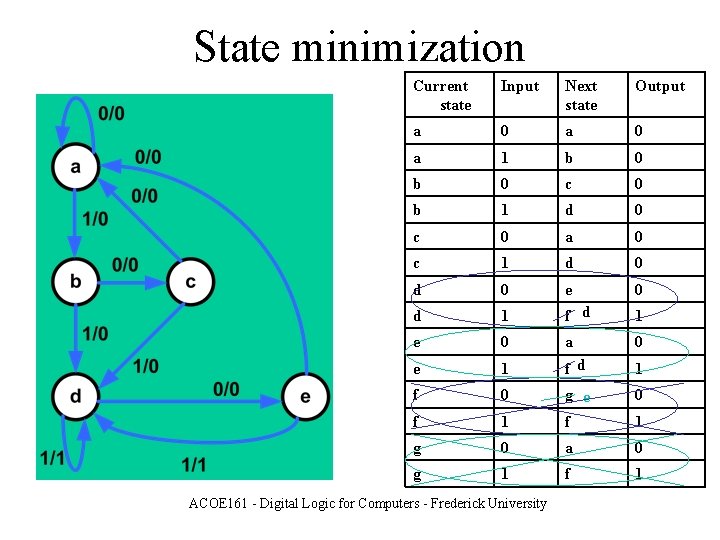

State minimization Current state Input Next state Output a 0 a 1 b 0 c 0 b 1 d 0 c 0 a 0 c 1 d 0 e 0 d 1 f d 1 e 0 a 0 e 1 fd 1 f 0 g e 0 f 1 g 0 a 0 g 1 f 1 ACOE 161 - Digital Logic for Computers - Frederick University

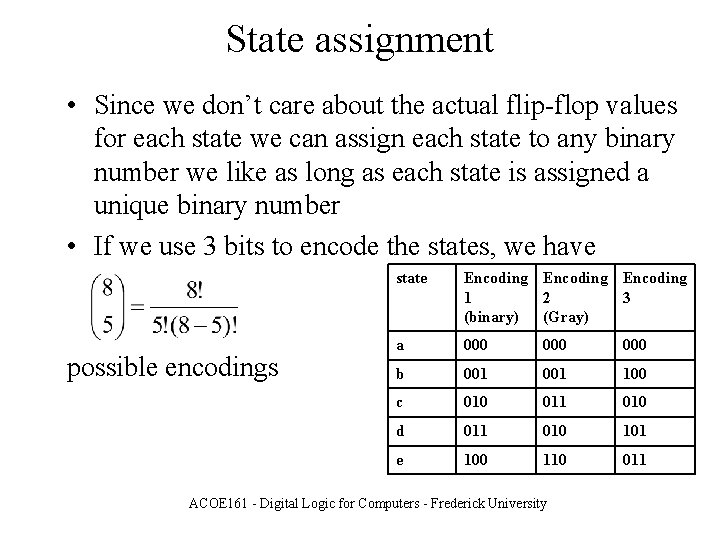

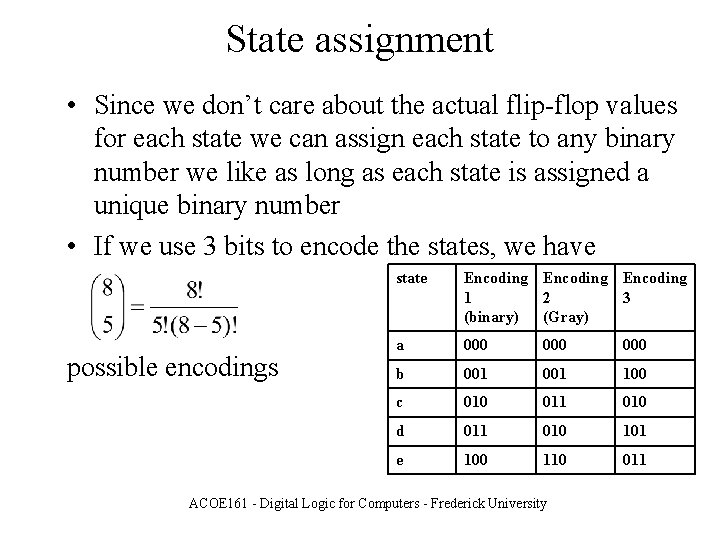

State assignment • Since we don’t care about the actual flip-flop values for each state we can assign each state to any binary number we like as long as each state is assigned a unique binary number • If we use 3 bits to encode the states, we have possible encodings state Encoding 1 2 3 (binary) (Gray) a 000 000 b 001 100 c 010 011 010 d 011 010 101 e 100 110 011 ACOE 161 - Digital Logic for Computers - Frederick University

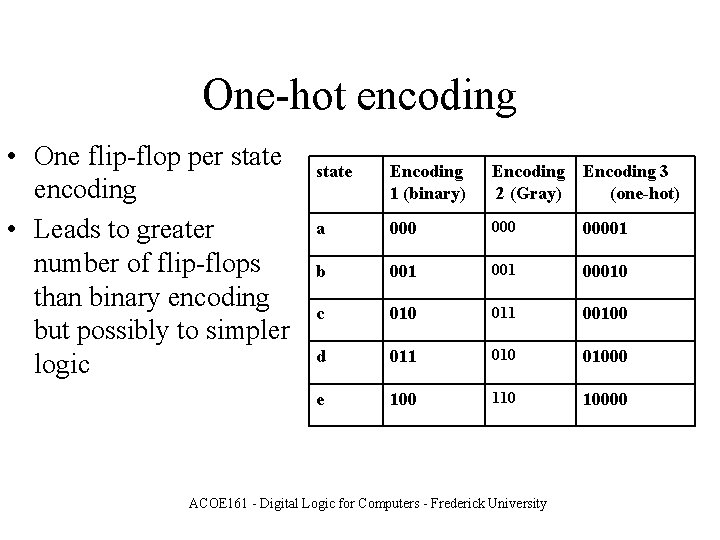

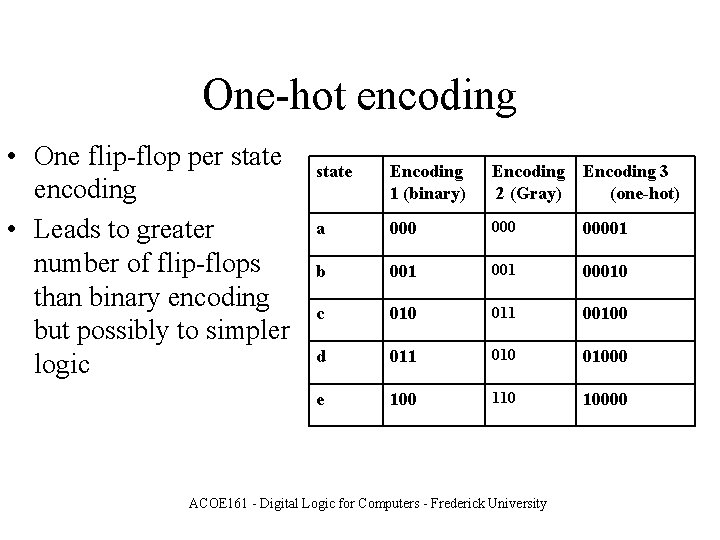

One-hot encoding • One flip-flop per state encoding • Leads to greater number of flip-flops than binary encoding but possibly to simpler logic state Encoding 1 (binary) Encoding 3 2 (Gray) (one-hot) a 000 00001 b 001 00010 c 010 011 00100 d 011 01000 e 100 110 10000 ACOE 161 - Digital Logic for Computers - Frederick University

Algorithmic State Machines

Introduction Digital system is specified by the following three components: • The set of registers in the system • The operations that are performed on the data stored in the registers. • The control that supervises the sequences of operations in the system. ACOE 161 - Digital Logic for Computers - Frederick University

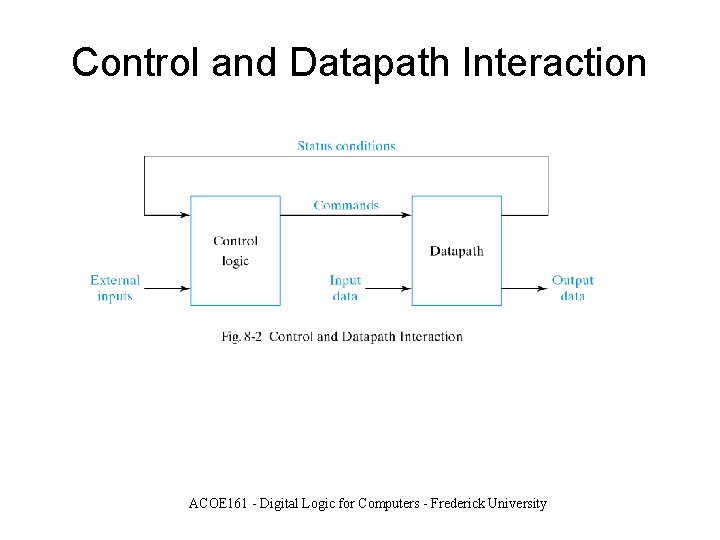

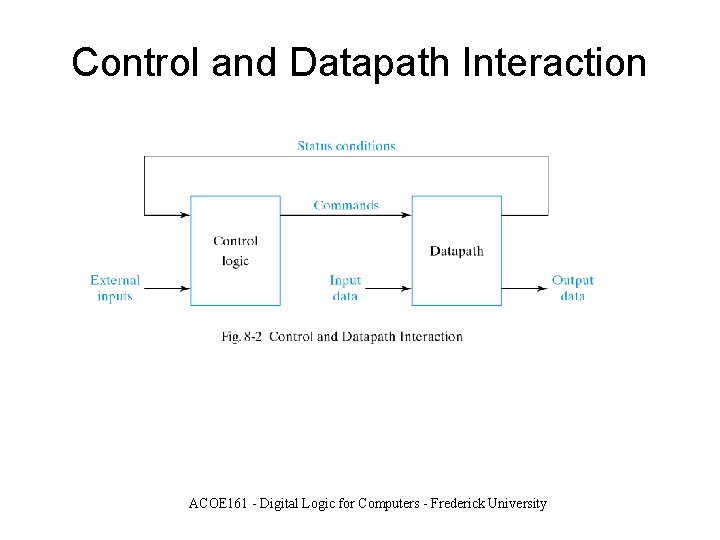

Control and Datapath Interaction ACOE 161 - Digital Logic for Computers - Frederick University

Datapath • Binary information in digital systems classified as either data or control. • Data – bits of information manipulated by performing arithmetic and logic operations. • Hardware components realizing above operations are adders, decoders, multiplexers, counters e. t. c ACOE 161 - Digital Logic for Computers - Frederick University

Control Path • Command signals used to supervise execution of algorithms by datapath. • Bi-directional communication with datapath through status conditions used to determine the sequence of control signals. • Control logic inherently sequential. • Control logic is usually implemented using FSMs ACOE 161 - Digital Logic for Computers - Frederick University

Algorithm Implementation • Often we have to implement an algorithm in hardware instead of software • Algorithm is a well defined procedure consisting of a finite number of steps to the solution of a problem. • It is often hard to translate the algorithm into an FSM. • ASMs can serve as stand-alone sequential network model. ACOE 161 - Digital Logic for Computers - Frederick University

Algorithmic State Machine • Used to graphically describe the operations of an FSM more concisely • Resembles conventional flowcharts – differs in interpretation. • Conventional flowchart – sequential way of representing procedural steps and decision paths for algorithm -No time relations incorporated • ASM chart – representation of sequence of events together with timing relations between states of sequential controller and events occurring while moving between steps ACOE 161 - Digital Logic for Computers - Frederick University

ASM Chart • Three basic elements: state box, decision box and conditional box -State and decision boxes used in conventional flowcharts -Conditional box characteristic to ASM • State box -Used to indicate states in control sequence • Register operations and output signals used to control generation of next state written ACOE 161 - Digital Logic for Computers - Frederick University

State box • Represents one state in the ASM. • May have an optional state output list. • Single entry. • Single exit to state or decision boxes. ACOE 161 - Digital Logic for Computers - Frederick University

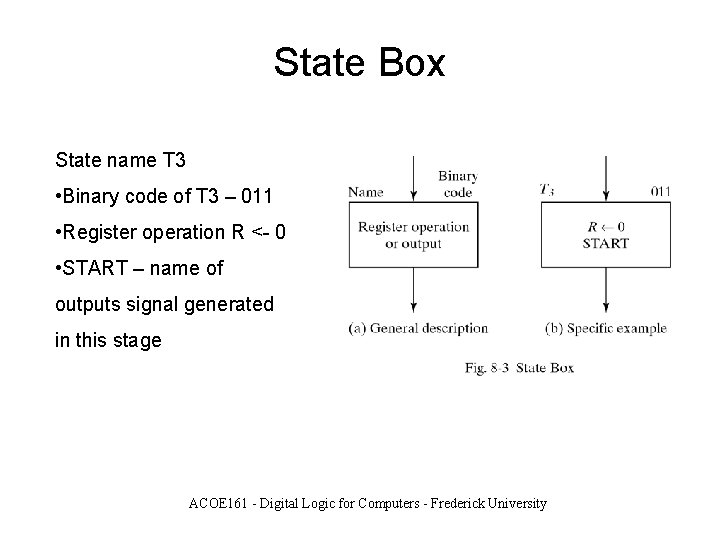

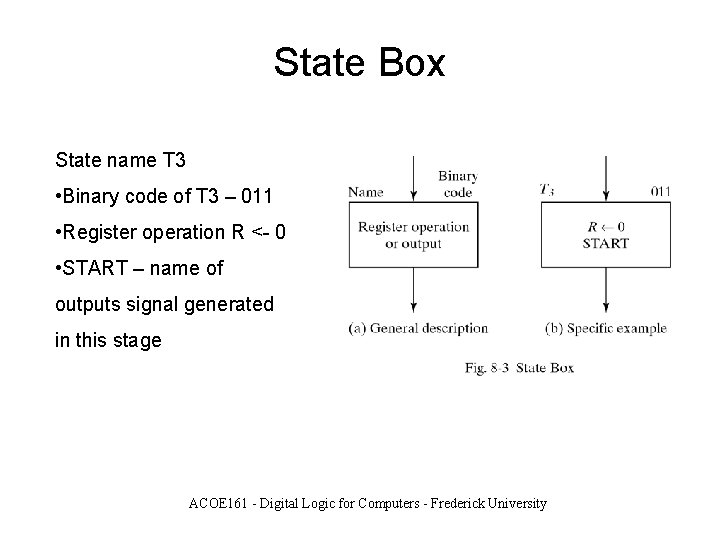

State Box State name T 3 • Binary code of T 3 – 011 • Register operation R <- 0 • START – name of outputs signal generated in this stage ACOE 161 - Digital Logic for Computers - Frederick University

Decision box • Provides for next alternatives and conditional outputs. • Conditional output based on logic value of Boolean expression involving external input variables and status information. • Single entry. • Dual exit, denoting if Boolean expression is true or false. • Exits to decision, state or conditional boxes. ACOE 161 - Digital Logic for Computers - Frederick University

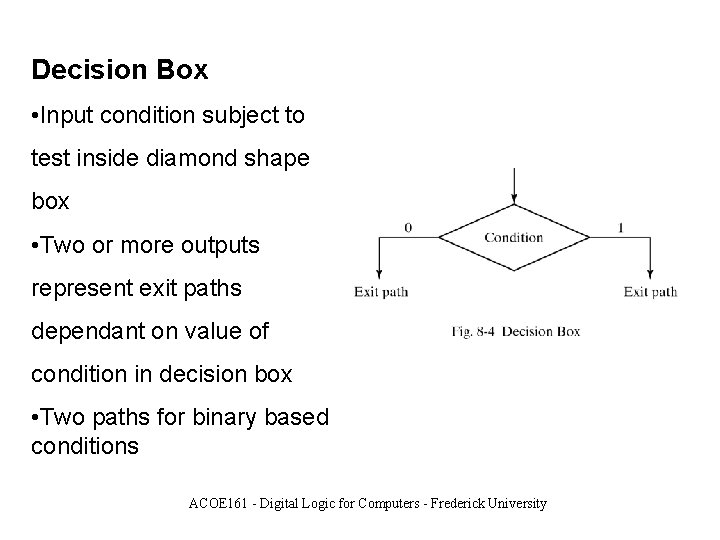

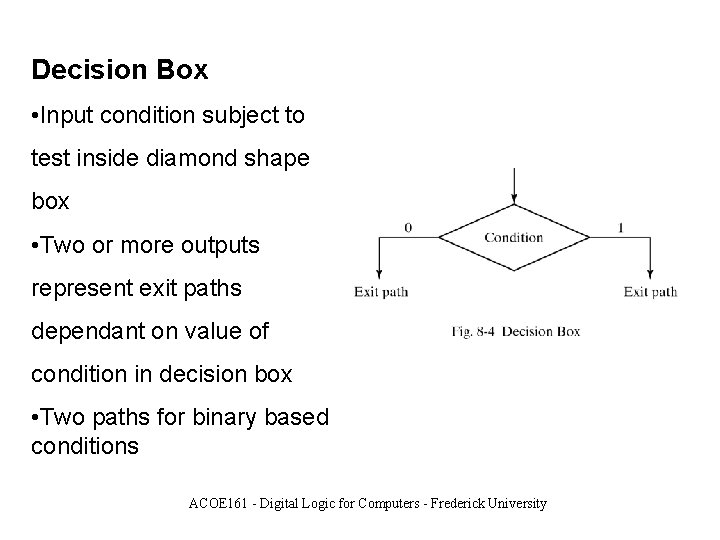

Decision Box • Input condition subject to test inside diamond shape box • Two or more outputs represent exit paths dependant on value of condition in decision box • Two paths for binary based conditions ACOE 161 - Digital Logic for Computers - Frederick University

Conditional output box • Provides a listing of output variables that are to have a value logic-1, i. e. , those output variables being asserted. • Single entry from decision box. • Single exit to decision or state box. ACOE 161 - Digital Logic for Computers - Frederick University

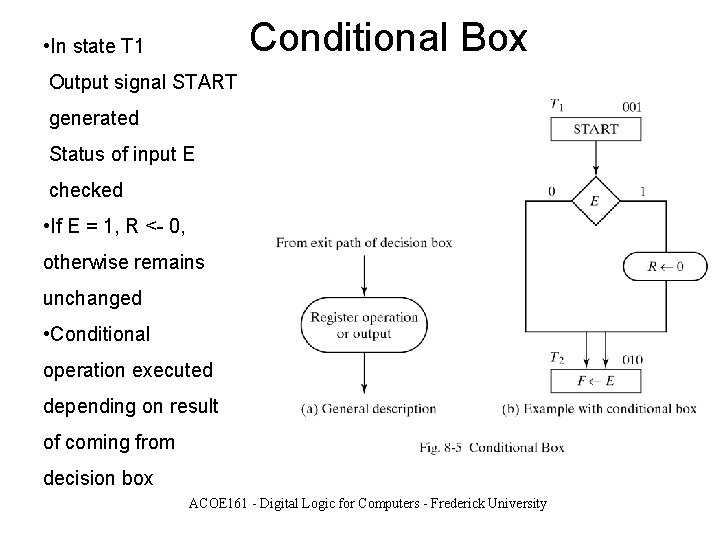

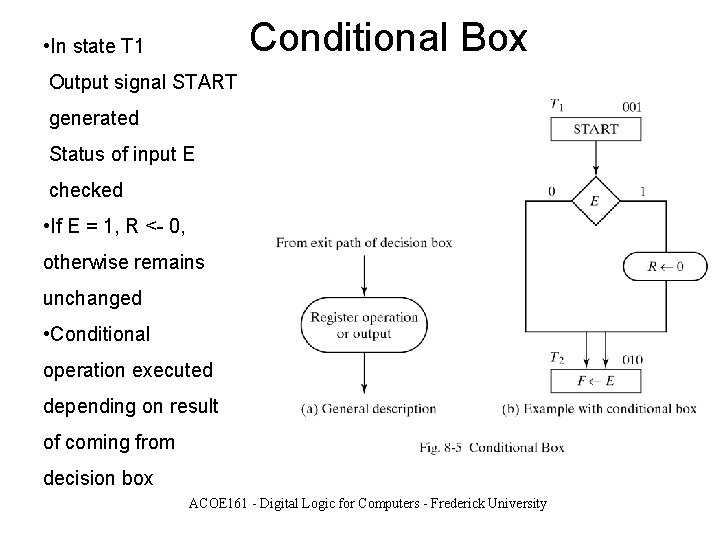

Conditional Box • In state T 1 Output signal START generated Status of input E checked • If E = 1, R <- 0, otherwise remains unchanged • Conditional operation executed depending on result of coming from decision box ACOE 161 - Digital Logic for Computers - Frederick University

ASM Block • Consists of the interconnection of a single state box along with one or more decision and/or conditional boxes. • It has one entry path which leads directly to its state box, and one or more exit paths. • Each exit path must lead directly to a state, including the state box in itself. • A path through an ASM block from its state box to an exit path is called a link path. ACOE 161 - Digital Logic for Computers - Frederick University

Timing Considerations All sequential elements in datapath and control path controlled by master-clock generator. Does not necessarily imply single clock in design. • Multiple clocks can be obtained through division of clock signals from master-clock generator. • Not only internal signals, but also inputs synchronized with clock. • Normally, inputs supplied by other devices working with the same master clock. • Some inputs can arrive asynchronously Difficult to handle by synchronous designs, require asynchronous glue-logic. ACOE 161 - Digital Logic for Computers - Frederick University

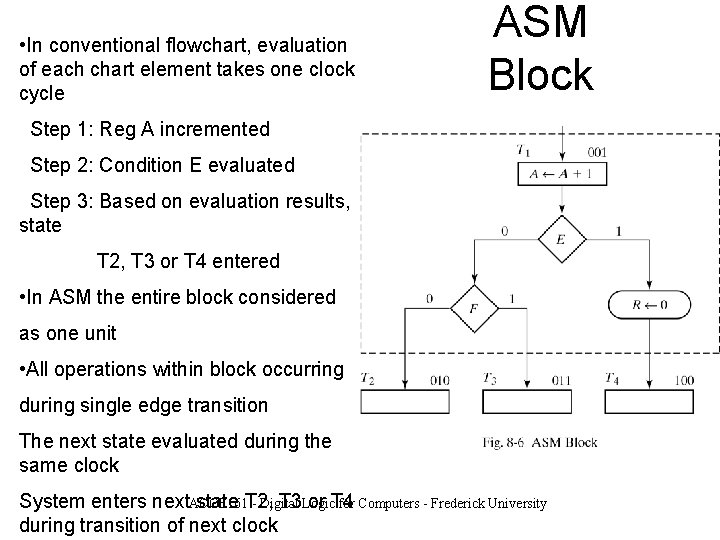

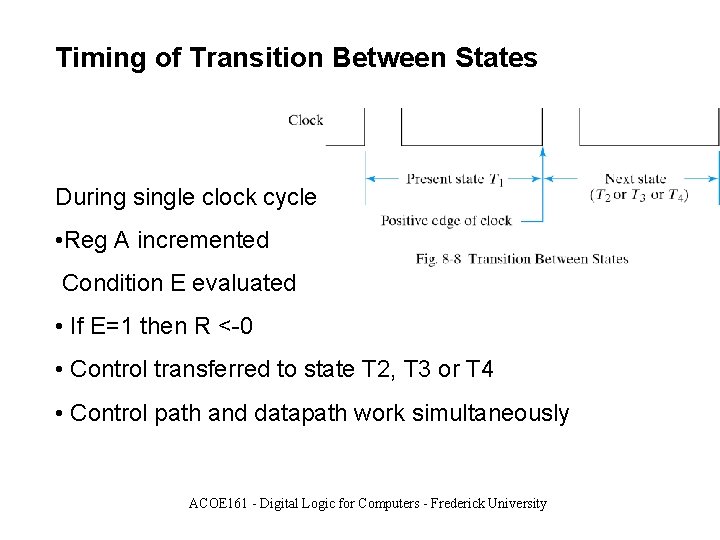

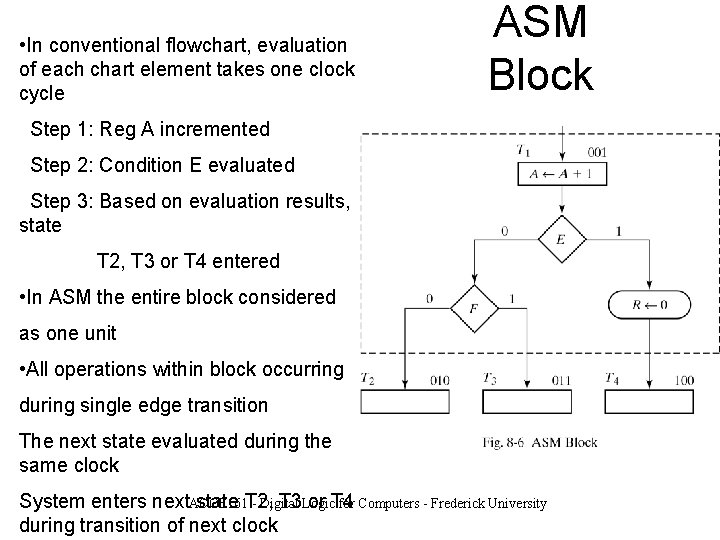

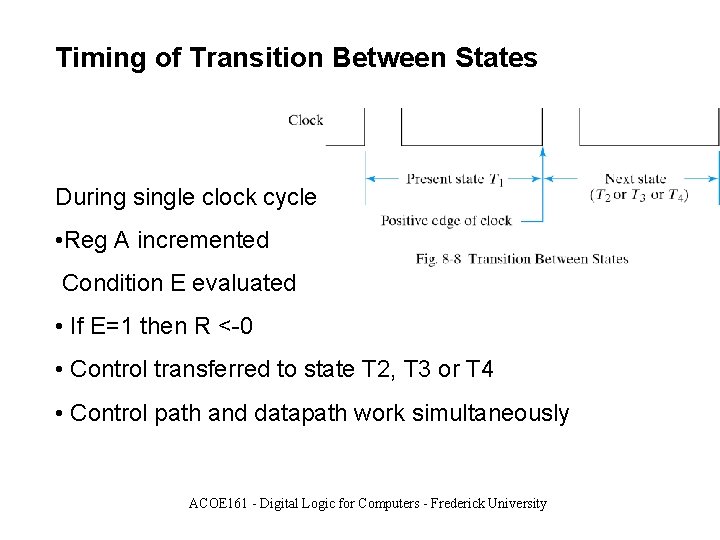

• In conventional flowchart, evaluation of each chart element takes one clock cycle ASM Block Step 1: Reg A incremented Step 2: Condition E evaluated Step 3: Based on evaluation results, state T 2, T 3 or T 4 entered • In ASM the entire block considered as one unit • All operations within block occurring during single edge transition The next state evaluated during the same clock System enters next. ACOE 161 - Digital Logic for Computers - Frederick University state T 2, T 3 or T 4 during transition of next clock

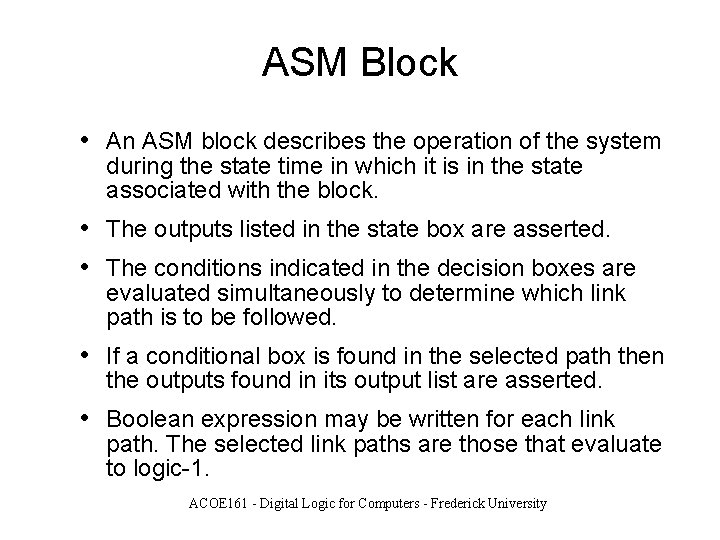

ASM Block • An ASM block describes the operation of the system during the state time in which it is in the state associated with the block. • The outputs listed in the state box are asserted. • The conditions indicated in the decision boxes are evaluated simultaneously to determine which link path is to be followed. • If a conditional box is found in the selected path then the outputs found in its output list are asserted. • Boolean expression may be written for each link path. The selected link paths are those that evaluate to logic-1. ACOE 161 - Digital Logic for Computers - Frederick University

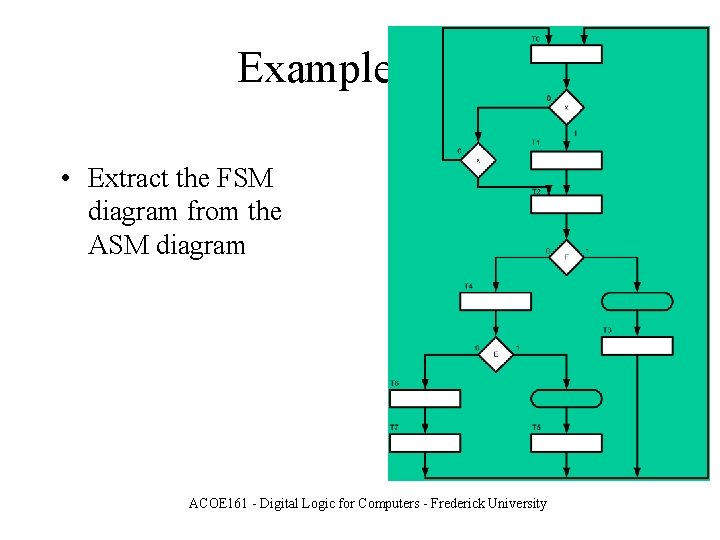

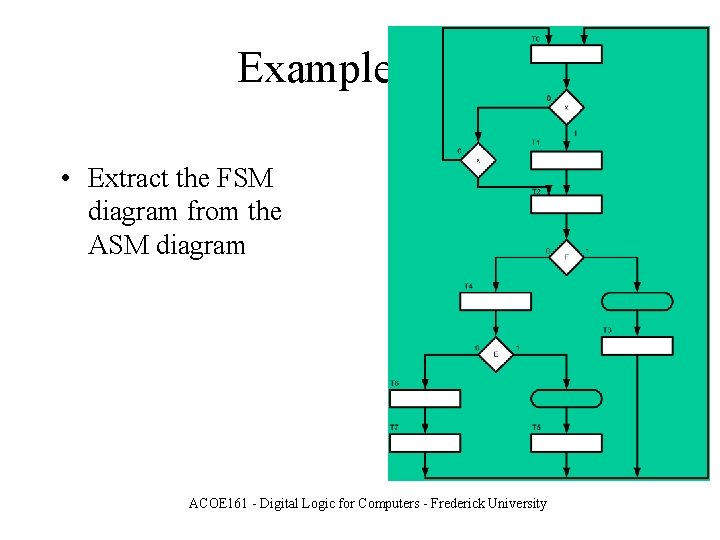

Example 2 • Extract the FSM diagram from the ASM diagram ACOE 161 - Digital Logic for Computers - Frederick University

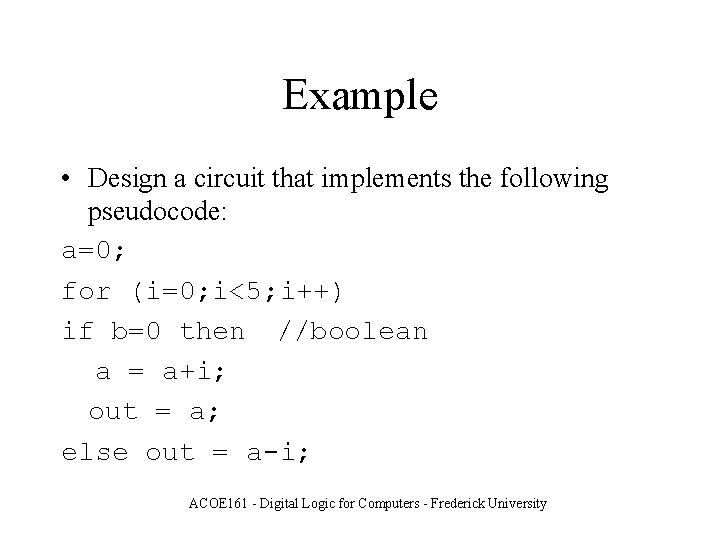

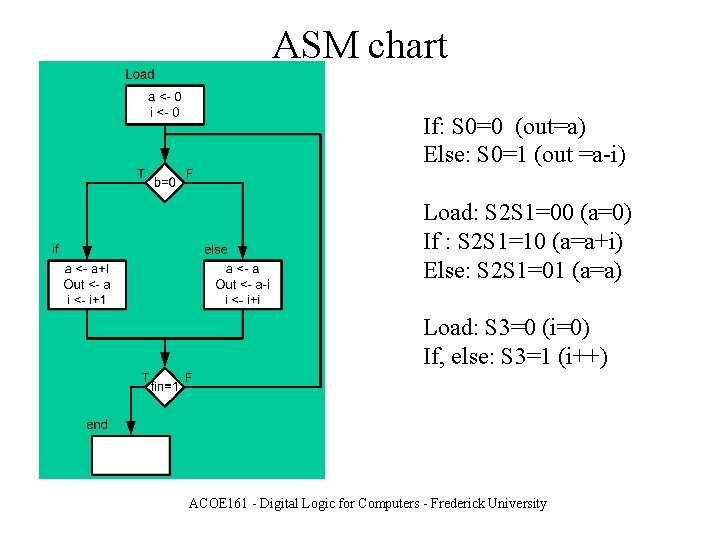

Example • Design a circuit that implements the following pseudocode: a=0; for (i=0; i<5; i++) if b=0 then //boolean a = a+i; out = a; else out = a-i; ACOE 161 - Digital Logic for Computers - Frederick University

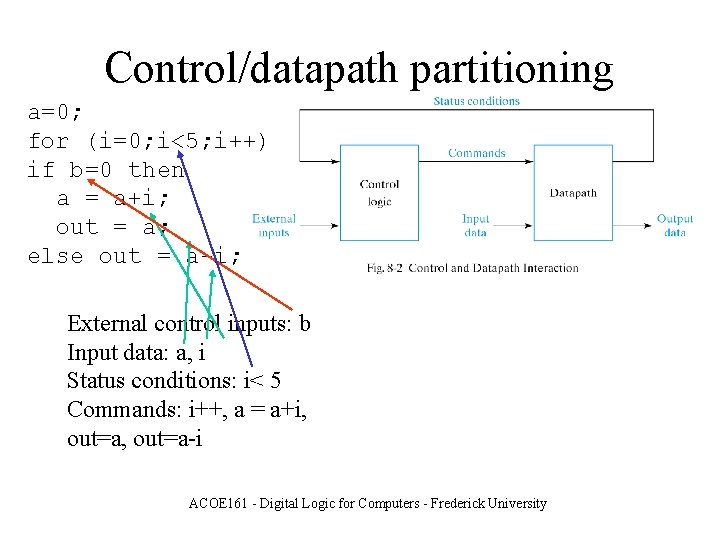

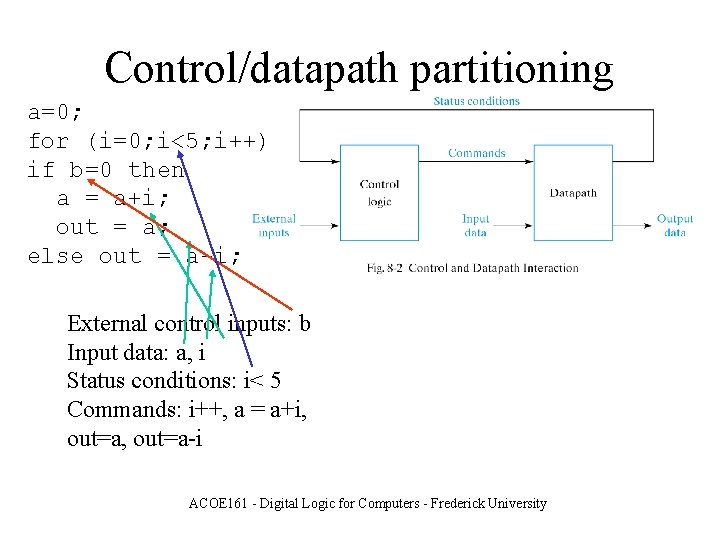

Control/datapath partitioning a=0; for (i=0; i<5; i++) if b=0 then a = a+i; out = a; else out = a-i; External control inputs: b Input data: a, i Status conditions: i< 5 Commands: i++, a = a+i, out=a, out=a-i ACOE 161 - Digital Logic for Computers - Frederick University

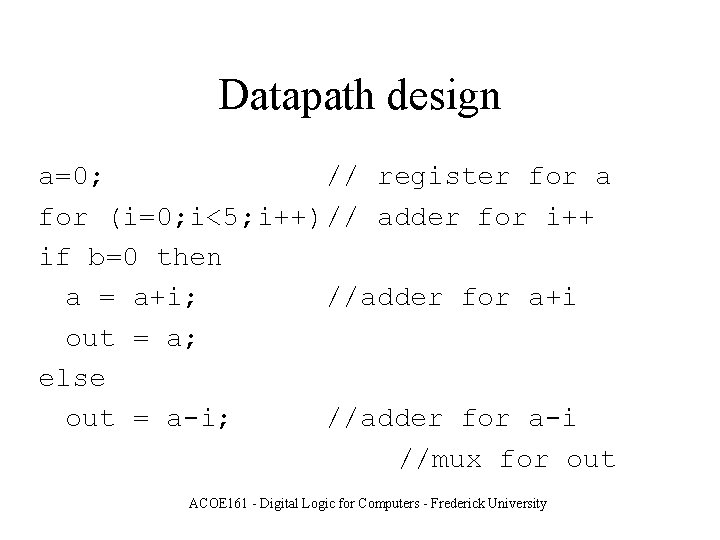

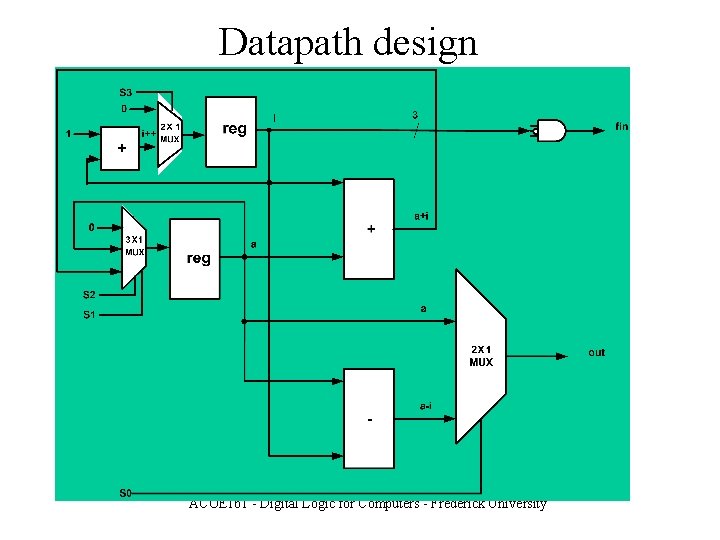

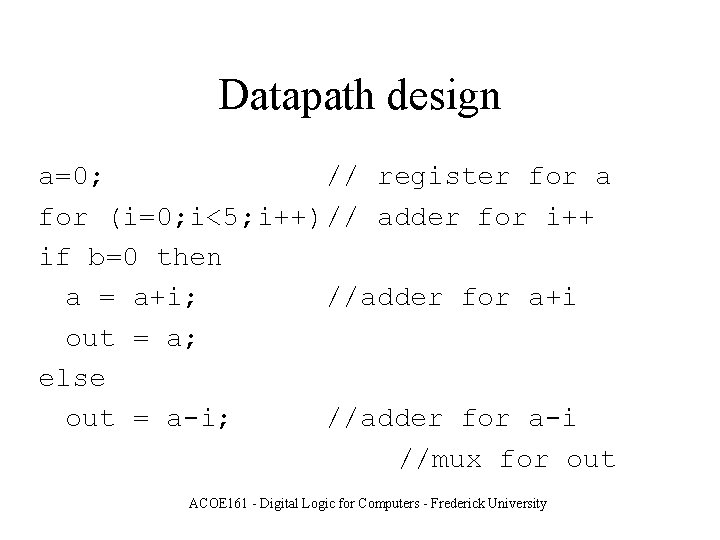

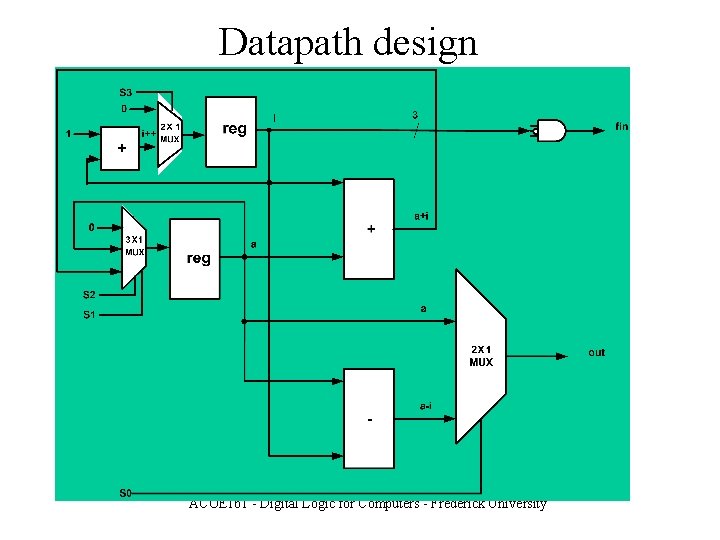

Datapath design a=0; // register for a for (i=0; i<5; i++)// adder for i++ if b=0 then a = a+i; //adder for a+i out = a; else out = a-i; //adder for a-i //mux for out ACOE 161 - Digital Logic for Computers - Frederick University

Datapath design ACOE 161 - Digital Logic for Computers - Frederick University

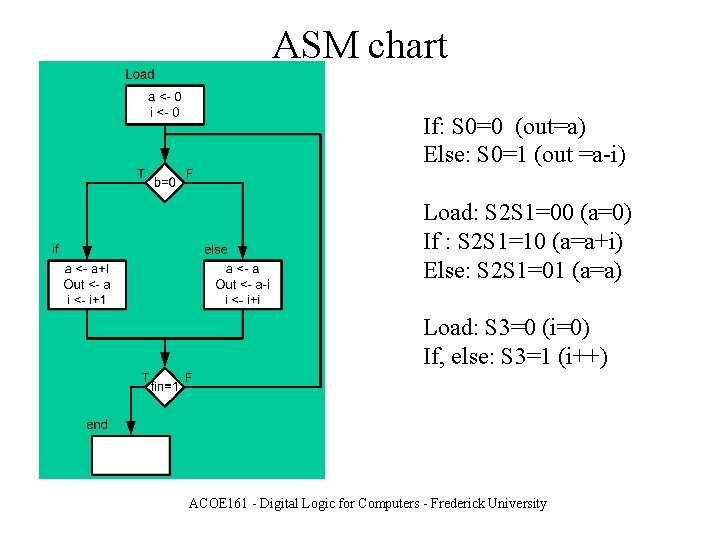

ASM chart If: S 0=0 (out=a) Else: S 0=1 (out =a-i) Load: S 2 S 1=00 (a=0) If : S 2 S 1=10 (a=a+i) Else: S 2 S 1=01 (a=a) Load: S 3=0 (i=0) If, else: S 3=1 (i++) ACOE 161 - Digital Logic for Computers - Frederick University

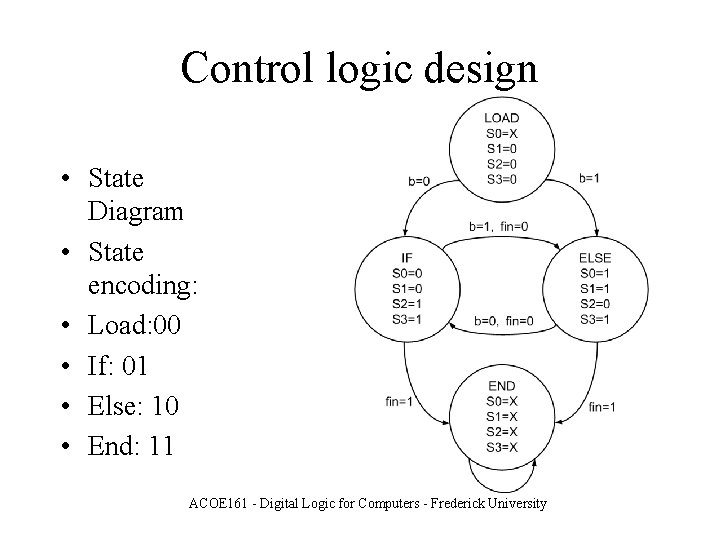

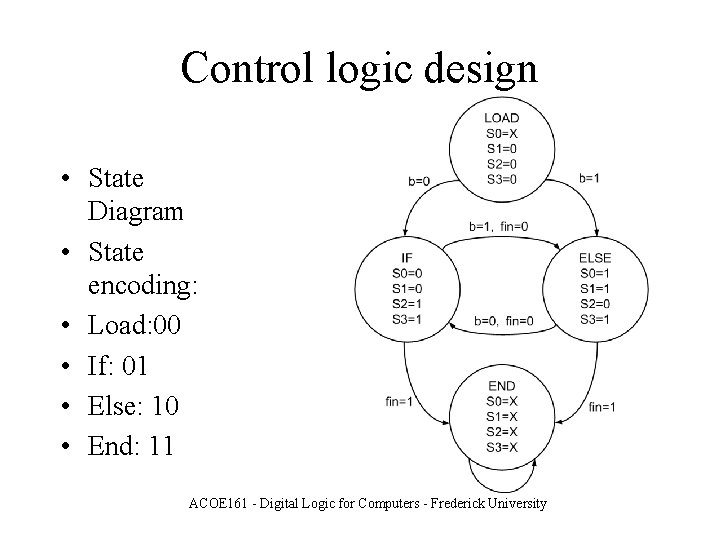

Control logic design • State Diagram • State encoding: • Load: 00 • If: 01 • Else: 10 • End: 11 ACOE 161 - Digital Logic for Computers - Frederick University

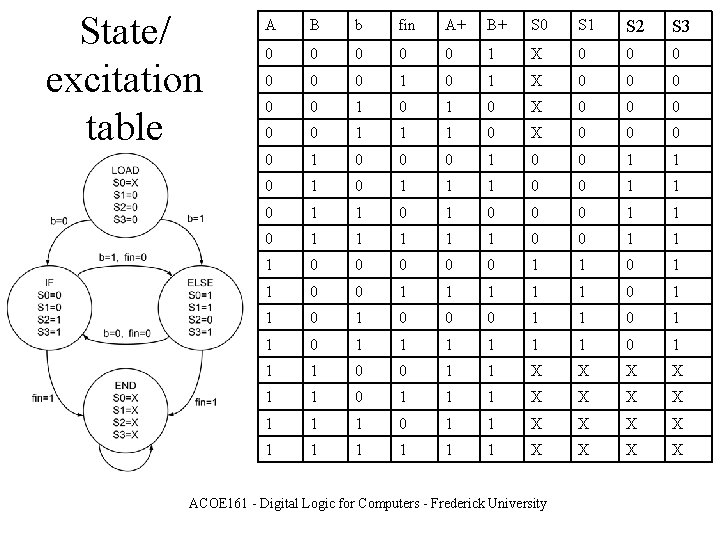

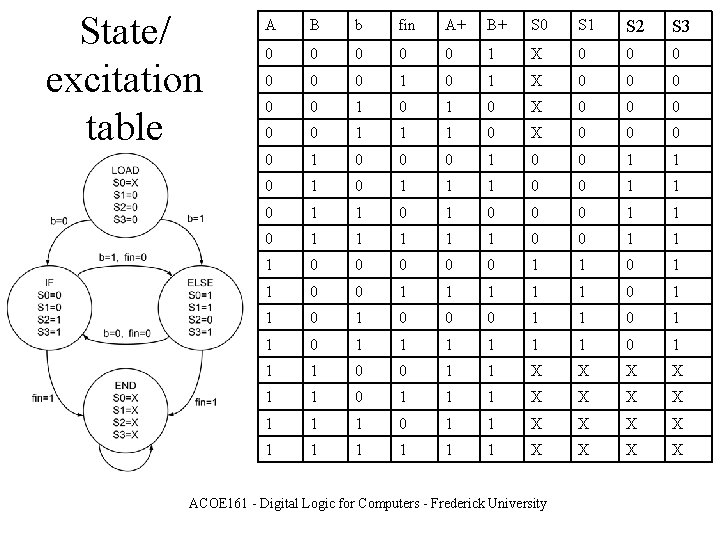

State/ excitation table A B b fin A+ B+ S 0 S 1 S 2 S 3 0 0 0 1 X 0 0 0 1 0 X 0 0 0 1 1 1 0 X 0 0 1 0 0 0 1 1 1 0 0 1 1 0 1 0 0 0 1 1 1 1 1 0 0 0 0 0 1 1 1 0 1 0 0 0 1 1 1 0 1 1 1 0 0 1 1 X X 1 1 0 1 1 1 X X 1 1 1 0 1 1 X X 1 1 1 X X ACOE 161 - Digital Logic for Computers - Frederick University

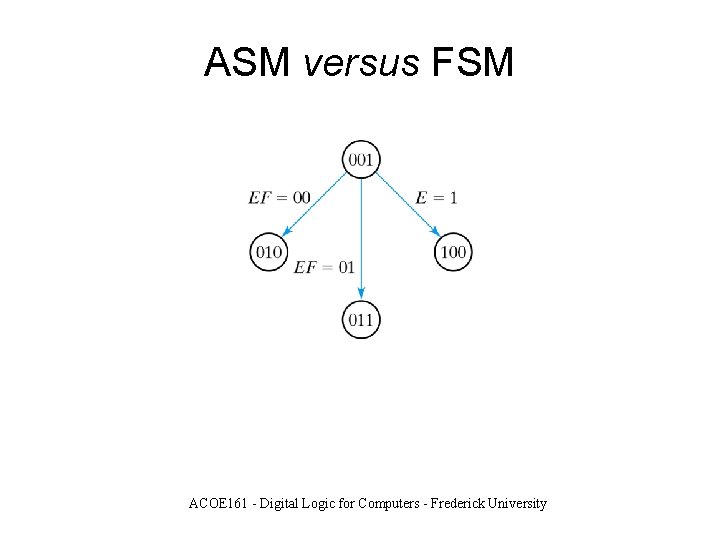

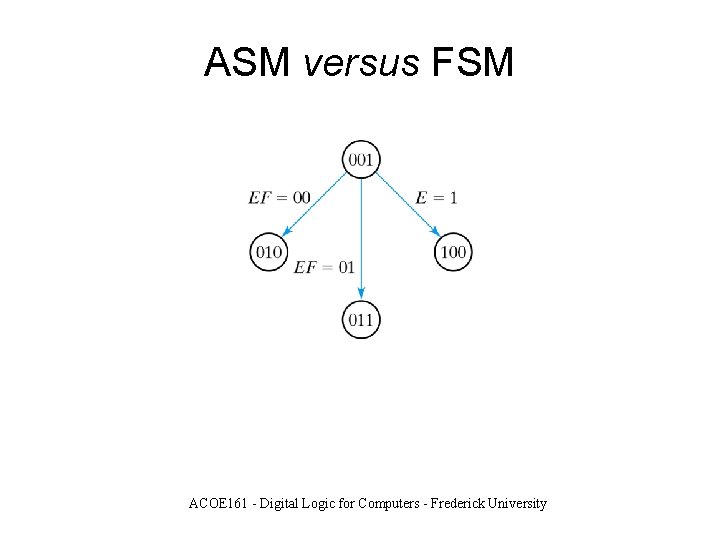

ASM versus FSM ACOE 161 - Digital Logic for Computers - Frederick University

Timing of Transition Between States During single clock cycle • Reg A incremented Condition E evaluated • If E=1 then R <-0 • Control transferred to state T 2, T 3 or T 4 • Control path and datapath work simultaneously ACOE 161 - Digital Logic for Computers - Frederick University

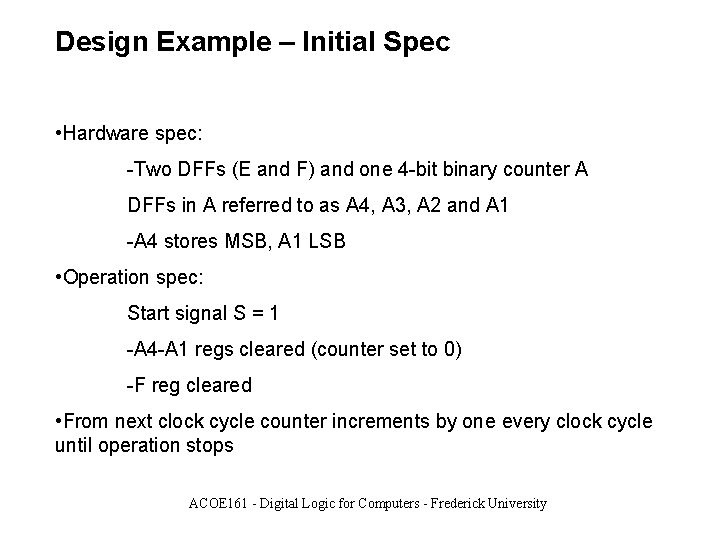

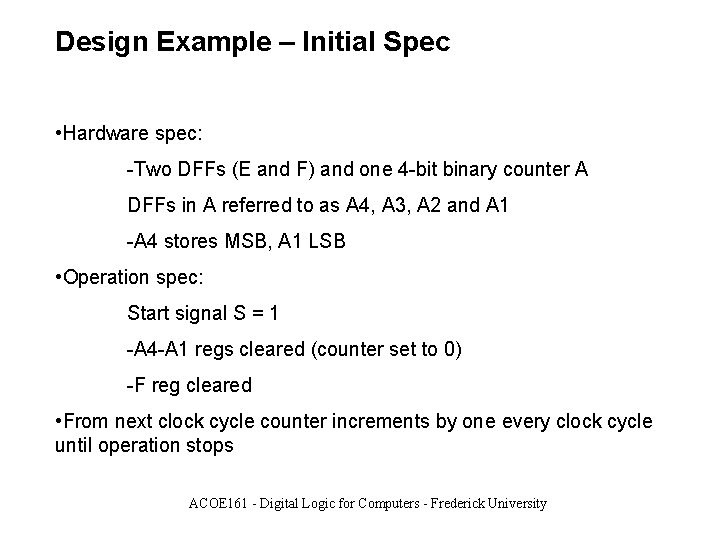

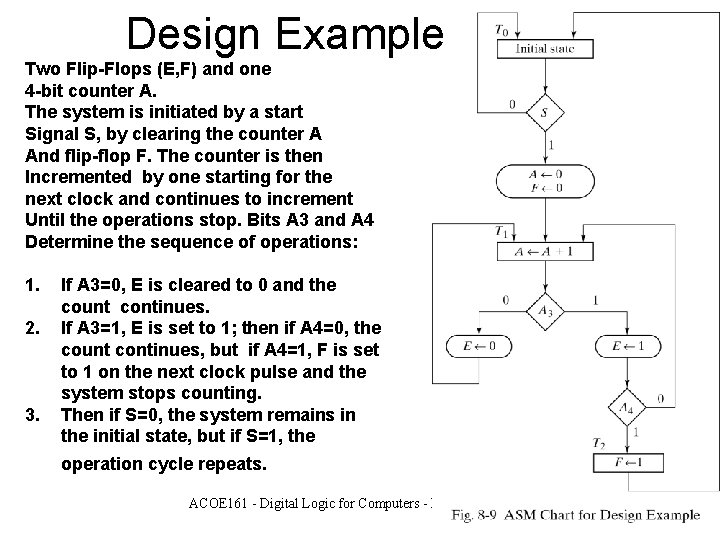

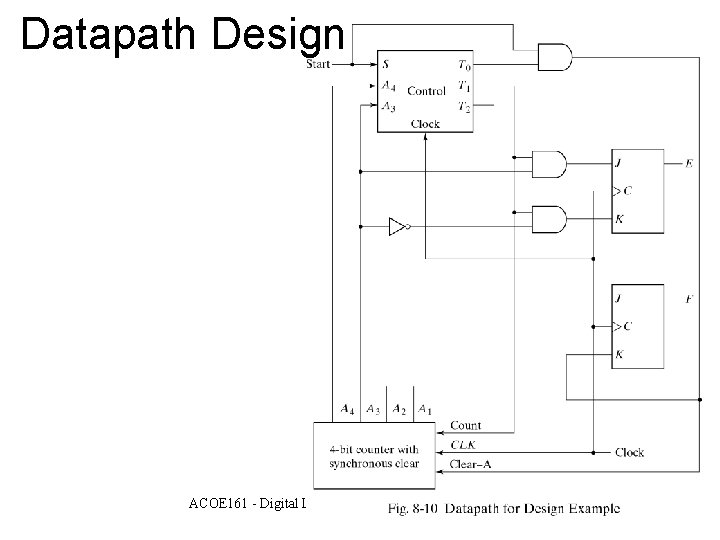

Design Example – Initial Spec • Hardware spec: -Two DFFs (E and F) and one 4 -bit binary counter A DFFs in A referred to as A 4, A 3, A 2 and A 1 -A 4 stores MSB, A 1 LSB • Operation spec: Start signal S = 1 -A 4 -A 1 regs cleared (counter set to 0) -F reg cleared • From next clock cycle counter increments by one every clock cycle until operation stops ACOE 161 - Digital Logic for Computers - Frederick University

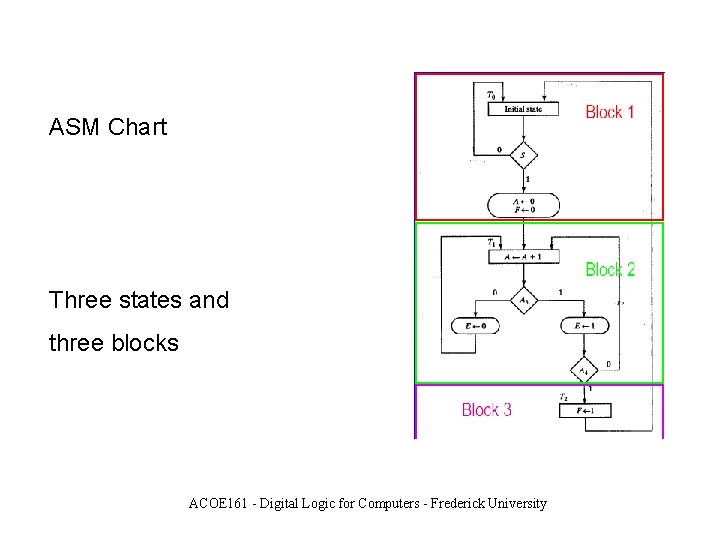

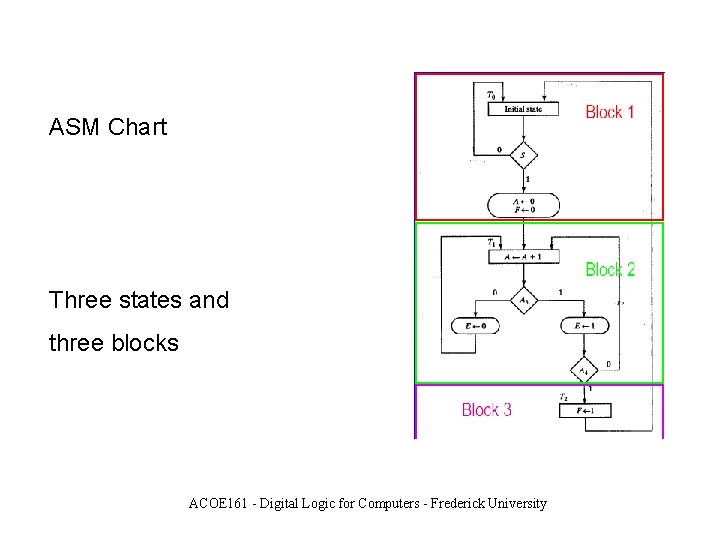

ASM Chart Three states and three blocks ACOE 161 - Digital Logic for Computers - Frederick University

Timing Sequence • Operation in each ASM block executed in one clock cycle -Operations in state and conditional boxes executed by datapath -Changes from one state to other performed in by control path ACOE 161 - Digital Logic for Computers - Frederick University

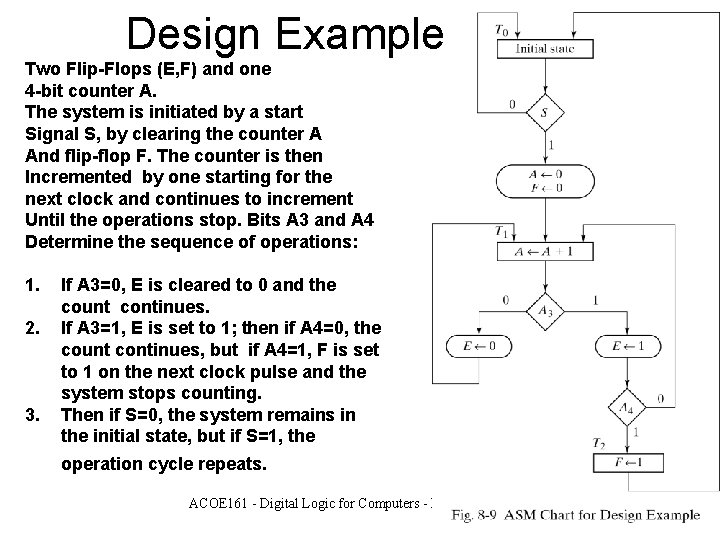

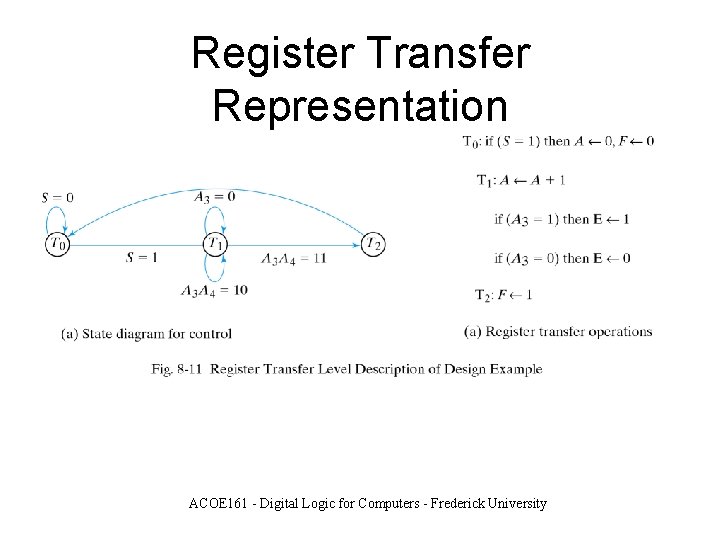

Design Example Two Flip-Flops (E, F) and one 4 -bit counter A. The system is initiated by a start Signal S, by clearing the counter A And flip-flop F. The counter is then Incremented by one starting for the next clock and continues to increment Until the operations stop. Bits A 3 and A 4 Determine the sequence of operations: 1. 2. 3. If A 3=0, E is cleared to 0 and the count continues. If A 3=1, E is set to 1; then if A 4=0, the count continues, but if A 4=1, F is set to 1 on the next clock pulse and the system stops counting. Then if S=0, the system remains in the initial state, but if S=1, the operation cycle repeats. ACOE 161 - Digital Logic for Computers - Frederick University

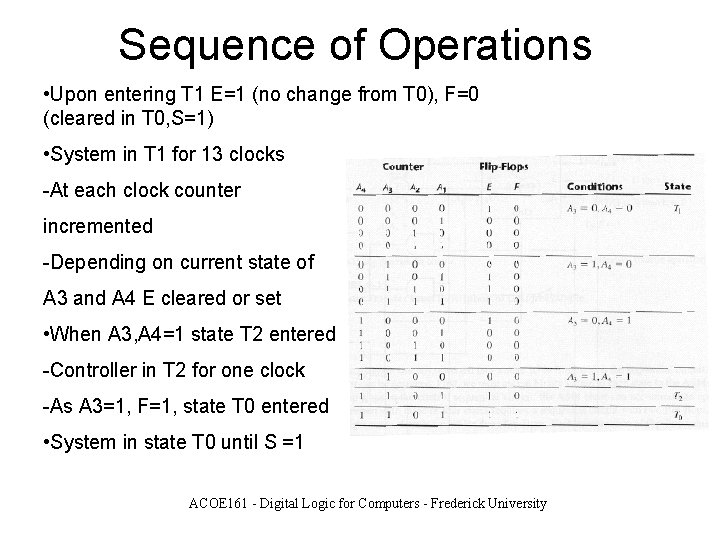

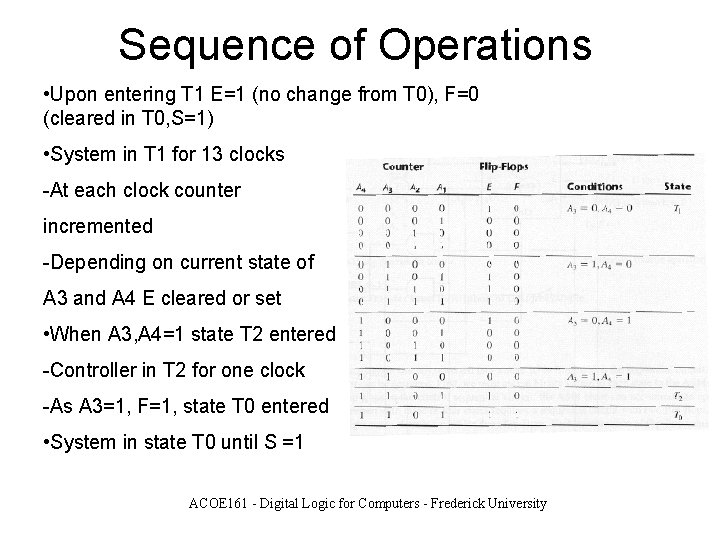

Sequence of Operations • Upon entering T 1 E=1 (no change from T 0), F=0 (cleared in T 0, S=1) • System in T 1 for 13 clocks -At each clock counter incremented -Depending on current state of A 3 and A 4 E cleared or set • When A 3, A 4=1 state T 2 entered -Controller in T 2 for one clock -As A 3=1, F=1, state T 0 entered • System in state T 0 until S =1 ACOE 161 - Digital Logic for Computers - Frederick University

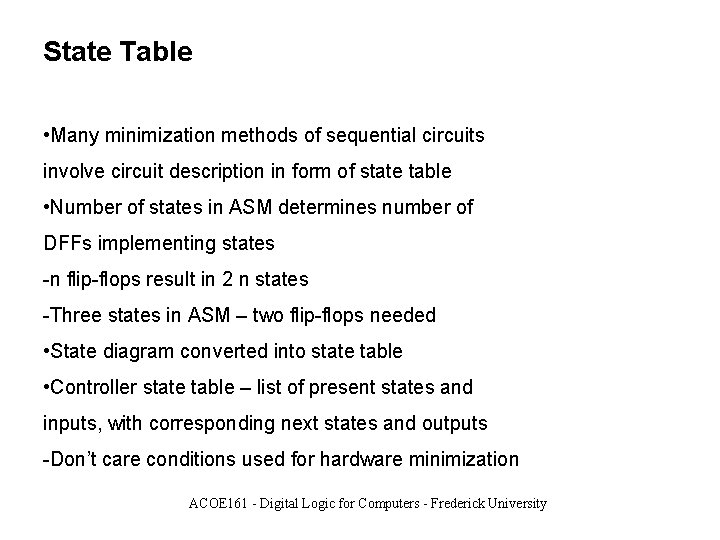

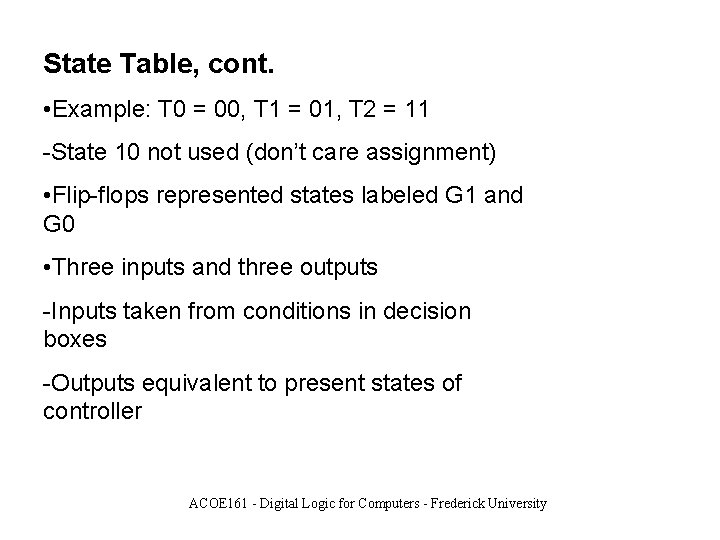

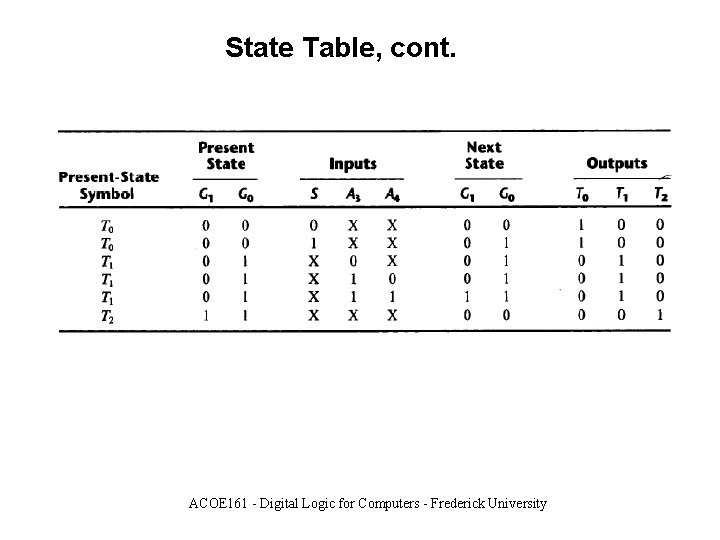

State Table • Many minimization methods of sequential circuits involve circuit description in form of state table • Number of states in ASM determines number of DFFs implementing states -n flip-flops result in 2 n states -Three states in ASM – two flip-flops needed • State diagram converted into state table • Controller state table – list of present states and inputs, with corresponding next states and outputs -Don’t care conditions used for hardware minimization ACOE 161 - Digital Logic for Computers - Frederick University

State Table, cont. • Example: T 0 = 00, T 1 = 01, T 2 = 11 -State 10 not used (don’t care assignment) • Flip-flops represented states labeled G 1 and G 0 • Three inputs and three outputs -Inputs taken from conditions in decision boxes -Outputs equivalent to present states of controller ACOE 161 - Digital Logic for Computers - Frederick University

State Table, cont. ACOE 161 - Digital Logic for Computers - Frederick University

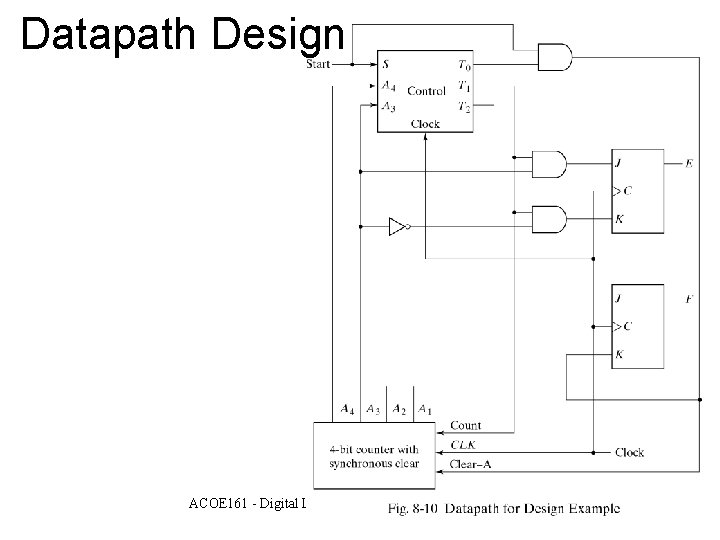

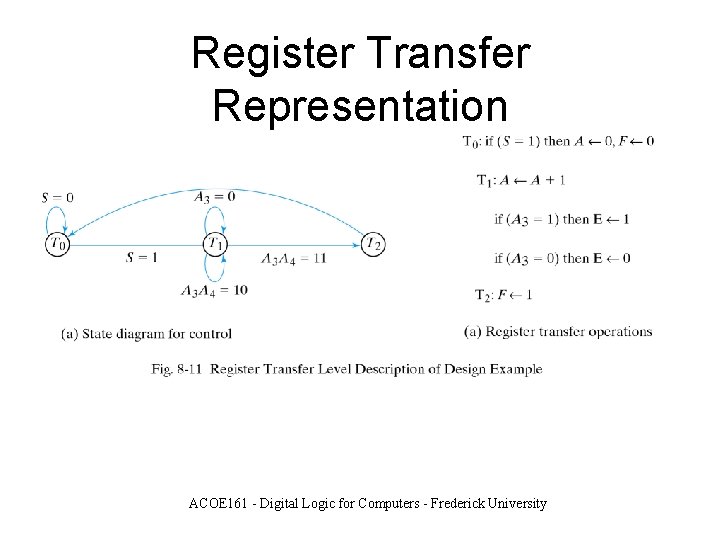

Datapath Design ACOE 161 - Digital Logic for Computers - Frederick University

Register Transfer Representation ACOE 161 - Digital Logic for Computers - Frederick University