Memoria Cach Estructura y Tecnolologa de Ordenadores Tema

- Slides: 48

Memoria Caché Estructura y Tecnolología de Ordenadores

Tema 3: Jerarquía de Memoria: Memoria Caché y Memoria Virtual Definición de memoria caché n Estrategias de Mapeado: Directo, Asociativo y Asociativo por conjunto n Algoritmos de reemplazamiento: FIFO, LRU, Aleatorio n Coherencia del caché. n Estructura y Tecnología de Ordenadores ETSII- ULL 2004

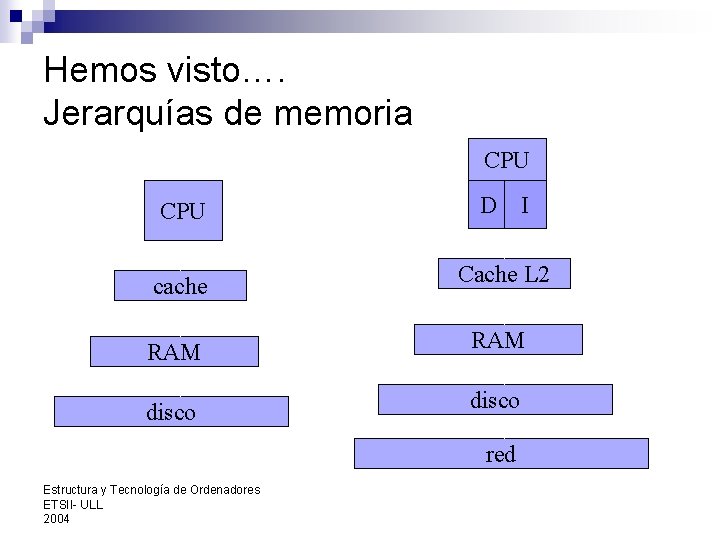

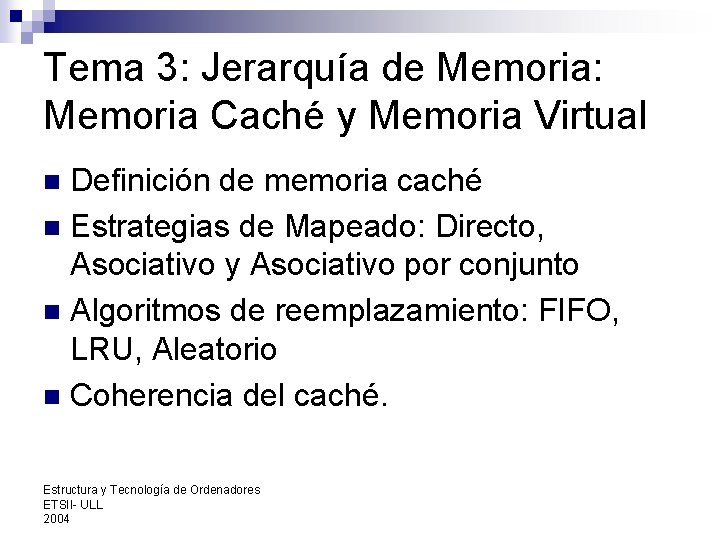

Hemos visto…. Jerarquías de memoria CPU D I cache Cache L 2 RAM disco red Estructura y Tecnología de Ordenadores ETSII- ULL 2004

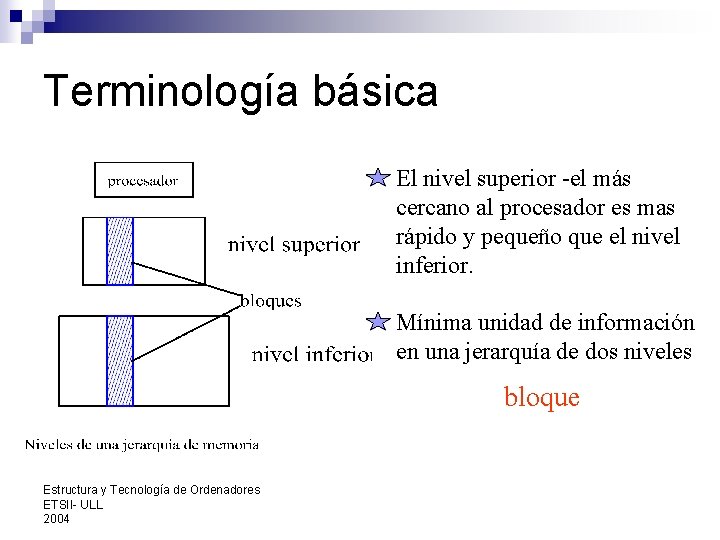

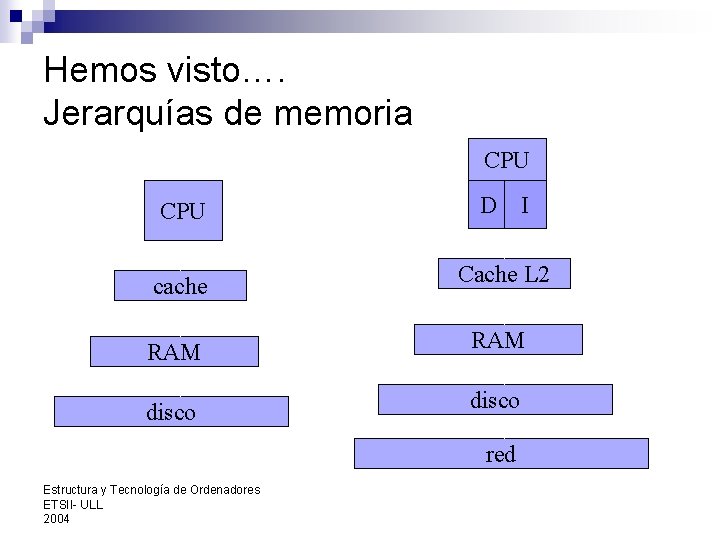

Terminología básica El nivel superior -el más cercano al procesador es mas rápido y pequeño que el nivel inferior. Mínima unidad de información en una jerarquía de dos niveles bloque Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Estructura y Tecnología de Ordenadores ETSII- ULL 2004

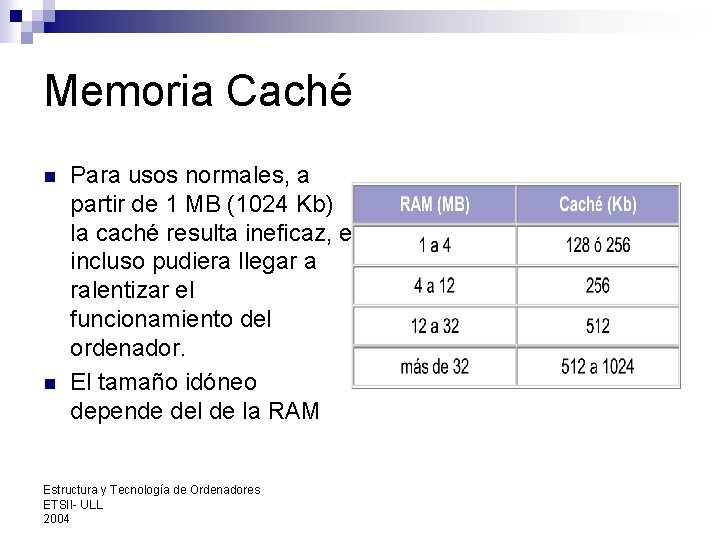

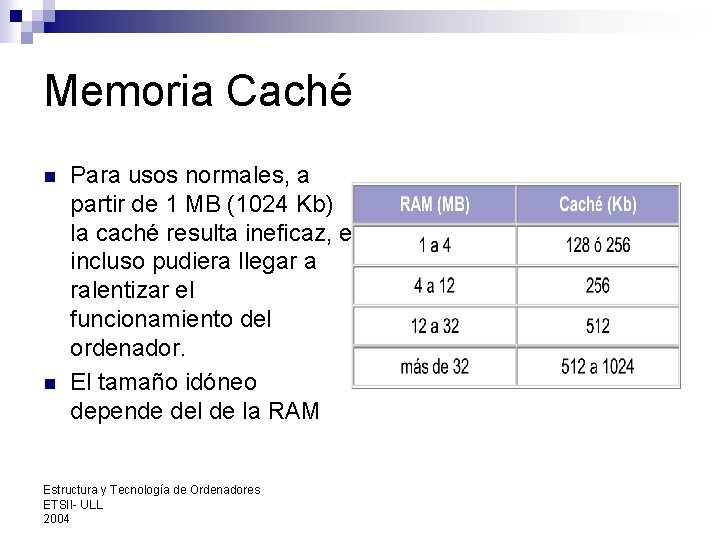

Memoria Caché n n Para usos normales, a partir de 1 MB (1024 Kb) la caché resulta ineficaz, e incluso pudiera llegar a ralentizar el funcionamiento del ordenador. El tamaño idóneo depende del de la RAM Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Ejemplo: n n n Pentium II/III tienen 32 Kb de caché interna, y 512 Kb de caché externa al encapsulado del microchip (L 2, en este caso de dos chips). Funciona a una frecuencia que es la mitad de la del micro (es decir, a 133, 150 MHz o más), mientras que la caché externa clásica funciona a la de la placa base (de 50 a 66 MHz en los Pentium y 100 MHz en los AMD K 6 -2). Estructura y Tecnología de Ordenadores ETSII- ULL 2004

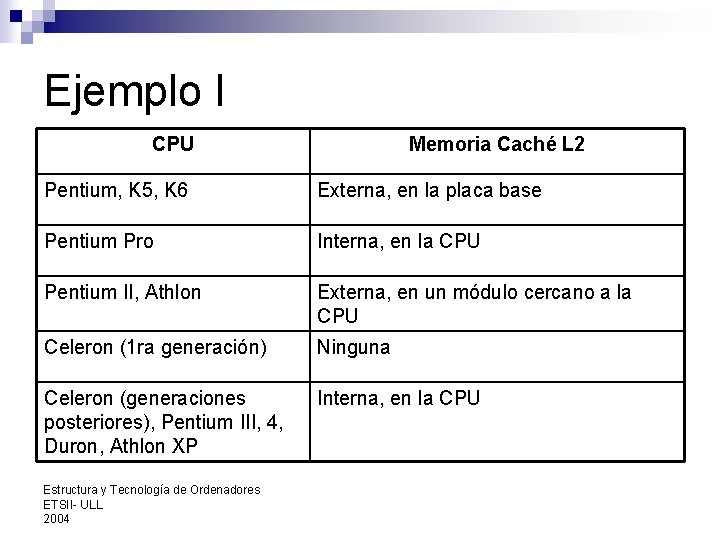

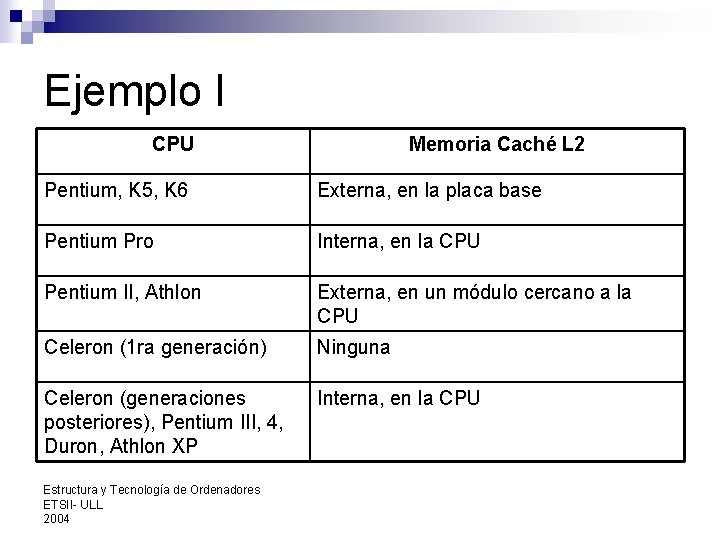

Ejemplo I CPU Memoria Caché L 2 Pentium, K 5, K 6 Externa, en la placa base Pentium Pro Interna, en la CPU Pentium II, Athlon Externa, en un módulo cercano a la CPU Celeron (1 ra generación) Ninguna Celeron (generaciones posteriores), Pentium III, 4, Duron, Athlon XP Interna, en la CPU Estructura y Tecnología de Ordenadores ETSII- ULL 2004

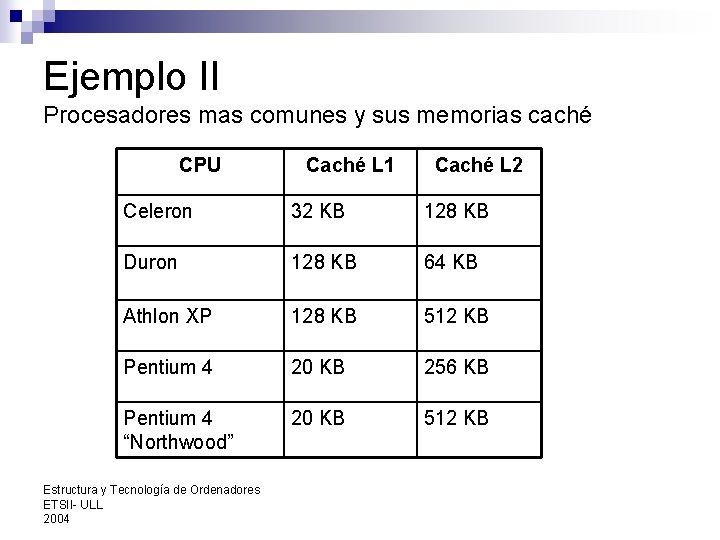

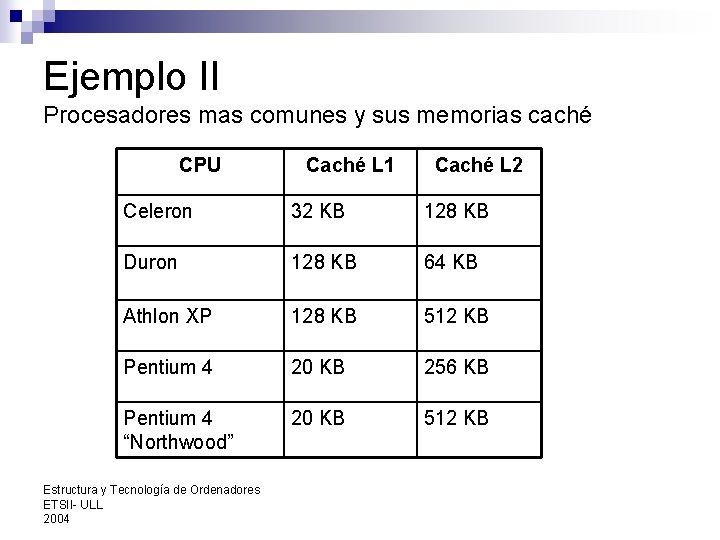

Ejemplo II Procesadores mas comunes y sus memorias caché CPU Caché L 1 Caché L 2 Celeron 32 KB 128 KB Duron 128 KB 64 KB Athlon XP 128 KB 512 KB Pentium 4 20 KB 256 KB Pentium 4 “Northwood” 20 KB 512 KB Estructura y Tecnología de Ordenadores ETSII- ULL 2004

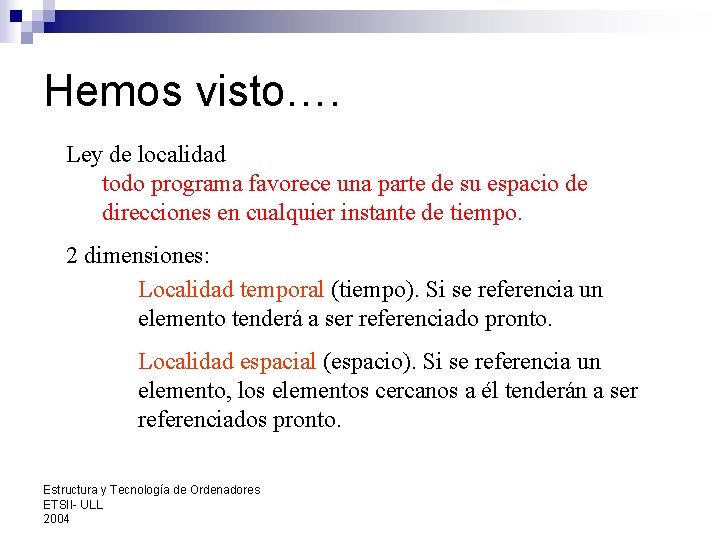

Hemos visto…. Ley de localidad todo programa favorece una parte de su espacio de direcciones en cualquier instante de tiempo. 2 dimensiones: Localidad temporal (tiempo). Si se referencia un elemento tenderá a ser referenciado pronto. Localidad espacial (espacio). Si se referencia un elemento, los elementos cercanos a él tenderán a ser referenciados pronto. Estructura y Tecnología de Ordenadores ETSII- ULL 2004

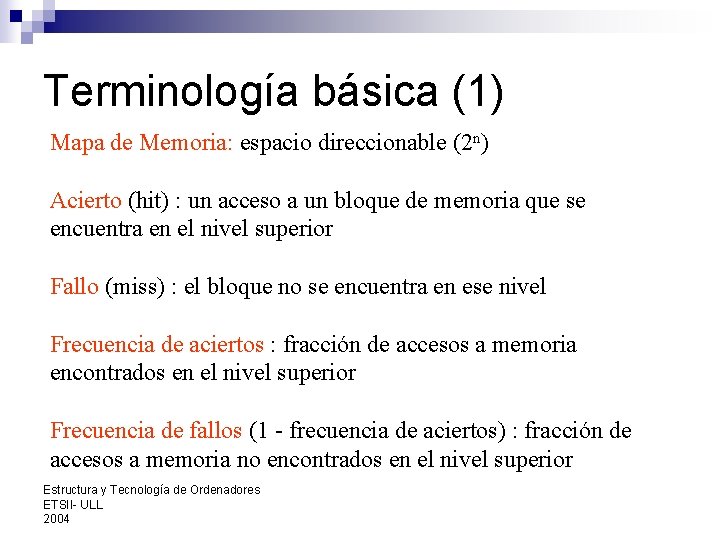

Terminología básica (1) Mapa de Memoria: espacio direccionable (2 n) Acierto (hit) : un acceso a un bloque de memoria que se encuentra en el nivel superior Fallo (miss) : el bloque no se encuentra en ese nivel Frecuencia de aciertos : fracción de accesos a memoria encontrados en el nivel superior Frecuencia de fallos (1 - frecuencia de aciertos) : fracción de accesos a memoria no encontrados en el nivel superior Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Terminología básica (2) Tiempo de acierto : tiempo necesario para acceder a un dato presente en el nivel superior de la jerarquía incluye el tiempo necesario para saber si el acceso es un acierto o un fallo Penalización de fallo : tiempo necesario para sustituir un bloque de nivel superior por el correspondiente bloque de nivel más bajo, más el tiempo necesario para proporcionar este bloque al dispositivo que lo solicito (generalmente la CPU). Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Penalización de fallo. . . 2 componentes: tiempo de acceso : tiempo necesario para acceder a la primera palabra de un bloque en un fallo relacionado con la latencia del nivel más bajo tiempo de transferencia : tiempo para transferir las restantes palabras del bloque relacionado con el ancho de banda entre las memoria de nivel más bajo y más alto. Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Cómo se pasan las direcciones entre la jerarquía de memorias? Ubicación del bloque Dónde puede ubicarse un bloque en el nivel superior? Identificación del bloque Cómo se encuentra un bloque en el nivel superior? Sustitución de bloque Qué bloque debe reemplazarse en caso de fallo? Estrategia de escritura Qué ocurre en una escritura? Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Entonces el diseño de la memoria caché ha de resolver los siguientes problemas: n n n MIGRACIÓN: ¿Qué objetos migran de la memoria principal a la cache? IDENTIFICACIÓN: ¿Cómo se busca una palabra en la cache? UBICACIÓN: ¿En que marco de línea se puede almacenar cada línea? EXTRACCIÓN: ¿Qué líneas se copian a la cache y cuándo? REEMPLAZO: ¿Qué información debe desalojarse para almacenar una nueva línea producto de un fallo? ESCRITURA: ¿Cómo se tratan las escrituras? Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Migración n n n La política que cumplen todas las caches es la de migrar bloques de información de tamaño fijo que se denominan “líneas”. Por ello se considera dividida la memoria principal en líneas y la cache en marcos de línea. Las líneas suelen tener un tamaño de 2 v palabras. La dirección de la línea se obtiene eliminando los v bits menos significativos de la dirección de la palabra. Valores típicos de v=1, 2, 3 o 4 Esto da líneas de 2, 4, 8 o 16 palabras. Estructura y Tecnología de Ordenadores ETSII- ULL 2004

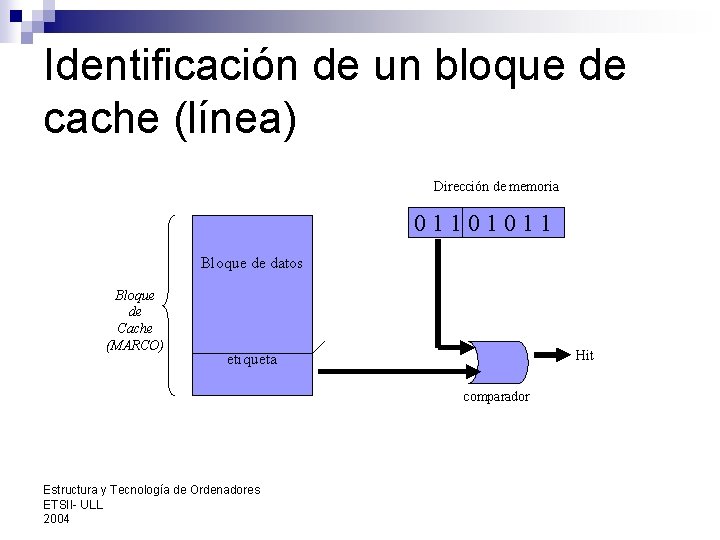

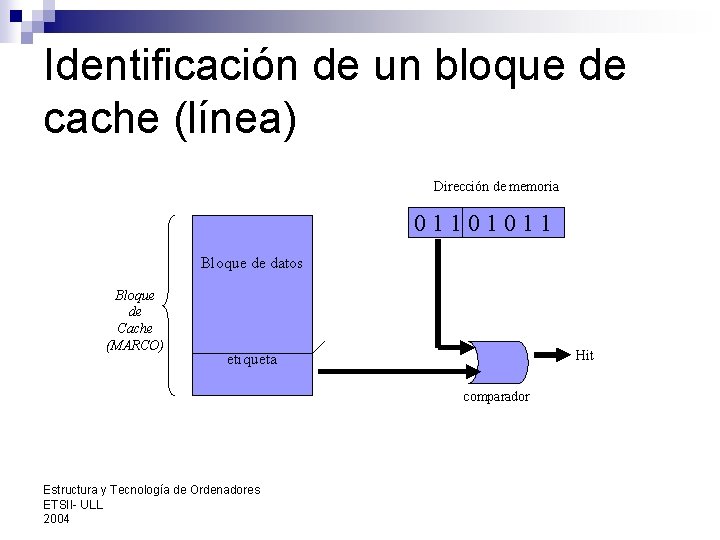

Identificación de un bloque de cache (línea) Dirección de memoria 01101011 Bloque de datos Bloque de Cache (MARCO) Hit etiqueta comparador Estructura y Tecnología de Ordenadores ETSII- ULL 2004

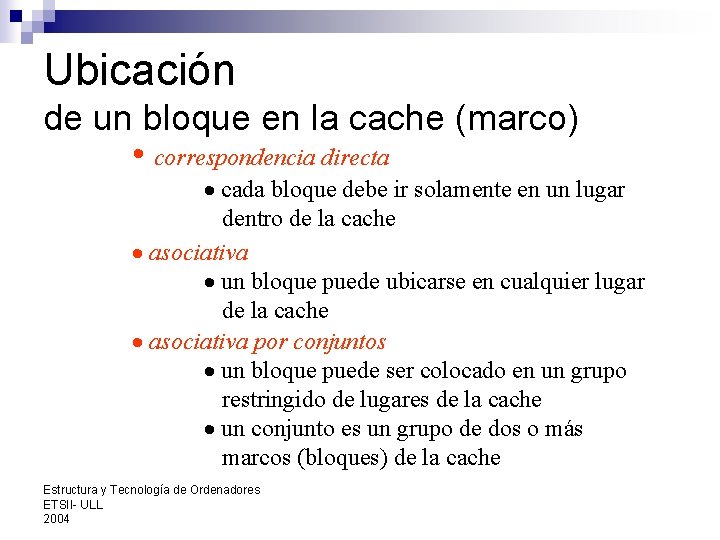

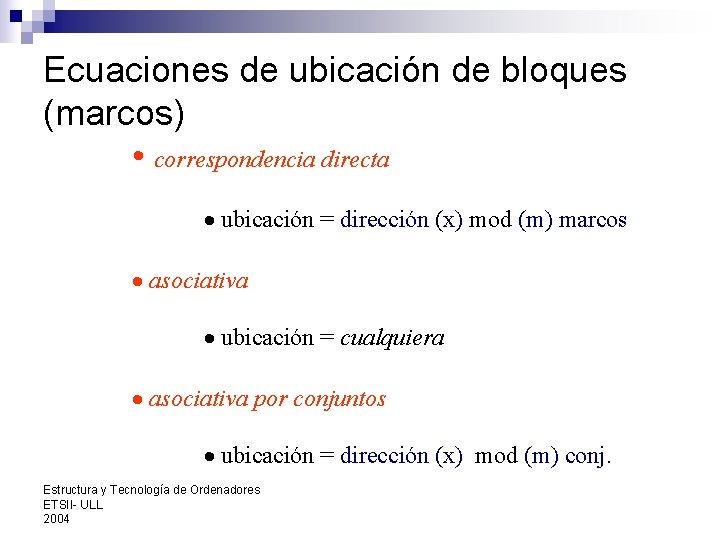

Ubicación de un bloque en la cache (marco) • correspondencia directa · cada bloque debe ir solamente en un lugar dentro de la cache · asociativa · un bloque puede ubicarse en cualquier lugar de la cache · asociativa por conjuntos · un bloque puede ser colocado en un grupo restringido de lugares de la cache · un conjunto es un grupo de dos o más marcos (bloques) de la cache Estructura y Tecnología de Ordenadores ETSII- ULL 2004

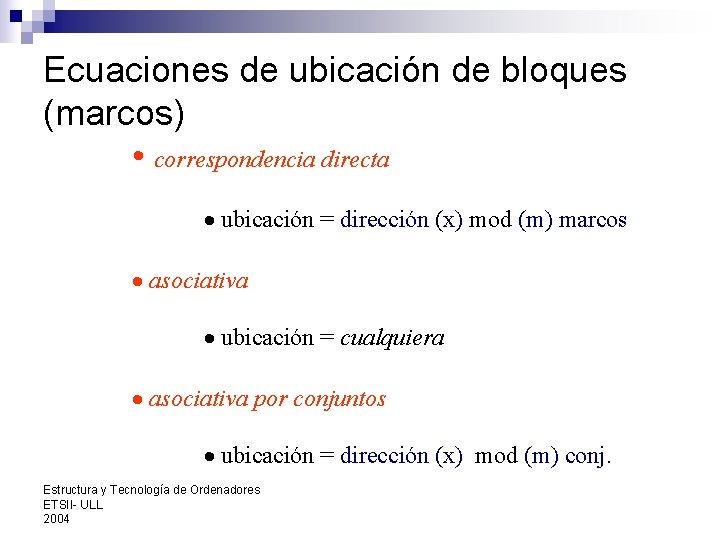

Ecuaciones de ubicación de bloques (marcos) • correspondencia directa · ubicación = dirección (x) mod (m) marcos · asociativa · ubicación = cualquiera · asociativa por conjuntos · ubicación = dirección (x) mod (m) conj. Estructura y Tecnología de Ordenadores ETSII- ULL 2004

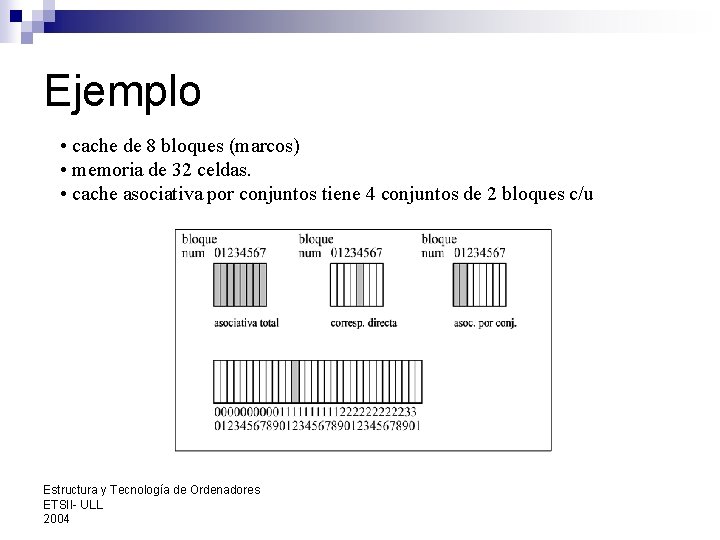

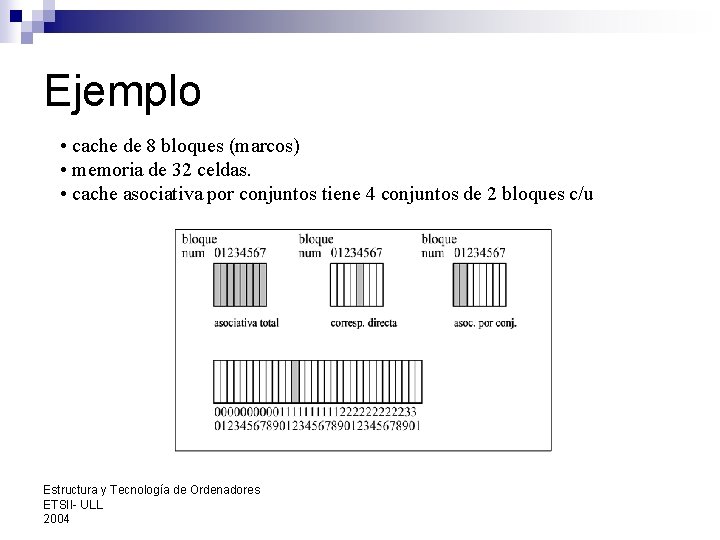

Ejemplo • cache de 8 bloques (marcos) • memoria de 32 celdas. • cache asociativa por conjuntos tiene 4 conjuntos de 2 bloques c/u Estructura y Tecnología de Ordenadores ETSII- ULL 2004

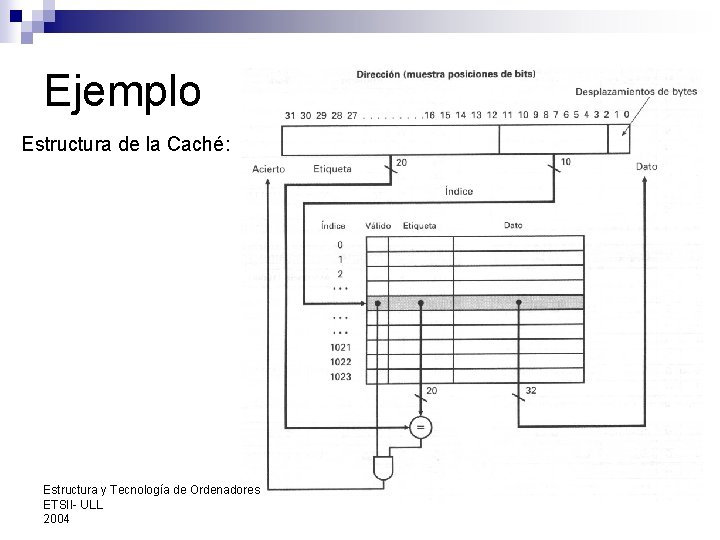

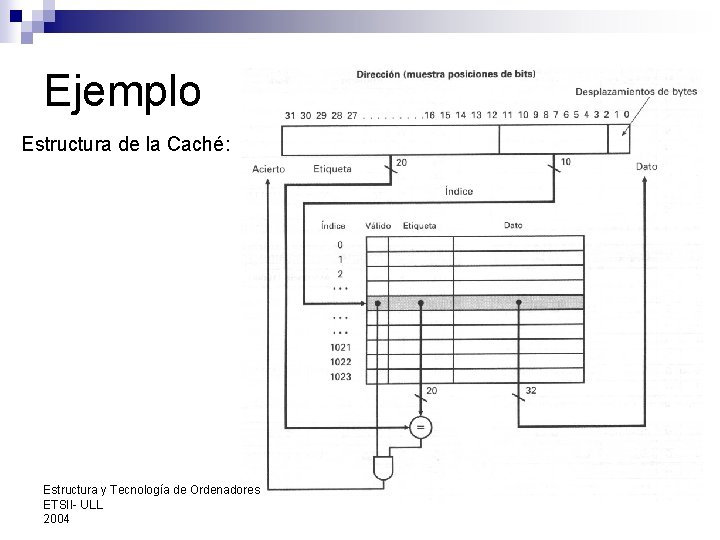

Ejemplo Estructura de la Caché: Estructura y Tecnología de Ordenadores ETSII- ULL 2004

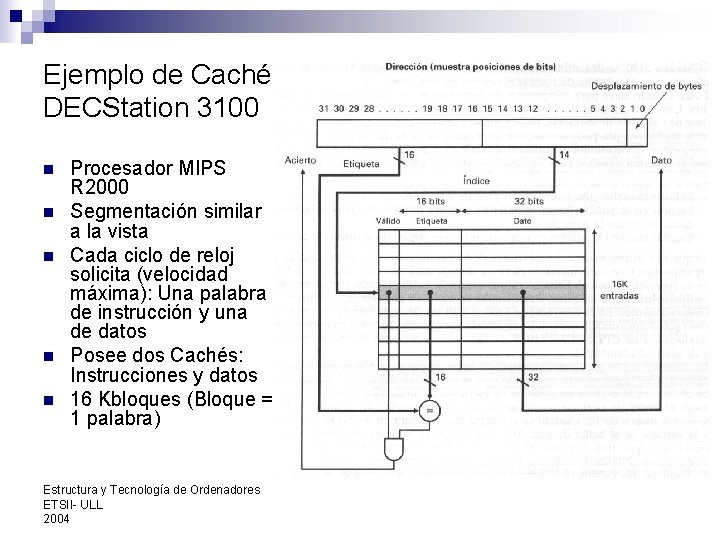

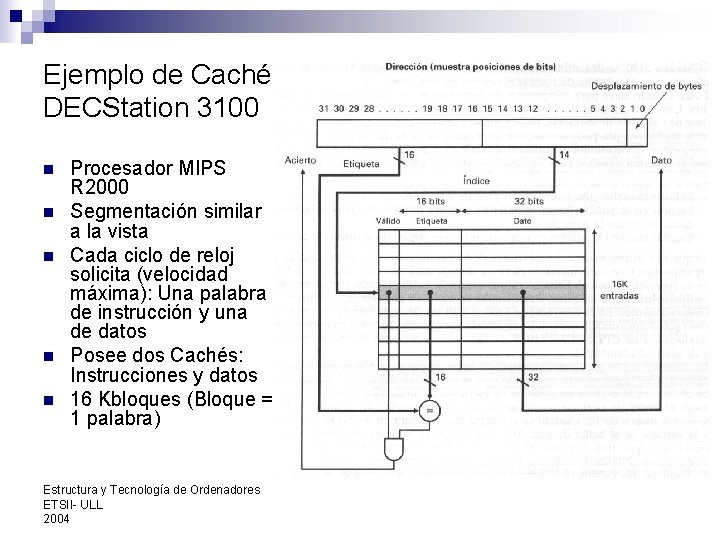

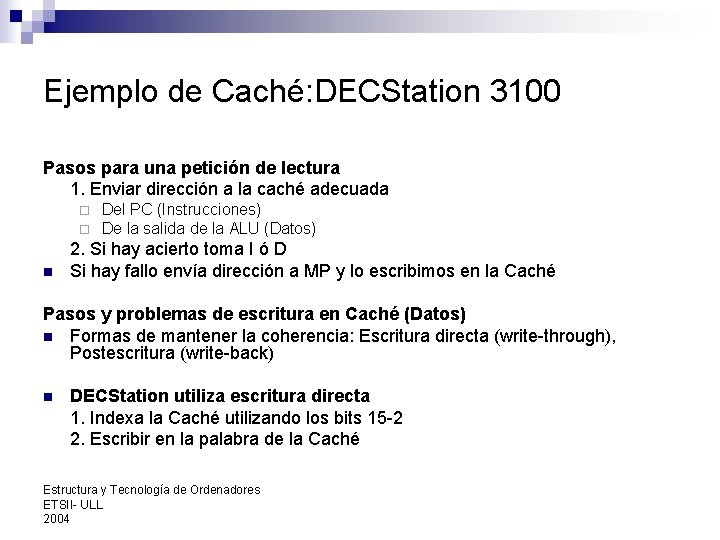

Ejemplo de Caché: DECStation 3100 n n n Procesador MIPS R 2000 Segmentación similar a la vista Cada ciclo de reloj solicita (velocidad máxima): Una palabra de instrucción y una de datos Posee dos Cachés: Instrucciones y datos 16 Kbloques (Bloque = 1 palabra) Estructura y Tecnología de Ordenadores ETSII- ULL 2004

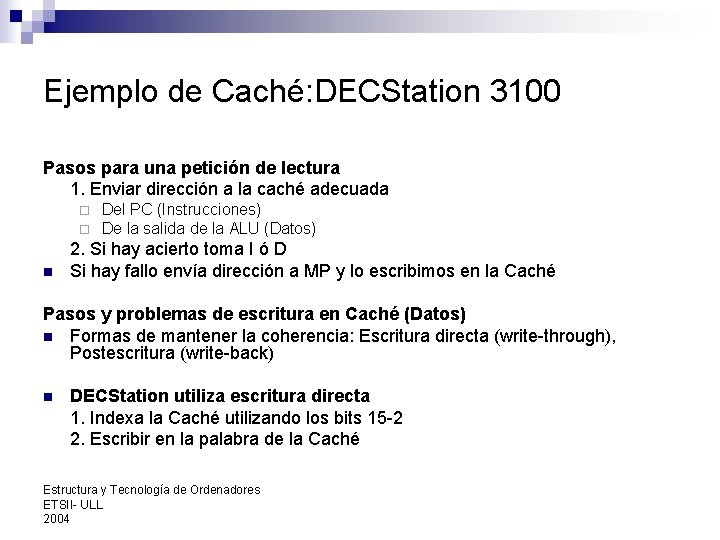

Ejemplo de Caché: DECStation 3100 Pasos para una petición de lectura 1. Enviar dirección a la caché adecuada ¨ ¨ n Del PC (Instrucciones) De la salida de la ALU (Datos) 2. Si hay acierto toma I ó D Si hay fallo envía dirección a MP y lo escribimos en la Caché Pasos y problemas de escritura en Caché (Datos) n Formas de mantener la coherencia: Escritura directa (write-through), Postescritura (write-back) n DECStation utiliza escritura directa 1. Indexa la Caché utilizando los bits 15 -2 2. Escribir en la palabra de la Caché Estructura y Tecnología de Ordenadores ETSII- ULL 2004

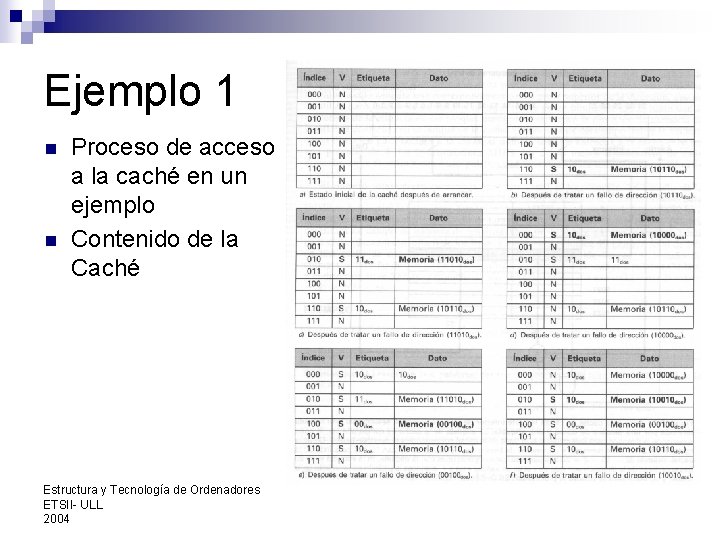

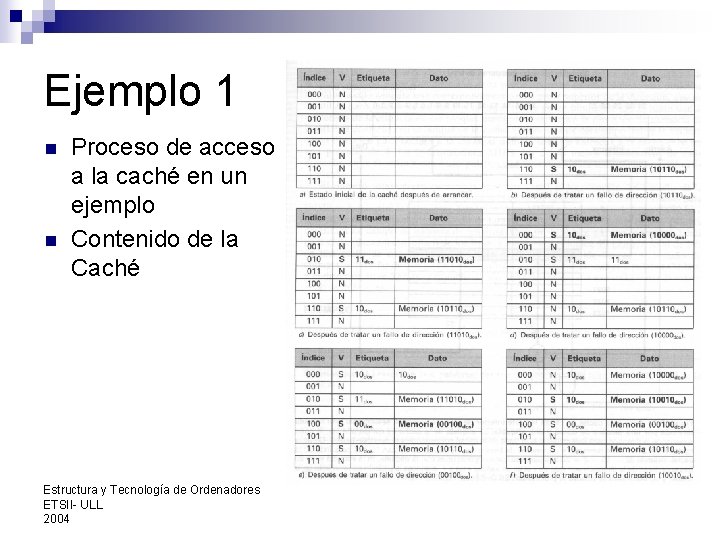

Ejemplo 1 n n Proceso de acceso a la caché en un ejemplo Contenido de la Caché Estructura y Tecnología de Ordenadores ETSII- ULL 2004

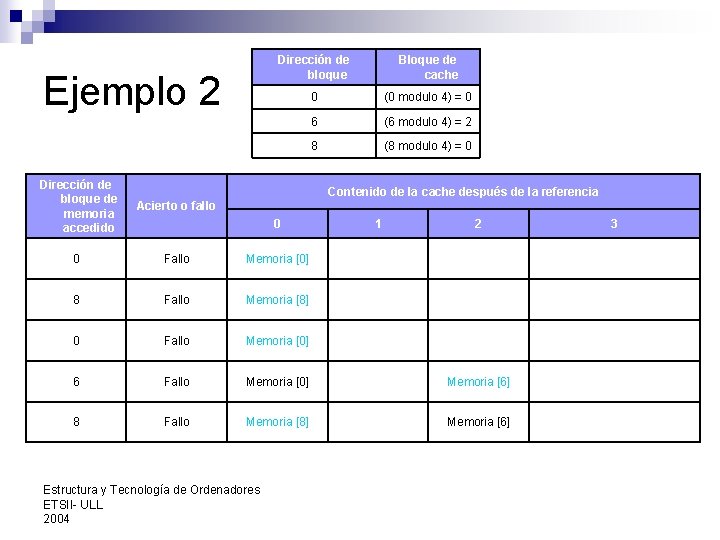

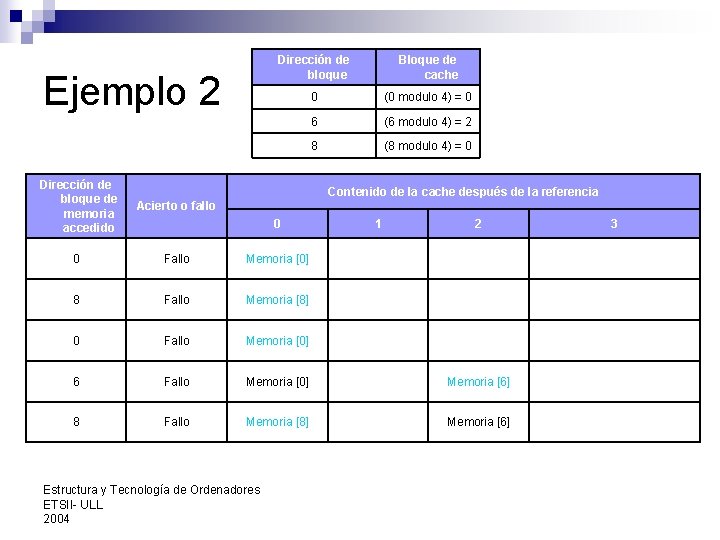

Ejemplo 2 Dirección de bloque Bloque de cache 0 (0 modulo 4) = 0 6 (6 modulo 4) = 2 8 (8 modulo 4) = 0 Dirección de bloque de memoria accedido Acierto o fallo 0 Fallo Memoria [0] 8 Fallo Memoria [8] 0 Fallo Memoria [0] 6 Fallo Memoria [0] Memoria [6] 8 Fallo Memoria [8] Memoria [6] Contenido de la cache después de la referencia 0 Estructura y Tecnología de Ordenadores ETSII- ULL 2004 1 2 3

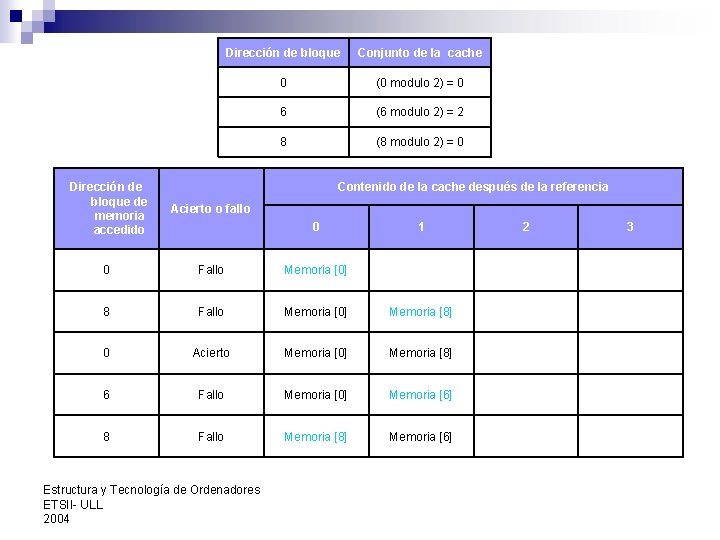

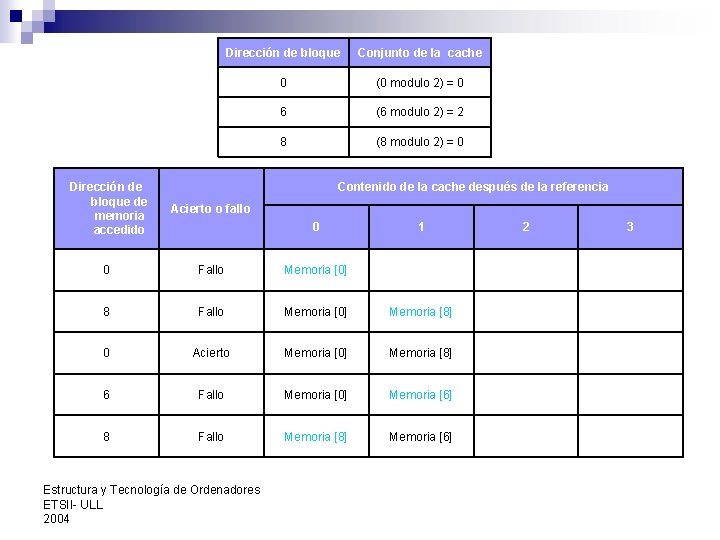

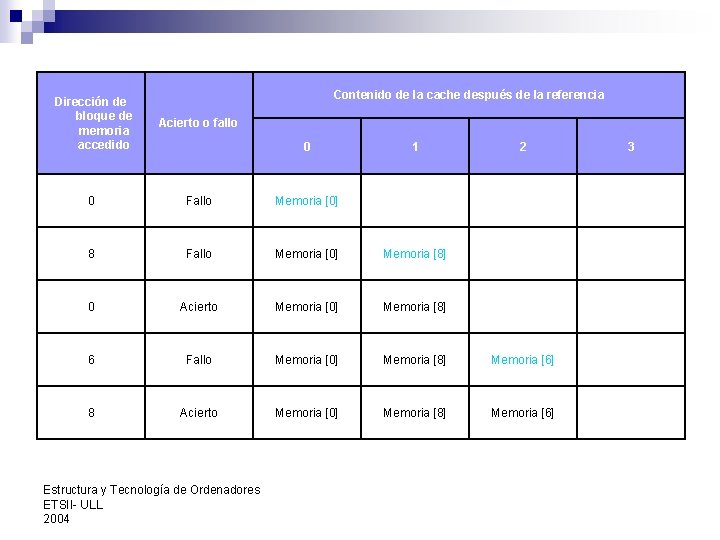

Dirección de bloque Conjunto de la cache 0 (0 modulo 2) = 0 6 (6 modulo 2) = 2 8 (8 modulo 2) = 0 Contenido de la cache después de la referencia Dirección de bloque de memoria accedido Acierto o fallo 0 Fallo Memoria [0] 8 Fallo Memoria [0] Memoria [8] 0 Acierto Memoria [0] Memoria [8] 6 Fallo Memoria [0] Memoria [6] 8 Fallo Memoria [8] Memoria [6] 0 Estructura y Tecnología de Ordenadores ETSII- ULL 2004 1 2 3

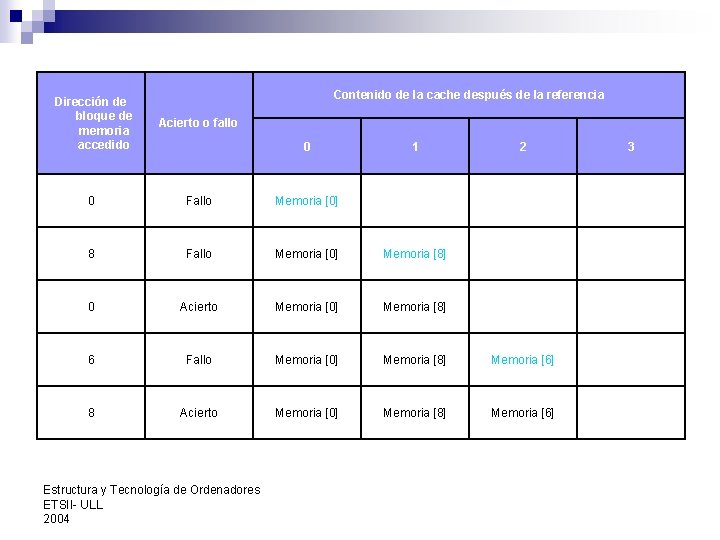

Contenido de la cache después de la referencia Dirección de bloque de memoria accedido Acierto o fallo 0 Fallo Memoria [0] 8 Fallo Memoria [0] Memoria [8] 0 Acierto Memoria [0] Memoria [8] 6 Fallo Memoria [0] Memoria [8] Memoria [6] 8 Acierto Memoria [0] Memoria [8] Memoria [6] 0 Estructura y Tecnología de Ordenadores ETSII- ULL 2004 1 2 3

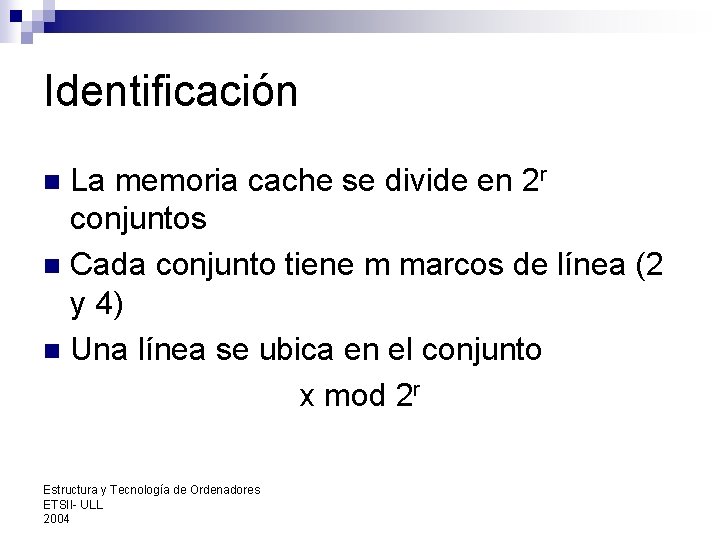

Identificación La memoria cache se divide en 2 r conjuntos n Cada conjunto tiene m marcos de línea (2 y 4) n Una línea se ubica en el conjunto x mod 2 r n Estructura y Tecnología de Ordenadores ETSII- ULL 2004

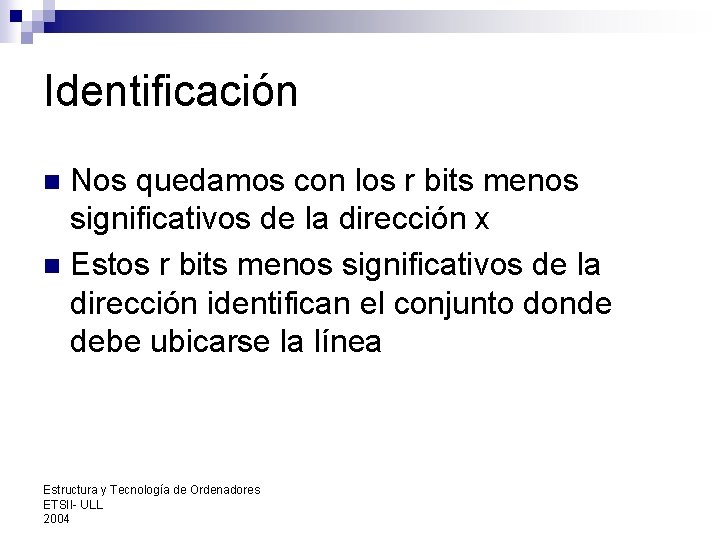

Identificación Nos quedamos con los r bits menos significativos de la dirección x n Estos r bits menos significativos de la dirección identifican el conjunto donde debe ubicarse la línea n Estructura y Tecnología de Ordenadores ETSII- ULL 2004

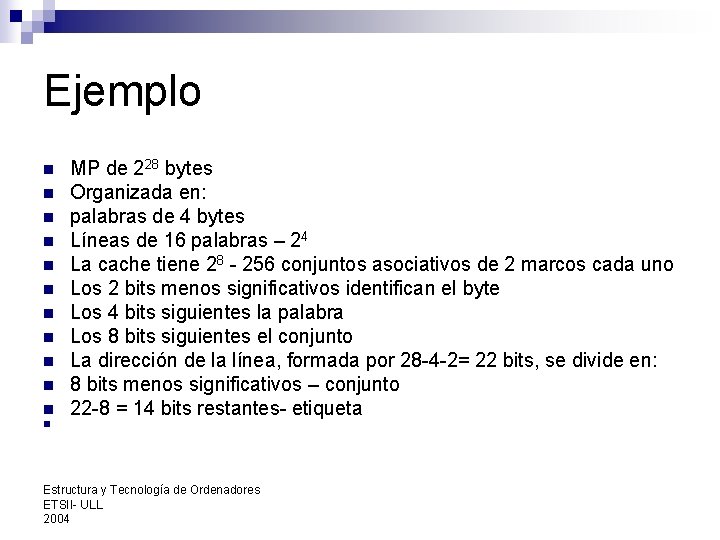

Ejemplo n n n MP de 228 bytes Organizada en: palabras de 4 bytes Líneas de 16 palabras – 24 La cache tiene 28 - 256 conjuntos asociativos de 2 marcos cada uno Los 2 bits menos significativos identifican el byte Los 4 bits siguientes la palabra Los 8 bits siguientes el conjunto La dirección de la línea, formada por 28 -4 -2= 22 bits, se divide en: 8 bits menos significativos – conjunto 22 -8 = 14 bits restantes- etiqueta Estructura y Tecnología de Ordenadores ETSII- ULL 2004

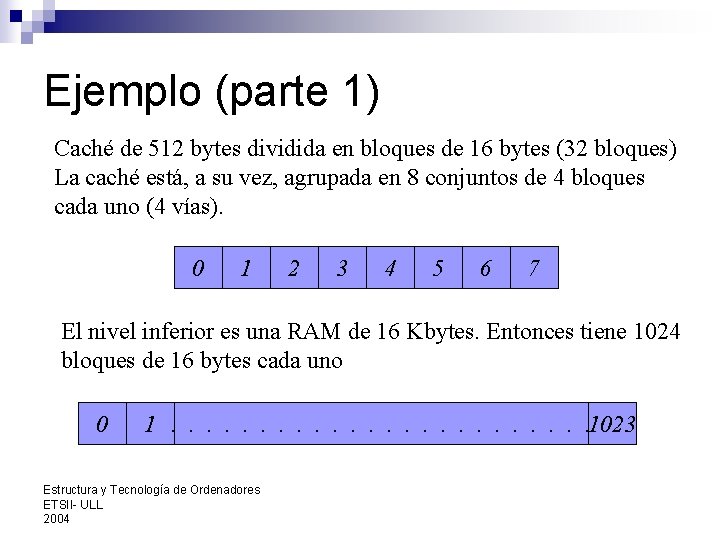

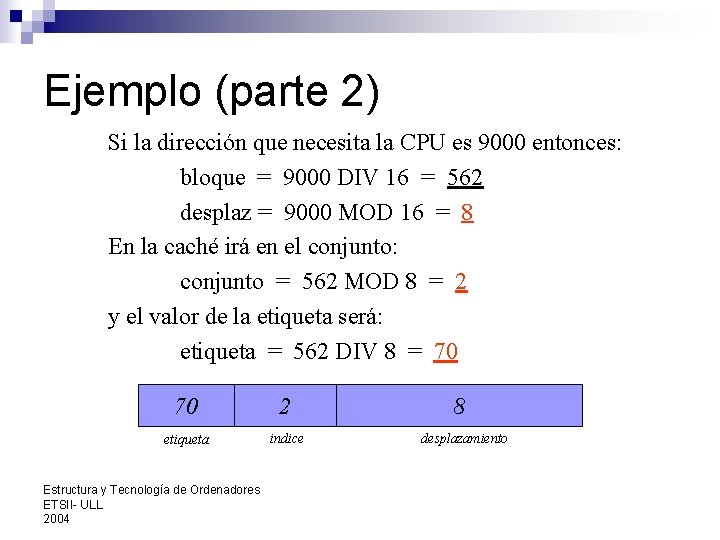

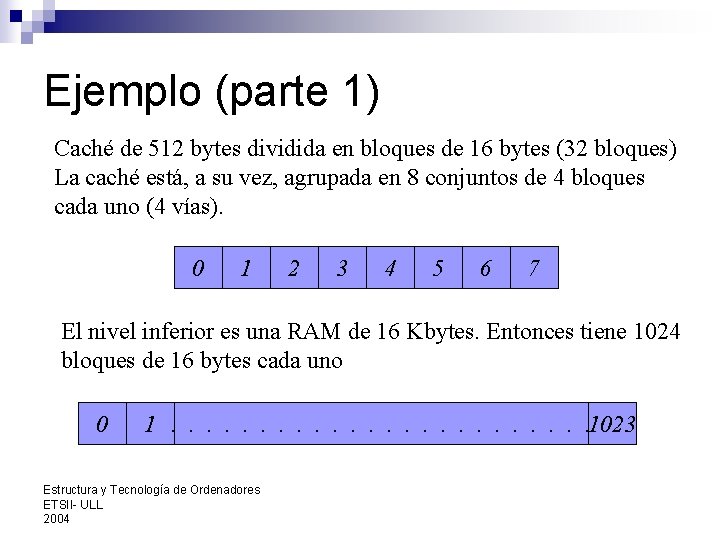

Ejemplo (parte 1) Caché de 512 bytes dividida en bloques de 16 bytes (32 bloques) La caché está, a su vez, agrupada en 8 conjuntos de 4 bloques cada uno (4 vías). 0 1 2 3 4 5 6 7 El nivel inferior es una RAM de 16 Kbytes. Entonces tiene 1024 bloques de 16 bytes cada uno 0 1. . . 1023 Estructura y Tecnología de Ordenadores ETSII- ULL 2004

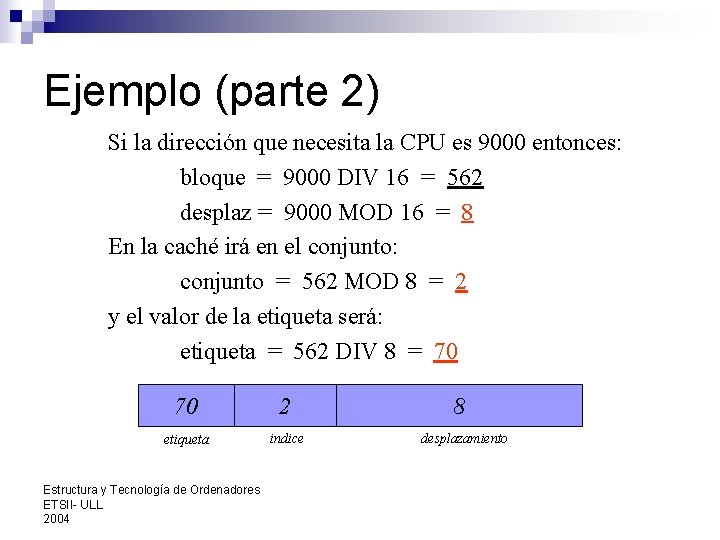

Ejemplo (parte 2) Si la dirección que necesita la CPU es 9000 entonces: bloque = 9000 DIV 16 = 562 desplaz = 9000 MOD 16 = 8 En la caché irá en el conjunto: conjunto = 562 MOD 8 = 2 y el valor de la etiqueta será: etiqueta = 562 DIV 8 = 70 70 2 etiqueta indice Estructura y Tecnología de Ordenadores ETSII- ULL 2004 8 desplazamiento

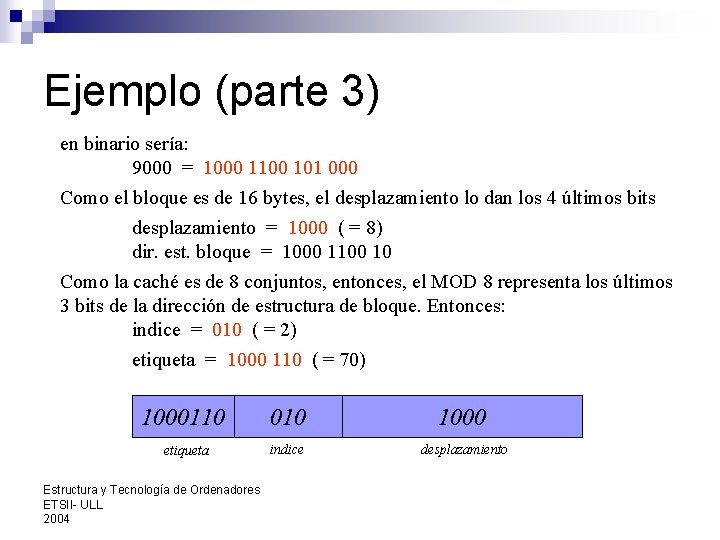

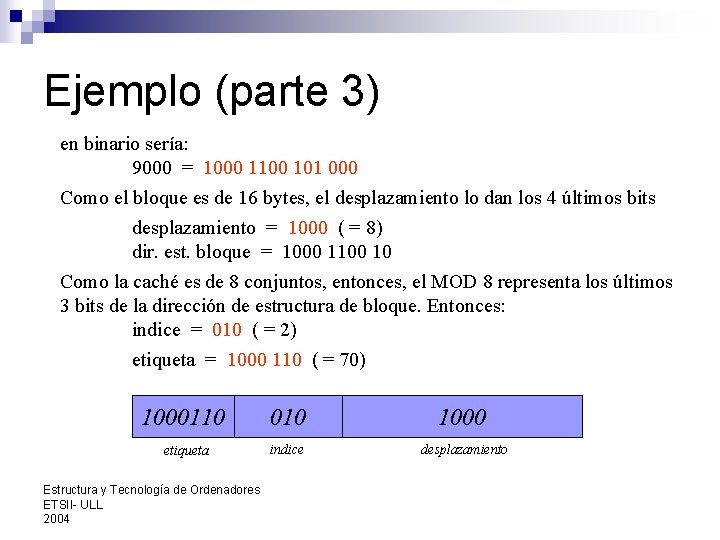

Ejemplo (parte 3) en binario sería: 9000 = 1000 1100 101 000 Como el bloque es de 16 bytes, el desplazamiento lo dan los 4 últimos bits desplazamiento = 1000 ( = 8) dir. est. bloque = 1000 1100 10 Como la caché es de 8 conjuntos, entonces, el MOD 8 representa los últimos 3 bits de la dirección de estructura de bloque. Entonces: indice = 010 ( = 2) etiqueta = 1000 110 ( = 70) 1000110 010 1000 etiqueta indice desplazamiento Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Extracción Determina qué líneas se transfieren a la cache y cuando. n Existen dos técnicas: n ¨ Extracción por demanda ¨ Extracción por anticipación Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Extracción n Por demanda: se transfiere una línea a la caché cuando hay un fallo ¨ Cuando la palabra pedida NO está en la caché n Por anticipación: se aprovecha la proximidad secuencial trayendo líneas antes que se produzcan fallos Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Extracción por anticipación Alternativas n Traer la línea j+1 cuando se accede a una palabra de la línea j (siempre que NO este) n Cuando se produce un fallo en la línea j, se traen las líneas j y j+1 ¨ La n línea j+1 se marca como anticipada Son exitosas en las caches de instrucciones por la gran proximidad secuencial Estructura y Tecnología de Ordenadores ETSII- ULL 2004

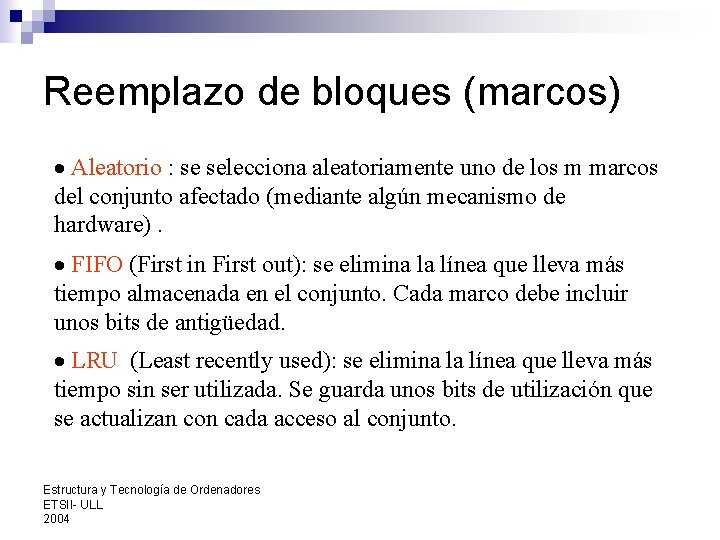

Reemplazo Cuando se ha producido un fallo de acceso en la cache se procede a obtener la línea afectada de la memoria principal y almacenarla en la cache. n Sabemos que se almacenará en el conjunto que le corresponda por su dirección, pero ¿dónde se debe almacenar la nueva línea? n Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Reemplazo de bloques (marcos) Ante un fallo de cache es necesario traer un bloque nuevo y ubicarlo en algún lugar del nivel superior Si existe algún bloque de cache con datos no válidos, el reemplazo se hace en ese lugar Debido a la alta frecuencia de aciertos de la cache es necesario tomar estrategias de reemplazo Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Reemplazo de bloques (marcos) Si la cache es de mapeo directo no hay problema, ya que el nuevo bloque puede ir en un solo lugar En caso de caches asociativas el bloque puede ubicarse en diferentes lugares. Estrategias: • reemplazo aleatorio • reemplazo pseudo aleatorio • LRU (menos recientemente usado) Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Reemplazo de bloques (marcos) · Aleatorio : se selecciona aleatoriamente uno de los m marcos del conjunto afectado (mediante algún mecanismo de hardware). · FIFO (First in First out): se elimina la línea que lleva más tiempo almacenada en el conjunto. Cada marco debe incluir unos bits de antigüedad. · LRU (Least recently used): se elimina la línea que lleva más tiempo sin ser utilizada. Se guarda unos bits de utilización que se actualizan con cada acceso al conjunto. Estructura y Tecnología de Ordenadores ETSII- ULL 2004

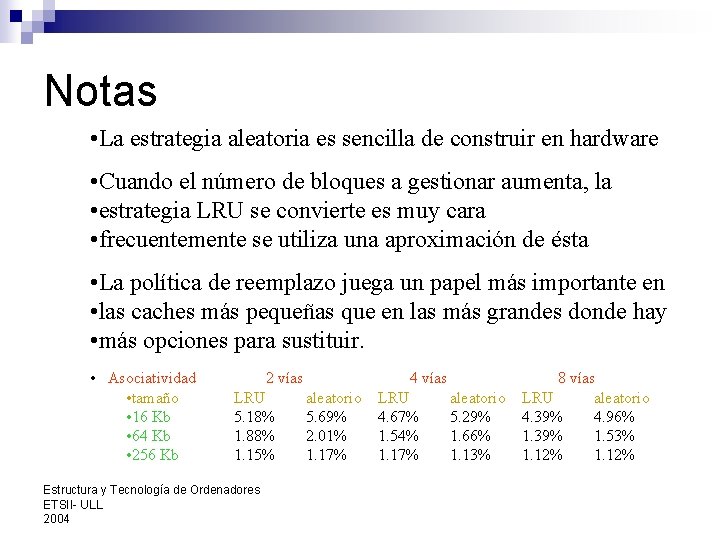

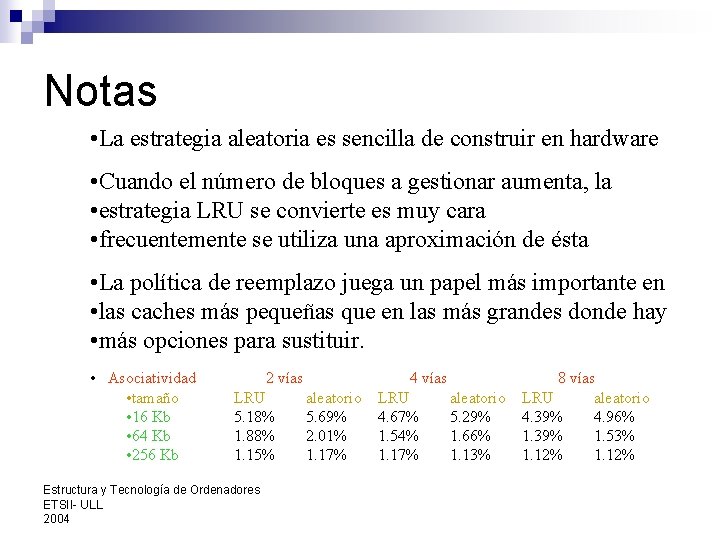

Notas • La estrategia aleatoria es sencilla de construir en hardware • Cuando el número de bloques a gestionar aumenta, la • estrategia LRU se convierte es muy cara • frecuentemente se utiliza una aproximación de ésta • La política de reemplazo juega un papel más importante en • las caches más pequeñas que en las más grandes donde hay • más opciones para sustituir. • Asociatividad • tamaño • 16 Kb • 64 Kb • 256 Kb 2 vías LRU 5. 18% 1. 88% 1. 15% Estructura y Tecnología de Ordenadores ETSII- ULL 2004 4 vías aleatorio 5. 69% 2. 01% 1. 17% LRU 4. 67% 1. 54% 1. 17% aleatorio 5. 29% 1. 66% 1. 13% 8 vías LRU aleatorio 4. 39% 4. 96% 1. 39% 1. 53% 1. 12%

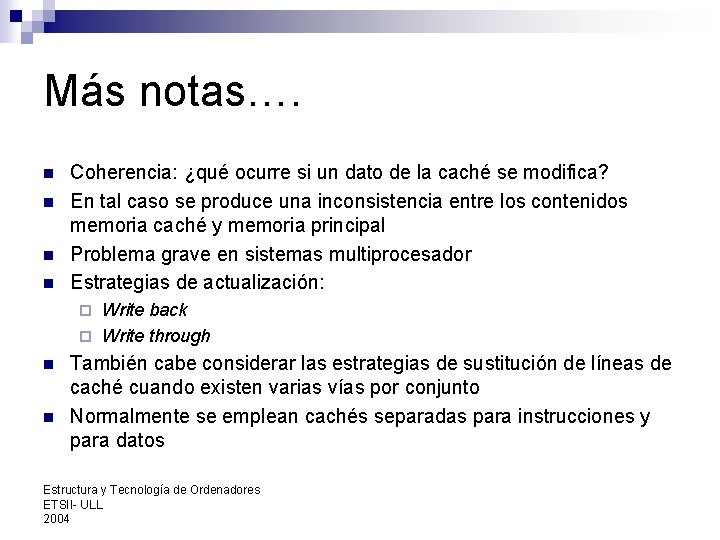

Más notas…. n n Coherencia: ¿qué ocurre si un dato de la caché se modifica? En tal caso se produce una inconsistencia entre los contenidos memoria caché y memoria principal Problema grave en sistemas multiprocesador Estrategias de actualización: Write back ¨ Write through ¨ n n También cabe considerar las estrategias de sustitución de líneas de caché cuando existen varias vías por conjunto Normalmente se emplean cachés separadas para instrucciones y para datos Estructura y Tecnología de Ordenadores ETSII- ULL 2004

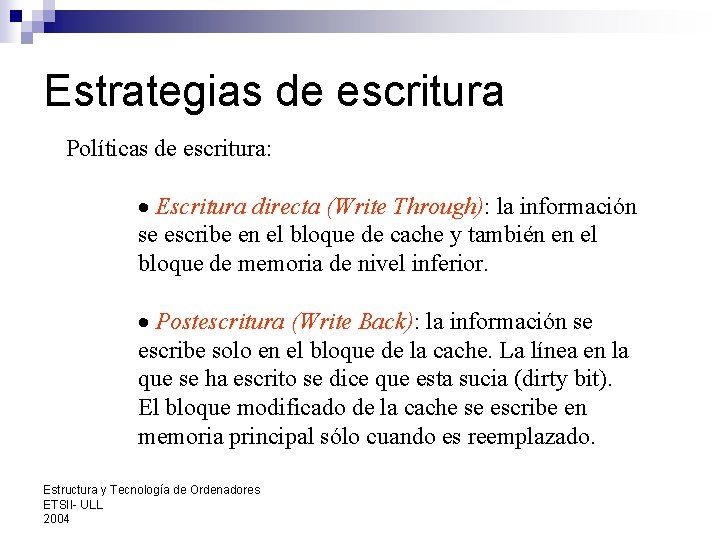

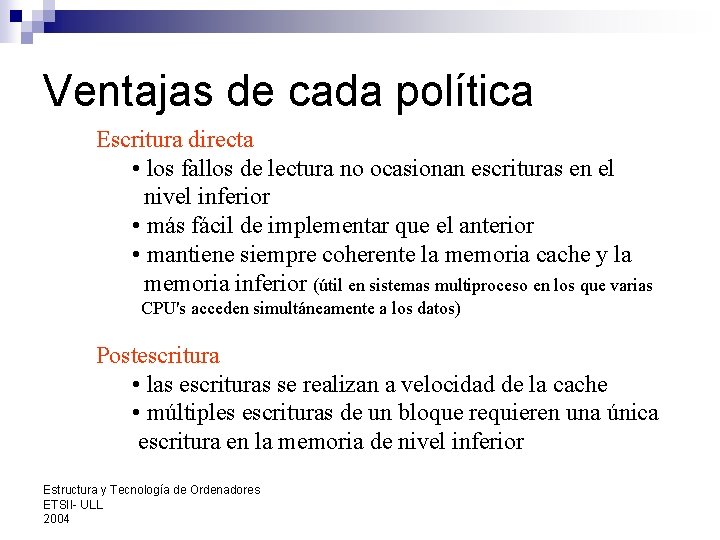

Estrategias de escritura Políticas de escritura: · Escritura directa (Write Through): la información se escribe en el bloque de cache y también en el bloque de memoria de nivel inferior. · Postescritura (Write Back): la información se escribe solo en el bloque de la cache. La línea en la que se ha escrito se dice que esta sucia (dirty bit). El bloque modificado de la cache se escribe en memoria principal sólo cuando es reemplazado. Estructura y Tecnología de Ordenadores ETSII- ULL 2004

Ventajas de cada política Escritura directa • los fallos de lectura no ocasionan escrituras en el nivel inferior • más fácil de implementar que el anterior • mantiene siempre coherente la memoria cache y la memoria inferior (útil en sistemas multiproceso en los que varias CPU's acceden simultáneamente a los datos) Postescritura • las escrituras se realizan a velocidad de la cache • múltiples escrituras de un bloque requieren una única escritura en la memoria de nivel inferior Estructura y Tecnología de Ordenadores ETSII- ULL 2004

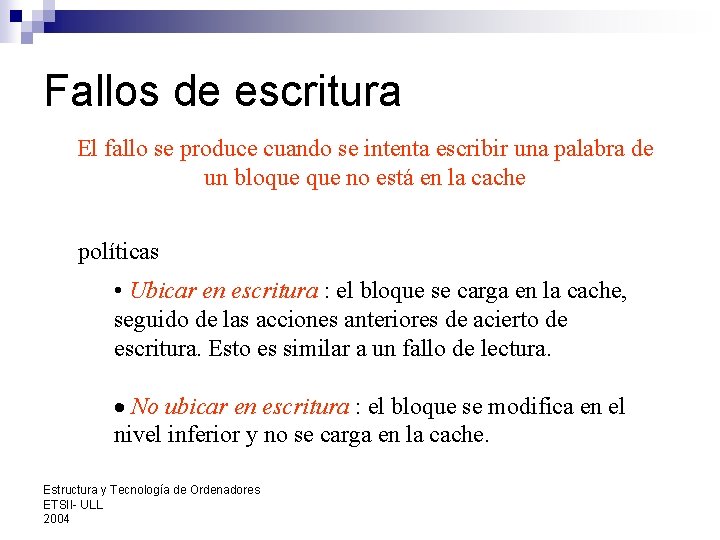

Fallos de escritura El fallo se produce cuando se intenta escribir una palabra de un bloque no está en la cache políticas • Ubicar en escritura : el bloque se carga en la cache, seguido de las acciones anteriores de acierto de escritura. Esto es similar a un fallo de lectura. · No ubicar en escritura : el bloque se modifica en el nivel inferior y no se carga en la cache. Estructura y Tecnología de Ordenadores ETSII- ULL 2004

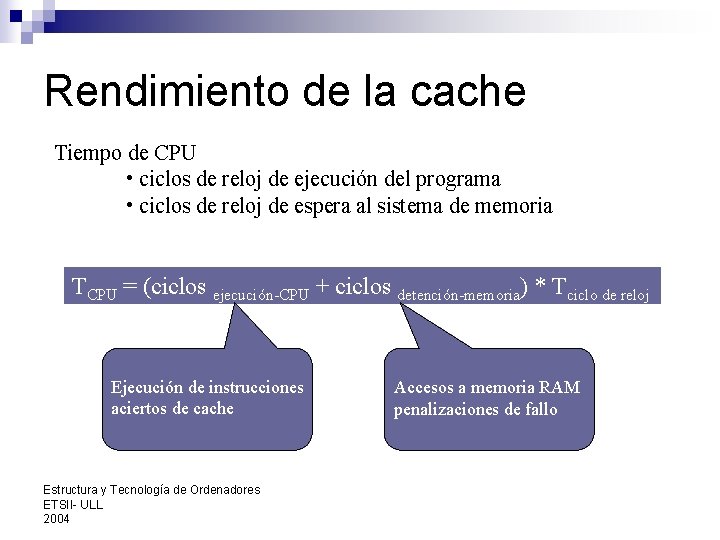

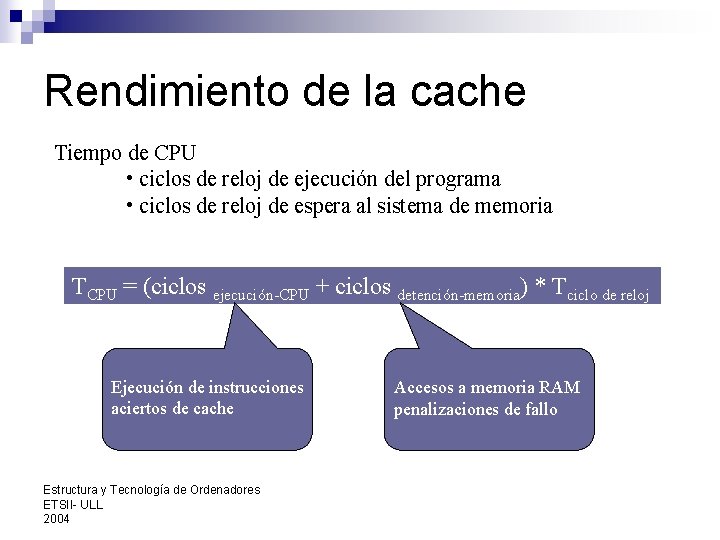

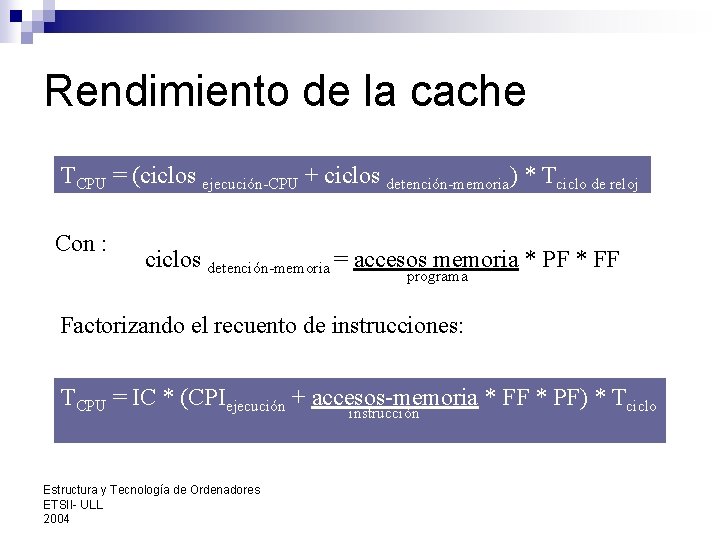

Rendimiento de la cache Tiempo de CPU • ciclos de reloj de ejecución del programa • ciclos de reloj de espera al sistema de memoria TCPU = (ciclos ejecución-CPU + ciclos detención-memoria) * Tciclo de reloj Ejecución de instrucciones aciertos de cache Estructura y Tecnología de Ordenadores ETSII- ULL 2004 Accesos a memoria RAM penalizaciones de fallo

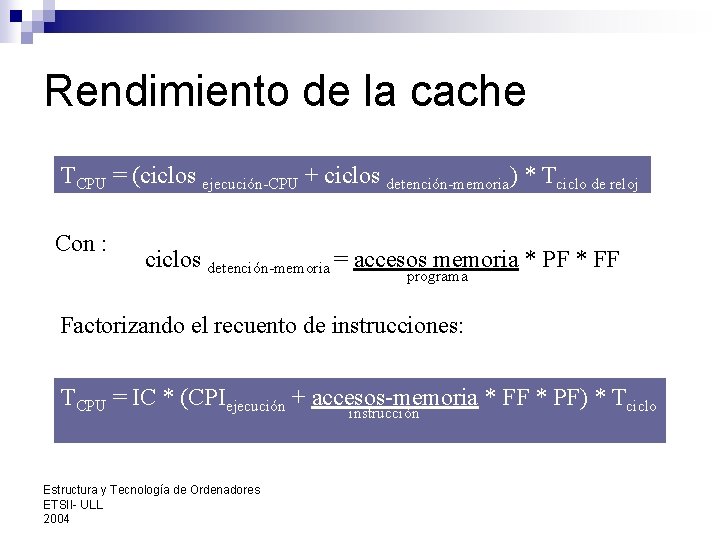

Rendimiento de la cache TCPU = (ciclos ejecución-CPU + ciclos detención-memoria) * Tciclo de reloj Con : ciclos detención-memoria = accesos memoria * PF * FF programa Factorizando el recuento de instrucciones: TCPU = IC * (CPIejecución + accesos-memoria * FF * PF) * Tciclo instrucción Estructura y Tecnología de Ordenadores ETSII- ULL 2004

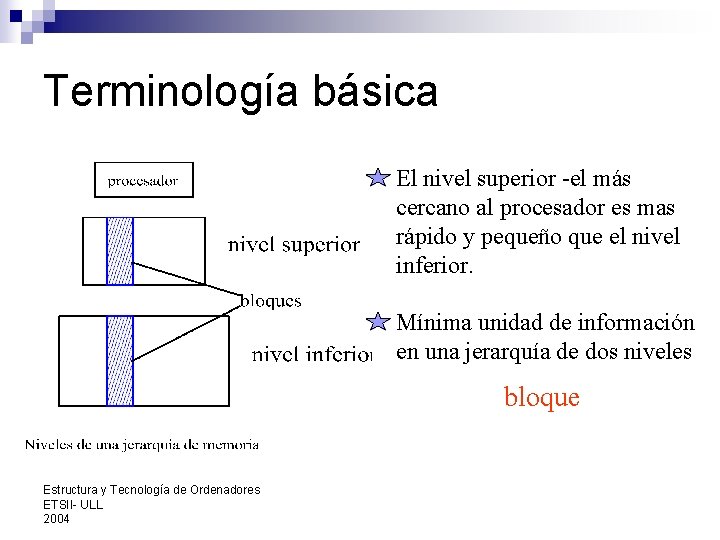

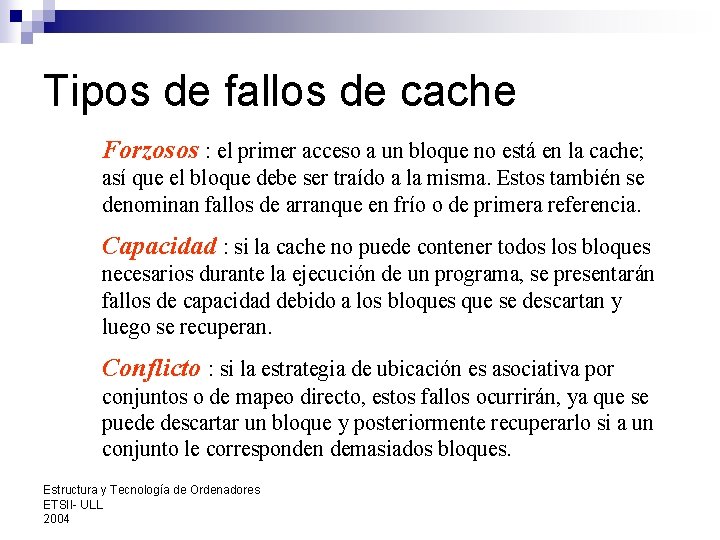

Tipos de fallos de cache Forzosos : el primer acceso a un bloque no está en la cache; así que el bloque debe ser traído a la misma. Estos también se denominan fallos de arranque en frío o de primera referencia. Capacidad : si la cache no puede contener todos los bloques necesarios durante la ejecución de un programa, se presentarán fallos de capacidad debido a los bloques que se descartan y luego se recuperan. Conflicto : si la estrategia de ubicación es asociativa por conjuntos o de mapeo directo, estos fallos ocurrirán, ya que se puede descartar un bloque y posteriormente recuperarlo si a un conjunto le corresponden demasiados bloques. Estructura y Tecnología de Ordenadores ETSII- ULL 2004