Lattice Mico 32 Technical Seminar Tour 2007 LATTICES

- Slides: 46

Lattice. Mico 32 Technical Seminar Tour 2007 LATTICE‘S PROGRAMMABLE LOWCOST SOLUTIONS Technical Seminar Tour 2006 Lattice. Mico 32 - Page 1

Lattice. Mico 32 Agenda ¨ Architecture and Peripherals ¨ Development tools ¨ Software Deployment ¨ Tool Flow ¨ Demo Technical Seminar Tour 2006 Lattice. Mico 32 - Page 2

Introducing the Lattice. Mico 32 ¨ Flexible, High Performance 32 -Bit Microprocessor ¨ Optimized For Lattice Leading-Edge Families – – Lattice. EC/P Lattice. ECP 2/M Lattice. SC Lattice. XP ¨ Targeted Towards Wide Variety of Applications – – – Consumer Computation Communications Medical Industrial Automotive Technical Seminar Tour 2006 Lattice. Mico 32 - Page 3

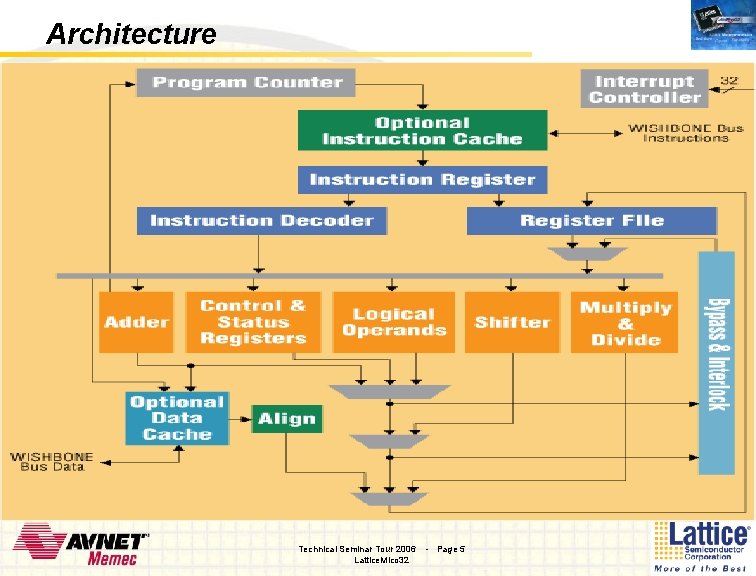

Performance Enhanced Feature Set ¨ RISC architecture ¨ 32 -bit data path and 32 -bit instructions ¨ 32 general purpose register ¨ Handles up to 32 external interrupts ¨ Optional instruction and data caches ¨ Dual Wishbone memory interfaces (Instruction and Data) Technical Seminar Tour 2006 Lattice. Mico 32 - Page 4

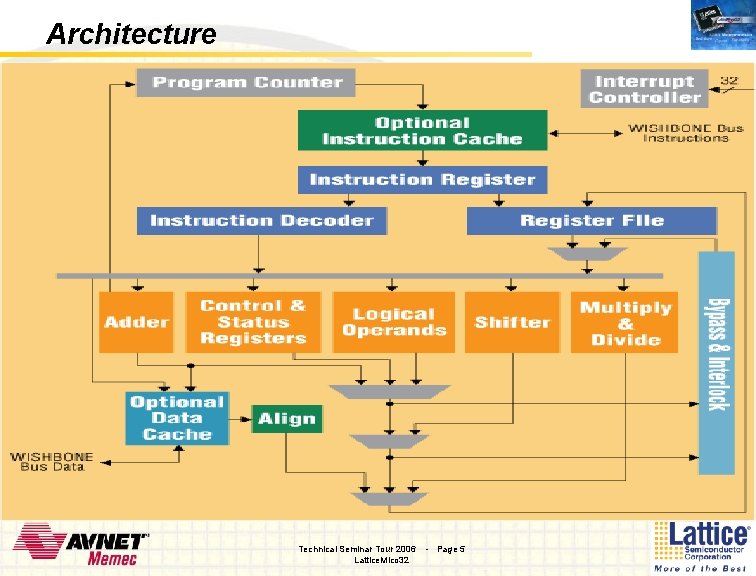

Architecture Technical Seminar Tour 2006 Lattice. Mico 32 - Page 5

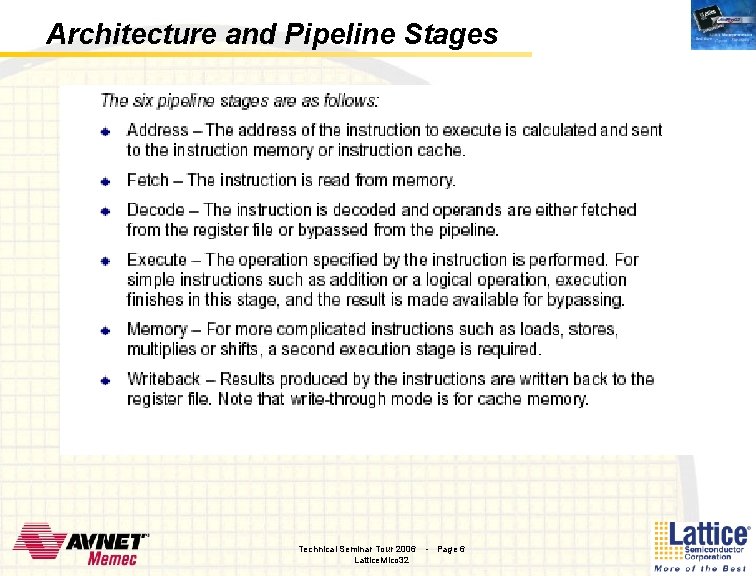

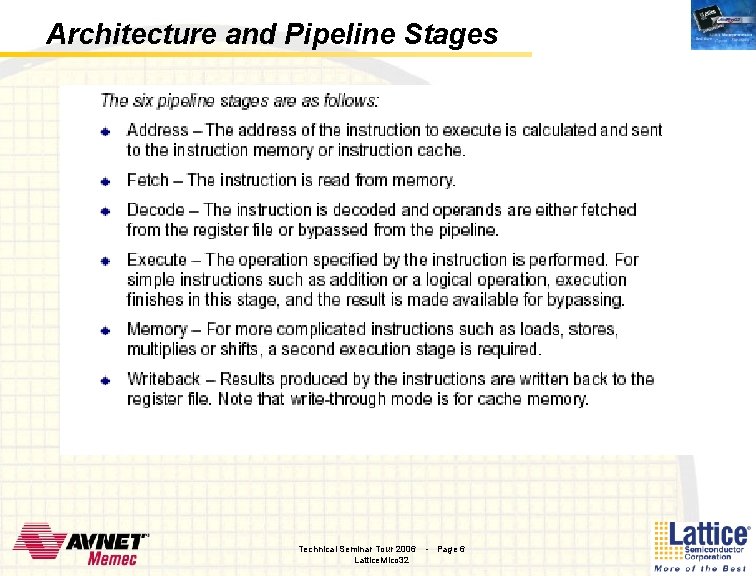

Architecture and Pipeline Stages Technical Seminar Tour 2006 Lattice. Mico 32 - Page 6

Peripheral Components ¨ Enable Design of Complete Embedded Systems ¨ Connect via a WISHBONE Bus Interface – Royalty-free – Public domain specification controlled by Open. Cores. org Technical Seminar Tour 2006 Lattice. Mico 32 - Page 7

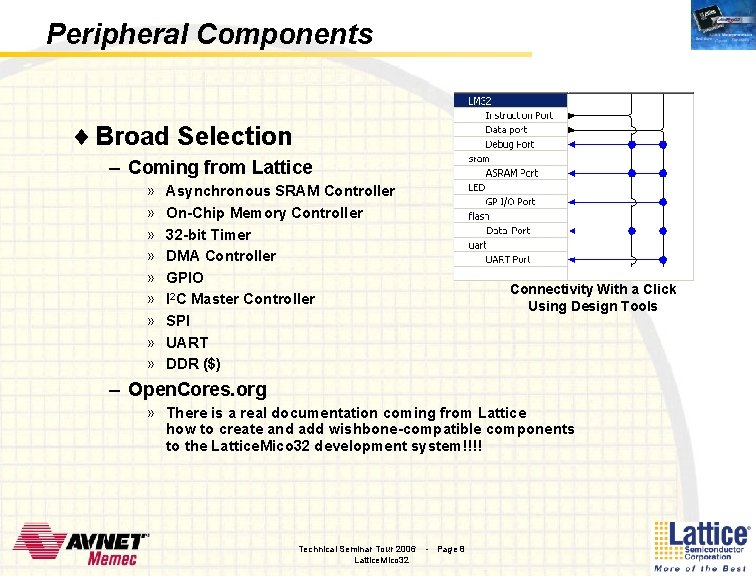

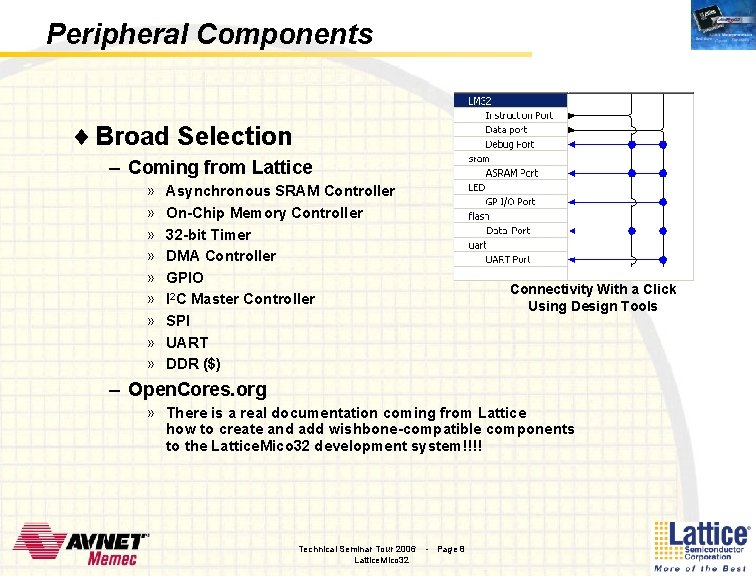

Peripheral Components ¨ Broad Selection – Coming from Lattice » » » » » Asynchronous SRAM Controller On-Chip Memory Controller 32 -bit Timer DMA Controller GPIO I 2 C Master Controller SPI UART DDR ($) Connectivity With a Click Using Design Tools – Open. Cores. org » There is a real documentation coming from Lattice how to create and add wishbone-compatible components to the Lattice. Mico 32 development system!!!! Technical Seminar Tour 2006 Lattice. Mico 32 - Page 8

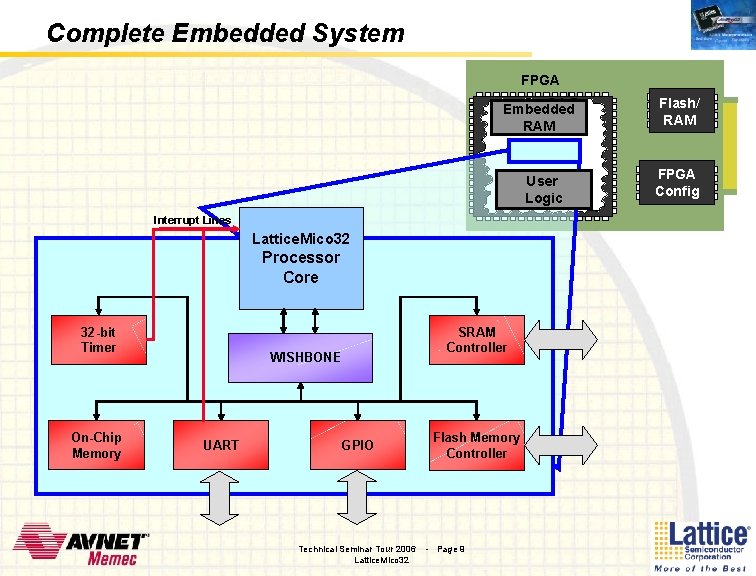

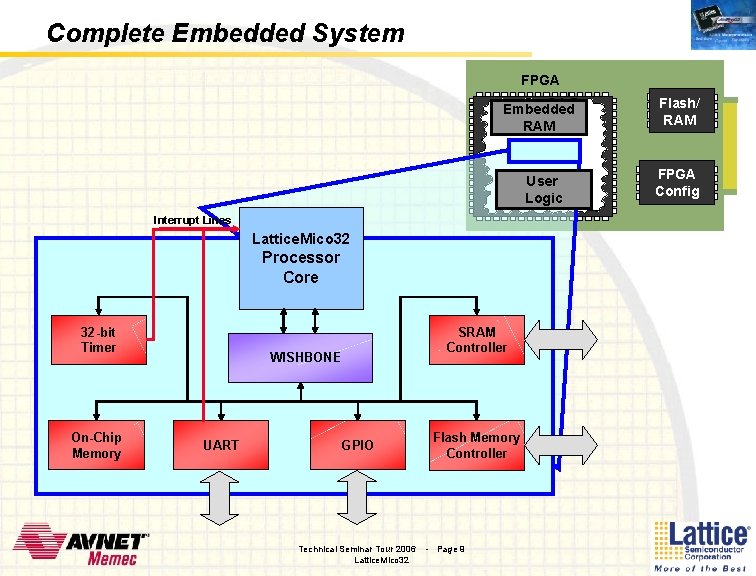

Complete Embedded System FPGA Embedded RAM User Logic Interrupt Lines Lattice. Mico 32 Processor Core 32 -bit Timer On-Chip Memory WISHBONE UART GPIO Technical Seminar Tour 2006 Lattice. Mico 32 SRAM Controller Flash Memory Controller - Page 9 Flash/ RAM FPGA Config

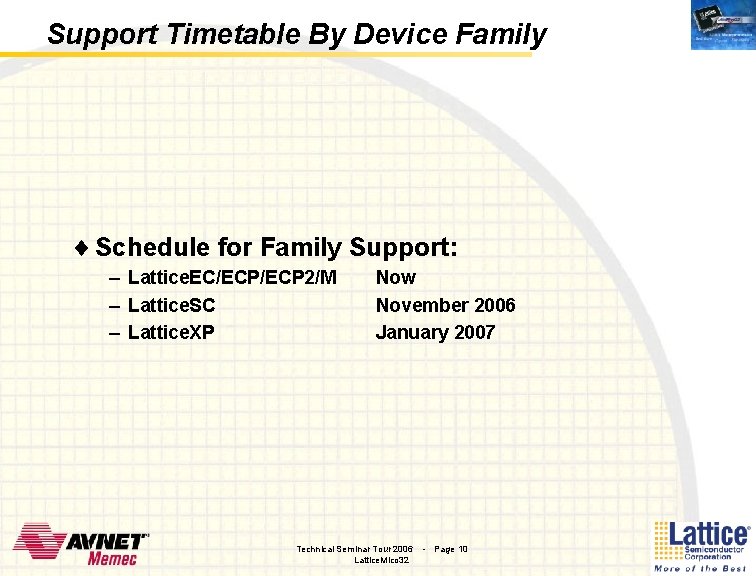

Support Timetable By Device Family ¨ Schedule for Family Support: – Lattice. EC/ECP 2/M – Lattice. SC – Lattice. XP Now November 2006 January 2007 Technical Seminar Tour 2006 Lattice. Mico 32 - Page 10

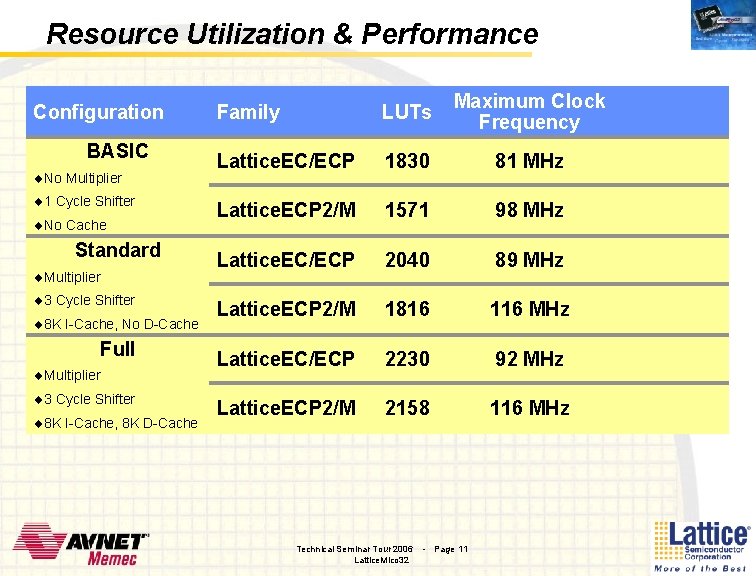

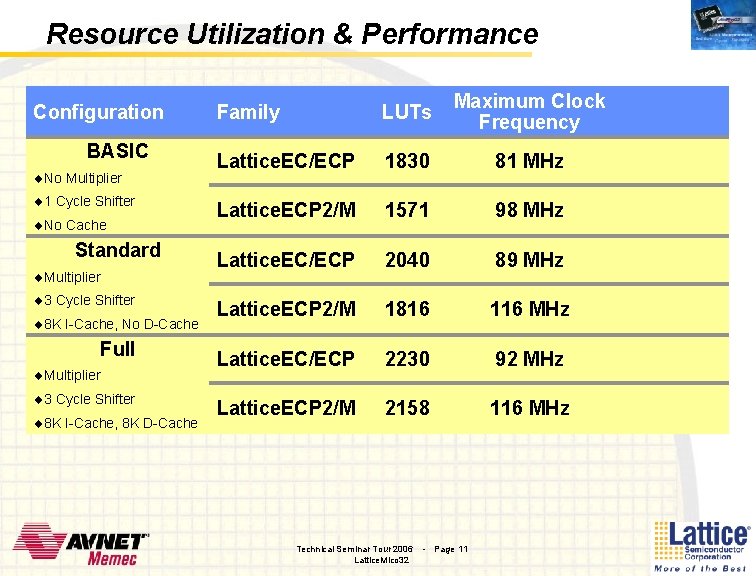

Resource Utilization & Performance Configuration BASIC ¨No Multiplier ¨ 1 Cycle Shifter ¨No Cache Standard ¨Multiplier ¨ 3 Cycle Shifter ¨ 8 K I-Cache, No D-Cache Full ¨Multiplier ¨ 3 Cycle Shifter ¨ 8 K I-Cache, 8 K D-Cache Family LUTs Maximum Clock Frequency Lattice. EC/ECP 1830 81 MHz Lattice. ECP 2/M 1571 98 MHz Lattice. EC/ECP 2040 89 MHz Lattice. ECP 2/M 1816 116 MHz Lattice. EC/ECP 2230 92 MHz Lattice. ECP 2/M 2158 116 MHz Technical Seminar Tour 2006 Lattice. Mico 32 - Page 11

Open IP Core Licensing ¨ Innovative Open IP Core License – Visibility, Reliability, Scalability ¨ Free of Charge ¨ Generated Lattice. Mico 32 core and Peripherals based on HDL Technical Seminar Tour 2006 Lattice. Mico 32 - Page 12

Development Tool Lattice. Mico 32 System ¨ to implement HW-IP (u. P and Peripherals) and SW ¨ Based on Eclipse C/C++ Dev. Tools (CDT) ¨ Free of charge, via Internet ¨ Combined with isp. LEVER Technical Seminar Tour 2006 Lattice. Mico 32 - Page 13

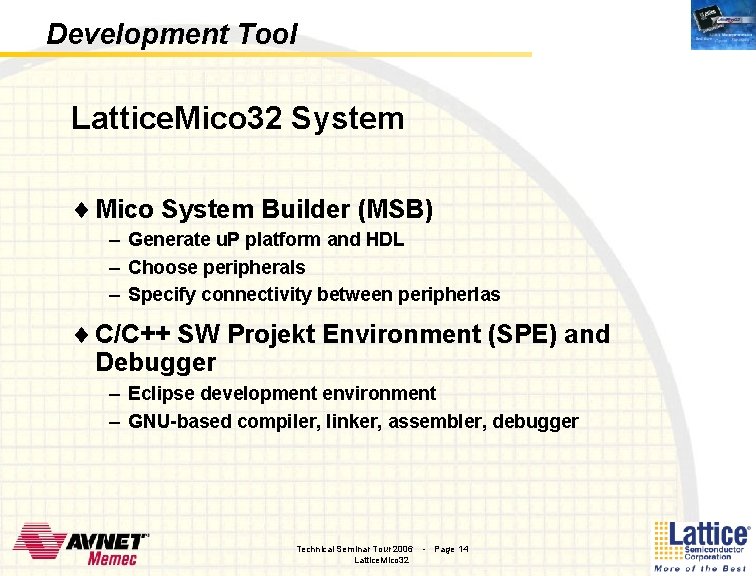

Development Tool Lattice. Mico 32 System ¨ Mico System Builder (MSB) – Generate u. P platform and HDL – Choose peripherals – Specify connectivity between peripherlas ¨ C/C++ SW Projekt Environment (SPE) and Debugger – Eclipse development environment – GNU-based compiler, linker, assembler, debugger Technical Seminar Tour 2006 Lattice. Mico 32 - Page 14

RTOS Support Micrium’s u. C/OS-II RTOS ¨ Included in Lattice. Mico 32 System ¨ Open source ¨ free of charge for eval and non-commercial use ¨ For commercial-use obtain a license directly from Micrium Technical Seminar Tour 2006 Lattice. Mico 32 - Page 15

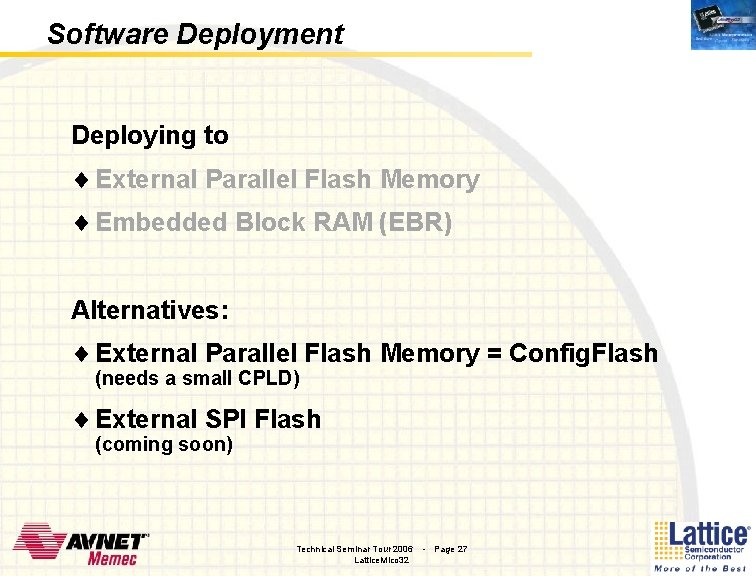

Software Deployment Deploying to ¨External Parallel Flash ¨On-Chip (Embedded Block RAM EBR) Technical Seminar Tour 2006 Lattice. Mico 32 - Page 16

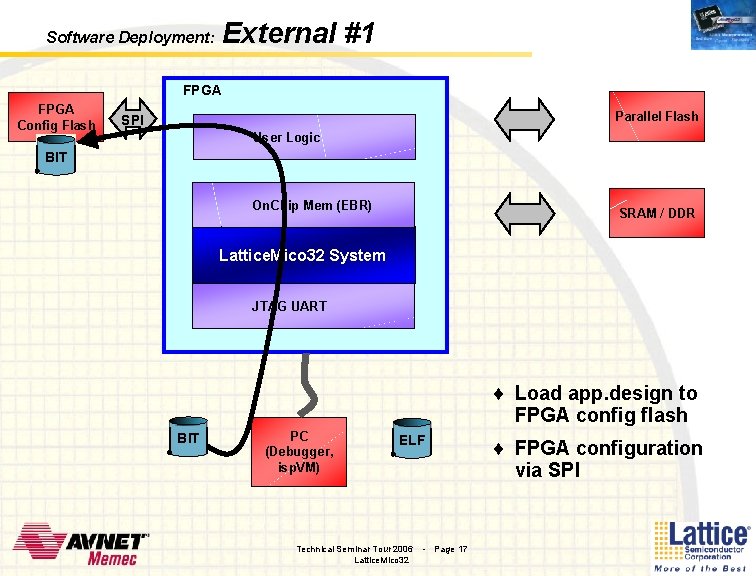

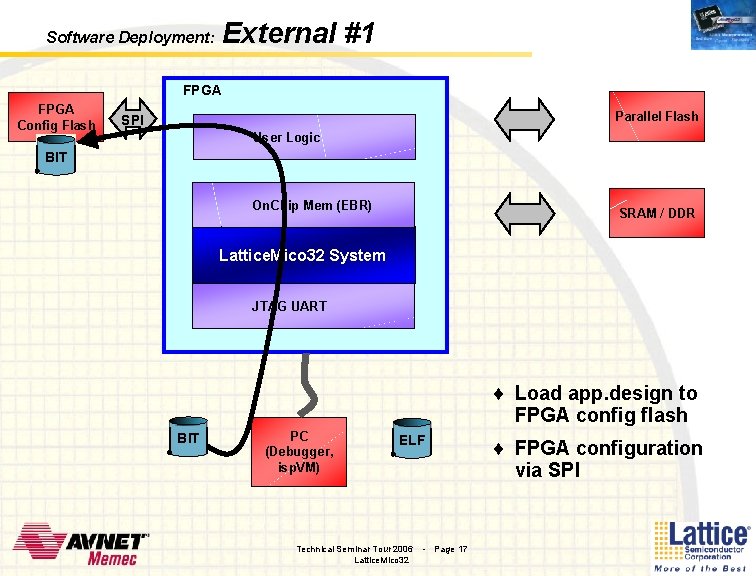

Software Deployment: External #1 FPGA Config Flash Parallel Flash SPI User Logic BIT On. Chip Mem (EBR) SRAM / DDR Lattice. Mico 32 System JTAG UART ¨ Load app. design to FPGA config flash BIT PC (Debugger, isp. VM) ELF Technical Seminar Tour 2006 Lattice. Mico 32 - Page 17 ¨ FPGA configuration via SPI

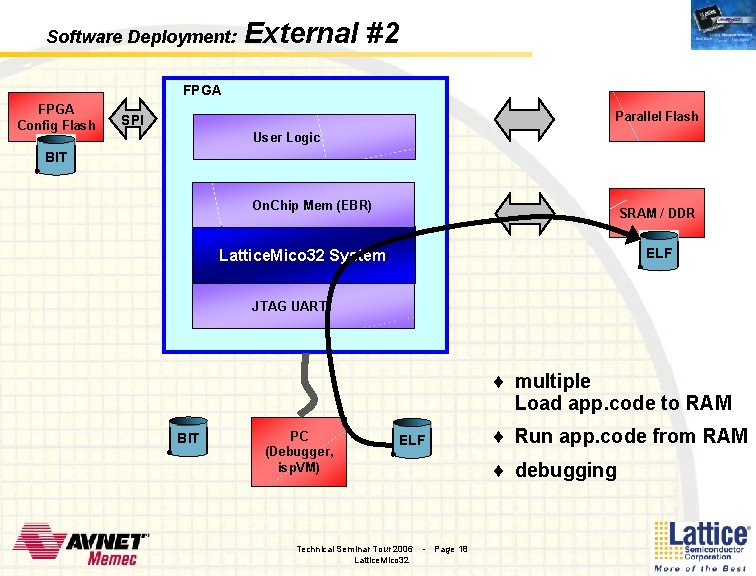

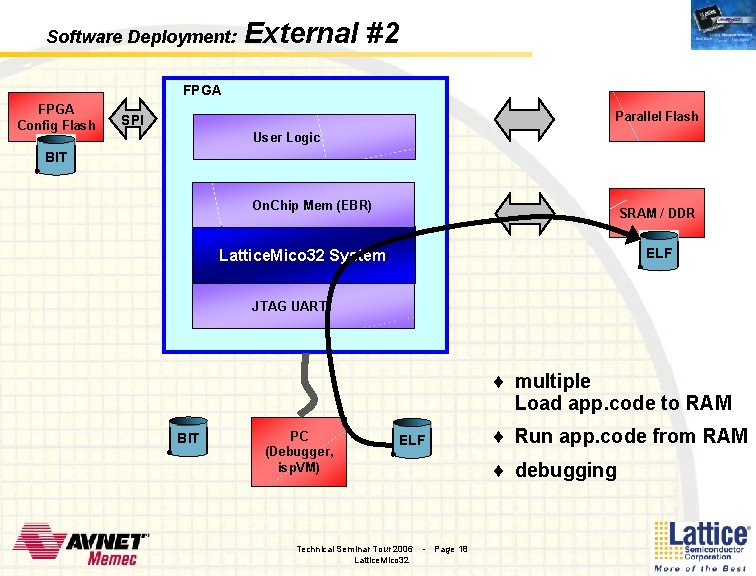

Software Deployment: External #2 FPGA Config Flash Parallel Flash SPI User Logic BIT On. Chip Mem (EBR) SRAM / DDR ELF Lattice. Mico 32 System JTAG UART ¨ multiple Load app. code to RAM BIT PC (Debugger, isp. VM) ELF Technical Seminar Tour 2006 Lattice. Mico 32 ¨ Run app. code from RAM ¨ debugging - Page 18

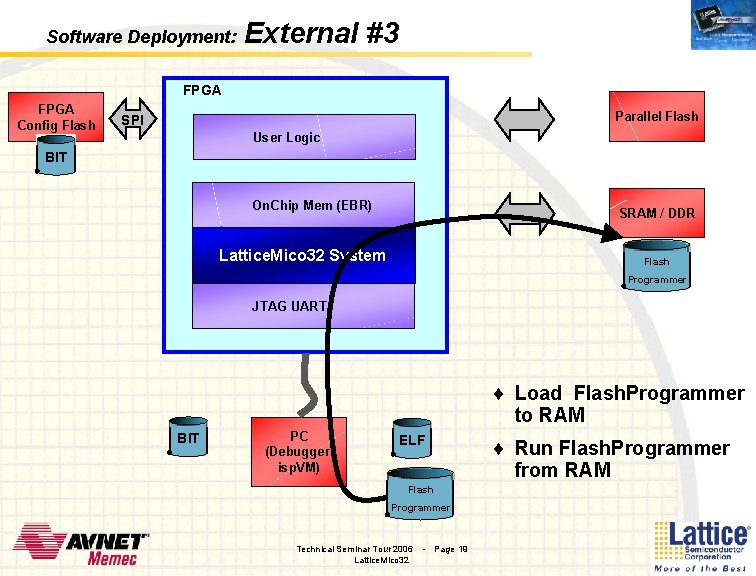

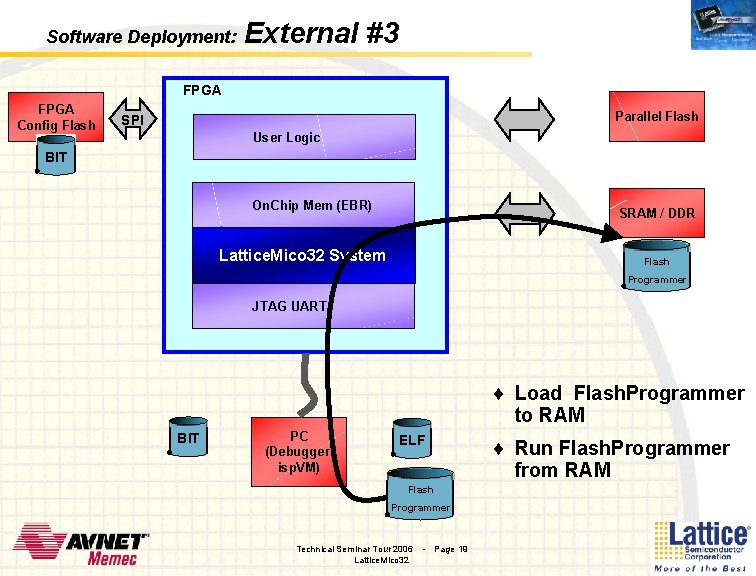

Software Deployment: External #3 FPGA Config Flash Parallel Flash SPI User Logic BIT On. Chip Mem (EBR) SRAM / DDR Lattice. Mico 32 System Flash Programmer JTAG UART ¨ Load Flash. Programmer to RAM BIT PC (Debugger, isp. VM) ELF Flash Programmer Technical Seminar Tour 2006 Lattice. Mico 32 - Page 19 ¨ Run Flash. Programmer from RAM

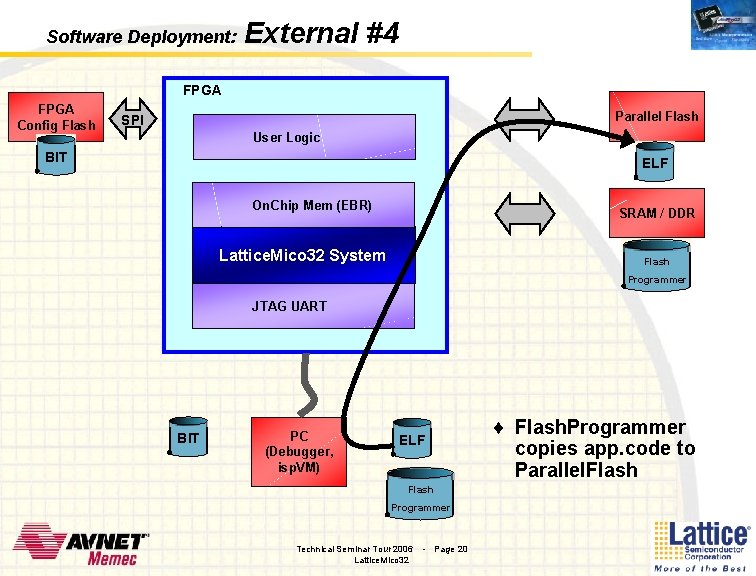

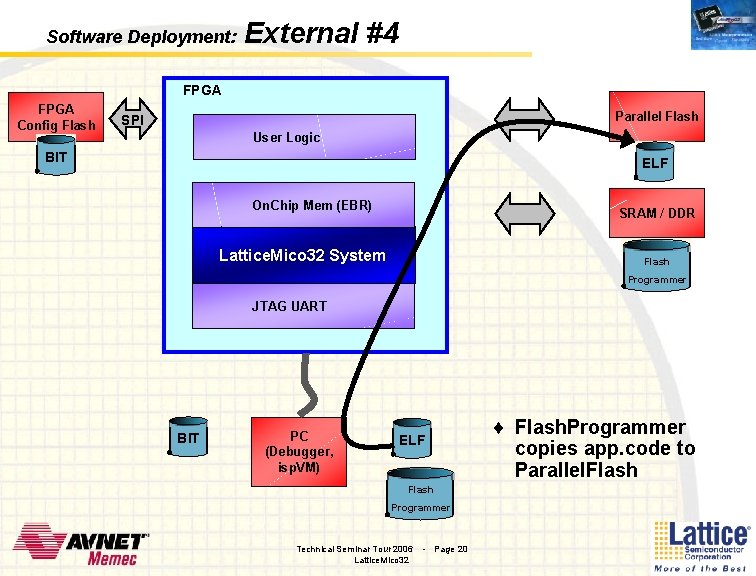

Software Deployment: External #4 FPGA Config Flash Parallel Flash SPI User Logic BIT ELF On. Chip Mem (EBR) SRAM / DDR Lattice. Mico 32 System Flash Programmer JTAG UART BIT PC (Debugger, isp. VM) ELF Flash Programmer Technical Seminar Tour 2006 Lattice. Mico 32 - Page 20 ¨ Flash. Programmer copies app. code to Parallel. Flash

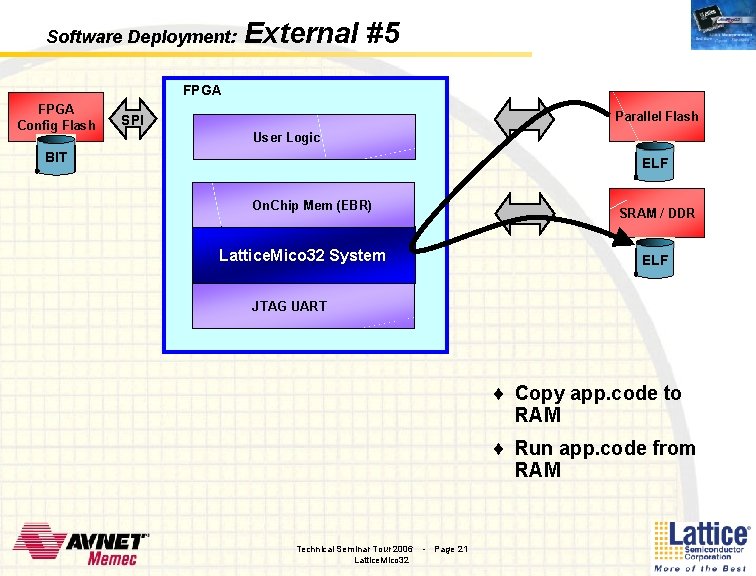

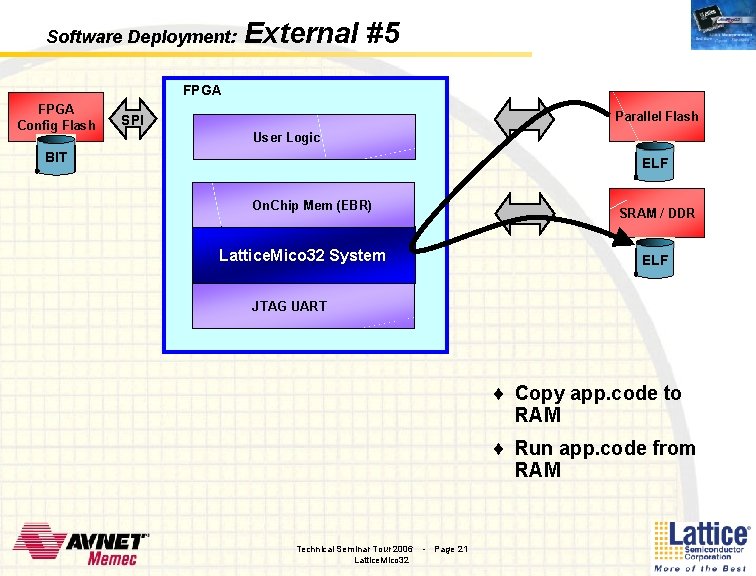

Software Deployment: External #5 FPGA Config Flash Parallel Flash SPI User Logic BIT ELF On. Chip Mem (EBR) SRAM / DDR Lattice. Mico 32 System ELF JTAG UART ¨ Copy app. code to RAM ¨ Run app. code from RAM Technical Seminar Tour 2006 Lattice. Mico 32 - Page 21

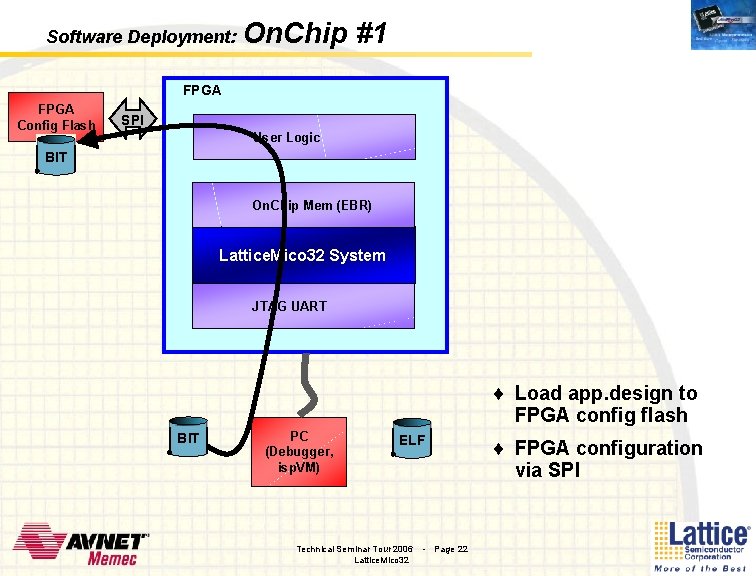

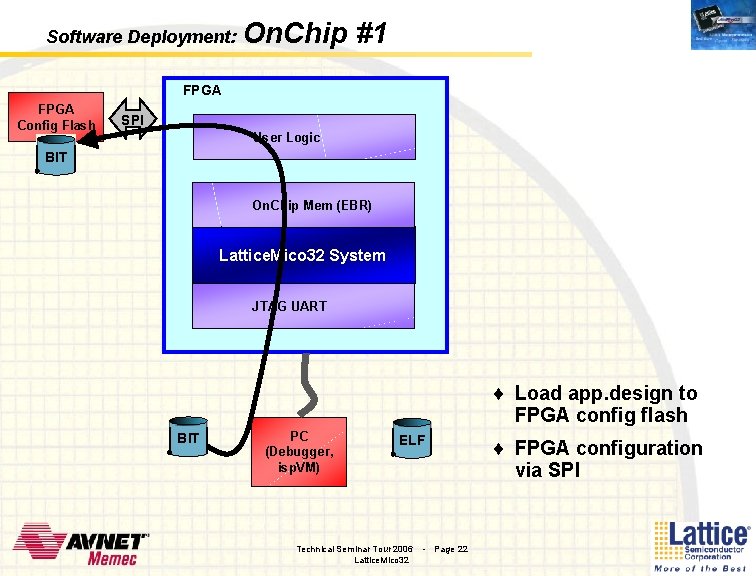

Software Deployment: On. Chip #1 FPGA Config Flash SPI User Logic BIT On. Chip Mem (EBR) Lattice. Mico 32 System JTAG UART ¨ Load app. design to FPGA config flash BIT PC (Debugger, isp. VM) ELF Technical Seminar Tour 2006 Lattice. Mico 32 - Page 22 ¨ FPGA configuration via SPI

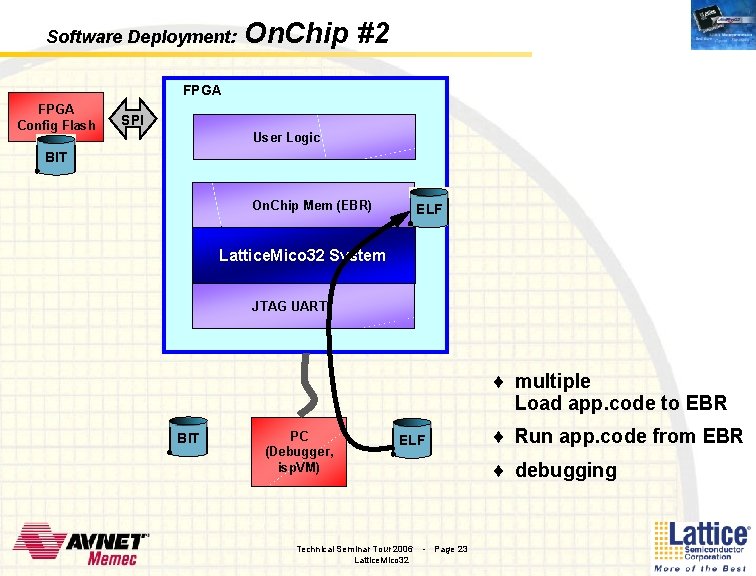

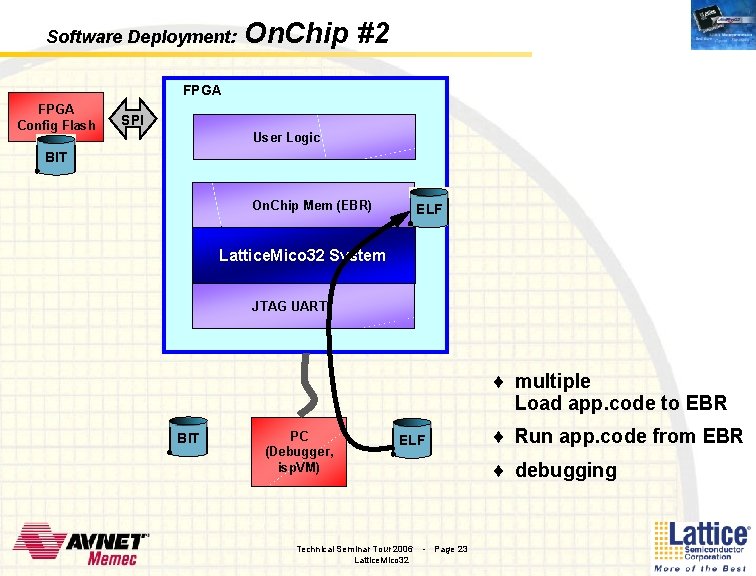

Software Deployment: On. Chip #2 FPGA Config Flash SPI User Logic BIT On. Chip Mem (EBR) ELF Lattice. Mico 32 System JTAG UART ¨ multiple Load app. code to EBR BIT PC (Debugger, isp. VM) ELF Technical Seminar Tour 2006 Lattice. Mico 32 ¨ Run app. code from EBR ¨ debugging - Page 23

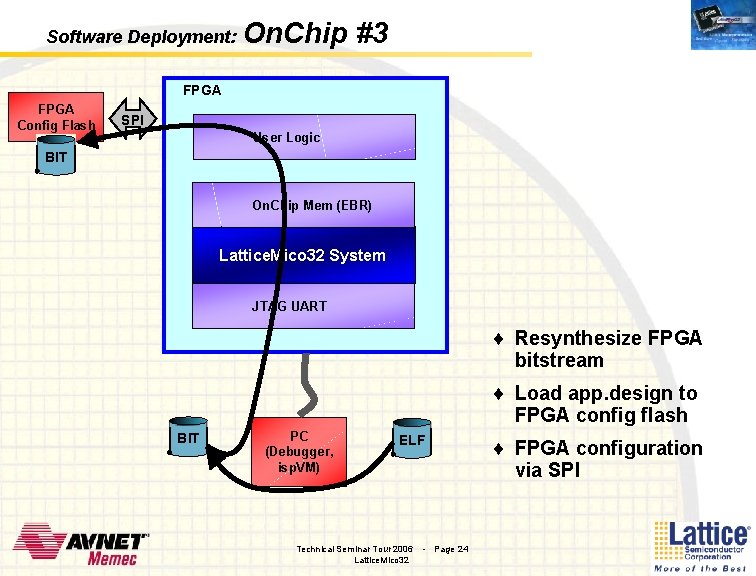

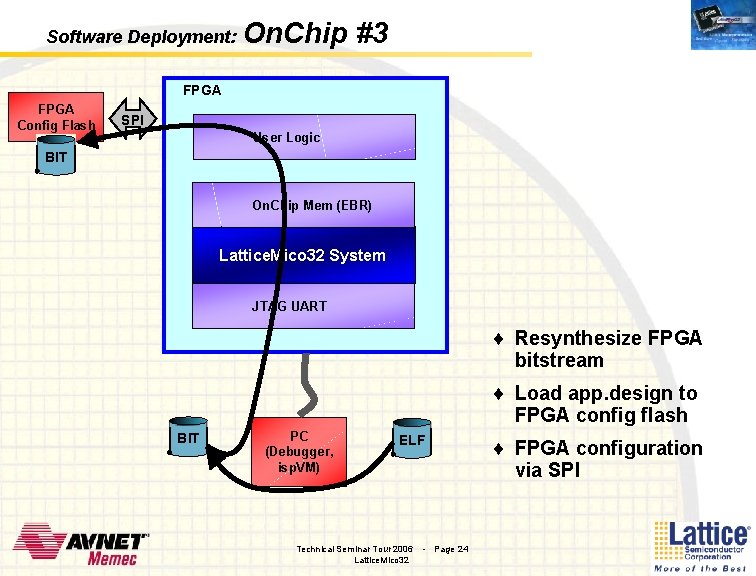

Software Deployment: On. Chip #3 FPGA Config Flash SPI User Logic BIT On. Chip Mem (EBR) Lattice. Mico 32 System JTAG UART ¨ Resynthesize FPGA bitstream ¨ Load app. design to FPGA config flash BIT PC (Debugger, isp. VM) ELF Technical Seminar Tour 2006 Lattice. Mico 32 - Page 24 ¨ FPGA configuration via SPI

Software Deployment: This are just very simplified descriptions Please have a look to: ¨ Lattice. Mico 32 Tutorial (based on the Lattice 32 Development Board) ¨ SW Developers User. Guide Technical Seminar Tour 2006 Lattice. Mico 32 - Page 25

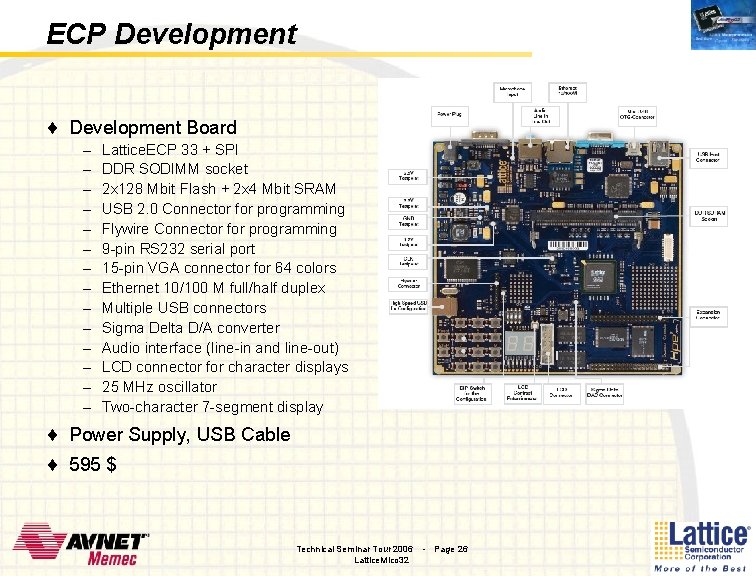

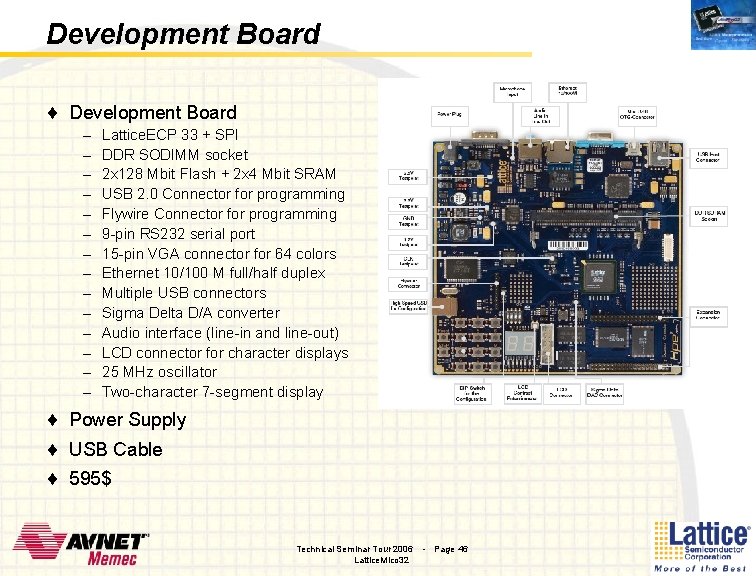

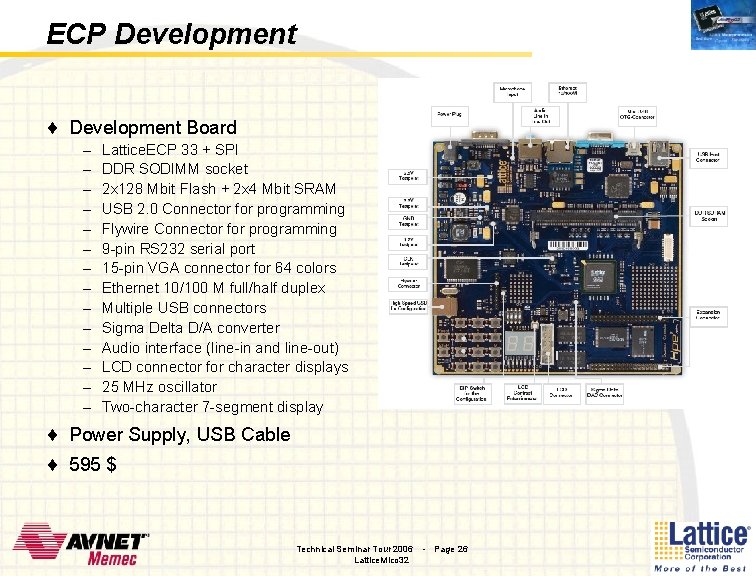

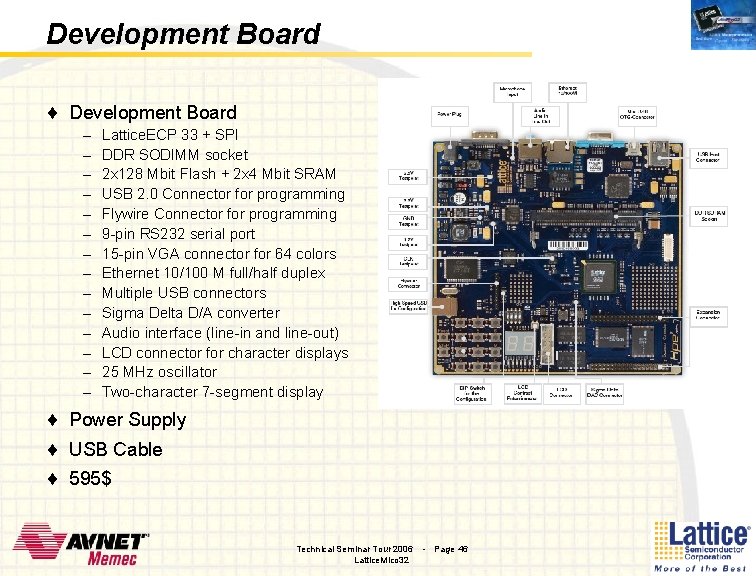

ECP Development ¨ Development Board – – – – Lattice. ECP 33 + SPI DDR SODIMM socket 2 x 128 Mbit Flash + 2 x 4 Mbit SRAM USB 2. 0 Connector for programming Flywire Connector for programming 9 -pin RS 232 serial port 15 -pin VGA connector for 64 colors Ethernet 10/100 M full/half duplex Multiple USB connectors Sigma Delta D/A converter Audio interface (line-in and line-out) LCD connector for character displays 25 MHz oscillator Two-character 7 -segment display ¨ Power Supply, USB Cable ¨ 595 $ Technical Seminar Tour 2006 Lattice. Mico 32 - Page 26

Software Deployment Deploying to ¨ External Parallel Flash Memory ¨ Embedded Block RAM (EBR) Alternatives: ¨ External Parallel Flash Memory = Config. Flash (needs a small CPLD) ¨ External SPI Flash (coming soon) Technical Seminar Tour 2006 Lattice. Mico 32 - Page 27

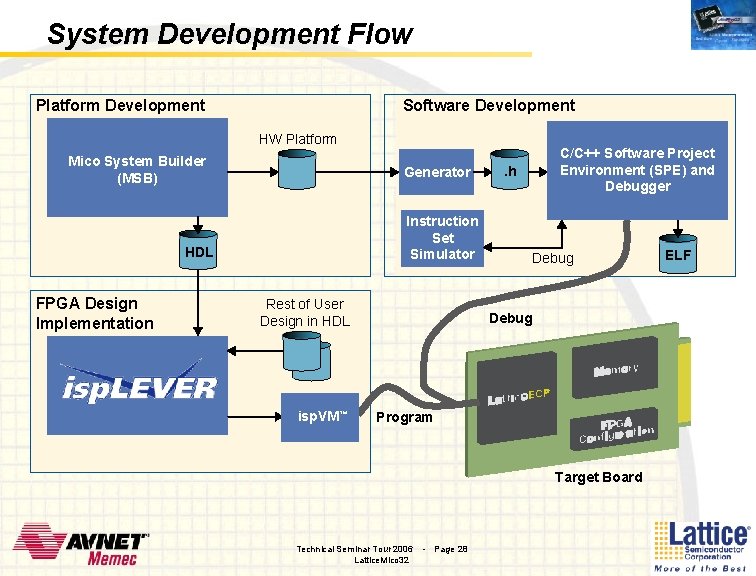

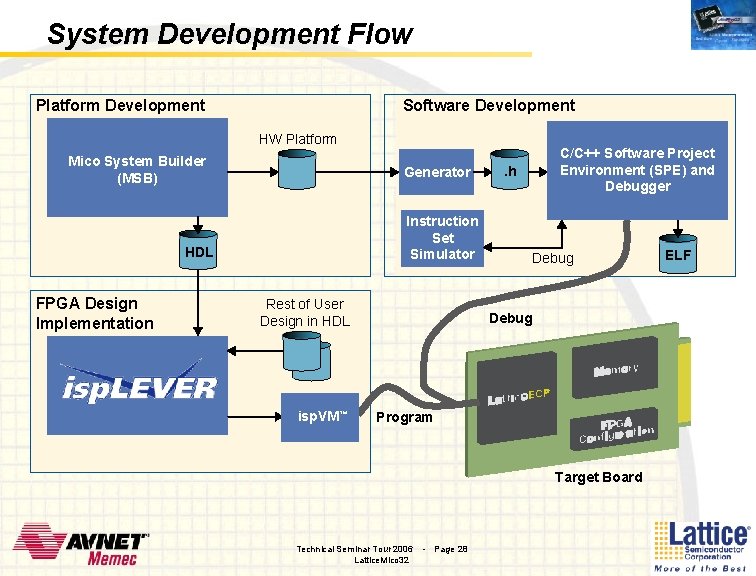

System Development Flow Platform Development Software Development HW Platform Mico System Builder (MSB) Generator Instruction Set Simulator HDL FPGA Design Implementation . h Rest of User Design in HDL isp. VM™ C/C++ Software Project Environment (SPE) and Debugger Debug Program Target Board Technical Seminar Tour 2006 Lattice. Mico 32 - Page 28 ELF

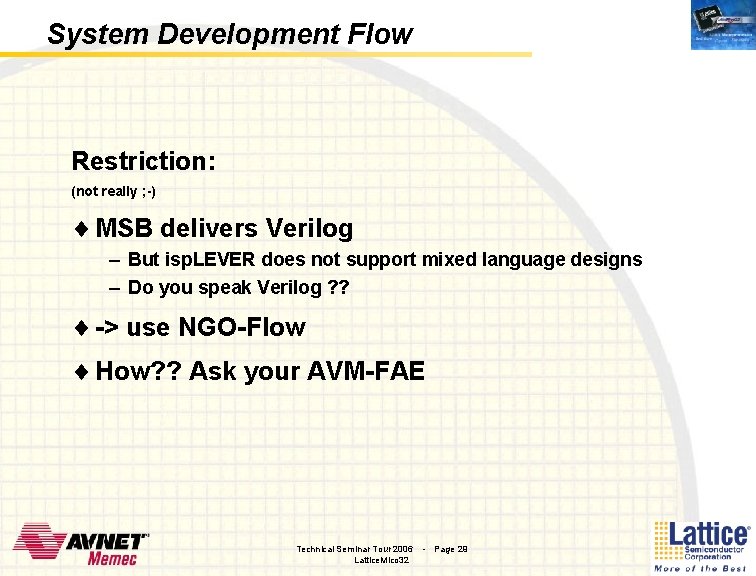

System Development Flow Restriction: (not really ; -) ¨ MSB delivers Verilog – But isp. LEVER does not support mixed language designs – Do you speak Verilog ? ? ¨ -> use NGO-Flow ¨ How? ? Ask your AVM-FAE Technical Seminar Tour 2006 Lattice. Mico 32 - Page 29

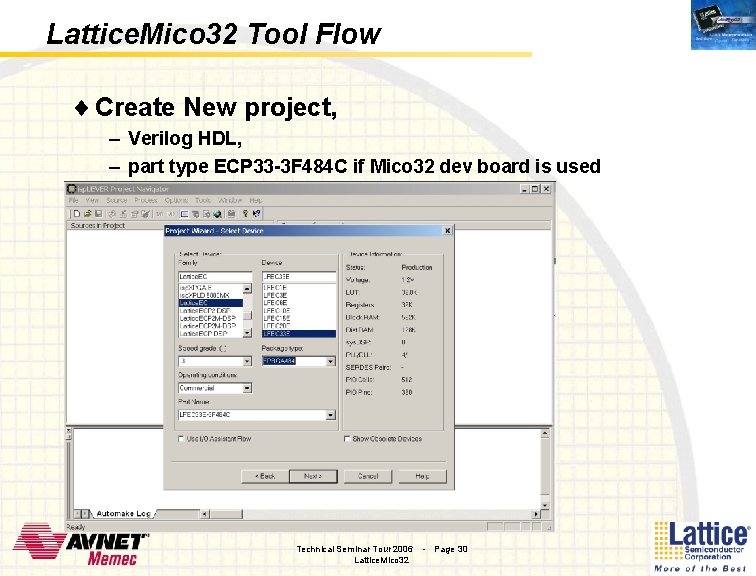

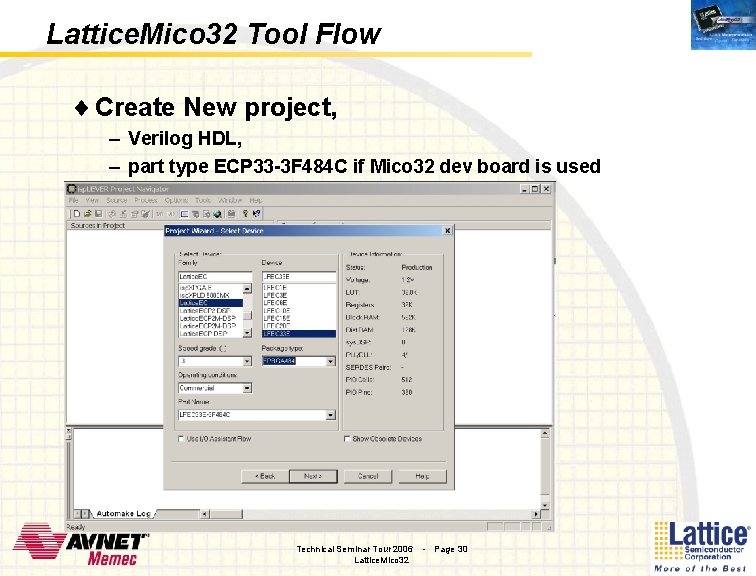

Lattice. Mico 32 Tool Flow ¨ Create New project, – Verilog HDL, – part type ECP 33 -3 F 484 C if Mico 32 dev board is used Technical Seminar Tour 2006 Lattice. Mico 32 - Page 30

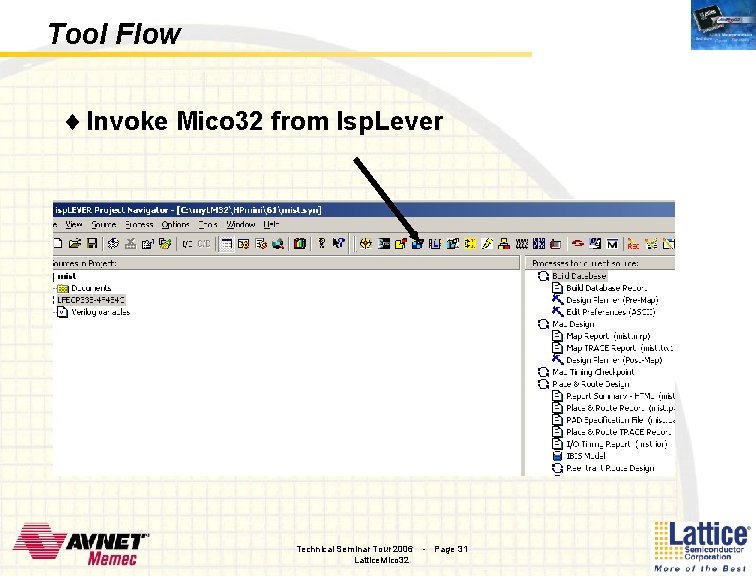

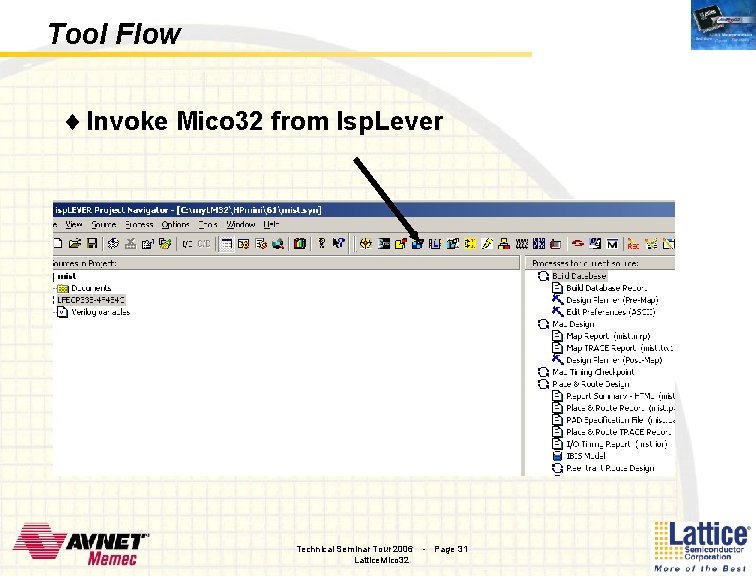

Tool Flow ¨ Invoke Mico 32 from Isp. Lever Technical Seminar Tour 2006 Lattice. Mico 32 - Page 31

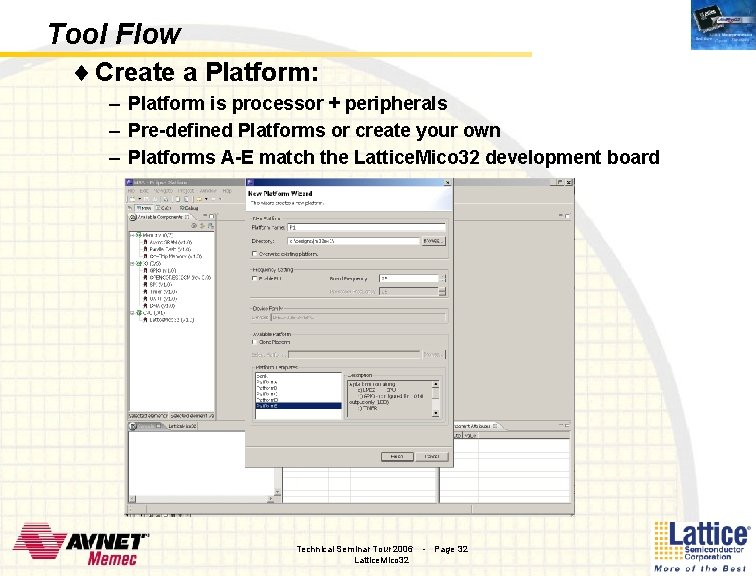

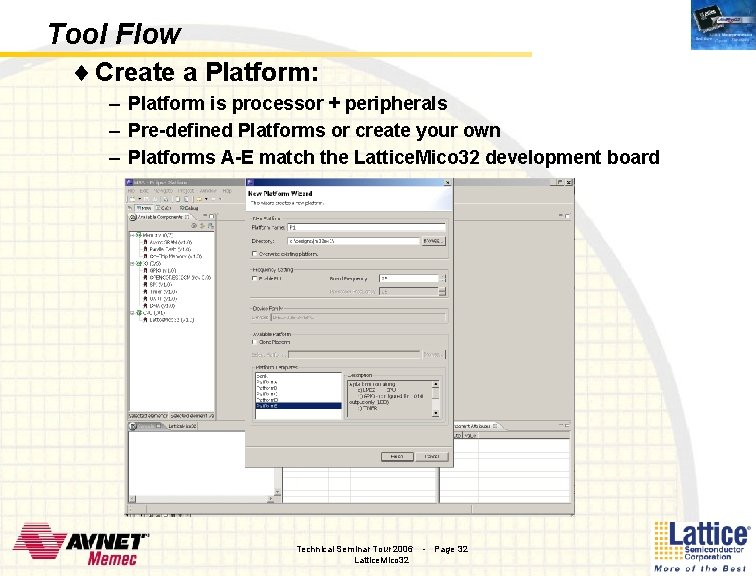

Tool Flow ¨ Create a Platform: – Platform is processor + peripherals – Pre-defined Platforms or create your own – Platforms A-E match the Lattice. Mico 32 development board Technical Seminar Tour 2006 Lattice. Mico 32 - Page 32

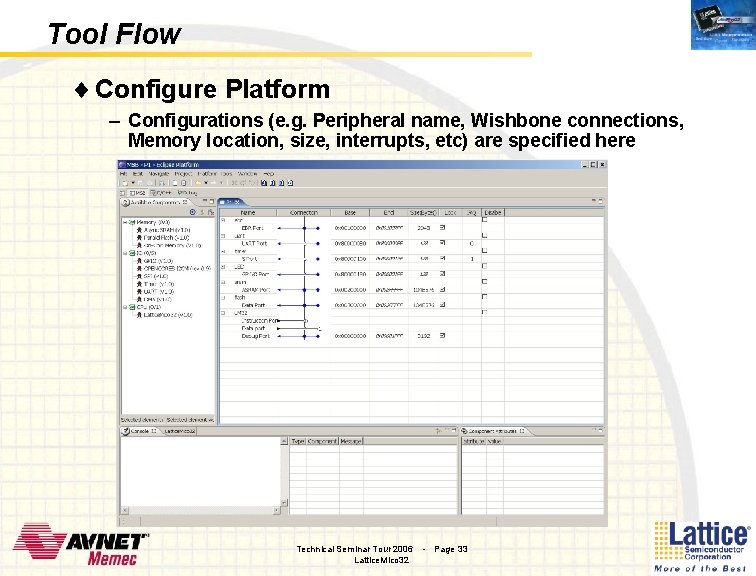

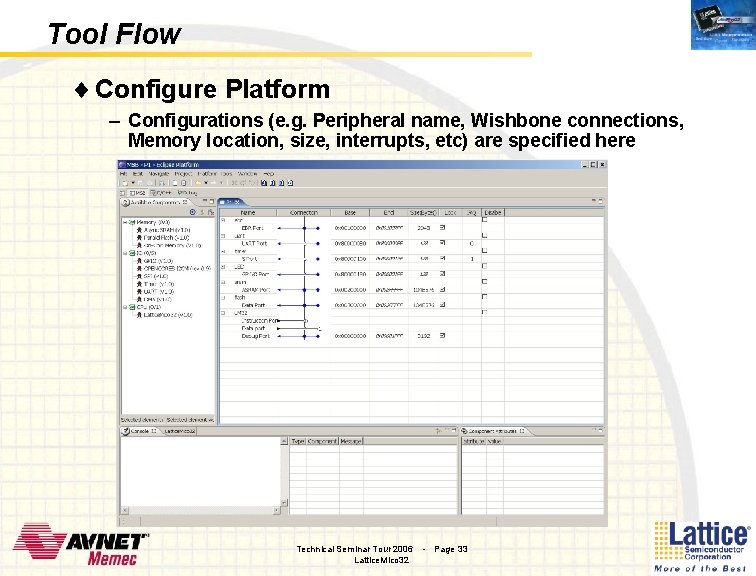

Tool Flow ¨ Configure Platform – Configurations (e. g. Peripheral name, Wishbone connections, Memory location, size, interrupts, etc) are specified here Technical Seminar Tour 2006 Lattice. Mico 32 - Page 33

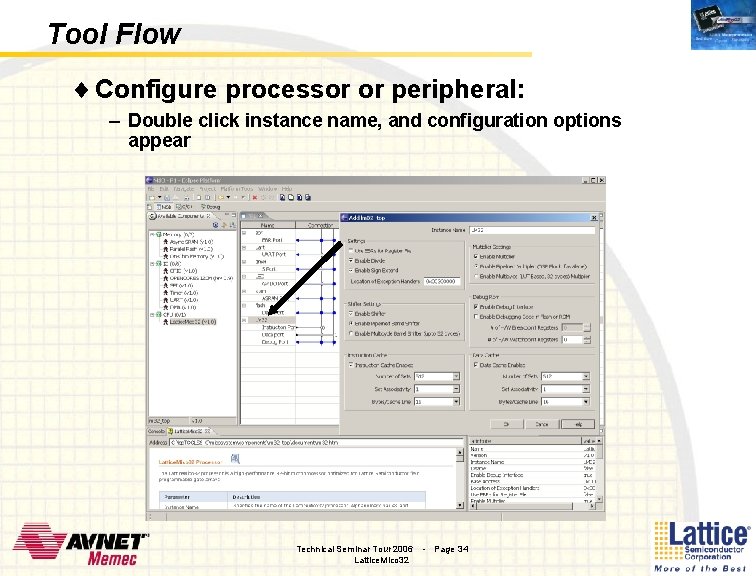

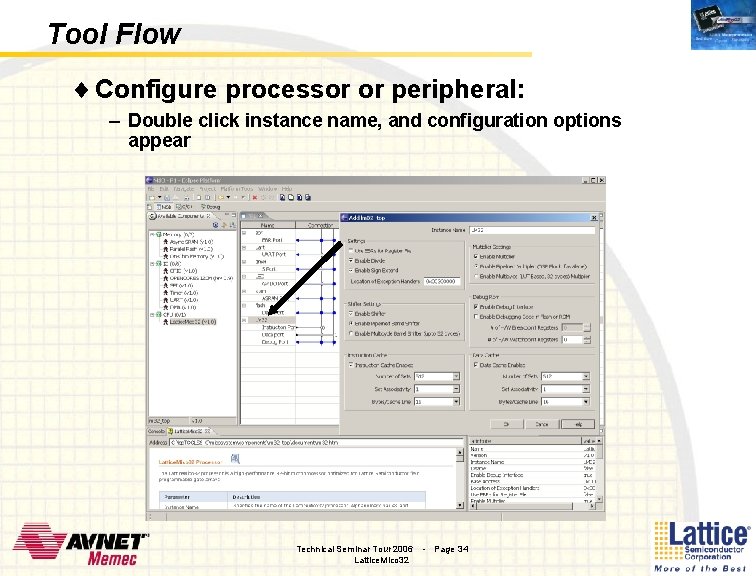

Tool Flow ¨ Configure processor or peripheral: – Double click instance name, and configuration options appear Technical Seminar Tour 2006 Lattice. Mico 32 - Page 34

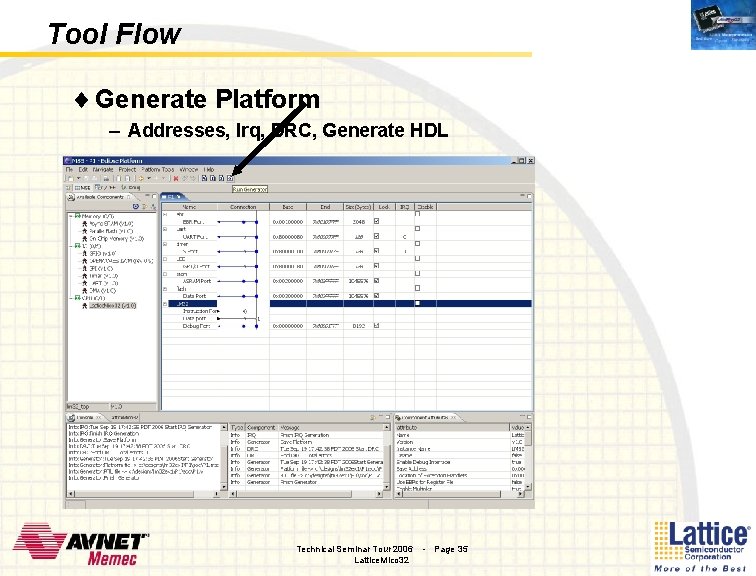

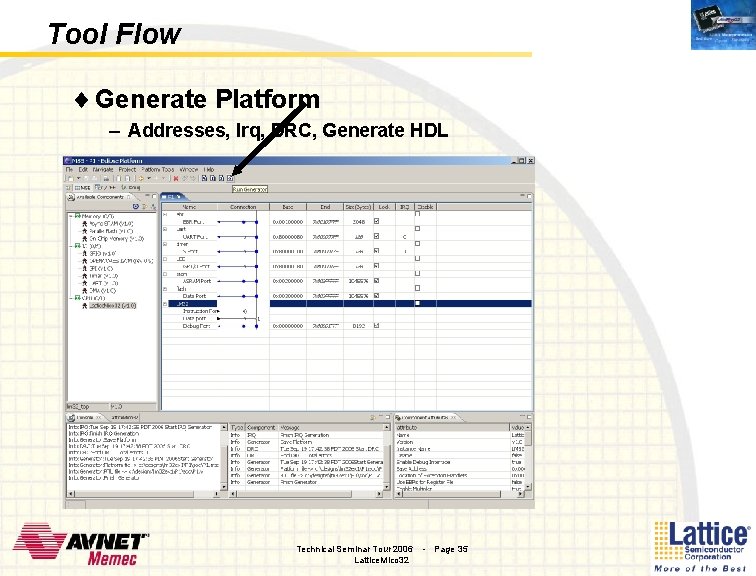

Tool Flow ¨ Generate Platform – Addresses, Irq, DRC, Generate HDL Technical Seminar Tour 2006 Lattice. Mico 32 - Page 35

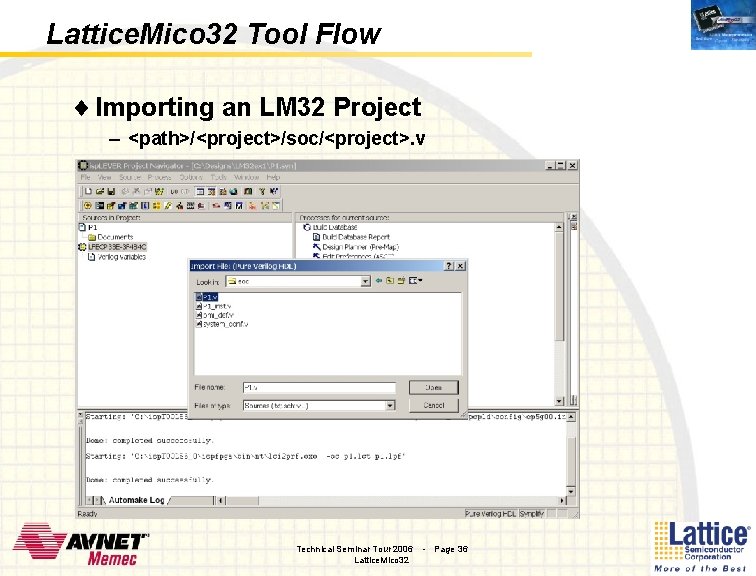

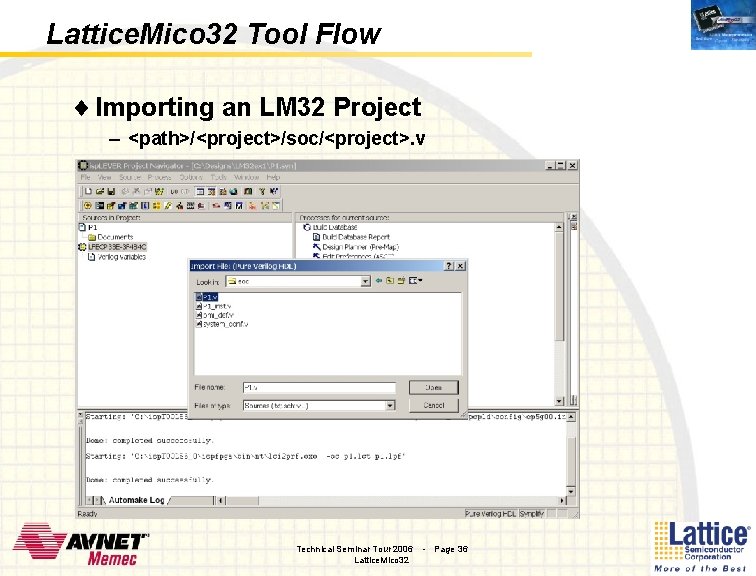

Lattice. Mico 32 Tool Flow ¨ Importing an LM 32 Project – <path>/<project>/soc/<project>. v – Technical Seminar Tour 2006 Lattice. Mico 32 - Page 36

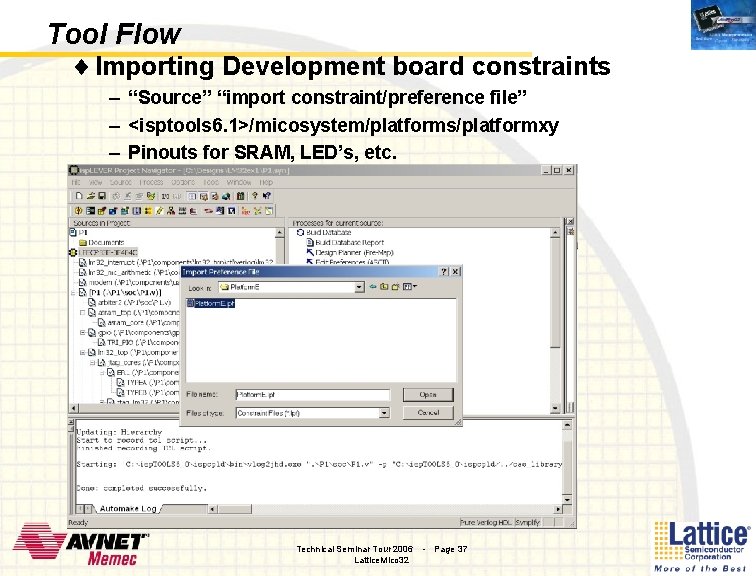

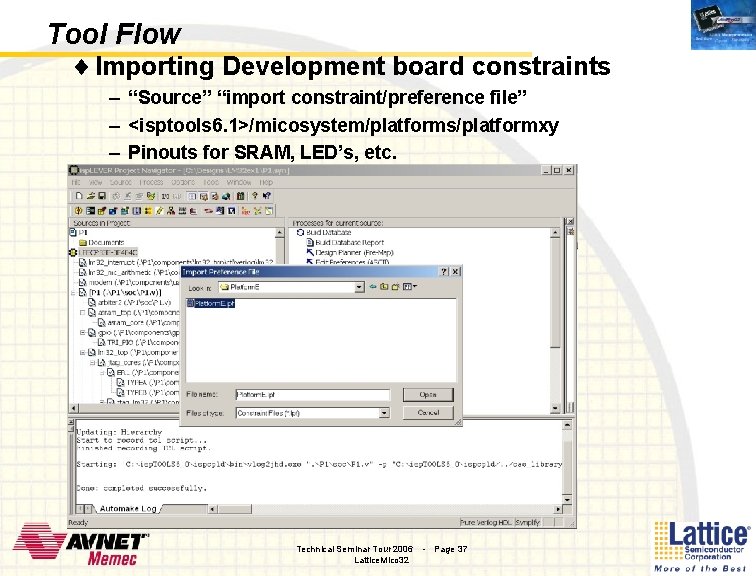

Tool Flow ¨ Importing Development board constraints – “Source” “import constraint/preference file” – <isptools 6. 1>/micosystem/platforms/platformxy – Pinouts for SRAM, LED’s, etc. Technical Seminar Tour 2006 Lattice. Mico 32 - Page 37

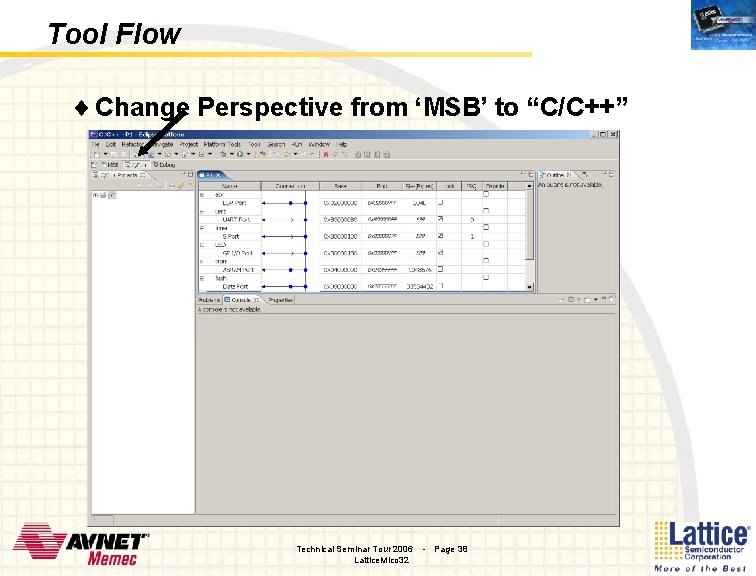

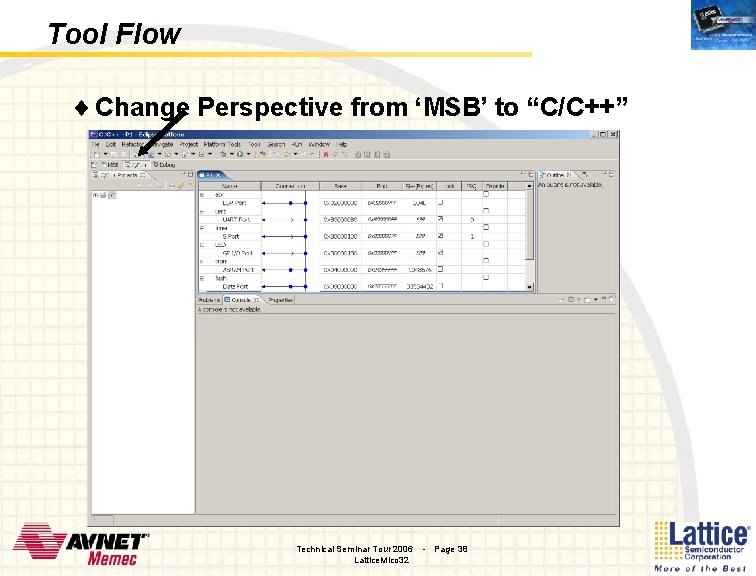

Tool Flow ¨ Change Perspective from ‘MSB’ to “C/C++” – Technical Seminar Tour 2006 Lattice. Mico 32 - Page 38

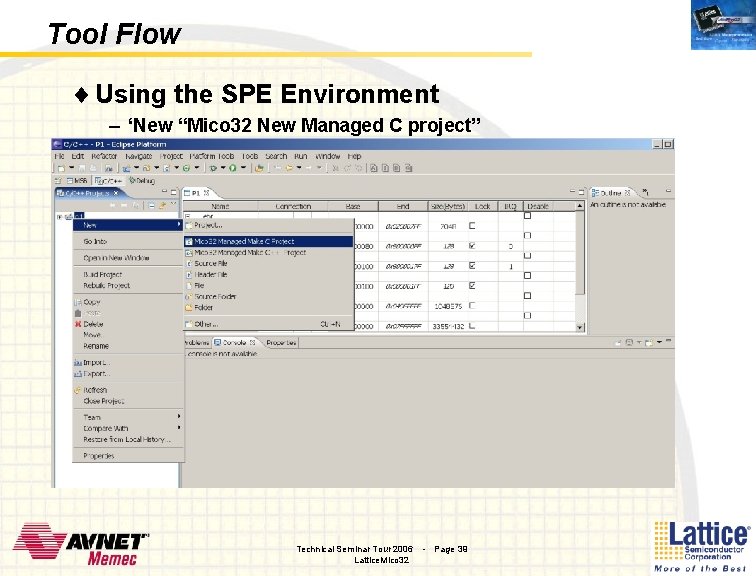

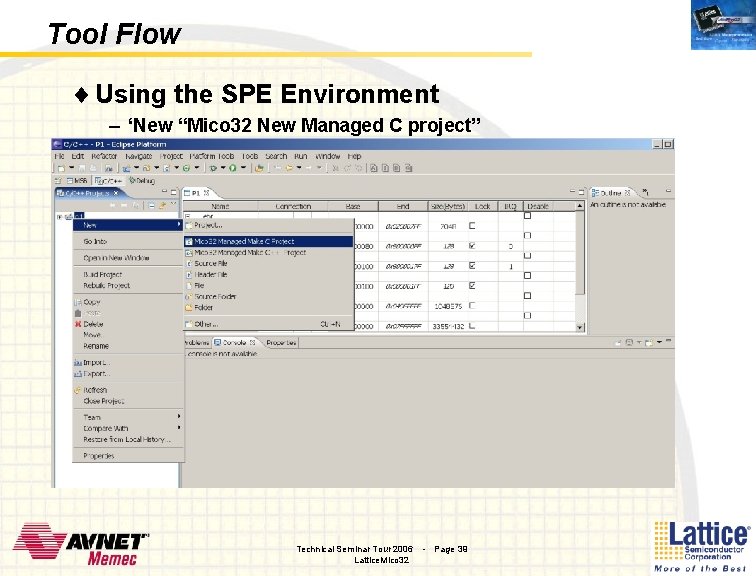

Tool Flow ¨ Using the SPE Environment – ‘New “Mico 32 New Managed C project” – Technical Seminar Tour 2006 Lattice. Mico 32 - Page 39

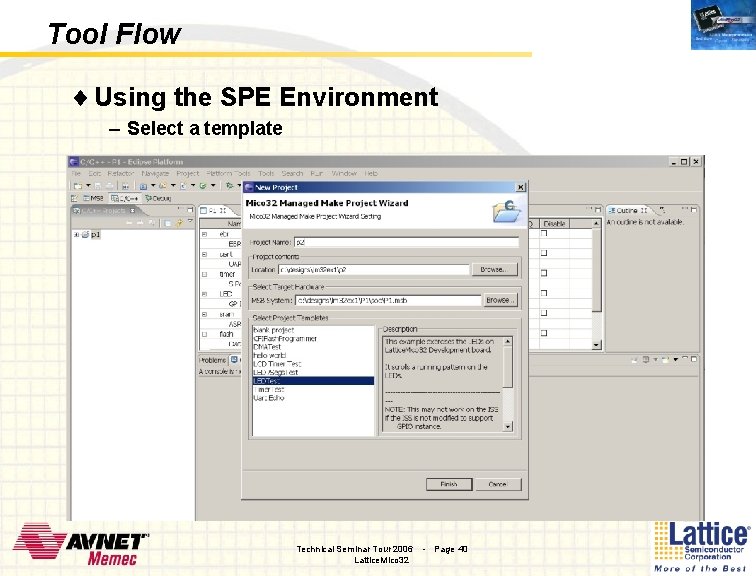

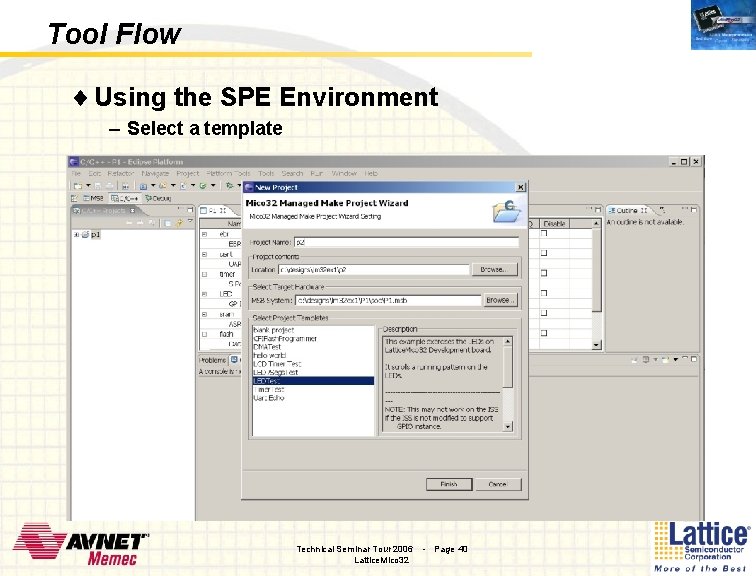

Tool Flow ¨ Using the SPE Environment – Select a template Technical Seminar Tour 2006 Lattice. Mico 32 - Page 40

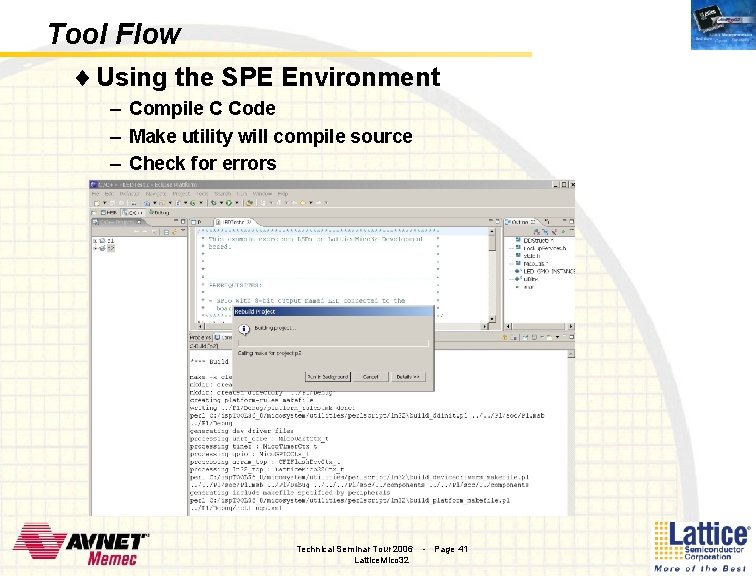

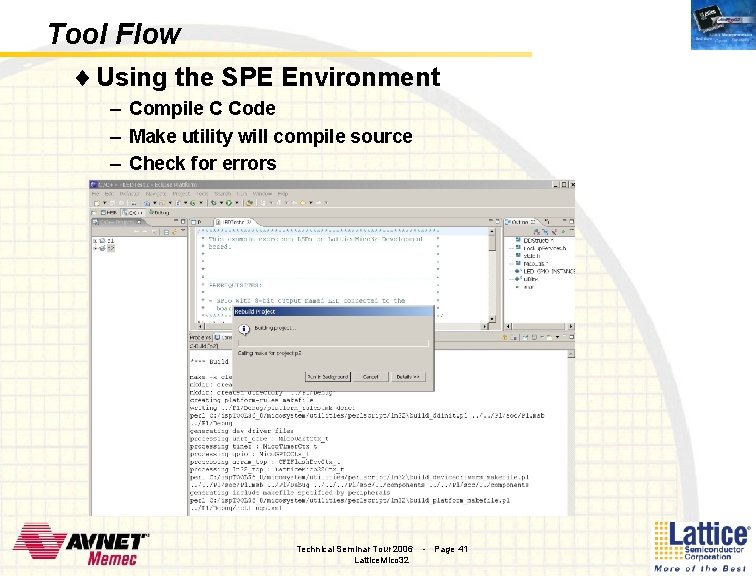

Tool Flow ¨ Using the SPE Environment – Compile C Code – Make utility will compile source – Check for errors Technical Seminar Tour 2006 Lattice. Mico 32 - Page 41

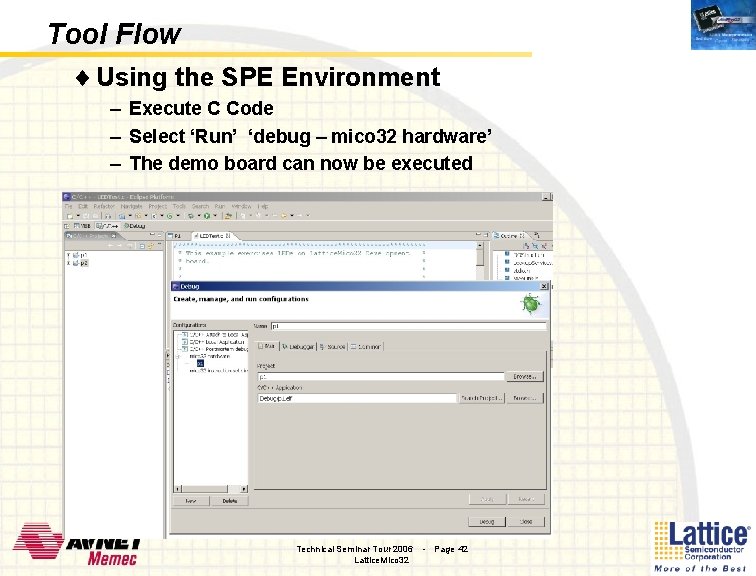

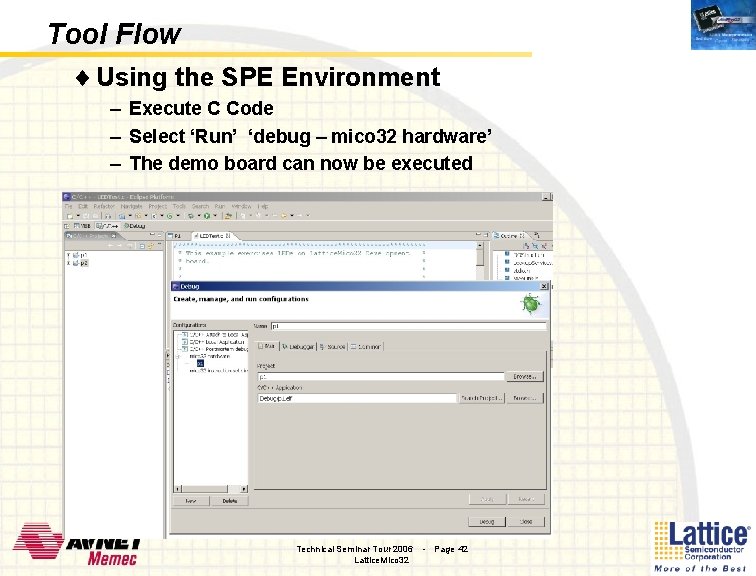

Tool Flow ¨ Using the SPE Environment – Execute C Code – Select ‘Run’ ‘debug – mico 32 hardware’ – The demo board can now be executed Technical Seminar Tour 2006 Lattice. Mico 32 - Page 42

Lattice. Mico 32 Website http: //www. latticesemi. com/products/intellectualproperty/ipcores/latticemico 32. cfm Technical Seminar Tour 2006 Lattice. Mico 32 - Page 43

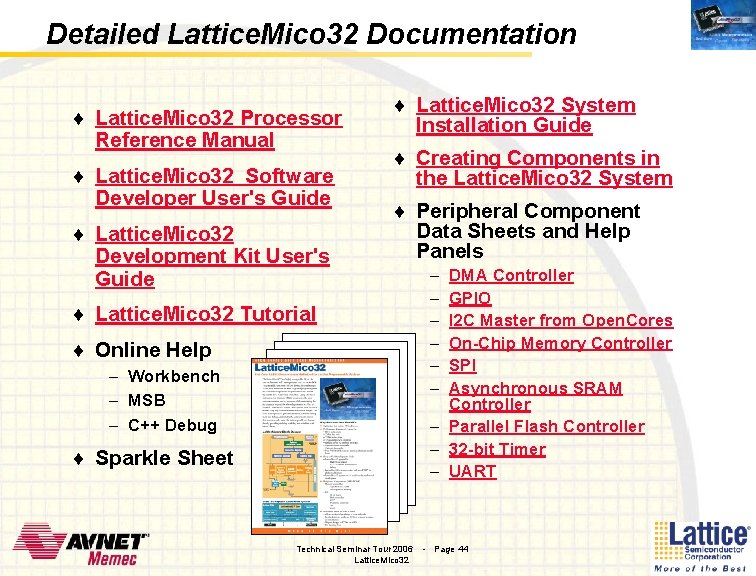

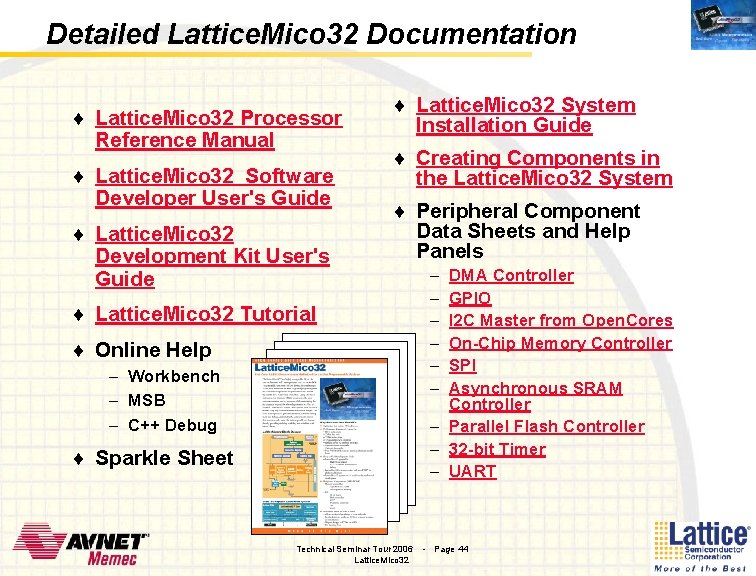

Detailed Lattice. Mico 32 Documentation ¨ Lattice. Mico 32 Processor Reference Manual ¨ Lattice. Mico 32 Software Developer User's Guide ¨ Lattice. Mico 32 Development Kit User's Guide ¨ Lattice. Mico 32 System Installation Guide ¨ Creating Components in the Lattice. Mico 32 System ¨ Peripheral Component Data Sheets and Help Panels ¨ Lattice. Mico 32 Tutorial ¨ Online Help – Workbench – MSB – C++ Debug ¨ Sparkle Sheet Technical Seminar Tour 2006 Lattice. Mico 32 – – – DMA Controller GPIO I 2 C Master from Open. Cores On-Chip Memory Controller SPI Asynchronous SRAM Controller – Parallel Flash Controller – 32 -bit Timer – UART - Page 44

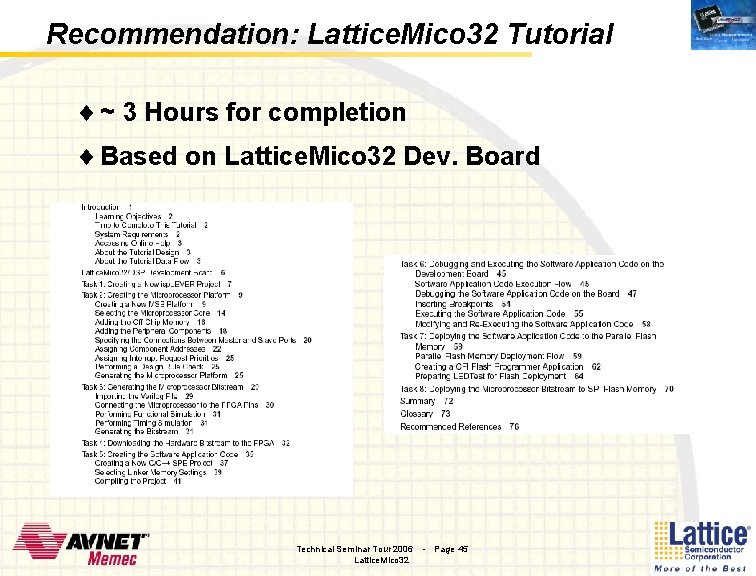

Recommendation: Lattice. Mico 32 Tutorial ¨ ~ 3 Hours for completion ¨ Based on Lattice. Mico 32 Dev. Board Technical Seminar Tour 2006 Lattice. Mico 32 - Page 45

Development Board ¨ Development Board – – – – Lattice. ECP 33 + SPI DDR SODIMM socket 2 x 128 Mbit Flash + 2 x 4 Mbit SRAM USB 2. 0 Connector for programming Flywire Connector for programming 9 -pin RS 232 serial port 15 -pin VGA connector for 64 colors Ethernet 10/100 M full/half duplex Multiple USB connectors Sigma Delta D/A converter Audio interface (line-in and line-out) LCD connector for character displays 25 MHz oscillator Two-character 7 -segment display ¨ Power Supply ¨ USB Cable ¨ 595$ Technical Seminar Tour 2006 Lattice. Mico 32 - Page 46