EGR 2131 Unit 11 Registers and Counters Read

- Slides: 48

EGR 2131 Unit 11 Registers and Counters ¡ Read Brown & Vranesic, Sections 7. 8 to 7. 13 and Sections A. 10. 6 to A. 10. 9. Homework #11 and Lab #11 due next week. ¡ Quiz next week. ¡

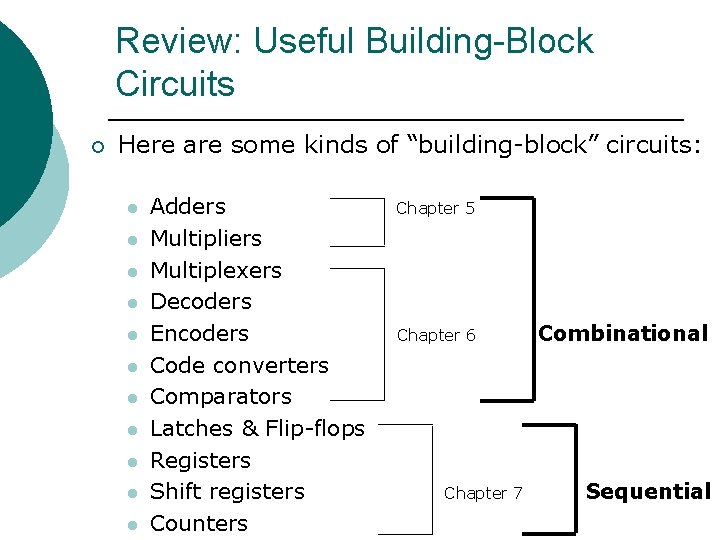

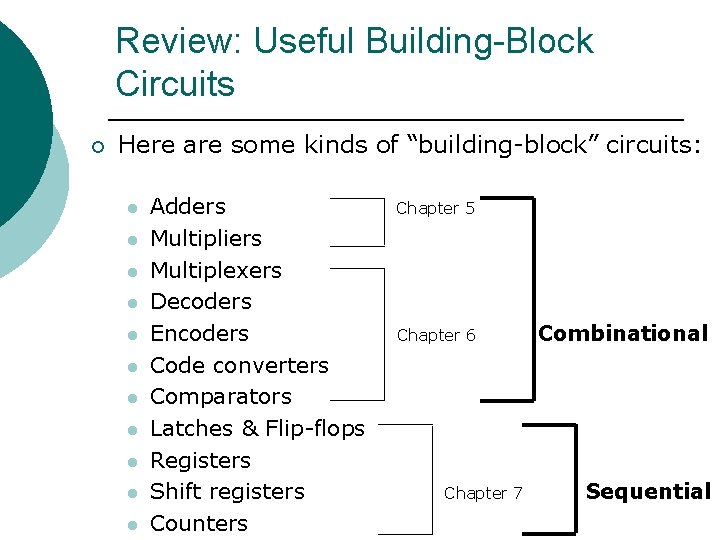

Review: Useful Building-Block Circuits ¡ Here are some kinds of “building-block” circuits: l l l Adders Multipliers Multiplexers Decoders Encoders Code converters Comparators Latches & Flip-flops Registers Shift registers Counters Chapter 5 Chapter 6 Chapter 7 Combinational Sequential

A Brief Detour: Contact Bounce Before looking at this unit’s main topics, the next eight slides discuss an equipment-related issue that we’ll have to deal with in the upcoming labs. ¡ The issue, which is a very common practical problem that you should be able to recognize and address, is called contact bounce. ¡ l Contact bounce is not discussed in the textbook.

Contact Bounce ¡ ¡ ¡ Although it’s not obvious to us in everyday life, most mechanical switches suffer from contact bounce. When you flip the switch lever, the contacts inside the switch repeatedly bounce open and closed for a short time ( 50 ms). This can lead to problems in digital circuits, particularly in circuits that keep track of how many times a switch was flipped.

Contact Bounce: An Illustration ¡ ¡ You may recall that we ran into this problem in Lab 3. Open your Quartus project named Lab 3 Counter, download it to the DE 2115 board, and note that the count on the green LEDs sometimes increases by more than one for a single press on the KEY 3 pushbutton.

Ways to Solve Contact Bounce ¡ ¡ There are several standard ways to debounce a switch. In hardware, one standard solution uses a latch or flip-flop. Another uses an RC circuit with a Schmitt-trigger gate. (Good discussion at http: //www. ganssle. com/debouncing-pt 2. htm. ) ¡ Debouncing can also be done in software by checking the input at wellspaced time intervals, and only accepting a value if it is steady for some time.

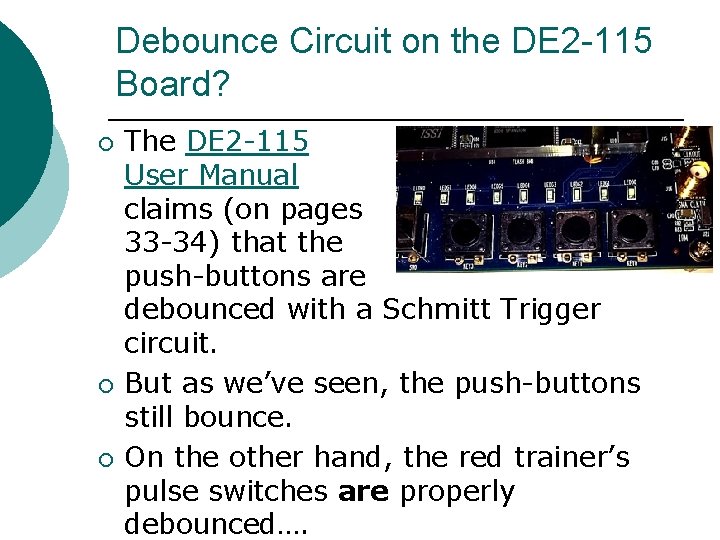

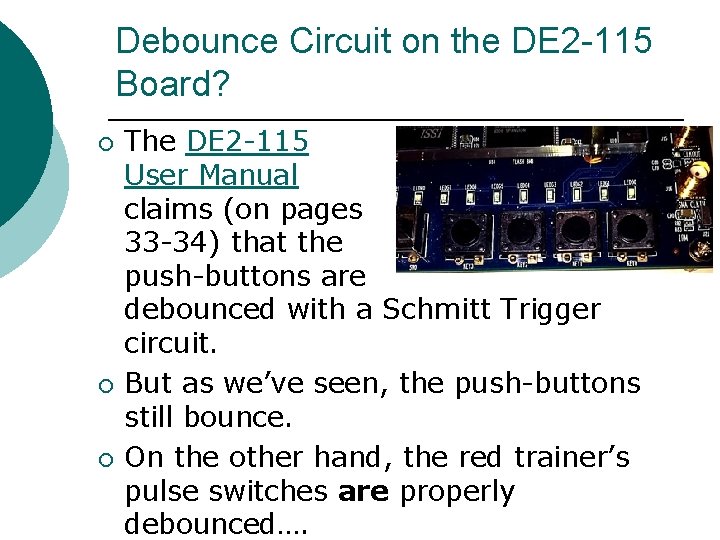

Debounce Circuit on the DE 2 -115 Board? ¡ ¡ ¡ The DE 2 -115 User Manual claims (on pages 33 -34) that the push-buttons are debounced with a Schmitt Trigger circuit. But as we’ve seen, the push-buttons still bounce. On the other hand, the red trainer’s pulse switches are properly debounced….

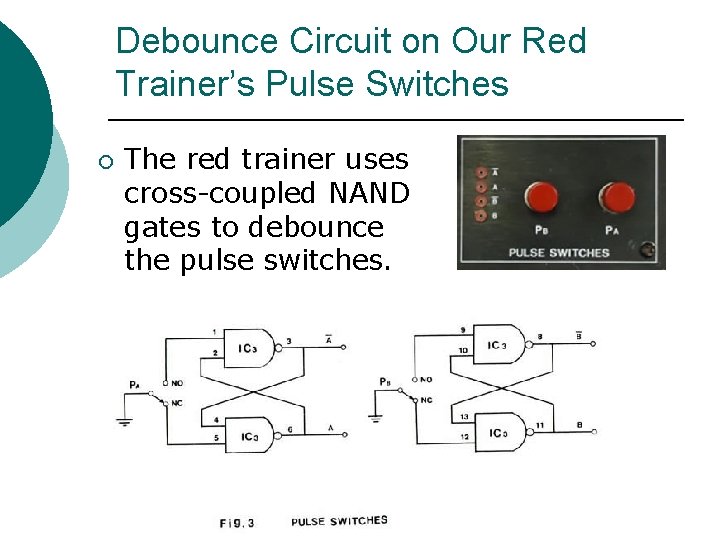

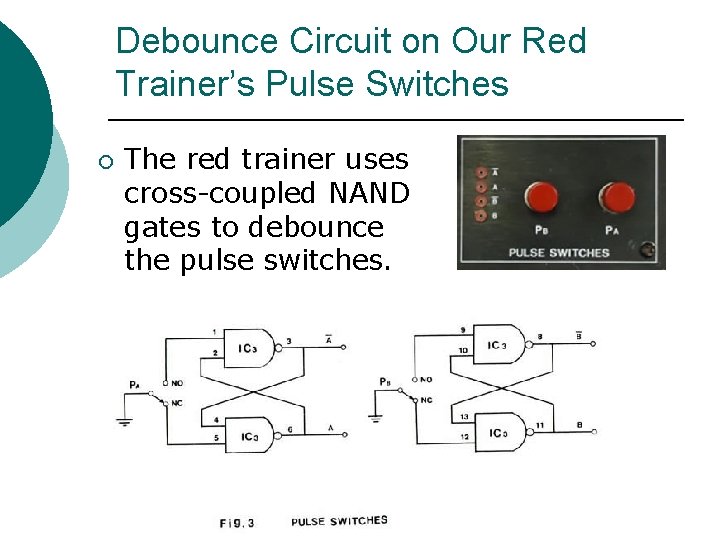

Debounce Circuit on Our Red Trainer’s Pulse Switches ¡ The red trainer uses cross-coupled NAND gates to debounce the pulse switches.

A Debounce Solution ¡ ¡ A page on Digi-Key’s website describes a debouncer circuit (and equivalent VHDL code) that you can build in Quartus. We’ll be able to understand this circuit in another week or two. But for now, just download the. vhd and. bsf files from the course’s Unit 11 webpage, and insert the. bsf file into any schematic diagram that requires debouncing.

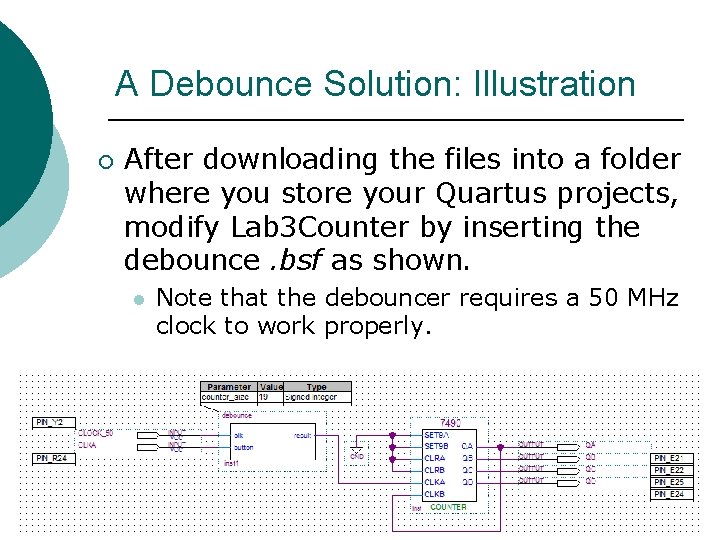

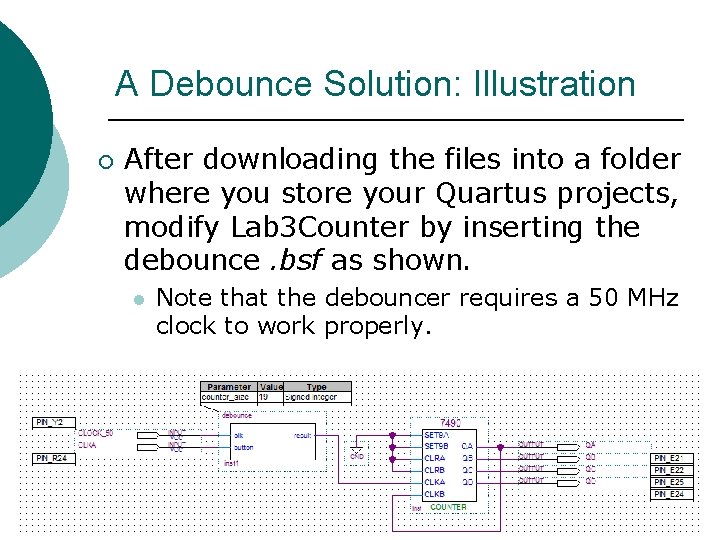

A Debounce Solution: Illustration ¡ After downloading the files into a folder where you store your Quartus projects, modify Lab 3 Counter by inserting the debounce. bsf as shown. l Note that the debouncer requires a 50 MHz clock to work properly.

Going Forward… ¡ ¡ Many of the circuits that you’ll build in the coming weeks use a push-button to clock a circuit. You should get into the habit of inserting debounce. bsf into these circuits to debounce the clock, even if the written directions don’t tell you to do this. Now, on to the main topics of this unit….

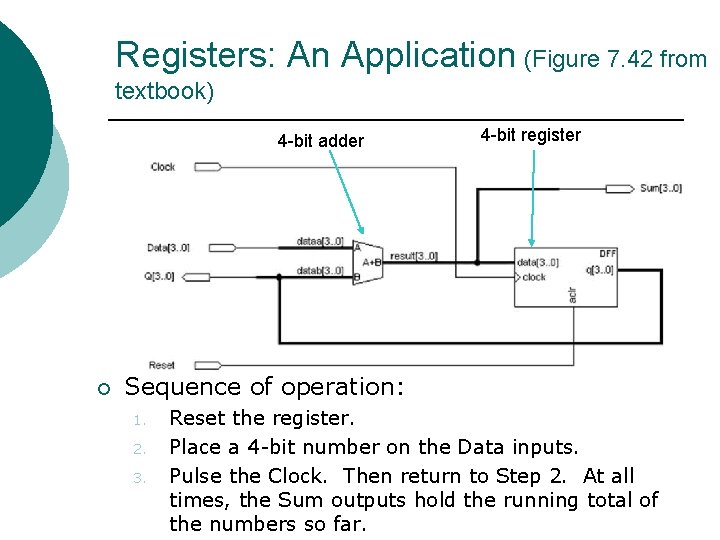

Registers Recall that a latch or flop-flop stores one bit of information. When a set of n flip-flops that share a clock are used to store n bits of information, such as an n-bit number, we call these flipflops a register. ¡ The next slide shows a good application, which you’ll build in lab. It’s an adder with registered feedback that sequentially adds a list of numbers, one at a time. ¡

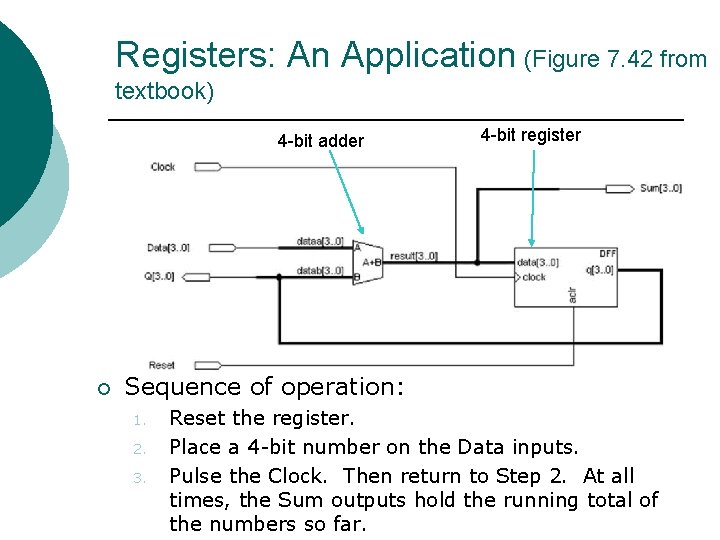

Registers: An Application (Figure 7. 42 from textbook) 4 -bit adder ¡ 4 -bit register Sequence of operation: 1. 2. 3. Reset the register. Place a 4 -bit number on the Data inputs. Pulse the Clock. Then return to Step 2. At all times, the Sum outputs hold the running total of the numbers so far.

Asynchronous versus Synchronous Inputs When working with clocked circuits such as registers and counters, we must pay attention to whether specific inputs are synchronous or asynchronous. ¡ For example, the register on the previous slide has an input labeled aclr, which stands for asynchronous clear. As soon as this input goes high, the register is cleared. ¡

Asynchronous versus Synchronous Inputs (Cont’d. ) On the other hand, if that register had a synchronous clear input, then the register would not be cleared until the next active clock edge after the clear input goes high. ¡ Both kinds are useful, and we’ll see examples of circuits that have one or the other. ¡

Shift Registers Many registers provide the additional ability to shift their contents to the left or right, resulting in what we call a shift register. ¡ A common application of shift registers is conversion from serial format to parallel format, or vice versa. ¡

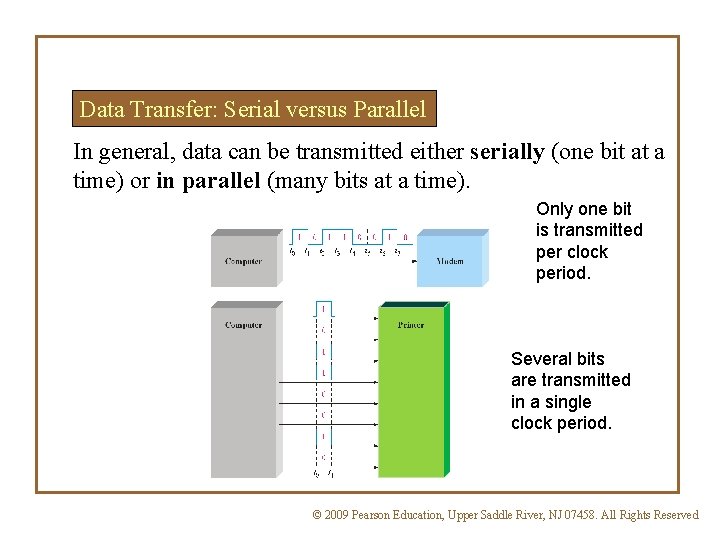

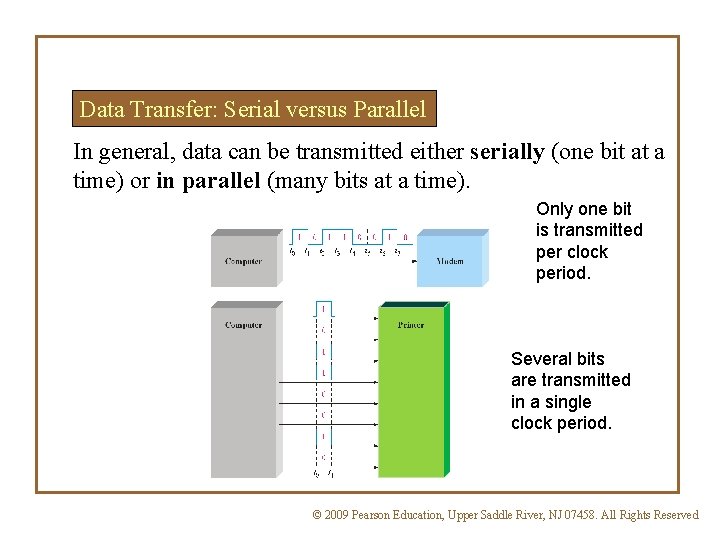

Data Transfer: Serial versus Parallel In general, data can be transmitted either serially (one bit at a time) or in parallel (many bits at a time). Only one bit is transmitted per clock period. Several bits are transmitted in a single clock period. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

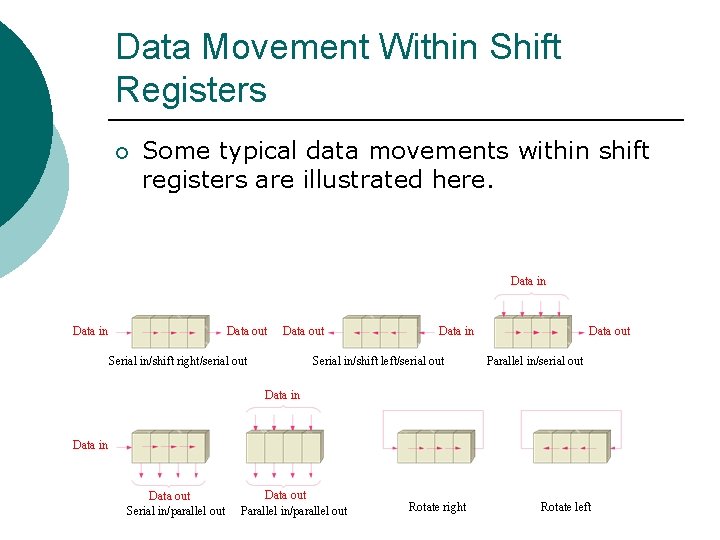

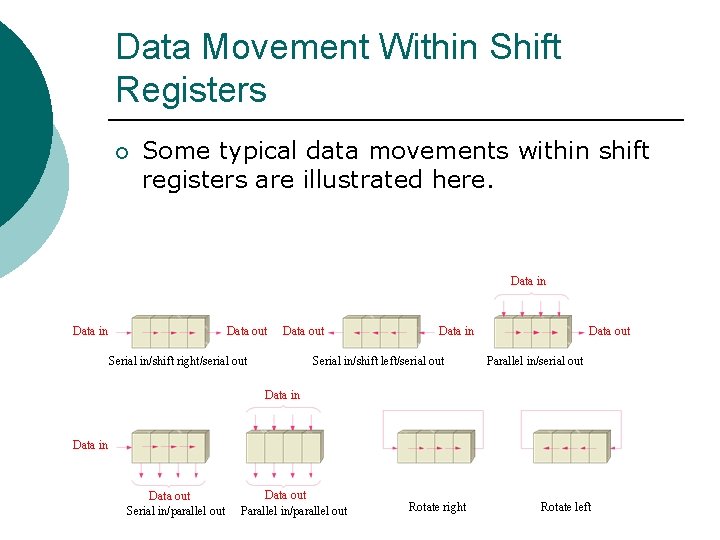

Data Movement Within Shift Registers ¡ Some typical data movements within shift registers are illustrated here. Data in Data out Serial in/shift right/serial out Data in Serial in/shift left/serial out Data out Parallel in/serial out Data in Data out Serial in/parallel out Data out Parallel in/parallel out Rotate right Rotate left

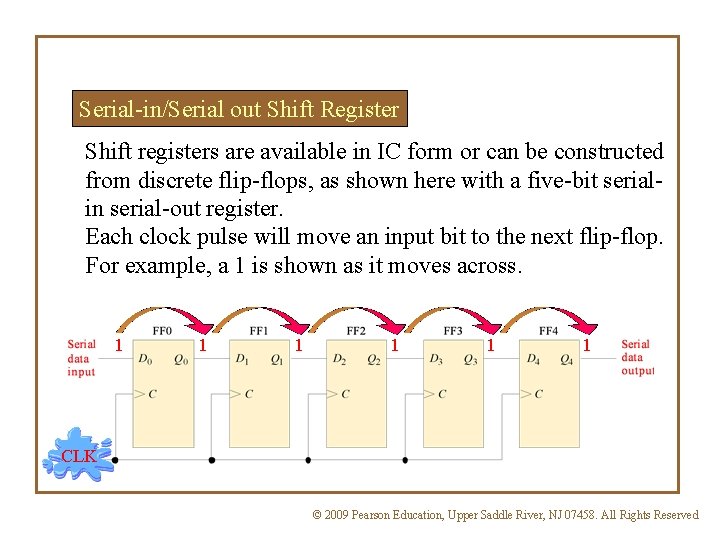

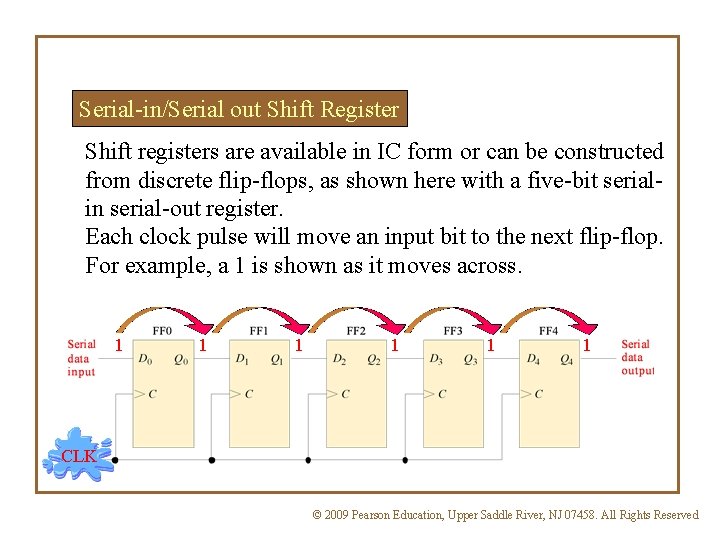

Serial-in/Serial out Shift Register Shift registers are available in IC form or can be constructed from discrete flip-flops, as shown here with a five-bit serialin serial-out register. Each clock pulse will move an input bit to the next flip-flop. For example, a 1 is shown as it moves across. 1 1 1 CLK © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

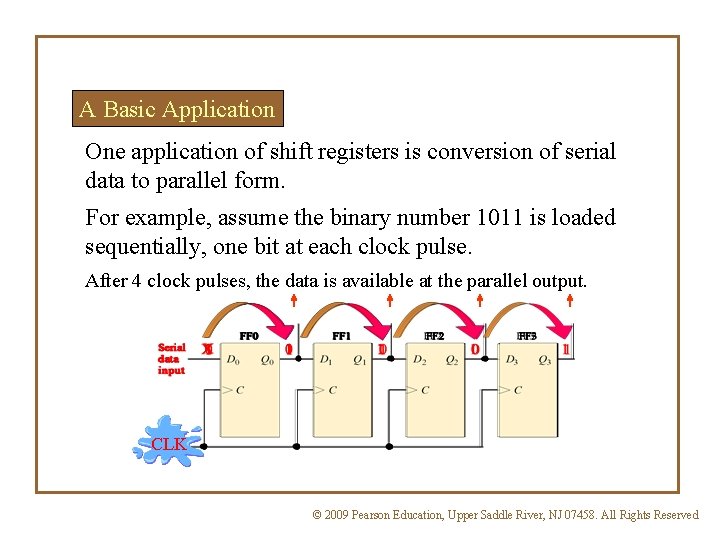

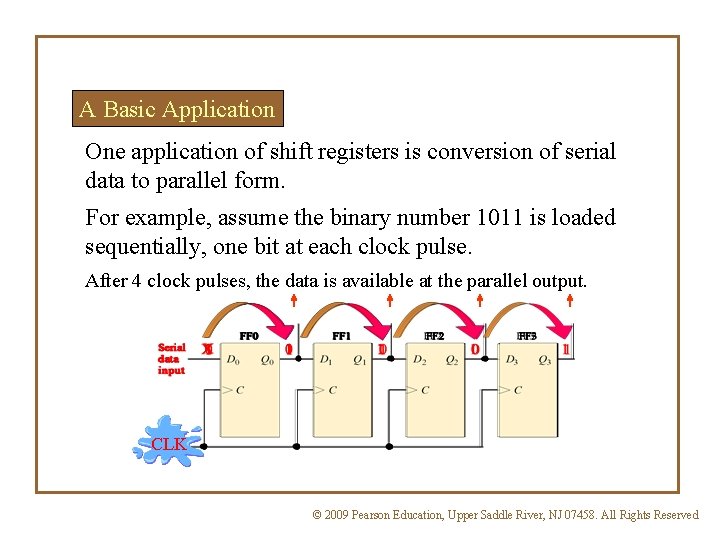

A Basic Application One application of shift registers is conversion of serial data to parallel form. For example, assume the binary number 1011 is loaded sequentially, one bit at each clock pulse. After 4 clock pulses, the data is available at the parallel output. CLK © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

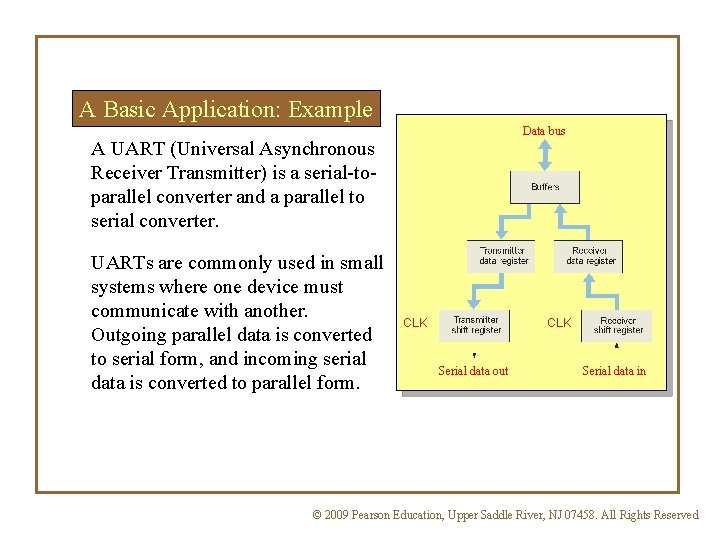

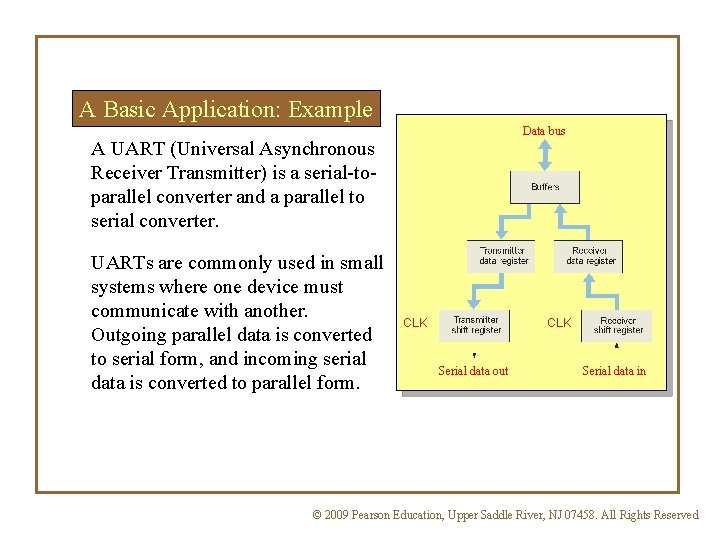

A Basic Application: Example Data bus A UART (Universal Asynchronous Receiver Transmitter) is a serial-toparallel converter and a parallel to serial converter. UARTs are commonly used in small systems where one device must communicate with another. Outgoing parallel data is converted to serial form, and incoming serial data is converted to parallel form. CLK Serial data out Serial data in © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

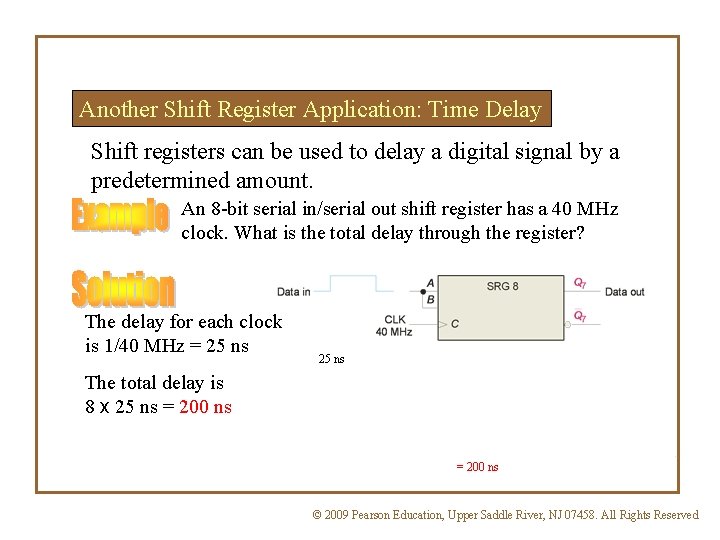

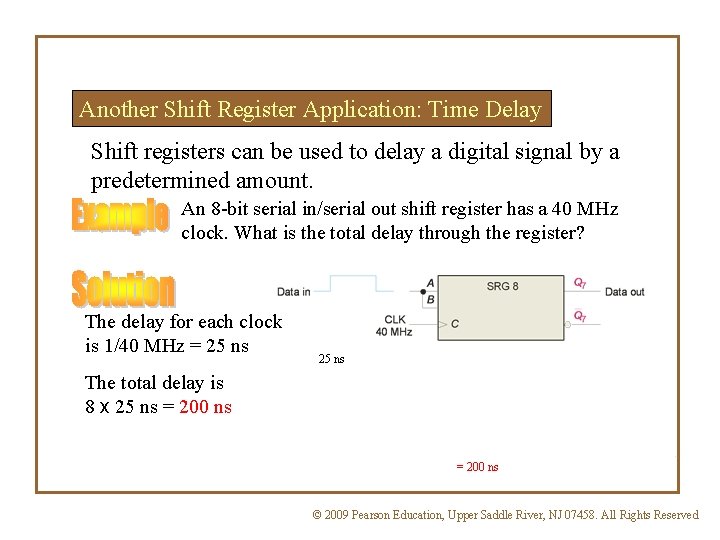

Another Shift Register Application: Time Delay Shift registers can be used to delay a digital signal by a predetermined amount. An 8 -bit serial in/serial out shift register has a 40 MHz clock. What is the total delay through the register? The delay for each clock is 1/40 MHz = 25 ns The total delay is 8 x 25 ns = 200 ns © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Some 74 xx Shift Register Chips ¡ 74164 (8 -bit serial-in/parallel-out) l ¡ 74165 (8 -bit parallel-in/serial-out) l ¡ Parallel Load is asynchronous. 74194 (4 -bit bidirectional universal) l l ¡ Clear is asynchronous. Parallel Load is synchronous. 74195 (4 -bit parallel access) l l Clear is asynchronous. Parallel Load is synchronous.

Registers and Shift Registers in Quartus ¡ Quartus gives you several ways to implement registers and shift registers: l Using schematic capture: Build registers out of individual flip-flops. ¡ Place virtual copies of 74 xx chips such as the 74164 or 74194. ¡ Place and configure customizable components from Quartus’ Library of Parameterized Modules: l lpm_ff for registers. l lpm_shiftreg for shift registers. ¡ l Using VHDL code.

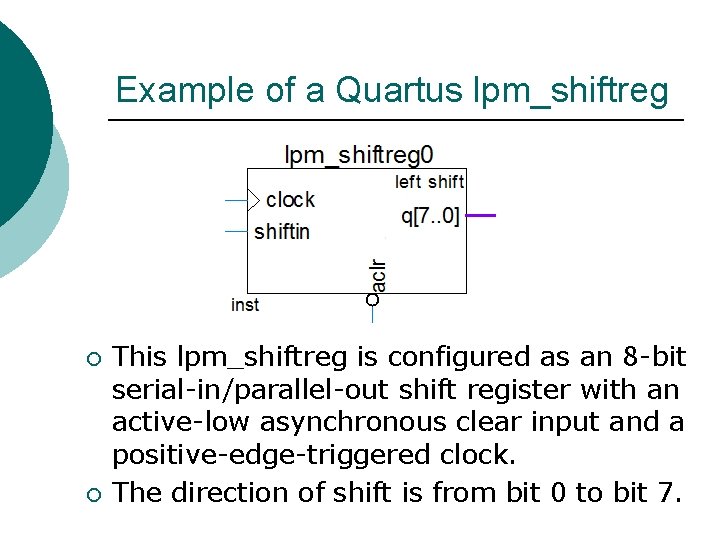

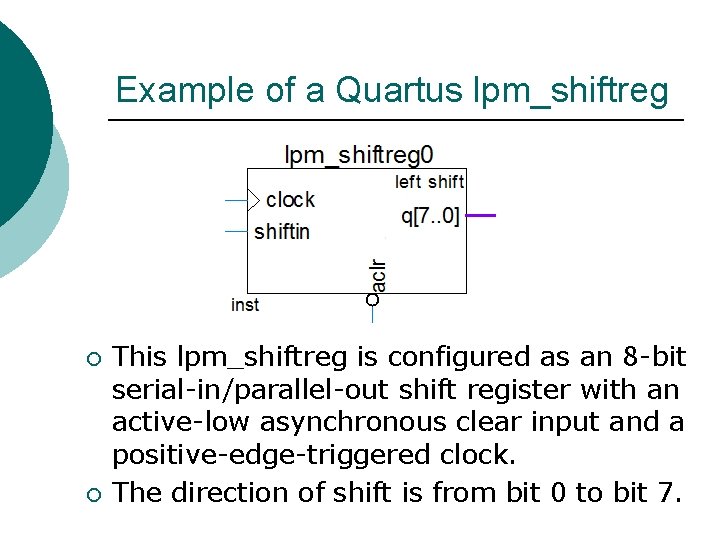

Example of a Quartus lpm_shiftreg ¡ ¡ This lpm_shiftreg is configured as an 8 -bit serial-in/parallel-out shift register with an active-low asynchronous clear input and a positive-edge-triggered clock. The direction of shift is from bit 0 to bit 7.

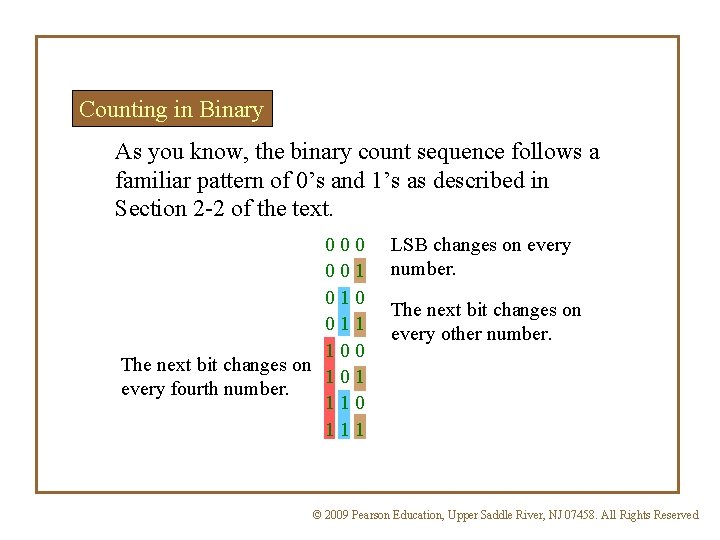

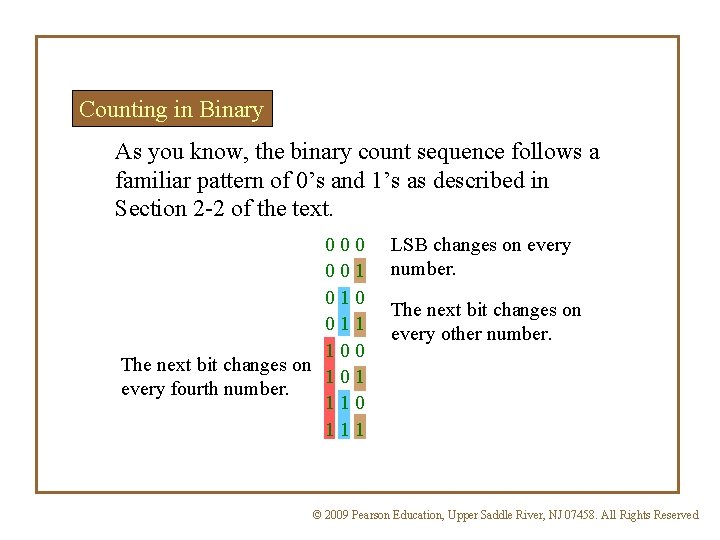

Counting in Binary As you know, the binary count sequence follows a familiar pattern of 0’s and 1’s as described in Section 2 -2 of the text. 000 001 010 011 100 The next bit changes on 101 every fourth number. 110 111 LSB changes on every number. The next bit changes on every other number. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

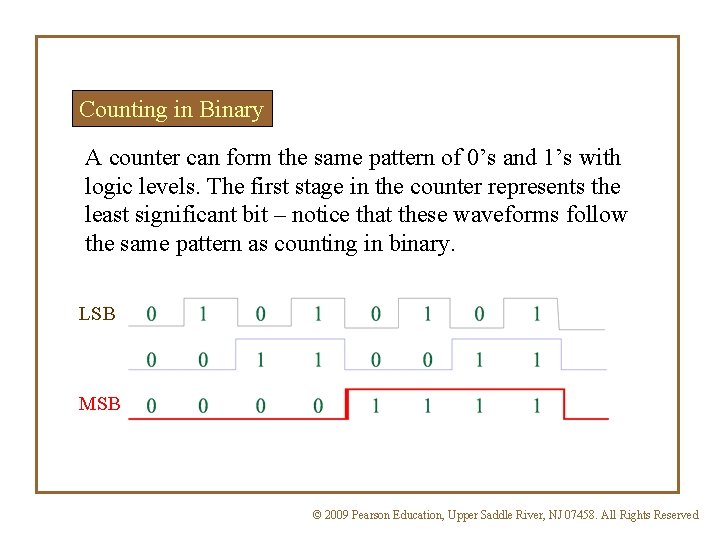

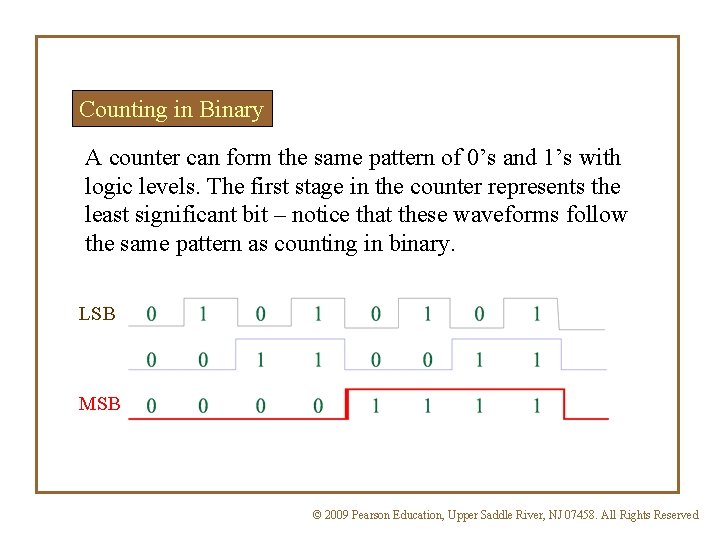

Counting in Binary A counter can form the same pattern of 0’s and 1’s with logic levels. The first stage in the counter represents the least significant bit – notice that these waveforms follow the same pattern as counting in binary. LSB MSB © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

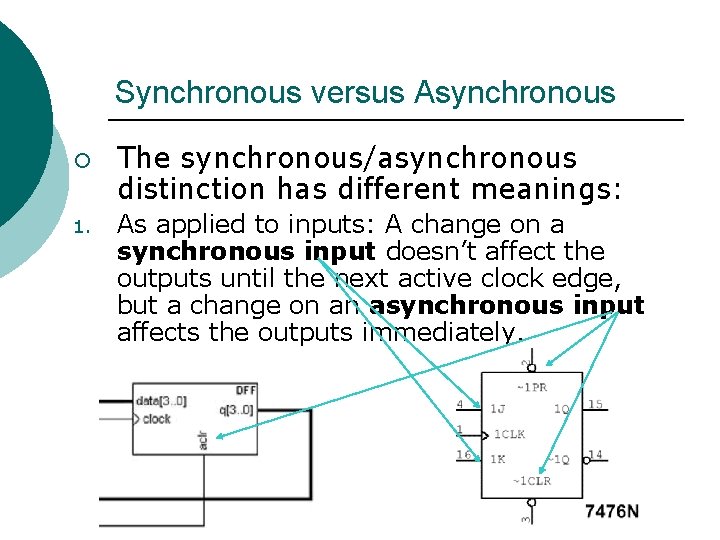

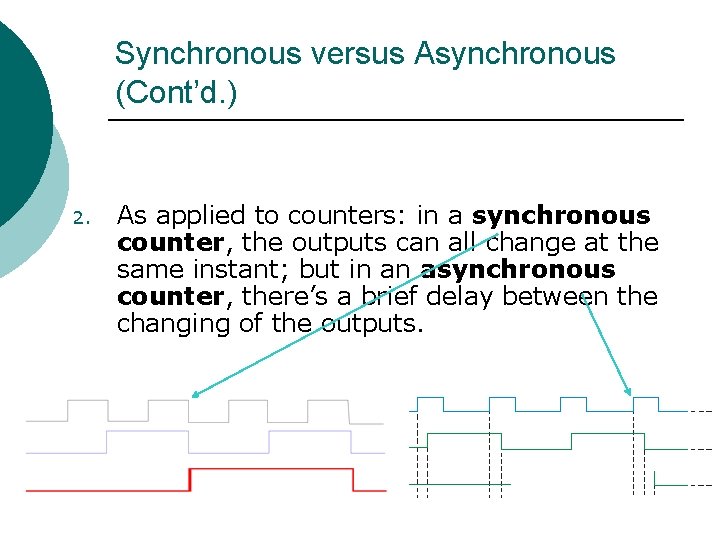

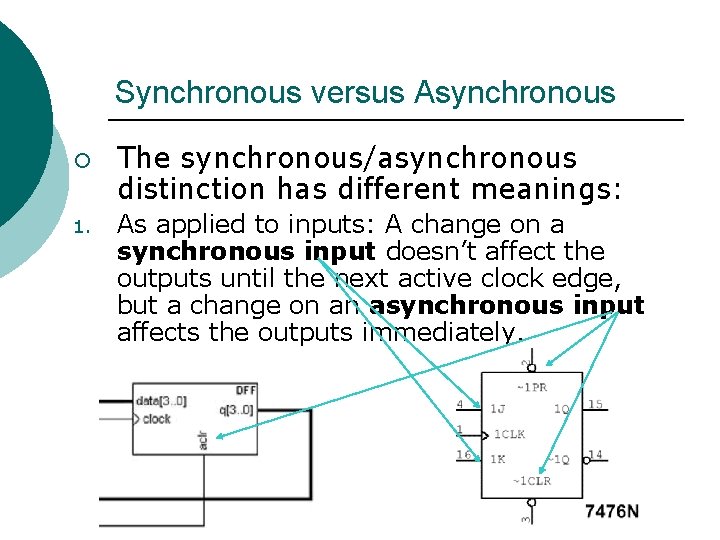

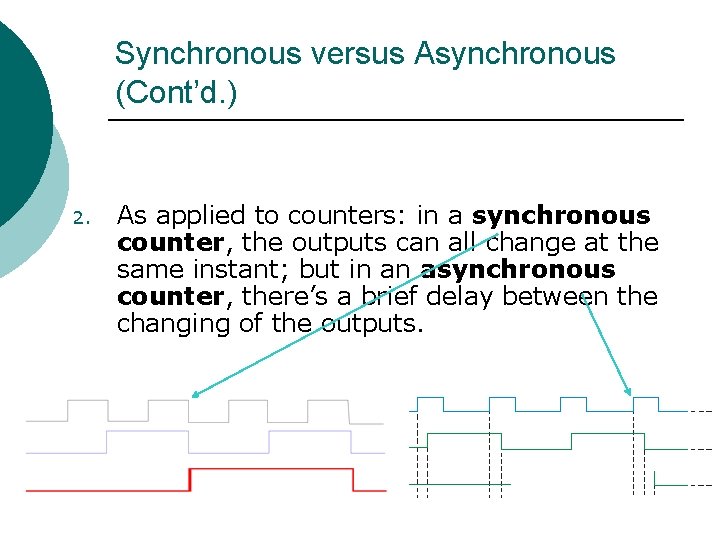

Synchronous versus Asynchronous ¡ 1. The synchronous/asynchronous distinction has different meanings: As applied to inputs: A change on a synchronous input doesn’t affect the outputs until the next active clock edge, but a change on an asynchronous input affects the outputs immediately.

Synchronous versus Asynchronous (Cont’d. ) 2. As applied to counters: in a synchronous counter, the outputs can all change at the same instant; but in an asynchronous counter, there’s a brief delay between the changing of the outputs.

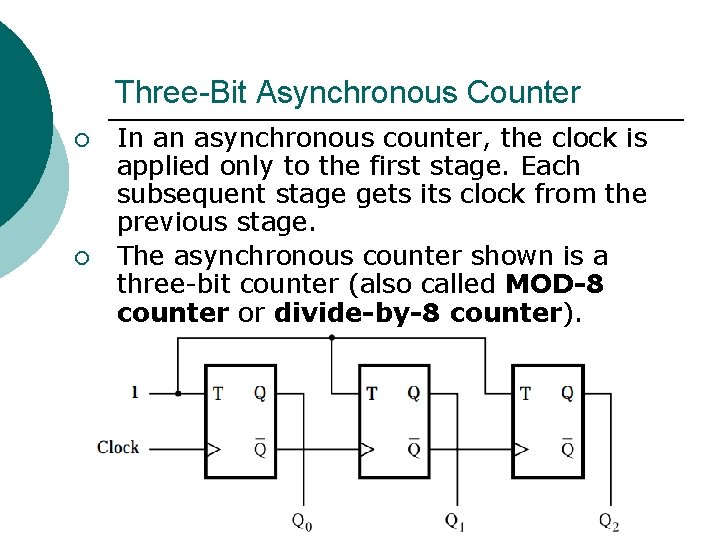

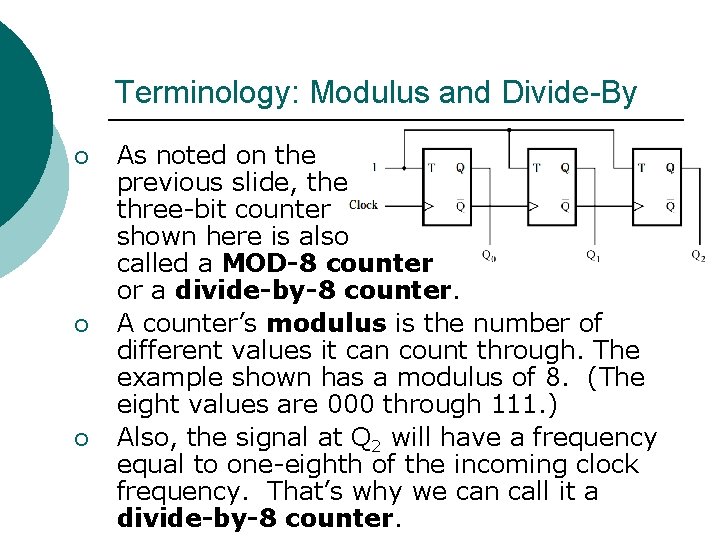

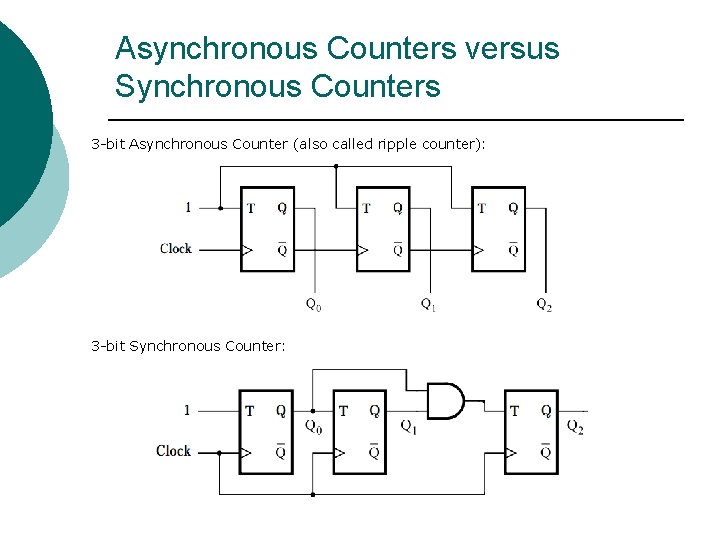

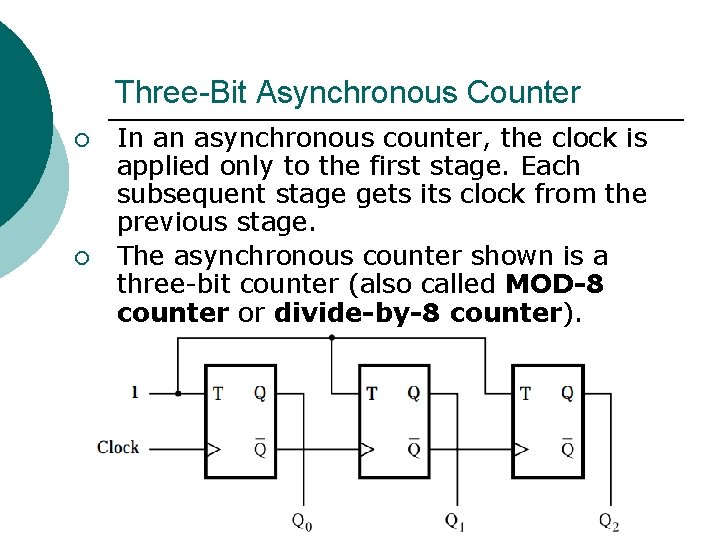

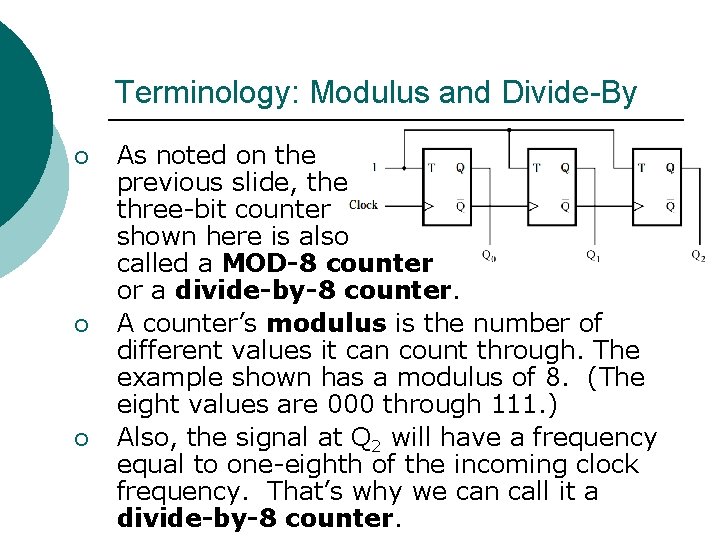

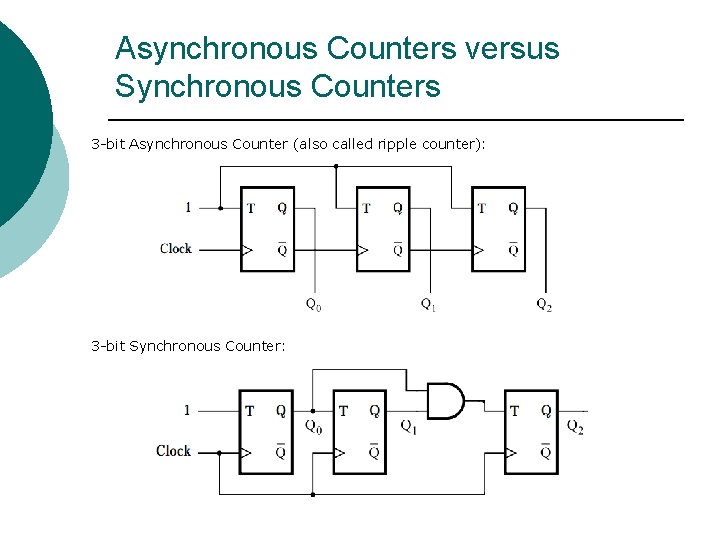

Three-Bit Asynchronous Counter ¡ ¡ In an asynchronous counter, the clock is applied only to the first stage. Each subsequent stage gets its clock from the previous stage. The asynchronous counter shown is a three-bit counter (also called MOD-8 counter or divide-by-8 counter).

Terminology: Modulus and Divide-By ¡ ¡ ¡ As noted on the previous slide, the three-bit counter shown here is also called a MOD-8 counter or a divide-by-8 counter. A counter’s modulus is the number of different values it can count through. The example shown has a modulus of 8. (The eight values are 000 through 111. ) Also, the signal at Q 2 will have a frequency equal to one-eighth of the incoming clock frequency. That’s why we can call it a divide-by-8 counter.

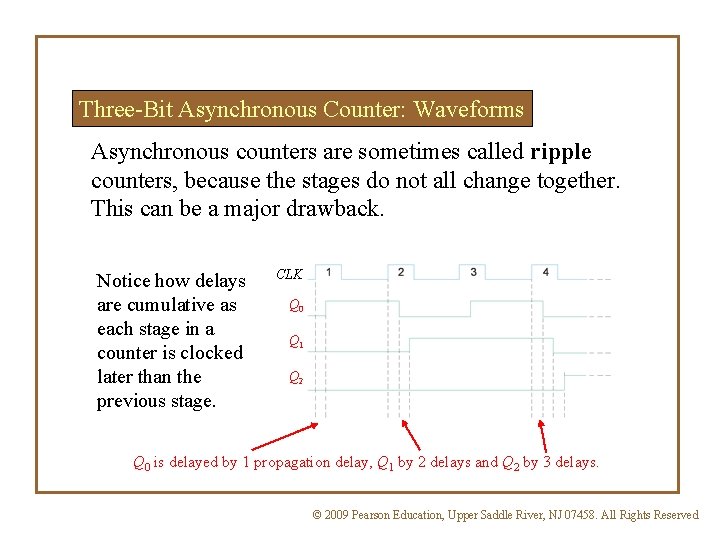

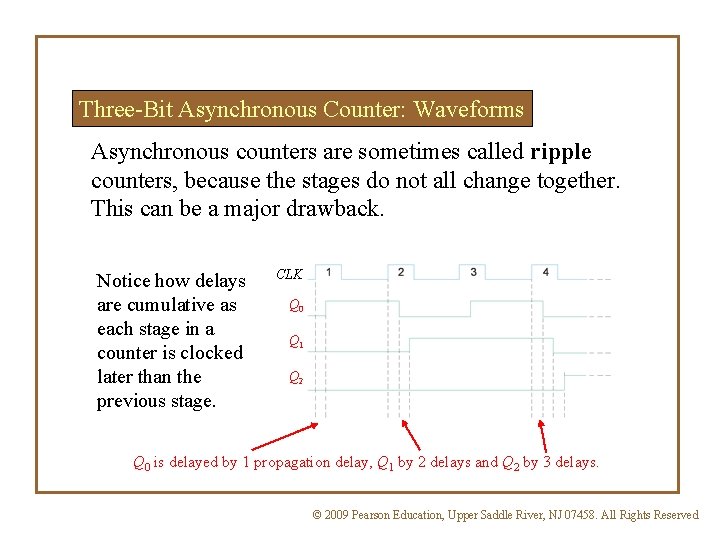

Three-Bit Asynchronous Counter: Waveforms Asynchronous counters are sometimes called ripple counters, because the stages do not all change together. This can be a major drawback. Notice how delays are cumulative as each stage in a counter is clocked later than the previous stage. CLK Q 0 Q 1 Q 2 Q 0 is delayed by 1 propagation delay, Q 1 by 2 delays and Q 2 by 3 delays. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Some 74 XX Asynchronous Counter ICs 7490 Four bit decade counter (MOD 10) ¡ 7492 Four bit divide-by-12 counter (MOD ¡ 12) ¡ 7493 Four bit binary counter (MOD 16)

Asynchronous Counters versus Synchronous Counters 3 -bit Asynchronous Counter (also called ripple counter): 3 -bit Synchronous Counter:

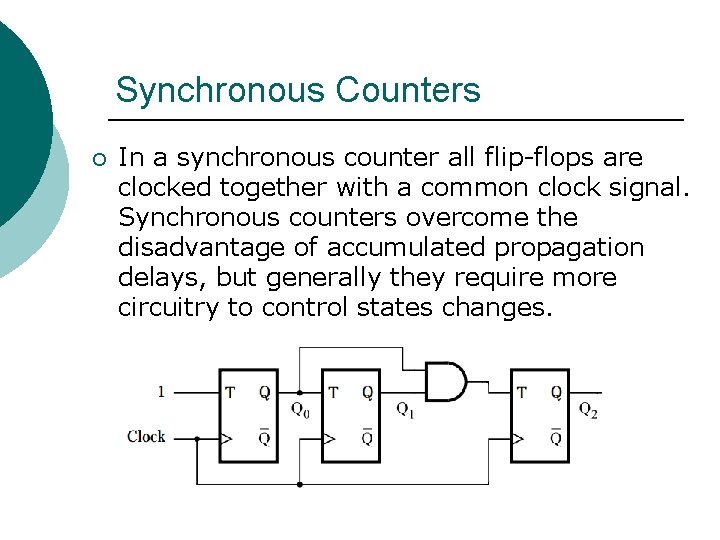

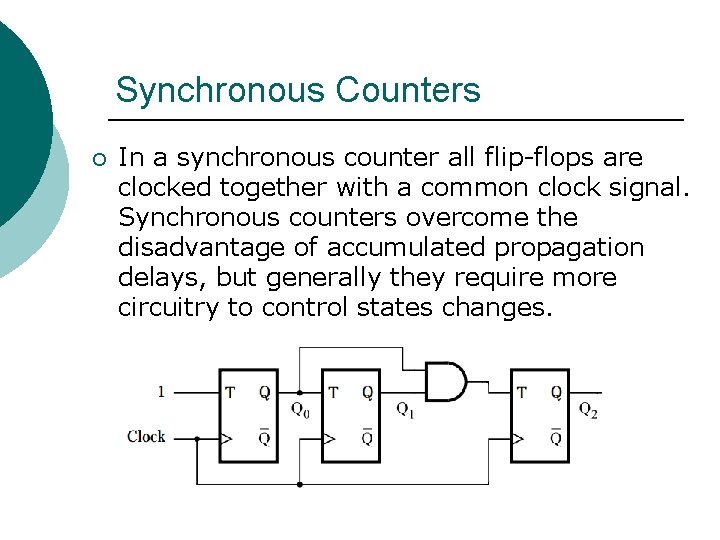

Synchronous Counters ¡ In a synchronous counter all flip-flops are clocked together with a common clock signal. Synchronous counters overcome the disadvantage of accumulated propagation delays, but generally they require more circuitry to control states changes.

Some 74 XX Synchronous Counter ICs ¡ 74160 and 74162: Four-bit synchronous decade counters (MOD 10) l ¡ 160’s clear is asynchronous, 162’s is synchronous. 74161 and 74163: Four-bit synchronous binary counters (MOD 16) l ¡ 161’s clear is asynchronous, 163’s is synchronous. 74190: Four-bit synchronous up/down decade counter (MOD 10) ¡ 74191: Four-bit synchronous up/down binary counter (MOD 16)

Counters in Quartus ¡ Quartus gives you several ways to implement counters: l Using schematic capture: Build counters out of individual flip-flops. ¡ Place virtual copies of 74 xx chips such as the 7490 or 74190. ¡ Place and configure a customizable counter (named lpm_counter) from Quartus’ Library of Parameterized Modules. ¡ l Using VHDL code.

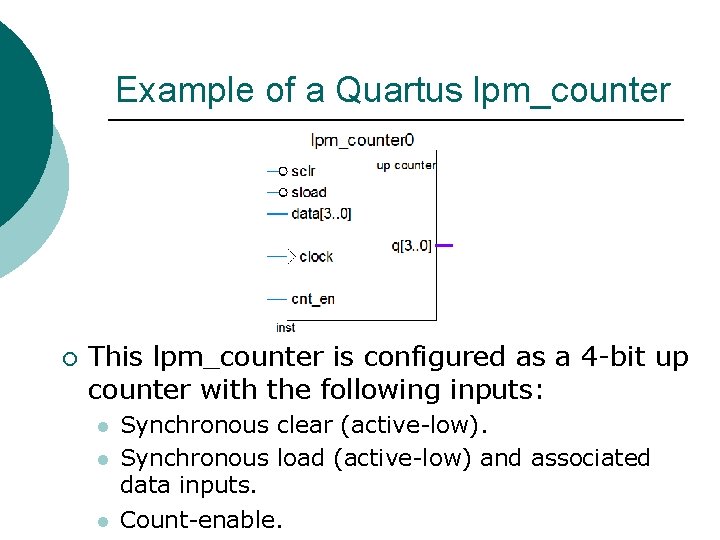

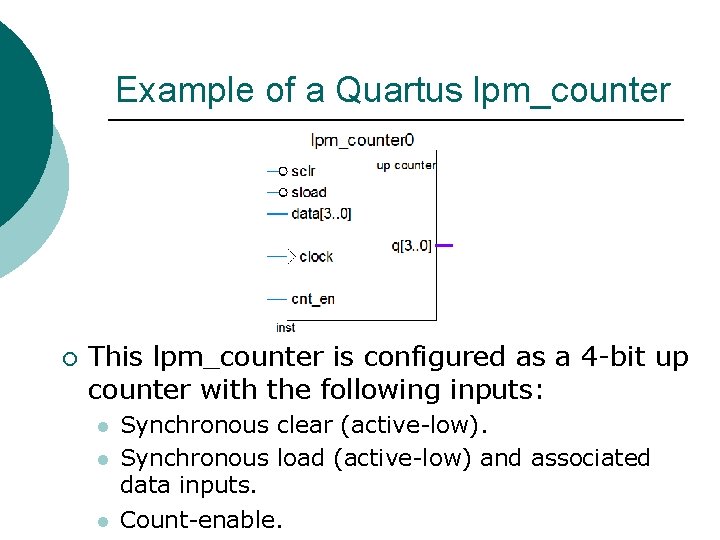

Example of a Quartus lpm_counter ¡ This lpm_counter is configured as a 4 -bit up counter with the following inputs: l l l Synchronous clear (active-low). Synchronous load (active-low) and associated data inputs. Count-enable.

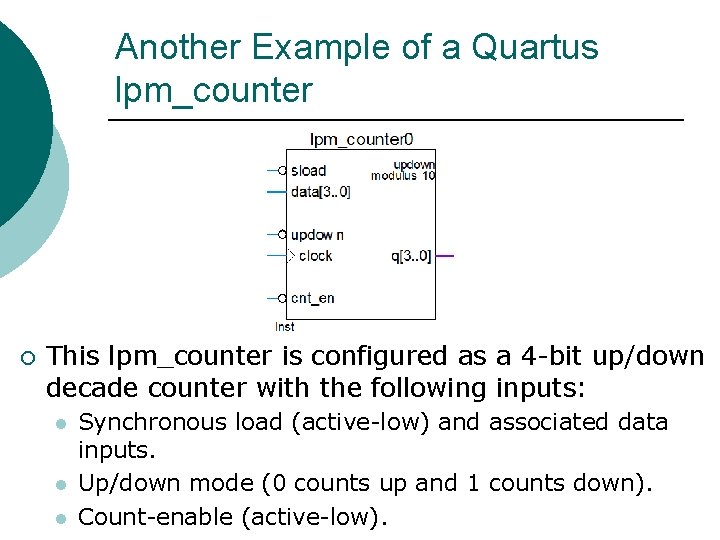

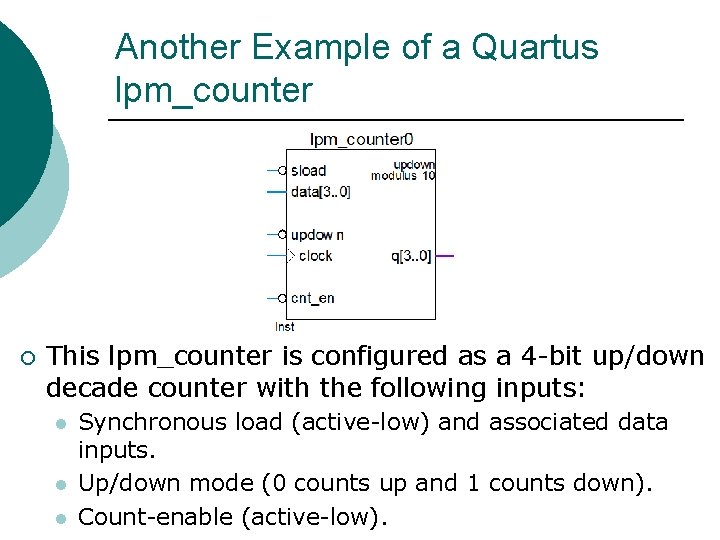

Another Example of a Quartus lpm_counter ¡ This lpm_counter is configured as a 4 -bit up/down decade counter with the following inputs: l l l Synchronous load (active-low) and associated data inputs. Up/down mode (0 counts up and 1 counts down). Count-enable (active-low).

Shift Counters ¡ ¡ Shift registers are often used to form counter-like circuits, called shift counters, that recirculate a pattern of 0’s and 1’s. Two common examples are the ring counter and the Johnson counter.

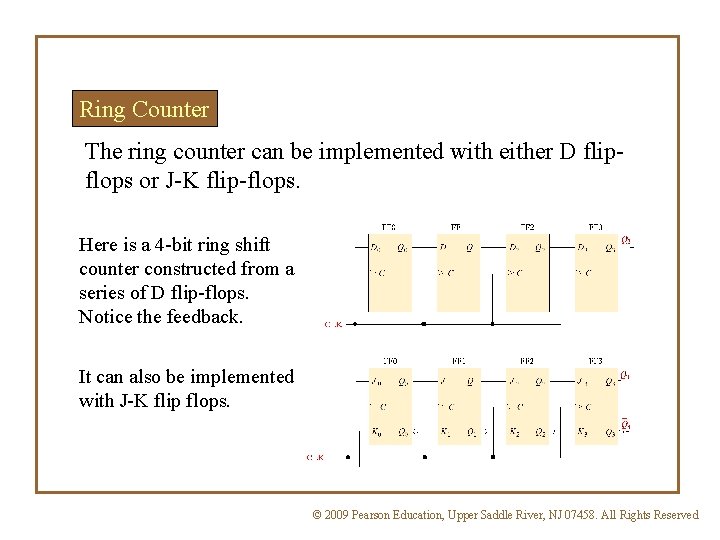

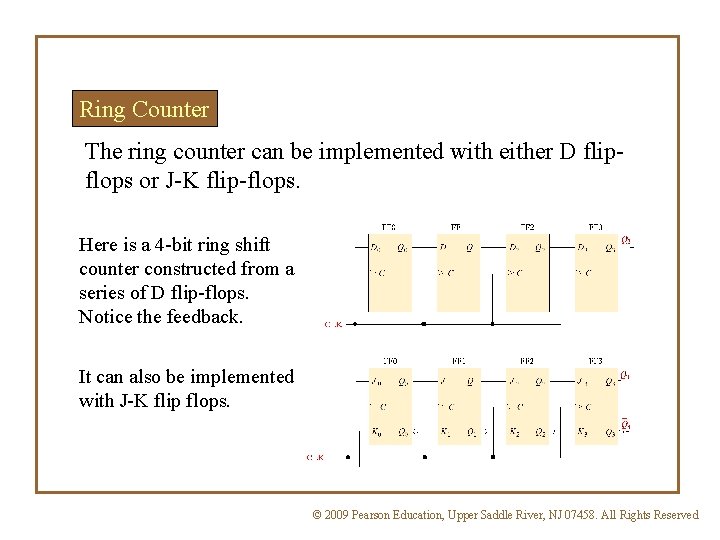

Ring Counter The ring counter can be implemented with either D flipflops or J-K flip-flops. Here is a 4 -bit ring shift counter constructed from a series of D flip-flops. Notice the feedback. It can also be implemented with J-K flip flops. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

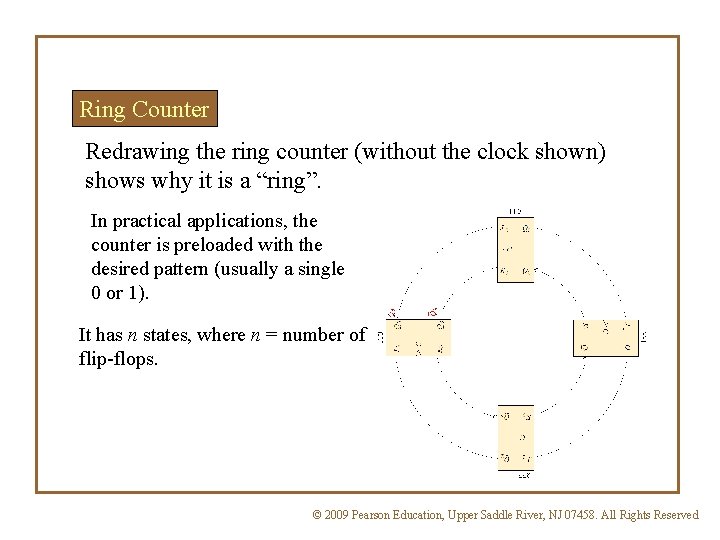

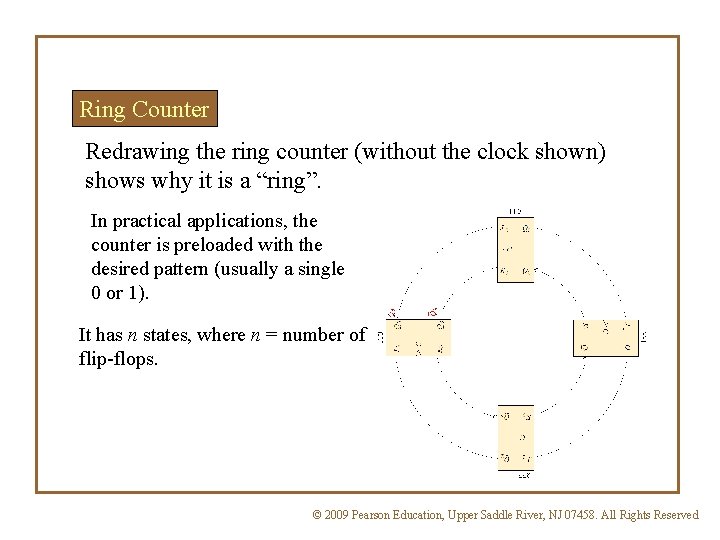

Ring Counter Redrawing the ring counter (without the clock shown) shows why it is a “ring”. In practical applications, the counter is preloaded with the desired pattern (usually a single 0 or 1). It has n states, where n = number of flip-flops. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

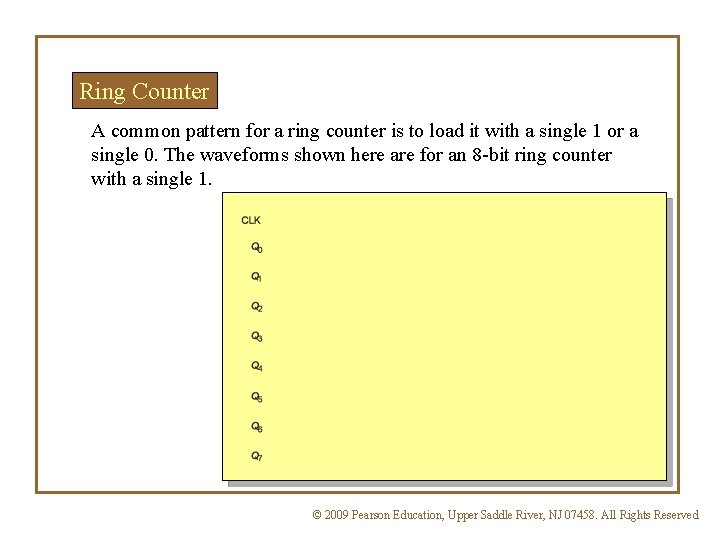

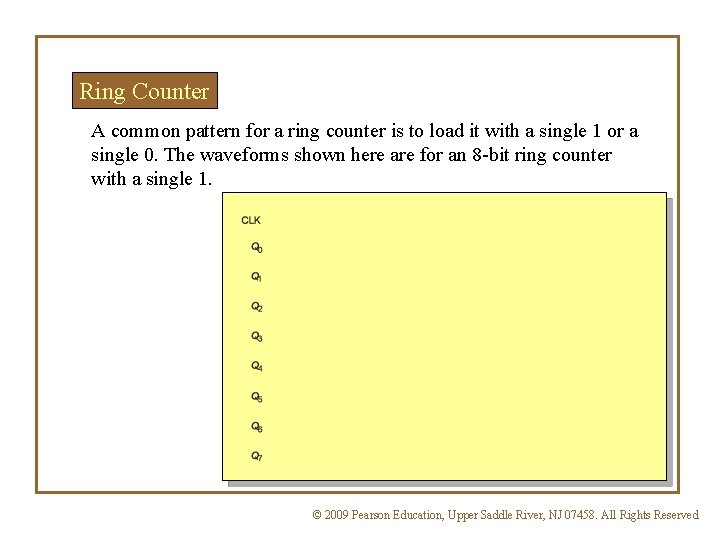

Ring Counter A common pattern for a ring counter is to load it with a single 1 or a single 0. The waveforms shown here are for an 8 -bit ring counter with a single 1. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

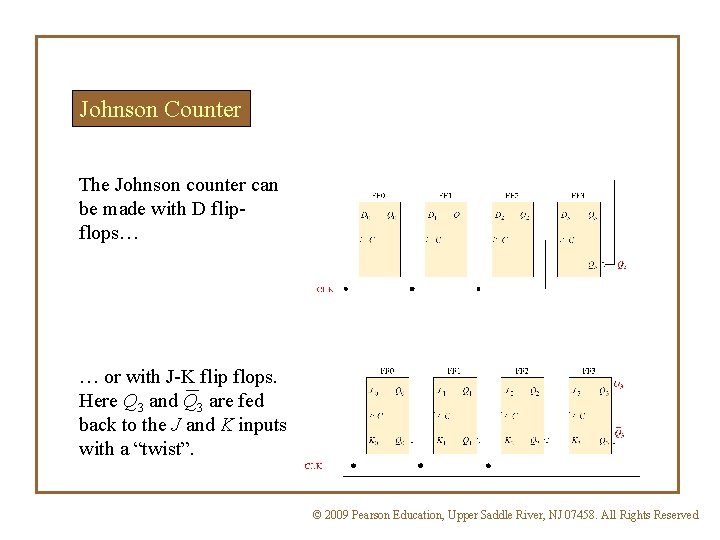

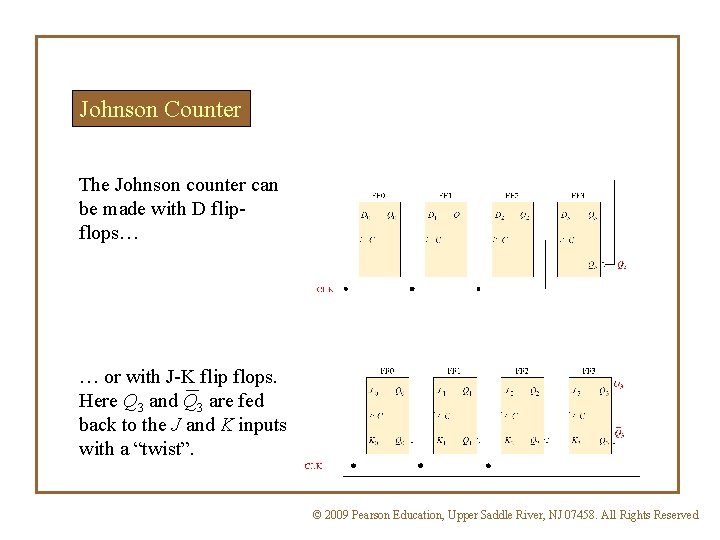

Johnson Counter The Johnson counter can be made with D flipflops… … or with J-K flip flops. Here Q 3 and Q 3 are fed back to the J and K inputs with a “twist”. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

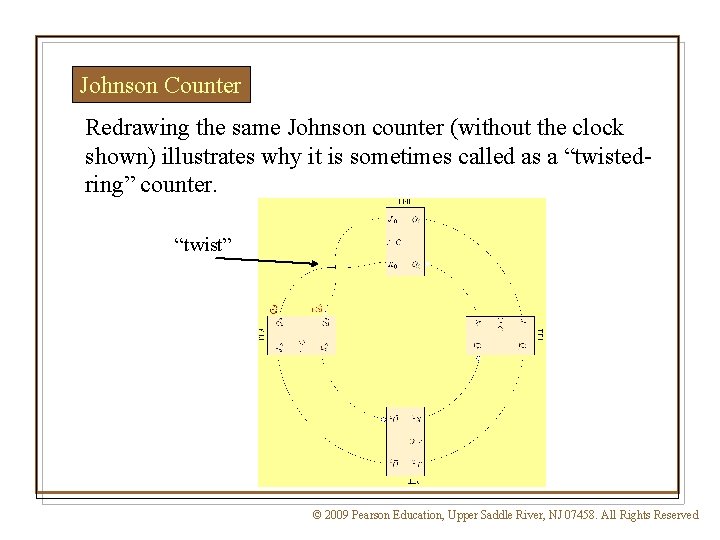

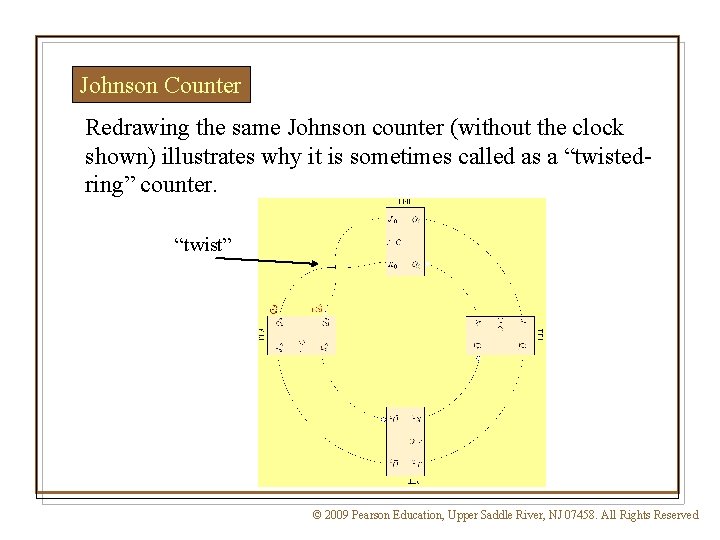

Johnson Counter Redrawing the same Johnson counter (without the clock shown) illustrates why it is sometimes called as a “twistedring” counter. “twist” © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

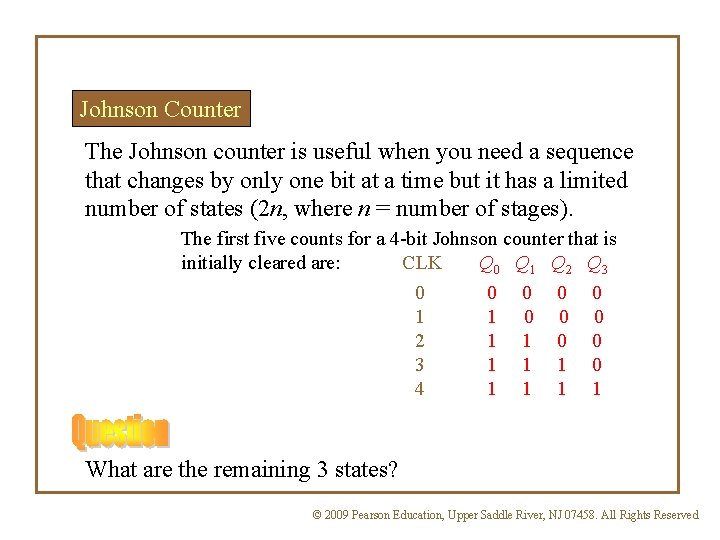

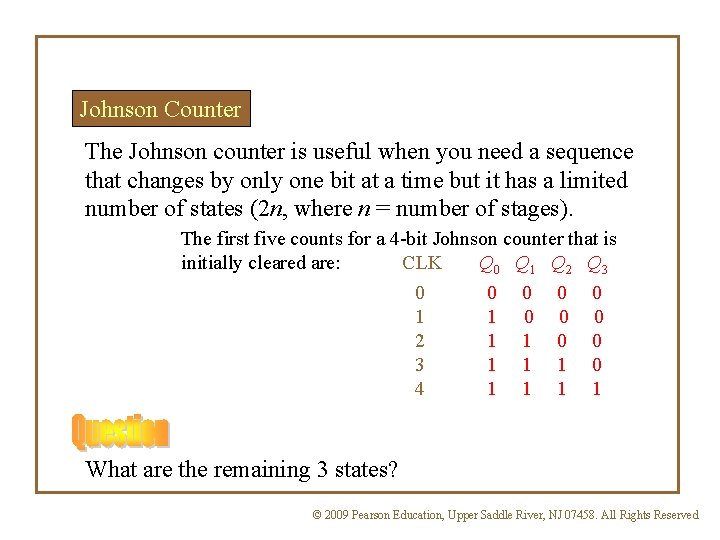

Johnson Counter The Johnson counter is useful when you need a sequence that changes by only one bit at a time but it has a limited number of states (2 n, where n = number of stages). The first five counts for a 4 -bit Johnson counter that is initially cleared are: CLK Q 0 Q 1 Q 2 Q 3 What are the remaining 3 states? 0 1 2 3 4 5 6 7 0 1 1 1 1 0 0 0 0 0 1 1 © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

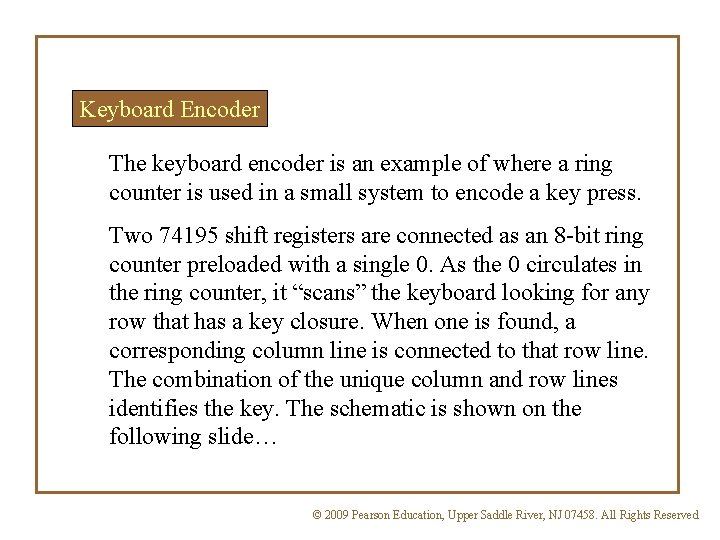

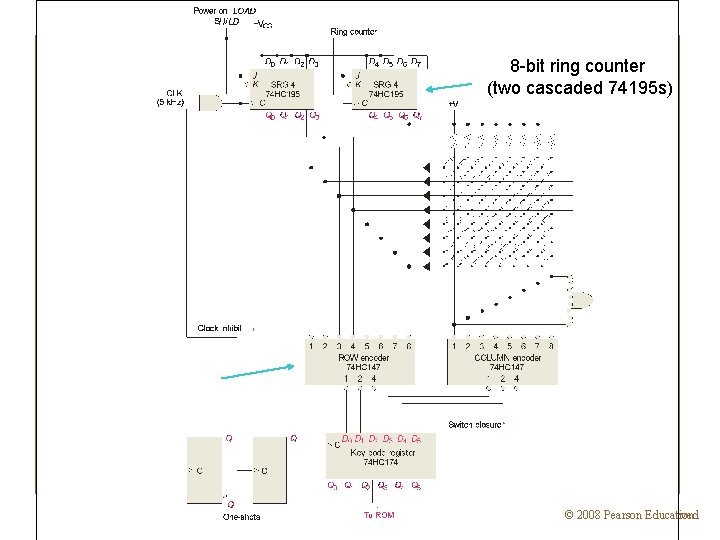

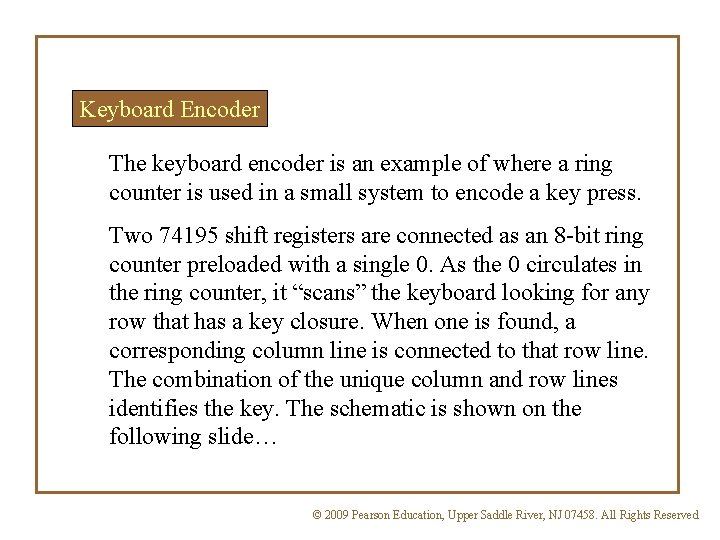

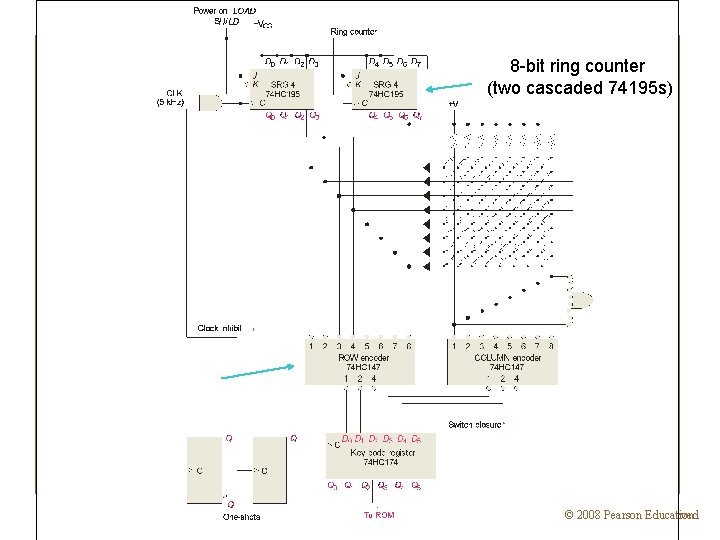

Keyboard Encoder The keyboard encoder is an example of where a ring counter is used in a small system to encode a key press. Two 74195 shift registers are connected as an 8 -bit ring counter preloaded with a single 0. As the 0 circulates in the ring counter, it “scans” the keyboard looking for any row that has a key closure. When one is found, a corresponding column line is connected to that row line. The combination of the unique column and row lines identifies the key. The schematic is shown on the following slide… © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

8 -bit ring counter (two cascaded 74195 s) © 2009 Pearson Education, Upper Saddle River, NJ © 07458. 2008 All Pearson Rights. Education Reserved