EECS 470 Lecture 1 Computer Architecture Apple A

- Slides: 38

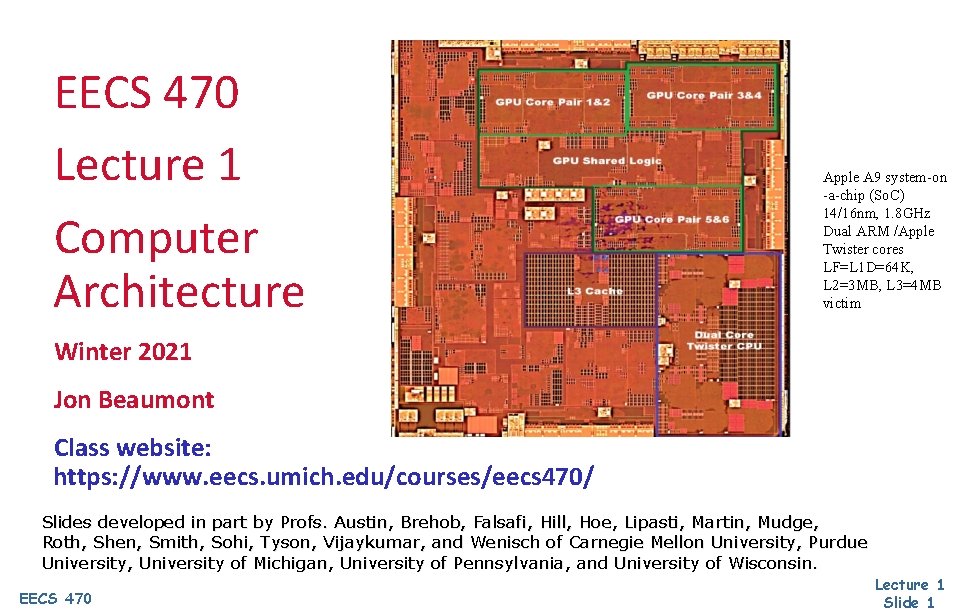

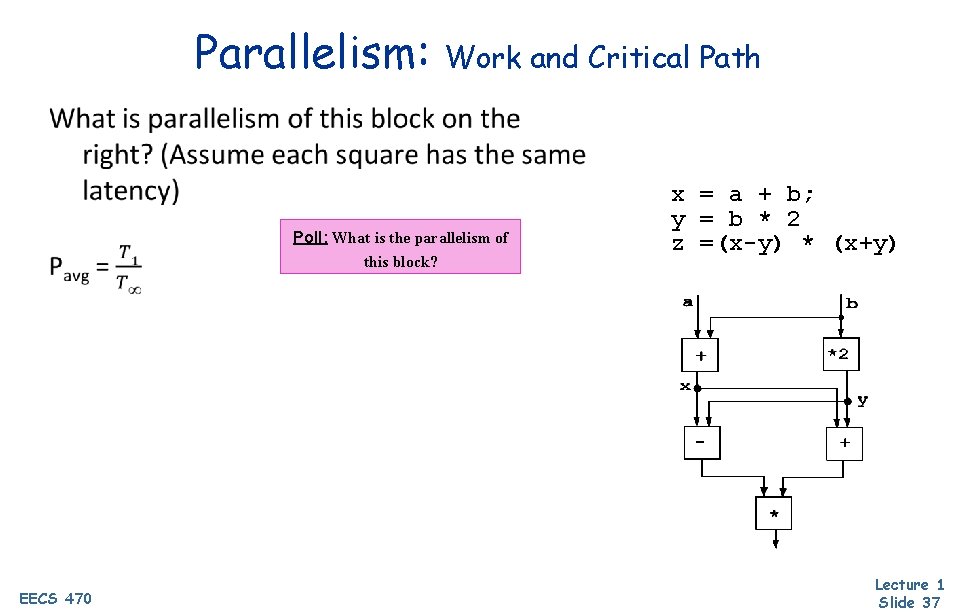

EECS 470 Lecture 1 Computer Architecture Apple A 9 system-on -a-chip (So. C) 14/16 nm, 1. 8 GHz Dual ARM /Apple Twister cores LF=L 1 D=64 K, L 2=3 MB, L 3=4 MB victim Winter 2021 Jon Beaumont Class website: https: //www. eecs. umich. edu/courses/eecs 470/ Slides developed in part by Profs. Austin, Brehob, Falsafi, Hill, Hoe, Lipasti, Martin, Mudge, Roth, Shen, Smith, Sohi, Tyson, Vijaykumar, and Wenisch of Carnegie Mellon University, Purdue University, University of Michigan, University of Pennsylvania, and University of Wisconsin. EECS 470 Lecture 1 Slide 1

Hello! Feel free to unmute your mic and say hi! We will start a few minutes late today to give everyone time to join EECS 470 Lecture 1 Slide 2

• This slide is just to remind Jon to record the lectures EECS 470 Lecture 1 Slide 3

Today Introductions and Class logistics Computer architecture overview q q Goals Trends Basic Principles Metrics ISA EECS 470 Lecture 1 Slide 4

Who am I? • Lecturer in CS department • Bachelors (CE), Masters (CSE), and Ph. D (CSE) all from Michigan! • Research in computer architecture r EECS 470 How to make devices like Graphics Processing Units (GPUs) better at non-graphics stuff? Lecture 1 Slide 5

Who am I? • When not doing school stuff, you can find me: r Triathlon training r Cooking r Designing retro games / emulators • Call me: r Jon r Dr / Prof Beaumont r “Yo Teach!” EECS 470 Lecture 1 Slide 6

Who are They? GSIs • Scott Smith (ssscrazy@umich. edu) • Ali Khadem (arkhadem@umich. edu) IA • John Campbell (jbca@umich. edu) Talk to them about labs and projects EECS 470 Lecture 1 Slide 7

Who are You? • Zoom poll If you are accessing on a smartphone, netbook, tablet, etc, you may not be able to participate in polls r No worries, they are optional r Poll EECS 470 Lecture 1 Slide 8

Zoom Logistics • Please ask questions during lecture! r Back and forth between instructor and student (and students to students) are integral for learning • Best way to ask a question is to "raise your hand" r I see an ordered list of who has questions • You can also type it in chat, but I may miss it EECS 470 Lecture 1 Slide 9

What Is Computer Architecture? “The term architecture is used here to describe the attributes of a system as seen by the programmer, i. e. , the conceptual structure and functional behavior as distinct from the organization of the dataflow and controls, the logic design, and the physical implementation. ” Gene Amdahl, IBM Journal of R&D, April 1964 [Think of it as a contract between hardware and software. ] EECS 470 Lecture 1 Slide 10

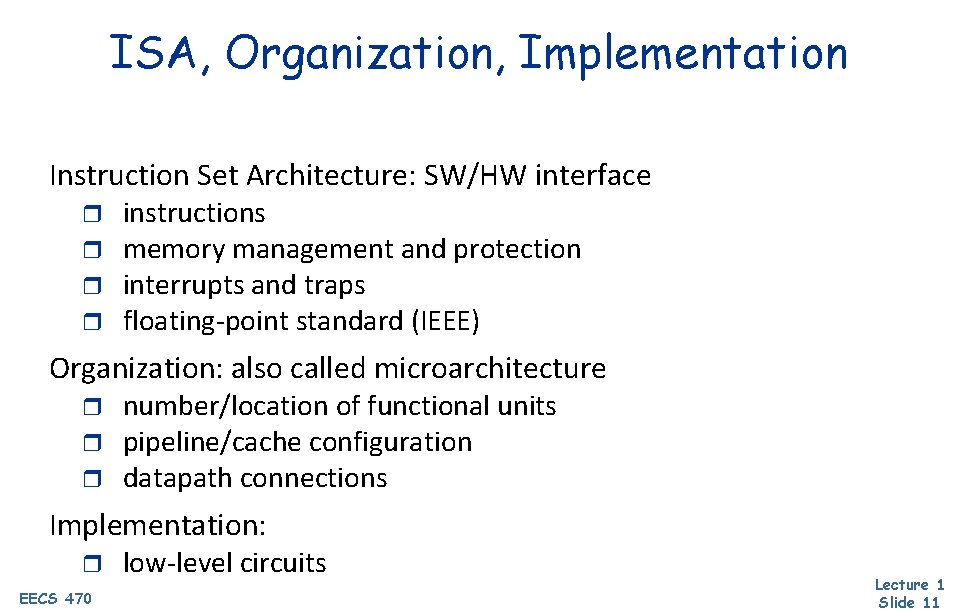

ISA, Organization, Implementation Instruction Set Architecture: SW/HW interface r r instructions memory management and protection interrupts and traps floating-point standard (IEEE) Organization: also called microarchitecture r r r number/location of functional units pipeline/cache configuration datapath connections Implementation: r EECS 470 low-level circuits Lecture 1 Slide 11

What Is 470 All About? High-level understanding of issues in modern architecture: r r r Dynamic out-of-order processing Memory architecture Multicore / multiprocessor issues Lectures, HW & Reading Low-level understanding of critical components: r r EECS 470 Microarchitecture of out-of-order machines Caches & memory sub-system Project & Reading Lecture 1 Slide 12

Who Should Take 470? Seniors (ambitious Juniors) & Graduate Students 1. 2. 3. Computer architects to be Computer system designers Those interested in computer systems Required Background r r r EECS 470 Basic digital logic (EECS 270) Basic architecture (EECS 370) Verilog/VHDL experience (reviewed in discussion) Lecture 1 Slide 13

Class Resources Website for lectures, projects and other resources https: //www. eecs. umich. edu/courses/eecs 470/ Piazza for discussion and questions https: //piazza. com/class/kjoqguntyr 139 preferred Gradescope for submitting homework and regrade requests https: //www. gradescope. com/courses/224596 Canvas for posting grades https: //umich. instructure. com/courses/405415 email for 470 staff: eecs 470 w 21 staff@umich. edu (Use Piazza when possible) EECS 470 Lecture 1 Slide 14

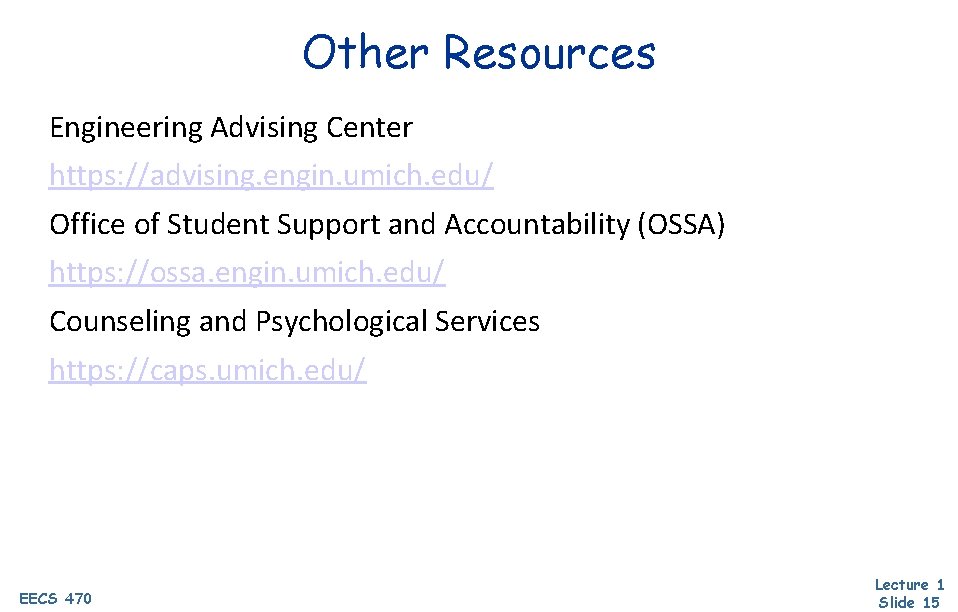

Other Resources Engineering Advising Center https: //advising. engin. umich. edu/ Office of Student Support and Accountability (OSSA) https: //ossa. engin. umich. edu/ Counseling and Psychological Services https: //caps. umich. edu/ EECS 470 Lecture 1 Slide 15

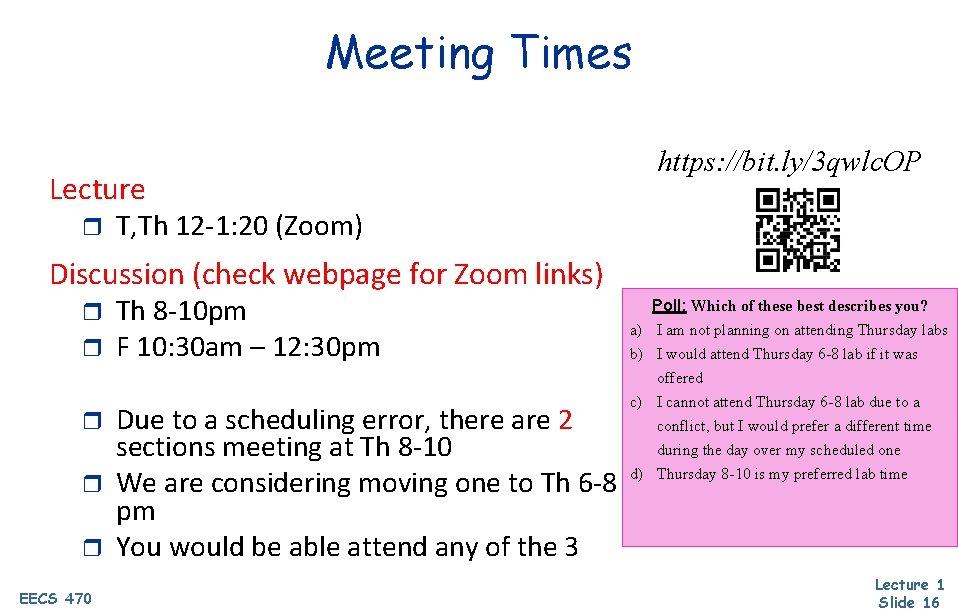

Meeting Times https: //bit. ly/3 qwlc. OP Lecture r T, Th 12 -1: 20 (Zoom) Discussion (check webpage for Zoom links) r r Th 8 -10 pm F 10: 30 am – 12: 30 pm Due to a scheduling error, there are 2 sections meeting at Th 8 -10 r We are considering moving one to Th 6 -8 pm r You would be able attend any of the 3 r EECS 470 a) b) c) d) Poll: Which of these best describes you? I am not planning on attending Thursday labs I would attend Thursday 6 -8 lab if it was offered I cannot attend Thursday 6 -8 lab due to a conflict, but I would prefer a different time during the day over my scheduled one Thursday 8 -10 is my preferred lab time Lecture 1 Slide 16

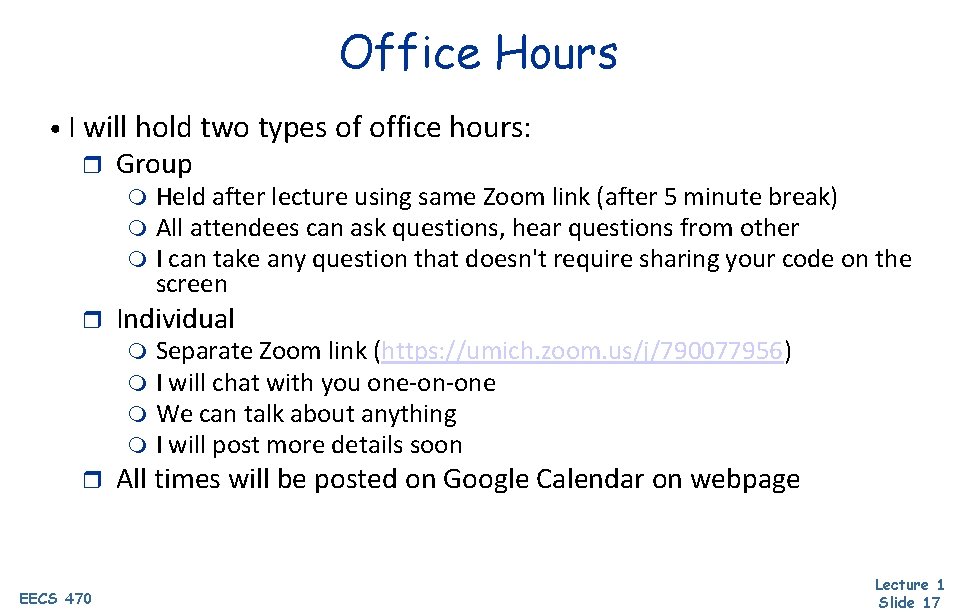

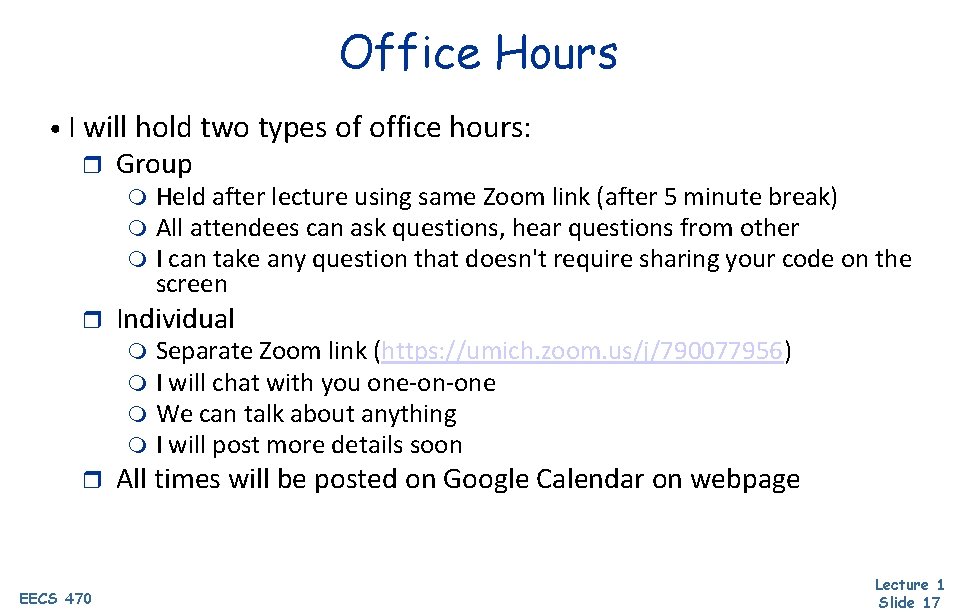

Office Hours • I will hold two types of office hours: r Group m m m r Individual m m r EECS 470 Held after lecture using same Zoom link (after 5 minute break) All attendees can ask questions, hear questions from other I can take any question that doesn't require sharing your code on the screen Separate Zoom link (https: //umich. zoom. us/j/790077956) I will chat with you one-on-one We can talk about anything I will post more details soon All times will be posted on Google Calendar on webpage Lecture 1 Slide 17

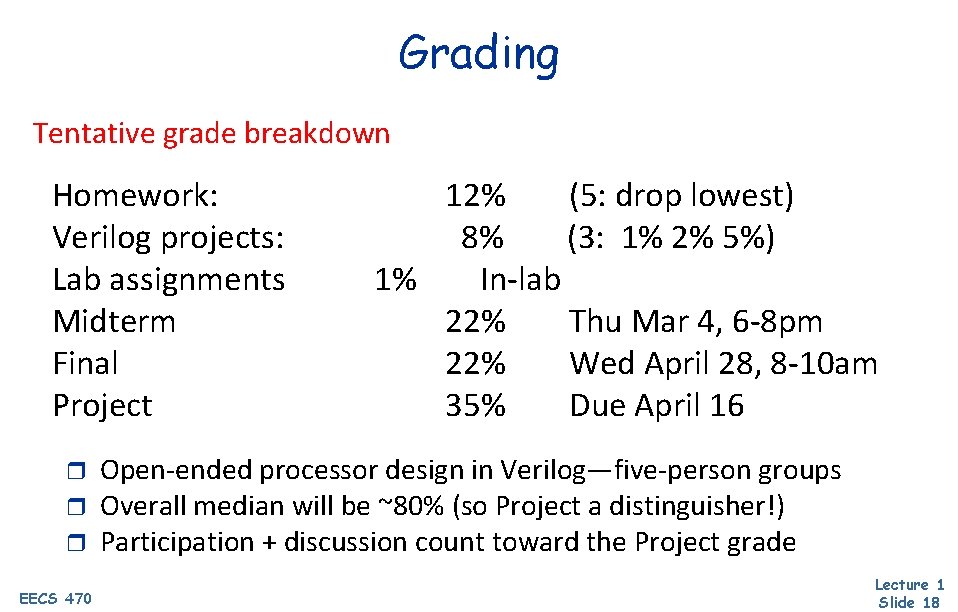

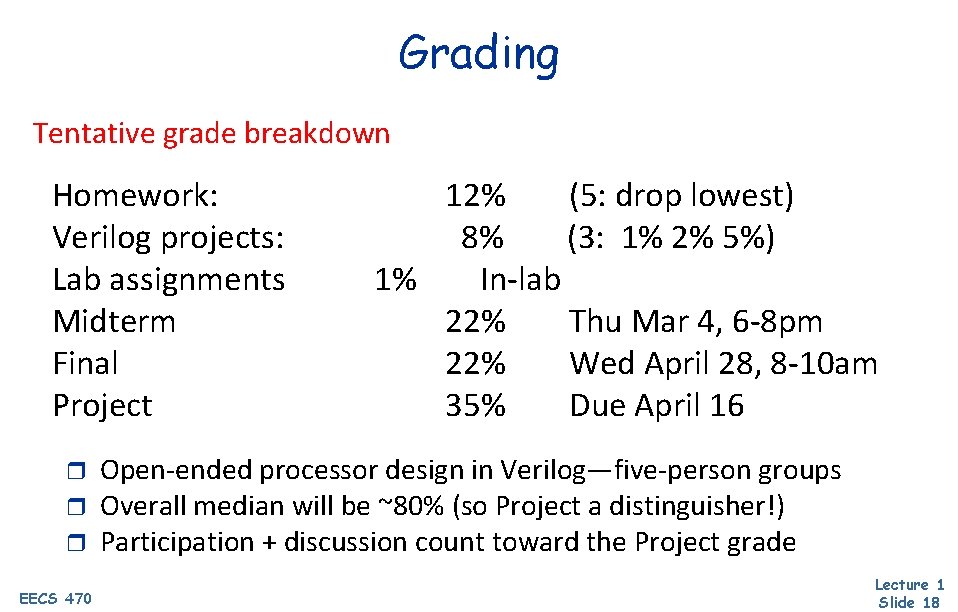

Grading Tentative grade breakdown Homework: Verilog projects: Lab assignments Midterm Final Project r r r EECS 470 12% (5: drop lowest) 8% (3: 1% 2% 5%) 1% In-lab 22% Thu Mar 4, 6 -8 pm 22% Wed April 28, 8 -10 am 35% Due April 16 Open-ended processor design in Verilog—five-person groups Overall median will be ~80% (so Project a distinguisher!) Participation + discussion count toward the Project grade Lecture 1 Slide 18

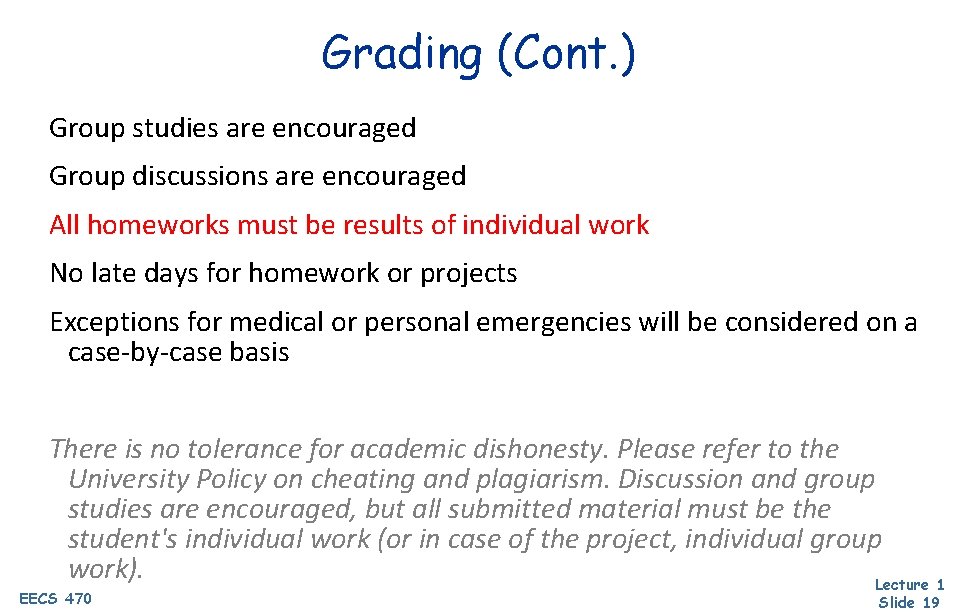

Grading (Cont. ) Group studies are encouraged Group discussions are encouraged All homeworks must be results of individual work No late days for homework or projects Exceptions for medical or personal emergencies will be considered on a case-by-case basis There is no tolerance for academic dishonesty. Please refer to the University Policy on cheating and plagiarism. Discussion and group studies are encouraged, but all submitted material must be the student's individual work (or in case of the project, individual group work). Lecture 1 EECS 470 Slide 19

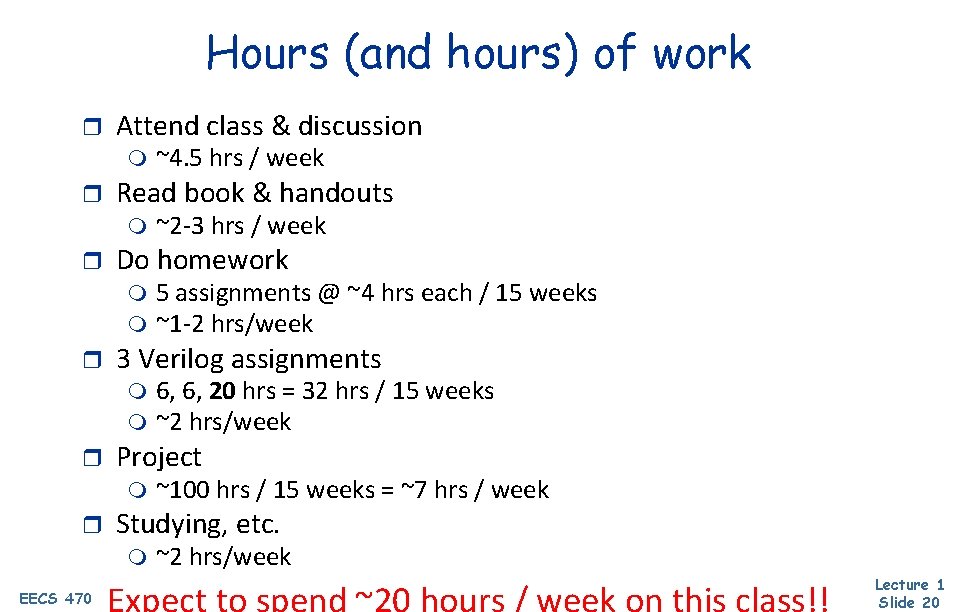

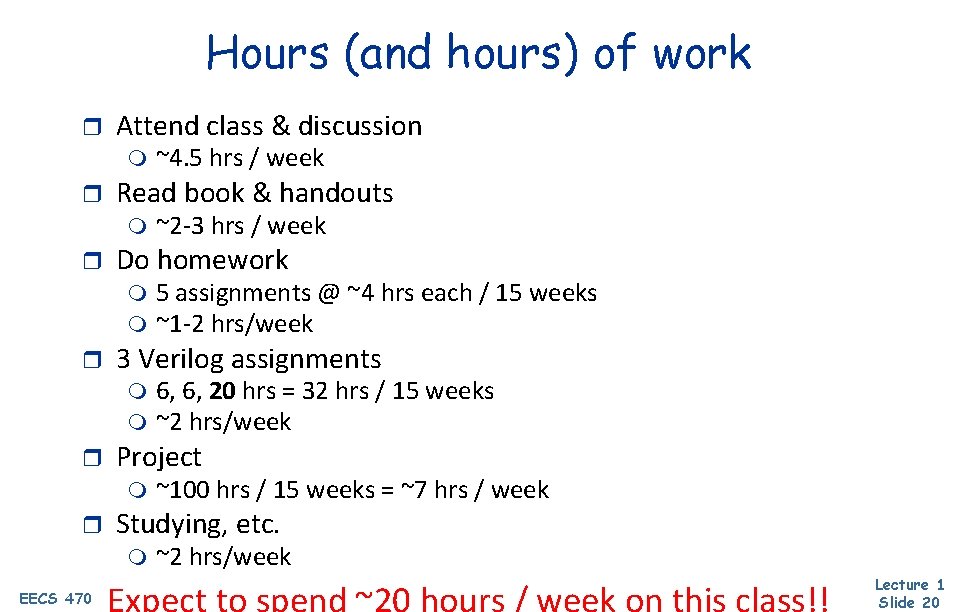

Hours (and hours) of work r Attend class & discussion m r Read book & handouts m r ~100 hrs / 15 weeks = ~7 hrs / week Studying, etc. m EECS 470 6, 6, 20 hrs = 32 hrs / 15 weeks ~2 hrs/week Project m r 5 assignments @ ~4 hrs each / 15 weeks ~1 -2 hrs/week 3 Verilog assignments m m r ~2 -3 hrs / week Do homework m m r ~4. 5 hrs / week ~2 hrs/week Lecture 1 Slide 20

Upcoming Deadlines Lab # 1 due at end of next week's lab session q Check off in lab or during office hours Project #1 due Saturday 1/29 11: 59 p q q Submit to autograder More details in discussion this Thursday / Friday HW # 1 due Th 2/4 11: 59 p—upload to Gradescope EECS 470 Lecture 1 Slide 21

Discussion: What are the Goals in Designing Architectures EECS 470 Lecture 1 Slide 22

Fundamental concepts EECS 470 Lecture 1 Slide 23

How Do We Speedup Tasks? Time Three Options: r r r EECS 470 Do less stuff Do stuff faster Do more stuff at the same time Lecture 1 Slide 24

Do Less Stuff Time EECS 470 Lecture 1 Slide 25

Do Less Stuff Time q q EECS 470 I. e. reduce number of instructions More efficient algorithms (EECS 281, 477) More efficient code, compiler optimizations (483, 583) Not much to do in microarchitecture Lecture 1 Slide 26

Do Stuff Faster Time EECS 470 Lecture 1 Slide 27

Do Stuff Faster Time q q I. e. reduce instruction latency Logic optimization (EECS 270, 478) Transistor improvements, gate and low level circuit design (312, 320, 427) Architecture: q q EECS 470 Memoization (save results of previous computation in memory, avoid recomputing) Locality (guess what data will be used next, used in caches) Lecture 1 Slide 28

Do More Stuff at Same Time EECS 470 Lecture 1 Slide 29

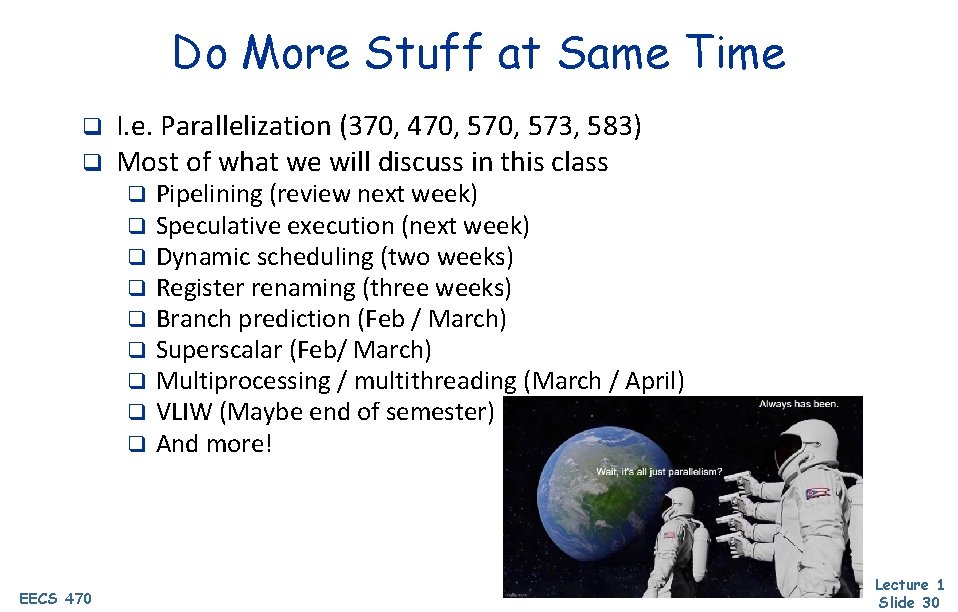

Do More Stuff at Same Time q q I. e. Parallelization (370, 470, 573, 583) Most of what we will discuss in this class q q q q q EECS 470 Pipelining (review next week) Speculative execution (next week) Dynamic scheduling (two weeks) Register renaming (three weeks) Branch prediction (Feb / March) Superscalar (Feb/ March) Multiprocessing / multithreading (March / April) VLIW (Maybe end of semester) And more! Lecture 1 Slide 30

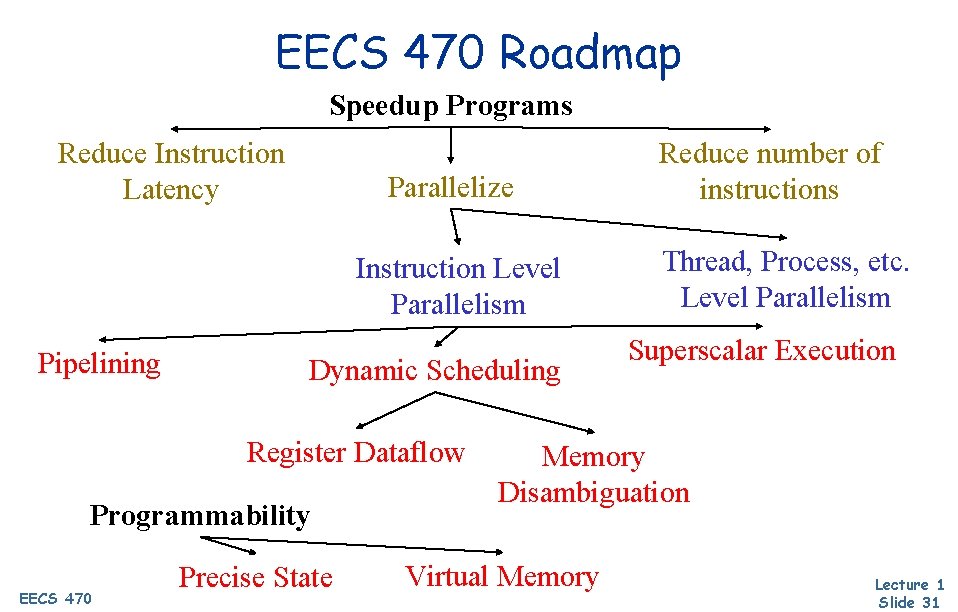

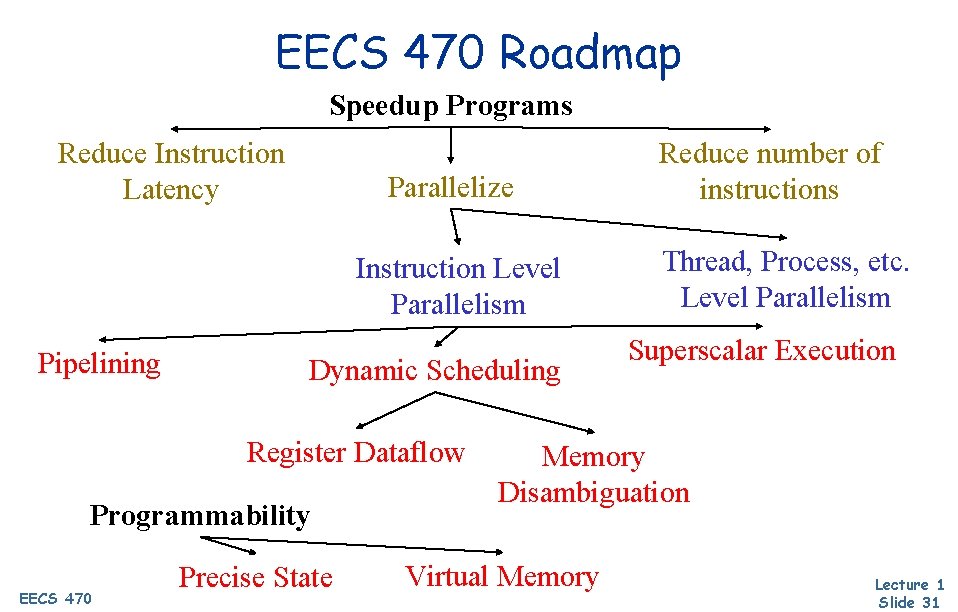

EECS 470 Roadmap Speedup Programs Reduce Instruction Latency Parallelize Instruction Level Parallelism Pipelining Dynamic Scheduling Register Dataflow Programmability EECS 470 Precise State Reduce number of instructions Thread, Process, etc. Level Parallelism Superscalar Execution Memory Disambiguation Virtual Memory Lecture 1 Slide 31

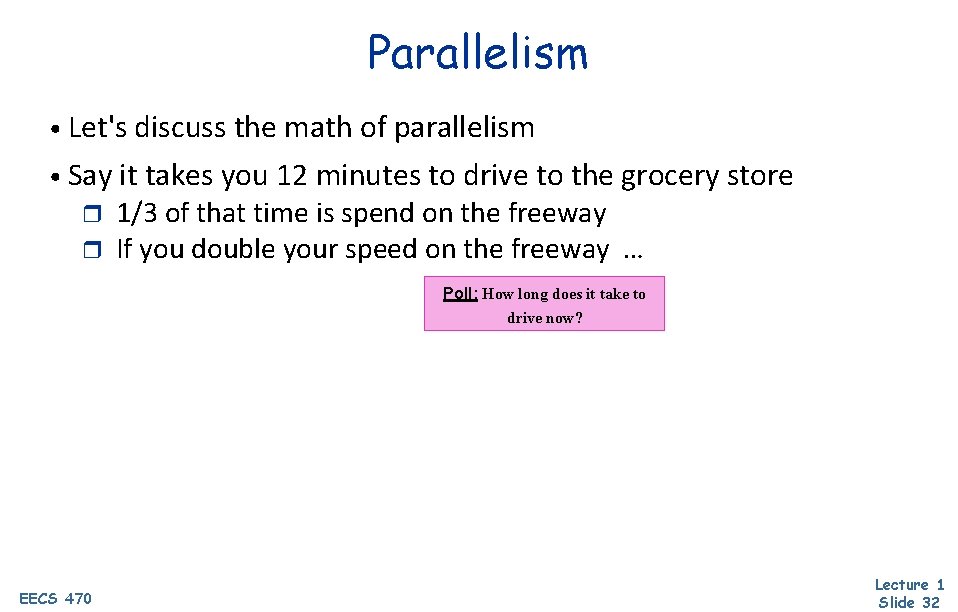

Parallelism • Let's discuss the math of parallelism • Say it takes you 12 minutes to drive to the grocery store r r 1/3 of that time is spend on the freeway If you double your speed on the freeway … Poll: How long does it take to drive now? EECS 470 Lecture 1 Slide 32

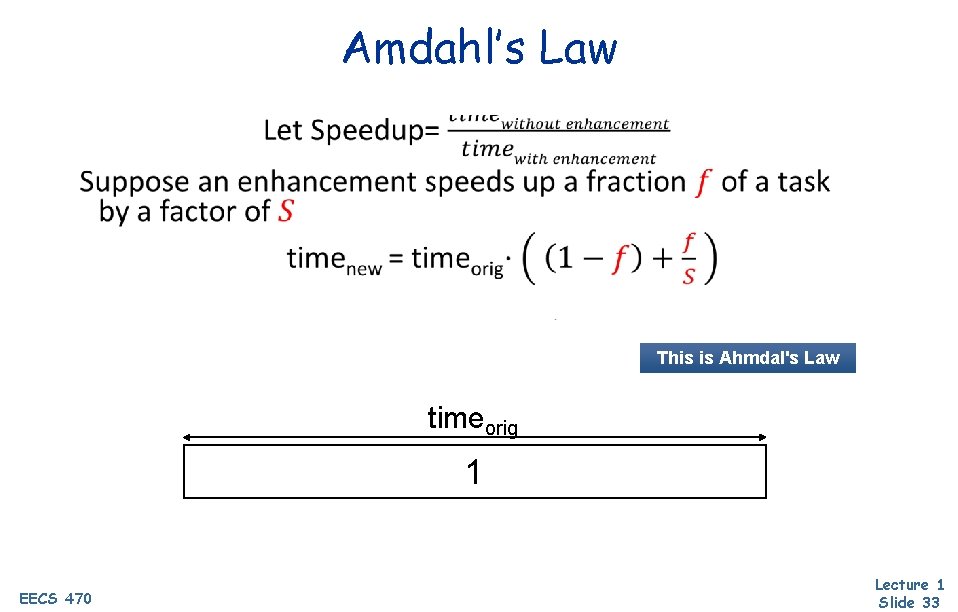

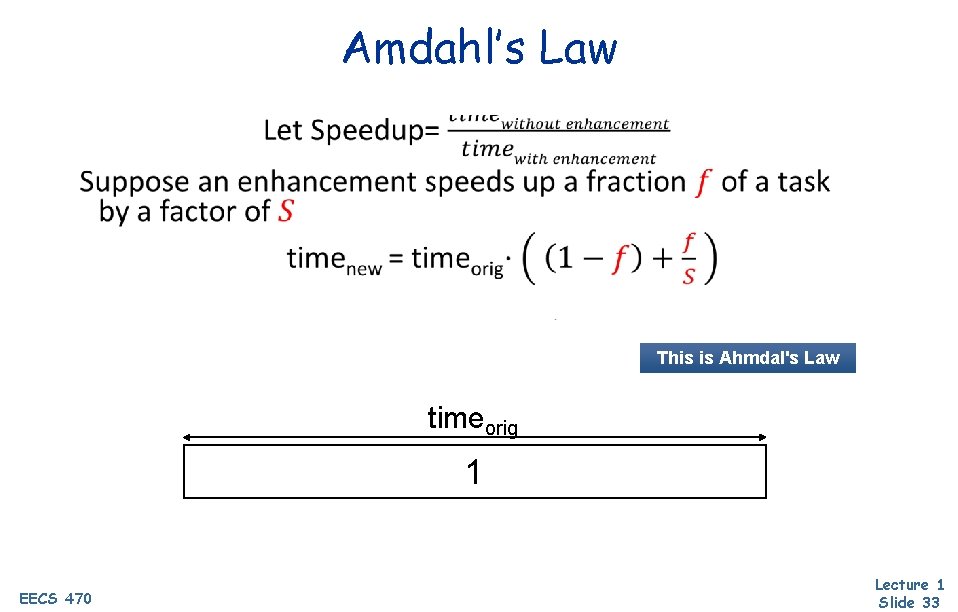

Amdahl’s Law • This is Ahmdal's Law timeorig 1 EECS 470 Lecture 1 Slide 33

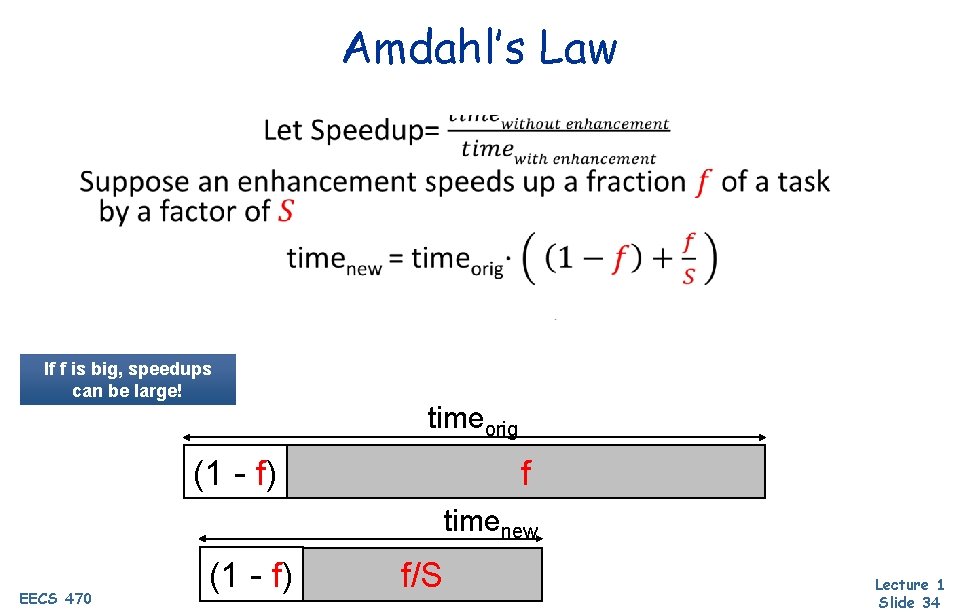

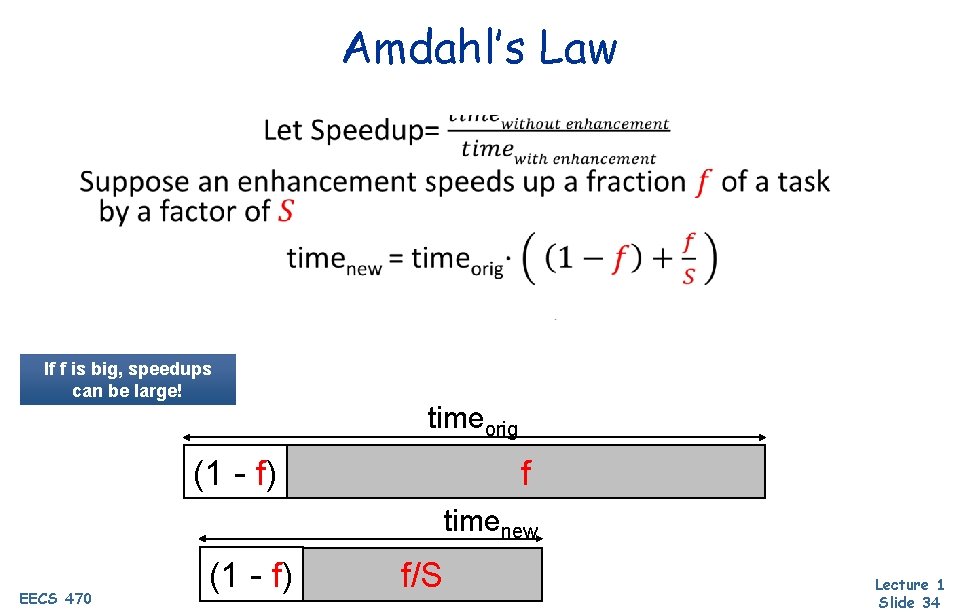

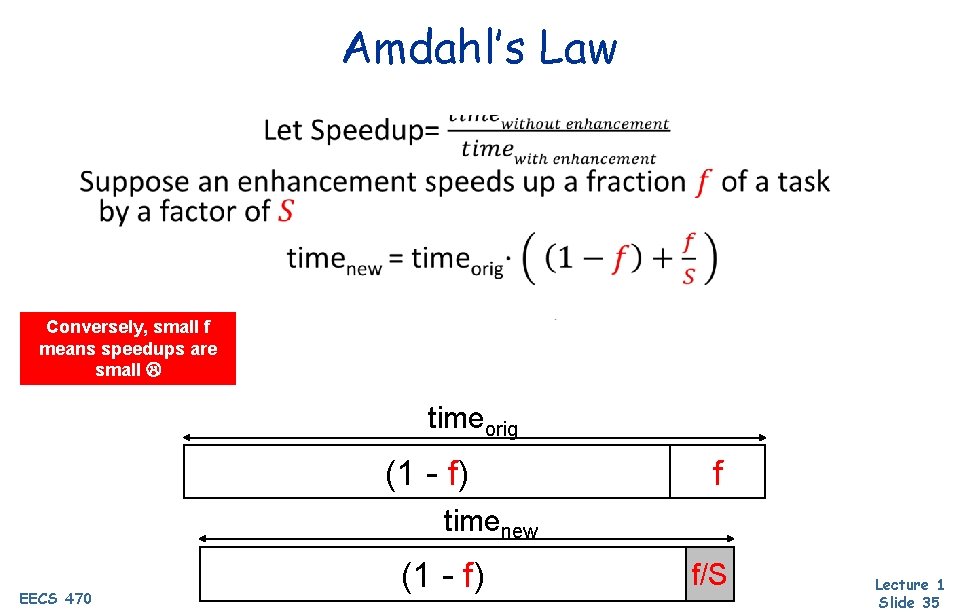

Amdahl’s Law If f is big, speedups can be large! timeorig (1 - f) f timenew EECS 470 (1 - f) f/S Lecture 1 Slide 34

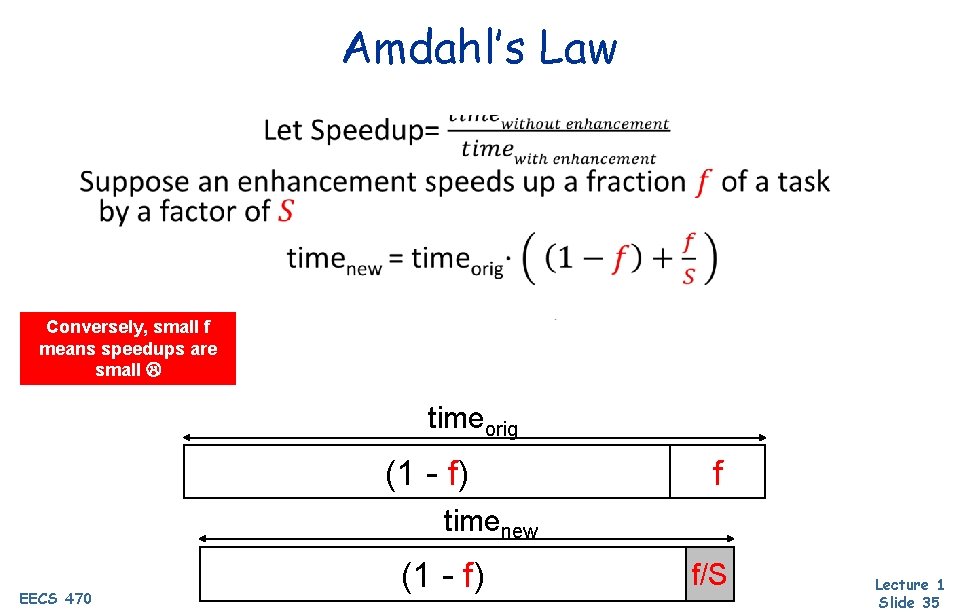

Amdahl’s Law • Conversely, small f means speedups are small timeorig (1 - f) f timenew EECS 470 (1 - f) f/S Lecture 1 Slide 35

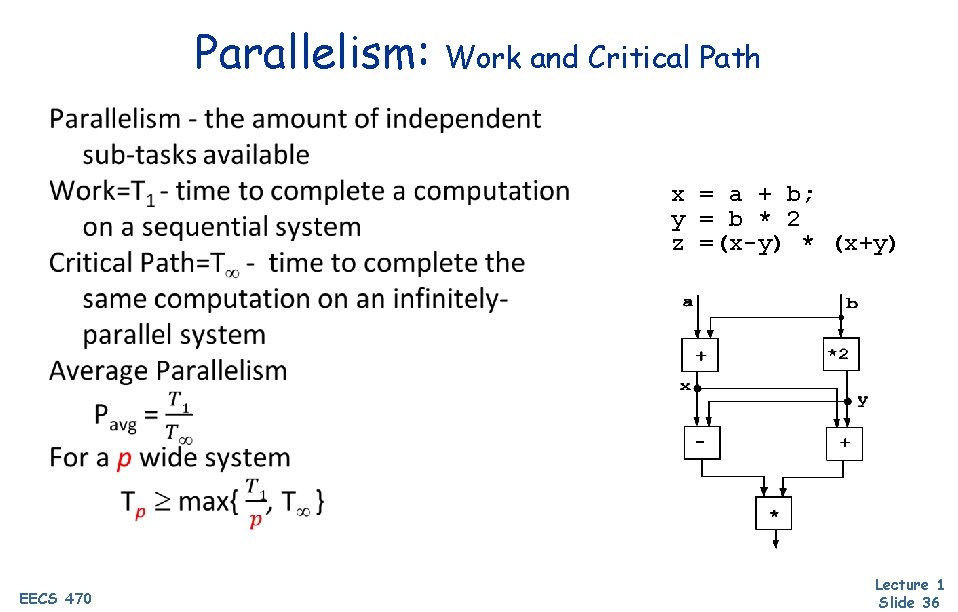

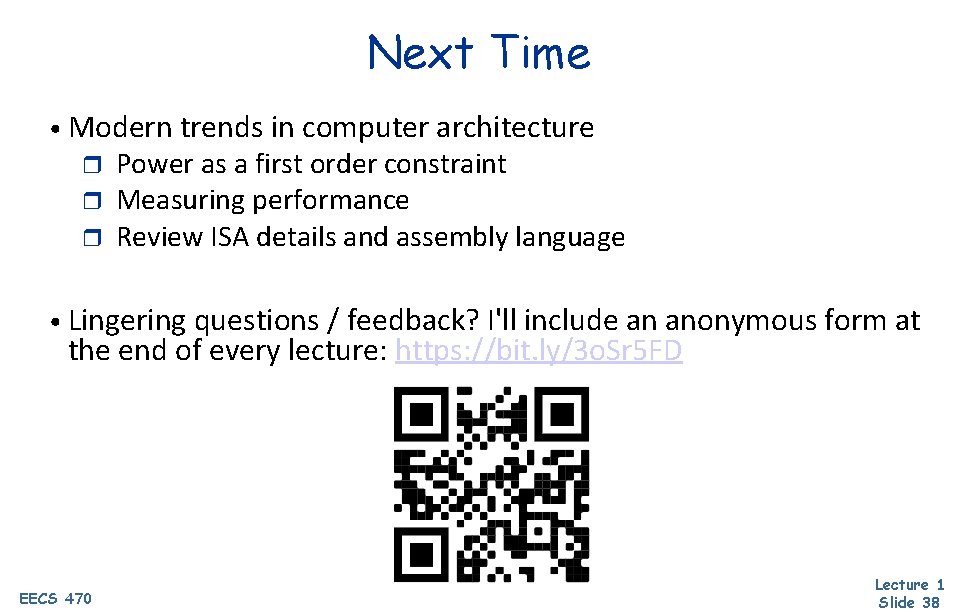

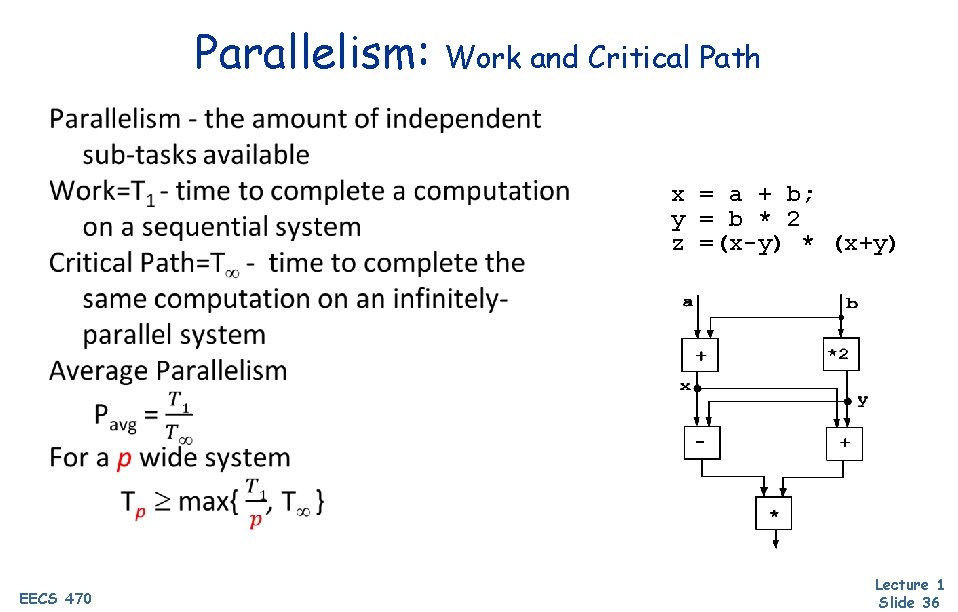

Parallelism: Work and Critical Path • x = a + b; y = b * 2 z =(x-y) * (x+y) EECS 470 Lecture 1 Slide 36

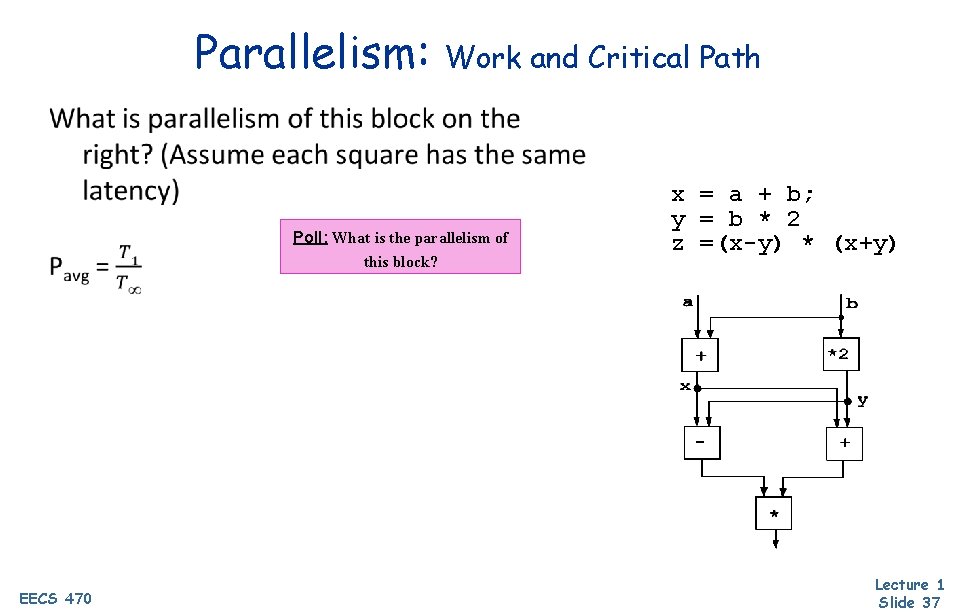

Parallelism: Work and Critical Path • Poll: What is the parallelism of this block? EECS 470 x = a + b; y = b * 2 z =(x-y) * (x+y) Lecture 1 Slide 37

Next Time • Modern trends in computer architecture r r r Power as a first order constraint Measuring performance Review ISA details and assembly language • Lingering questions / feedback? I'll include an anonymous form at the end of every lecture: https: //bit. ly/3 o. Sr 5 FD EECS 470 Lecture 1 Slide 38