ECE 545 Lecture 9 Memories RAM ROM Advanced

![Assert - syntax ASSERT condition [REPORT "message" [SEVERITY severity_level ]; The message is written Assert - syntax ASSERT condition [REPORT "message" [SEVERITY severity_level ]; The message is written](https://slidetodoc.com/presentation_image_h2/1de529e37649c97ef6ec5bb237a99165/image-53.jpg)

![Report - syntax REPORT "message" [SEVERITY severity_level ]; The message is always written. Severity_level Report - syntax REPORT "message" [SEVERITY severity_level ]; The message is always written. Severity_level](https://slidetodoc.com/presentation_image_h2/1de529e37649c97ef6ec5bb237a99165/image-55.jpg)

- Slides: 81

ECE 545 Lecture 9 Memories: RAM, ROM Advanced Testbenches ECE 545 – Introduction to VHDL George Mason University

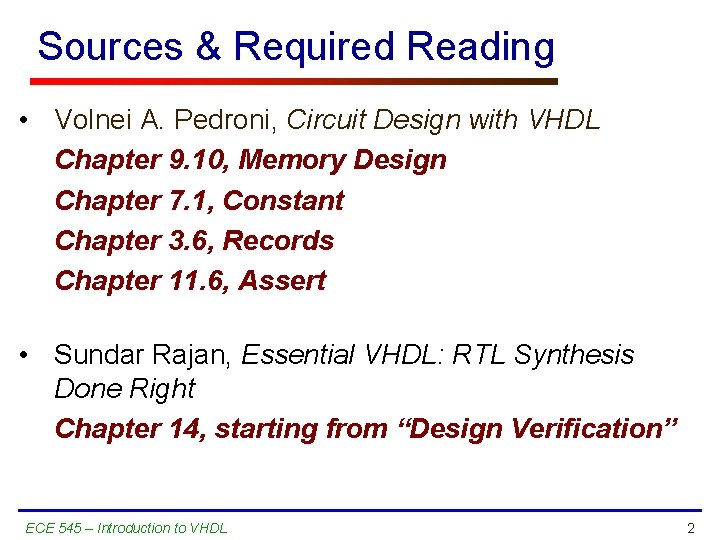

Sources & Required Reading • Volnei A. Pedroni, Circuit Design with VHDL Chapter 9. 10, Memory Design Chapter 7. 1, Constant Chapter 3. 6, Records Chapter 11. 6, Assert • Sundar Rajan, Essential VHDL: RTL Synthesis Done Right Chapter 14, starting from “Design Verification” ECE 545 – Introduction to VHDL 2

Generic Memories ECE 545 – Introduction to VHDL 3

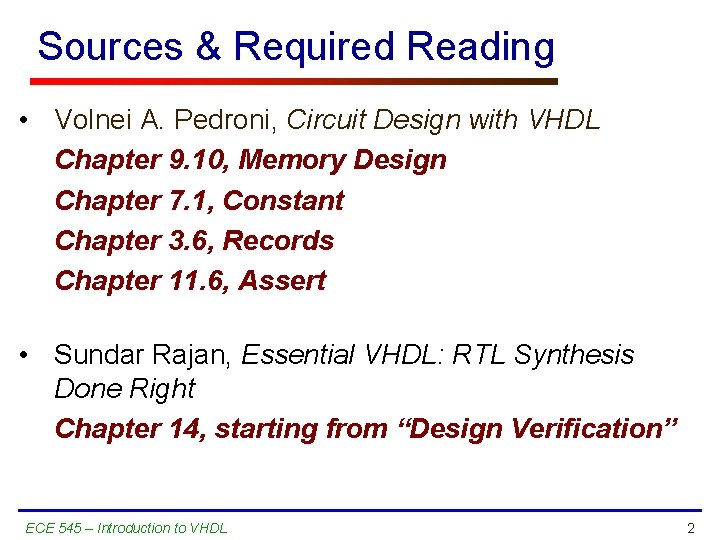

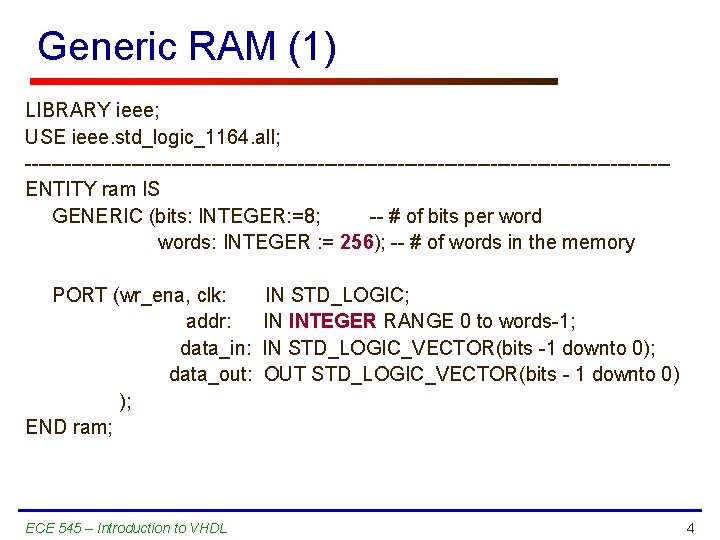

Generic RAM (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ------------------------------------------------ENTITY ram IS GENERIC (bits: INTEGER: =8; -- # of bits per words: INTEGER : = 256); -- # of words in the memory PORT (wr_ena, clk: addr: data_in: data_out: ); END ram; ECE 545 – Introduction to VHDL IN STD_LOGIC; IN INTEGER RANGE 0 to words-1; IN STD_LOGIC_VECTOR(bits -1 downto 0); OUT STD_LOGIC_VECTOR(bits - 1 downto 0) 4

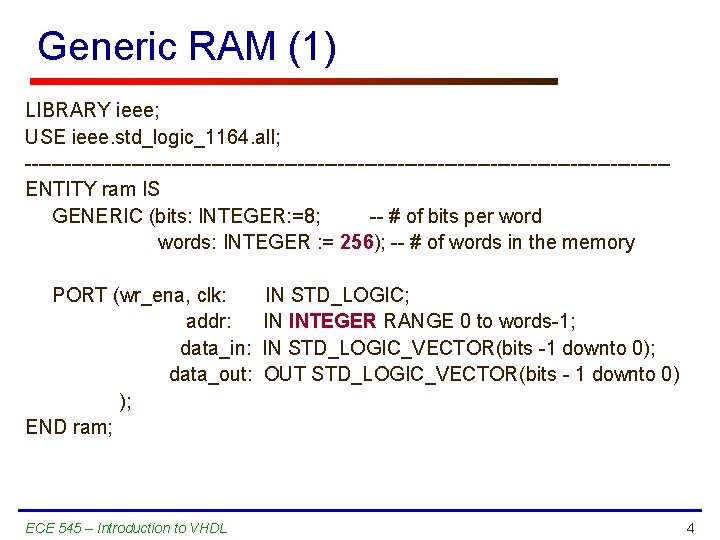

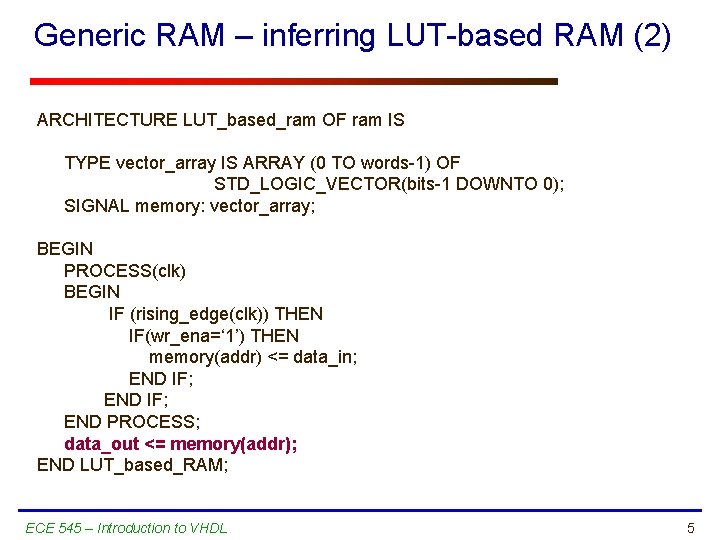

Generic RAM – inferring LUT-based RAM (2) ARCHITECTURE LUT_based_ram OF ram IS TYPE vector_array IS ARRAY (0 TO words-1) OF STD_LOGIC_VECTOR(bits-1 DOWNTO 0); SIGNAL memory: vector_array; BEGIN PROCESS(clk) BEGIN IF (rising_edge(clk)) THEN IF(wr_ena=‘ 1’) THEN memory(addr) <= data_in; END IF; END PROCESS; data_out <= memory(addr); END LUT_based_RAM; ECE 545 – Introduction to VHDL 5

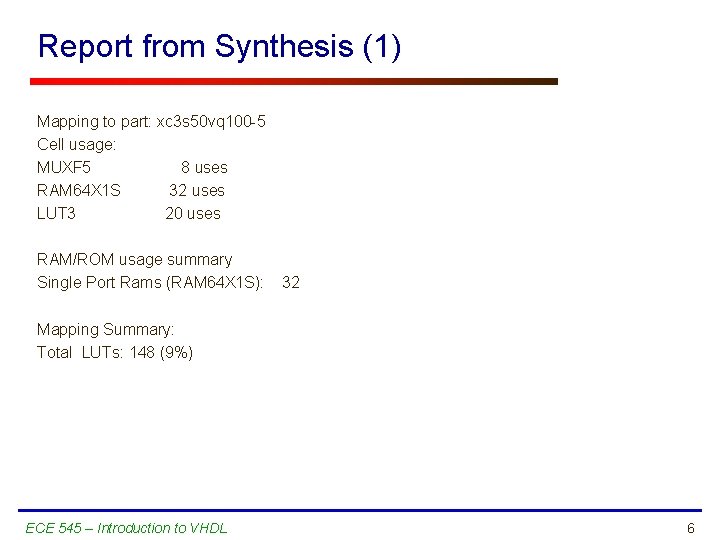

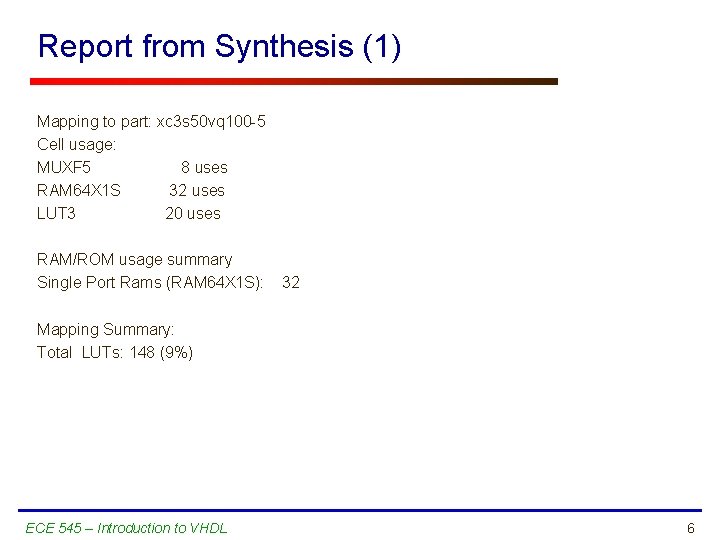

Report from Synthesis (1) Mapping to part: xc 3 s 50 vq 100 -5 Cell usage: MUXF 5 8 uses RAM 64 X 1 S 32 uses LUT 3 20 uses RAM/ROM usage summary Single Port Rams (RAM 64 X 1 S): 32 Mapping Summary: Total LUTs: 148 (9%) ECE 545 – Introduction to VHDL 6

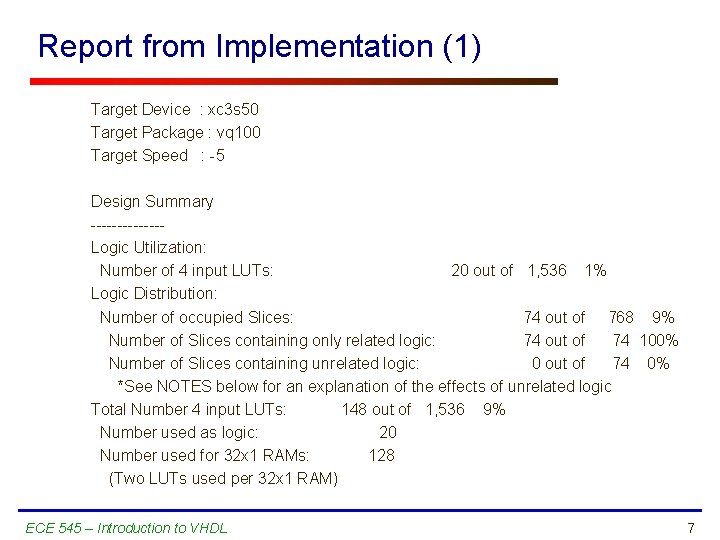

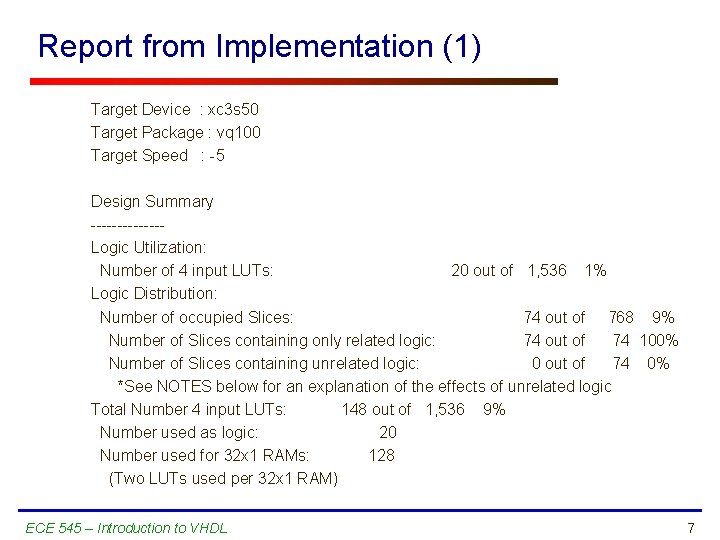

Report from Implementation (1) Target Device : xc 3 s 50 Target Package : vq 100 Target Speed : -5 Design Summary -------Logic Utilization: Number of 4 input LUTs: 20 out of 1, 536 1% Logic Distribution: Number of occupied Slices: 74 out of 768 9% Number of Slices containing only related logic: 74 out of 74 100% Number of Slices containing unrelated logic: 0 out of 74 0% *See NOTES below for an explanation of the effects of unrelated logic Total Number 4 input LUTs: 148 out of 1, 536 9% Number used as logic: 20 Number used for 32 x 1 RAMs: 128 (Two LUTs used per 32 x 1 RAM) ECE 545 – Introduction to VHDL 7

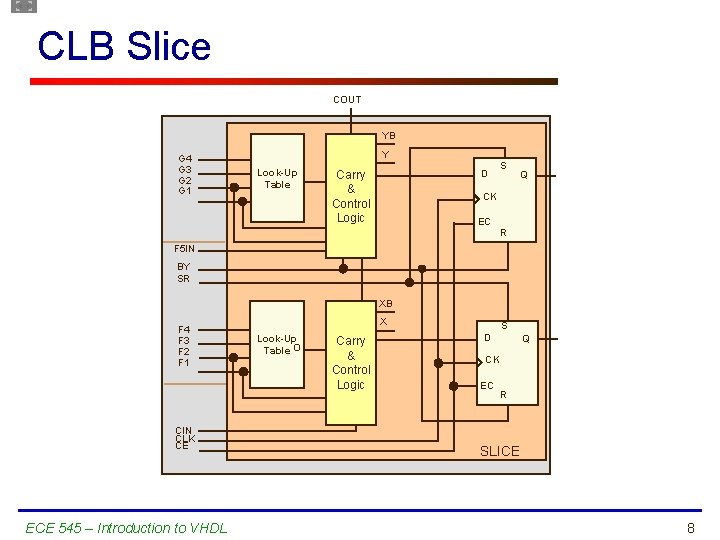

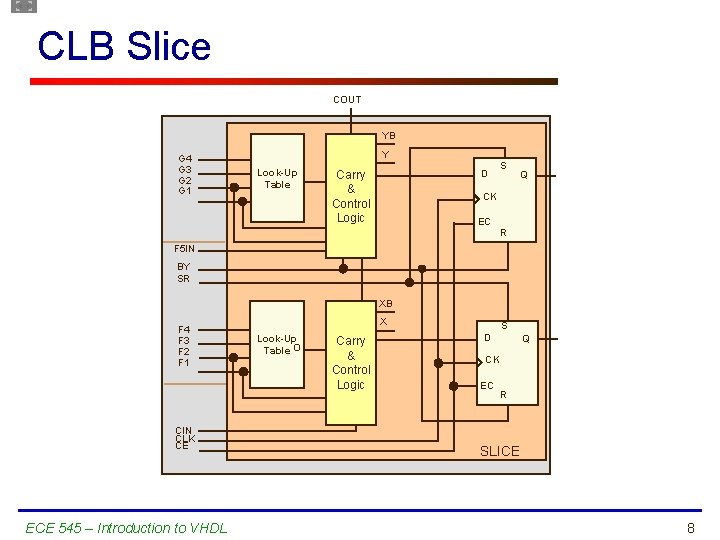

CLB Slice COUT YB G 4 G 3 G 2 G 1 Y Look-Up O Table D Carry & Control Logic S Q CK EC R F 5 IN BY SR XB F 4 F 3 F 2 F 1 CIN CLK CE ECE 545 – Introduction to VHDL X Look-Up Table O Carry & Control Logic S D Q CK EC R SLICE 8

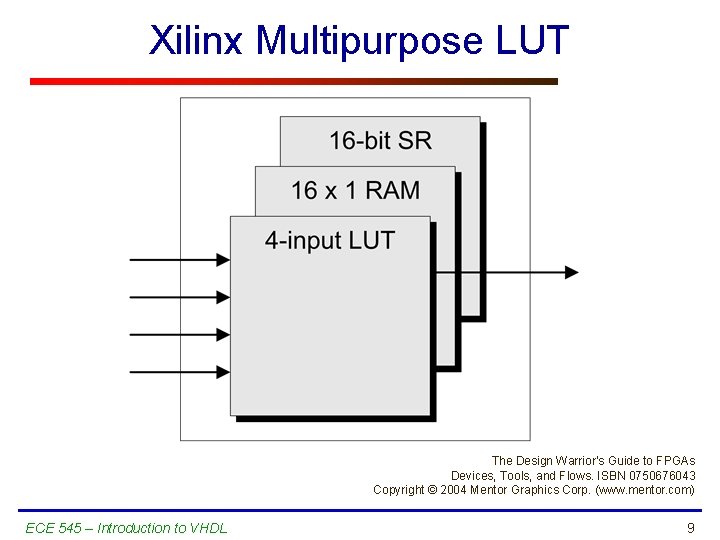

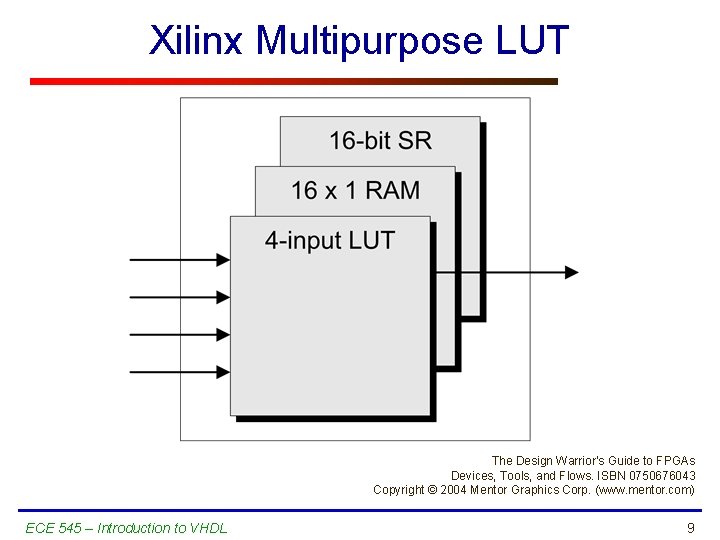

Xilinx Multipurpose LUT The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com) ECE 545 – Introduction to VHDL 9

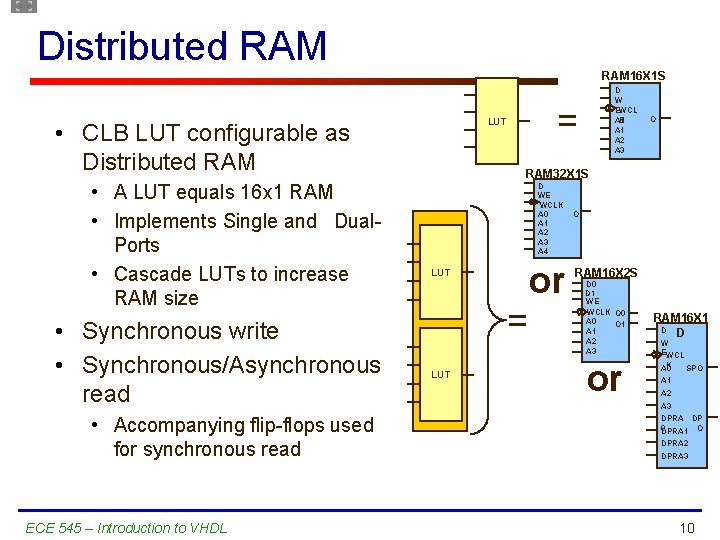

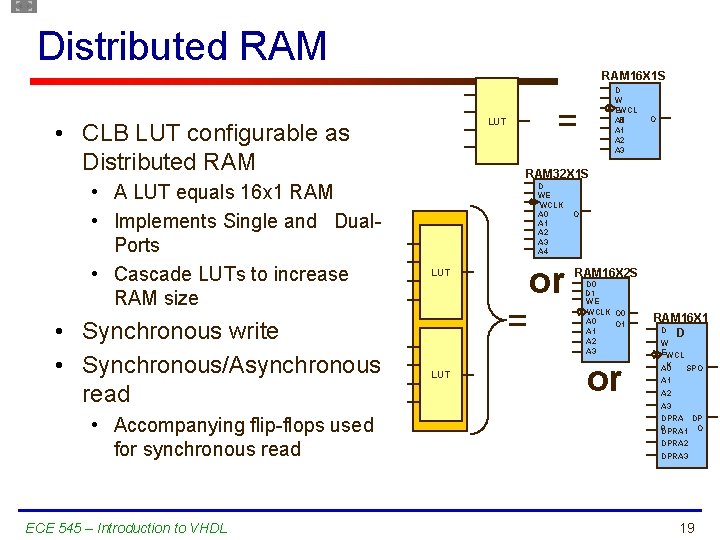

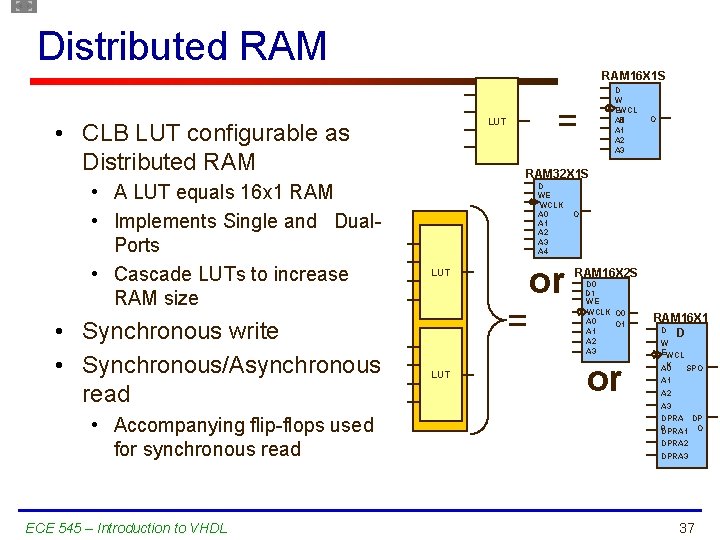

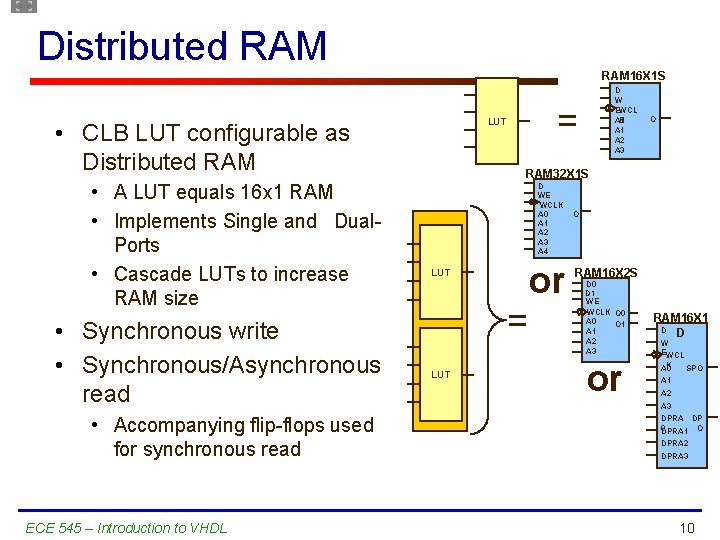

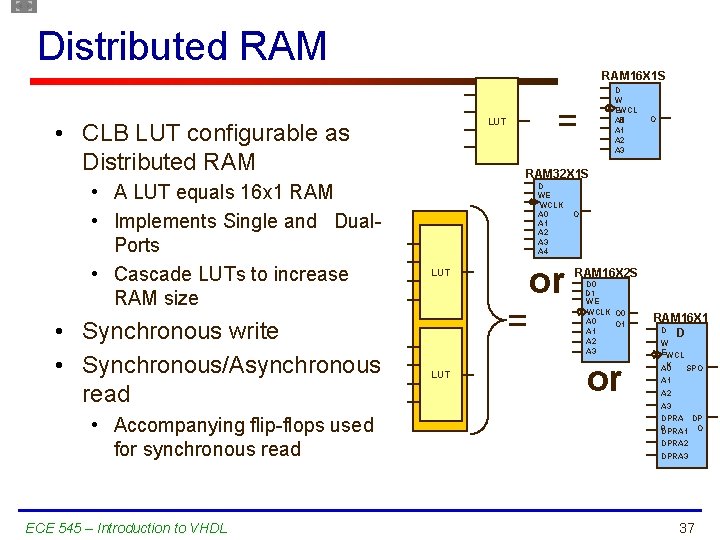

Distributed RAM 16 X 1 S • A LUT equals 16 x 1 RAM • Implements Single and Dual. Ports • Cascade LUTs to increase RAM size • Synchronous write • Synchronous/Asynchronous read • Accompanying flip-flops used for synchronous read ECE 545 – Introduction to VHDL = LUT • CLB LUT configurable as Distributed RAM D W EWCL K A 0 A 1 A 2 A 3 O RAM 32 X 1 S D WE WCLK A 0 A 1 A 2 A 3 A 4 LUT = LUT or O RAM 16 X 2 S D 0 D 1 WE WCLK O 0 A 0 O 1 A 2 A 3 or RAM 16 X 1 D D W EWCL K A 0 SPO A 1 A 2 A 3 DPRA DP 0 DPRA 1 O DPRA 2 DPRA 3 10

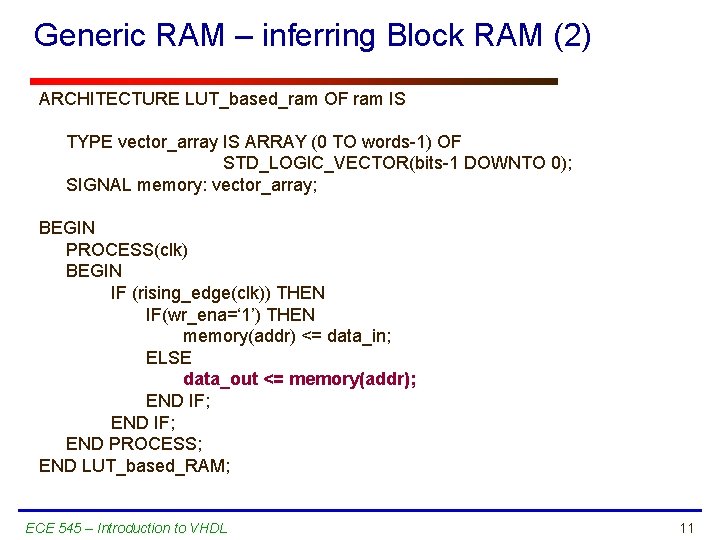

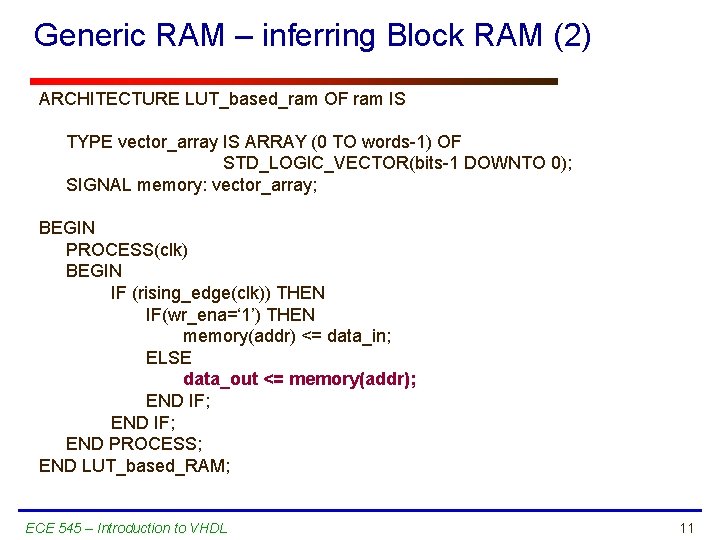

Generic RAM – inferring Block RAM (2) ARCHITECTURE LUT_based_ram OF ram IS TYPE vector_array IS ARRAY (0 TO words-1) OF STD_LOGIC_VECTOR(bits-1 DOWNTO 0); SIGNAL memory: vector_array; BEGIN PROCESS(clk) BEGIN IF (rising_edge(clk)) THEN IF(wr_ena=‘ 1’) THEN memory(addr) <= data_in; ELSE data_out <= memory(addr); END IF; END PROCESS; END LUT_based_RAM; ECE 545 – Introduction to VHDL 11

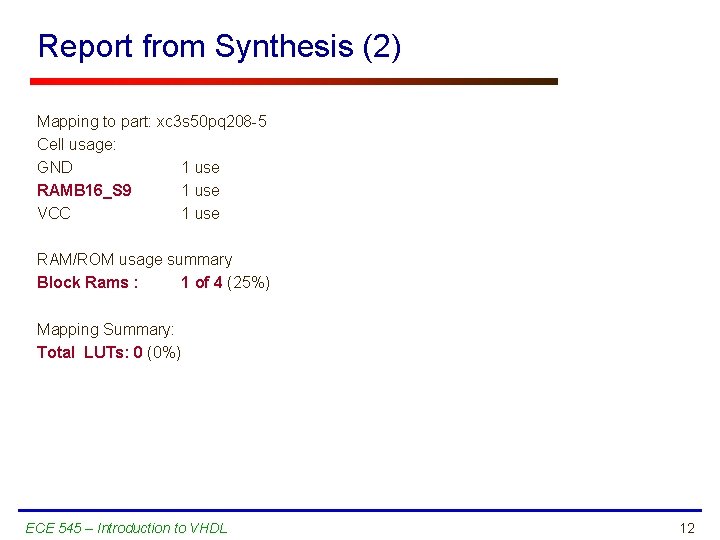

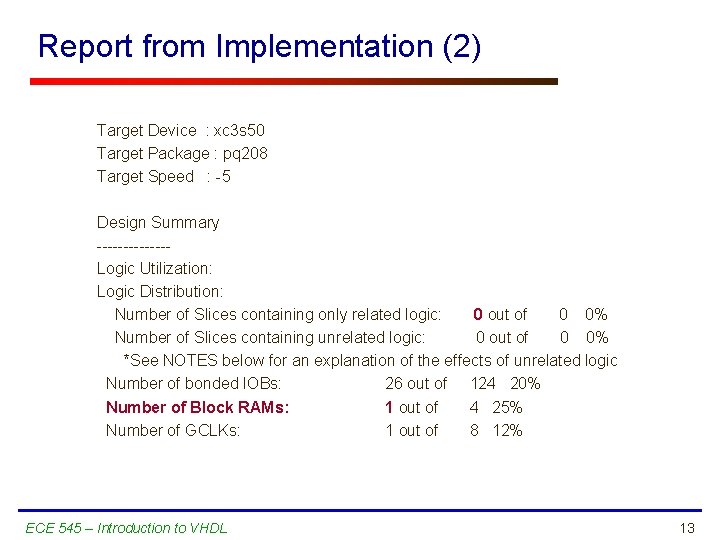

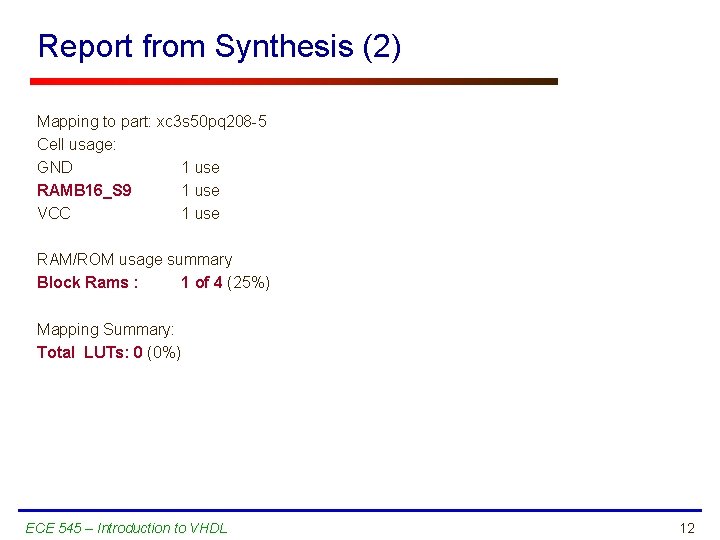

Report from Synthesis (2) Mapping to part: xc 3 s 50 pq 208 -5 Cell usage: GND 1 use RAMB 16_S 9 1 use VCC 1 use RAM/ROM usage summary Block Rams : 1 of 4 (25%) Mapping Summary: Total LUTs: 0 (0%) ECE 545 – Introduction to VHDL 12

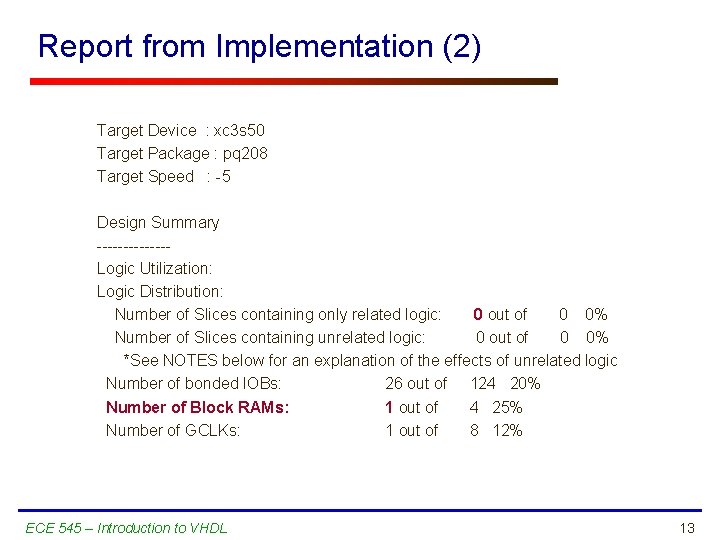

Report from Implementation (2) Target Device : xc 3 s 50 Target Package : pq 208 Target Speed : -5 Design Summary -------Logic Utilization: Logic Distribution: Number of Slices containing only related logic: 0 out of 0 0% Number of Slices containing unrelated logic: 0 out of 0 0% *See NOTES below for an explanation of the effects of unrelated logic Number of bonded IOBs: 26 out of 124 20% Number of Block RAMs: 1 out of 4 25% Number of GCLKs: 1 out of 8 12% ECE 545 – Introduction to VHDL 13

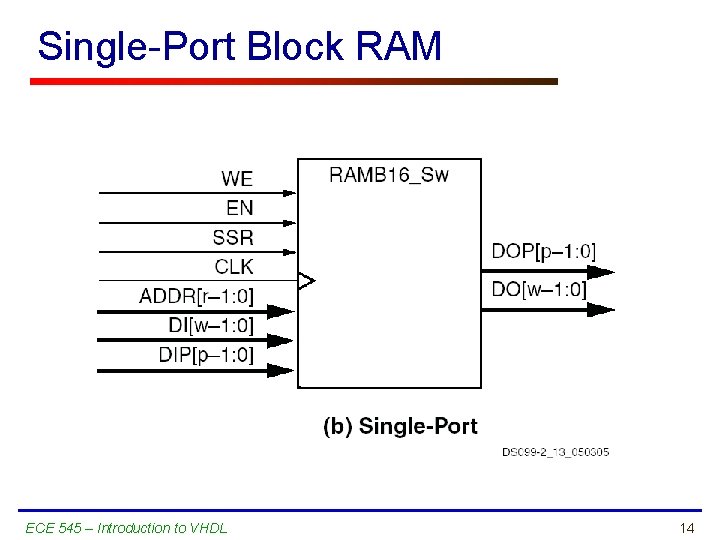

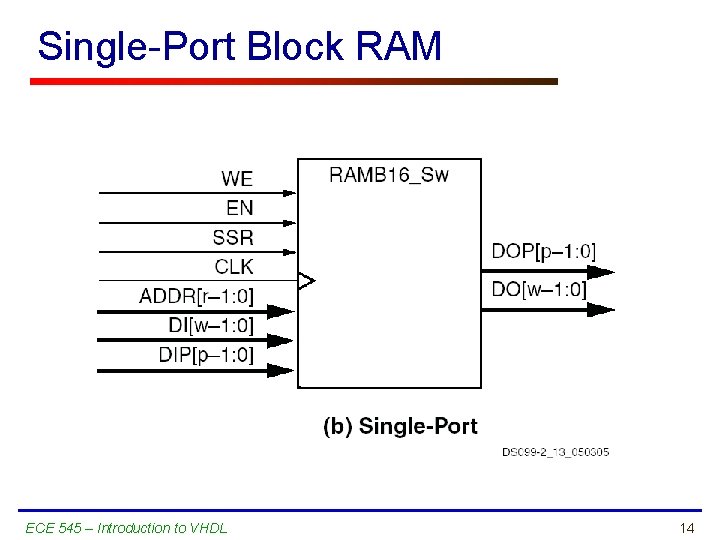

Single-Port Block RAM ECE 545 – Introduction to VHDL 14

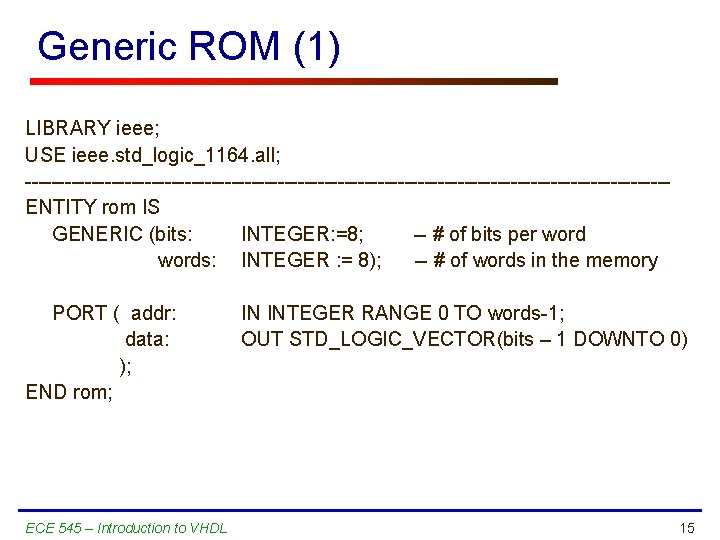

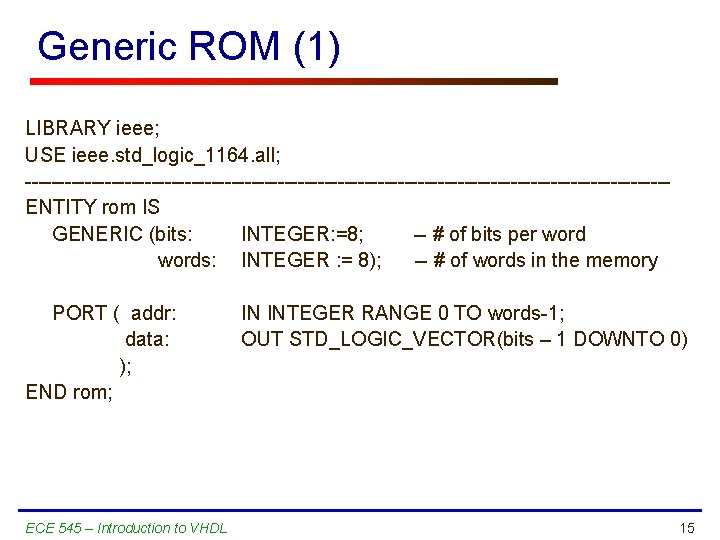

Generic ROM (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ------------------------------------------------ENTITY rom IS GENERIC (bits: INTEGER: =8; -- # of bits per words: INTEGER : = 8); -- # of words in the memory PORT ( addr: data: ); END rom; ECE 545 – Introduction to VHDL IN INTEGER RANGE 0 TO words-1; OUT STD_LOGIC_VECTOR(bits – 1 DOWNTO 0) 15

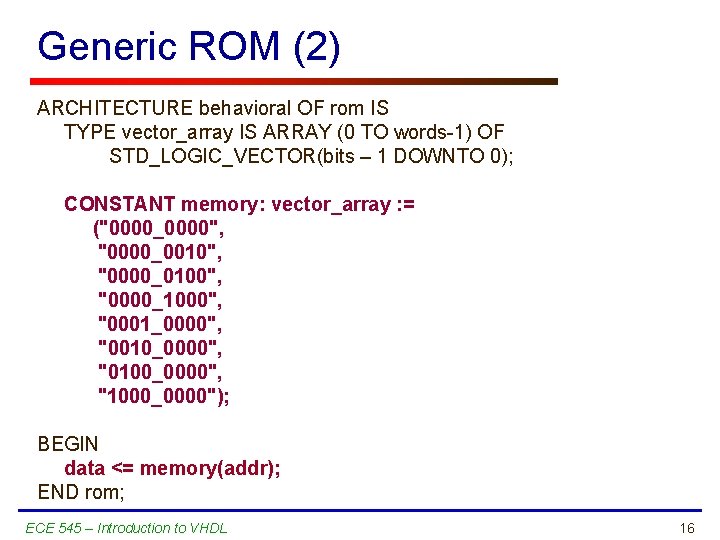

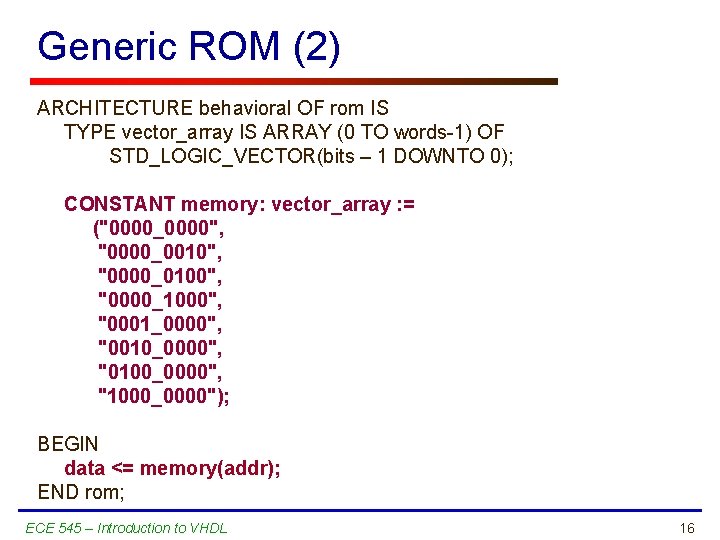

Generic ROM (2) ARCHITECTURE behavioral OF rom IS TYPE vector_array IS ARRAY (0 TO words-1) OF STD_LOGIC_VECTOR(bits – 1 DOWNTO 0); CONSTANT memory: vector_array : = ("0000_0000", "0000_0010", "0000_0100", "0000_1000", "0001_0000", "0010_0000", "0100_0000", "1000_0000"); BEGIN data <= memory(addr); END rom; ECE 545 – Introduction to VHDL 16

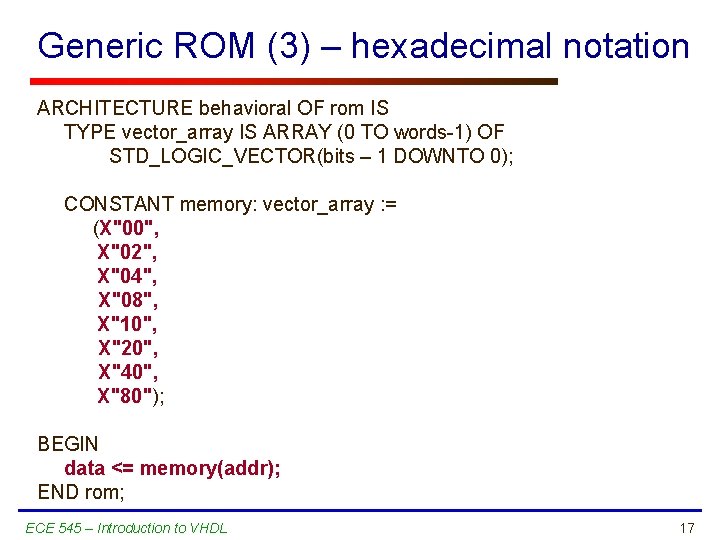

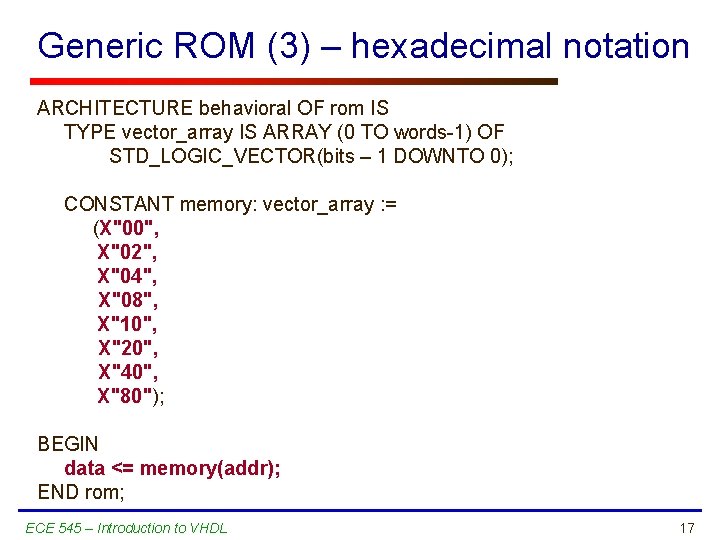

Generic ROM (3) – hexadecimal notation ARCHITECTURE behavioral OF rom IS TYPE vector_array IS ARRAY (0 TO words-1) OF STD_LOGIC_VECTOR(bits – 1 DOWNTO 0); CONSTANT memory: vector_array : = (X"00", X"02", X"04", X"08", X"10", X"20", X"40", X"80"); BEGIN data <= memory(addr); END rom; ECE 545 – Introduction to VHDL 17

FPGA specific memories ECE 545 – Introduction to VHDL 18

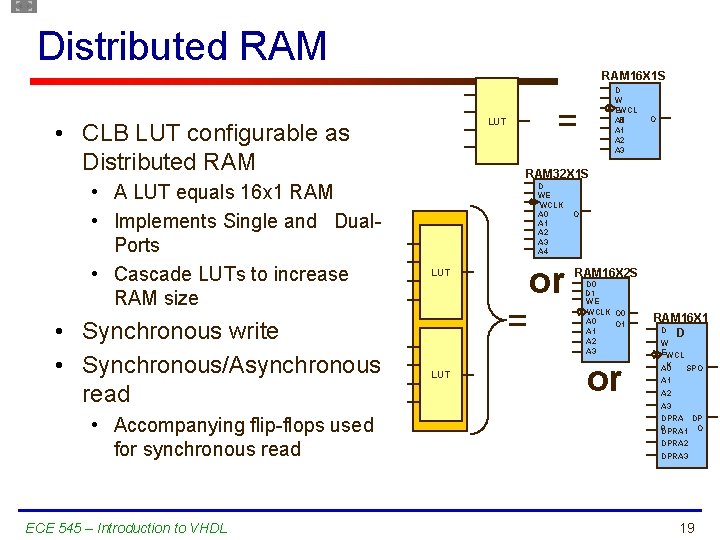

Distributed RAM 16 X 1 S • A LUT equals 16 x 1 RAM • Implements Single and Dual. Ports • Cascade LUTs to increase RAM size • Synchronous write • Synchronous/Asynchronous read • Accompanying flip-flops used for synchronous read ECE 545 – Introduction to VHDL = LUT • CLB LUT configurable as Distributed RAM D W EWCL K A 0 A 1 A 2 A 3 O RAM 32 X 1 S D WE WCLK A 0 A 1 A 2 A 3 A 4 LUT = LUT or O RAM 16 X 2 S D 0 D 1 WE WCLK O 0 A 0 O 1 A 2 A 3 or RAM 16 X 1 D D W EWCL K A 0 SPO A 1 A 2 A 3 DPRA DP 0 DPRA 1 O DPRA 2 DPRA 3 19

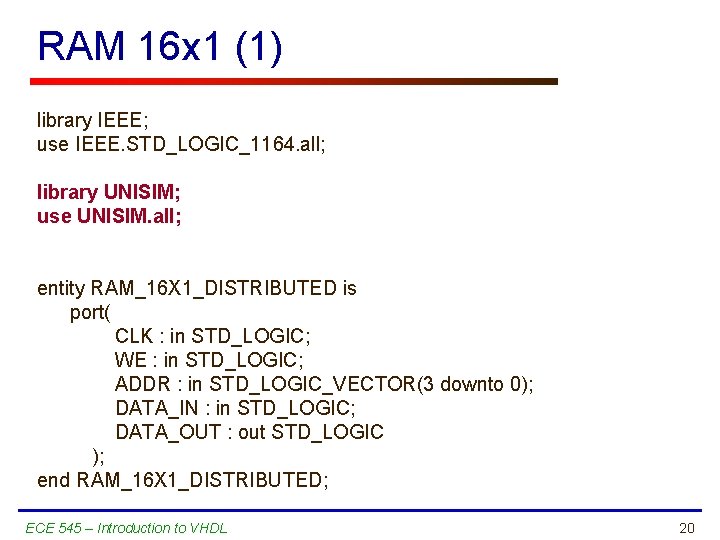

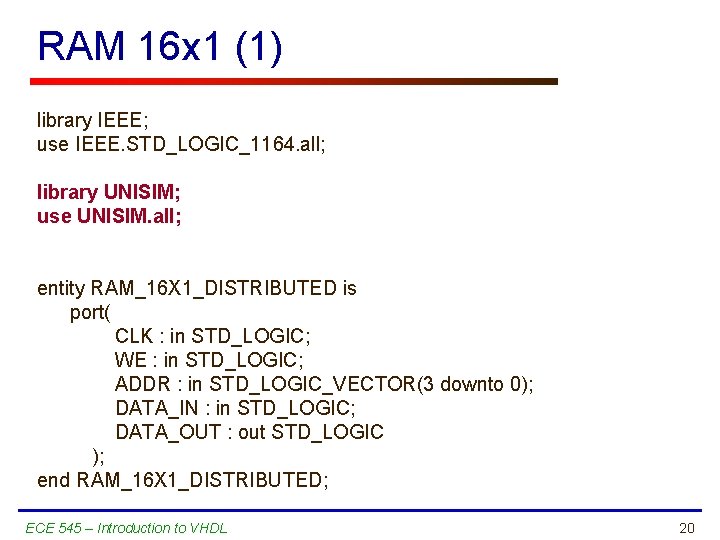

RAM 16 x 1 (1) library IEEE; use IEEE. STD_LOGIC_1164. all; library UNISIM; use UNISIM. all; entity RAM_16 X 1_DISTRIBUTED is port( CLK : in STD_LOGIC; WE : in STD_LOGIC; ADDR : in STD_LOGIC_VECTOR(3 downto 0); DATA_IN : in STD_LOGIC; DATA_OUT : out STD_LOGIC ); end RAM_16 X 1_DISTRIBUTED; ECE 545 – Introduction to VHDL 20

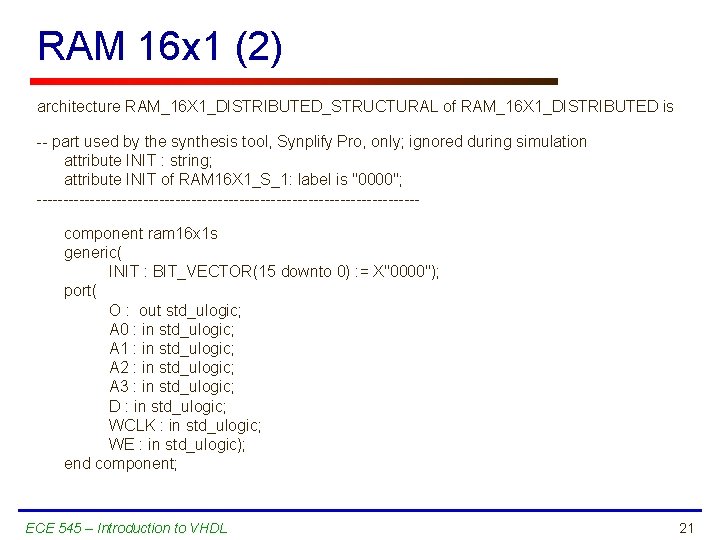

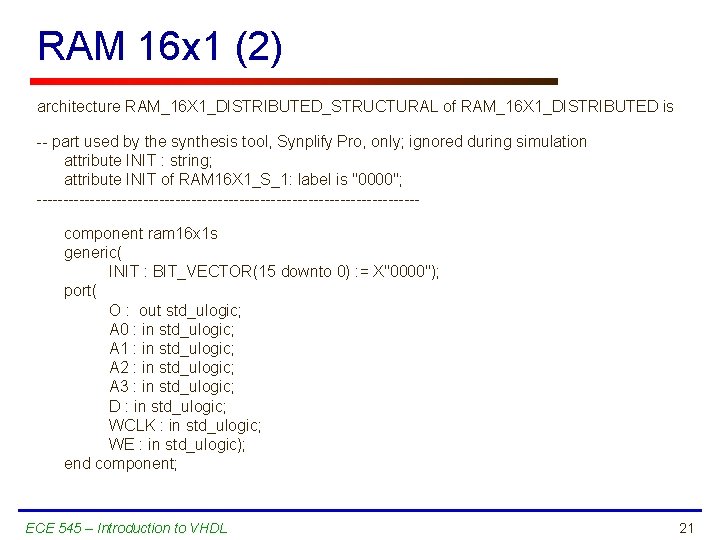

RAM 16 x 1 (2) architecture RAM_16 X 1_DISTRIBUTED_STRUCTURAL of RAM_16 X 1_DISTRIBUTED is -- part used by the synthesis tool, Synplify Pro, only; ignored during simulation attribute INIT : string; attribute INIT of RAM 16 X 1_S_1: label is "0000"; ------------------------------------component ram 16 x 1 s generic( INIT : BIT_VECTOR(15 downto 0) : = X"0000"); port( O : out std_ulogic; A 0 : in std_ulogic; A 1 : in std_ulogic; A 2 : in std_ulogic; A 3 : in std_ulogic; D : in std_ulogic; WCLK : in std_ulogic; WE : in std_ulogic); end component; ECE 545 – Introduction to VHDL 21

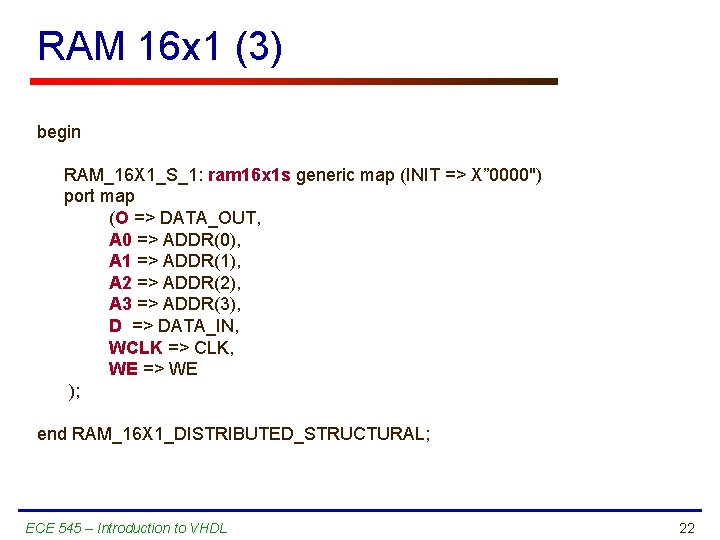

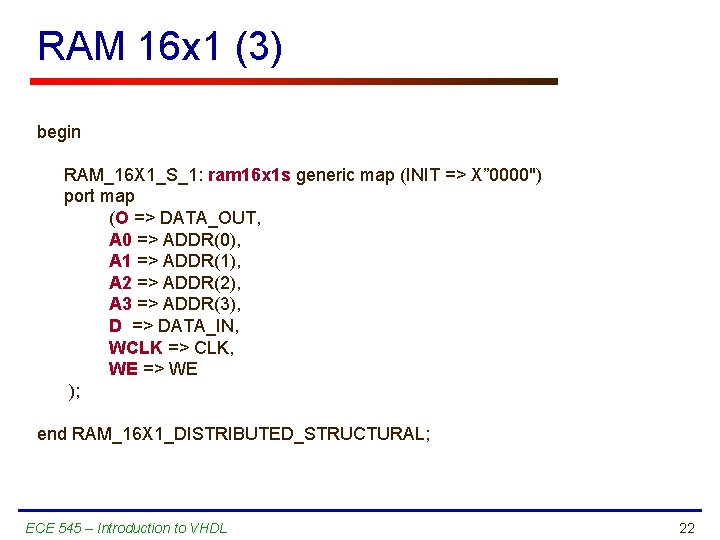

RAM 16 x 1 (3) begin RAM_16 X 1_S_1: ram 16 x 1 s generic map (INIT => X” 0000") port map (O => DATA_OUT, A 0 => ADDR(0), A 1 => ADDR(1), A 2 => ADDR(2), A 3 => ADDR(3), D => DATA_IN, WCLK => CLK, WE => WE ); end RAM_16 X 1_DISTRIBUTED_STRUCTURAL; ECE 545 – Introduction to VHDL 22

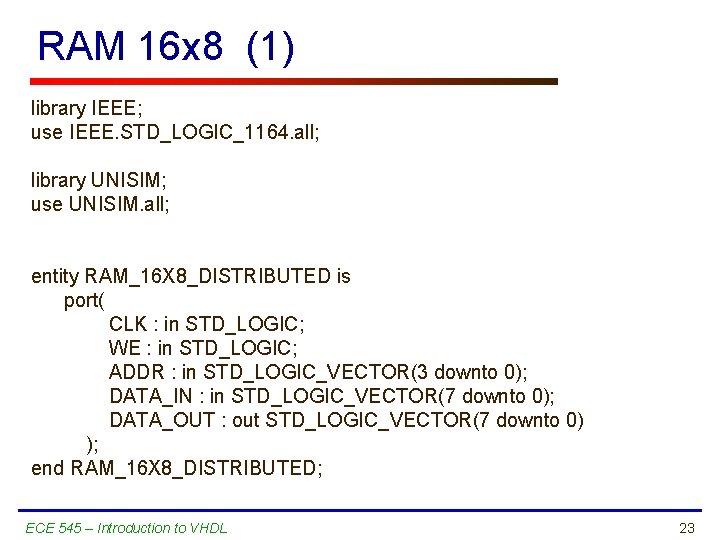

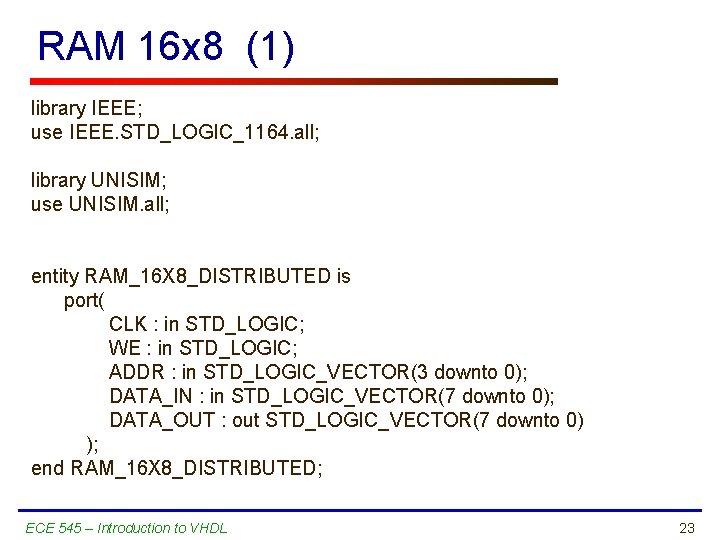

RAM 16 x 8 (1) library IEEE; use IEEE. STD_LOGIC_1164. all; library UNISIM; use UNISIM. all; entity RAM_16 X 8_DISTRIBUTED is port( CLK : in STD_LOGIC; WE : in STD_LOGIC; ADDR : in STD_LOGIC_VECTOR(3 downto 0); DATA_IN : in STD_LOGIC_VECTOR(7 downto 0); DATA_OUT : out STD_LOGIC_VECTOR(7 downto 0) ); end RAM_16 X 8_DISTRIBUTED; ECE 545 – Introduction to VHDL 23

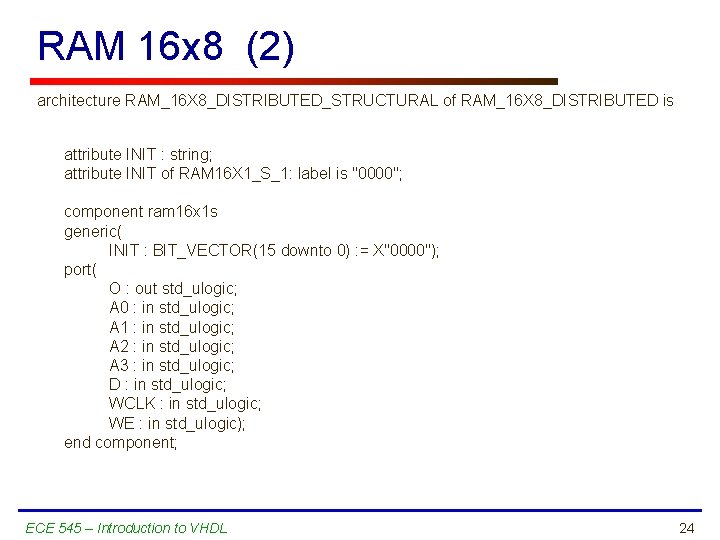

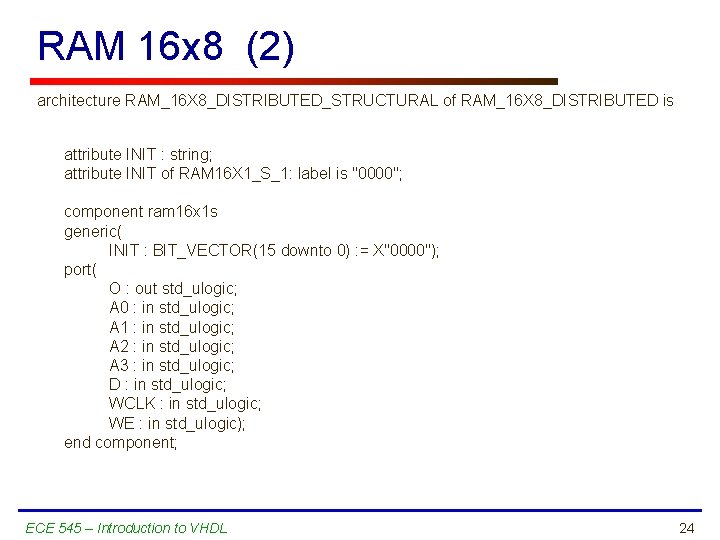

RAM 16 x 8 (2) architecture RAM_16 X 8_DISTRIBUTED_STRUCTURAL of RAM_16 X 8_DISTRIBUTED is attribute INIT : string; attribute INIT of RAM 16 X 1_S_1: label is "0000"; component ram 16 x 1 s generic( INIT : BIT_VECTOR(15 downto 0) : = X"0000"); port( O : out std_ulogic; A 0 : in std_ulogic; A 1 : in std_ulogic; A 2 : in std_ulogic; A 3 : in std_ulogic; D : in std_ulogic; WCLK : in std_ulogic; WE : in std_ulogic); end component; ECE 545 – Introduction to VHDL 24

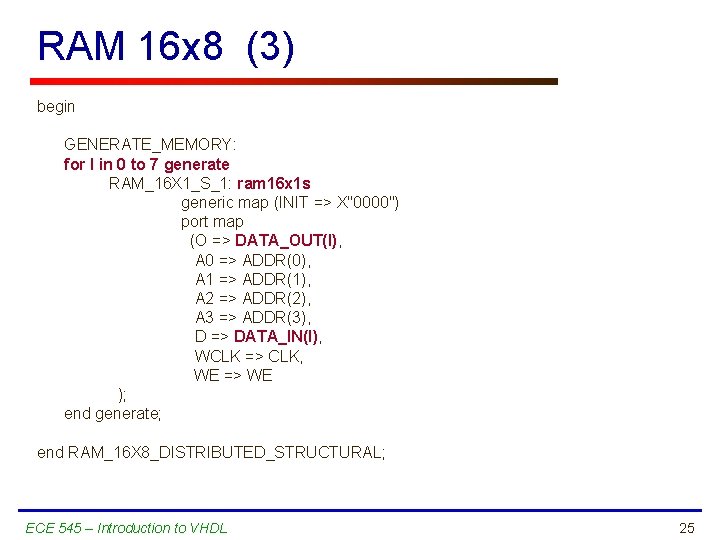

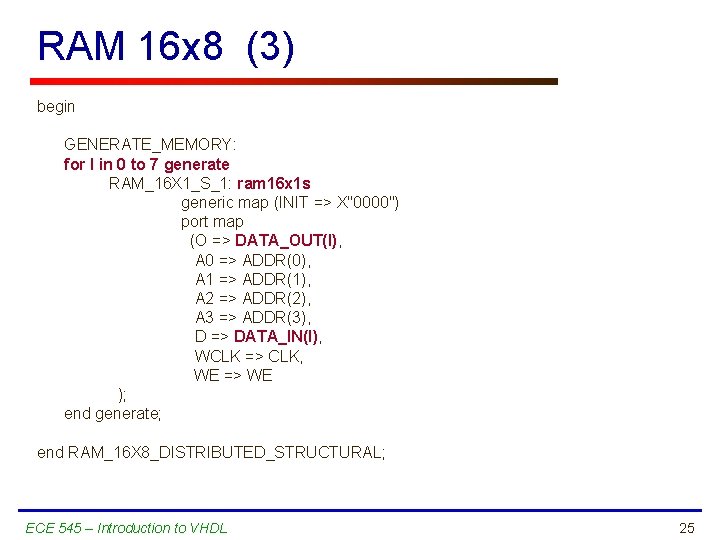

RAM 16 x 8 (3) begin GENERATE_MEMORY: for I in 0 to 7 generate RAM_16 X 1_S_1: ram 16 x 1 s generic map (INIT => X"0000") port map (O => DATA_OUT(I), A 0 => ADDR(0), A 1 => ADDR(1), A 2 => ADDR(2), A 3 => ADDR(3), D => DATA_IN(I), WCLK => CLK, WE => WE ); end generate; end RAM_16 X 8_DISTRIBUTED_STRUCTURAL; ECE 545 – Introduction to VHDL 25

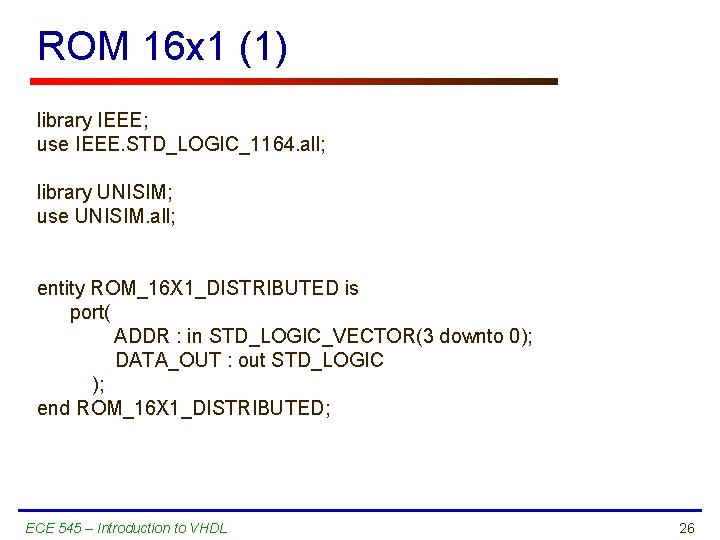

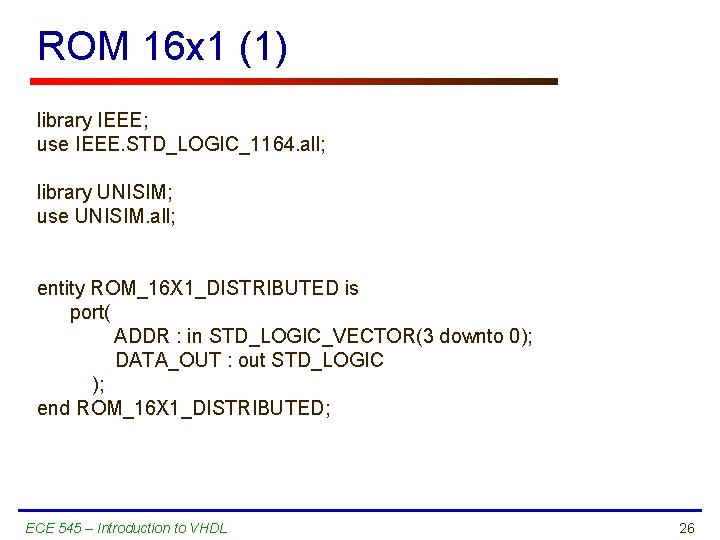

ROM 16 x 1 (1) library IEEE; use IEEE. STD_LOGIC_1164. all; library UNISIM; use UNISIM. all; entity ROM_16 X 1_DISTRIBUTED is port( ADDR : in STD_LOGIC_VECTOR(3 downto 0); DATA_OUT : out STD_LOGIC ); end ROM_16 X 1_DISTRIBUTED; ECE 545 – Introduction to VHDL 26

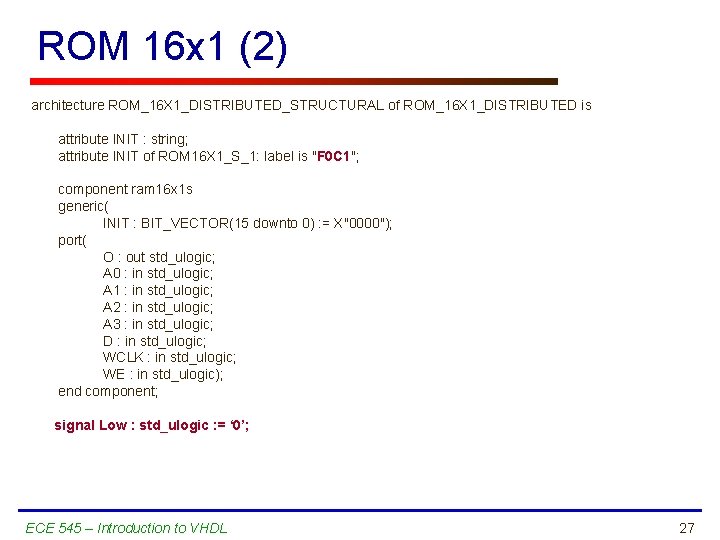

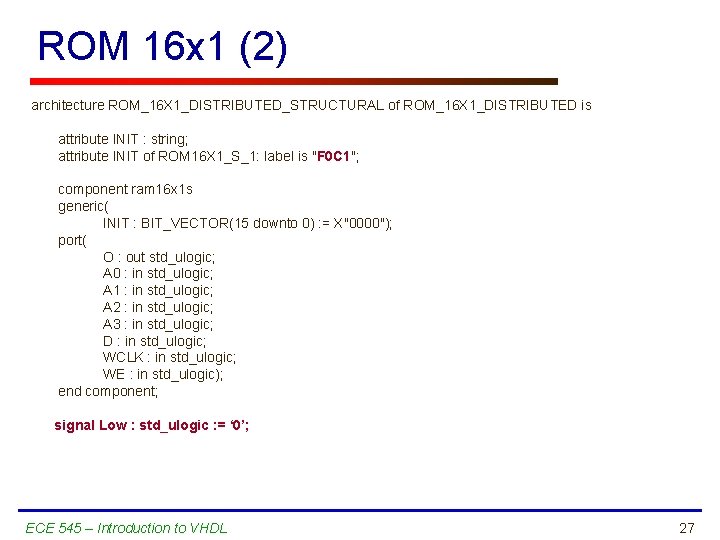

ROM 16 x 1 (2) architecture ROM_16 X 1_DISTRIBUTED_STRUCTURAL of ROM_16 X 1_DISTRIBUTED is attribute INIT : string; attribute INIT of ROM 16 X 1_S_1: label is "F 0 C 1"; component ram 16 x 1 s generic( INIT : BIT_VECTOR(15 downto 0) : = X"0000"); port( O : out std_ulogic; A 0 : in std_ulogic; A 1 : in std_ulogic; A 2 : in std_ulogic; A 3 : in std_ulogic; D : in std_ulogic; WCLK : in std_ulogic; WE : in std_ulogic); end component; signal Low : std_ulogic : = ‘ 0’; ECE 545 – Introduction to VHDL 27

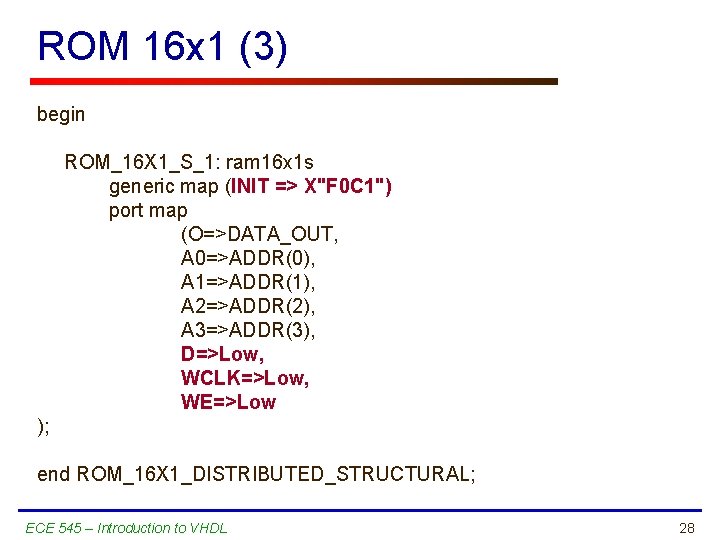

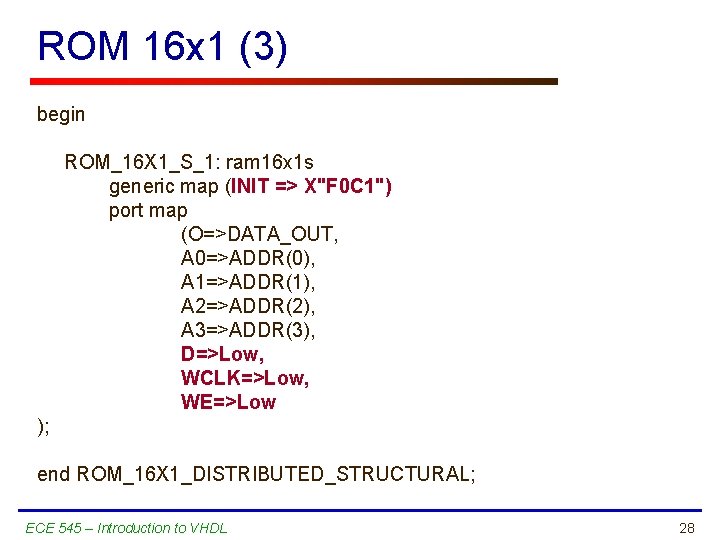

ROM 16 x 1 (3) begin ROM_16 X 1_S_1: ram 16 x 1 s generic map (INIT => X"F 0 C 1") port map (O=>DATA_OUT, A 0=>ADDR(0), A 1=>ADDR(1), A 2=>ADDR(2), A 3=>ADDR(3), D=>Low, WCLK=>Low, WE=>Low ); end ROM_16 X 1_DISTRIBUTED_STRUCTURAL; ECE 545 – Introduction to VHDL 28

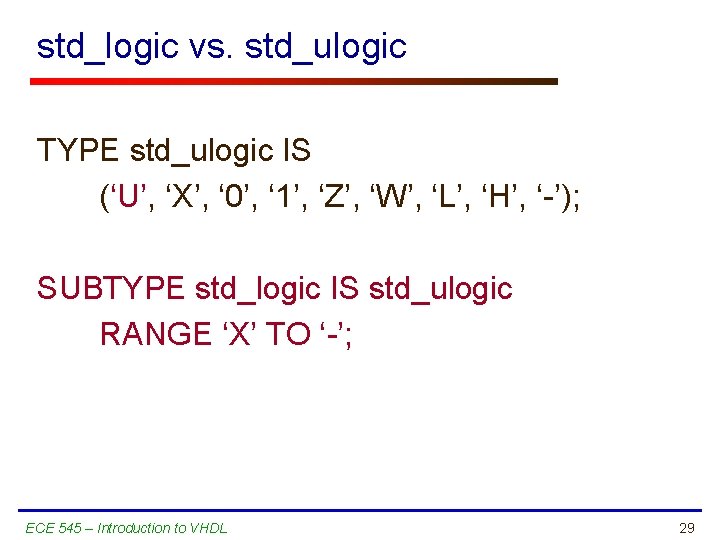

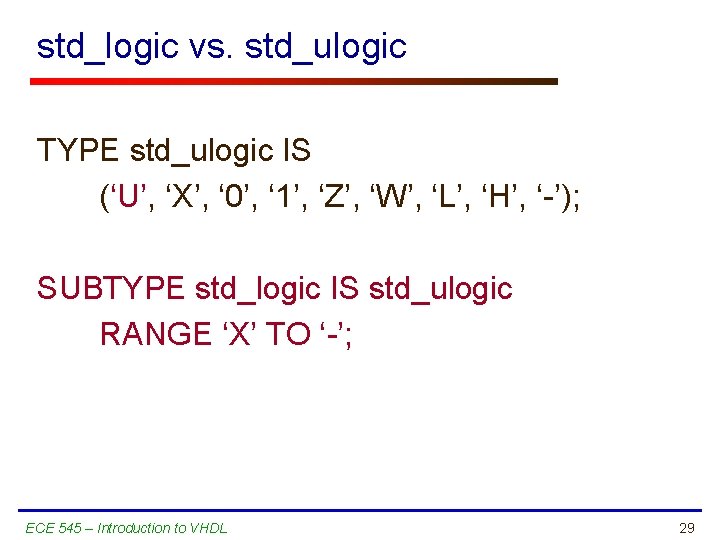

std_logic vs. std_ulogic TYPE std_ulogic IS (‘U’, ‘X’, ‘ 0’, ‘ 1’, ‘Z’, ‘W’, ‘L’, ‘H’, ‘-’); SUBTYPE std_logic IS std_ulogic RANGE ‘X’ TO ‘-’; ECE 545 – Introduction to VHDL 29

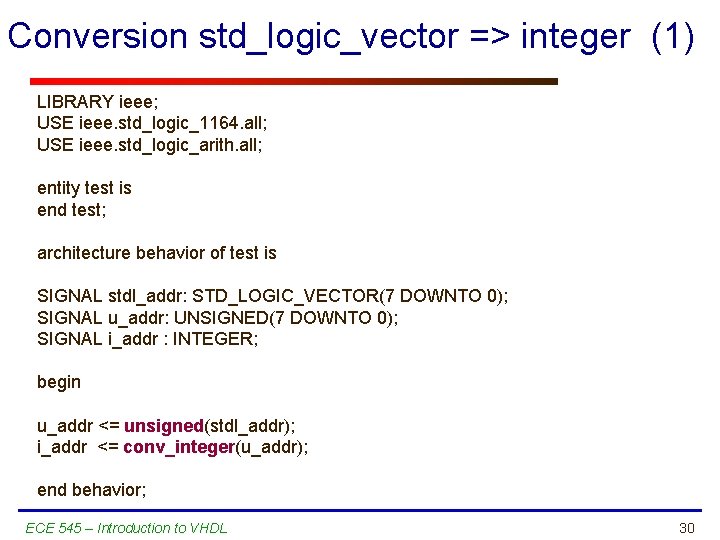

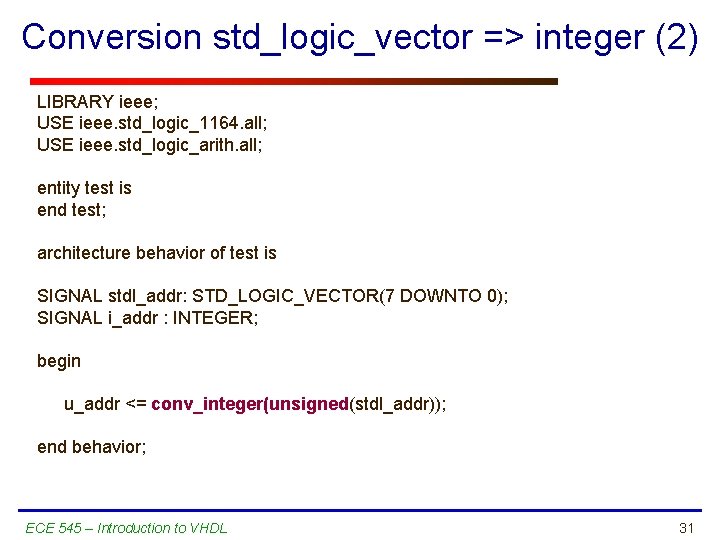

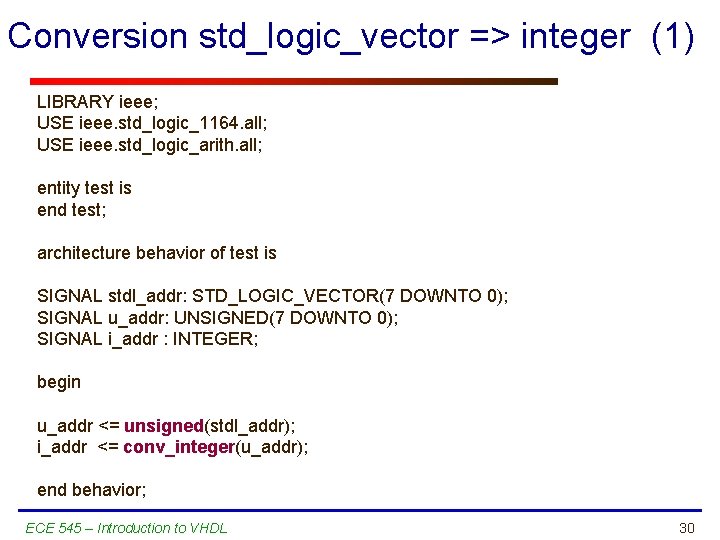

Conversion std_logic_vector => integer (1) LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_arith. all; entity test is end test; architecture behavior of test is SIGNAL stdl_addr: STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL u_addr: UNSIGNED(7 DOWNTO 0); SIGNAL i_addr : INTEGER; begin u_addr <= unsigned(stdl_addr); i_addr <= conv_integer(u_addr); end behavior; ECE 545 – Introduction to VHDL 30

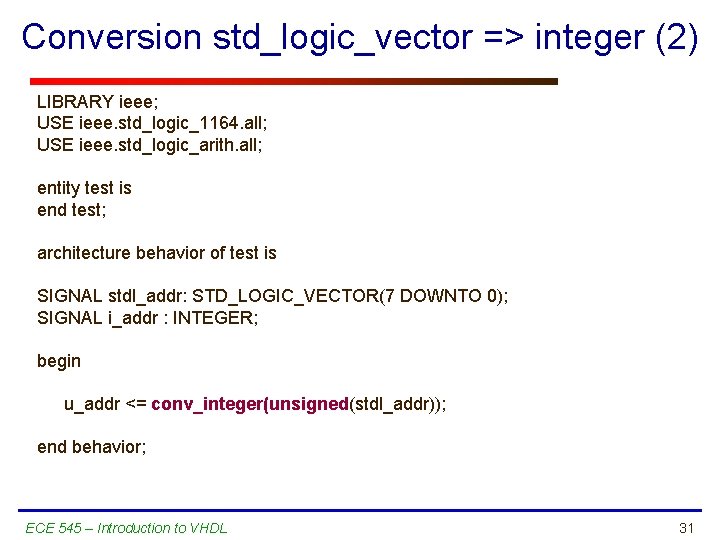

Conversion std_logic_vector => integer (2) LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_arith. all; entity test is end test; architecture behavior of test is SIGNAL stdl_addr: STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL i_addr : INTEGER; begin u_addr <= conv_integer(unsigned(stdl_addr)); end behavior; ECE 545 – Introduction to VHDL 31

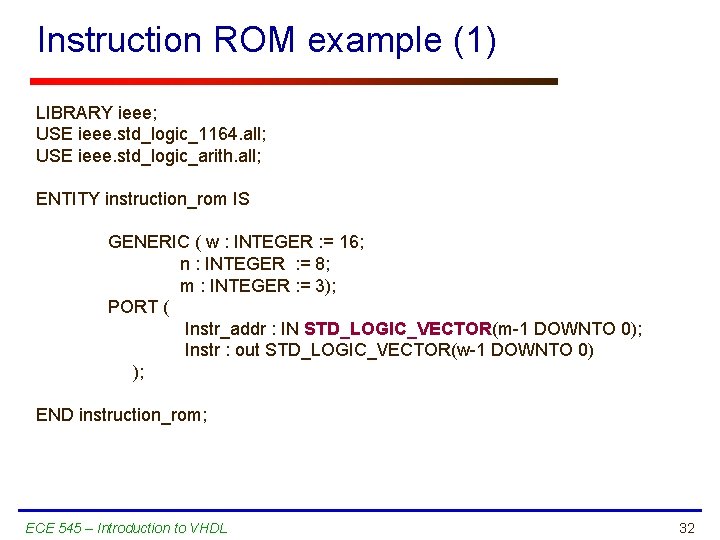

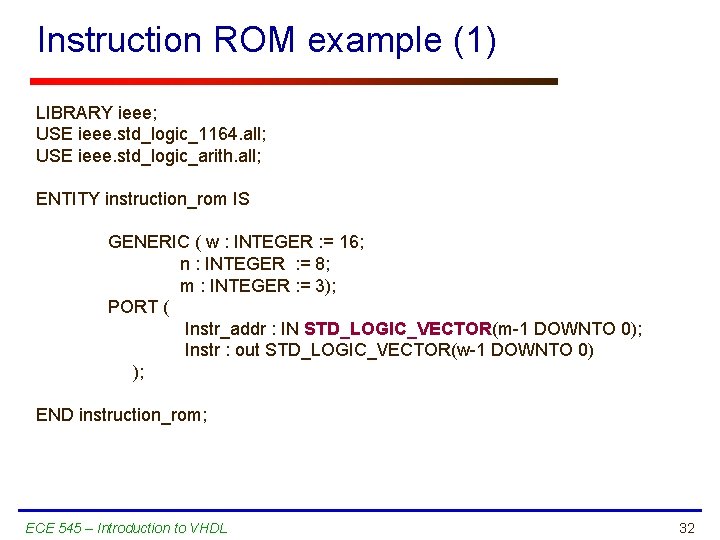

Instruction ROM example (1) LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_arith. all; ENTITY instruction_rom IS GENERIC ( w : INTEGER : = 16; n : INTEGER : = 8; m : INTEGER : = 3); PORT ( Instr_addr : IN STD_LOGIC_VECTOR(m-1 DOWNTO 0); Instr : out STD_LOGIC_VECTOR(w-1 DOWNTO 0) ); END instruction_rom; ECE 545 – Introduction to VHDL 32

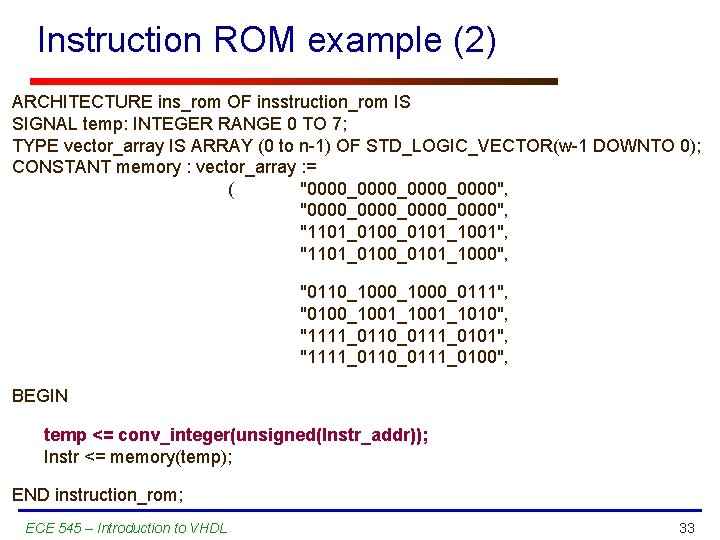

Instruction ROM example (2) ARCHITECTURE ins_rom OF insstruction_rom IS SIGNAL temp: INTEGER RANGE 0 TO 7; TYPE vector_array IS ARRAY (0 to n-1) OF STD_LOGIC_VECTOR(w-1 DOWNTO 0); CONSTANT memory : vector_array : = ( "0000_0000_0000_0000", "1101_0100_0101_1001", "1101_0100_0101_1000", "0110_1000_0111", "0100_1001_1010", "1111_0110_0111_0101", "1111_0110_0111_0100", BEGIN temp <= conv_integer(unsigned(Instr_addr)); Instr <= memory(temp); END instruction_rom; ECE 545 – Introduction to VHDL 33

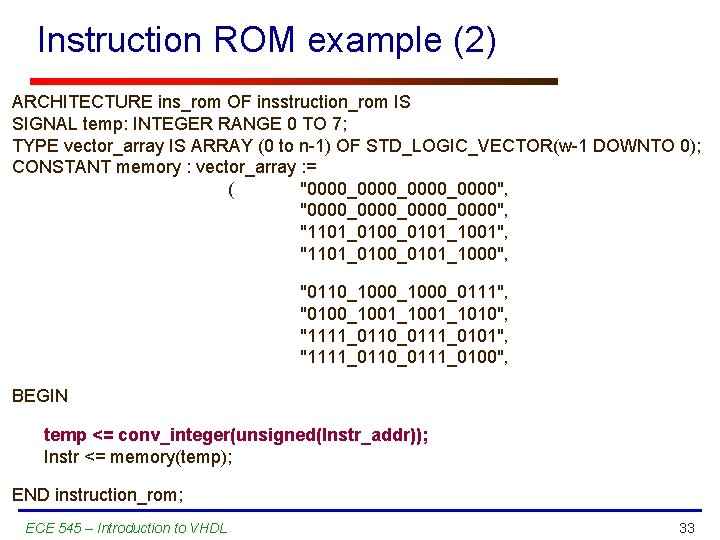

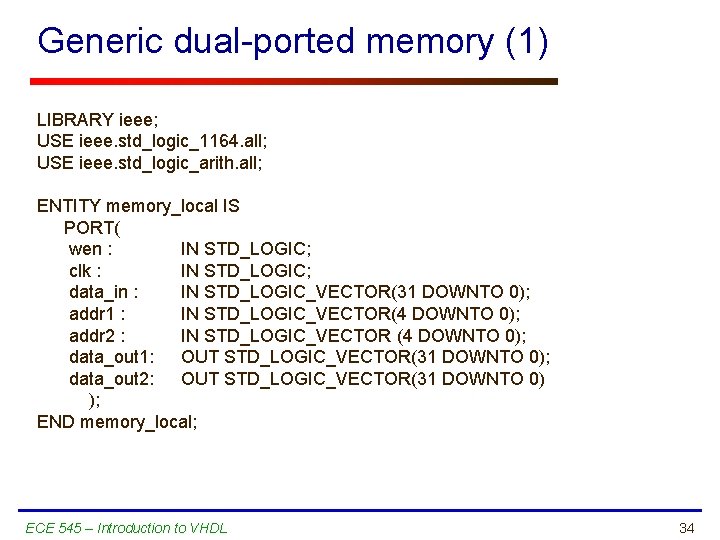

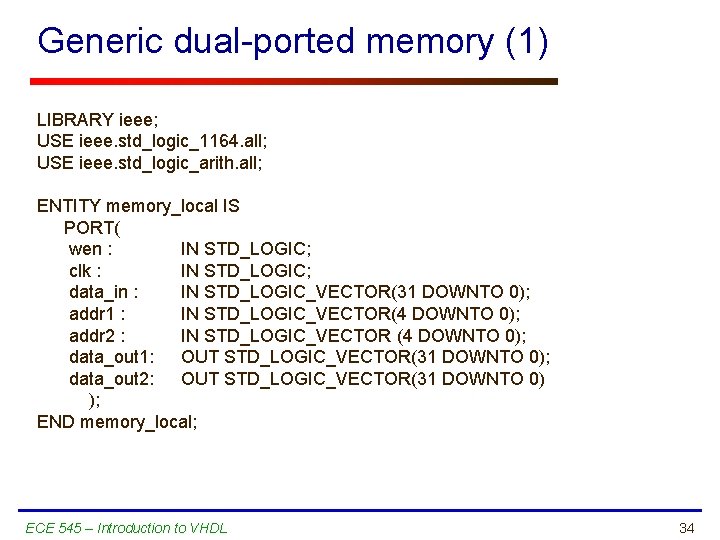

Generic dual-ported memory (1) LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_arith. all; ENTITY memory_local IS PORT( wen : IN STD_LOGIC; clk : IN STD_LOGIC; data_in : IN STD_LOGIC_VECTOR(31 DOWNTO 0); addr 1 : IN STD_LOGIC_VECTOR(4 DOWNTO 0); addr 2 : IN STD_LOGIC_VECTOR (4 DOWNTO 0); data_out 1: OUT STD_LOGIC_VECTOR(31 DOWNTO 0); data_out 2: OUT STD_LOGIC_VECTOR(31 DOWNTO 0) ); END memory_local; ECE 545 – Introduction to VHDL 34

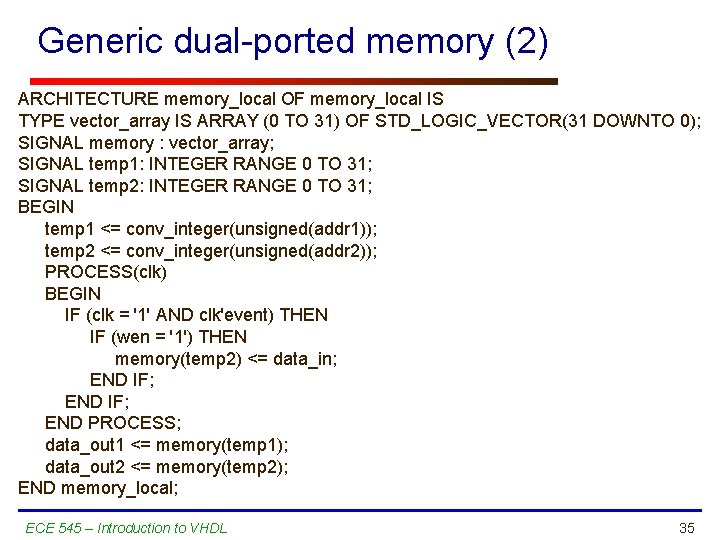

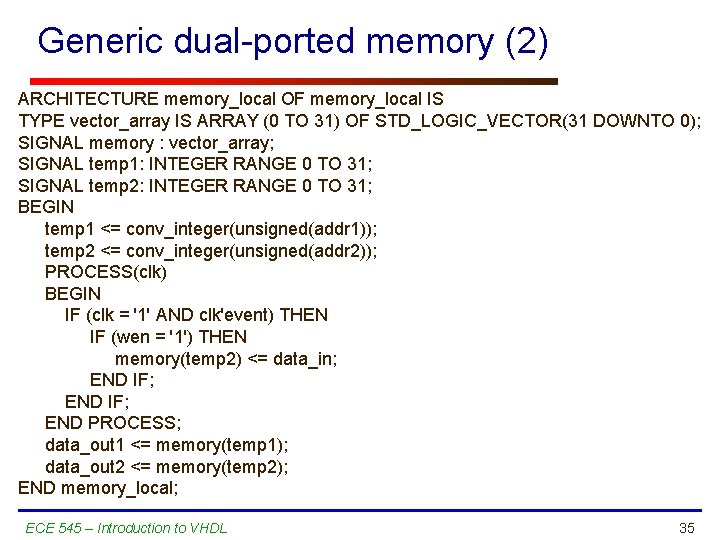

Generic dual-ported memory (2) ARCHITECTURE memory_local OF memory_local IS TYPE vector_array IS ARRAY (0 TO 31) OF STD_LOGIC_VECTOR(31 DOWNTO 0); SIGNAL memory : vector_array; SIGNAL temp 1: INTEGER RANGE 0 TO 31; SIGNAL temp 2: INTEGER RANGE 0 TO 31; BEGIN temp 1 <= conv_integer(unsigned(addr 1)); temp 2 <= conv_integer(unsigned(addr 2)); PROCESS(clk) BEGIN IF (clk = '1' AND clk'event) THEN IF (wen = '1') THEN memory(temp 2) <= data_in; END IF; END PROCESS; data_out 1 <= memory(temp 1); data_out 2 <= memory(temp 2); END memory_local; ECE 545 – Introduction to VHDL 35

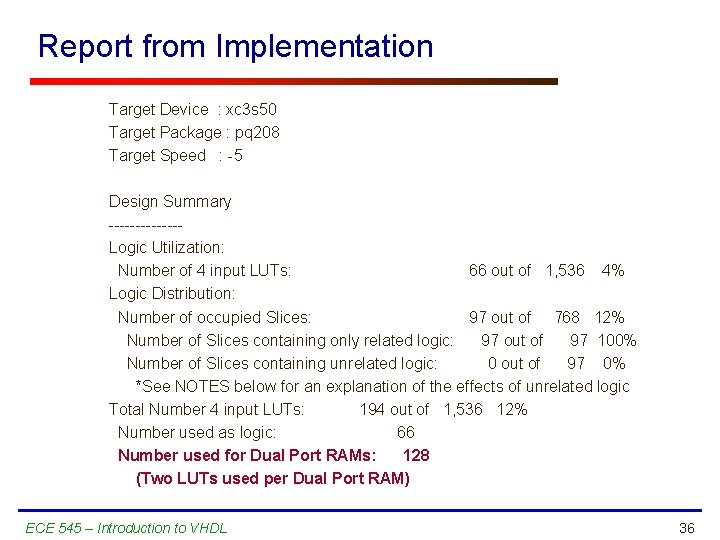

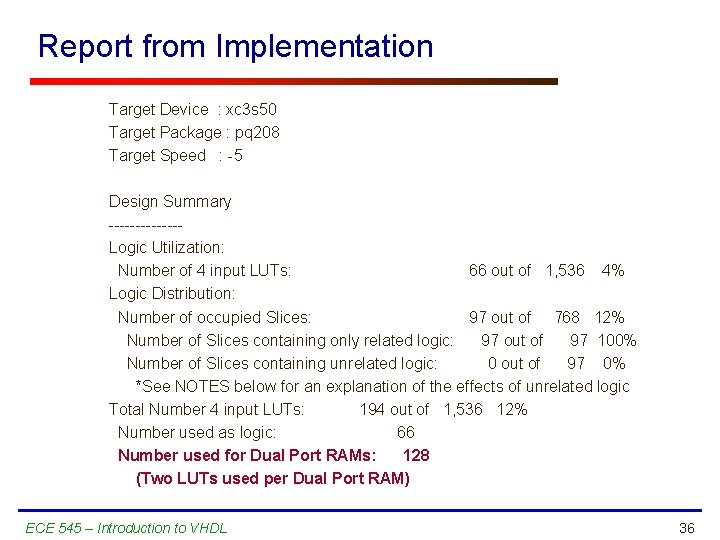

Report from Implementation Target Device : xc 3 s 50 Target Package : pq 208 Target Speed : -5 Design Summary -------Logic Utilization: Number of 4 input LUTs: 66 out of 1, 536 4% Logic Distribution: Number of occupied Slices: 97 out of 768 12% Number of Slices containing only related logic: 97 out of 97 100% Number of Slices containing unrelated logic: 0 out of 97 0% *See NOTES below for an explanation of the effects of unrelated logic Total Number 4 input LUTs: 194 out of 1, 536 12% Number used as logic: 66 Number used for Dual Port RAMs: 128 (Two LUTs used per Dual Port RAM) ECE 545 – Introduction to VHDL 36

Distributed RAM 16 X 1 S • A LUT equals 16 x 1 RAM • Implements Single and Dual. Ports • Cascade LUTs to increase RAM size • Synchronous write • Synchronous/Asynchronous read • Accompanying flip-flops used for synchronous read ECE 545 – Introduction to VHDL = LUT • CLB LUT configurable as Distributed RAM D W EWCL K A 0 A 1 A 2 A 3 O RAM 32 X 1 S D WE WCLK A 0 A 1 A 2 A 3 A 4 LUT = LUT or O RAM 16 X 2 S D 0 D 1 WE WCLK O 0 A 0 O 1 A 2 A 3 or RAM 16 X 1 D D W EWCL K A 0 SPO A 1 A 2 A 3 DPRA DP 0 DPRA 1 O DPRA 2 DPRA 3 37

Constants ECE 545 – Introduction to VHDL 38

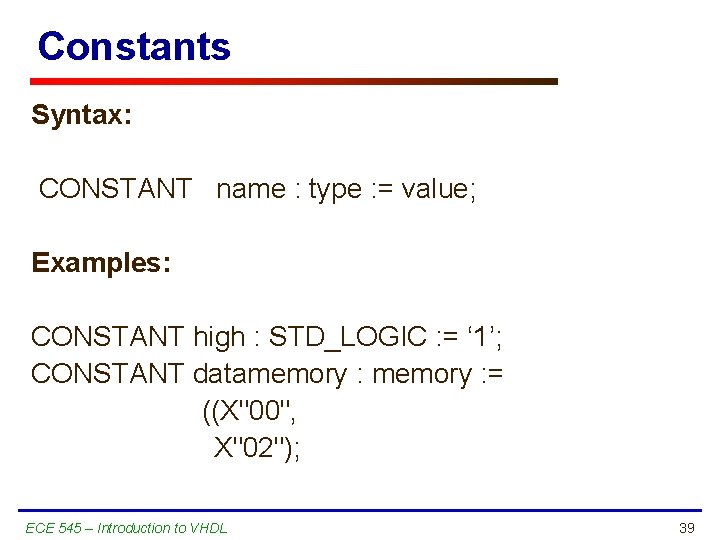

Constants Syntax: CONSTANT name : type : = value; Examples: CONSTANT high : STD_LOGIC : = ‘ 1’; CONSTANT datamemory : = ((X"00", X"02"); ECE 545 – Introduction to VHDL 39

Constants - features Constants can be declared in a PACKAGE, ENTITY, ARCHITECTURE When declared in a PACKAGE, the constant is truly global, for the package can be used in several entities. When declared in an ARCHITECTURE, the constant is local, i. e. , it is visible only within this architecture. When declared in an ENTITY, the constant can be used in all architectures associated with this entity. ECE 545 – Introduction to VHDL 40

Specifying time in VHDL ECE 545 – Introduction to VHDL 41

Physical data types Types representing physical quantities, such as time, voltage, capacitance, etc. are referred in VHDL as physical data types. TIME is the only predefined physical data type. Value of the physical data type is called a physical literal. ECE 545 – Introduction to VHDL 42

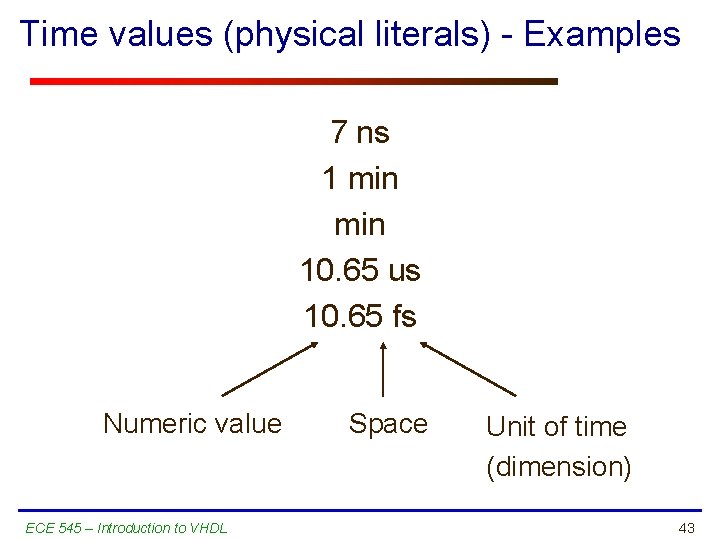

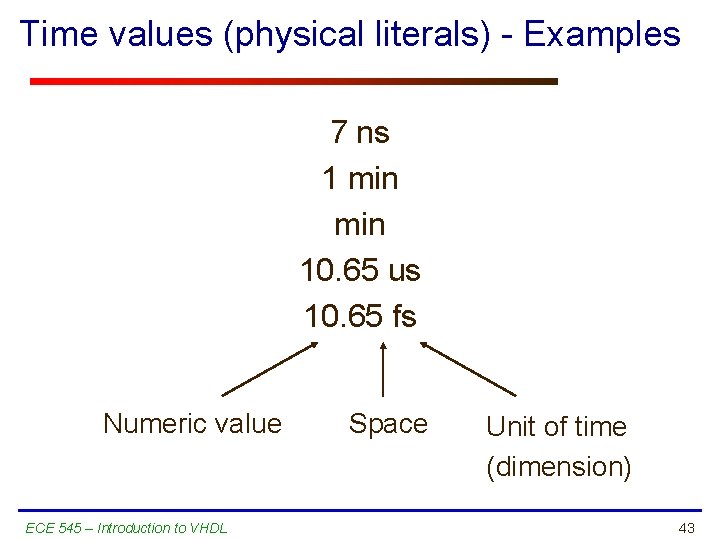

Time values (physical literals) - Examples 7 ns 1 min 10. 65 us 10. 65 fs Numeric value ECE 545 – Introduction to VHDL Space Unit of time (dimension) 43

TIME values Numeric value can be an integer or a floating point number. Numeric value is optional. If not given, 1 is implied. Numeric value and dimension MUST be separated by a space. ECE 545 – Introduction to VHDL 44

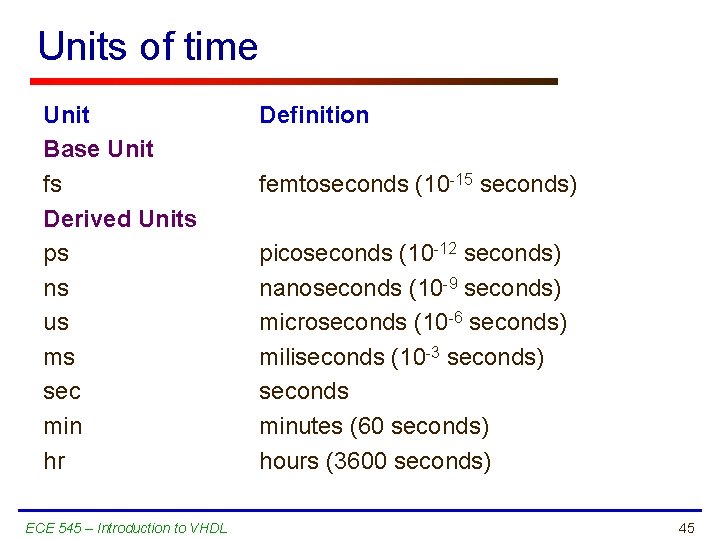

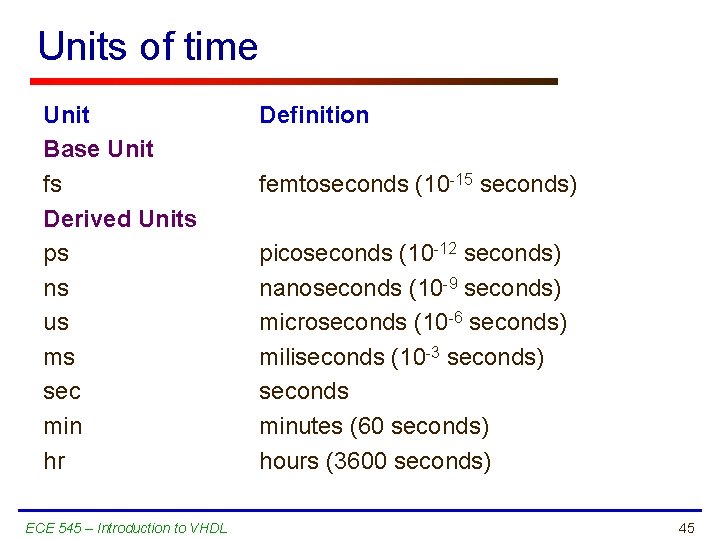

Units of time Unit Base Unit fs Derived Units ps ns us ms sec min hr ECE 545 – Introduction to VHDL Definition femtoseconds (10 -15 seconds) picoseconds (10 -12 seconds) nanoseconds (10 -9 seconds) microseconds (10 -6 seconds) miliseconds (10 -3 seconds) seconds minutes (60 seconds) hours (3600 seconds) 45

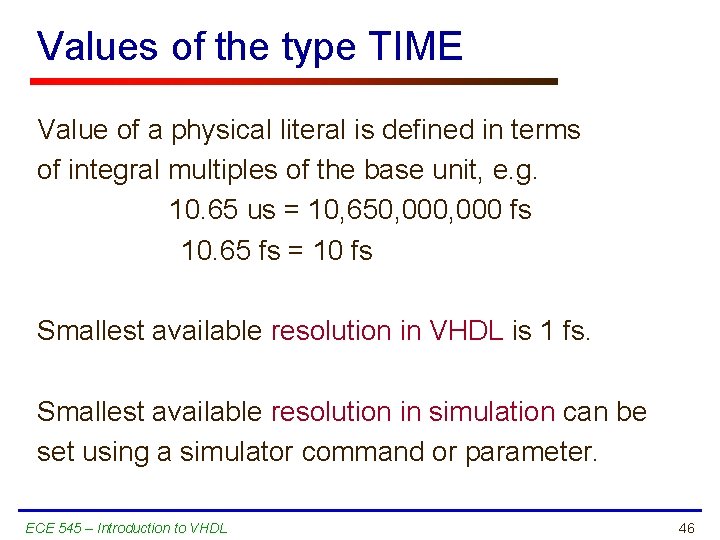

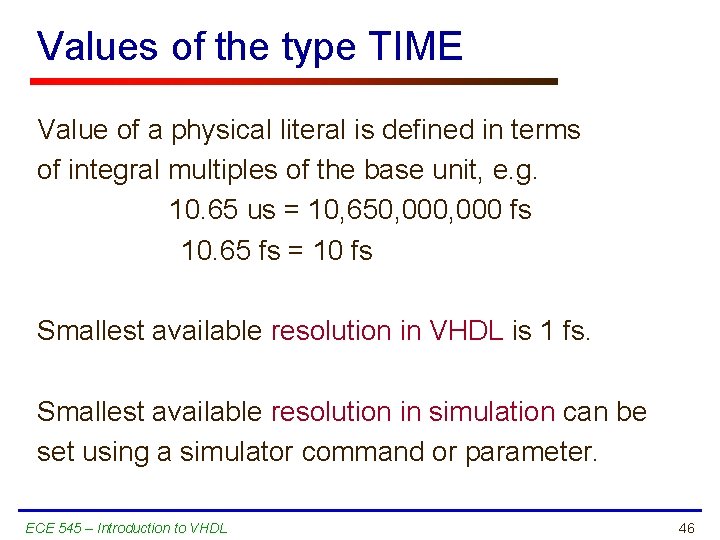

Values of the type TIME Value of a physical literal is defined in terms of integral multiples of the base unit, e. g. 10. 65 us = 10, 650, 000 fs 10. 65 fs = 10 fs Smallest available resolution in VHDL is 1 fs. Smallest available resolution in simulation can be set using a simulator command or parameter. ECE 545 – Introduction to VHDL 46

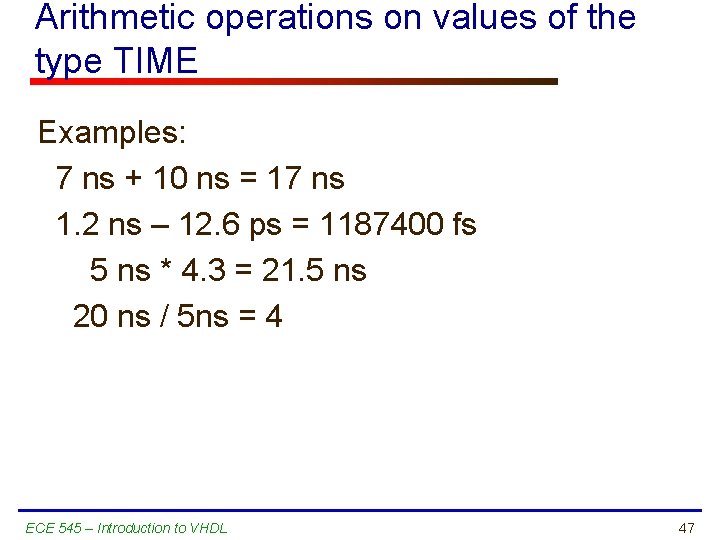

Arithmetic operations on values of the type TIME Examples: 7 ns + 10 ns = 17 ns 1. 2 ns – 12. 6 ps = 1187400 fs 5 ns * 4. 3 = 21. 5 ns 20 ns / 5 ns = 4 ECE 545 – Introduction to VHDL 47

Records ECE 545 – Introduction to VHDL 48

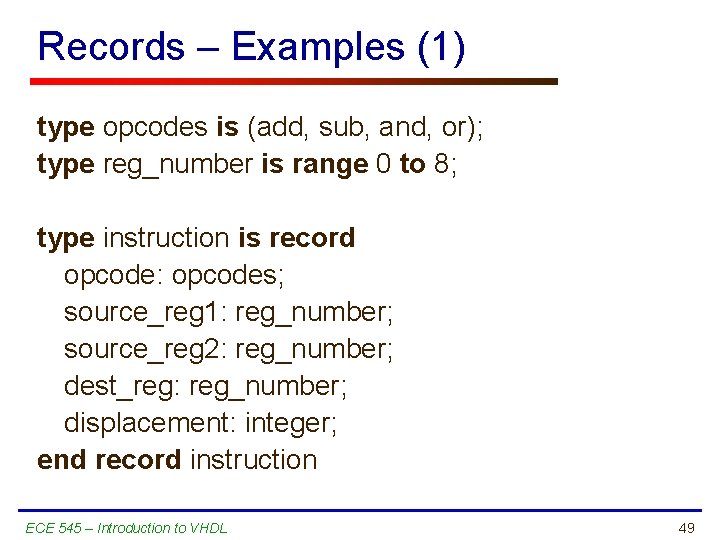

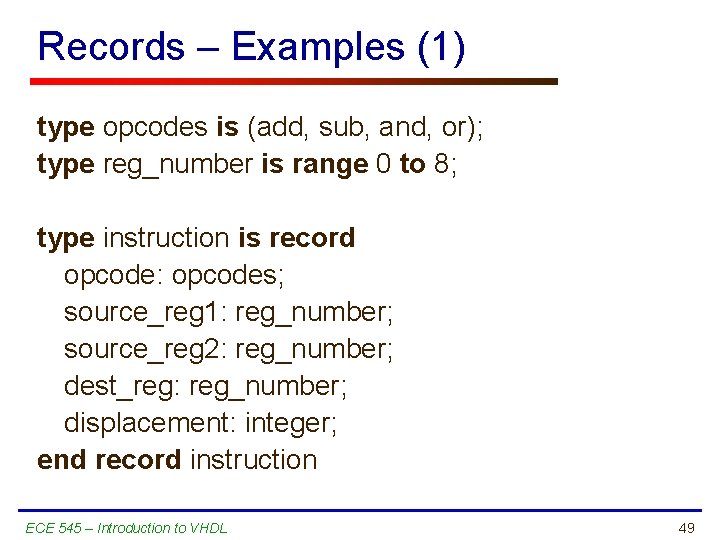

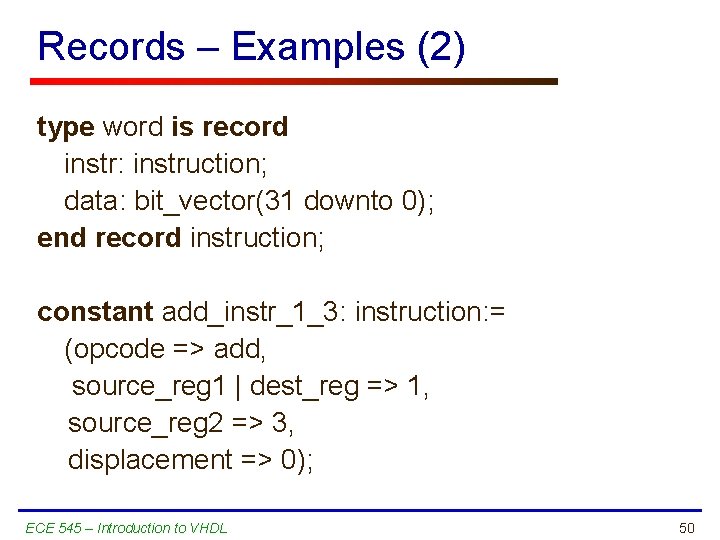

Records – Examples (1) type opcodes is (add, sub, and, or); type reg_number is range 0 to 8; type instruction is record opcode: opcodes; source_reg 1: reg_number; source_reg 2: reg_number; dest_reg: reg_number; displacement: integer; end record instruction ECE 545 – Introduction to VHDL 49

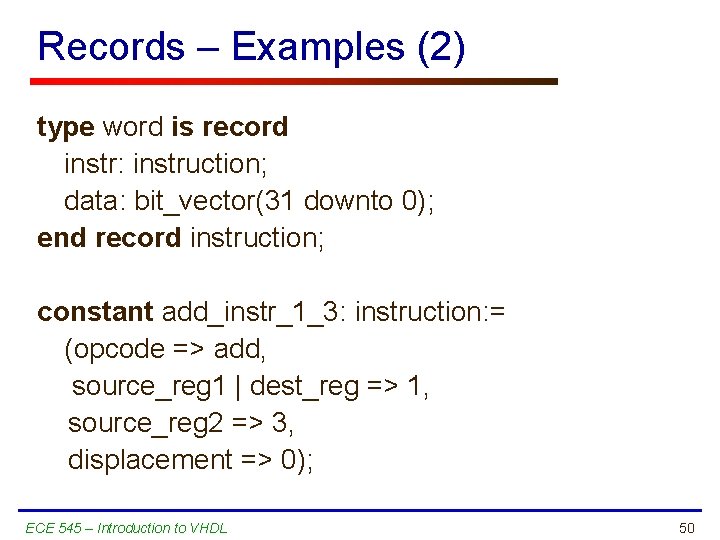

Records – Examples (2) type word is record instr: instruction; data: bit_vector(31 downto 0); end record instruction; constant add_instr_1_3: instruction: = (opcode => add, source_reg 1 | dest_reg => 1, source_reg 2 => 3, displacement => 0); ECE 545 – Introduction to VHDL 50

Asserts & Reports ECE 545 – Introduction to VHDL 51

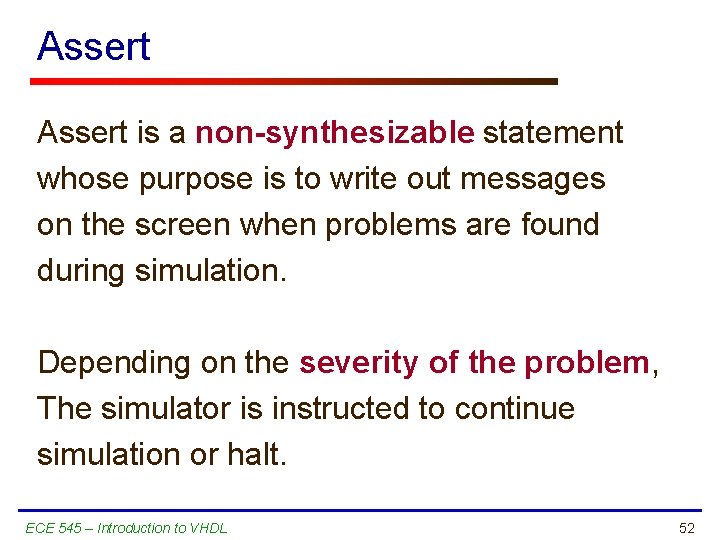

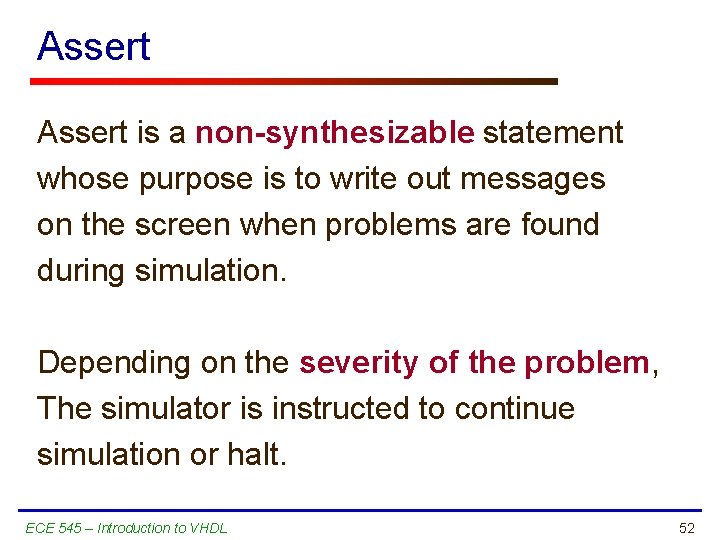

Assert is a non-synthesizable statement whose purpose is to write out messages on the screen when problems are found during simulation. Depending on the severity of the problem, The simulator is instructed to continue simulation or halt. ECE 545 – Introduction to VHDL 52

![Assert syntax ASSERT condition REPORT message SEVERITY severitylevel The message is written Assert - syntax ASSERT condition [REPORT "message" [SEVERITY severity_level ]; The message is written](https://slidetodoc.com/presentation_image_h2/1de529e37649c97ef6ec5bb237a99165/image-53.jpg)

Assert - syntax ASSERT condition [REPORT "message" [SEVERITY severity_level ]; The message is written when the condition is FALSE. Severity_level can be: Note, Warning, Error (default), or Failure. ECE 545 – Introduction to VHDL 53

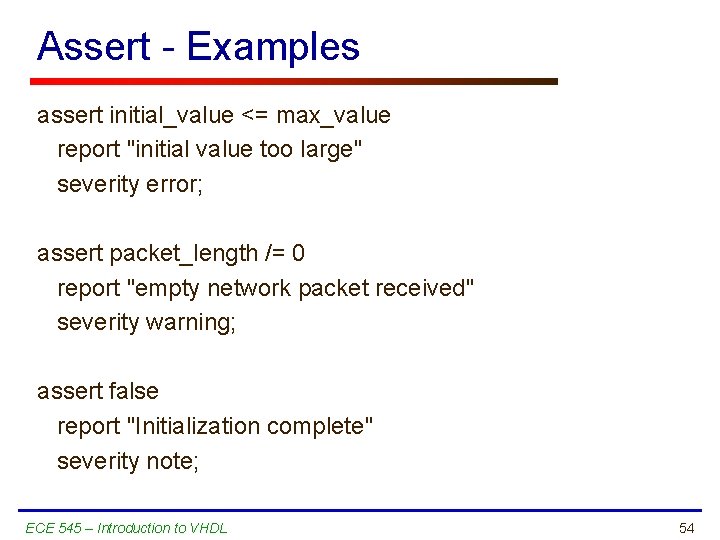

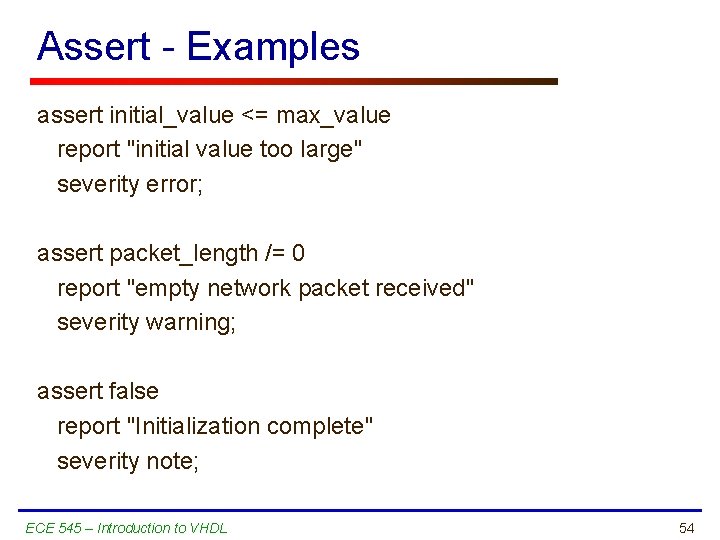

Assert - Examples assert initial_value <= max_value report "initial value too large" severity error; assert packet_length /= 0 report "empty network packet received" severity warning; assert false report "Initialization complete" severity note; ECE 545 – Introduction to VHDL 54

![Report syntax REPORT message SEVERITY severitylevel The message is always written Severitylevel Report - syntax REPORT "message" [SEVERITY severity_level ]; The message is always written. Severity_level](https://slidetodoc.com/presentation_image_h2/1de529e37649c97ef6ec5bb237a99165/image-55.jpg)

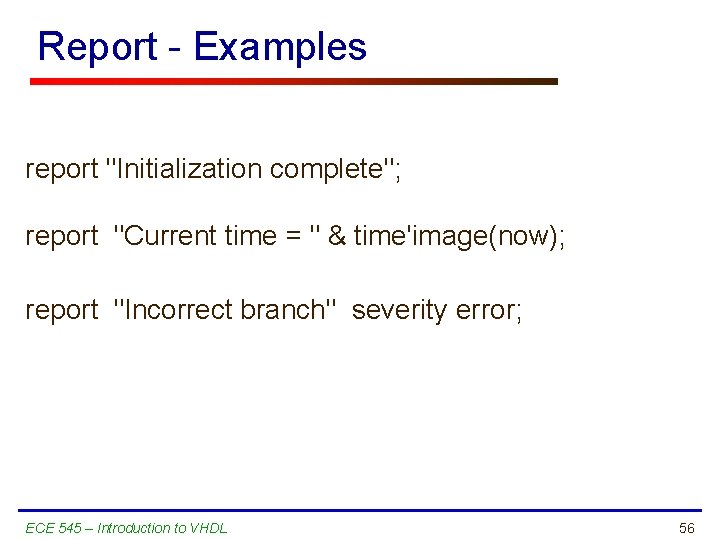

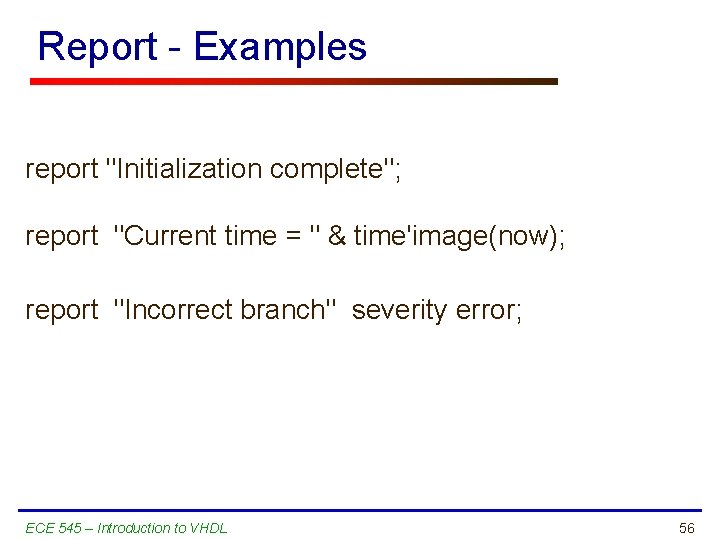

Report - syntax REPORT "message" [SEVERITY severity_level ]; The message is always written. Severity_level can be: Note (default), Warning, Error, or Failure. ECE 545 – Introduction to VHDL 55

Report - Examples report "Initialization complete"; report "Current time = " & time'image(now); report "Incorrect branch" severity error; ECE 545 – Introduction to VHDL 56

Variables ECE 545 – Introduction to VHDL 57

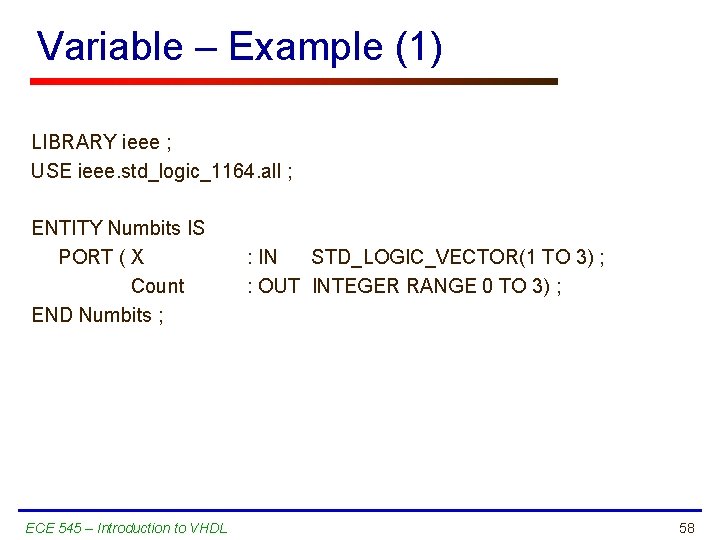

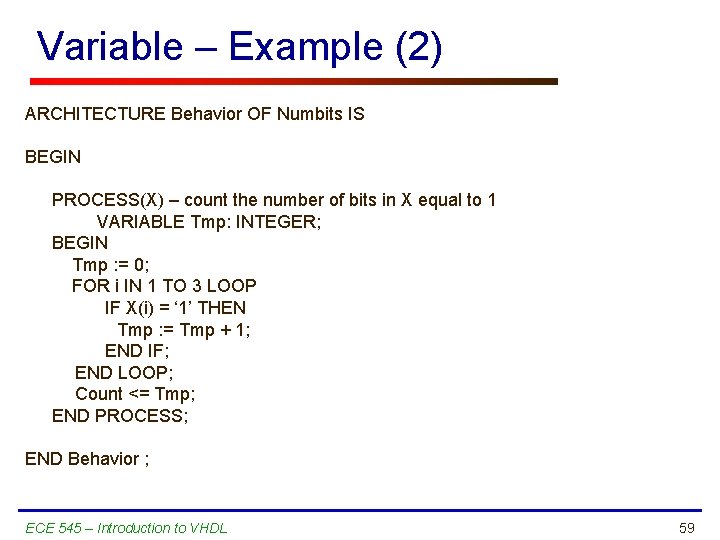

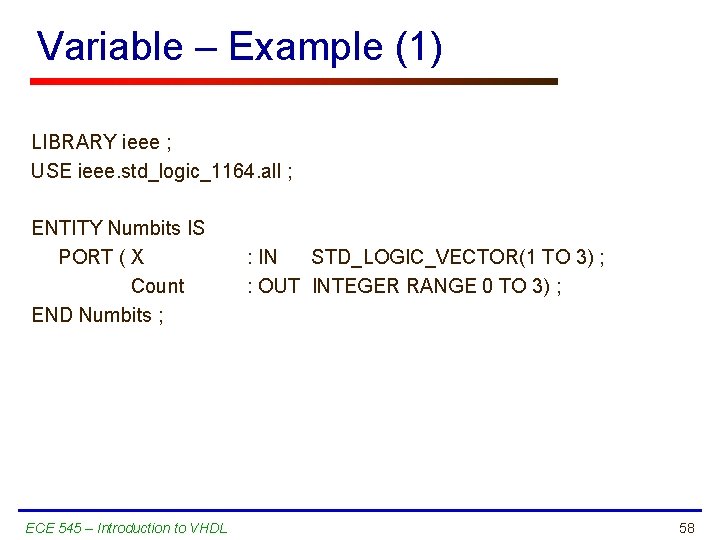

Variable – Example (1) LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY Numbits IS PORT ( X Count END Numbits ; ECE 545 – Introduction to VHDL : IN STD_LOGIC_VECTOR(1 TO 3) ; : OUT INTEGER RANGE 0 TO 3) ; 58

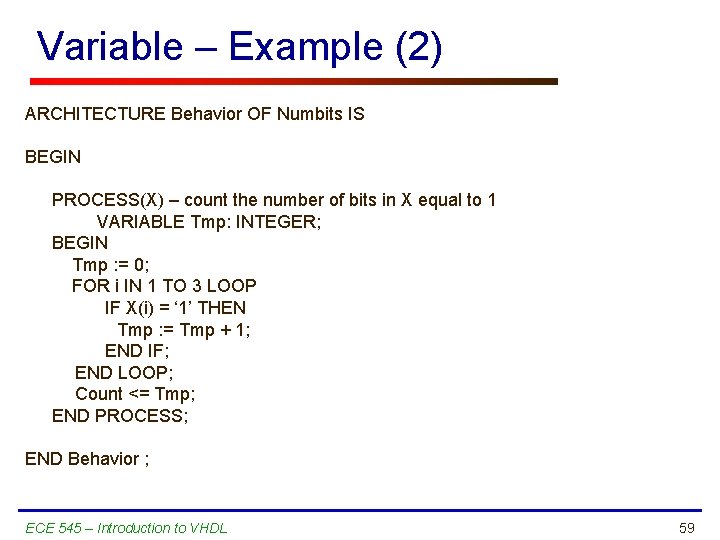

Variable – Example (2) ARCHITECTURE Behavior OF Numbits IS BEGIN PROCESS(X) – count the number of bits in X equal to 1 VARIABLE Tmp: INTEGER; BEGIN Tmp : = 0; FOR i IN 1 TO 3 LOOP IF X(i) = ‘ 1’ THEN Tmp : = Tmp + 1; END IF; END LOOP; Count <= Tmp; END PROCESS; END Behavior ; ECE 545 – Introduction to VHDL 59

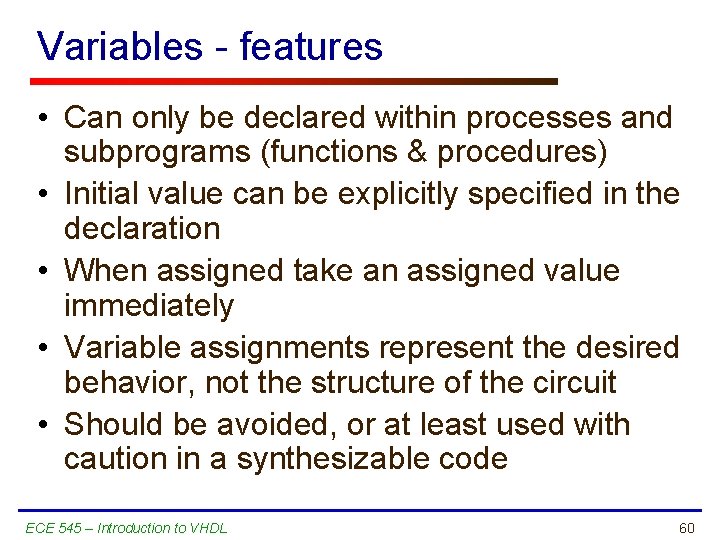

Variables - features • Can only be declared within processes and subprograms (functions & procedures) • Initial value can be explicitly specified in the declaration • When assigned take an assigned value immediately • Variable assignments represent the desired behavior, not the structure of the circuit • Should be avoided, or at least used with caution in a synthesizable code ECE 545 – Introduction to VHDL 60

Advanced Testbenches ECE 545 – Introduction to VHDL 61

Using Arrays of Test Vectors In Testbenches ECE 545 – Introduction to VHDL 62

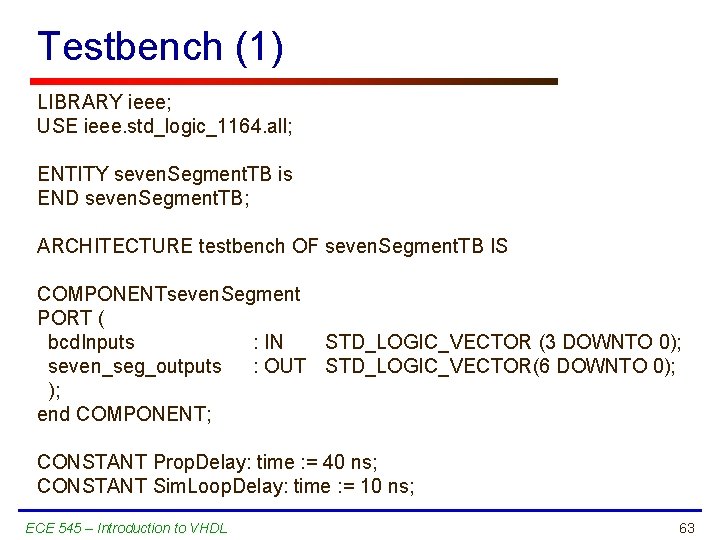

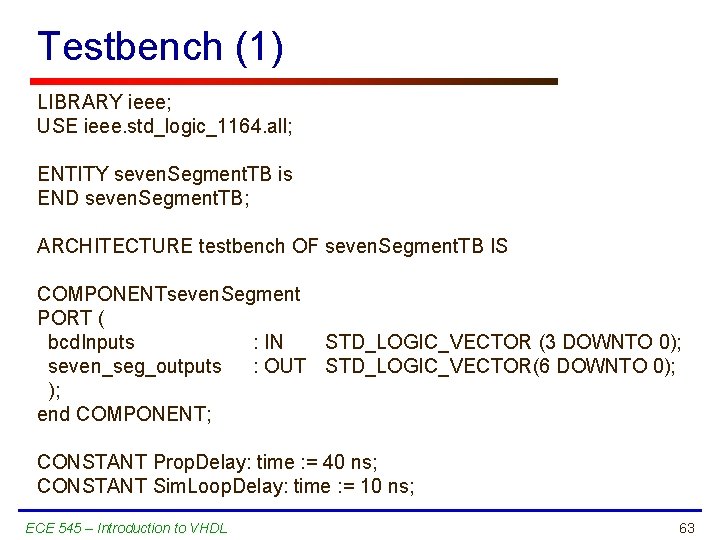

Testbench (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY seven. Segment. TB is END seven. Segment. TB; ARCHITECTURE testbench OF seven. Segment. TB IS COMPONENTseven. Segment PORT ( bcd. Inputs : IN STD_LOGIC_VECTOR (3 DOWNTO 0); seven_seg_outputs : OUT STD_LOGIC_VECTOR(6 DOWNTO 0); ); end COMPONENT; CONSTANT Prop. Delay: time : = 40 ns; CONSTANT Sim. Loop. Delay: time : = 10 ns; ECE 545 – Introduction to VHDL 63

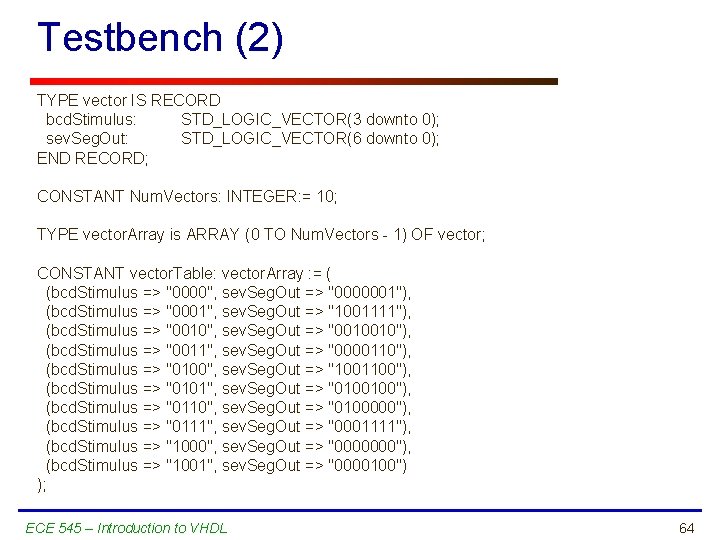

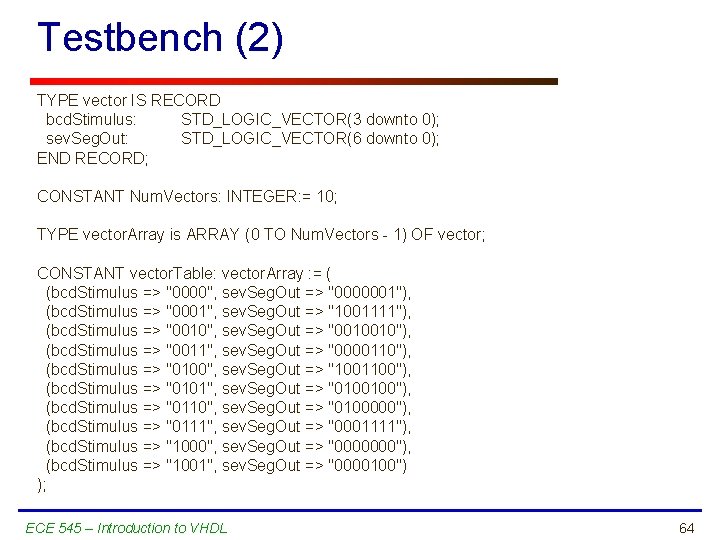

Testbench (2) TYPE vector IS RECORD bcd. Stimulus: STD_LOGIC_VECTOR(3 downto 0); sev. Seg. Out: STD_LOGIC_VECTOR(6 downto 0); END RECORD; CONSTANT Num. Vectors: INTEGER: = 10; TYPE vector. Array is ARRAY (0 TO Num. Vectors - 1) OF vector; CONSTANT vector. Table: vector. Array : = ( (bcd. Stimulus => "0000", sev. Seg. Out => "0000001"), (bcd. Stimulus => "0001", sev. Seg. Out => "1001111"), (bcd. Stimulus => "0010", sev. Seg. Out => "0010010"), (bcd. Stimulus => "0011", sev. Seg. Out => "0000110"), (bcd. Stimulus => "0100", sev. Seg. Out => "1001100"), (bcd. Stimulus => "0101", sev. Seg. Out => "0100100"), (bcd. Stimulus => "0110", sev. Seg. Out => "0100000"), (bcd. Stimulus => "0111", sev. Seg. Out => "0001111"), (bcd. Stimulus => "1000", sev. Seg. Out => "0000000"), (bcd. Stimulus => "1001", sev. Seg. Out => "0000100") ); ECE 545 – Introduction to VHDL 64

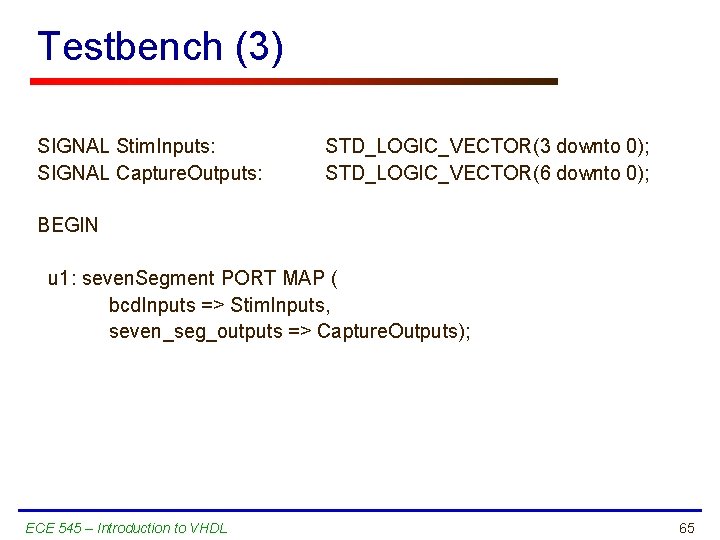

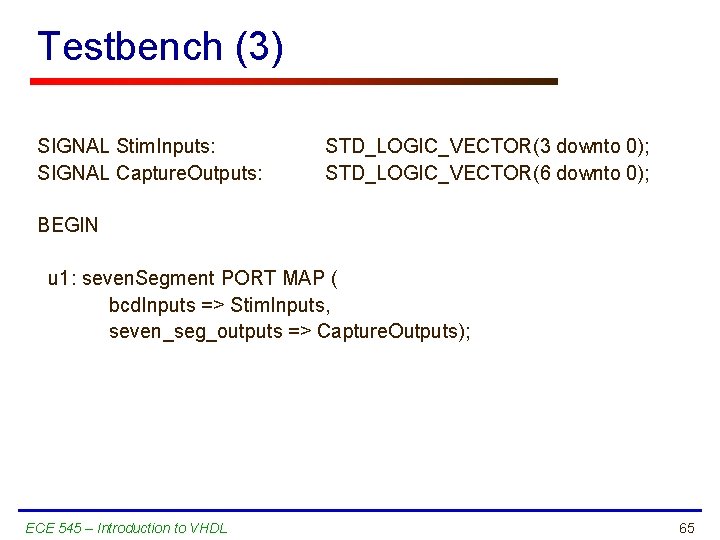

Testbench (3) SIGNAL Stim. Inputs: SIGNAL Capture. Outputs: STD_LOGIC_VECTOR(3 downto 0); STD_LOGIC_VECTOR(6 downto 0); BEGIN u 1: seven. Segment PORT MAP ( bcd. Inputs => Stim. Inputs, seven_seg_outputs => Capture. Outputs); ECE 545 – Introduction to VHDL 65

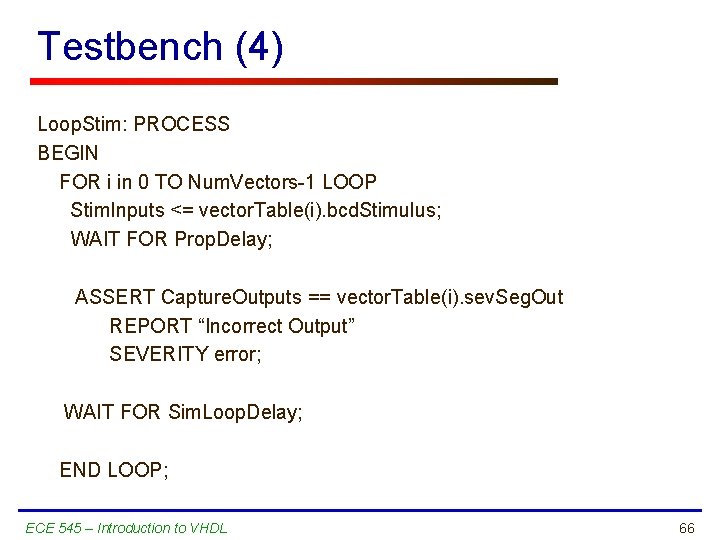

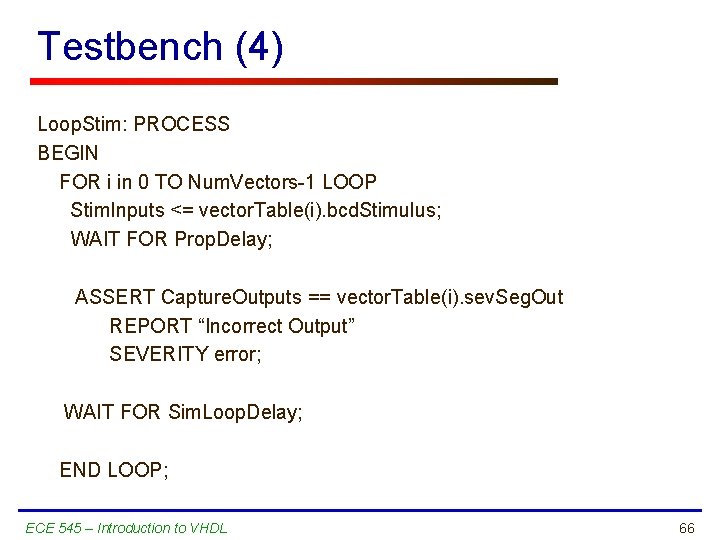

Testbench (4) Loop. Stim: PROCESS BEGIN FOR i in 0 TO Num. Vectors-1 LOOP Stim. Inputs <= vector. Table(i). bcd. Stimulus; WAIT FOR Prop. Delay; ASSERT Capture. Outputs == vector. Table(i). sev. Seg. Out REPORT “Incorrect Output” SEVERITY error; WAIT FOR Sim. Loop. Delay; END LOOP; ECE 545 – Introduction to VHDL 66

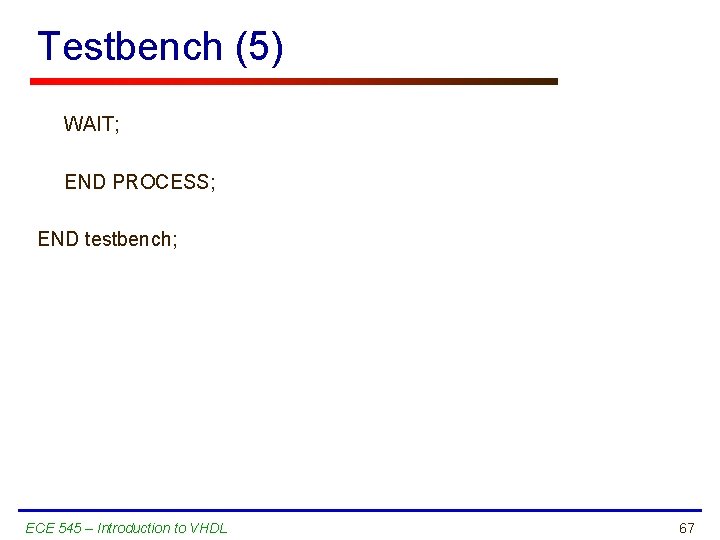

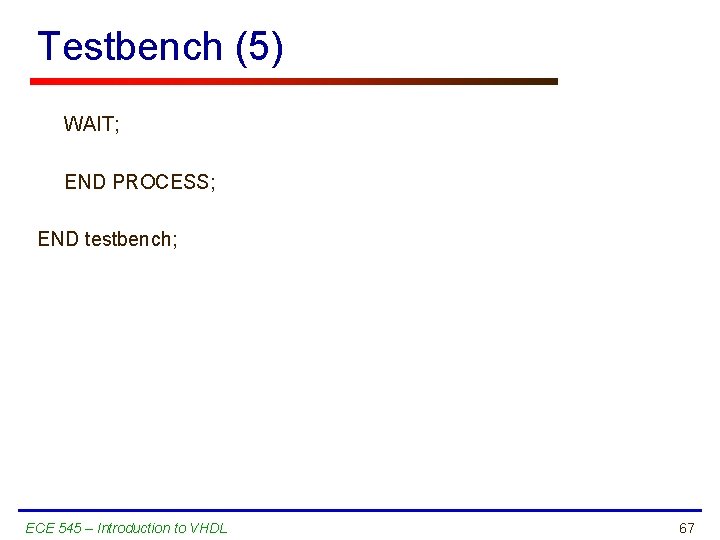

Testbench (5) WAIT; END PROCESS; END testbench; ECE 545 – Introduction to VHDL 67

File I/O ECE 545 – Introduction to VHDL 68

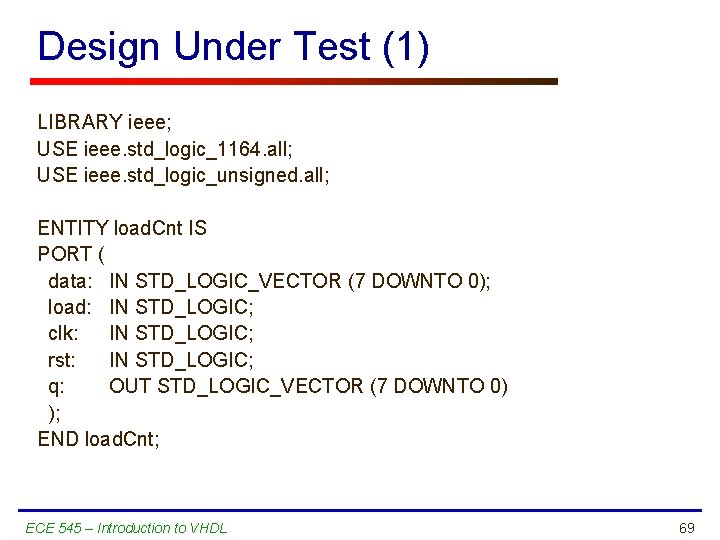

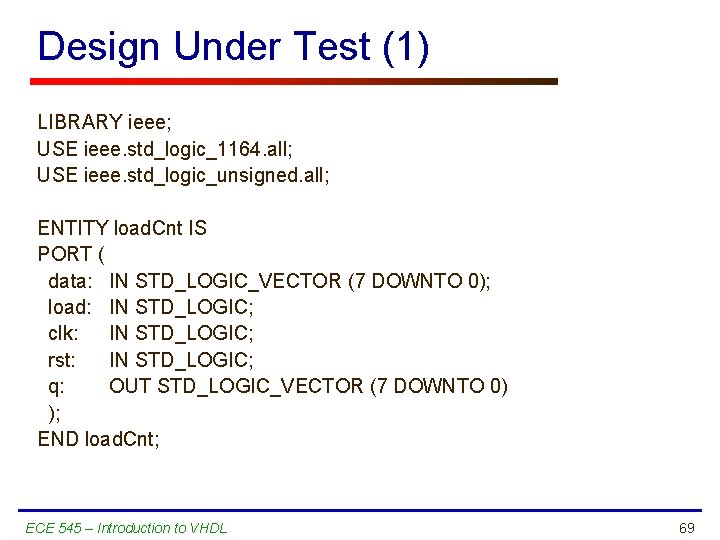

Design Under Test (1) LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_unsigned. all; ENTITY load. Cnt IS PORT ( data: IN STD_LOGIC_VECTOR (7 DOWNTO 0); load: IN STD_LOGIC; clk: IN STD_LOGIC; rst: IN STD_LOGIC; q: OUT STD_LOGIC_VECTOR (7 DOWNTO 0) ); END load. Cnt; ECE 545 – Introduction to VHDL 69

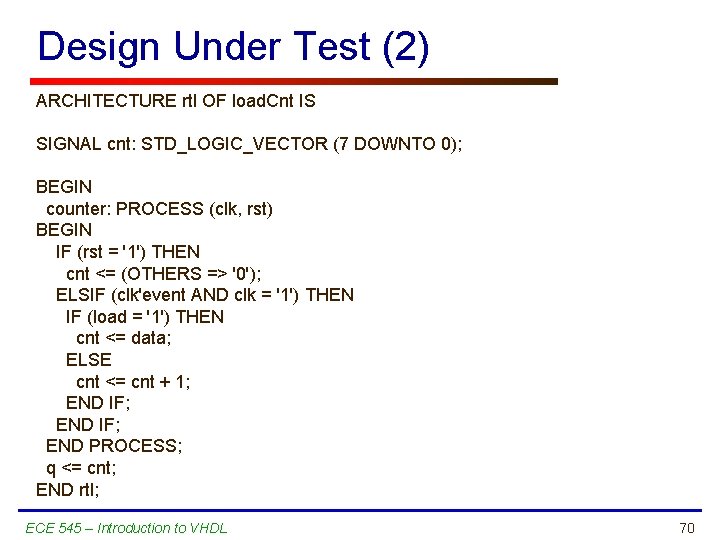

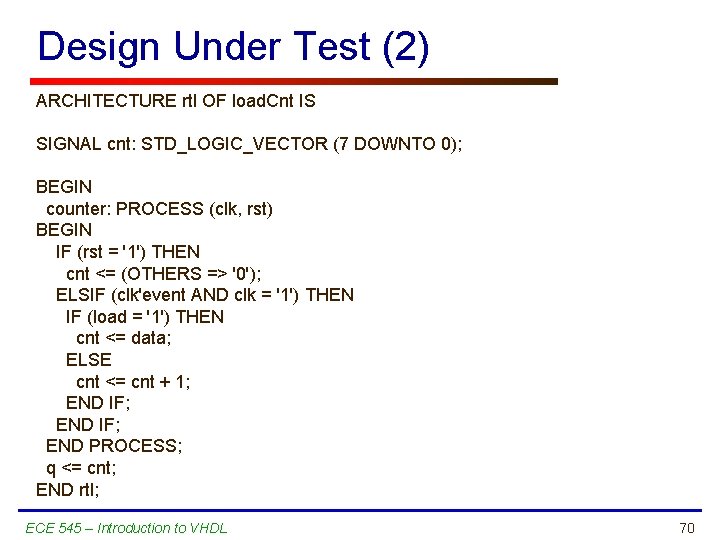

Design Under Test (2) ARCHITECTURE rtl OF load. Cnt IS SIGNAL cnt: STD_LOGIC_VECTOR (7 DOWNTO 0); BEGIN counter: PROCESS (clk, rst) BEGIN IF (rst = '1') THEN cnt <= (OTHERS => '0'); ELSIF (clk'event AND clk = '1') THEN IF (load = '1') THEN cnt <= data; ELSE cnt <= cnt + 1; END IF; END PROCESS; q <= cnt; END rtl; ECE 545 – Introduction to VHDL 70

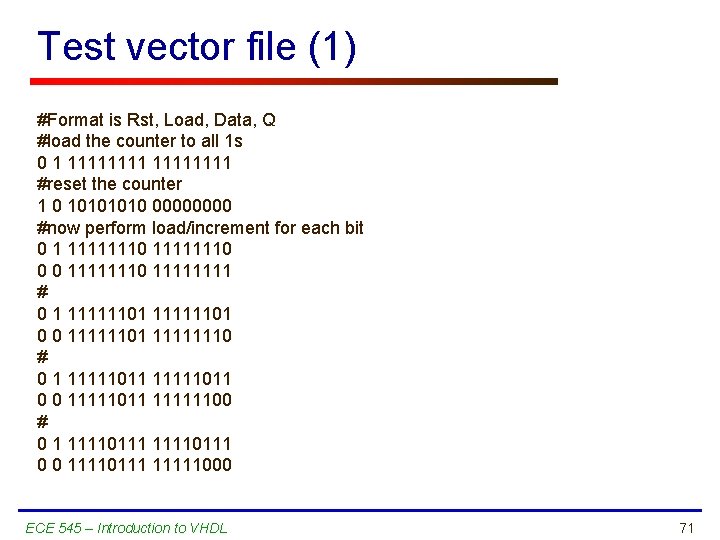

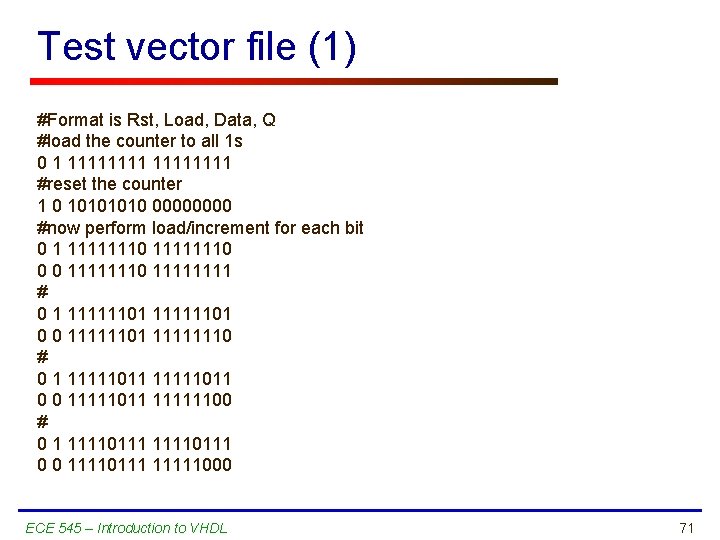

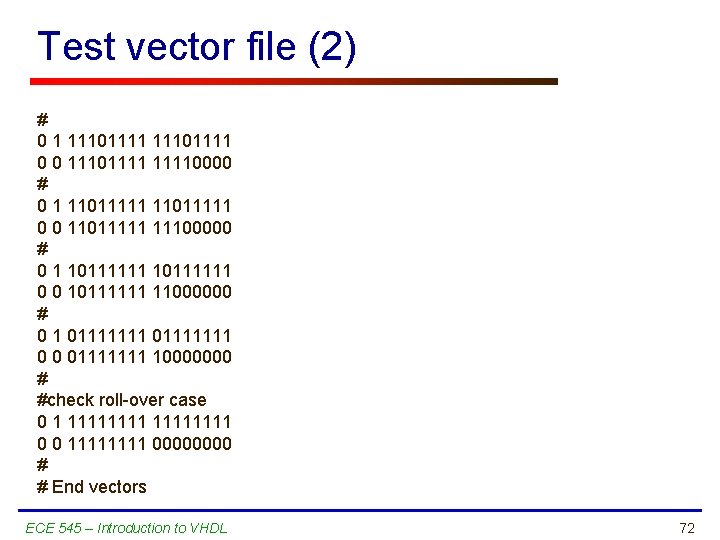

Test vector file (1) #Format is Rst, Load, Data, Q #load the counter to all 1 s 0 1 11111111 #reset the counter 1 0 1010 0000 #now perform load/increment for each bit 0 1 11111110 0 0 11111111 # 0 1 11111101 0 0 11111101 11111110 # 0 1 11111011 0 0 11111011 11111100 # 0 1 11110111 0 0 11110111 11111000 ECE 545 – Introduction to VHDL 71

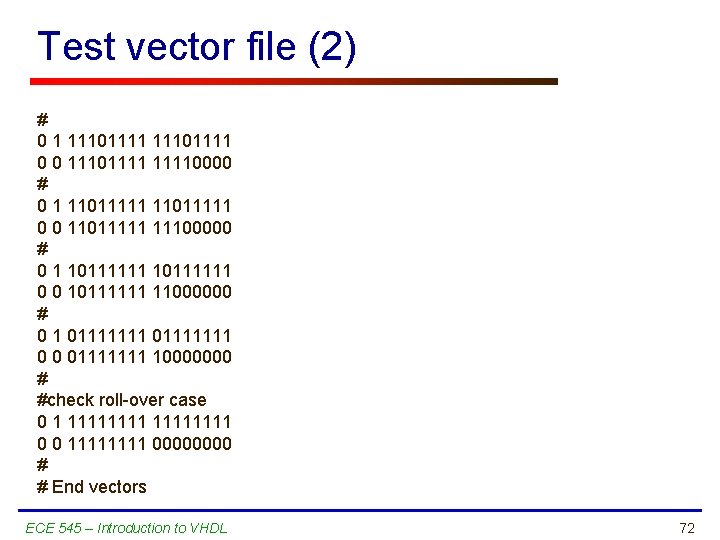

Test vector file (2) # 0 1 11101111 0 0 111011110000 # 0 1 11011111 0 0 11011111 11100000 # 0 1 10111111 0 0 10111111 11000000 # 0 1 01111111 0 0 01111111 10000000 # #check roll-over case 0 1 11111111 0 0 1111 0000 # # End vectors ECE 545 – Introduction to VHDL 72

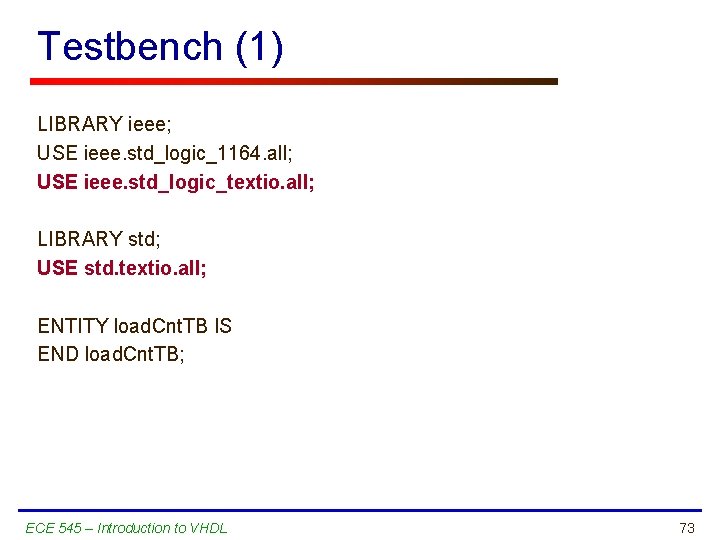

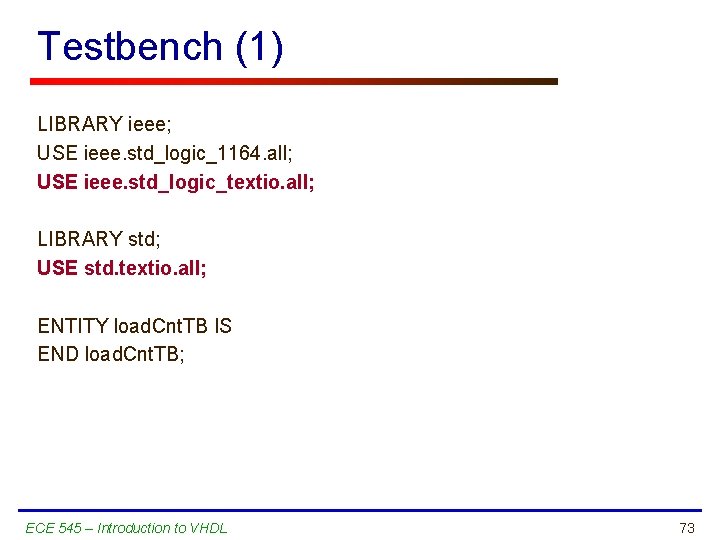

Testbench (1) LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_textio. all; LIBRARY std; USE std. textio. all; ENTITY load. Cnt. TB IS END load. Cnt. TB; ECE 545 – Introduction to VHDL 73

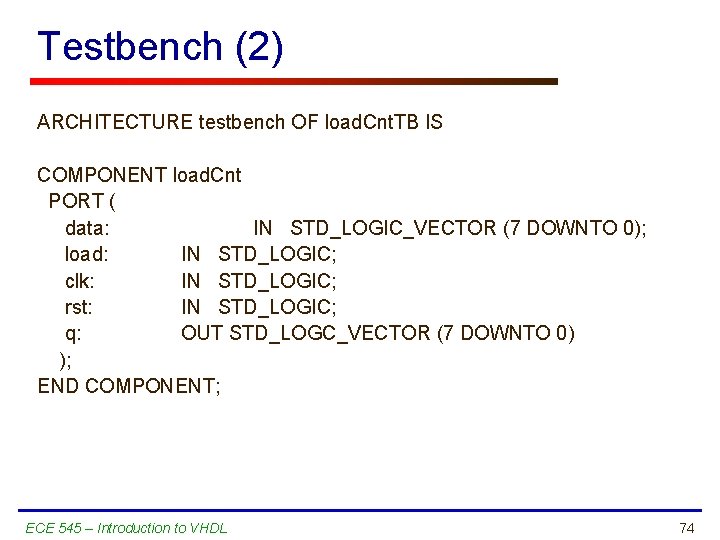

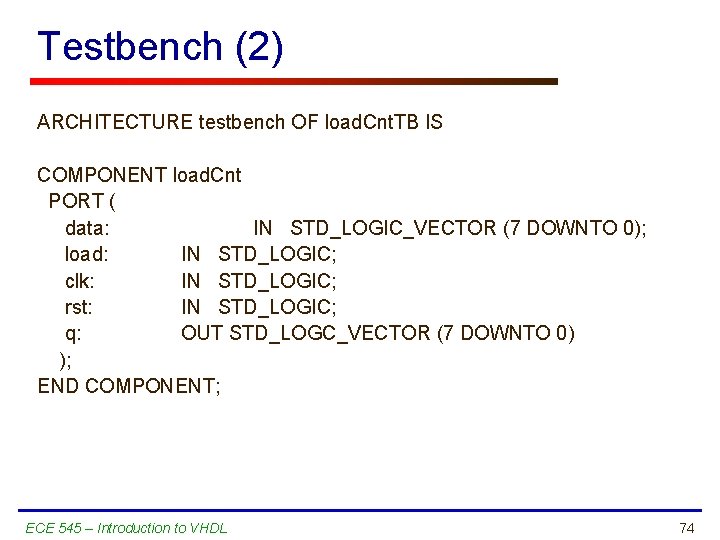

Testbench (2) ARCHITECTURE testbench OF load. Cnt. TB IS COMPONENT load. Cnt PORT ( data: IN STD_LOGIC_VECTOR (7 DOWNTO 0); load: IN STD_LOGIC; clk: IN STD_LOGIC; rst: IN STD_LOGIC; q: OUT STD_LOGC_VECTOR (7 DOWNTO 0) ); END COMPONENT; ECE 545 – Introduction to VHDL 74

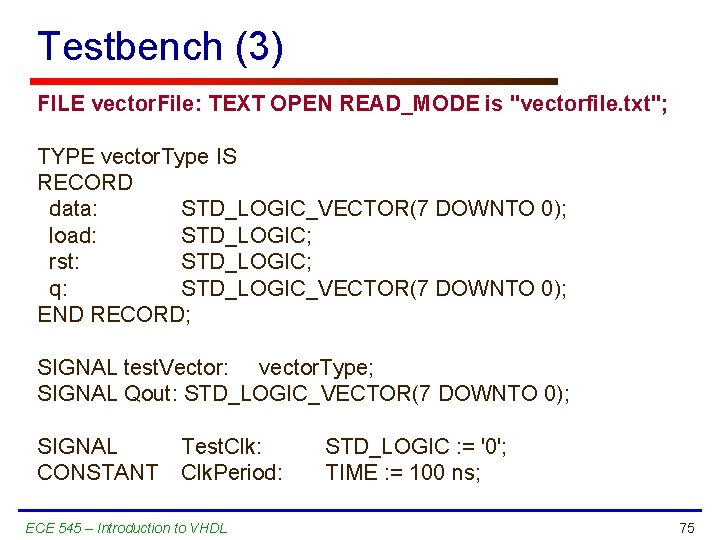

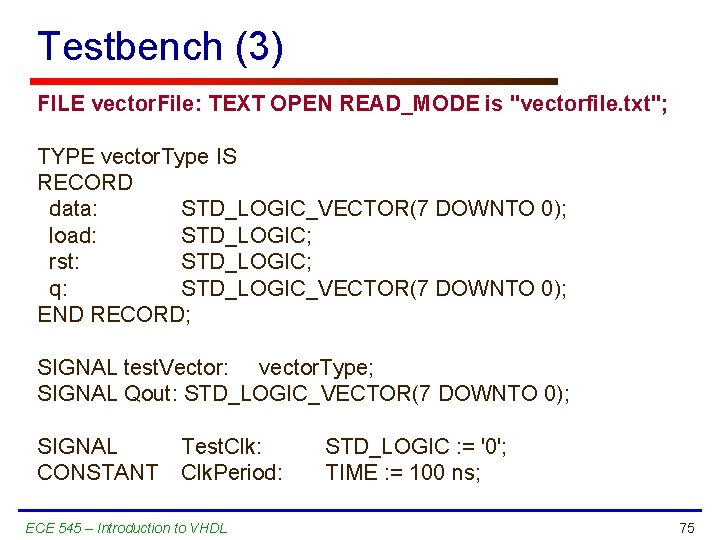

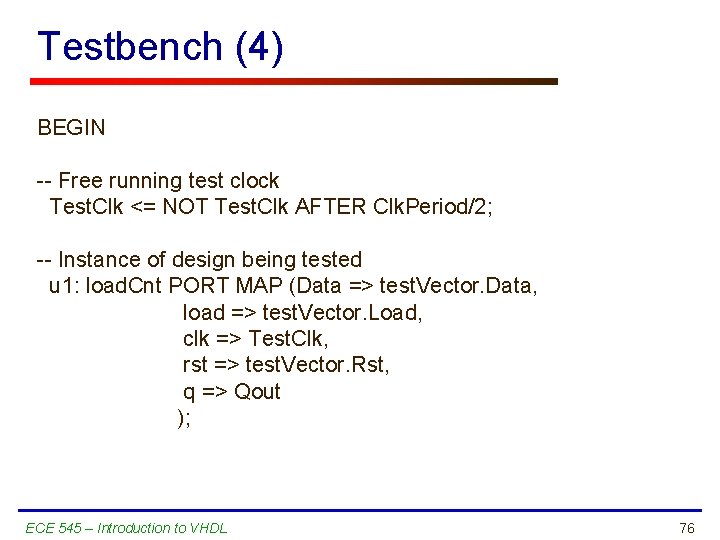

Testbench (3) FILE vector. File: TEXT OPEN READ_MODE is "vectorfile. txt"; TYPE vector. Type IS RECORD data: STD_LOGIC_VECTOR(7 DOWNTO 0); load: STD_LOGIC; rst: STD_LOGIC; q: STD_LOGIC_VECTOR(7 DOWNTO 0); END RECORD; SIGNAL test. Vector: vector. Type; SIGNAL Qout: STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL CONSTANT Test. Clk: Clk. Period: ECE 545 – Introduction to VHDL STD_LOGIC : = '0'; TIME : = 100 ns; 75

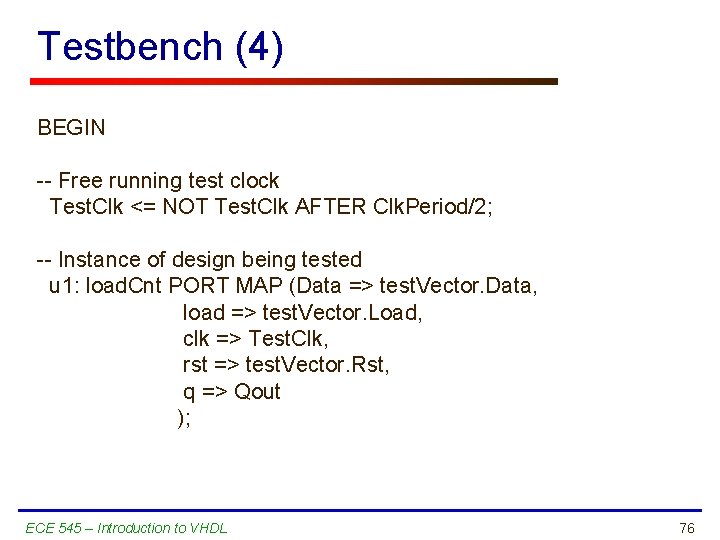

Testbench (4) BEGIN -- Free running test clock Test. Clk <= NOT Test. Clk AFTER Clk. Period/2; -- Instance of design being tested u 1: load. Cnt PORT MAP (Data => test. Vector. Data, load => test. Vector. Load, clk => Test. Clk, rst => test. Vector. Rst, q => Qout ); ECE 545 – Introduction to VHDL 76

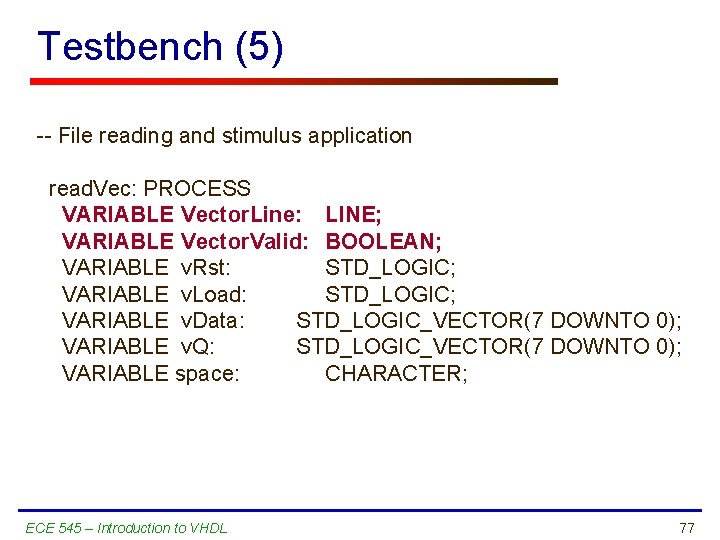

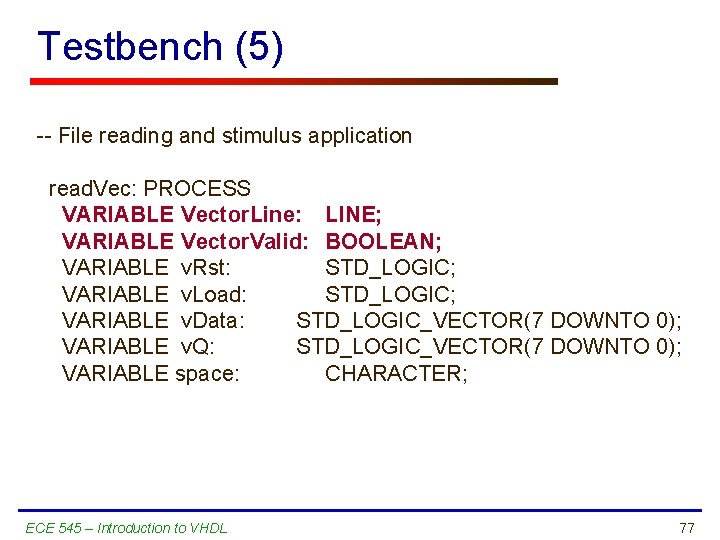

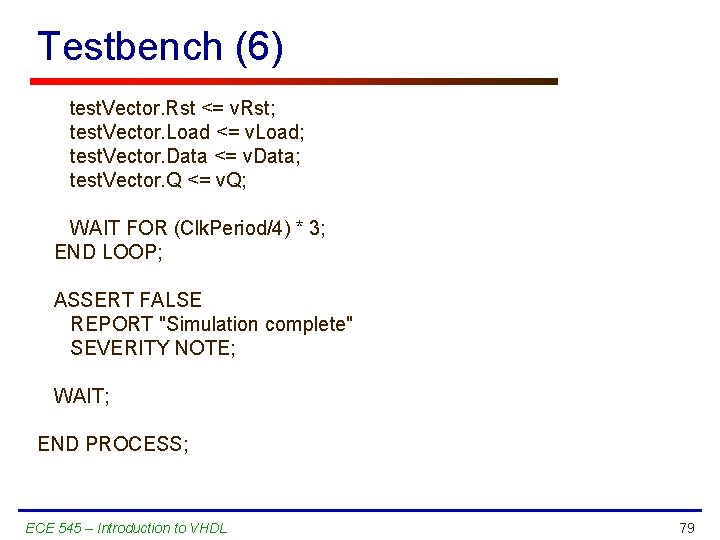

Testbench (5) -- File reading and stimulus application read. Vec: PROCESS VARIABLE Vector. Line: LINE; VARIABLE Vector. Valid: BOOLEAN; VARIABLE v. Rst: STD_LOGIC; VARIABLE v. Load: STD_LOGIC; VARIABLE v. Data: STD_LOGIC_VECTOR(7 DOWNTO 0); VARIABLE v. Q: STD_LOGIC_VECTOR(7 DOWNTO 0); VARIABLE space: CHARACTER; ECE 545 – Introduction to VHDL 77

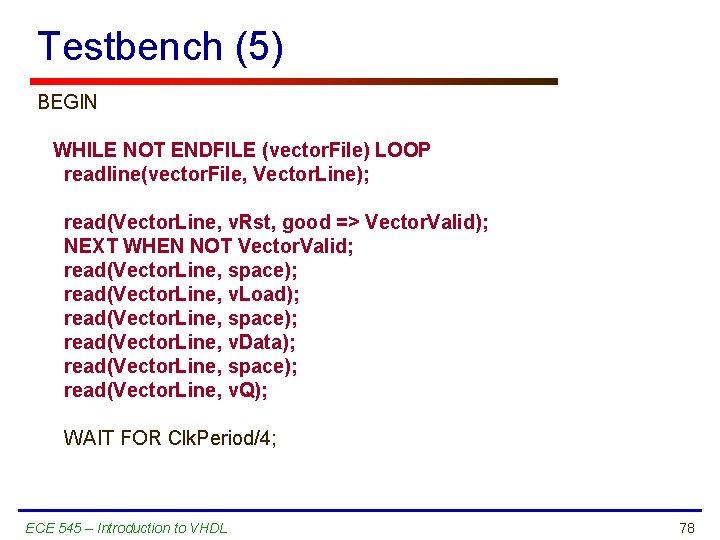

Testbench (5) BEGIN WHILE NOT ENDFILE (vector. File) LOOP readline(vector. File, Vector. Line); read(Vector. Line, v. Rst, good => Vector. Valid); NEXT WHEN NOT Vector. Valid; read(Vector. Line, space); read(Vector. Line, v. Load); read(Vector. Line, space); read(Vector. Line, v. Data); read(Vector. Line, space); read(Vector. Line, v. Q); WAIT FOR Clk. Period/4; ECE 545 – Introduction to VHDL 78

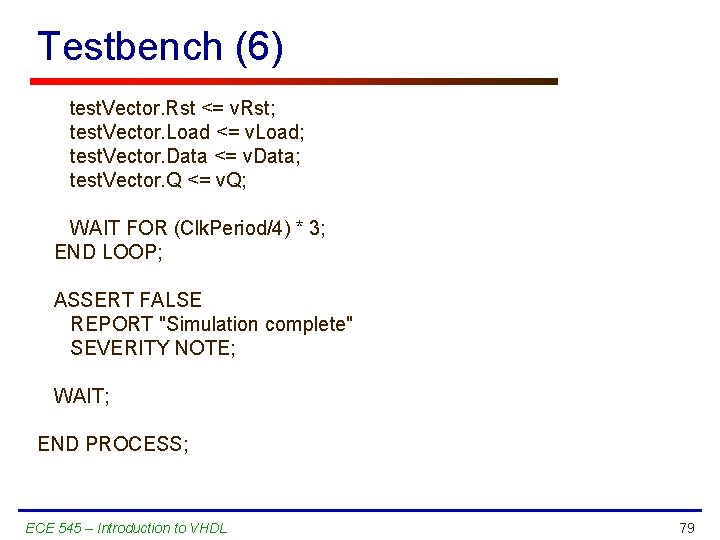

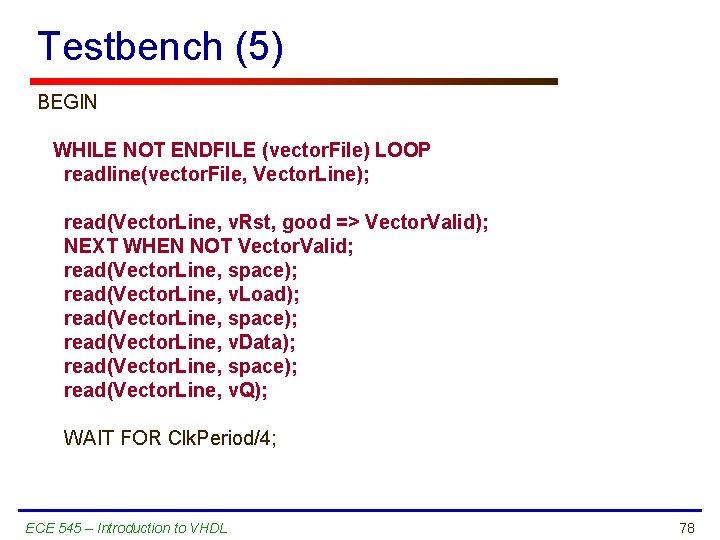

Testbench (6) test. Vector. Rst <= v. Rst; test. Vector. Load <= v. Load; test. Vector. Data <= v. Data; test. Vector. Q <= v. Q; WAIT FOR (Clk. Period/4) * 3; END LOOP; ASSERT FALSE REPORT "Simulation complete" SEVERITY NOTE; WAIT; END PROCESS; ECE 545 – Introduction to VHDL 79

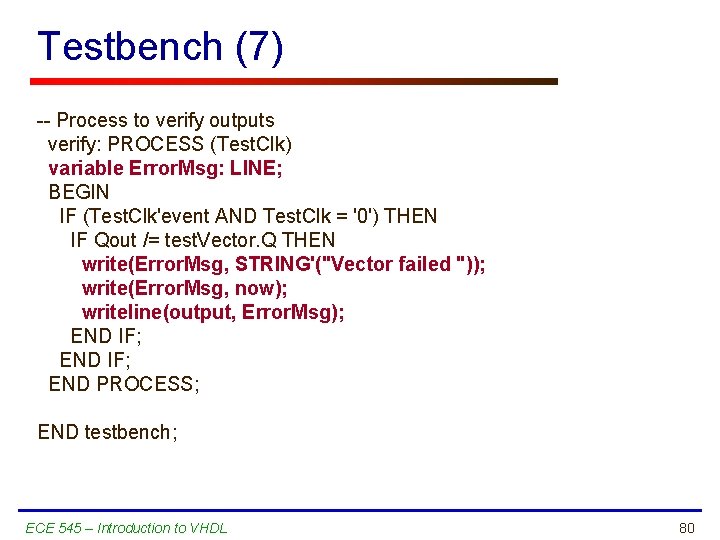

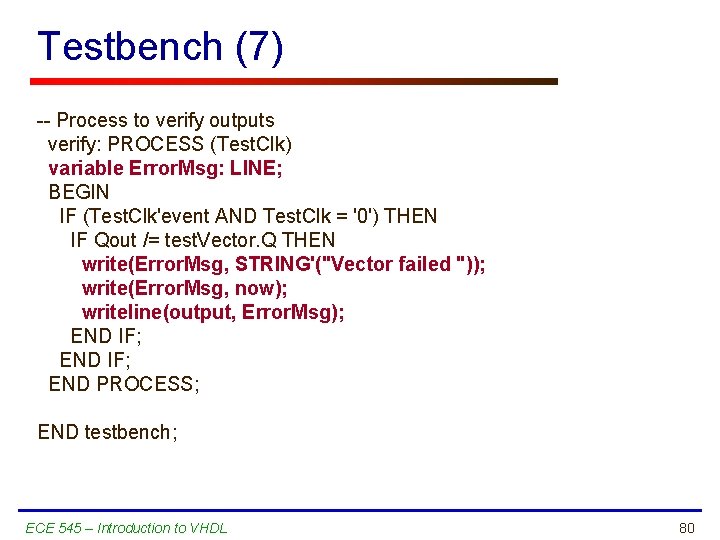

Testbench (7) -- Process to verify outputs verify: PROCESS (Test. Clk) variable Error. Msg: LINE; BEGIN IF (Test. Clk'event AND Test. Clk = '0') THEN IF Qout /= test. Vector. Q THEN write(Error. Msg, STRING'("Vector failed ")); write(Error. Msg, now); writeline(output, Error. Msg); END IF; END PROCESS; END testbench; ECE 545 – Introduction to VHDL 80

Hex format In order to read/write data in the hexadecimal notation, replace read with hread, and write with hwrite ECE 545 – Introduction to VHDL 81