CMOS Analog Design Using Allregion MOSFET Modeling Chapter

- Slides: 32

CMOS Analog Design Using All-region MOSFET Modeling Chapter 3 CMOS technology, components, and layout techniques CMOS Analog Design Using All-Region MOSFET Modeling 1

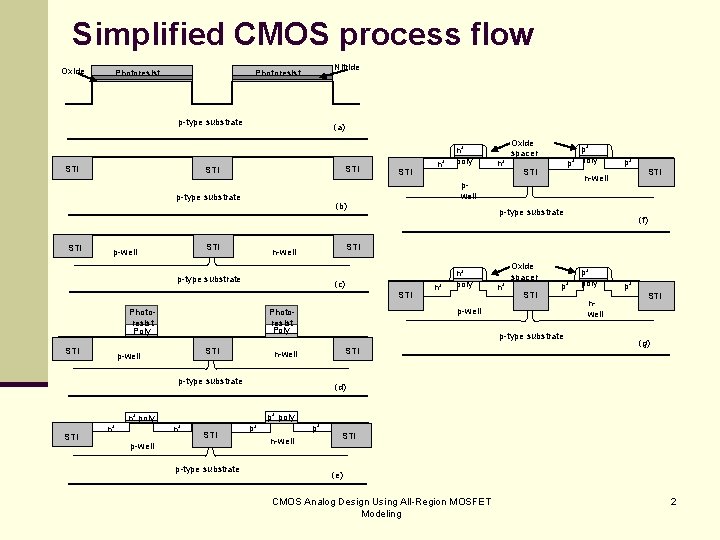

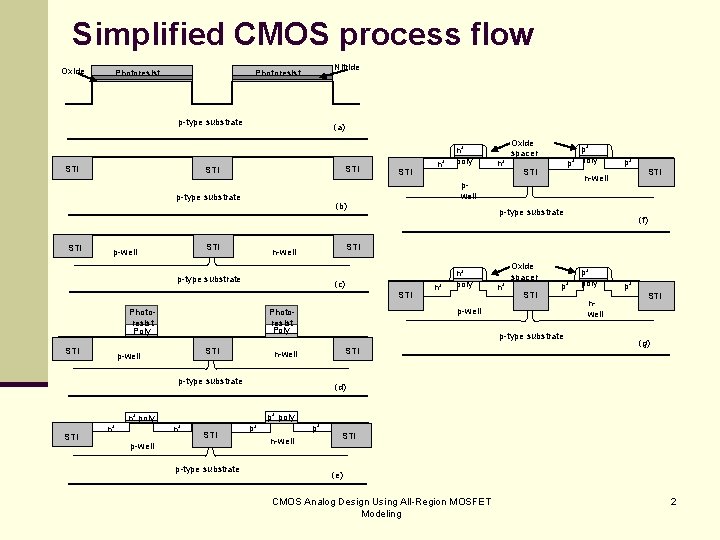

Simplified CMOS process flow Oxide Photoresist Nitride Photoresist p-type substrate STI (a) STI STI p-type substrate STI n-well STI (f) n+ Oxide spacer STI p+ p+ poly nwell p+ STI (g) (d) p+ poly n+ poly STI n+ n+ poly p-type substrate n+ p+ n-well p-well Photoresist Poly STI p+ poly p-type substrate STI p-well p+ pwell (c) Photoresist Poly n+ Oxide spacer STI n-well p-type substrate STI n+ (b) STI p-well STI n+ poly n+ STI p-well p-type substrate p+ p+ n-well STI (e) CMOS Analog Design Using All-Region MOSFET Modeling 2

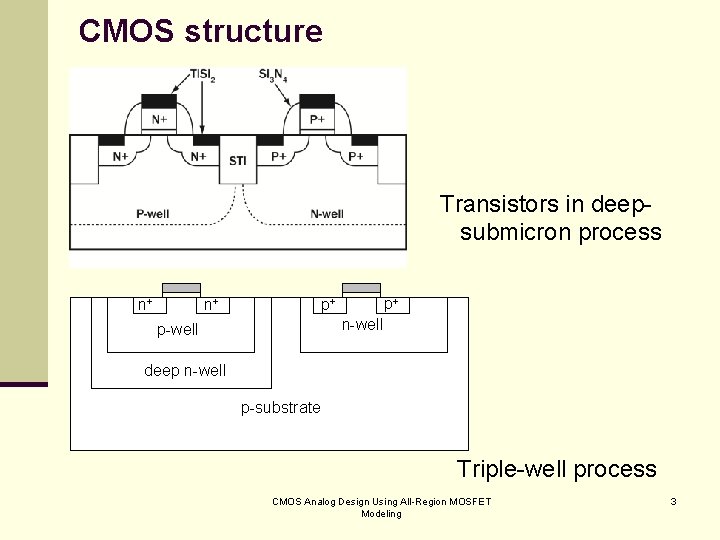

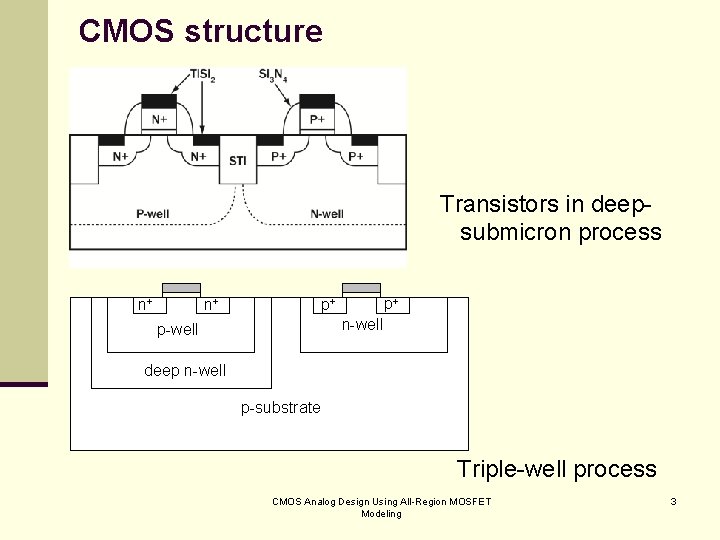

CMOS structure Transistors in deepsubmicron process n+ p+ p+ n+ n-well p-well deep n-well p-substrate Triple-well process CMOS Analog Design Using All-Region MOSFET Modeling 3

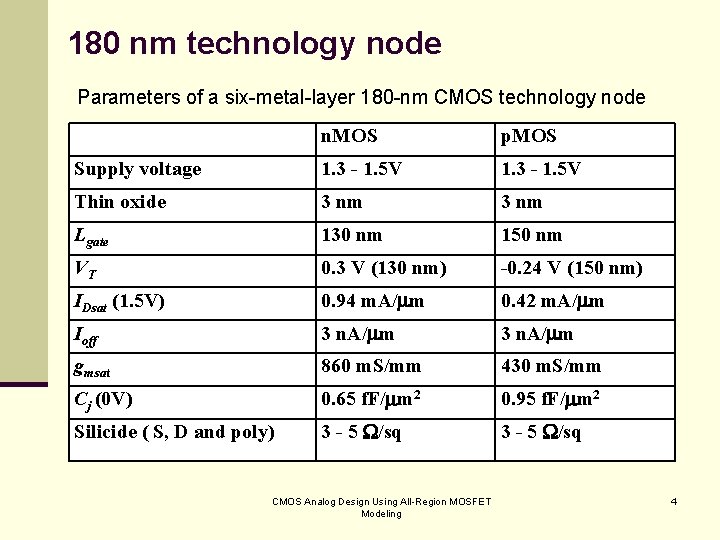

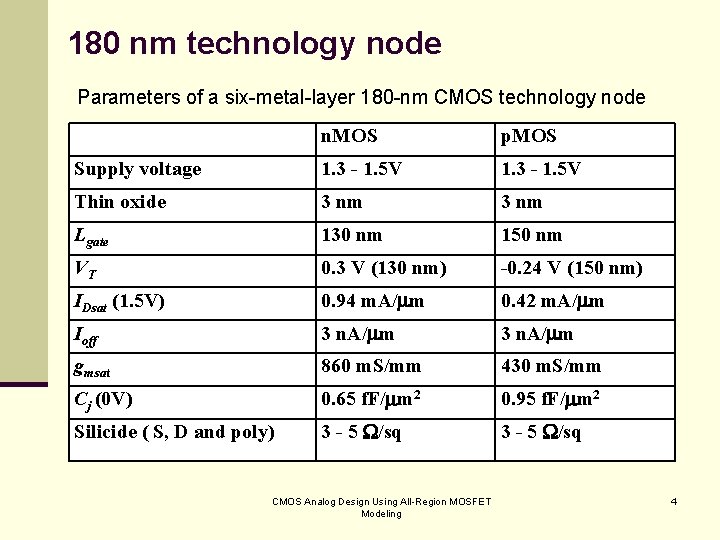

180 nm technology node Parameters of a six-metal-layer 180 -nm CMOS technology node n. MOS p. MOS Supply voltage 1. 3 - 1. 5 V Thin oxide 3 nm Lgate 130 nm 150 nm VT 0. 3 V (130 nm) -0. 24 V (150 nm) IDsat (1. 5 V) 0. 94 m. A/ m 0. 42 m. A/ m Ioff 3 n. A/ m gmsat 860 m. S/mm 430 m. S/mm Cj (0 V) 0. 65 f. F/ m 2 0. 95 f. F/ m 2 Silicide ( S, D and poly) 3 - 5 /sq CMOS Analog Design Using All-Region MOSFET Modeling 4

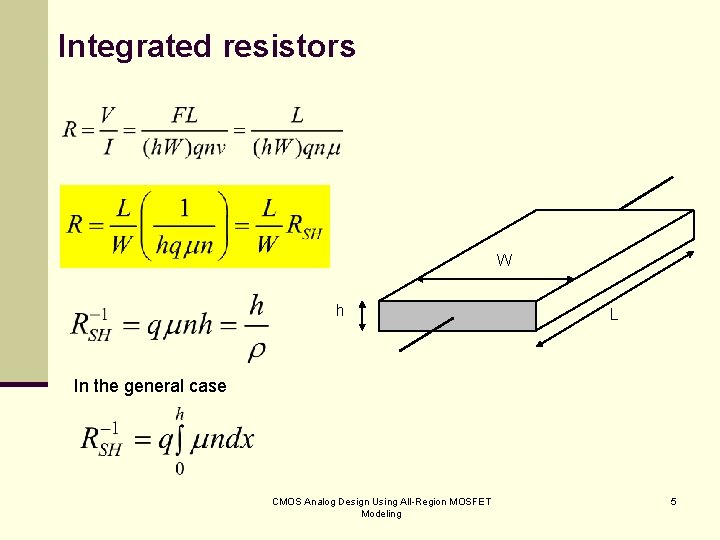

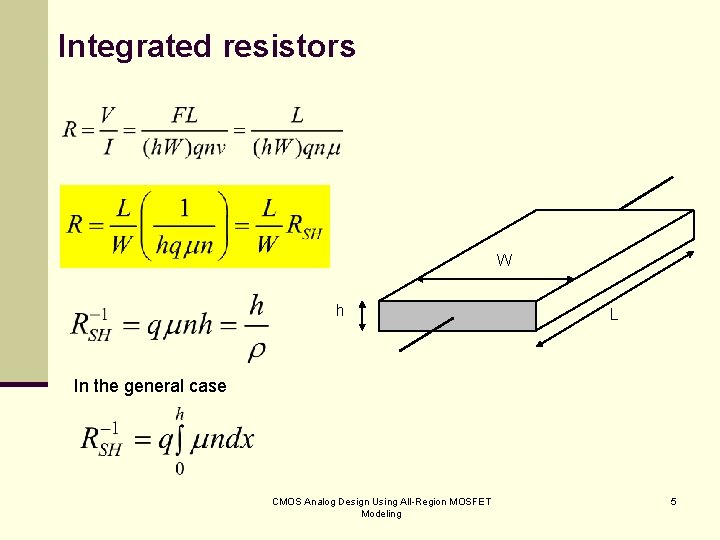

Integrated resistors W h L In the general case CMOS Analog Design Using All-Region MOSFET Modeling 5

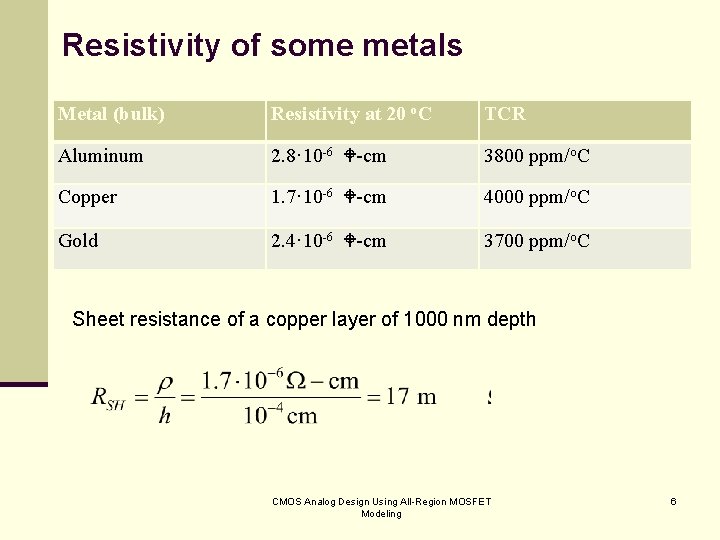

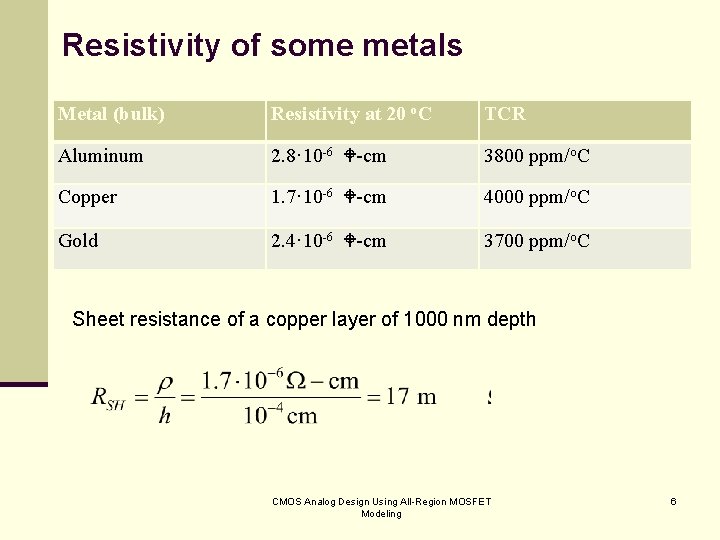

Resistivity of some metals Metal (bulk) Resistivity at 20 o. C TCR Aluminum 2. 8· 10 -6 -cm 3800 ppm/o. C Copper 1. 7· 10 -6 -cm 4000 ppm/o. C Gold 2. 4· 10 -6 -cm 3700 ppm/o. C Sheet resistance of a copper layer of 1000 nm depth CMOS Analog Design Using All-Region MOSFET Modeling 6

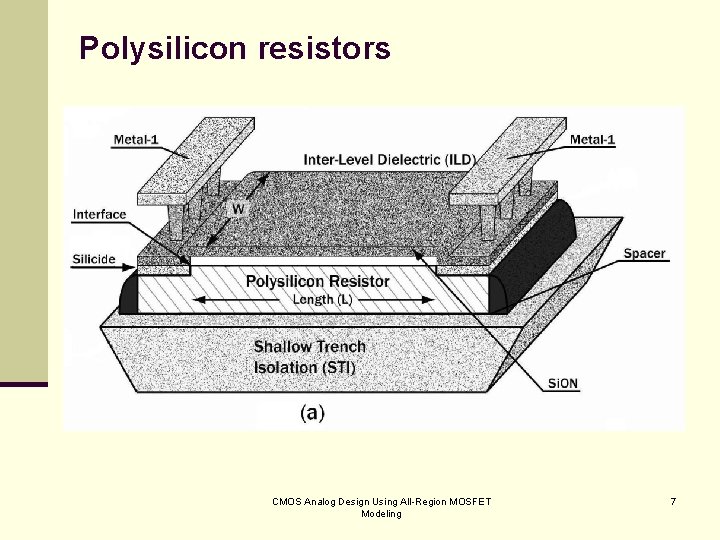

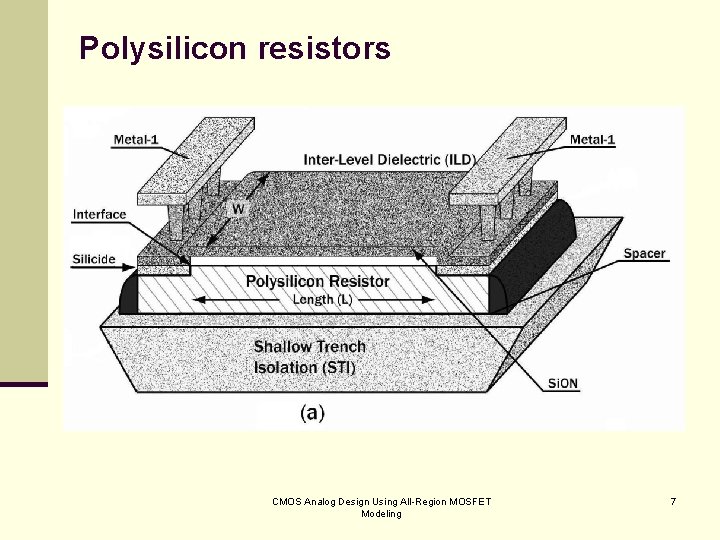

Polysilicon resistors CMOS Analog Design Using All-Region MOSFET Modeling 7

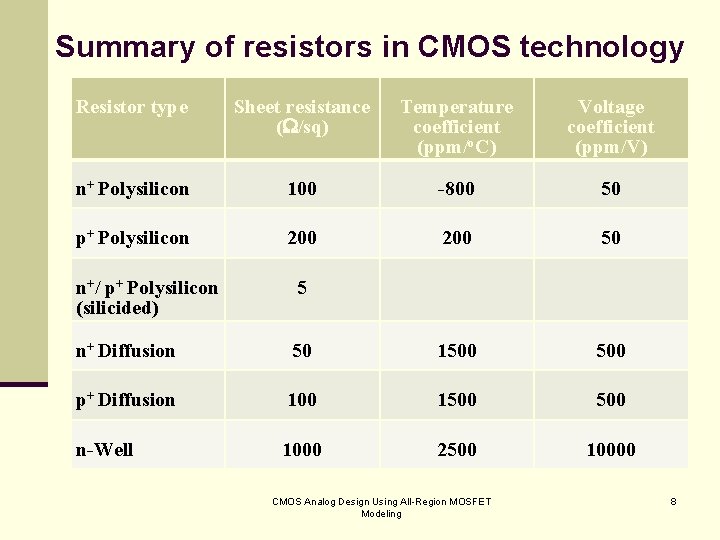

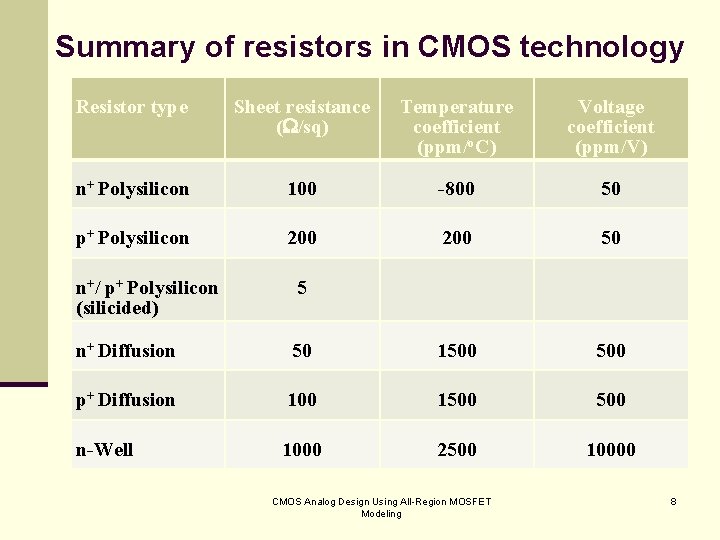

Summary of resistors in CMOS technology Resistor type Sheet resistance ( /sq) Temperature coefficient (ppm/o. C) Voltage coefficient (ppm/V) n+ Polysilicon 100 -800 50 p+ Polysilicon 200 50 n+/ p+ Polysilicon (silicided) 5 n+ Diffusion 50 1500 p+ Diffusion 100 1500 n-Well 1000 2500 10000 CMOS Analog Design Using All-Region MOSFET Modeling 8

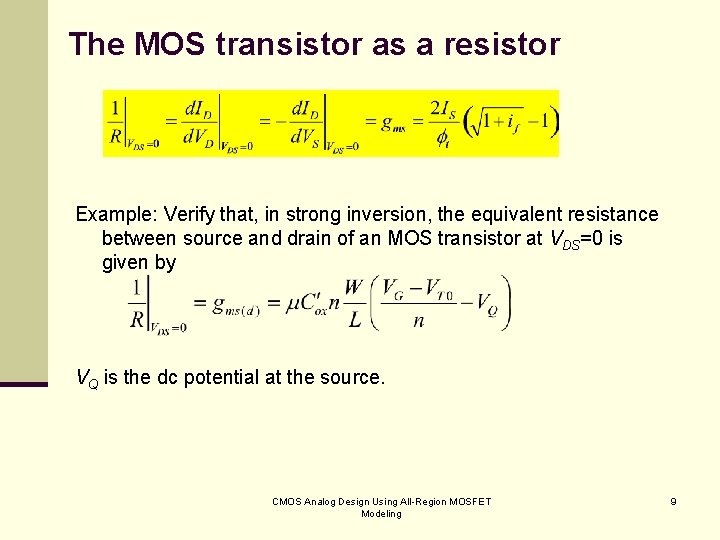

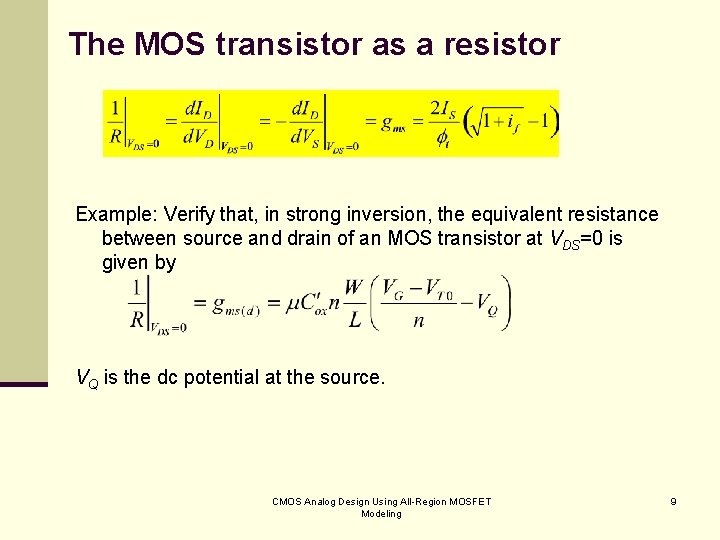

The MOS transistor as a resistor Example: Verify that, in strong inversion, the equivalent resistance between source and drain of an MOS transistor at VDS=0 is given by VQ is the dc potential at the source. CMOS Analog Design Using All-Region MOSFET Modeling 9

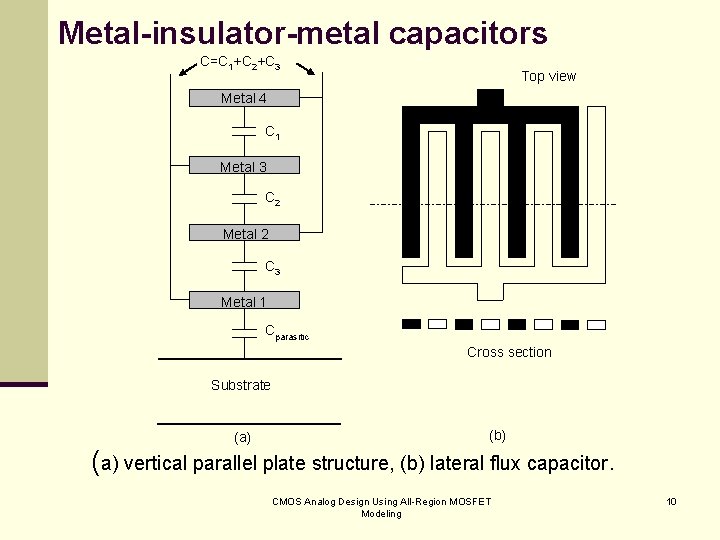

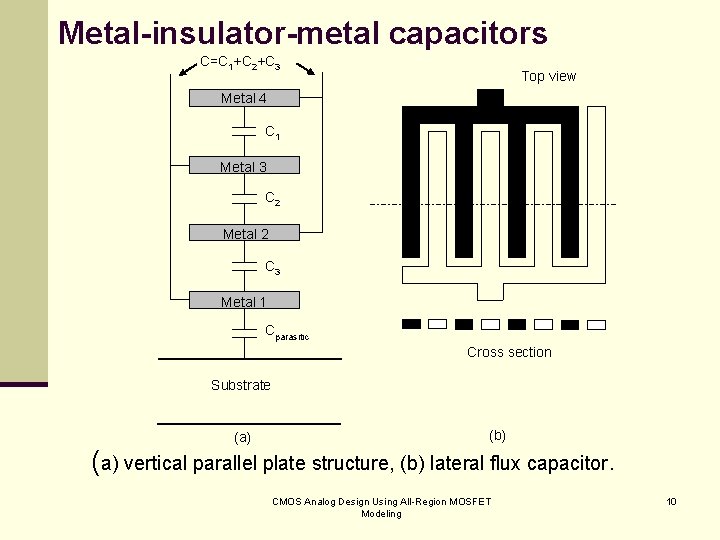

Metal-insulator-metal capacitors C=C 1+C 2+C 3 Top view Metal 4 C 1 Metal 3 C 2 Metal 2 C 3 Metal 1 Cparasitic Cross section Substrate (a) (b) (a) vertical parallel plate structure, (b) lateral flux capacitor. CMOS Analog Design Using All-Region MOSFET Modeling 10

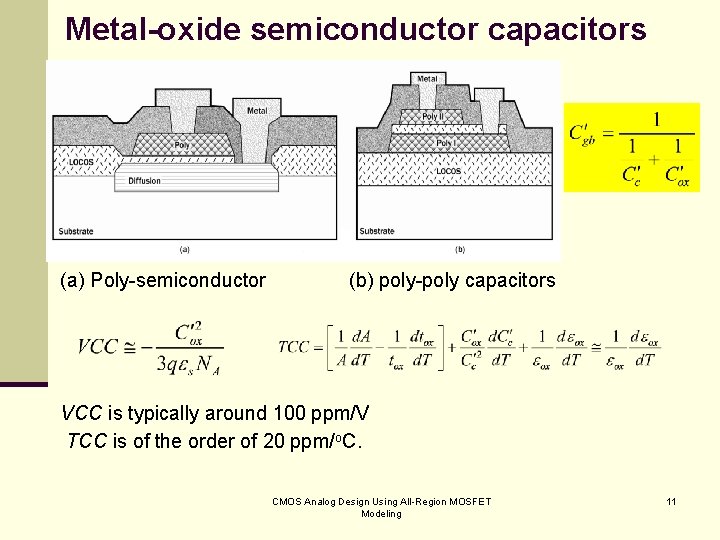

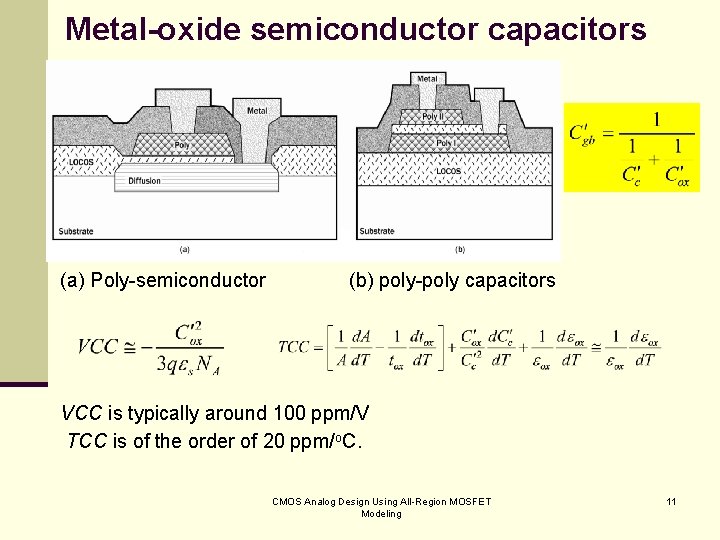

Metal-oxide semiconductor capacitors (a) Poly-semiconductor (b) poly-poly capacitors VCC is typically around 100 ppm/V TCC is of the order of 20 ppm/o. C. CMOS Analog Design Using All-Region MOSFET Modeling 11

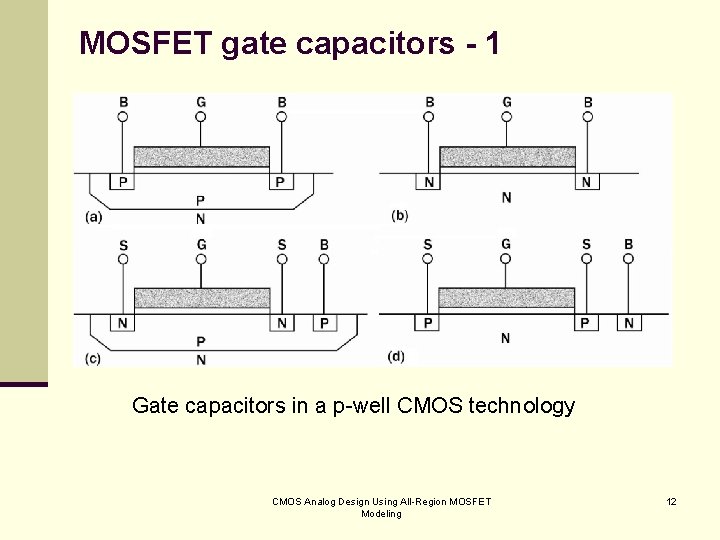

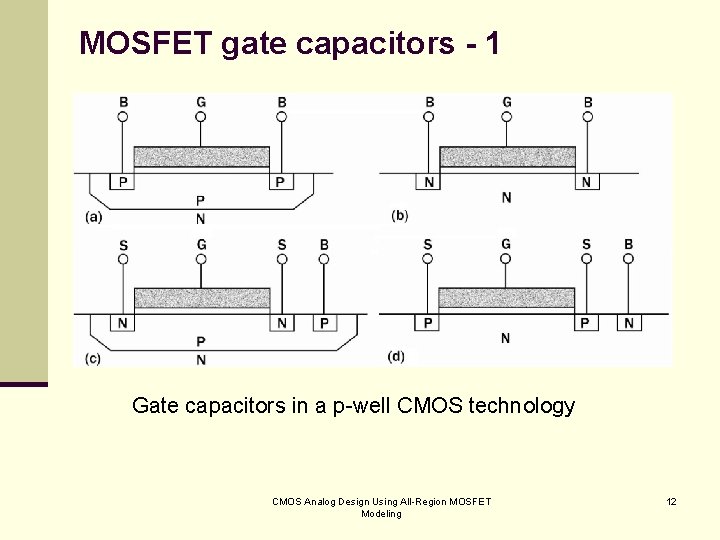

MOSFET gate capacitors - 1 Gate capacitors in a p-well CMOS technology CMOS Analog Design Using All-Region MOSFET Modeling 12

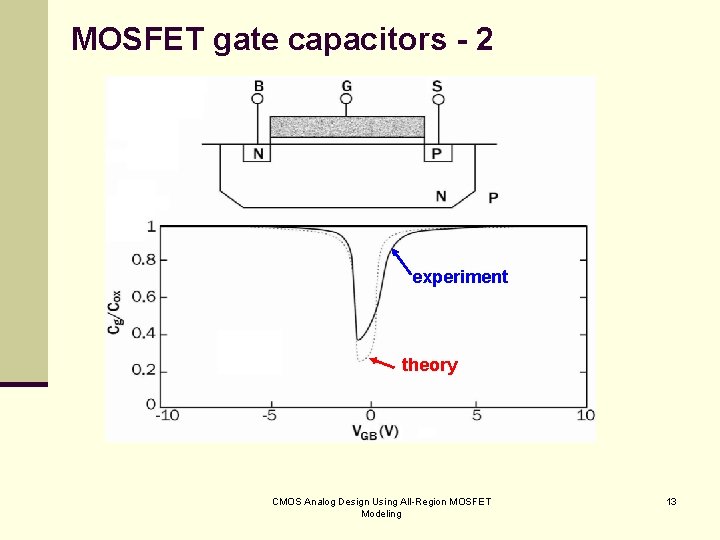

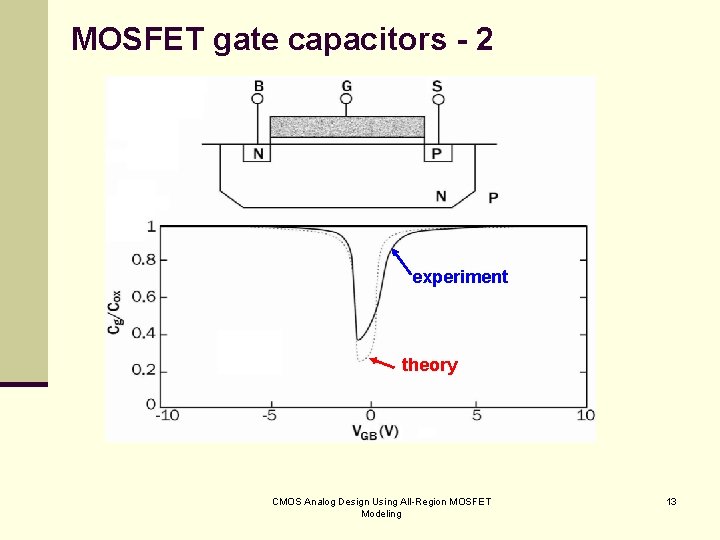

MOSFET gate capacitors - 2 experiment theory CMOS Analog Design Using All-Region MOSFET Modeling 13

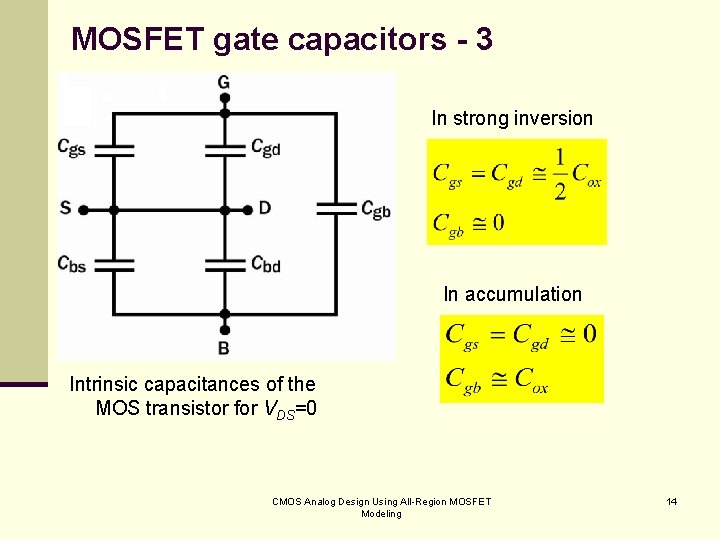

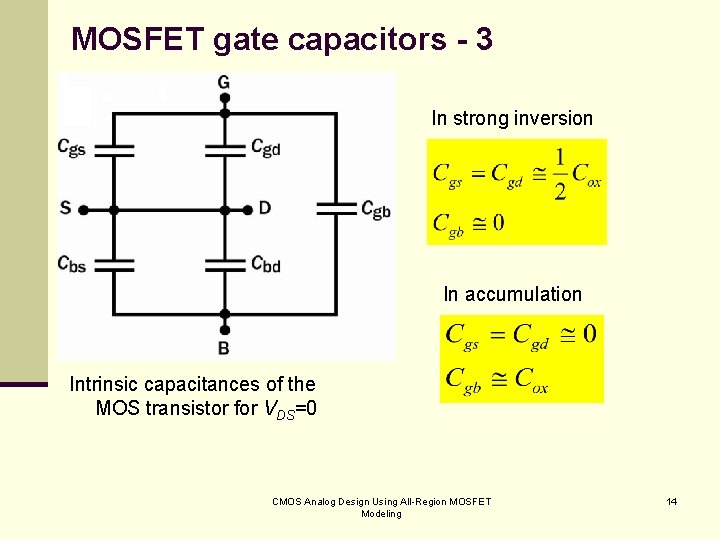

MOSFET gate capacitors - 3 In strong inversion In accumulation Intrinsic capacitances of the MOS transistor for VDS=0 CMOS Analog Design Using All-Region MOSFET Modeling 14

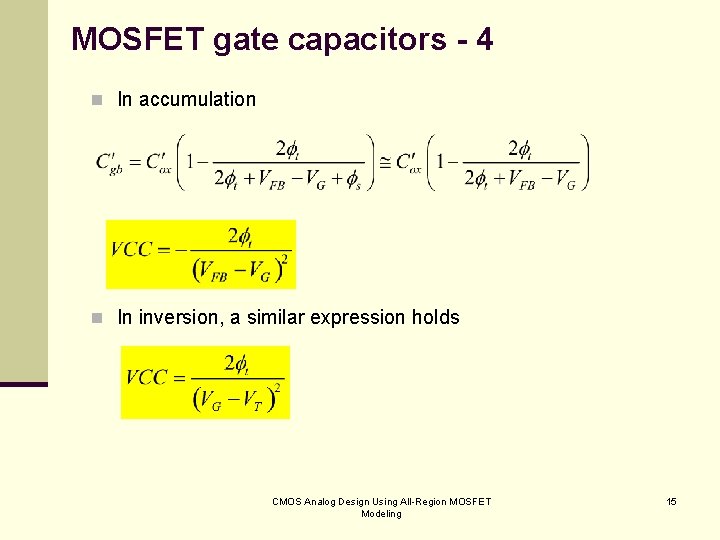

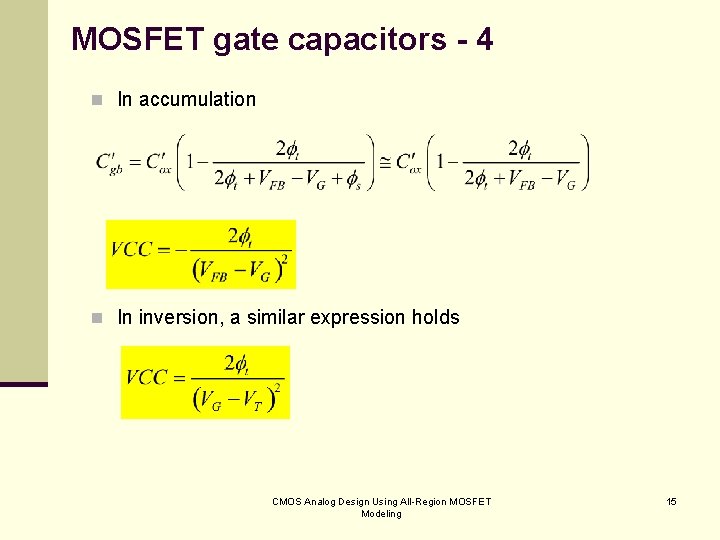

MOSFET gate capacitors - 4 n In accumulation n In inversion, a similar expression holds CMOS Analog Design Using All-Region MOSFET Modeling 15

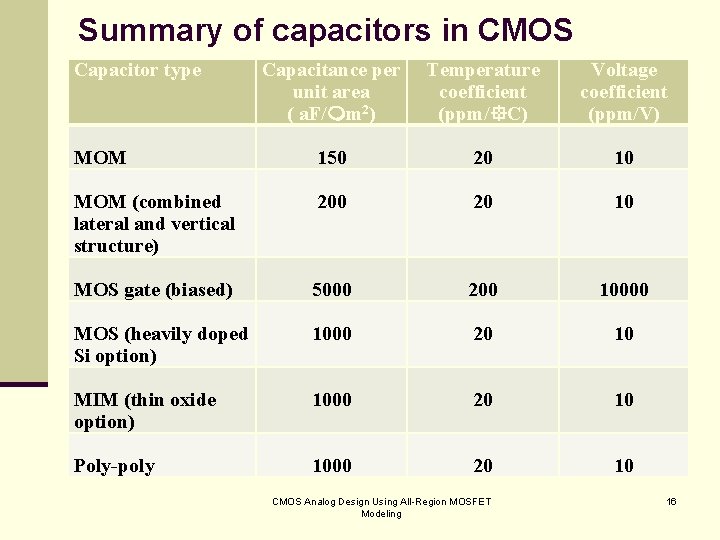

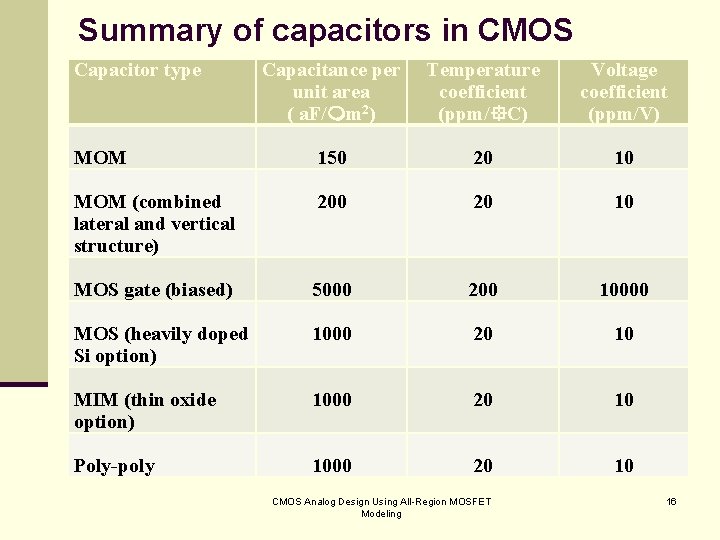

Summary of capacitors in CMOS Capacitor type Capacitance per unit area ( a. F/ m 2) Temperature coefficient (ppm/ C) Voltage coefficient (ppm/V) MOM 150 20 10 MOM (combined lateral and vertical structure) 200 20 10 MOS gate (biased) 5000 200 10000 MOS (heavily doped Si option) 1000 20 10 MIM (thin oxide option) 1000 20 10 Poly-poly 1000 20 10 CMOS Analog Design Using All-Region MOSFET Modeling 16

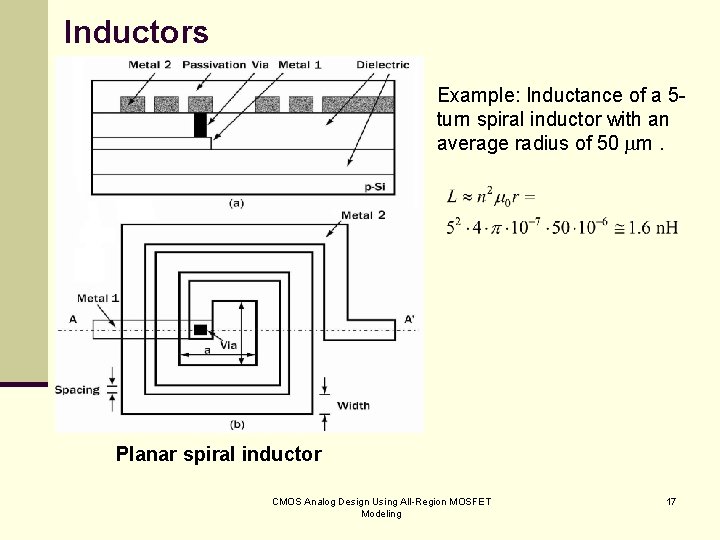

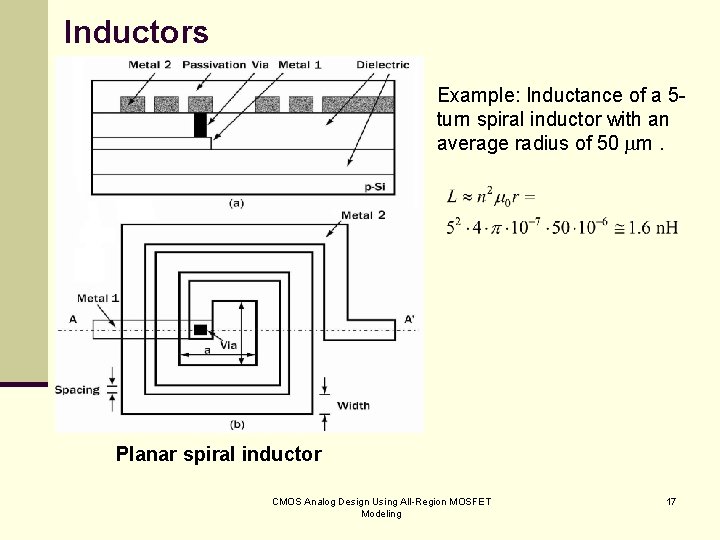

Inductors Example: Inductance of a 5 turn spiral inductor with an average radius of 50 m. Planar spiral inductor CMOS Analog Design Using All-Region MOSFET Modeling 17

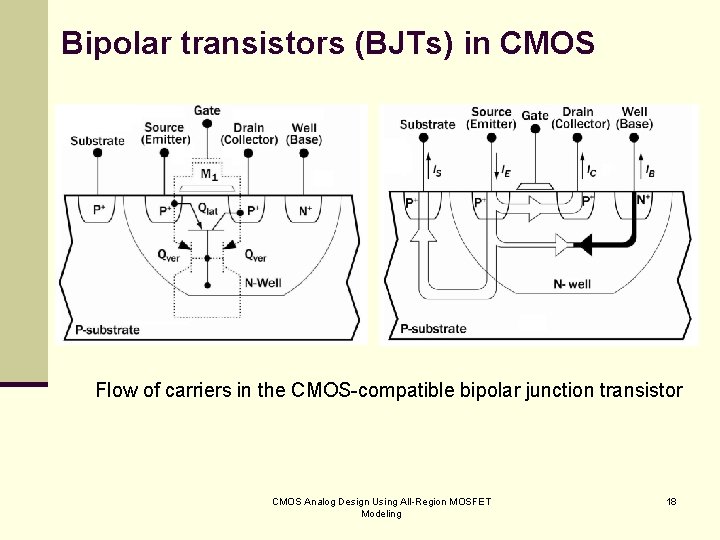

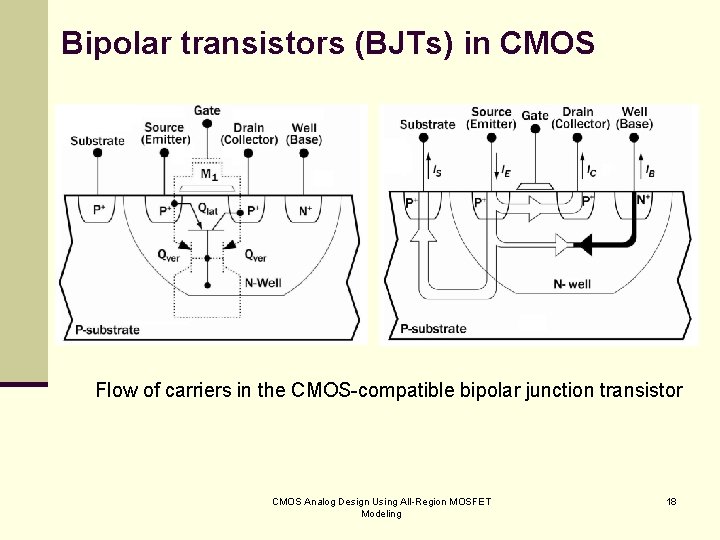

Bipolar transistors (BJTs) in CMOS Flow of carriers in the CMOS-compatible bipolar junction transistor CMOS Analog Design Using All-Region MOSFET Modeling 18

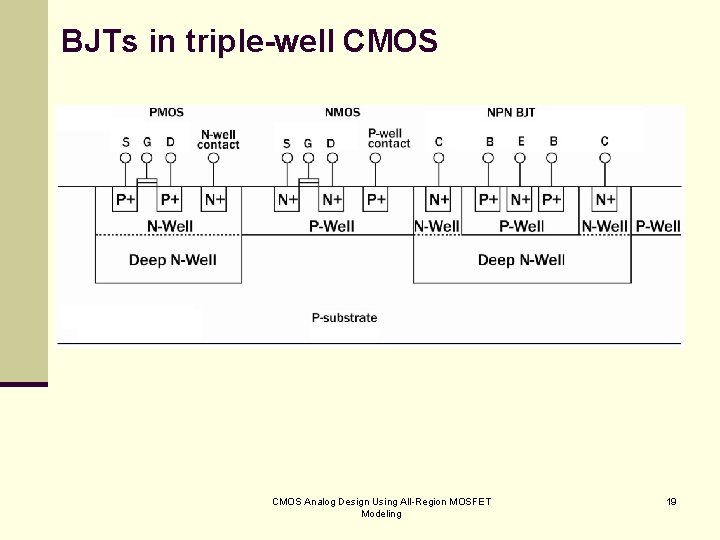

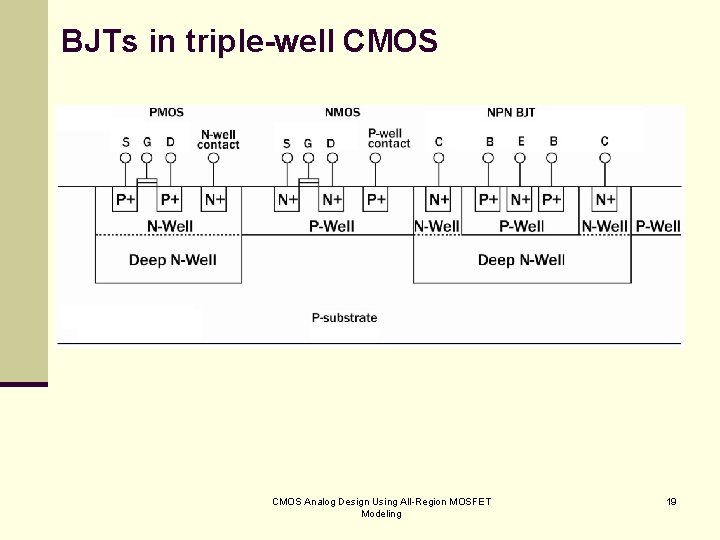

BJTs in triple-well CMOS Analog Design Using All-Region MOSFET Modeling 19

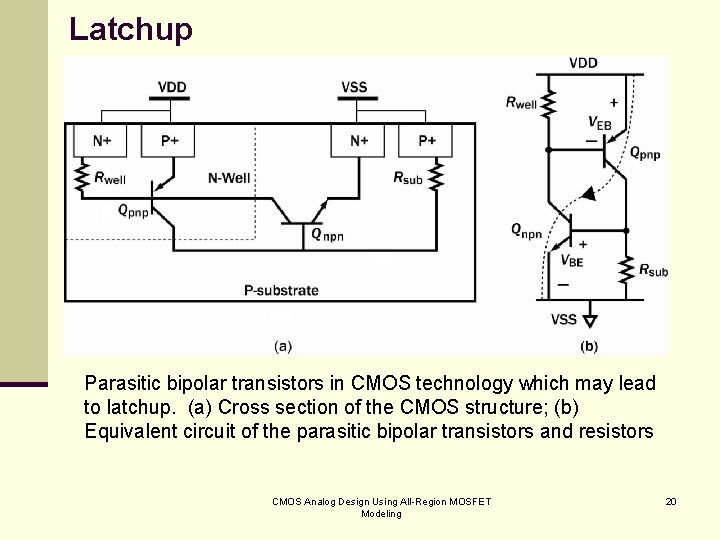

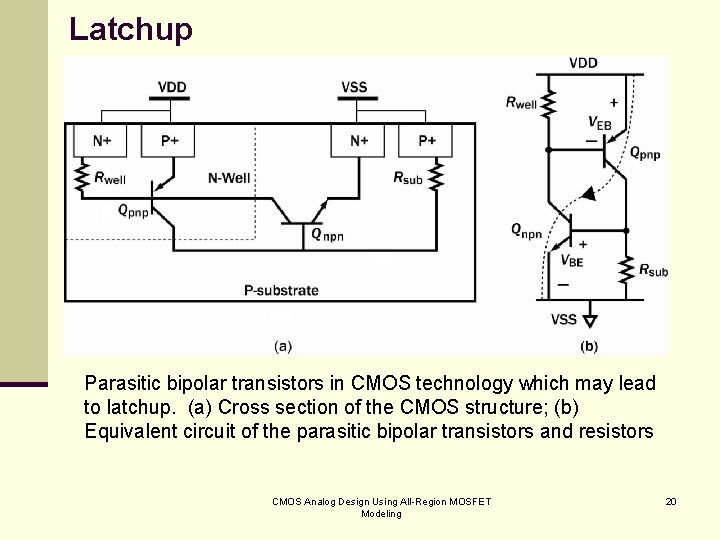

Latchup Parasitic bipolar transistors in CMOS technology which may lead to latchup. (a) Cross section of the CMOS structure; (b) Equivalent circuit of the parasitic bipolar transistors and resistors CMOS Analog Design Using All-Region MOSFET Modeling 20

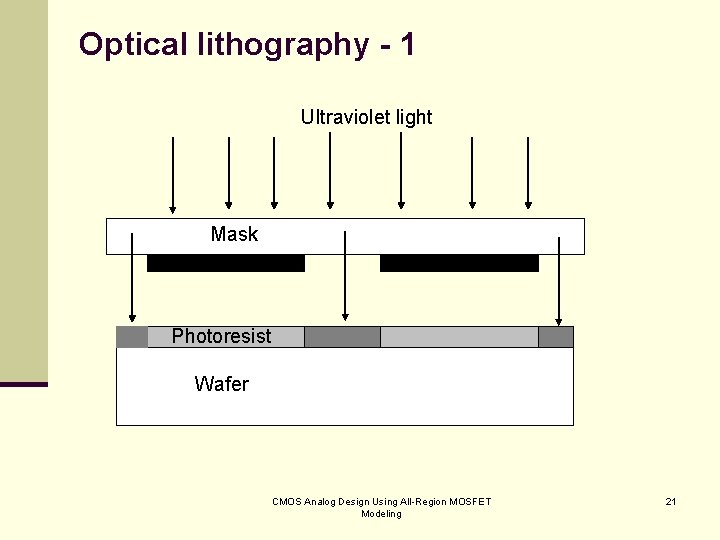

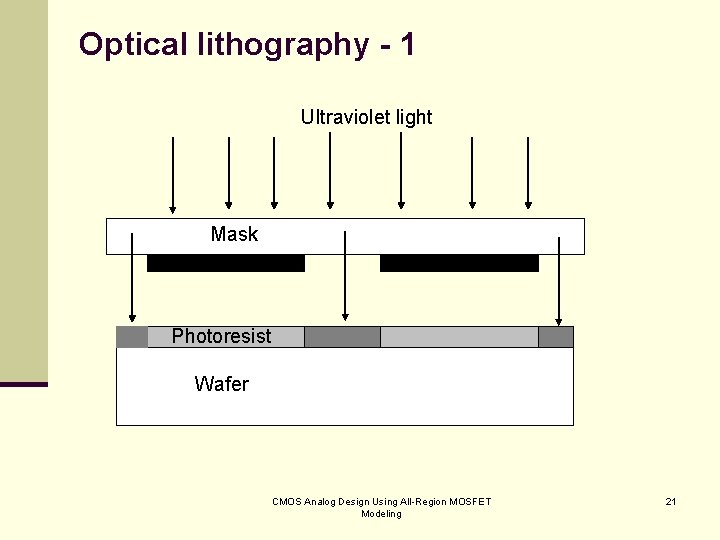

Optical lithography - 1 Ultraviolet light Mask Photoresist Wafer CMOS Analog Design Using All-Region MOSFET Modeling 21

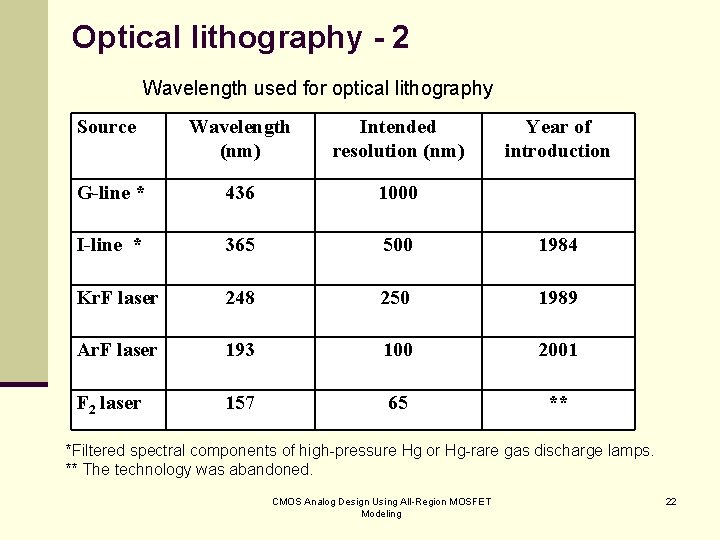

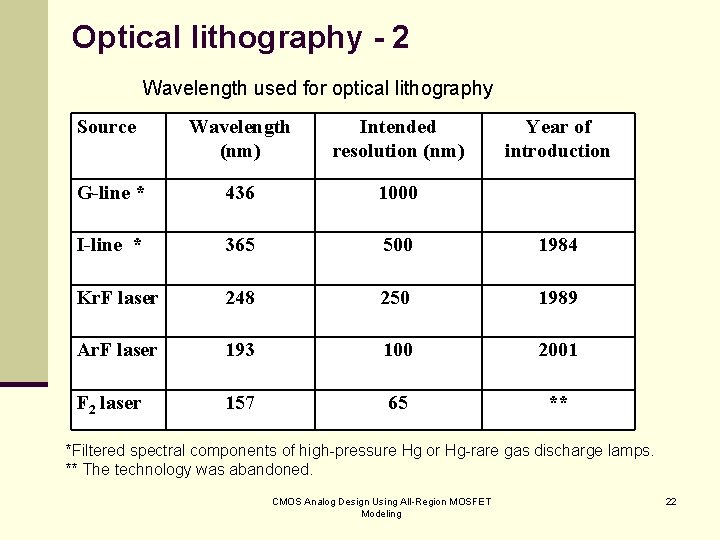

Optical lithography - 2 Wavelength used for optical lithography Source Wavelength (nm) Intended resolution (nm) Year of introduction G-line * 436 1000 I-line * 365 500 1984 Kr. F laser 248 250 1989 Ar. F laser 193 100 2001 F 2 laser 157 65 ** *Filtered spectral components of high-pressure Hg or Hg-rare gas discharge lamps. ** The technology was abandoned. CMOS Analog Design Using All-Region MOSFET Modeling 22

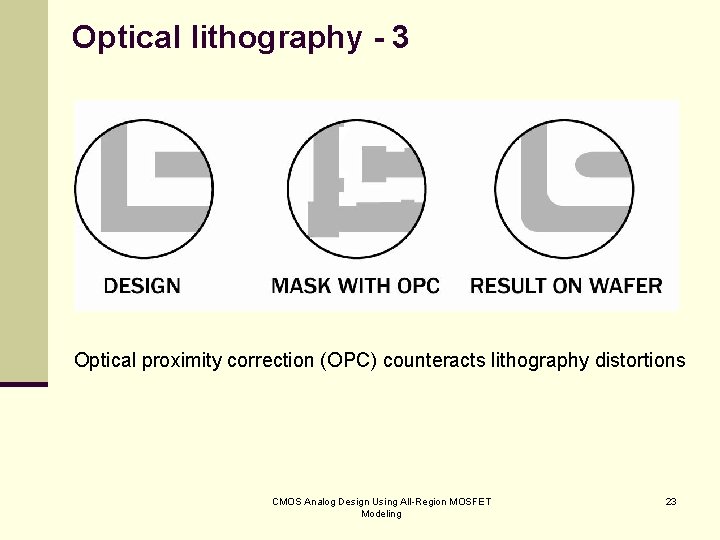

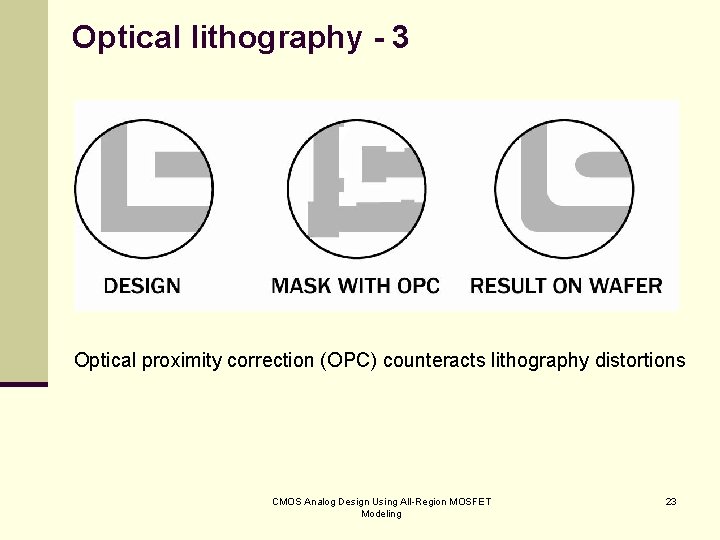

Optical lithography - 3 Optical proximity correction (OPC) counteracts lithography distortions CMOS Analog Design Using All-Region MOSFET Modeling 23

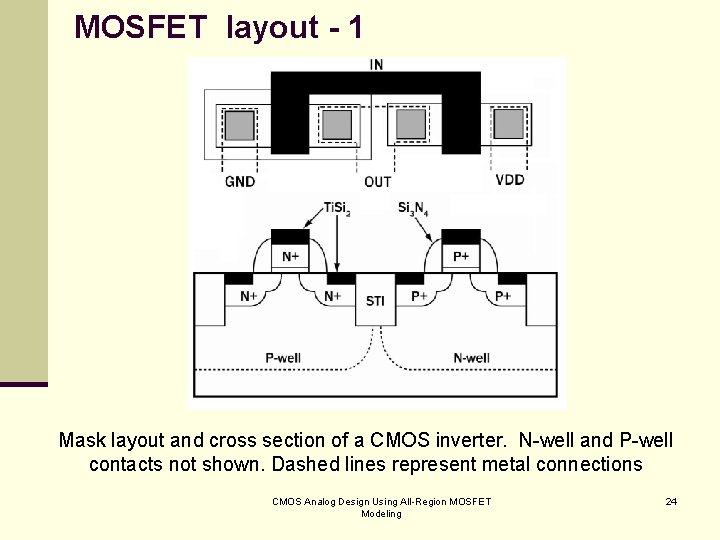

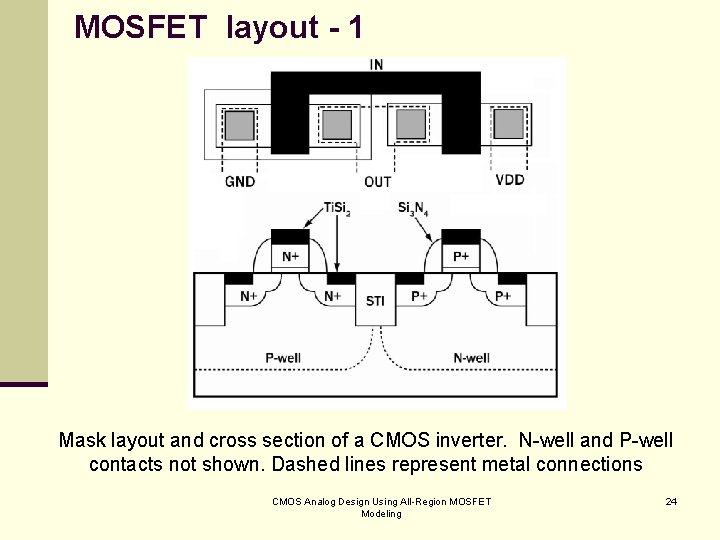

MOSFET layout - 1 Mask layout and cross section of a CMOS inverter. N-well and P-well contacts not shown. Dashed lines represent metal connections CMOS Analog Design Using All-Region MOSFET Modeling 24

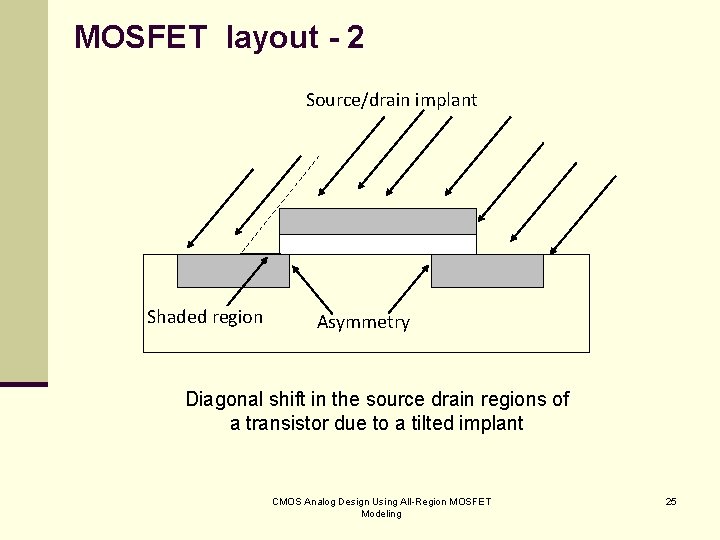

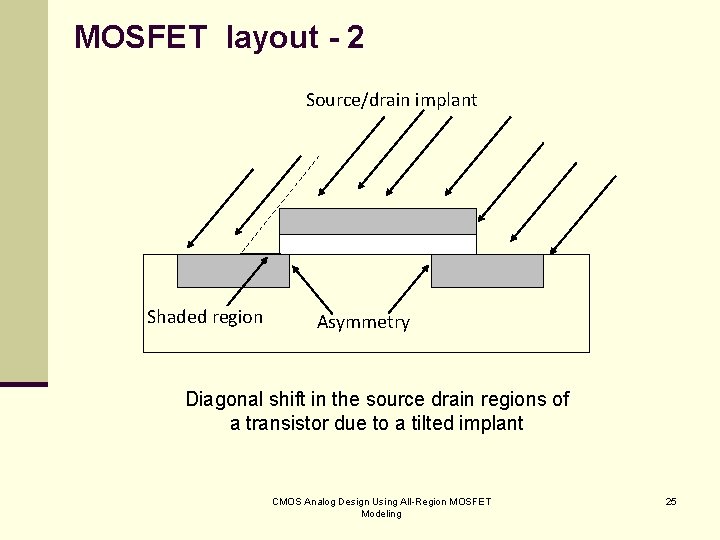

MOSFET layout - 2 Source/drain implant Shaded region Asymmetry Diagonal shift in the source drain regions of a transistor due to a tilted implant CMOS Analog Design Using All-Region MOSFET Modeling 25

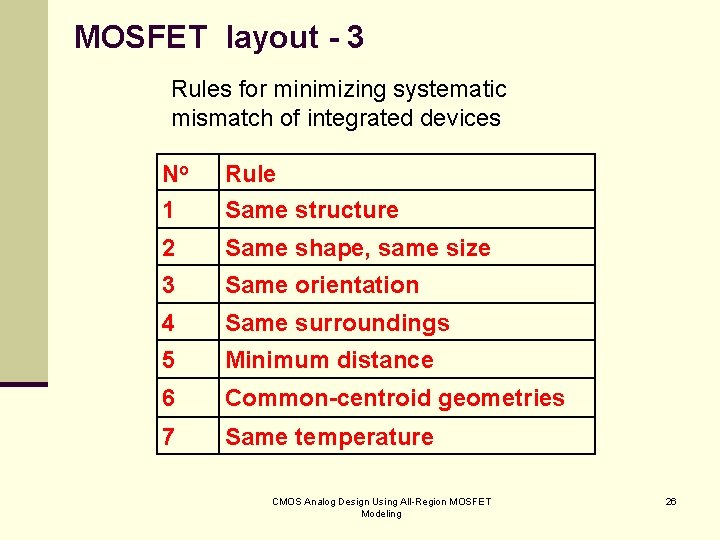

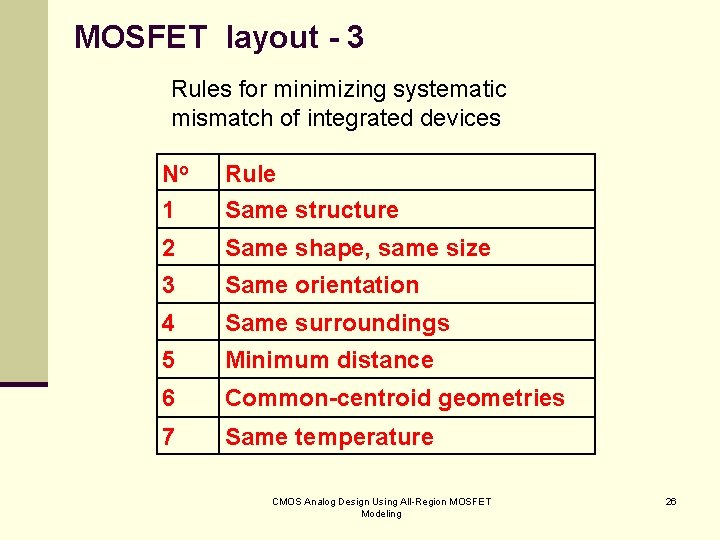

MOSFET layout - 3 Rules for minimizing systematic mismatch of integrated devices No 1 Rule Same structure 2 Same shape, same size 3 Same orientation 4 Same surroundings 5 Minimum distance 6 Common-centroid geometries 7 Same temperature CMOS Analog Design Using All-Region MOSFET Modeling 26

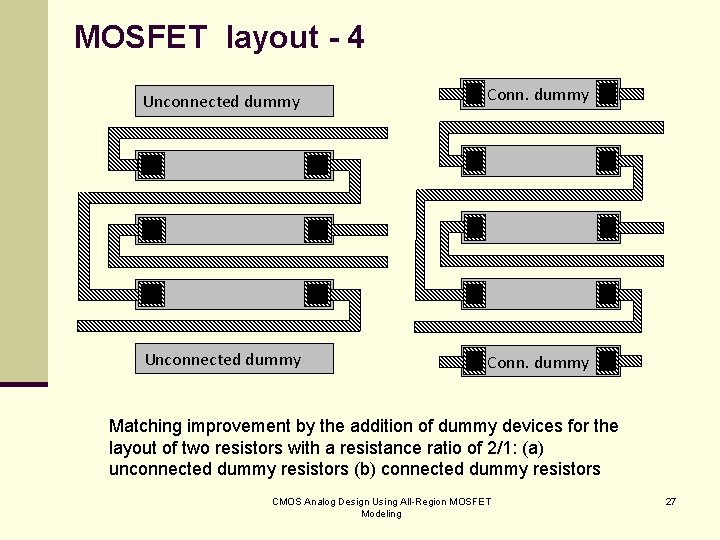

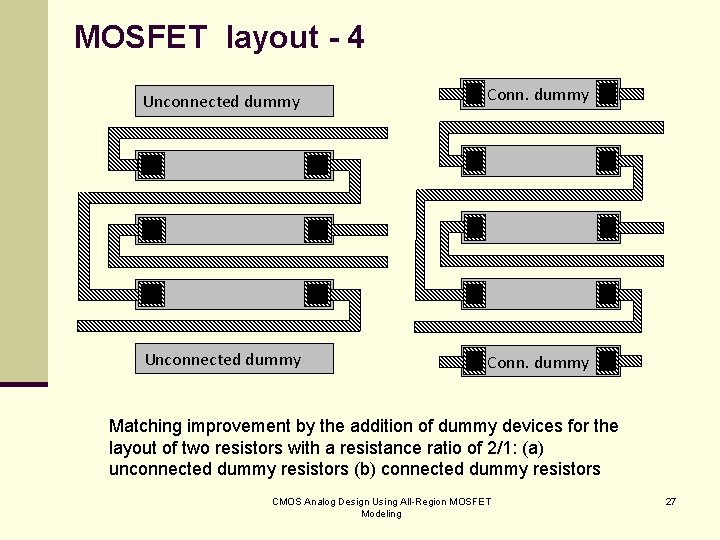

MOSFET layout - 4 Unconnected dummy Conn. dummy Matching improvement by the addition of dummy devices for the layout of two resistors with a resistance ratio of 2/1: (a) unconnected dummy resistors (b) connected dummy resistors CMOS Analog Design Using All-Region MOSFET Modeling 27

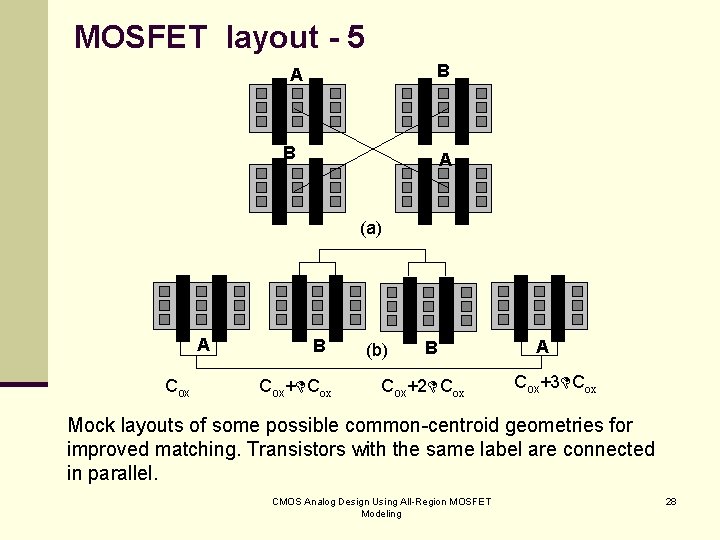

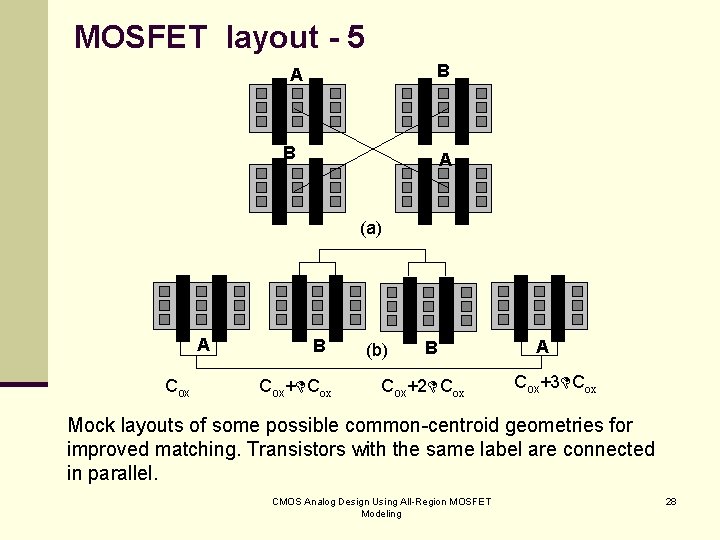

MOSFET layout - 5 B A (a) A Cox B Cox+ Cox (b) B Cox+2 Cox A Cox+3 Cox Mock layouts of some possible common-centroid geometries for improved matching. Transistors with the same label are connected in parallel. CMOS Analog Design Using All-Region MOSFET Modeling 28

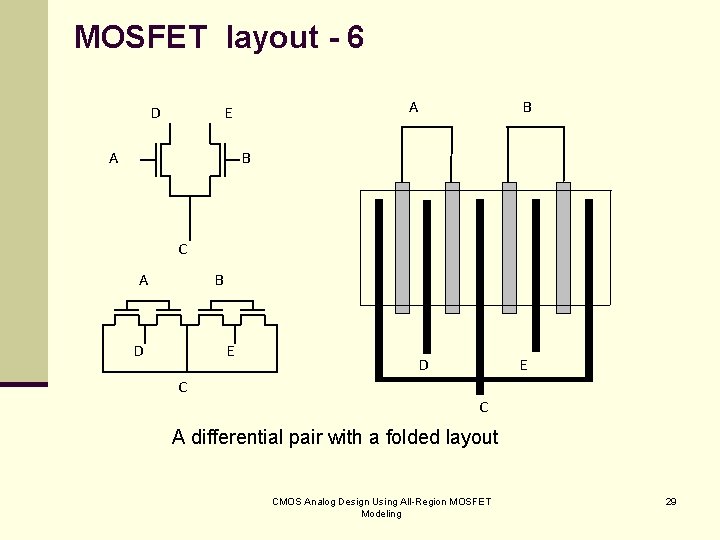

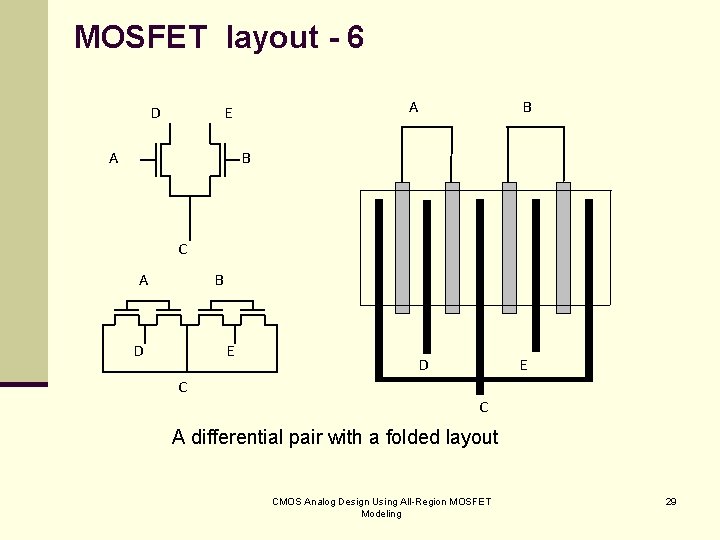

MOSFET layout - 6 D A B A E B C A B D E C C A differential pair with a folded layout CMOS Analog Design Using All-Region MOSFET Modeling 29

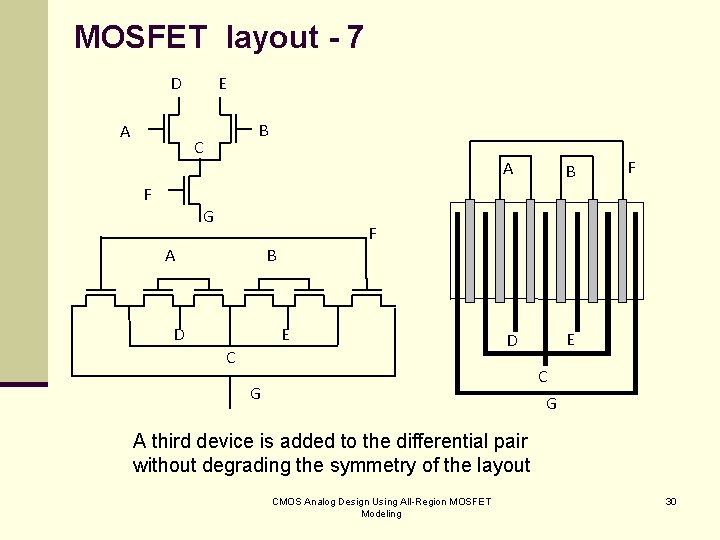

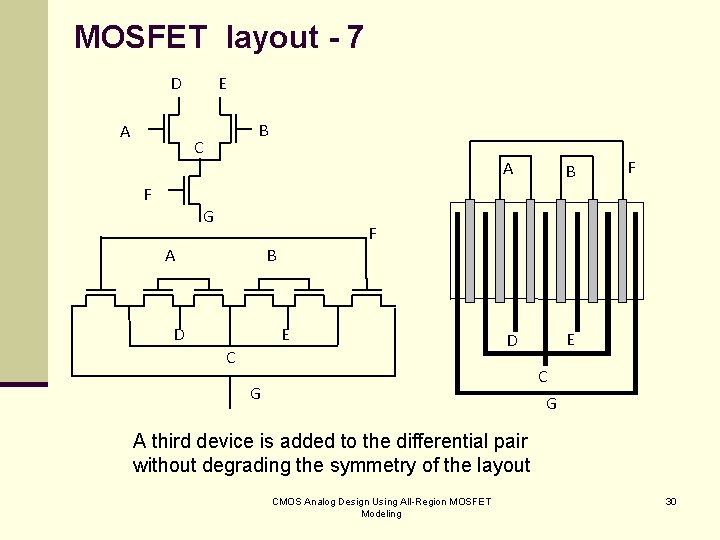

MOSFET layout - 7 D A E B C A B D E F F G A F B D E C C G G A third device is added to the differential pair without degrading the symmetry of the layout CMOS Analog Design Using All-Region MOSFET Modeling 30

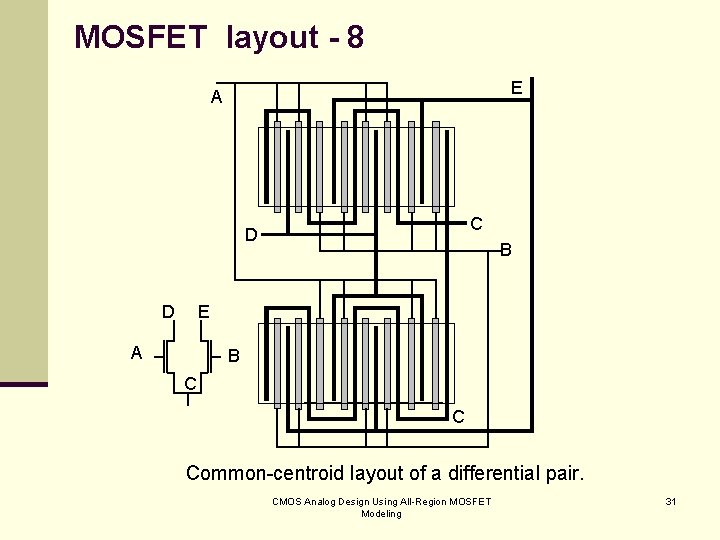

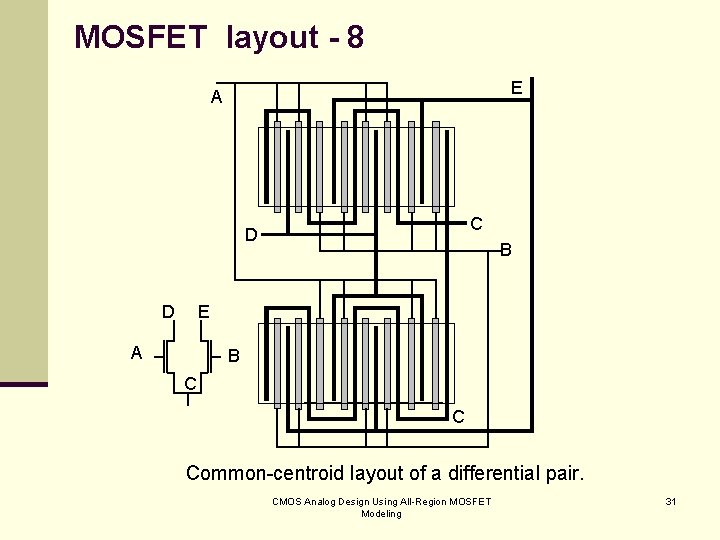

MOSFET layout - 8 E A C D D B E A B C C Common-centroid layout of a differential pair. CMOS Analog Design Using All-Region MOSFET Modeling 31

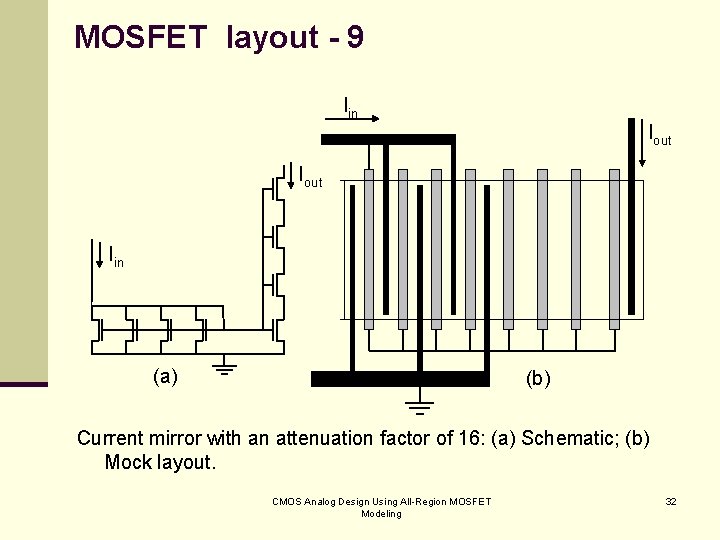

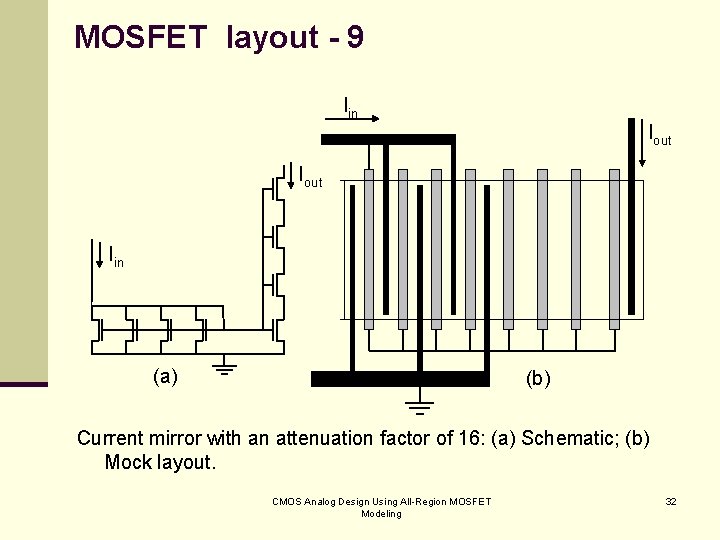

MOSFET layout - 9 Iin Iout Iin (a) (b) Current mirror with an attenuation factor of 16: (a) Schematic; (b) Mock layout. CMOS Analog Design Using All-Region MOSFET Modeling 32