1 A TimeToDigital Converter TDC Harley Cumming Lisa

- Slides: 35

1 A Time-To-Digital Converter (TDC) Harley Cumming Lisa Kotowski

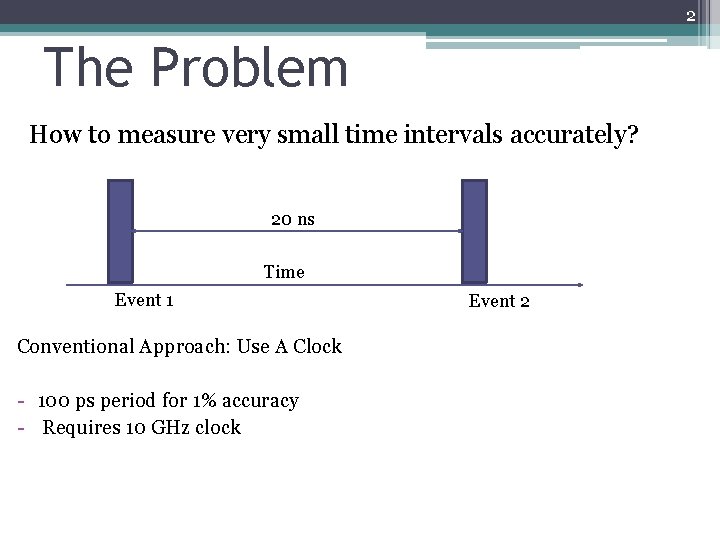

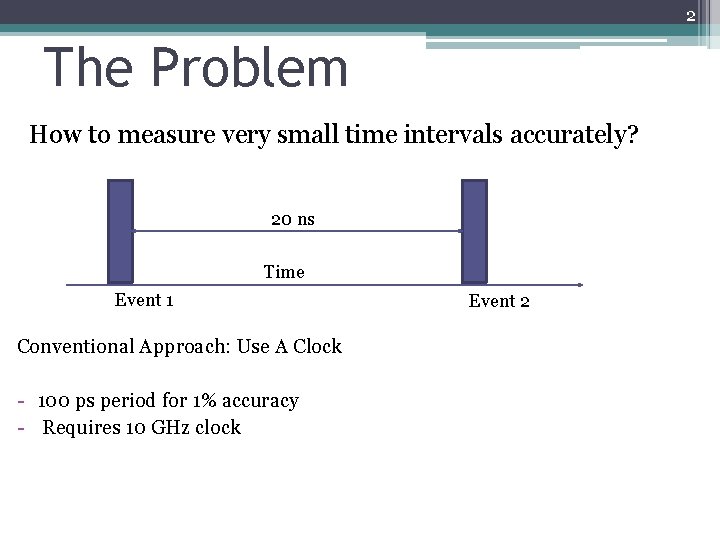

2 The Problem How to measure very small time intervals accurately? 20 ns Time Event 1 Conventional Approach: Use A Clock - 100 ps period for 1% accuracy - Requires 10 GHz clock Event 2

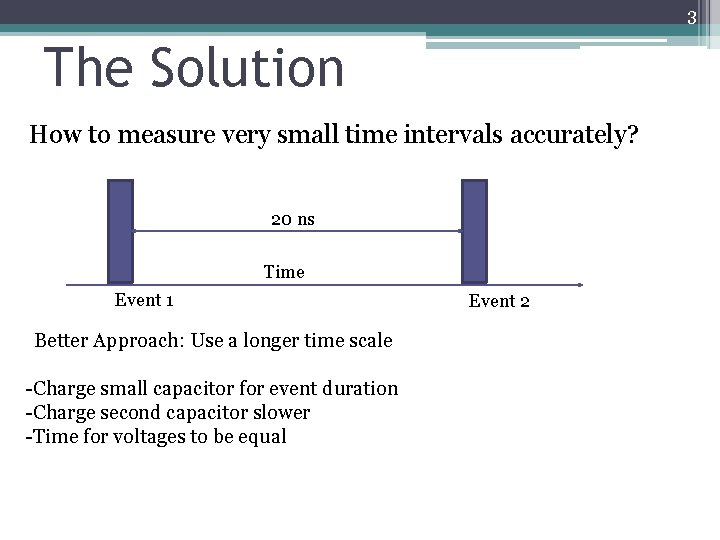

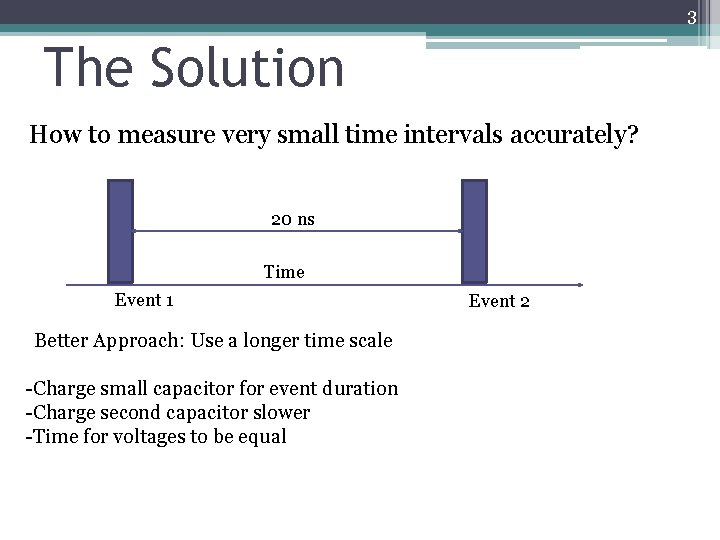

3 The Solution How to measure very small time intervals accurately? 20 ns Time Event 1 Better Approach: Use a longer time scale -Charge small capacitor for event duration -Charge second capacitor slower -Time for voltages to be equal Event 2

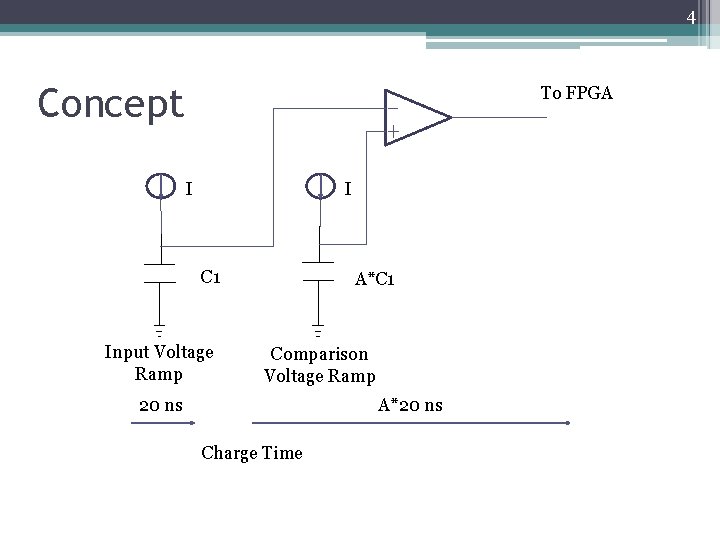

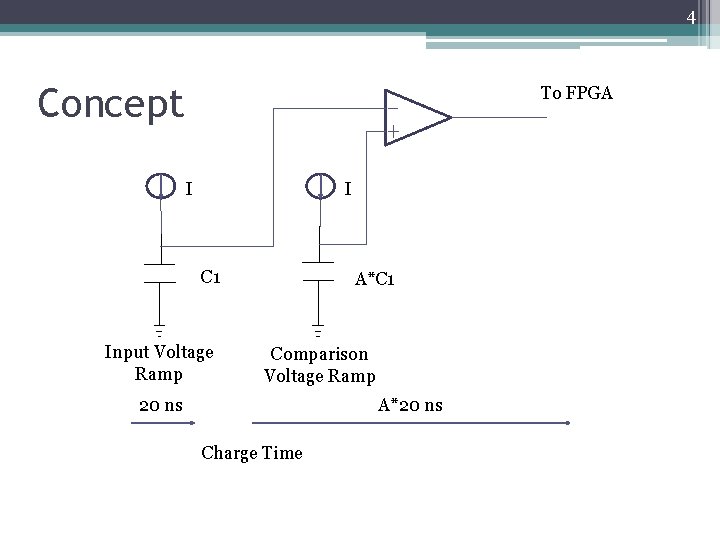

4 Concept To FPGA I I C 1 Input Voltage Ramp A*C 1 Comparison Voltage Ramp 20 ns A*20 ns Charge Time

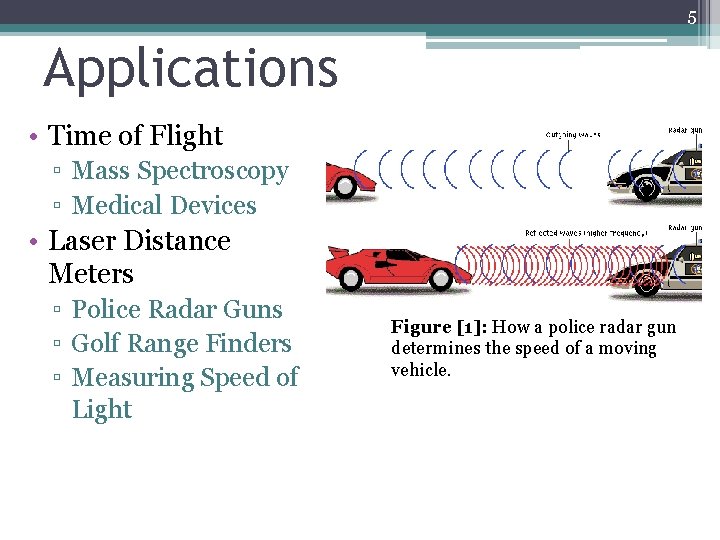

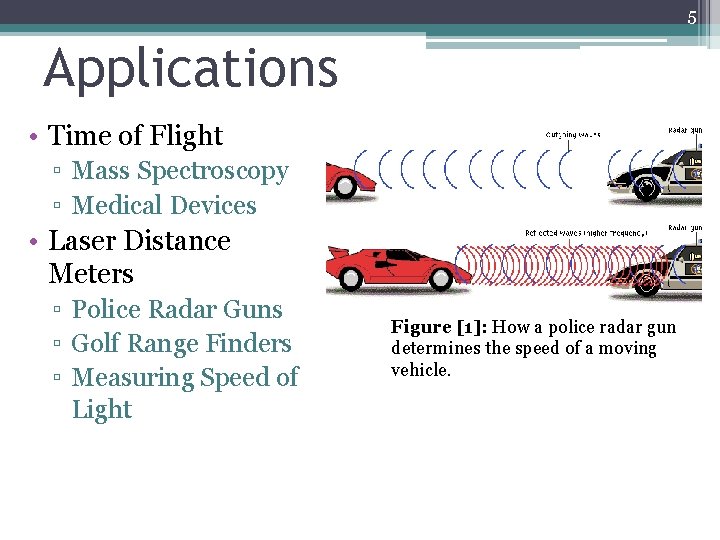

5 Applications • Time of Flight ▫ Mass Spectroscopy ▫ Medical Devices • Laser Distance Meters ▫ Police Radar Guns ▫ Golf Range Finders ▫ Measuring Speed of Light Figure [1]: How a police radar gun determines the speed of a moving vehicle.

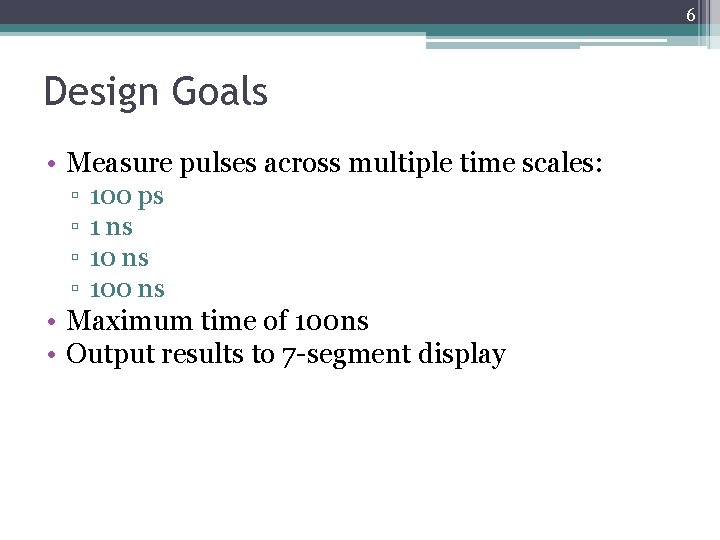

6 Design Goals • Measure pulses across multiple time scales: ▫ ▫ 100 ps 1 ns 100 ns • Maximum time of 100 ns • Output results to 7 -segment display

7 Design Considerations • Timing critical paths ▫ Voltage ramp controls ▫ FPGA Counter Logic • Component delay ▫ MOSFET turn-on/off time ▫ Logic gate

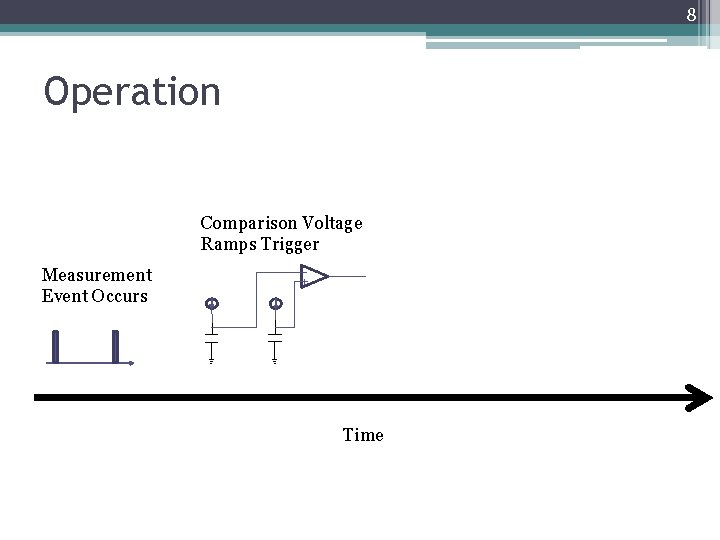

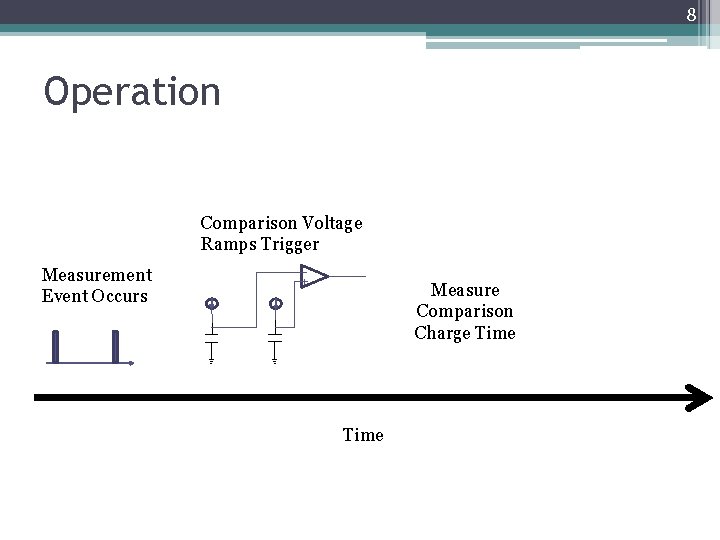

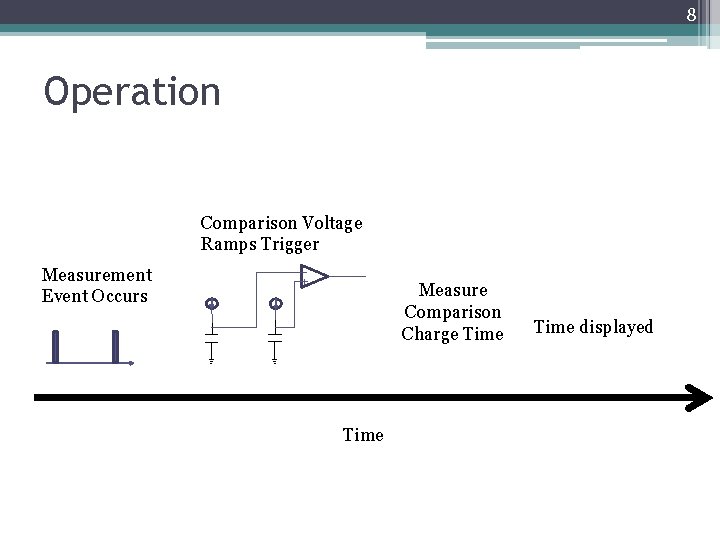

8 Operation Time

8 Operation Measurement Event Occurs Time

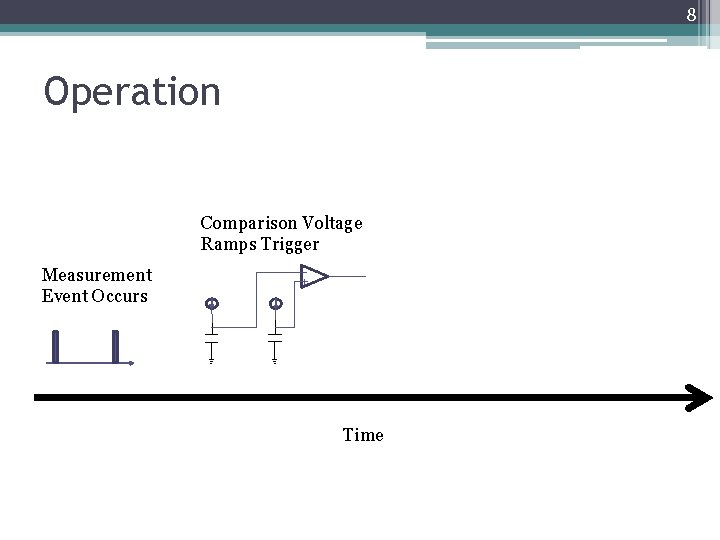

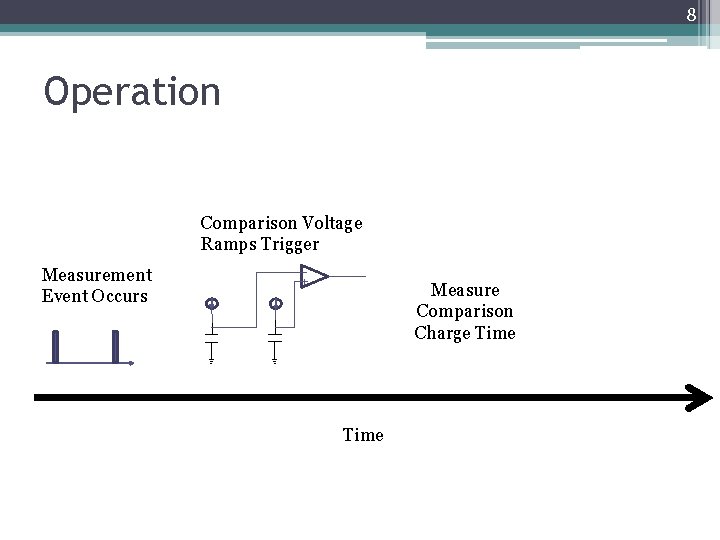

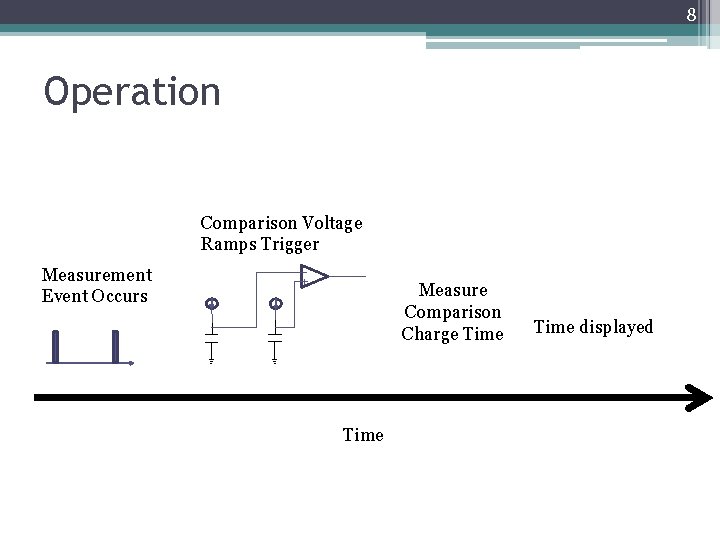

8 Operation Comparison Voltage Ramps Trigger Measurement Event Occurs Time

8 Operation Comparison Voltage Ramps Trigger Measurement Event Occurs Measure Comparison Charge Time

8 Operation Comparison Voltage Ramps Trigger Measurement Event Occurs Measure Comparison Charge Time displayed

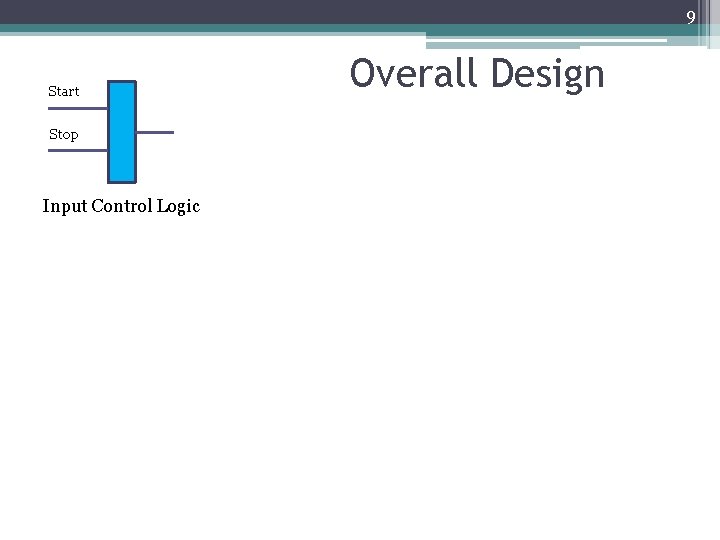

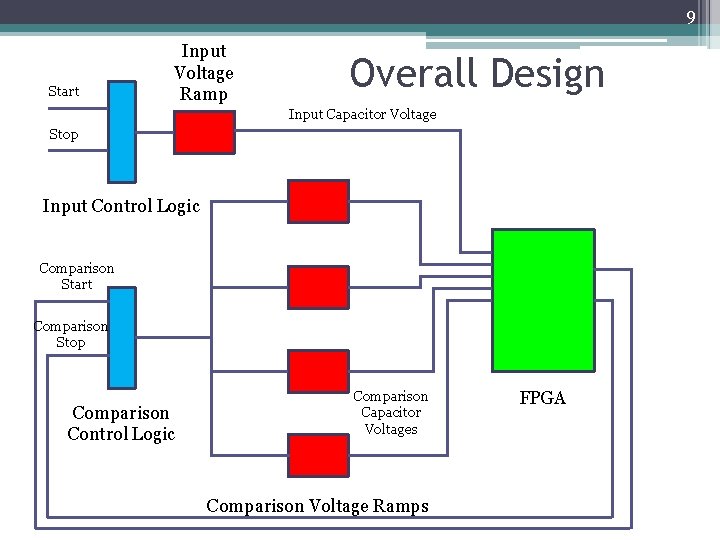

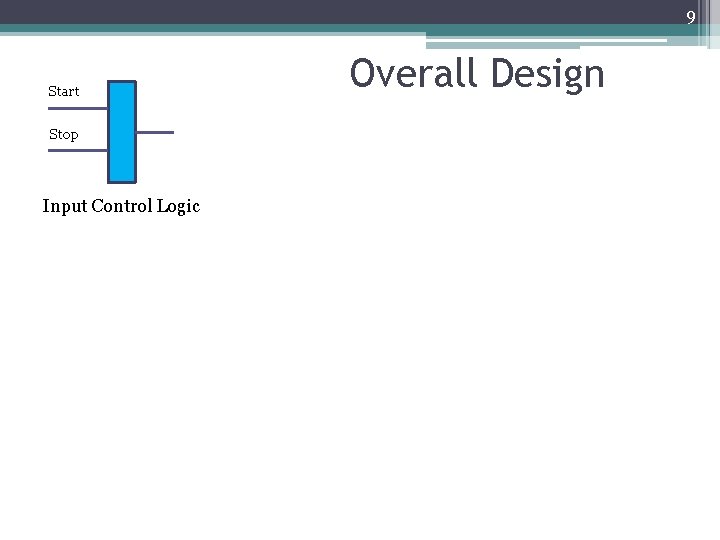

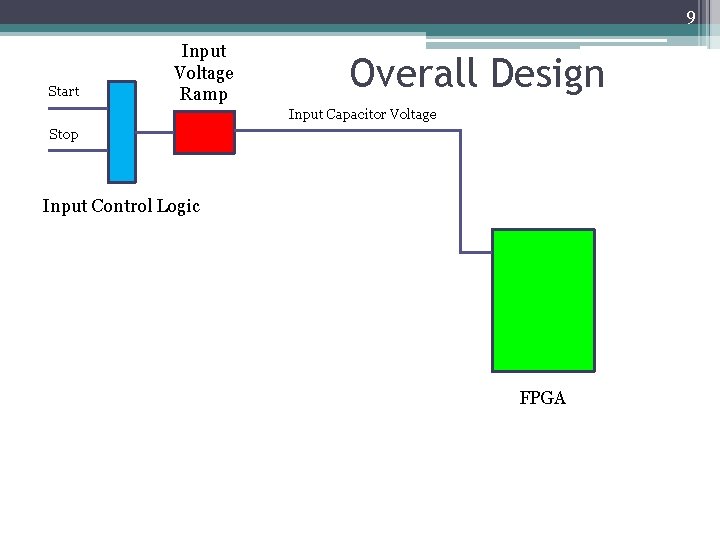

9 Start Stop Input Control Logic Overall Design

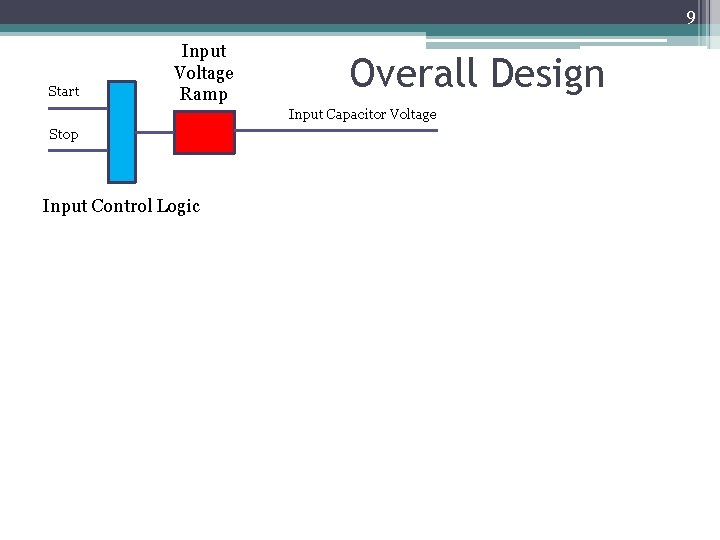

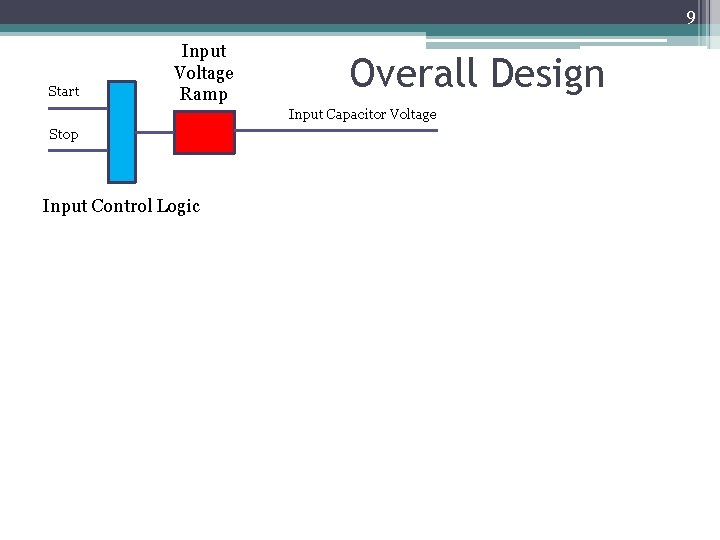

9 Start Input Voltage Ramp Overall Design Input Capacitor Voltage Stop Input Control Logic

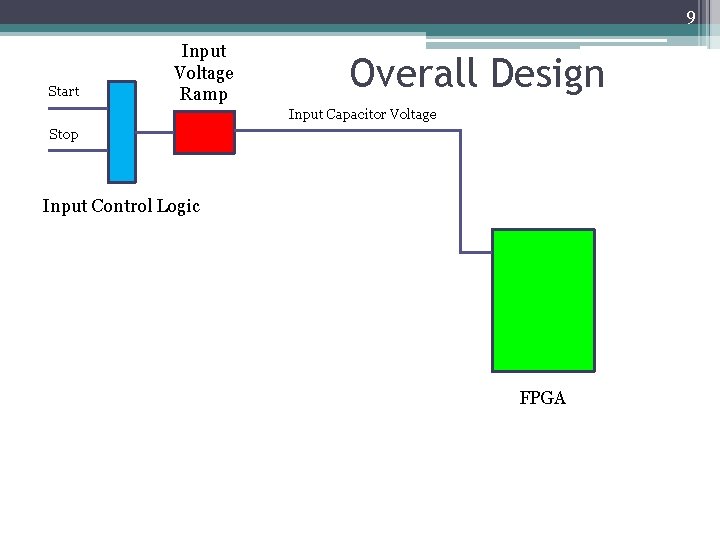

9 Start Input Voltage Ramp Overall Design Input Capacitor Voltage Stop Input Control Logic FPGA

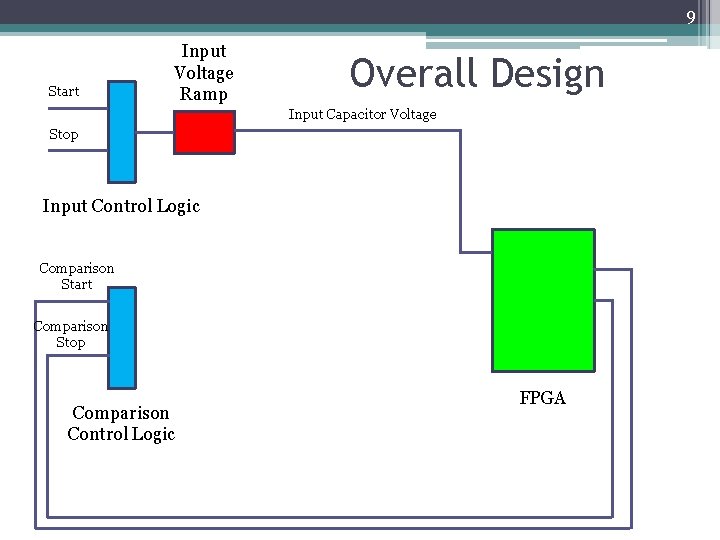

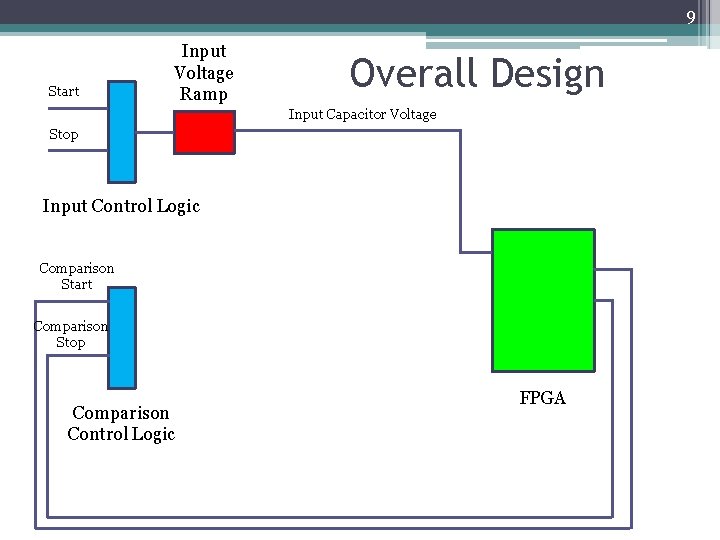

9 Start Input Voltage Ramp Overall Design Input Capacitor Voltage Stop Input Control Logic Comparison Start Comparison Stop Comparison Control Logic FPGA

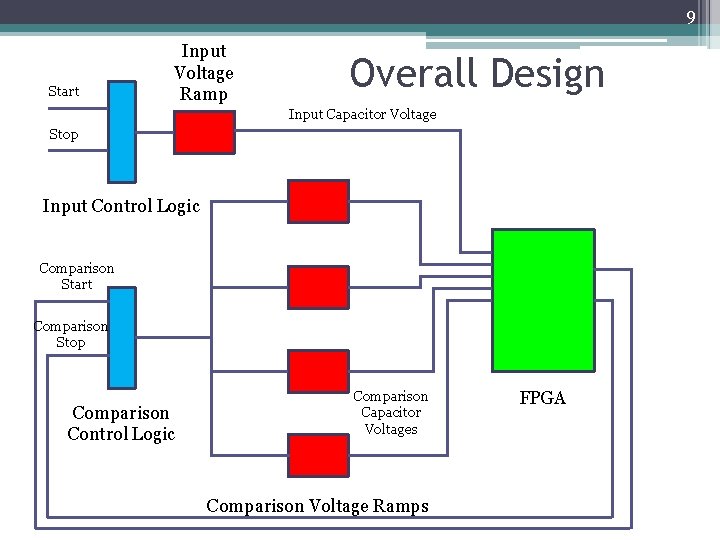

9 Start Input Voltage Ramp Overall Design Input Capacitor Voltage Stop Input Control Logic Comparison Start Comparison Stop Comparison Control Logic Comparison Capacitor Voltages Comparison Voltage Ramps FPGA

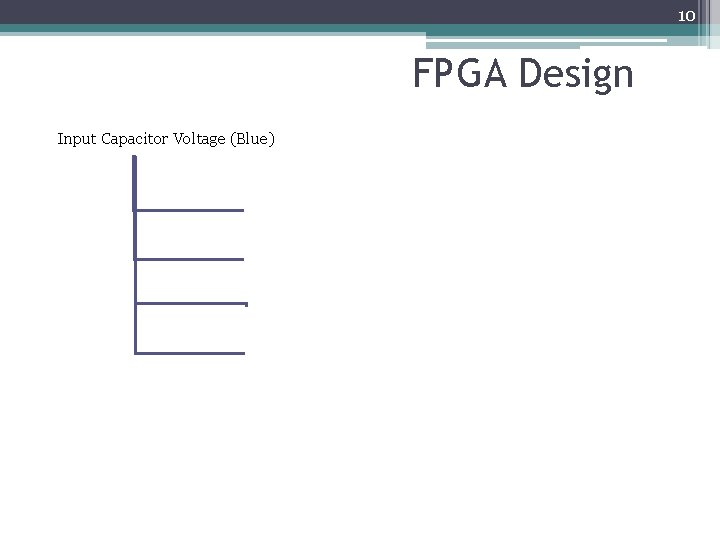

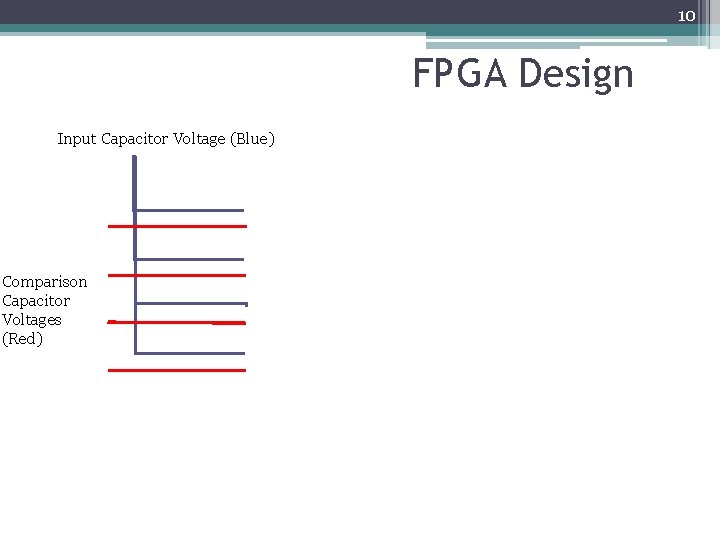

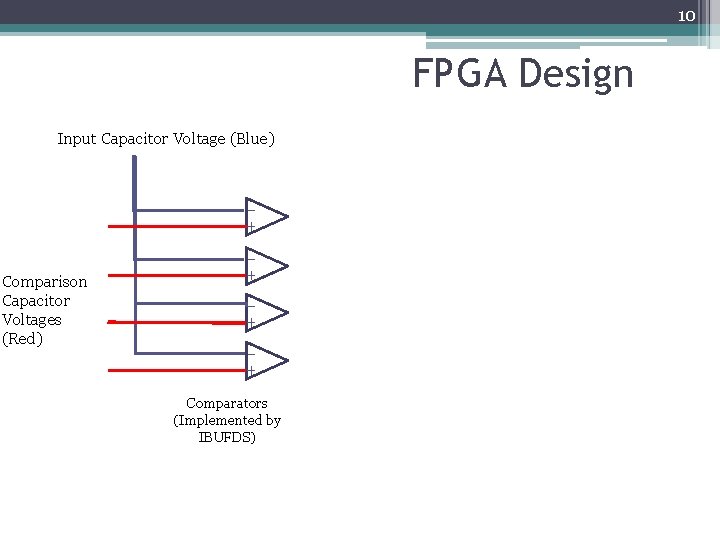

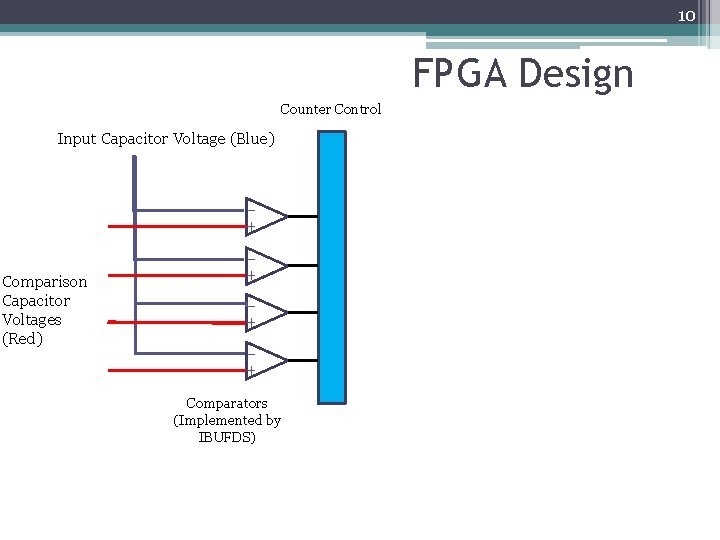

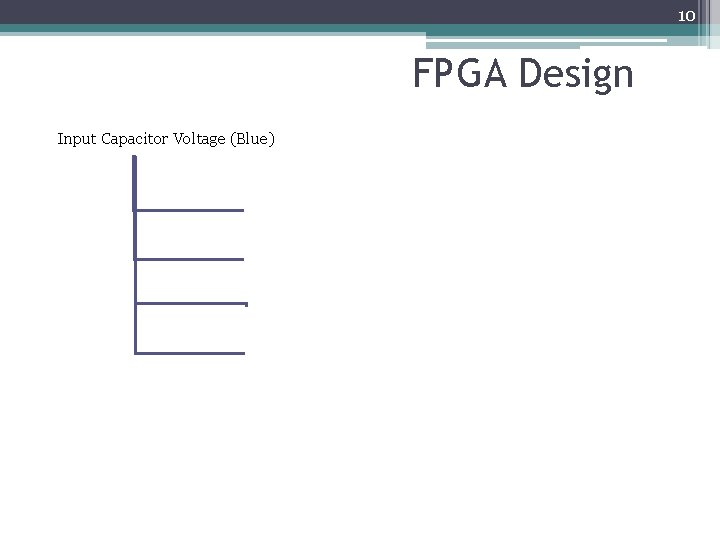

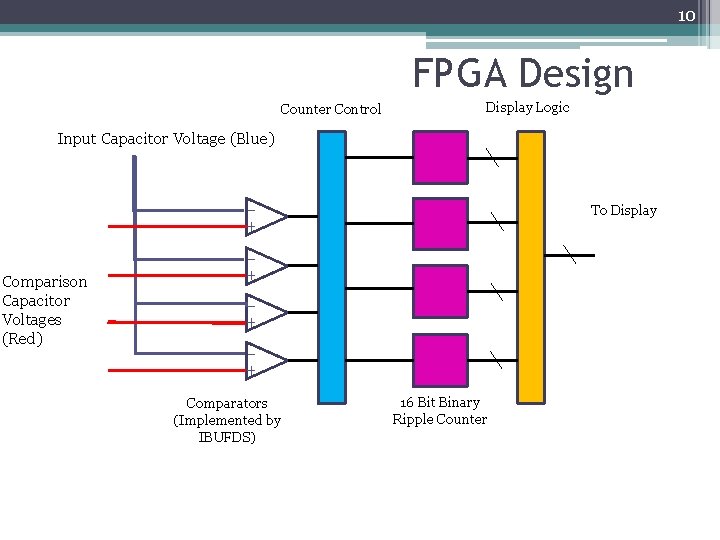

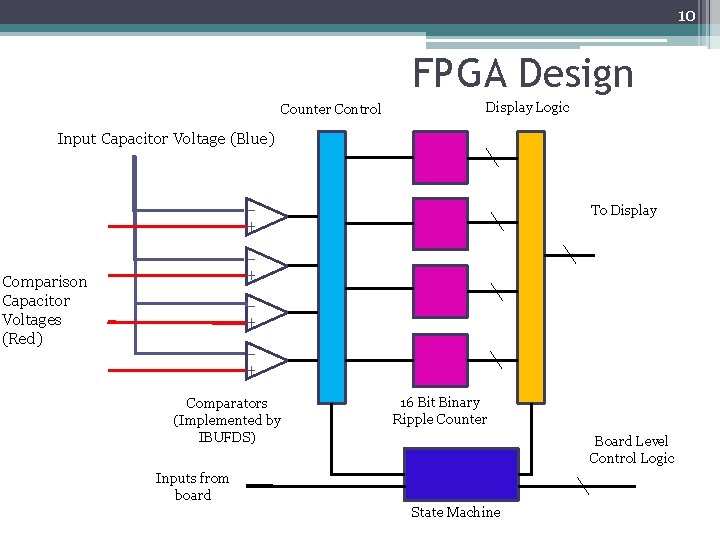

10 FPGA Design Input Capacitor Voltage (Blue)

10 FPGA Design Input Capacitor Voltage (Blue) Comparison Capacitor Voltages (Red)

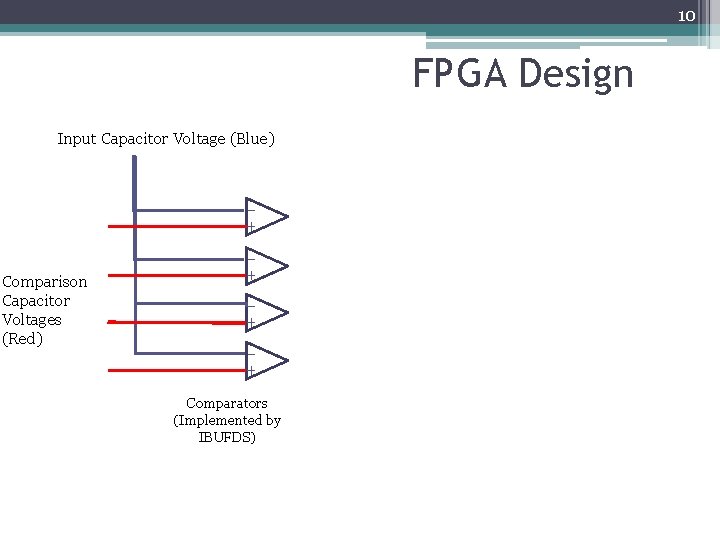

10 FPGA Design Input Capacitor Voltage (Blue) Comparison Capacitor Voltages (Red) Comparators (Implemented by IBUFDS)

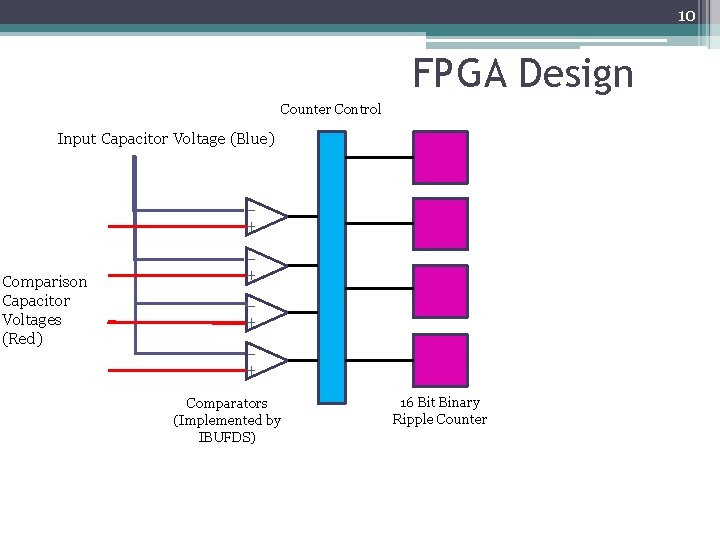

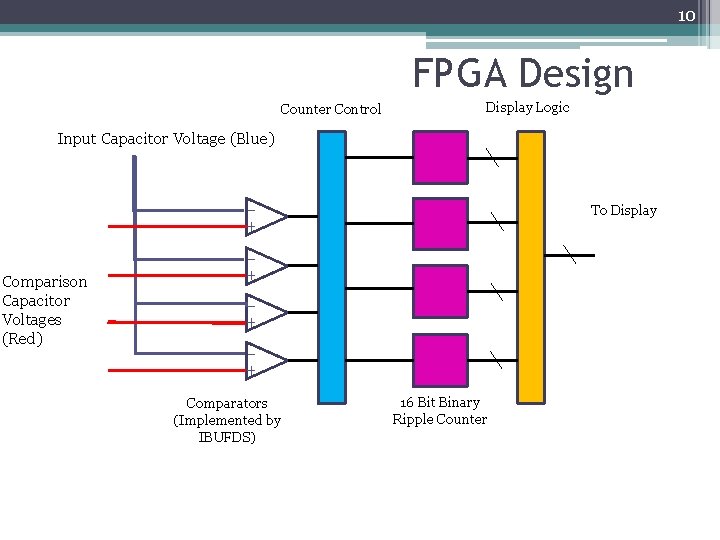

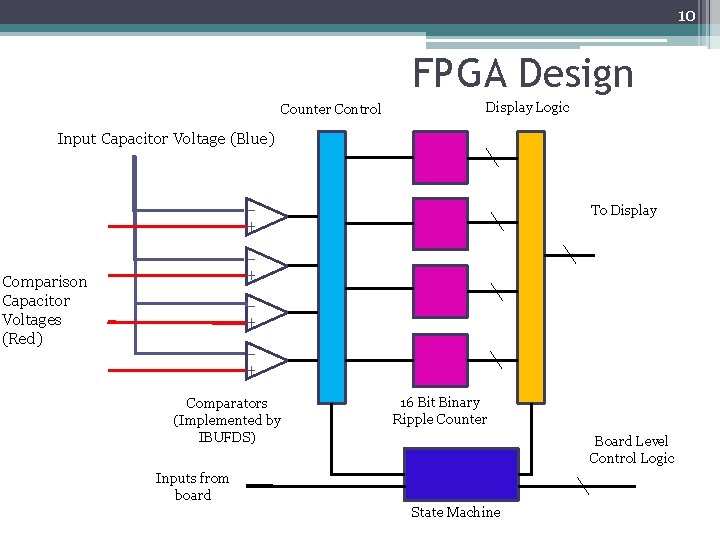

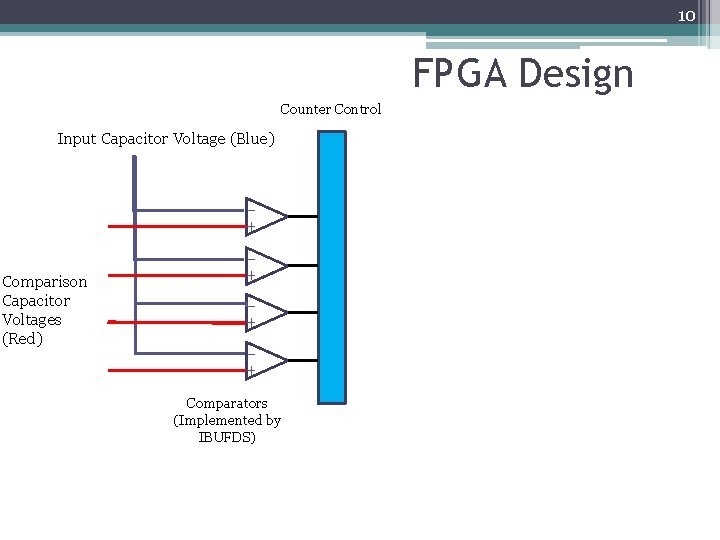

10 FPGA Design Counter Control Input Capacitor Voltage (Blue) Comparison Capacitor Voltages (Red) Comparators (Implemented by IBUFDS)

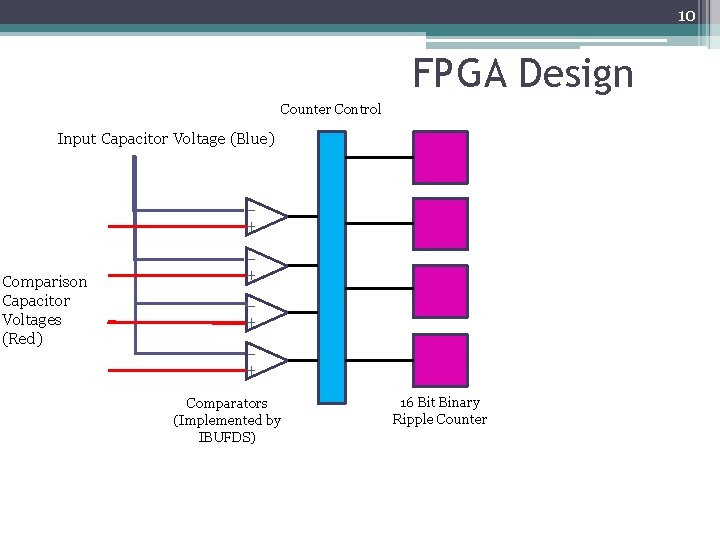

10 FPGA Design Counter Control Input Capacitor Voltage (Blue) Comparison Capacitor Voltages (Red) Comparators (Implemented by IBUFDS) 16 Bit Binary Ripple Counter

10 FPGA Design Counter Control Display Logic Input Capacitor Voltage (Blue) To Display Comparison Capacitor Voltages (Red) Comparators (Implemented by IBUFDS) 16 Bit Binary Ripple Counter

10 FPGA Design Counter Control Display Logic Input Capacitor Voltage (Blue) To Display Comparison Capacitor Voltages (Red) Comparators (Implemented by IBUFDS) 16 Bit Binary Ripple Counter Board Level Control Logic Inputs from board State Machine

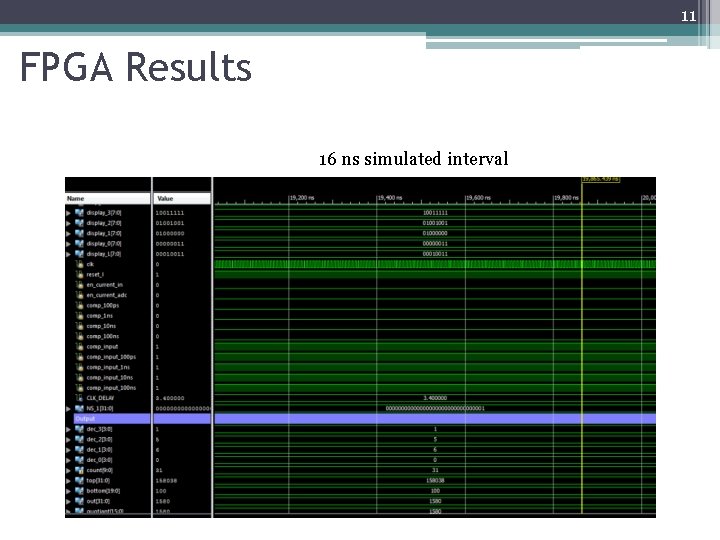

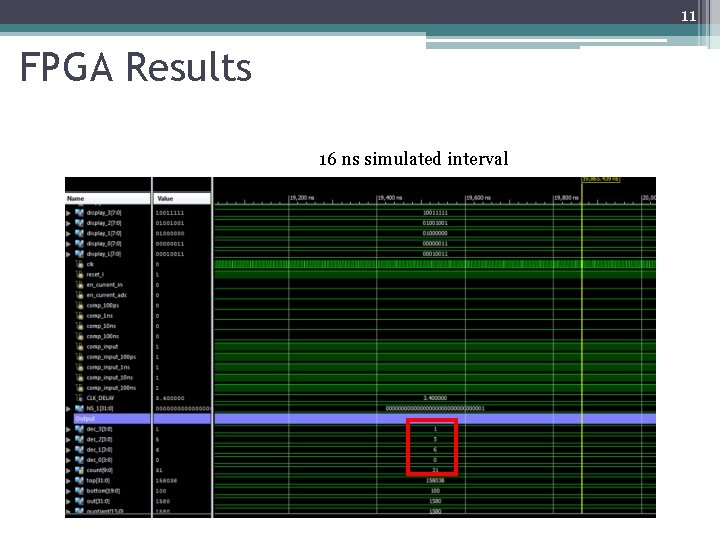

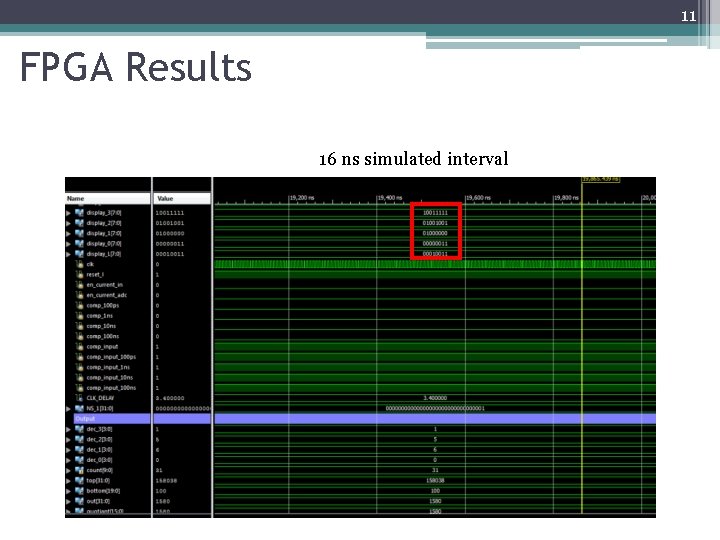

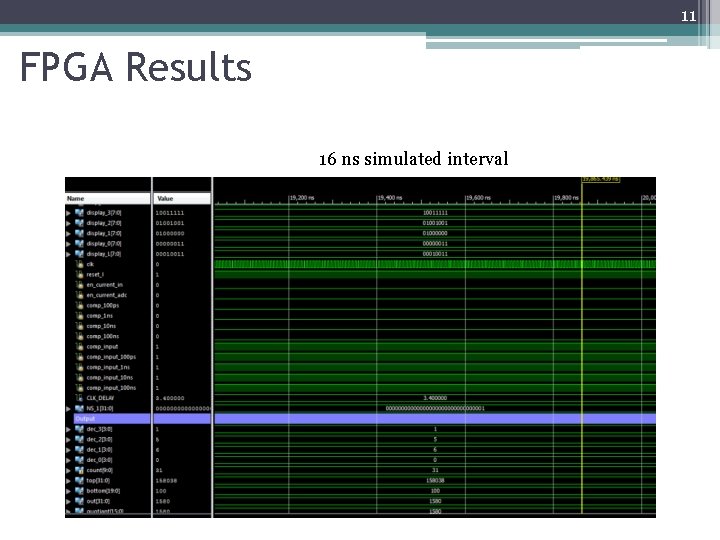

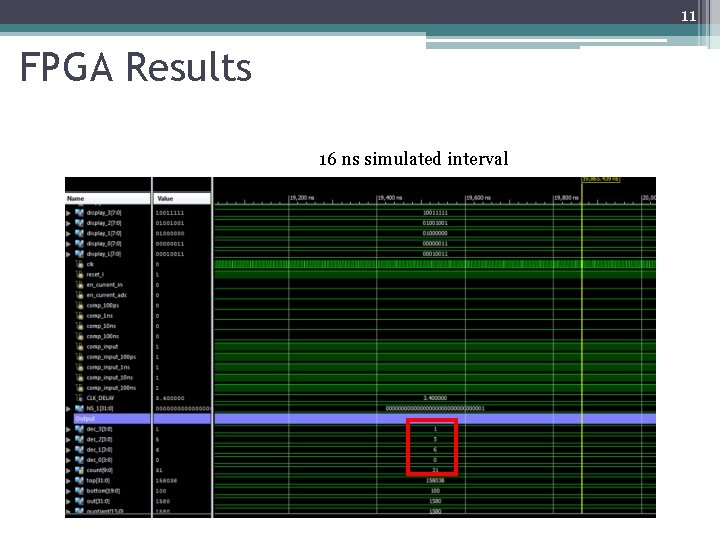

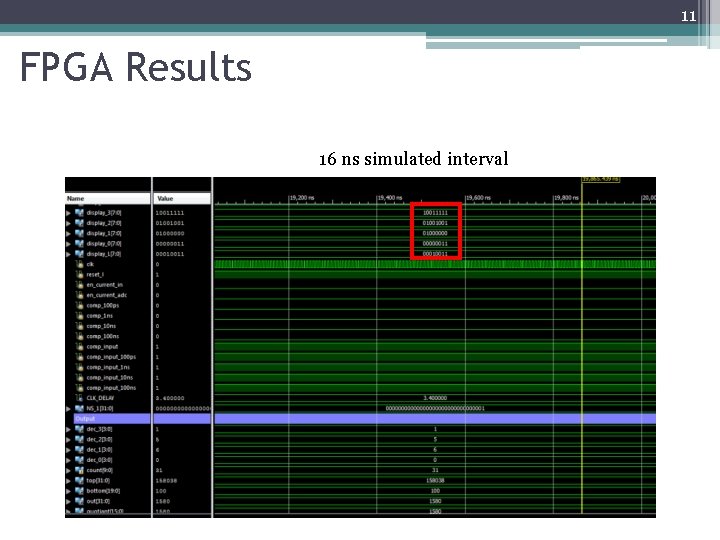

11 FPGA Results 16 ns simulated interval

11 FPGA Results 16 ns simulated interval

11 FPGA Results 16 ns simulated interval

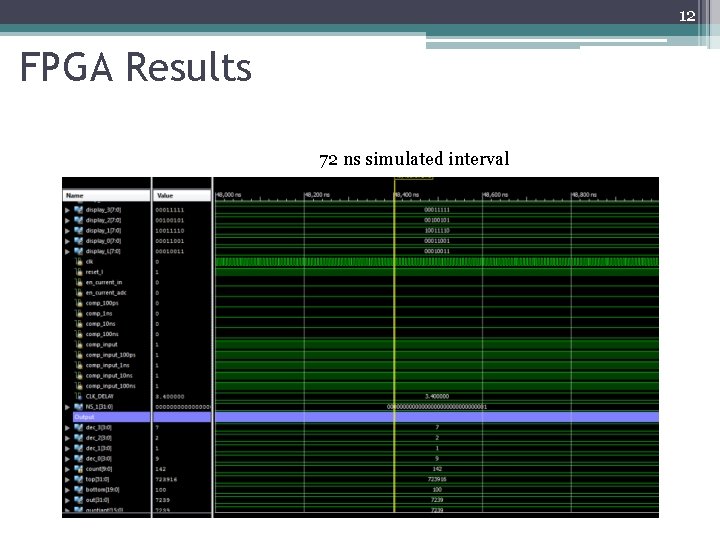

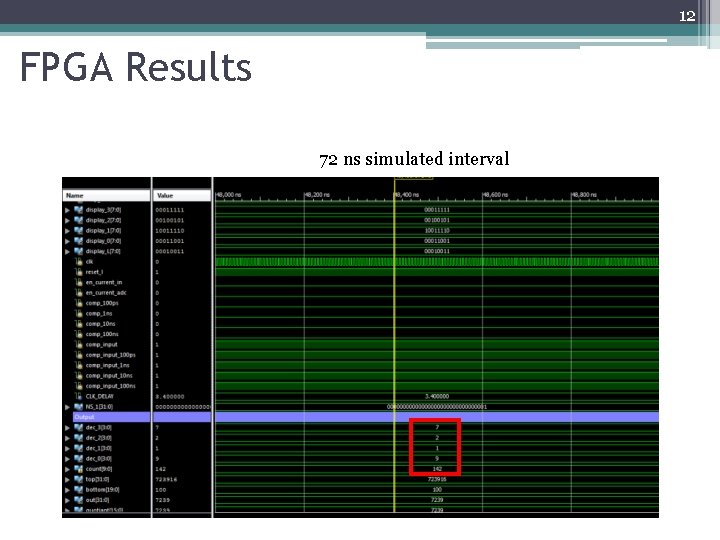

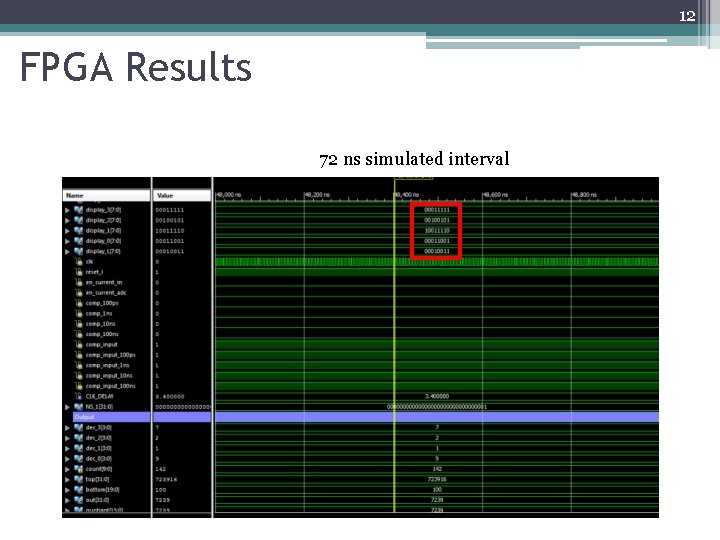

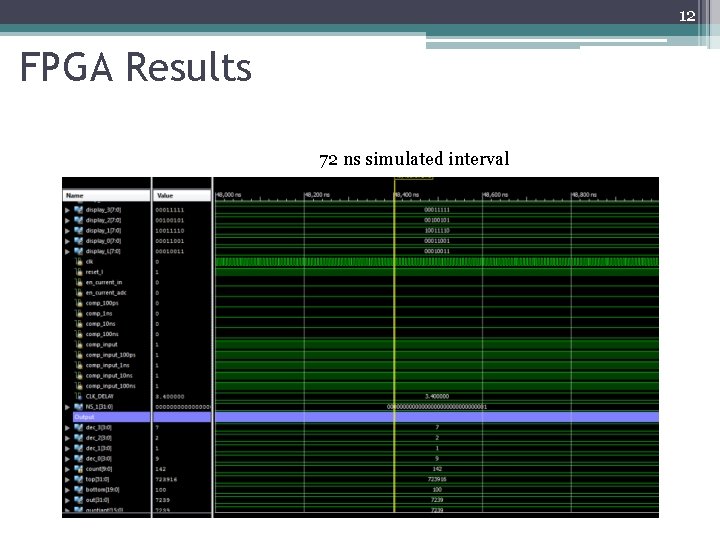

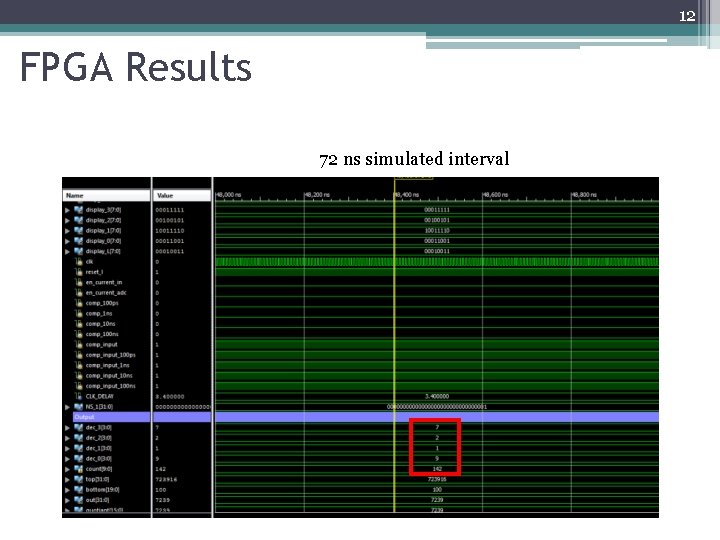

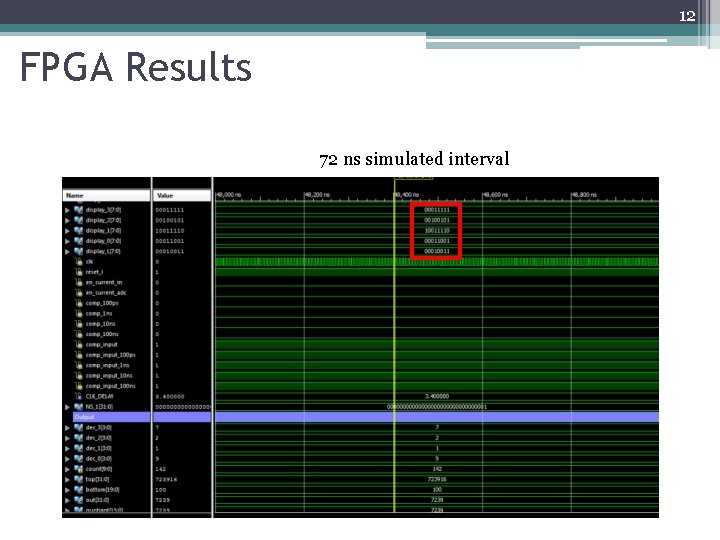

12 FPGA Results 72 ns simulated interval

12 FPGA Results 72 ns simulated interval

12 FPGA Results 72 ns simulated interval

13 Complications • Unable to order a PCB • Circuit implemented on SMT breadboard ▫ Added Capacitance and Delays ▫ Possible Hardware issues • Had to reorder some parts due to spacelimitations ▫ Original parts too small for SMT breadboard

14 Tasks Completed • FPGA Core Built and Simulated ▫ Synthesizes ▫ Timing requirements met ▫ Successfully measures and displays simulated times • SMT Breadboard Complete ▫ All parts placed and wired ▫ Short checks complete • Begin Testing

15 Tasks Remaining • Complete Integration ▫ Successfully measure event ▫ Compare observed and expected results

16 Acknowledgments Professor Varner for design review and implementation ideas Dr. Cooney for all the help and support he provided us in the last minute rush to completion IDL Staff for assistance with implementation

17 Questions?