Low Area and Low Power TimetoDigital Converter for

- Slides: 29

Low Area and Low Power Time-to-Digital Converter for Pixelated Detector with 6. 9 ps RMS Timing Jitter Nicolas Roy Frédéric Nolet, Frédérik Dubois, Réjean Fontaine, Jean-François Pratte FEE 2018 May 21 st

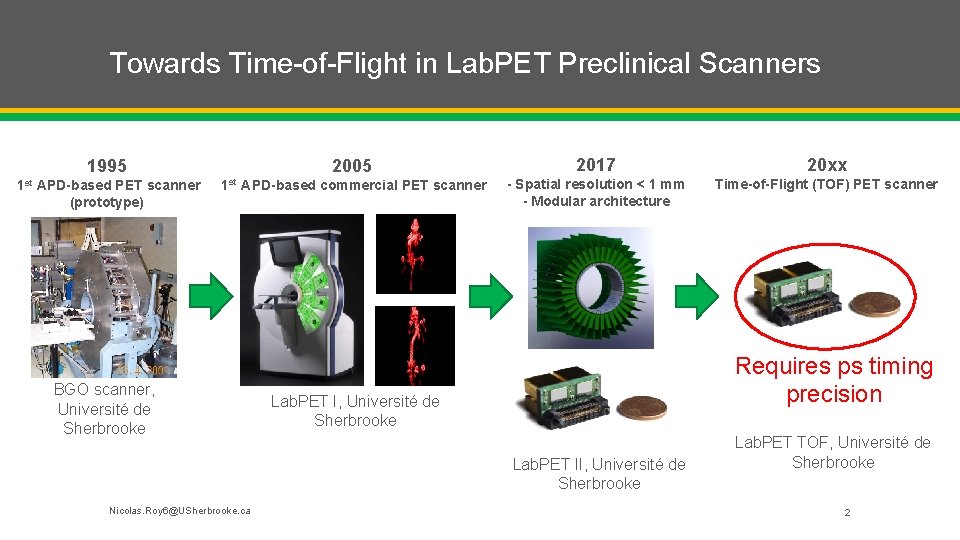

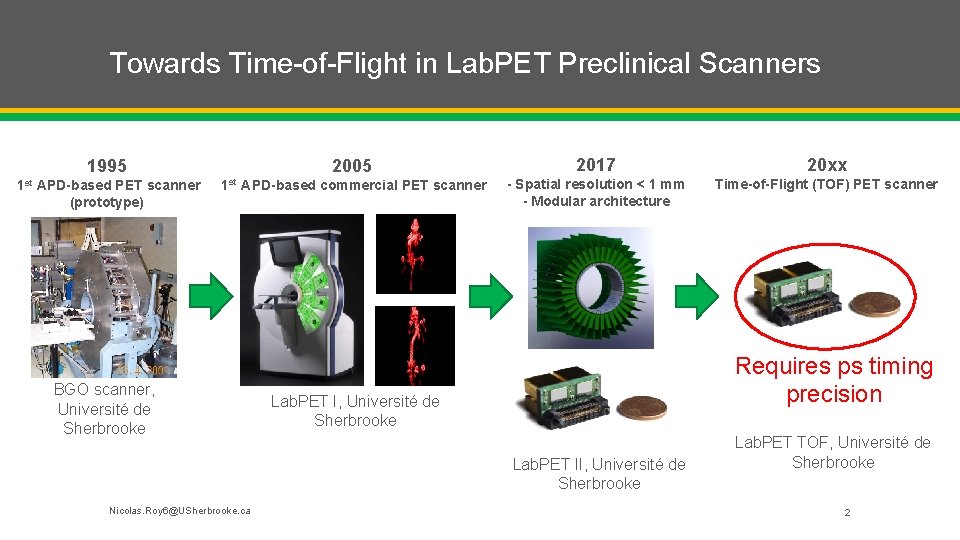

Towards Time-of-Flight in Lab. PET Preclinical Scanners 1995 2005 2017 20 xx 1 st APD-based PET scanner (prototype) 1 st APD-based commercial PET scanner - Spatial resolution < 1 mm - Modular architecture Time-of-Flight (TOF) PET scanner BGO scanner, Université de Sherbrooke Requires ps timing precision Lab. PET I, Université de Sherbrooke Lab. PET II, Université de Sherbrooke Nicolas. Roy 6@USherbrooke. ca Lab. PET TOF, Université de Sherbrooke 2

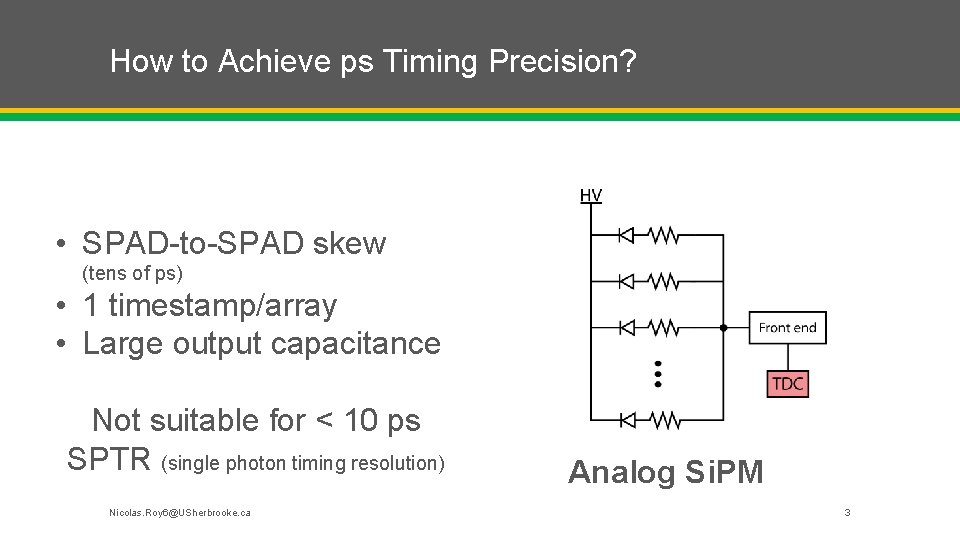

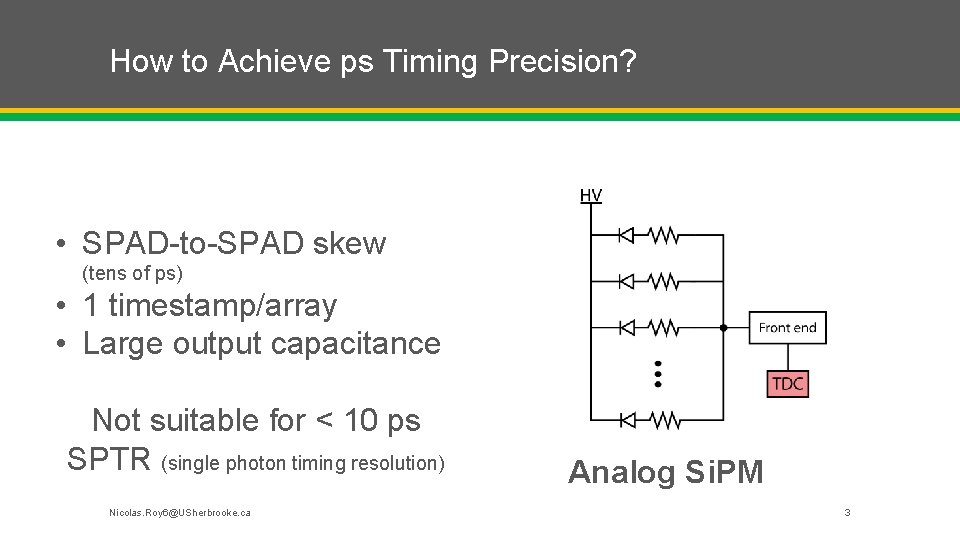

How to Achieve ps Timing Precision? • SPAD-to-SPAD skew (tens of ps) • 1 timestamp/array • Large output capacitance Not suitable for < 10 ps SPTR (single photon timing resolution) Nicolas. Roy 6@USherbrooke. ca Analog Si. PM 3

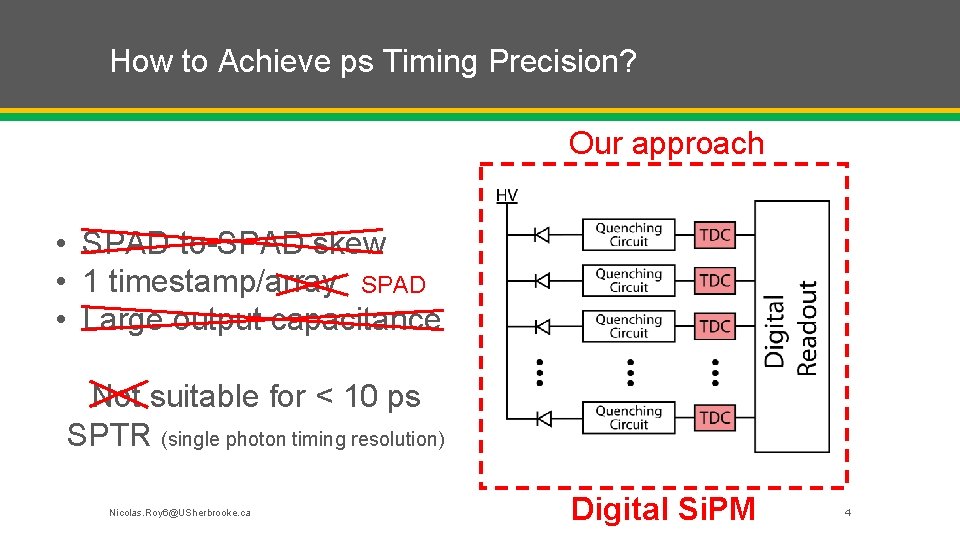

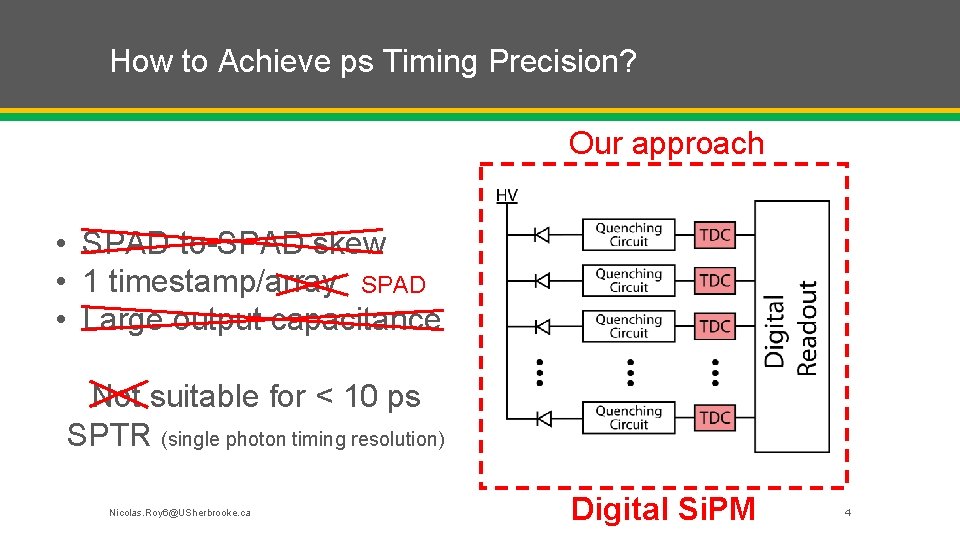

How to Achieve ps Timing Precision? Our approach • SPAD-to-SPAD skew • 1 timestamp/array SPAD • Large output capacitance Not suitable for < 10 ps SPTR (single photon timing resolution) Nicolas. Roy 6@USherbrooke. ca Digital Si. PM 4

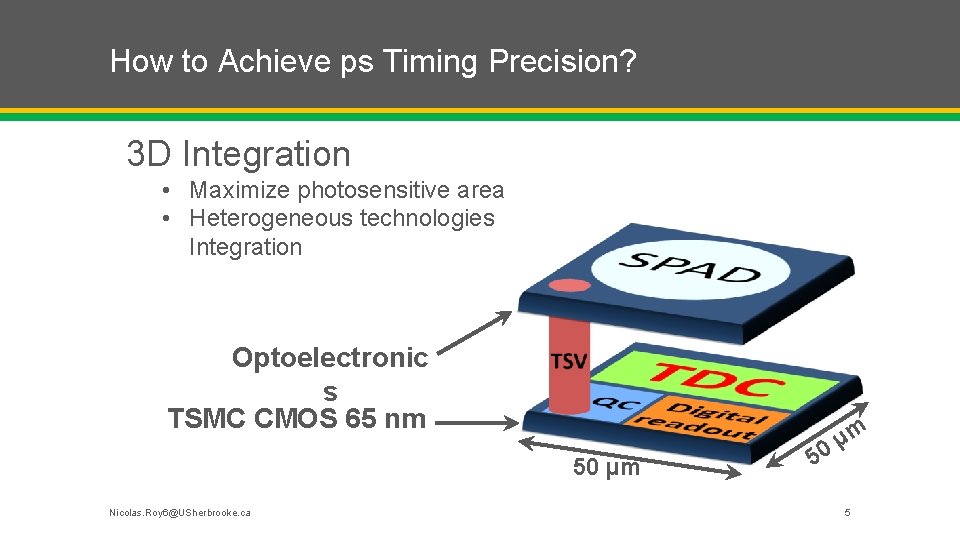

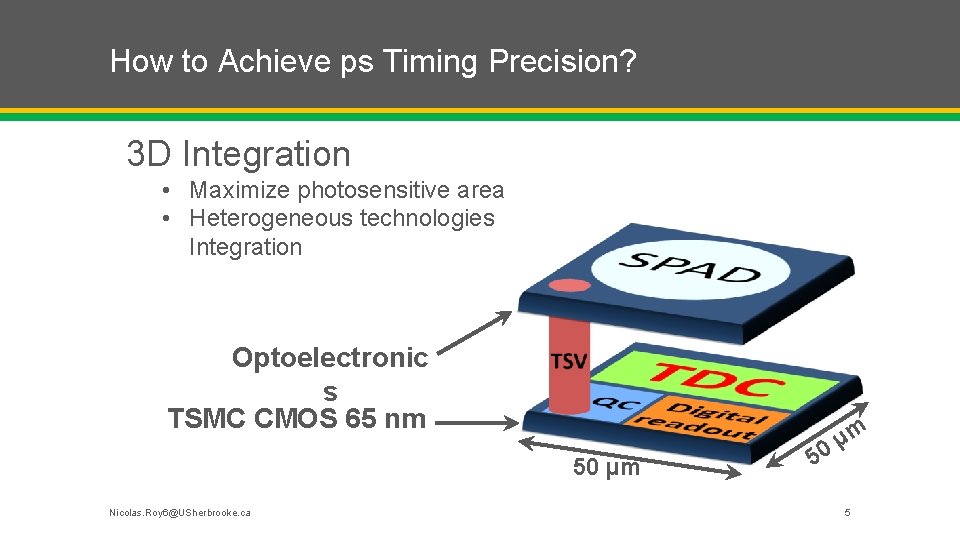

How to Achieve ps Timing Precision? 3 D Integration • Maximize photosensitive area • Heterogeneous technologies Integration Optoelectronic s TSMC CMOS 65 nm 50 µm Nicolas. Roy 6@USherbrooke. ca m µ 0 5 5

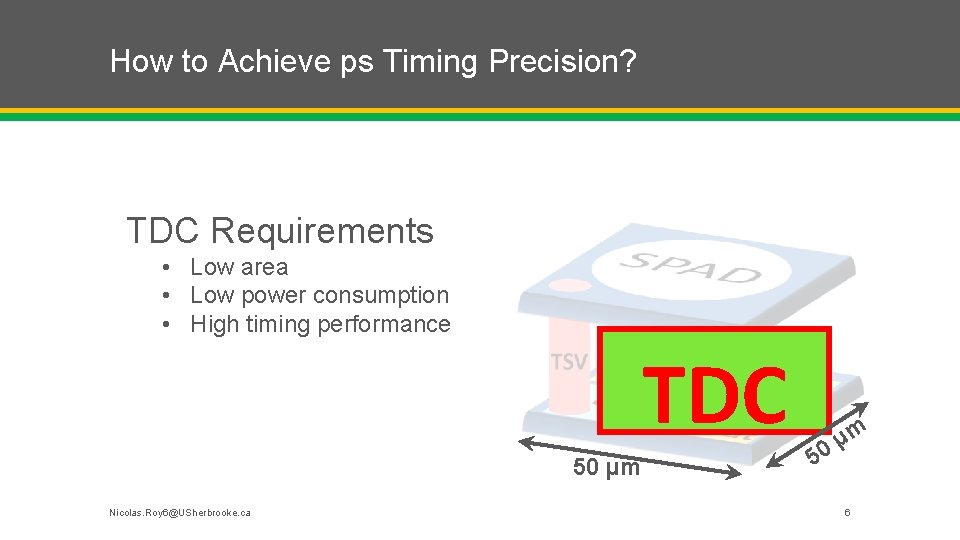

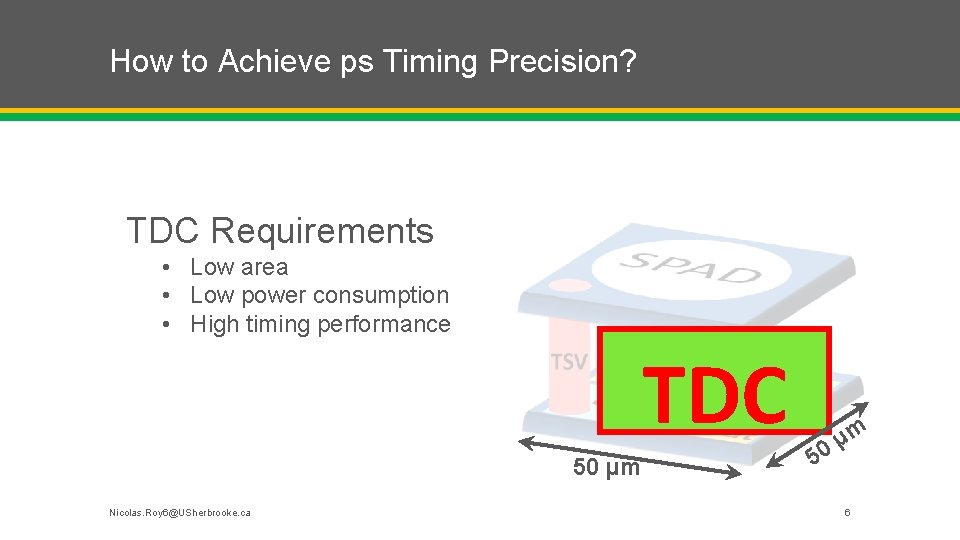

How to Achieve ps Timing Precision? TDC Requirements • Low area • Low power consumption • High timing performance TDC 50 µm Nicolas. Roy 6@USherbrooke. ca m µ 0 5 6

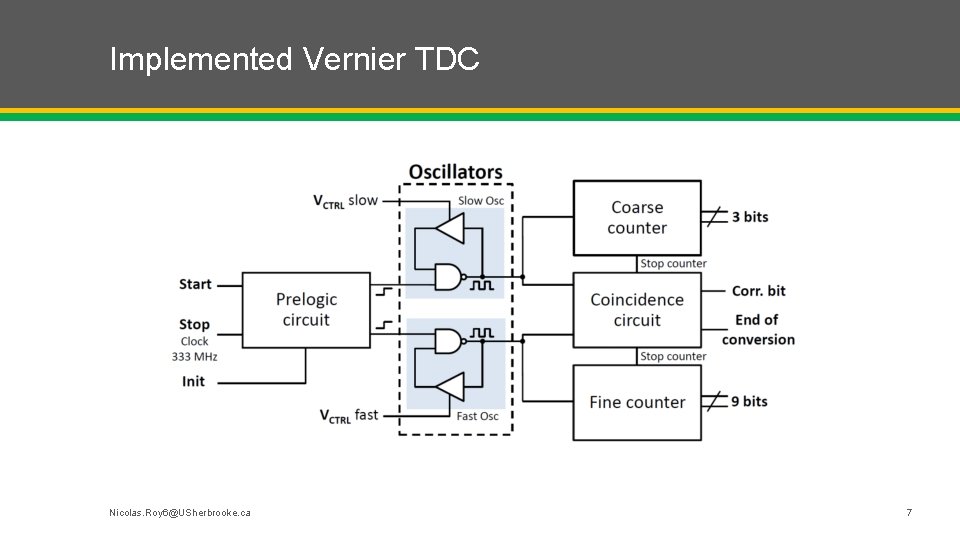

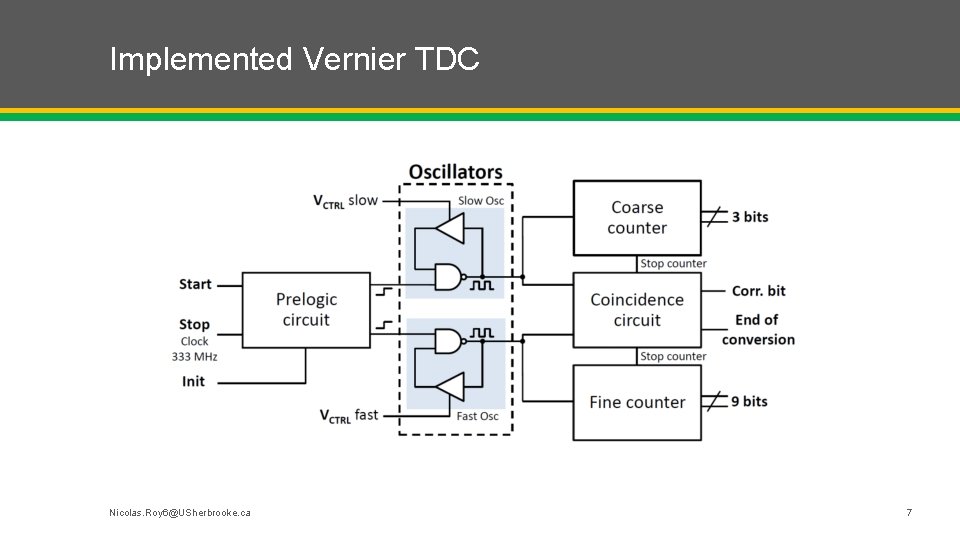

Implemented Vernier TDC Nicolas. Roy 6@USherbrooke. ca 7

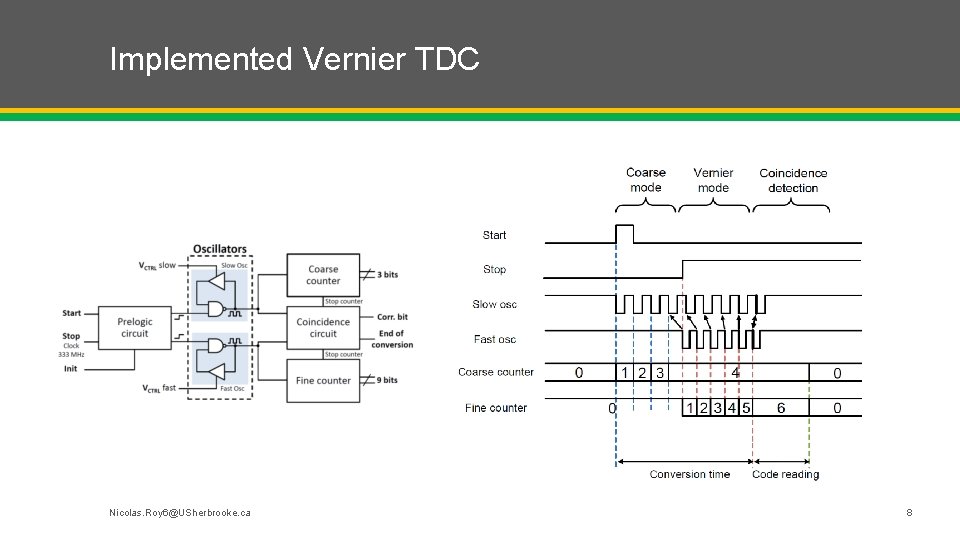

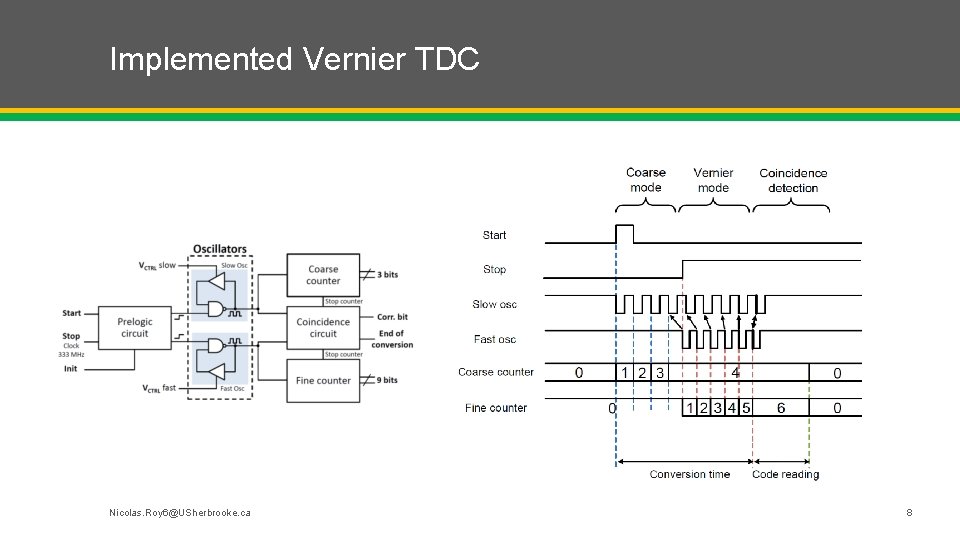

Implemented Vernier TDC Nicolas. Roy 6@USherbrooke. ca 8

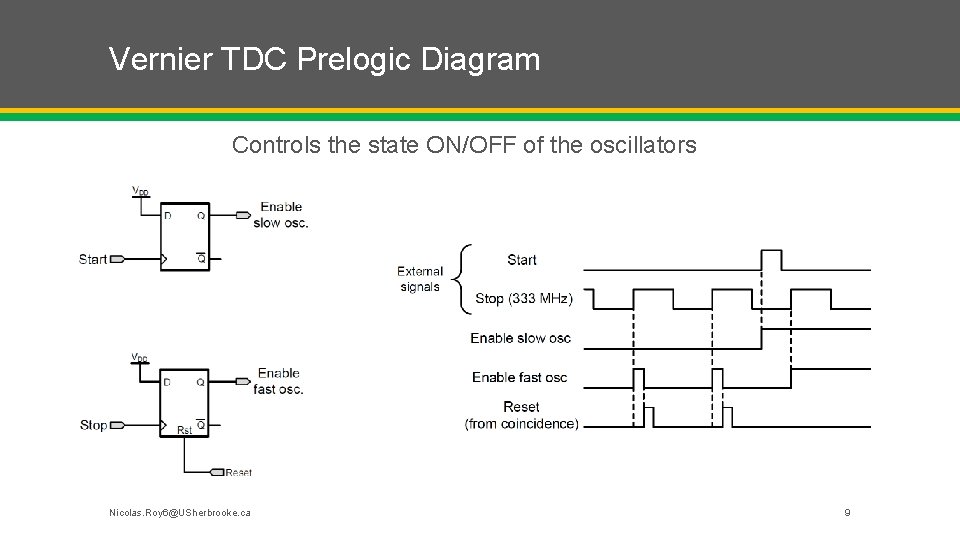

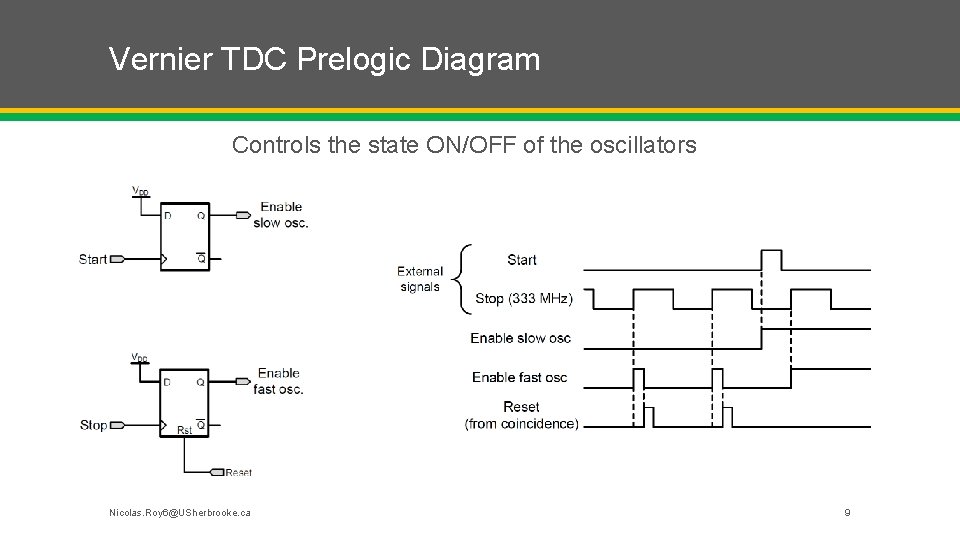

Vernier TDC Prelogic Diagram Controls the state ON/OFF of the oscillators Nicolas. Roy 6@USherbrooke. ca 9

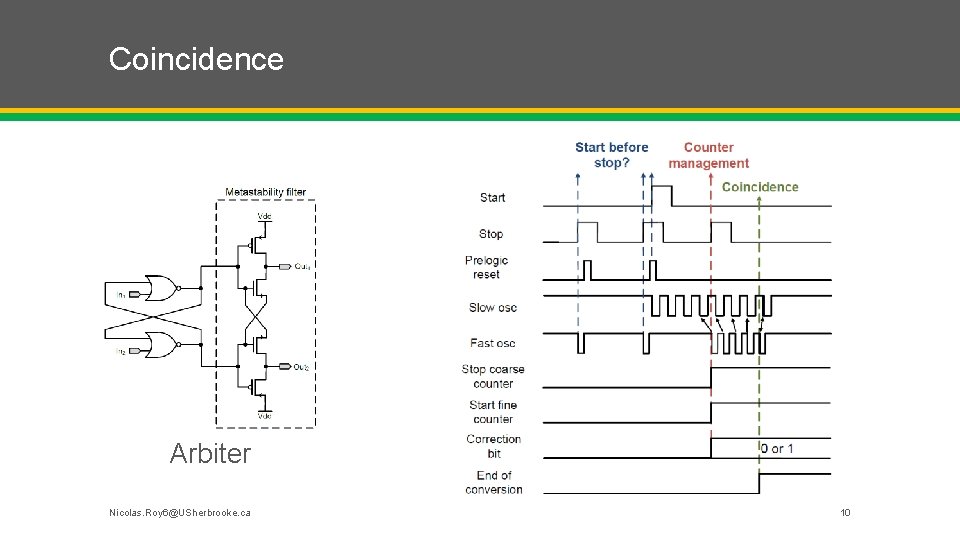

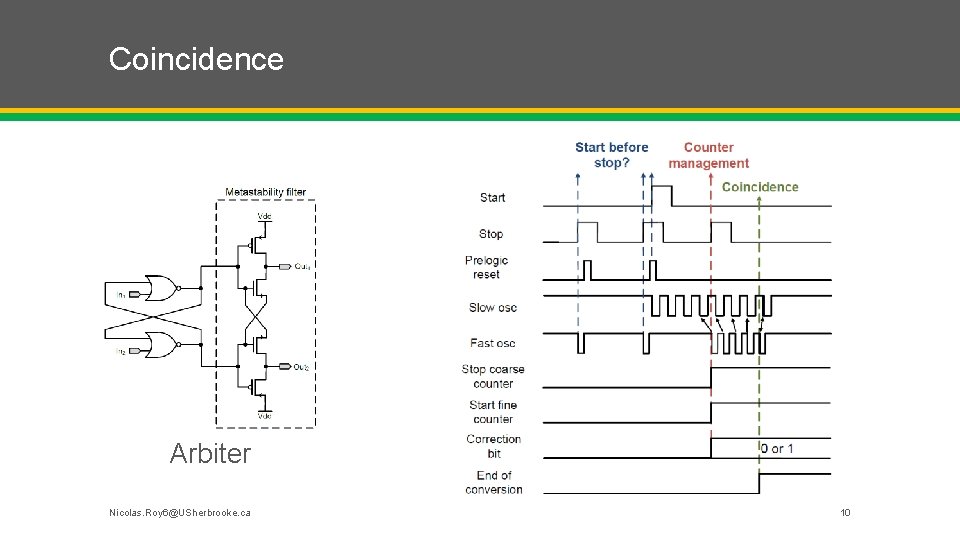

Coincidence Arbiter Nicolas. Roy 6@USherbrooke. ca 10

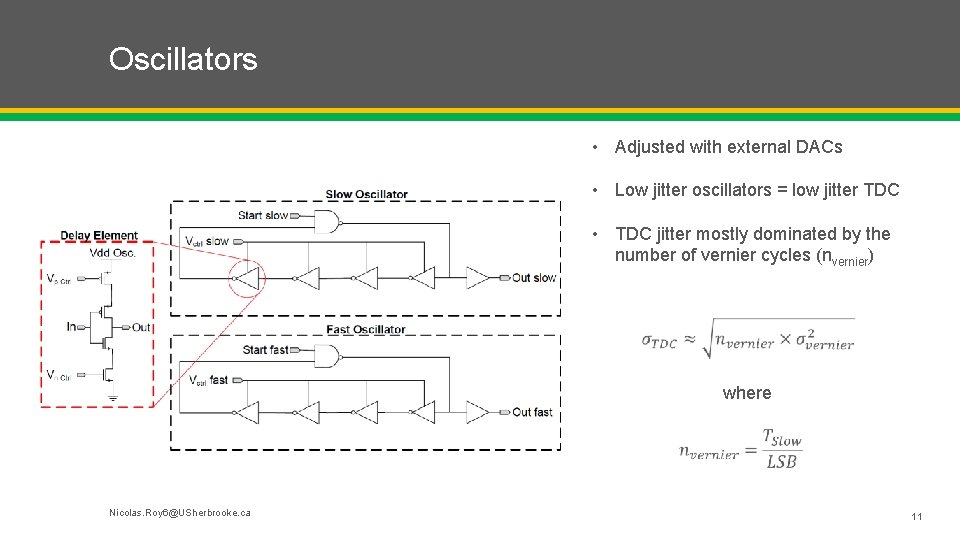

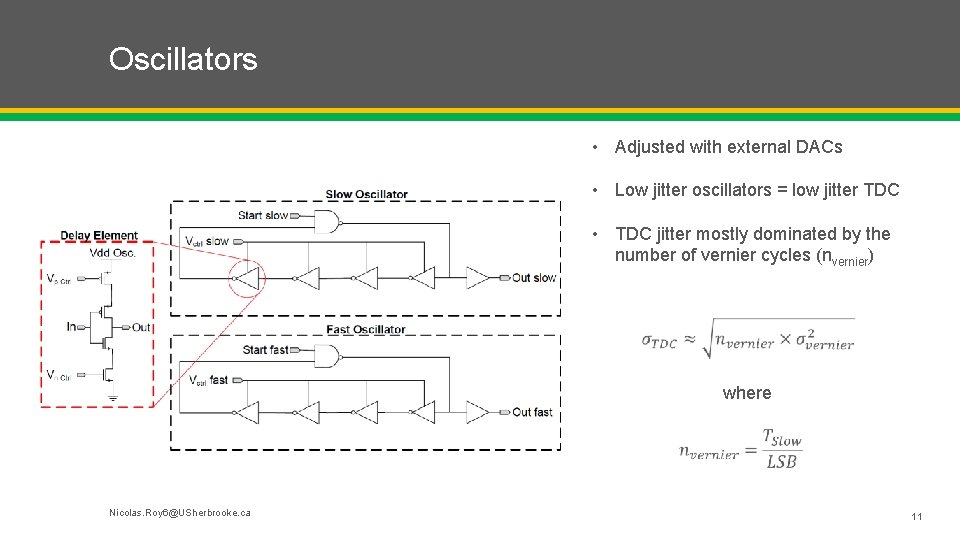

Oscillators • Adjusted with external DACs • Low jitter oscillators = low jitter TDC • TDC jitter mostly dominated by the number of vernier cycles (nvernier) where Nicolas. Roy 6@USherbrooke. ca 11

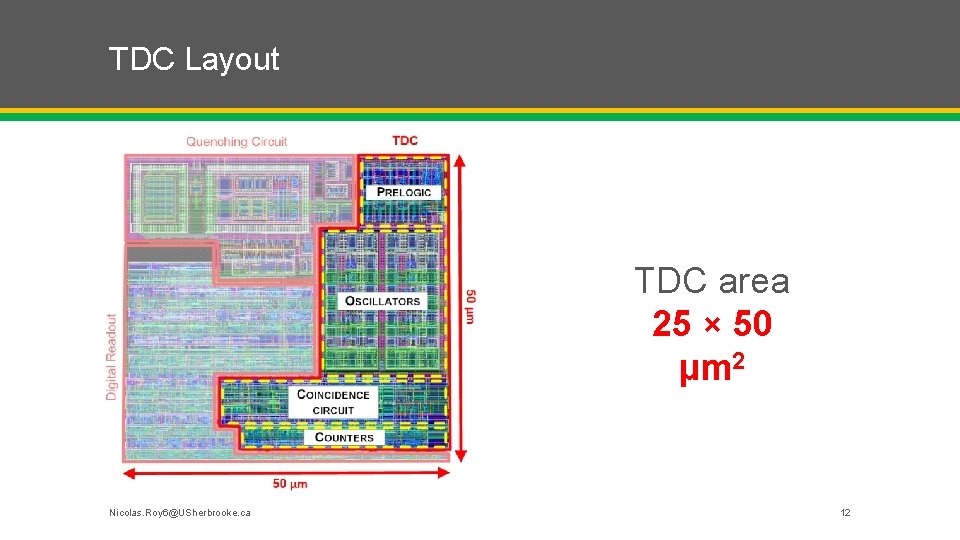

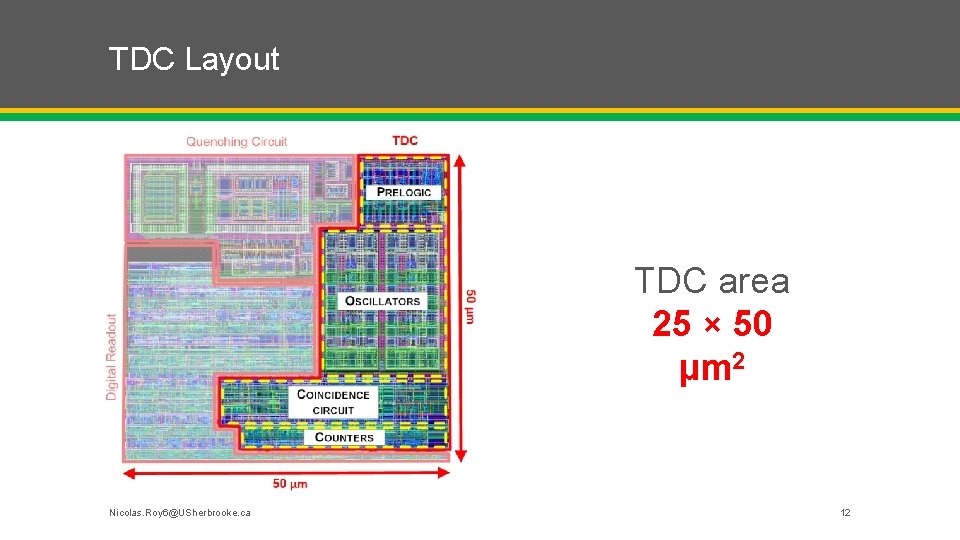

TDC Layout TDC area 25 × 50 µm 2 Nicolas. Roy 6@USherbrooke. ca 12

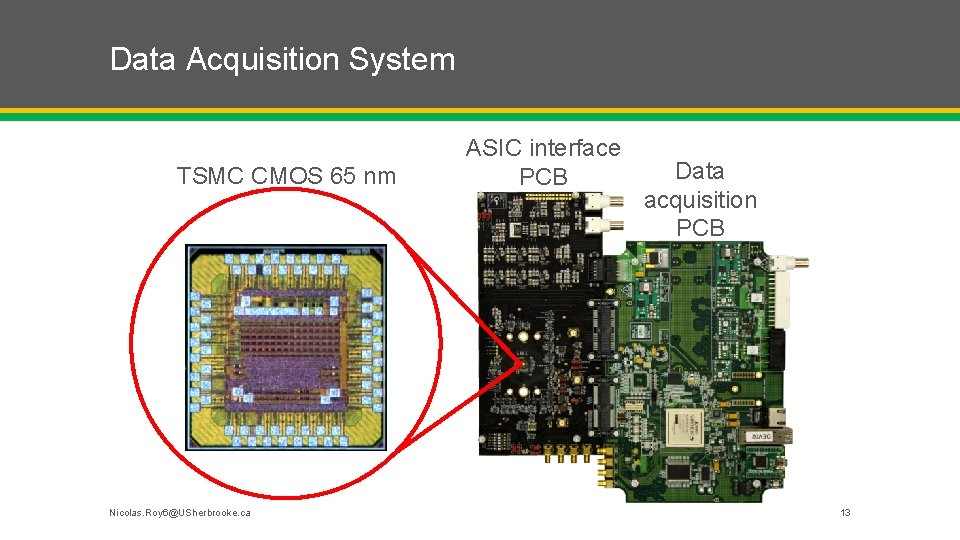

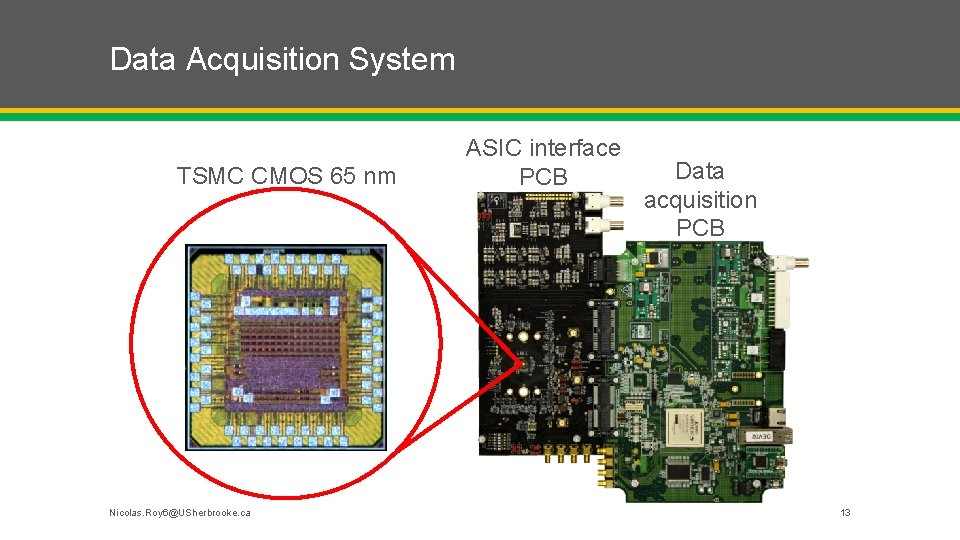

Data Acquisition System TSMC CMOS 65 nm Nicolas. Roy 6@USherbrooke. ca ASIC interface PCB Data acquisition PCB 13

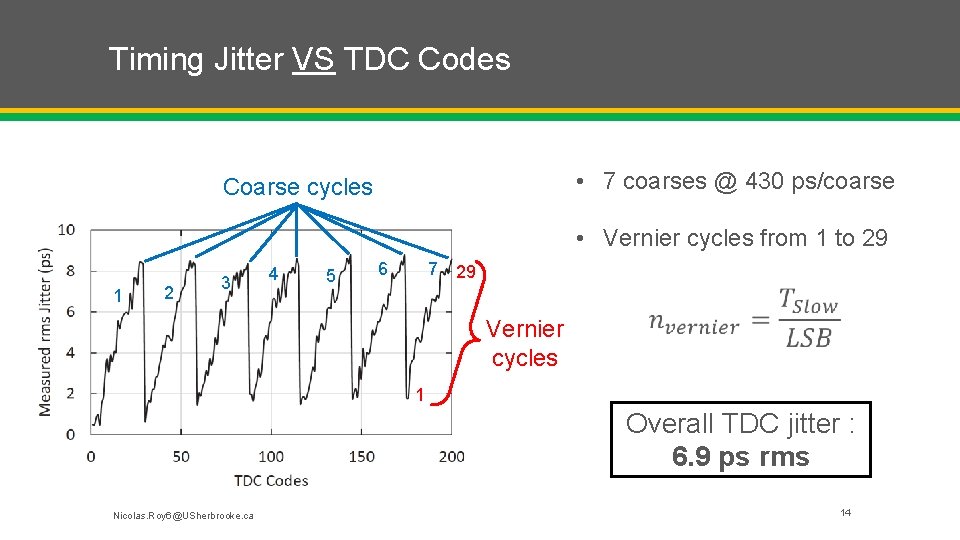

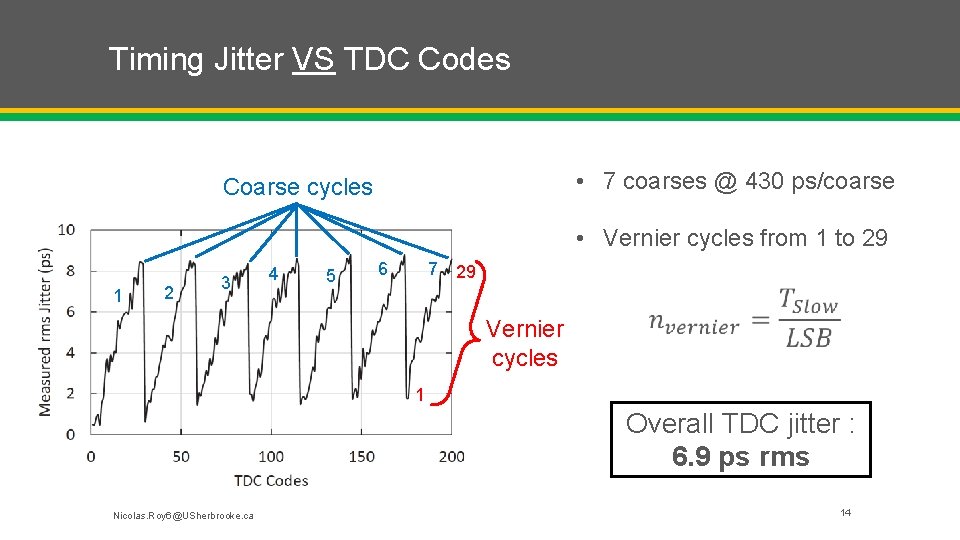

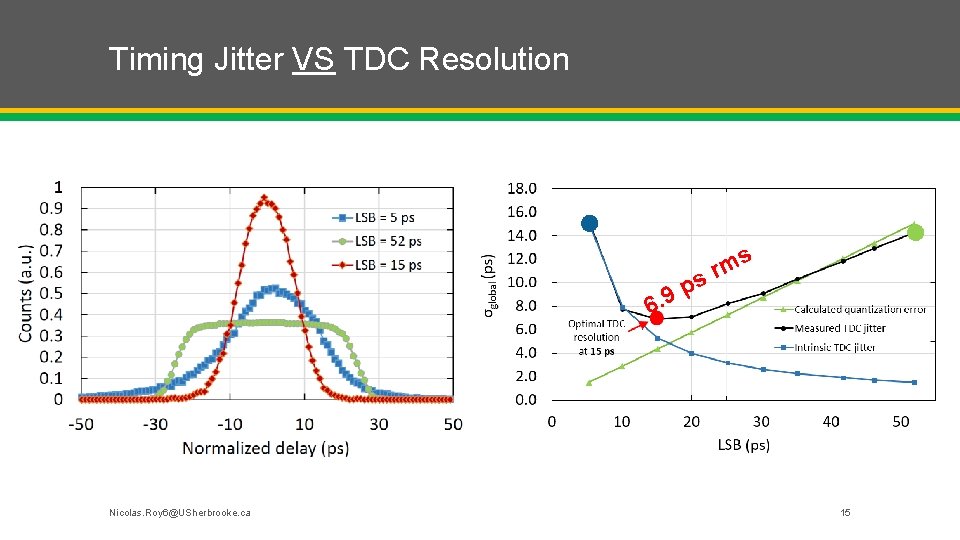

Timing Jitter VS TDC Codes • 7 coarses @ 430 ps/coarse Coarse cycles • Vernier cycles from 1 to 29 1 2 3 4 5 6 7 29 Vernier cycles 1 Overall TDC jitter : 6. 9 ps rms Nicolas. Roy 6@USherbrooke. ca 14

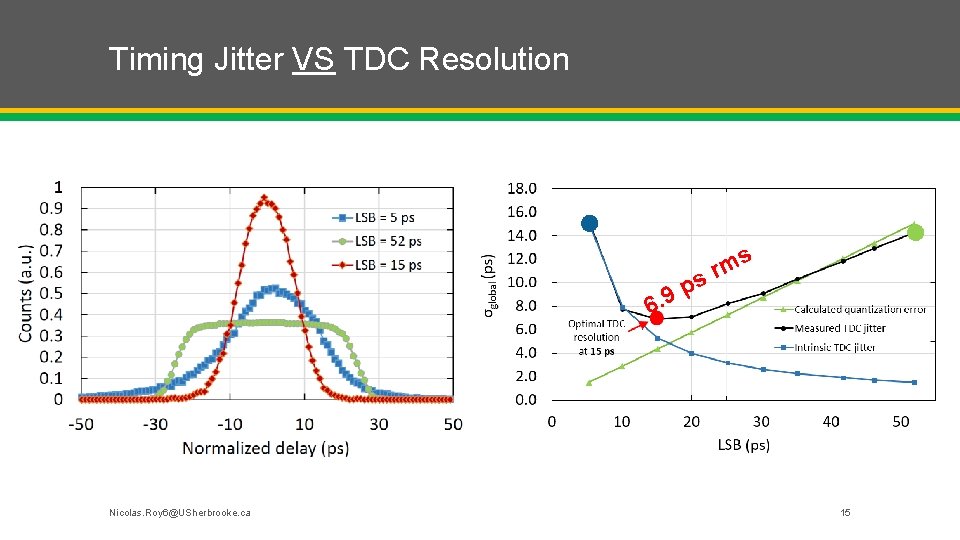

Timing Jitter VS TDC Resolution s m r s p 9 6. Nicolas. Roy 6@USherbrooke. ca 15

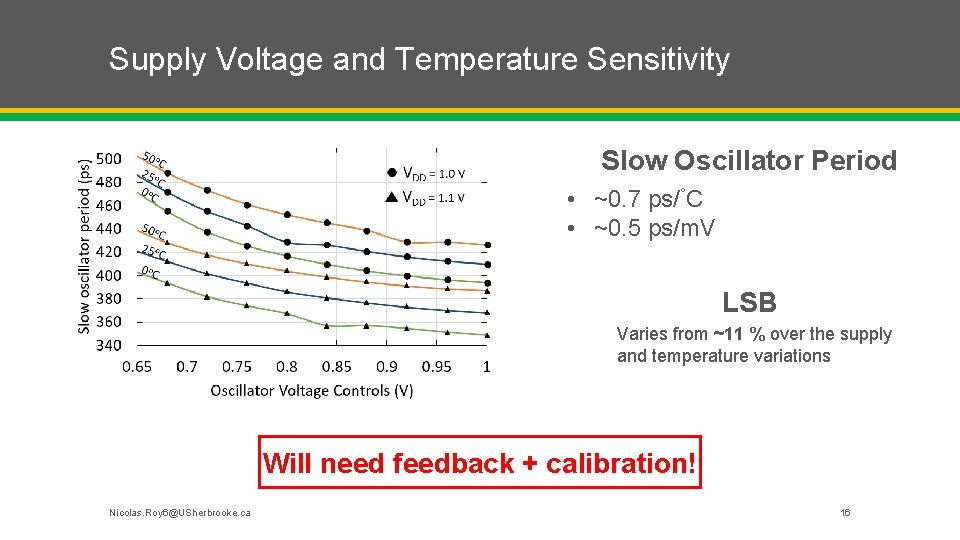

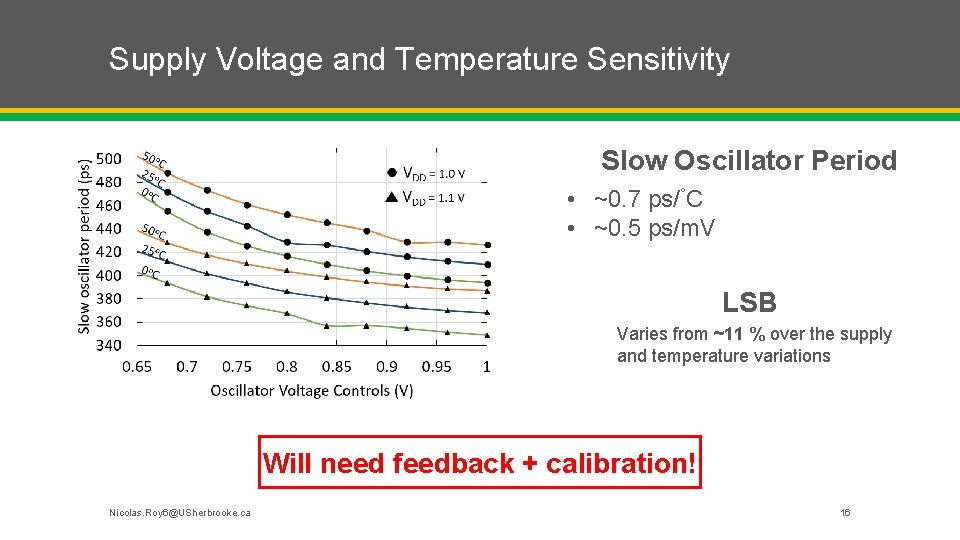

Supply Voltage and Temperature Sensitivity Slow Oscillator Period • ~0. 7 ps/°C • ~0. 5 ps/m. V LSB Varies from ~11 % over the supply and temperature variations Will need feedback + calibration! Nicolas. Roy 6@USherbrooke. ca 16

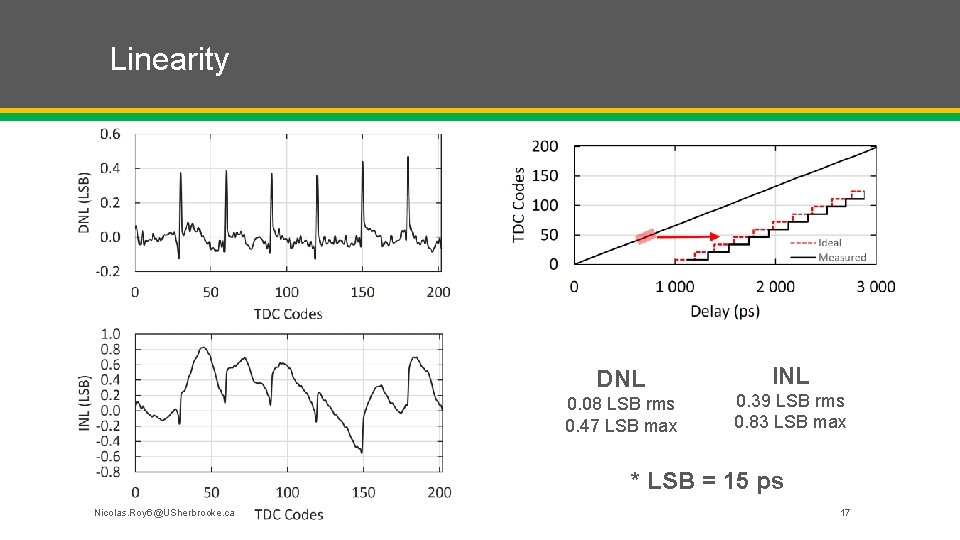

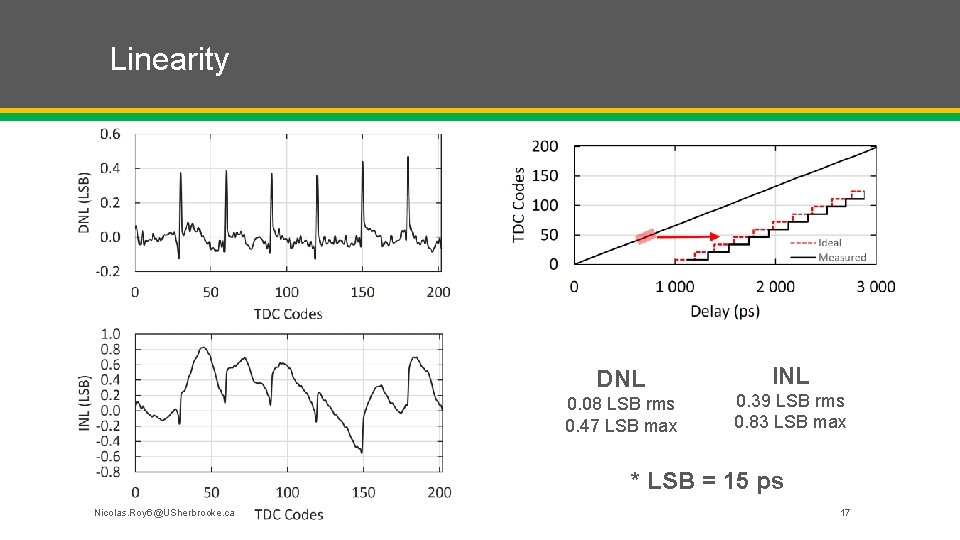

Linearity DNL 0. 08 LSB rms 0. 47 LSB max INL 0. 39 LSB rms 0. 83 LSB max * LSB = 15 ps Nicolas. Roy 6@USherbrooke. ca 17

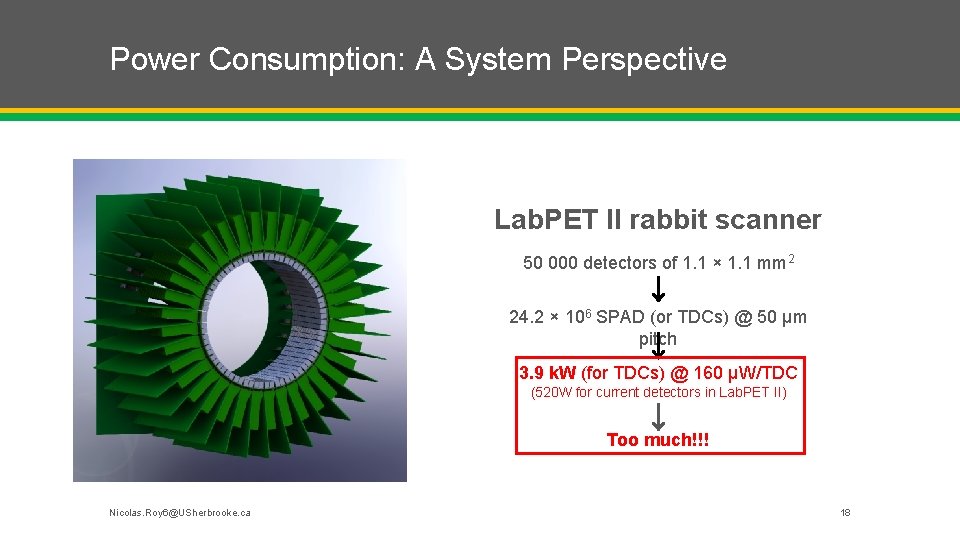

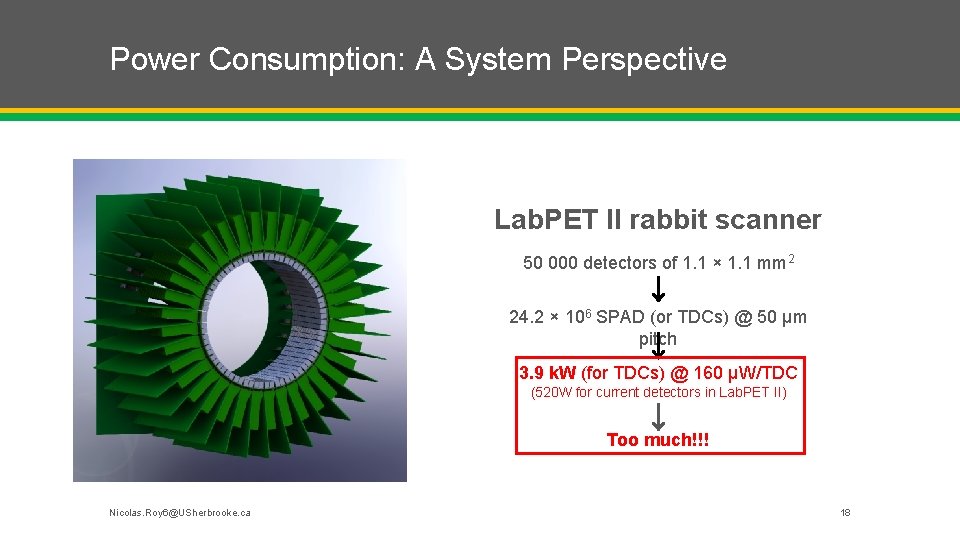

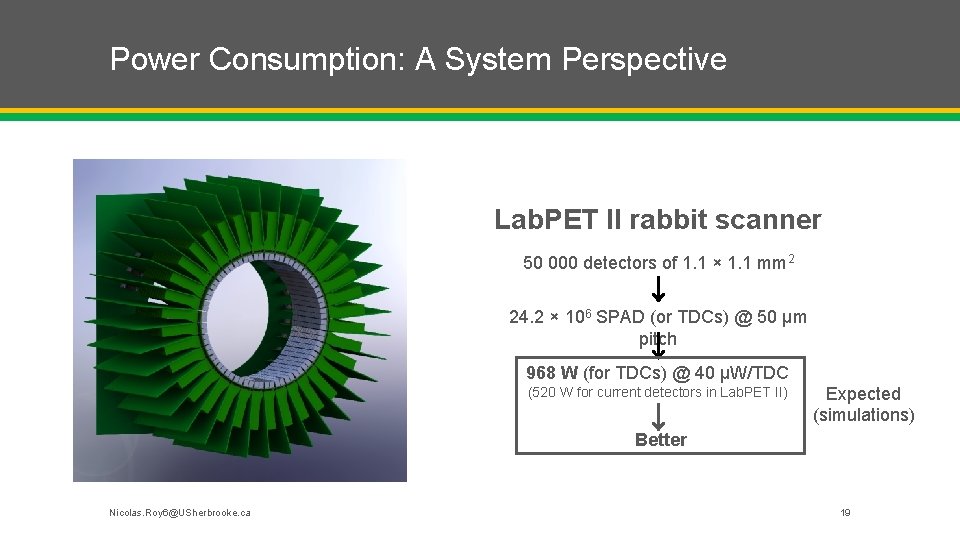

Power Consumption: A System Perspective Lab. PET II rabbit scanner 50 000 detectors of 1. 1 × 1. 1 mm 2 24. 2 × 106 SPAD (or TDCs) @ 50 µm pitch 3. 9 k. W (for TDCs) @ 160 µW/TDC (520 W for current detectors in Lab. PET II) Too much!!! Nicolas. Roy 6@USherbrooke. ca 18

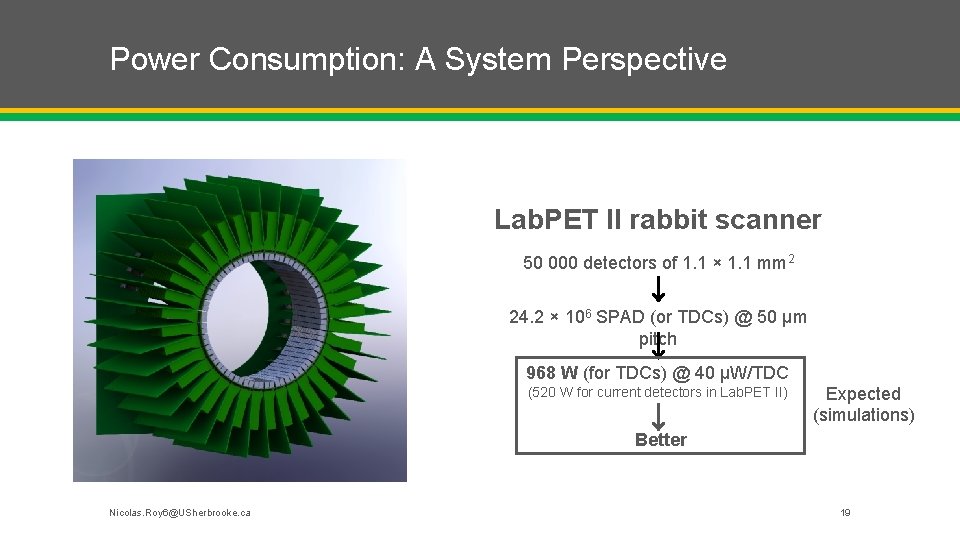

Power Consumption: A System Perspective Lab. PET II rabbit scanner 50 000 detectors of 1. 1 × 1. 1 mm 2 24. 2 × 106 SPAD (or TDCs) @ 50 µm pitch 968 W (for TDCs) @ 40 µW/TDC (520 W for current detectors in Lab. PET II) Expected (simulations) Better Nicolas. Roy 6@USherbrooke. ca 19

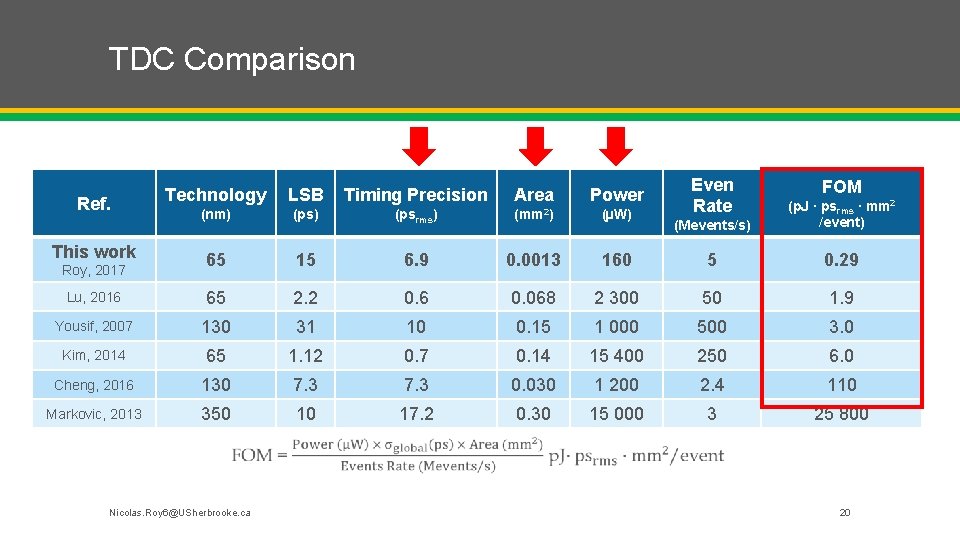

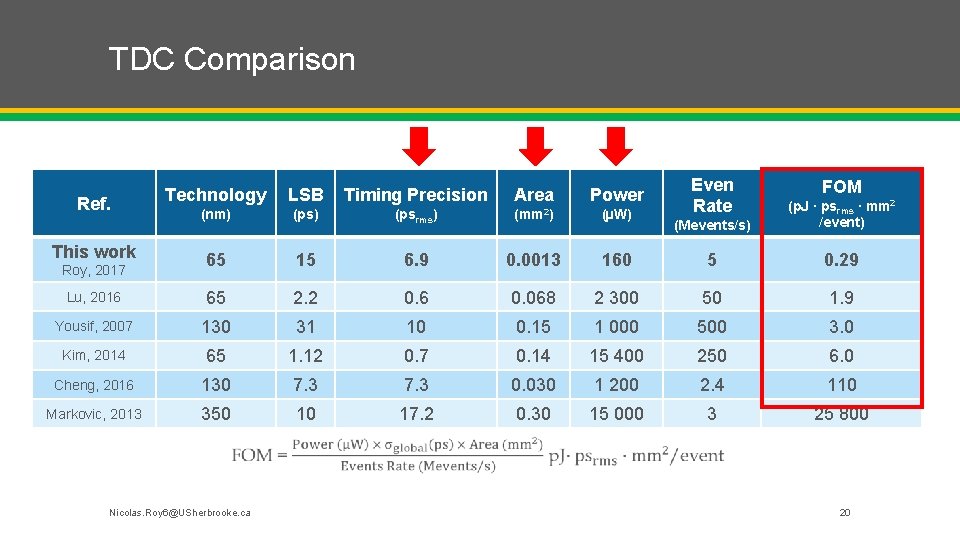

TDC Comparison Technology LSB Timing Precision Area Power (nm) (psrms) (mm 2) (µW) 65 15 6. 9 0. 0013 Lu, 2016 65 2. 2 0. 6 Yousif, 2007 130 31 Kim, 2014 65 Cheng, 2016 Markovic, 2013 Ref. This work Roy, 2017 Even Rate FOM (Mevents/s) (p. J ∙ psrms ∙ mm 2 /event) 160 5 0. 29 0. 068 2 300 50 1. 9 10 0. 15 1 000 500 3. 0 1. 12 0. 7 0. 14 15 400 250 6. 0 130 7. 3 0. 030 1 200 2. 4 110 350 10 17. 2 0. 30 15 000 3 25 800 Nicolas. Roy 6@USherbrooke. ca 20

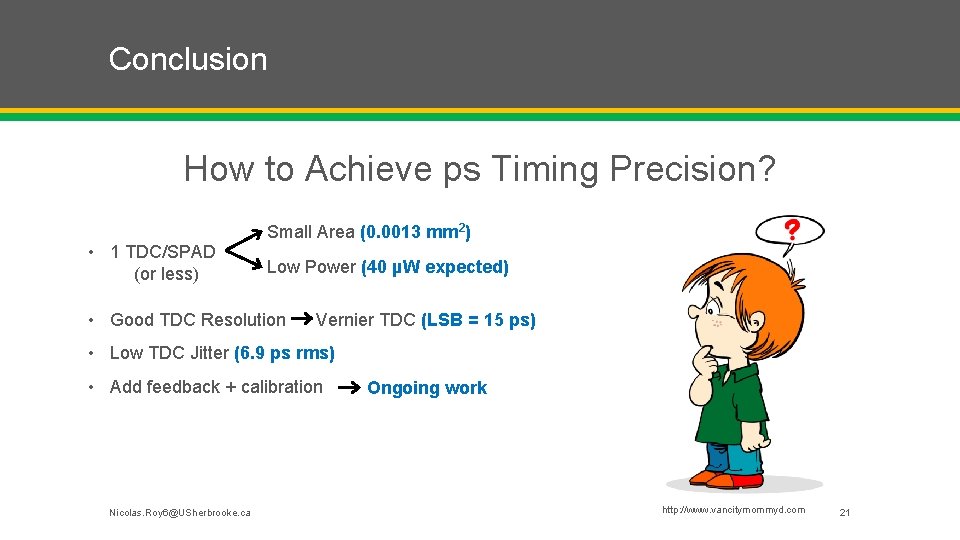

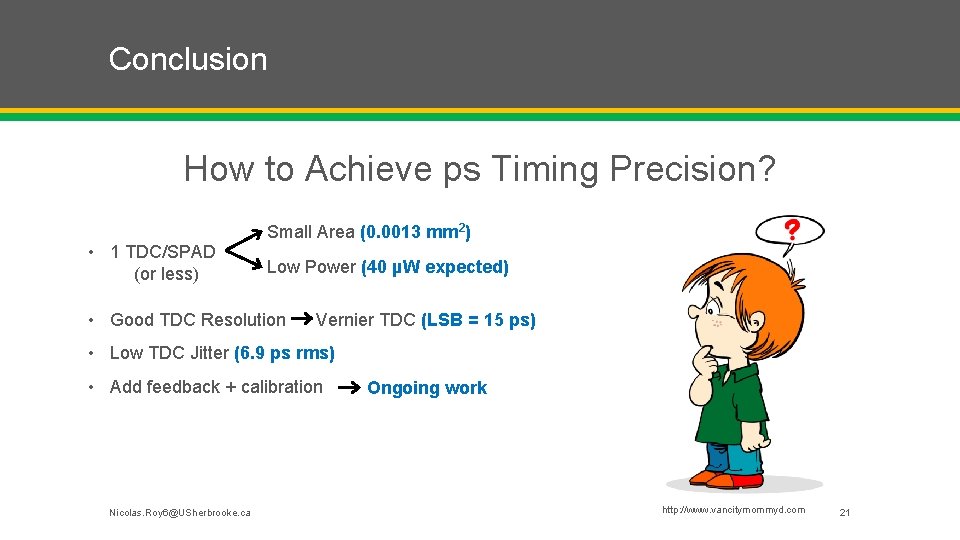

Conclusion How to Achieve ps Timing Precision? Small Area (0. 0013 mm 2) • 1 TDC/SPAD (or less) Low Power (40 µW expected) • Good TDC Resolution Vernier TDC (LSB = 15 ps) • Low TDC Jitter (6. 9 ps rms) • Add feedback + calibration Nicolas. Roy 6@USherbrooke. ca Ongoing work http: //www. vancitymommyd. com 21

Thank you! 22

Backup Slides 23

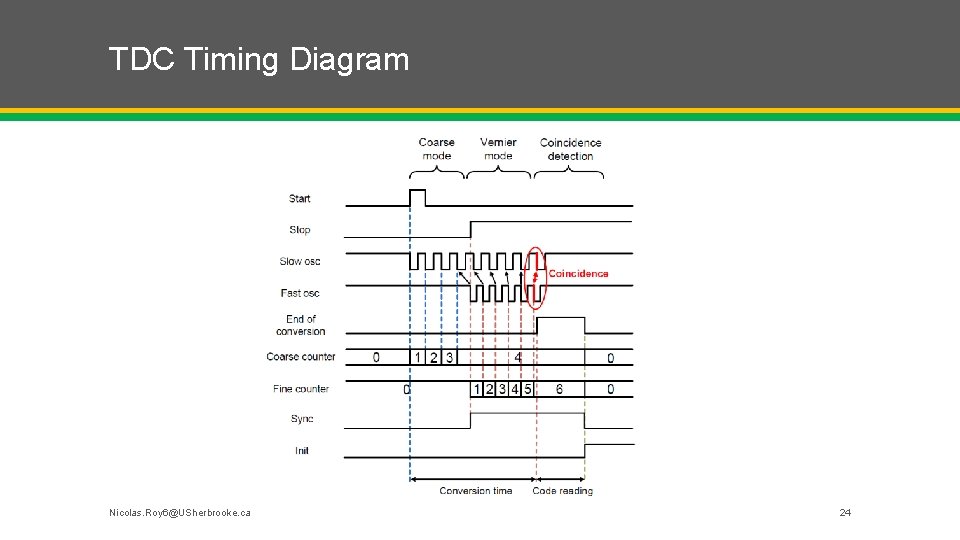

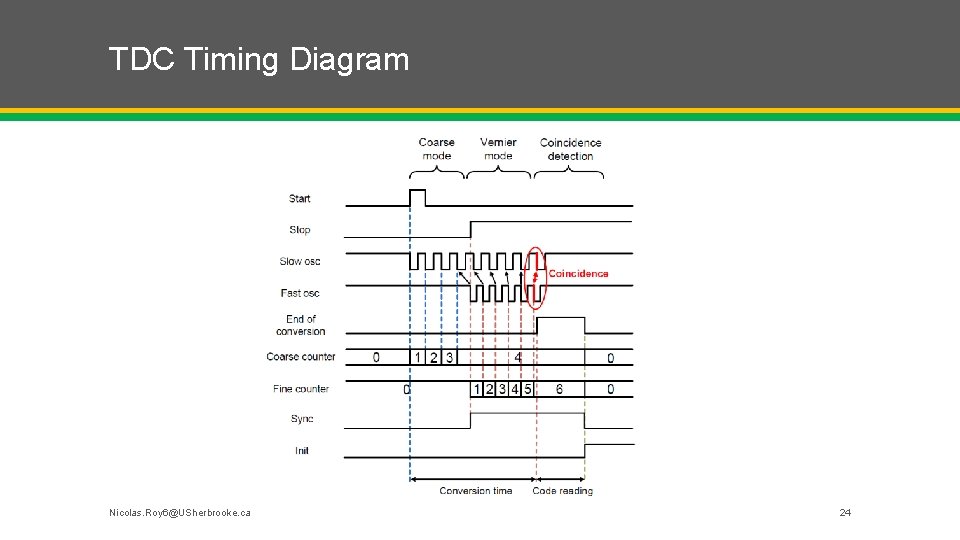

TDC Timing Diagram Nicolas. Roy 6@USherbrooke. ca 24

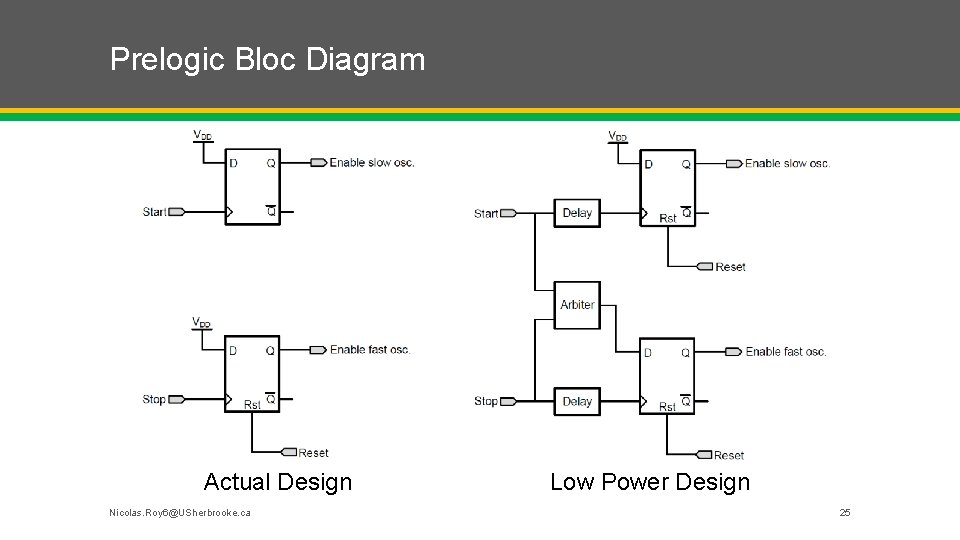

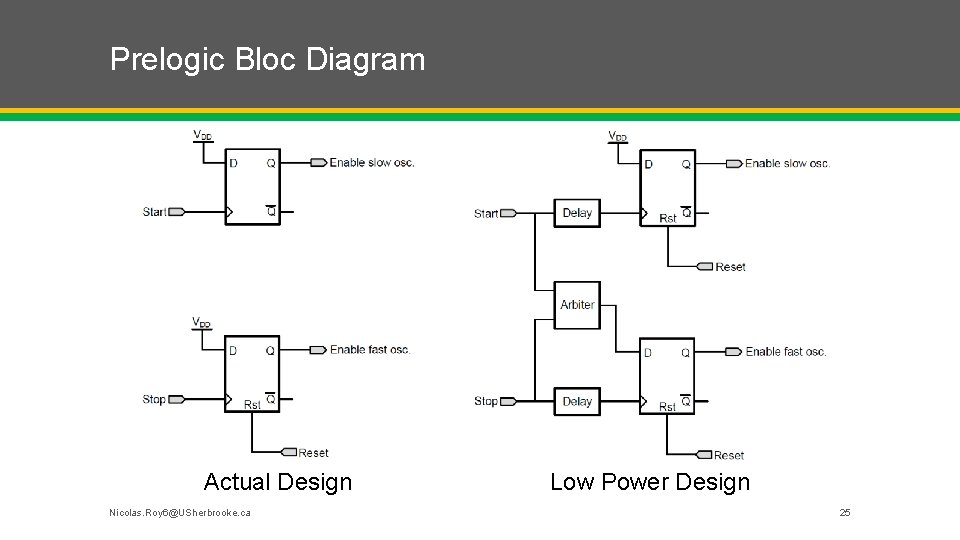

Prelogic Bloc Diagram Actual Design Nicolas. Roy 6@USherbrooke. ca Low Power Design 25

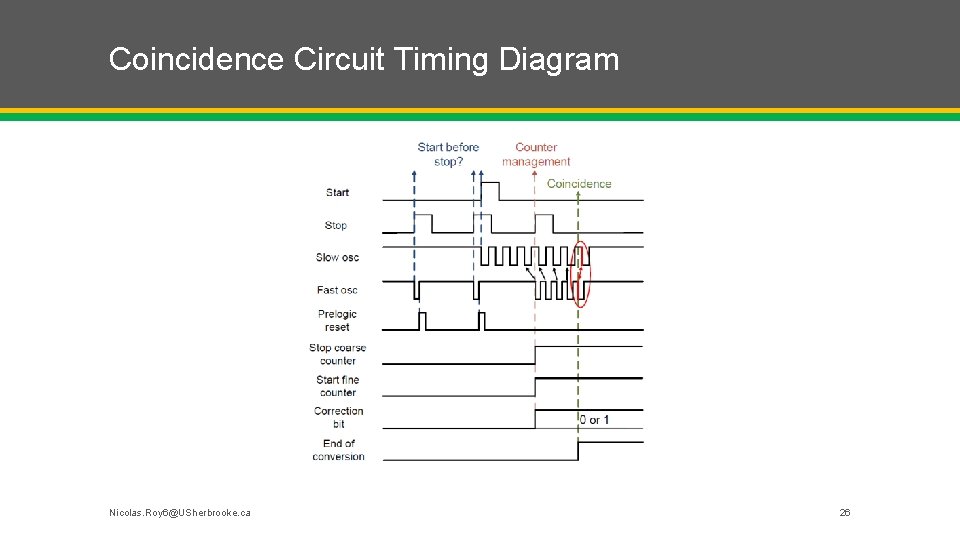

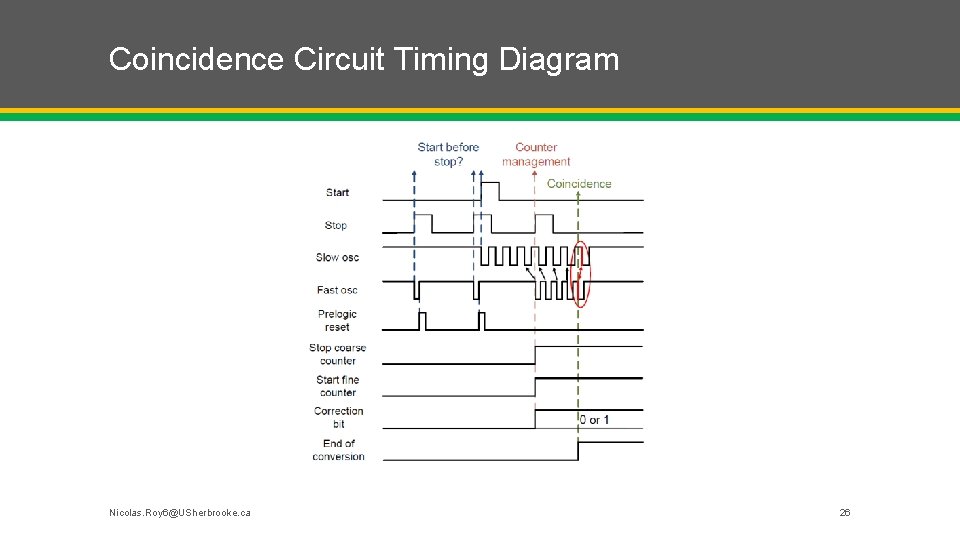

Coincidence Circuit Timing Diagram Nicolas. Roy 6@USherbrooke. ca 26

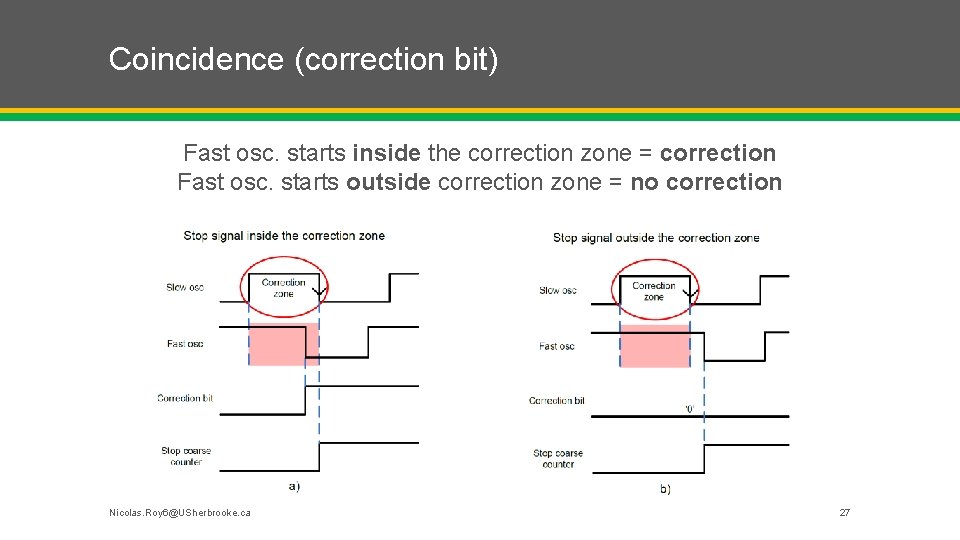

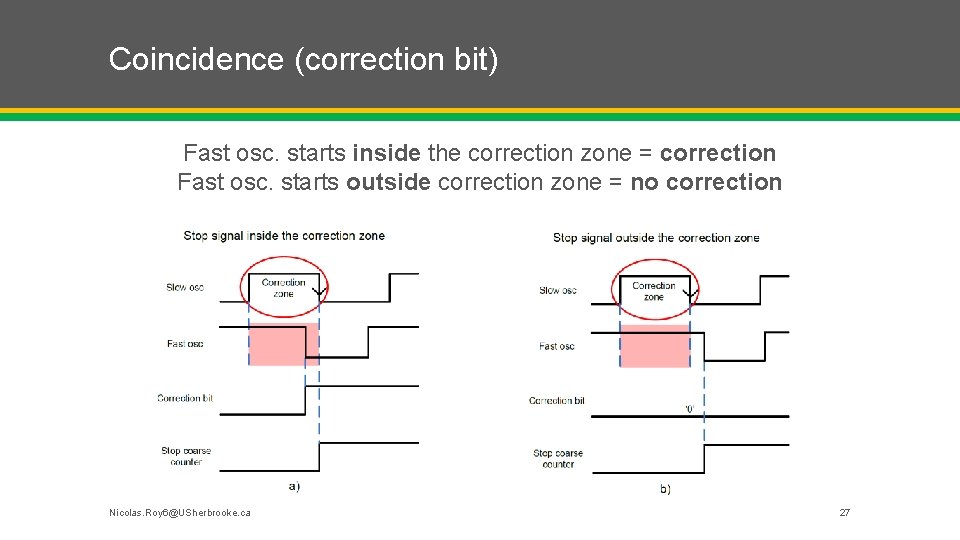

Coincidence (correction bit) Fast osc. starts inside the correction zone = correction Fast osc. starts outside correction zone = no correction Nicolas. Roy 6@USherbrooke. ca 27

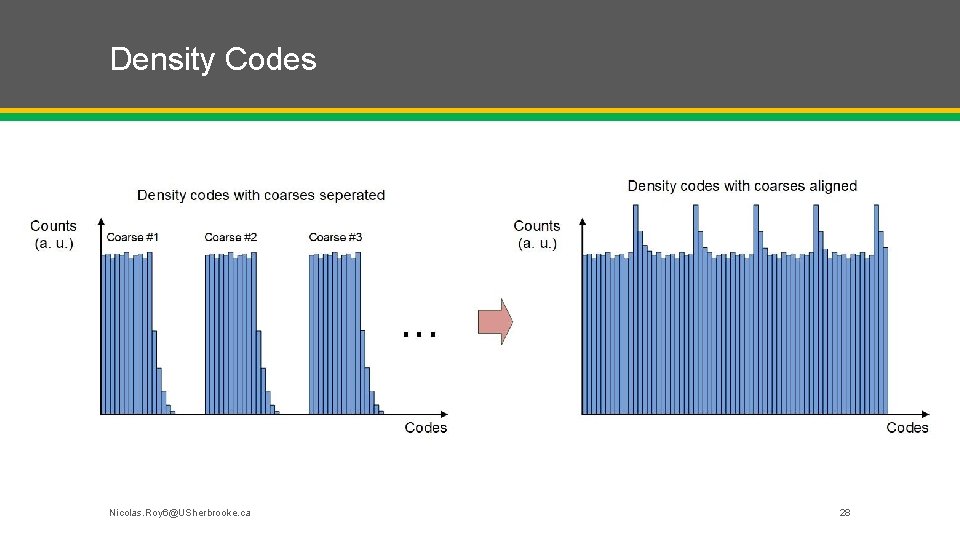

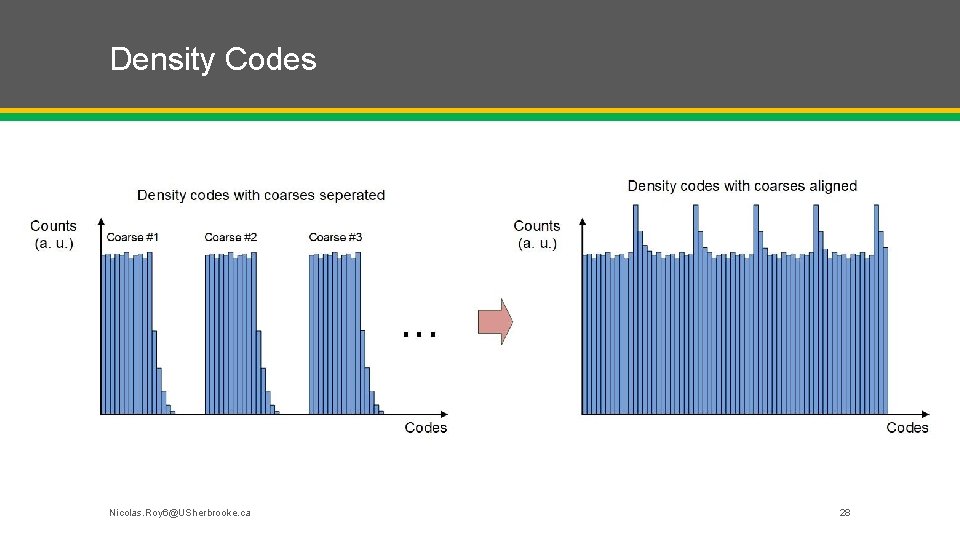

Density Codes Nicolas. Roy 6@USherbrooke. ca 28

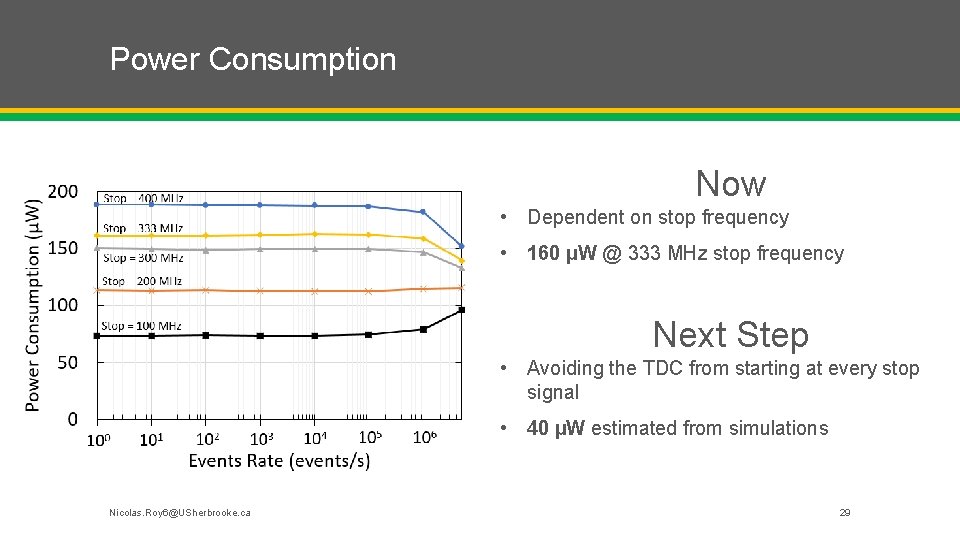

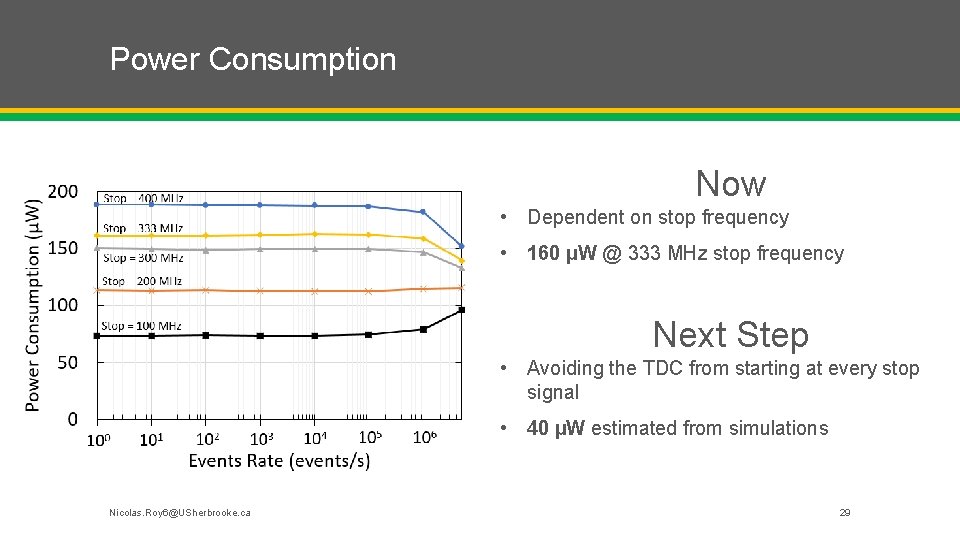

Power Consumption Now • Dependent on stop frequency • 160 µW @ 333 MHz stop frequency Next Step • Avoiding the TDC from starting at every stop signal • 40 µW estimated from simulations Nicolas. Roy 6@USherbrooke. ca 29