Synthesizing SRAM timing and Periphery using Synopsis st

![Constraints file set_driving_cell -lib_cell NBUFFX 16 -pin Z [get_ports clk] set_driving_cell -lib_cell NBUFFX 4 Constraints file set_driving_cell -lib_cell NBUFFX 16 -pin Z [get_ports clk] set_driving_cell -lib_cell NBUFFX 4](https://slidetodoc.com/presentation_image/57a1d381869d6ceb53ae93b5bb43f934/image-4.jpg)

- Slides: 23

Synthesizing SRAM timing and Periphery using Synopsis st Robu Low Robust er Pow LSI V Power VLSI By: Jim Boley

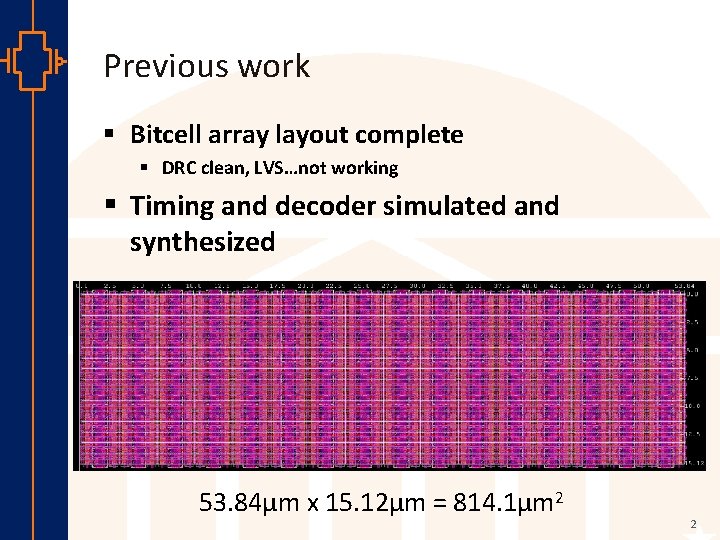

Previous work § Bitcell array layout complete § DRC clean, LVS…not working § Timing and decoder simulated and synthesized st Robu Low er Pow VLSI 53. 84μm x 15. 12μm = 814. 1μm 2 2

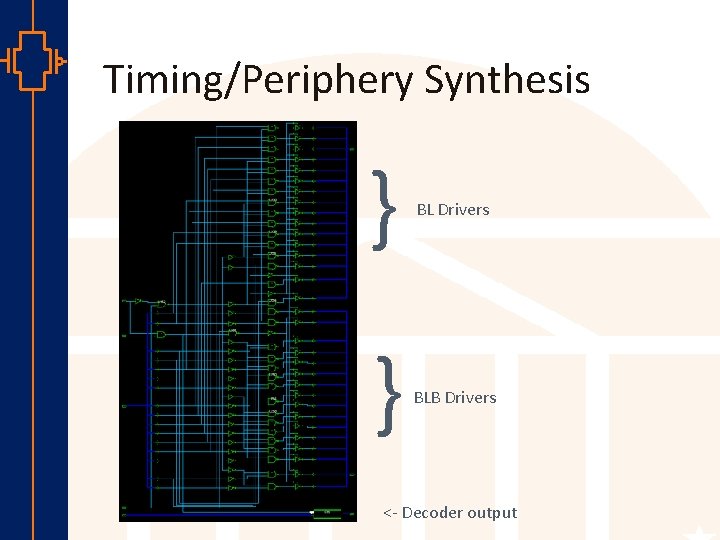

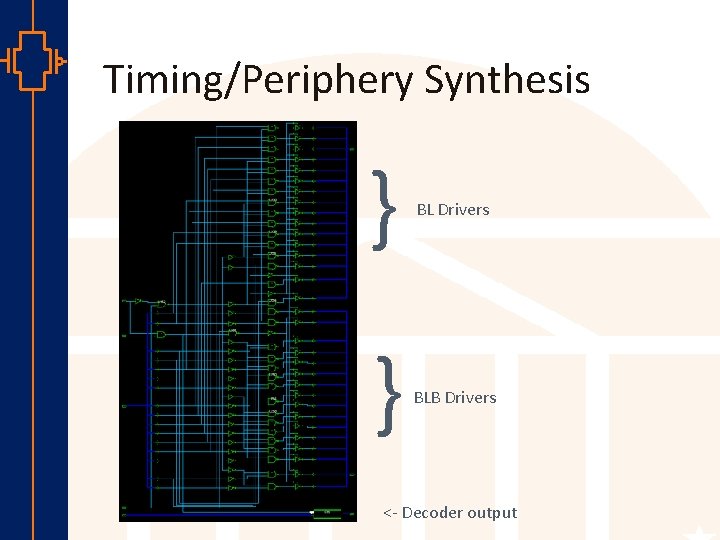

Timing/Periphery Synthesis st Robu Low er Pow VLSI } BL Drivers } BLB Drivers <- Decoder output

![Constraints file setdrivingcell libcell NBUFFX 16 pin Z getports clk setdrivingcell libcell NBUFFX 4 Constraints file set_driving_cell -lib_cell NBUFFX 16 -pin Z [get_ports clk] set_driving_cell -lib_cell NBUFFX 4](https://slidetodoc.com/presentation_image/57a1d381869d6ceb53ae93b5bb43f934/image-4.jpg)

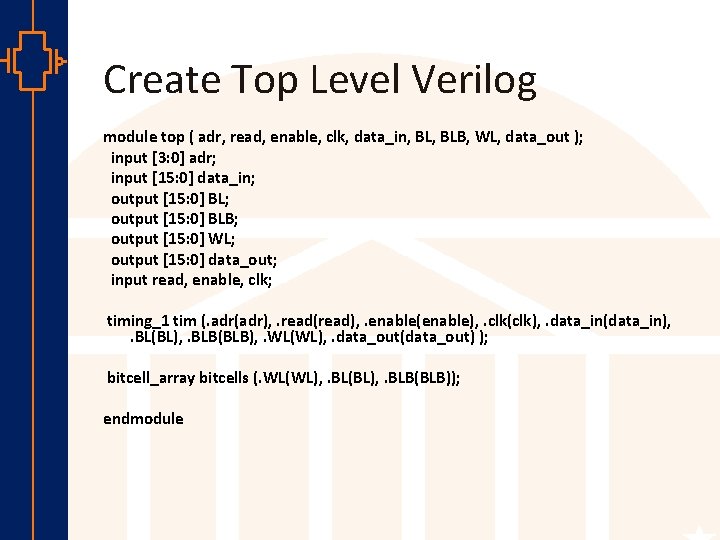

Constraints file set_driving_cell -lib_cell NBUFFX 16 -pin Z [get_ports clk] set_driving_cell -lib_cell NBUFFX 4 -pin Z [get_ports {read enable}] set_load [expr 16 * [load_of saed 90 nm_typ_ht/INVX 2/INP] ] [all_outputs] § set_driving_cell- sets input fan in § set_load- sets output fan out st Robu Low er Pow VLSI

Final Steps § Finish bitcell array- (power grid, add body contacts, add pins) § Convert layout into a Milkyway Library § Create final top level verilog netlist § Place and route using ICC st Robu Low er Pow VLSI

Converting Layout to a Milkyway Library st Robu Low er Pow VLSI 6

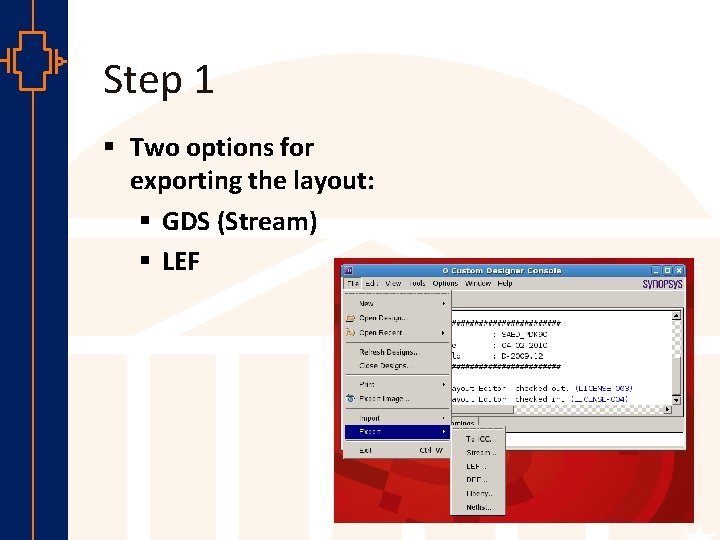

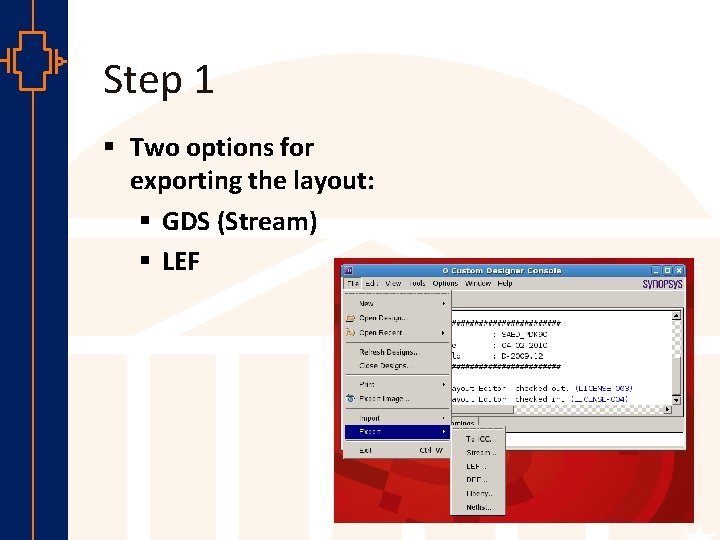

Step 1 § Two options for exporting the layout: § GDS (Stream) § LEF st Robu Low er Pow VLSI

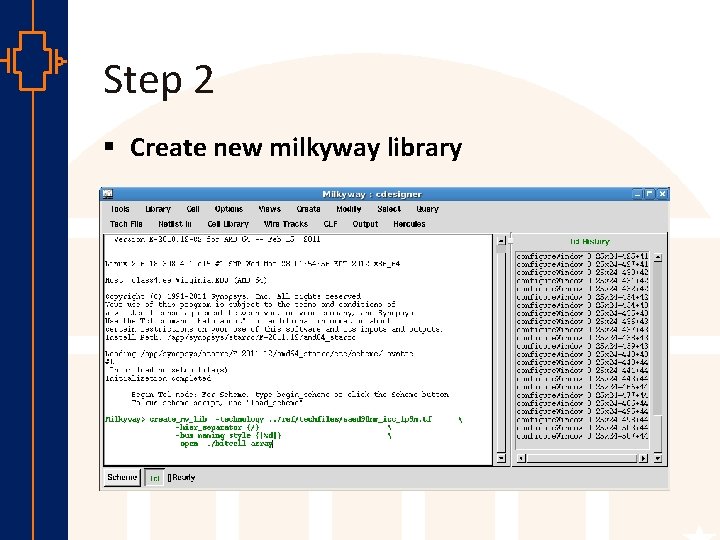

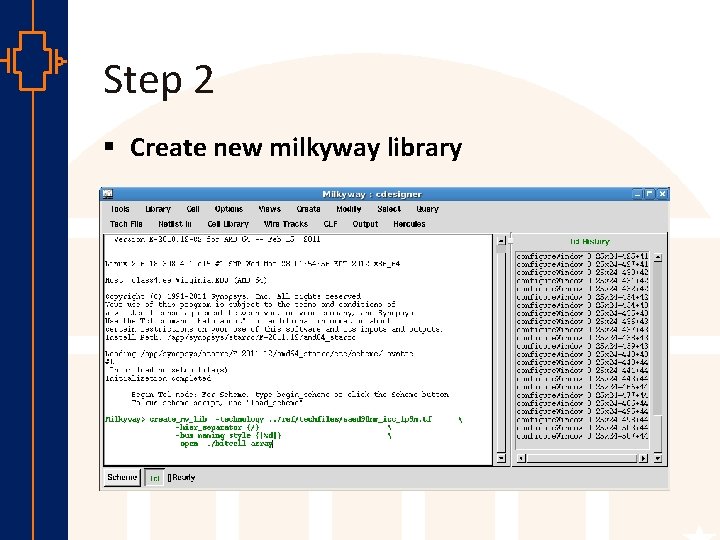

Step 2 § Create new milkyway library st Robu Low er Pow VLSI

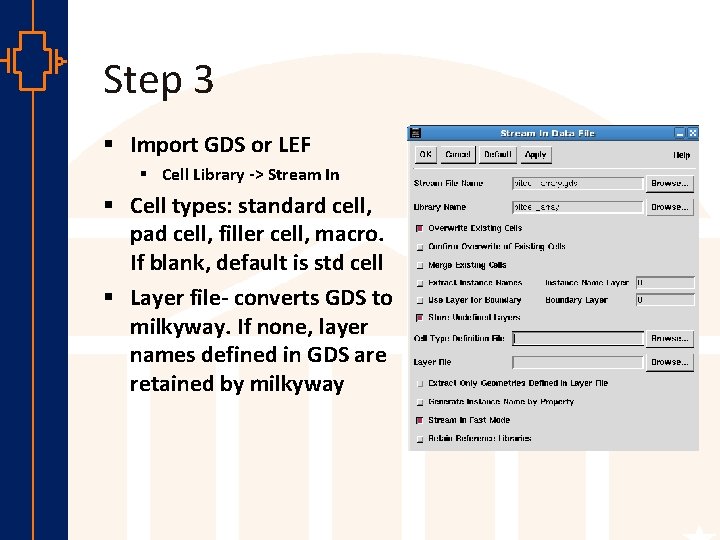

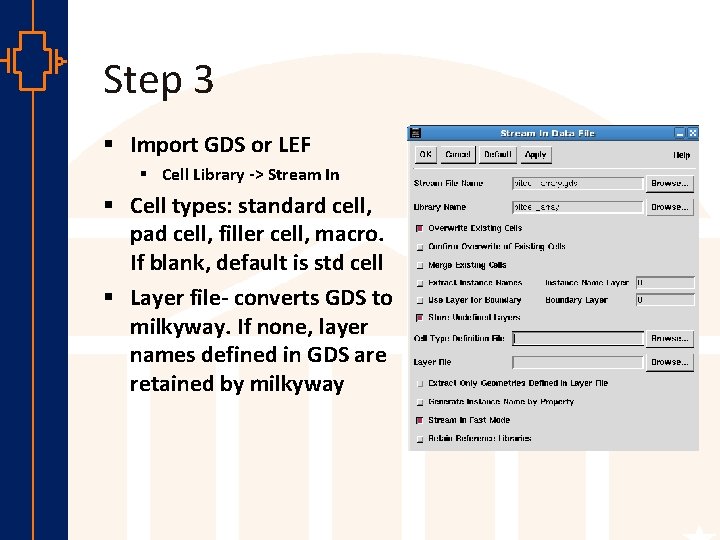

Step 3 § Import GDS or LEF § Cell Library -> Stream In § Cell types: standard cell, pad cell, filler cell, macro. If blank, default is std cell § Layer file- converts GDS to milkyway. If none, layer names defined in GDS are retained by milkyway st Robu Low er Pow VLSI

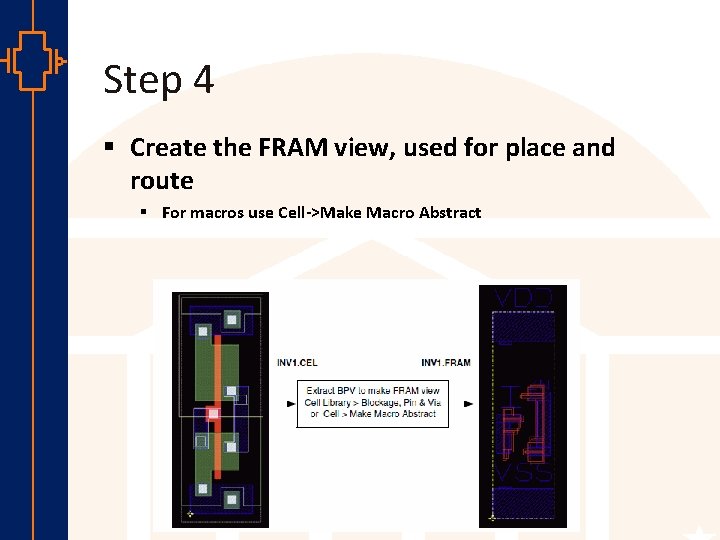

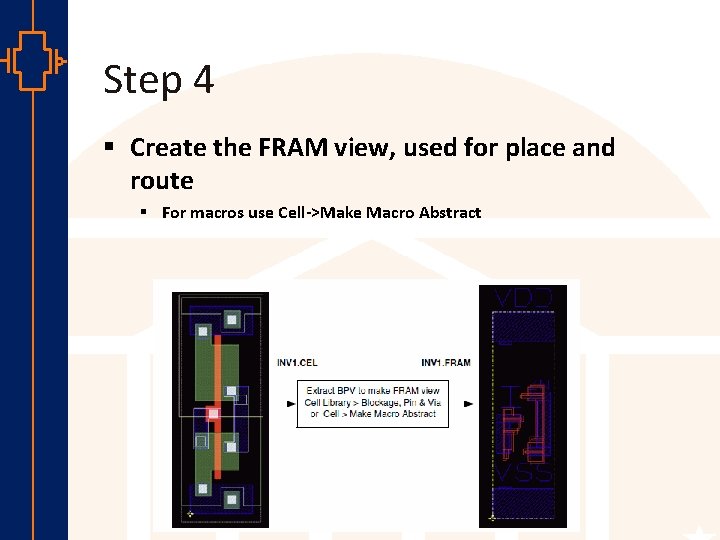

Step 4 § Create the FRAM view, used for place and route § For macros use Cell->Make Macro Abstract st Robu Low er Pow VLSI

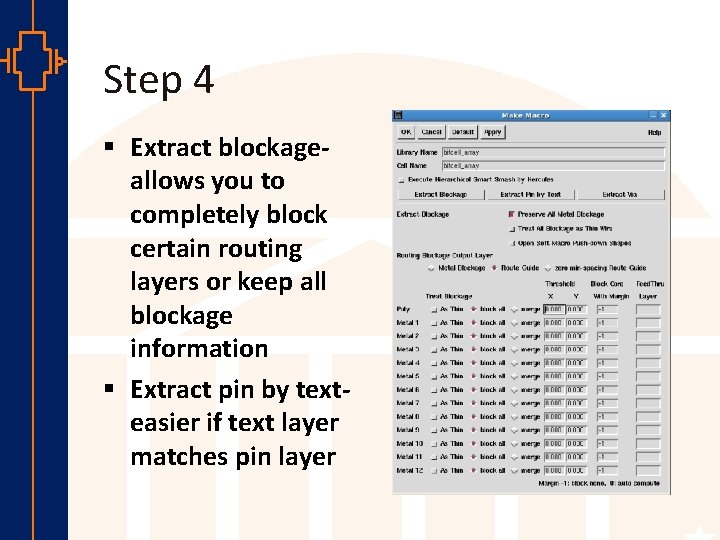

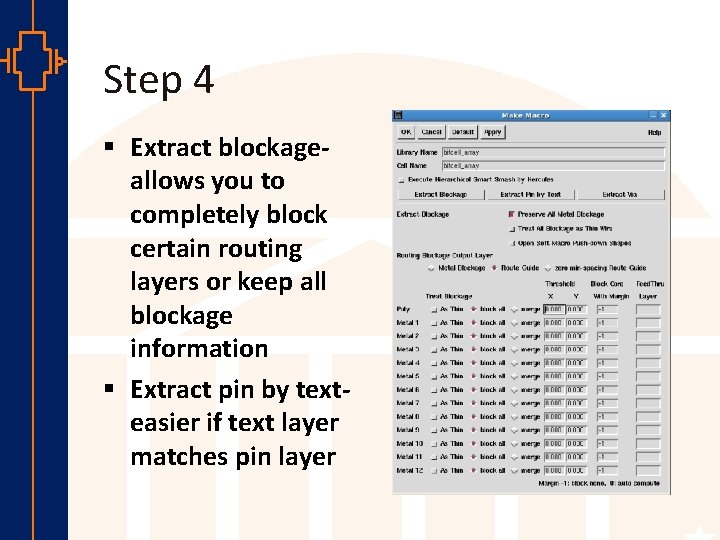

Step 4 st Robu Low er Pow VLSI § Extract blockageallows you to completely block certain routing layers or keep all blockage information § Extract pin by texteasier if text layer matches pin layer

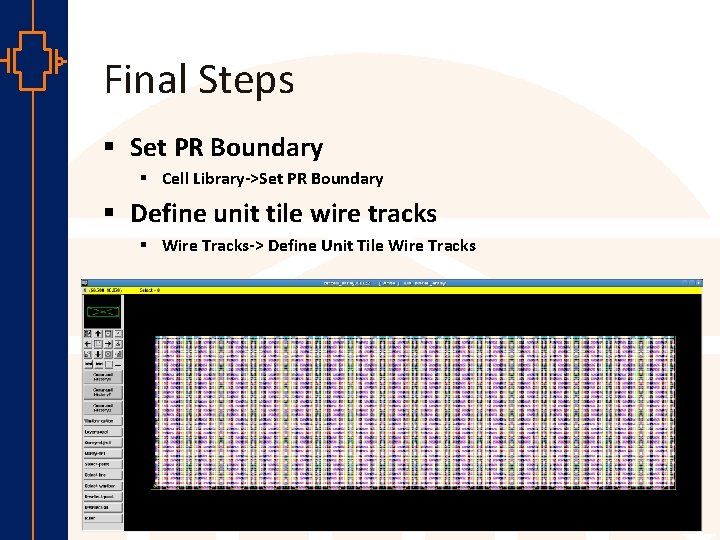

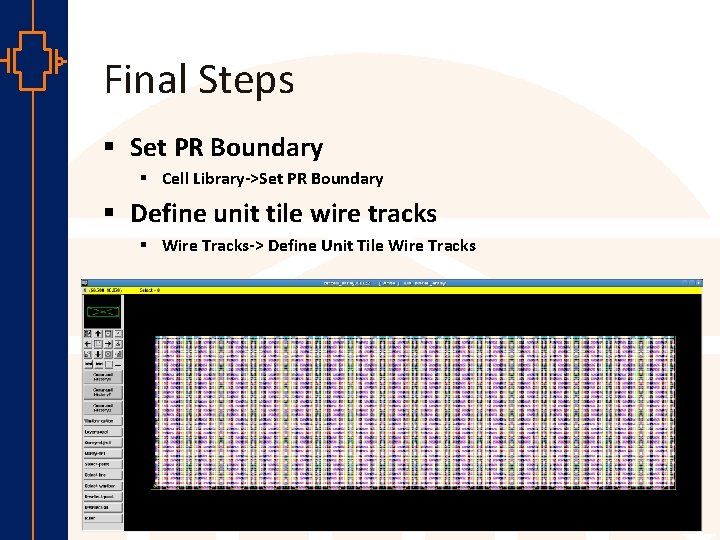

Final Steps § Set PR Boundary § Cell Library->Set PR Boundary § Define unit tile wire tracks § Wire Tracks-> Define Unit Tile Wire Tracks st Robu Low er Pow VLSI

Run ICC Place and Route st Robu Low er Pow VLSI 13

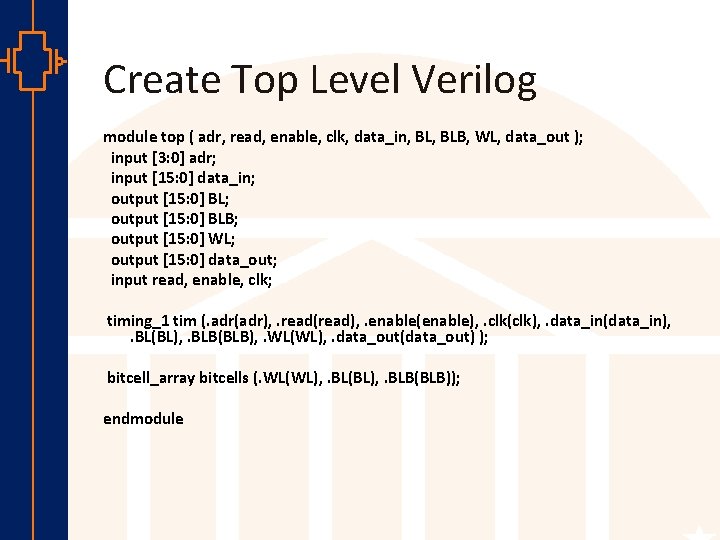

Create Top Level Verilog module top ( adr, read, enable, clk, data_in, BLB, WL, data_out ); input [3: 0] adr; input [15: 0] data_in; output [15: 0] BLB; output [15: 0] WL; output [15: 0] data_out; input read, enable, clk; timing_1 tim (. adr(adr), . read(read), . enable(enable), . clk(clk), . data_in(data_in), . BL(BL), . BLB(BLB), . WL(WL), . data_out(data_out) ); bitcell_array bitcells (. WL(WL), . BL(BL), . BLB(BLB)); st Robu Low er Pow VLSI endmodule

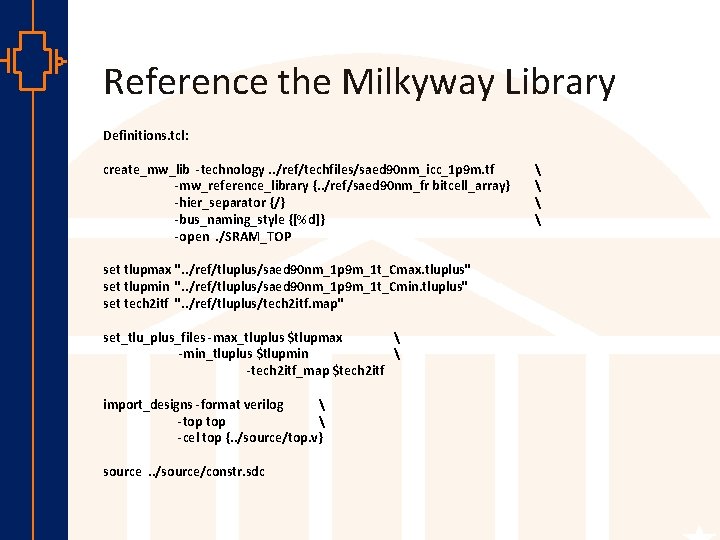

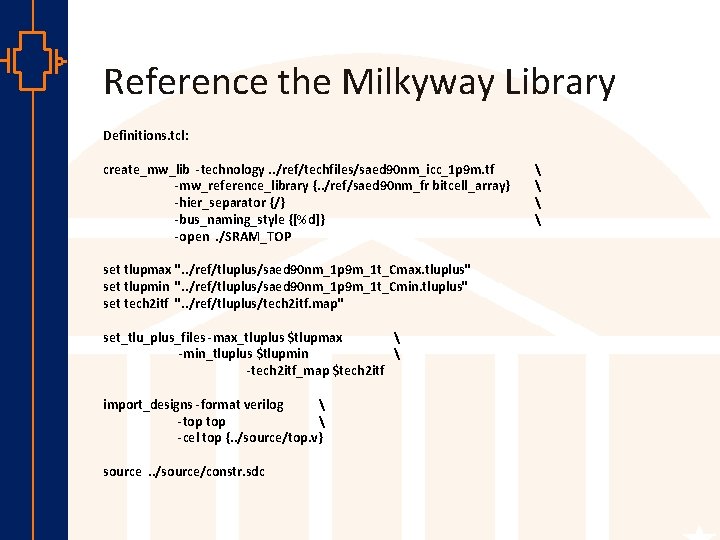

Reference the Milkyway Library Definitions. tcl: create_mw_lib -technology. . /ref/techfiles/saed 90 nm_icc_1 p 9 m. tf -mw_reference_library {. . /ref/saed 90 nm_fr bitcell_array} -hier_separator {/} -bus_naming_style {[%d]} -open. /SRAM_TOP set tlupmax ". . /ref/tluplus/saed 90 nm_1 p 9 m_1 t_Cmax. tluplus" set tlupmin ". . /ref/tluplus/saed 90 nm_1 p 9 m_1 t_Cmin. tluplus" set tech 2 itf ". . /ref/tluplus/tech 2 itf. map" set_tlu_plus_files -max_tluplus $tlupmax -min_tluplus $tlupmin -tech 2 itf_map $tech 2 itf st Robu Low er Pow VLSI import_designs -format verilog -top -cel top {. . /source/top. v} source. . /source/constr. sdc

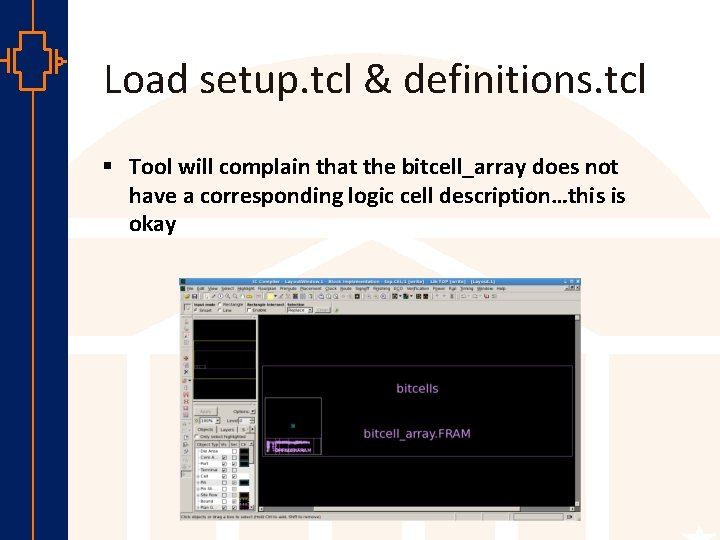

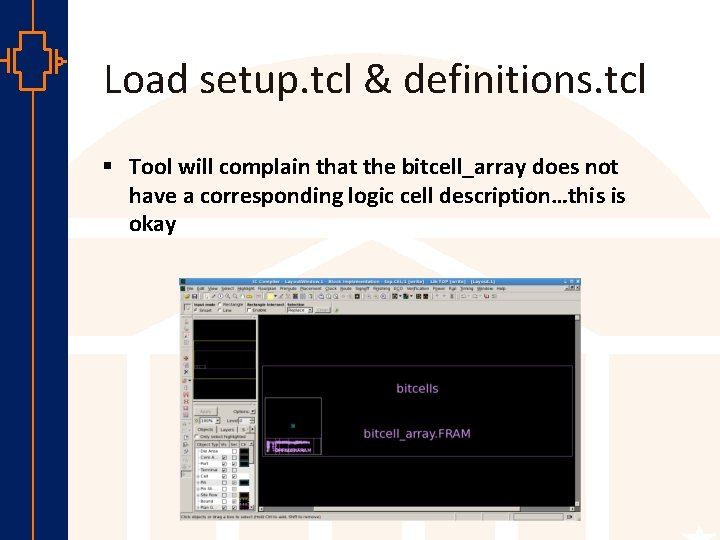

Load setup. tcl & definitions. tcl § Tool will complain that the bitcell_array does not have a corresponding logic cell description…this is okay st Robu Low er Pow VLSI

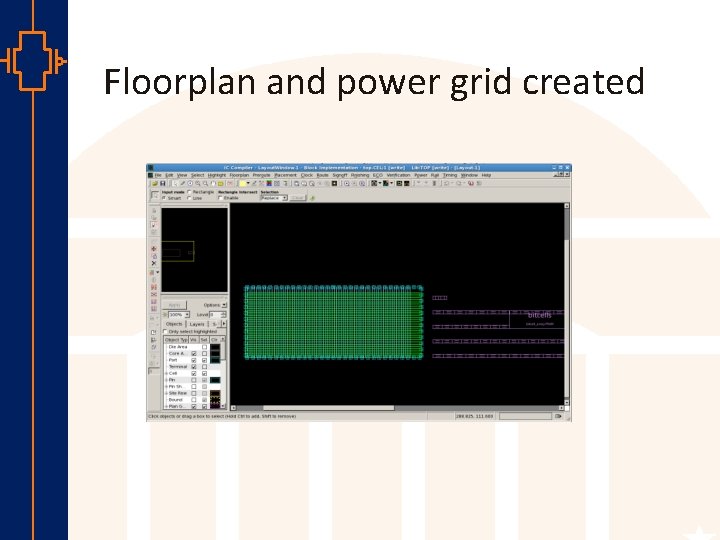

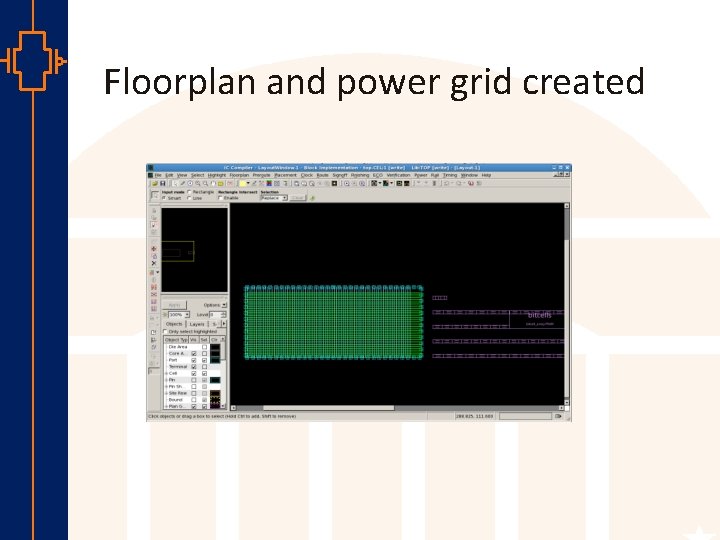

Floorplan and power grid created st Robu Low er Pow VLSI

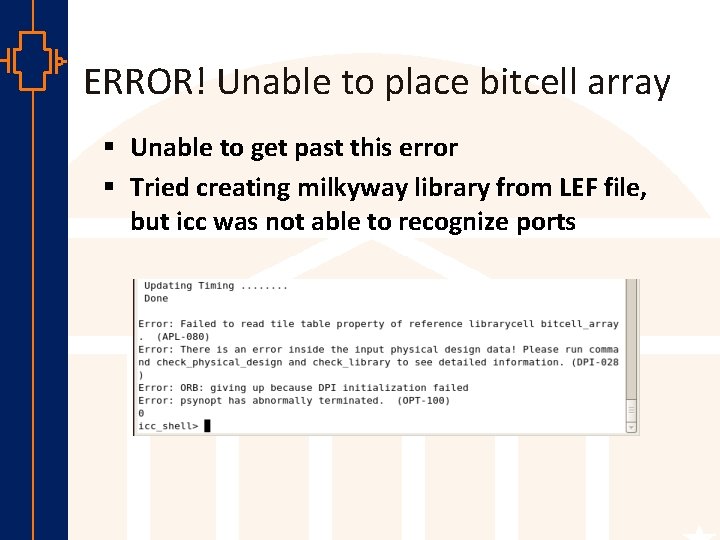

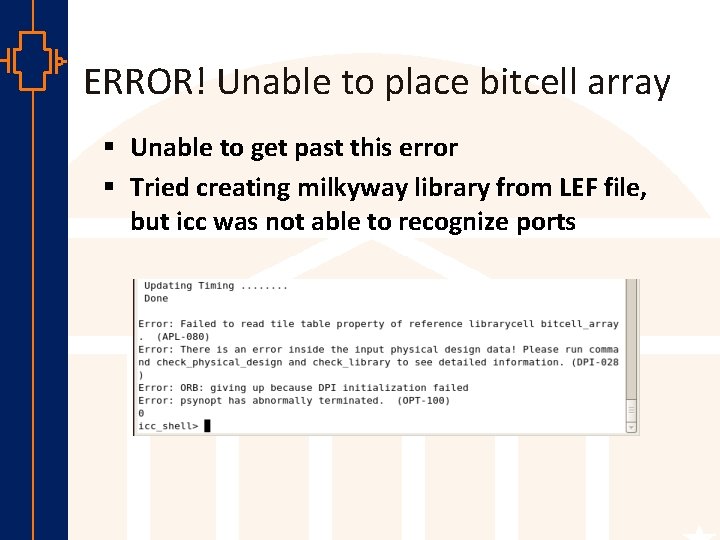

ERROR! Unable to place bitcell array § Unable to get past this error § Tried creating milkyway library from LEF file, but icc was not able to recognize ports st Robu Low er Pow VLSI

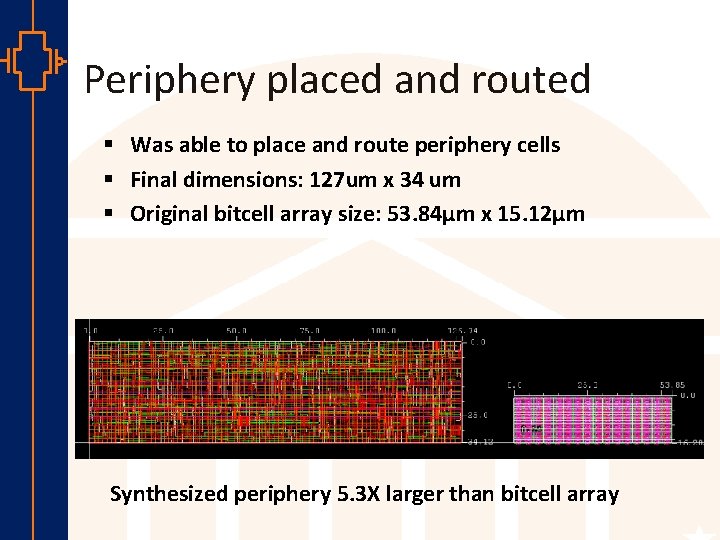

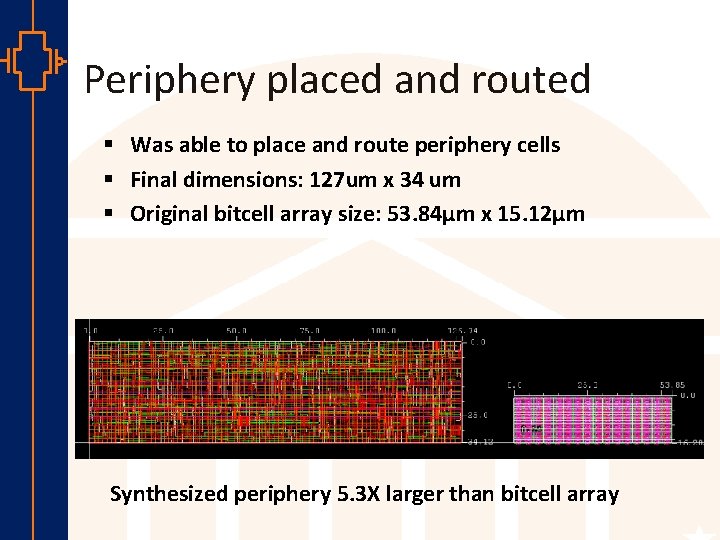

Periphery placed and routed § Was able to place and route periphery cells § Final dimensions: 127 um x 34 um § Original bitcell array size: 53. 84μm x 15. 12μm st Robu Low er Pow VLSI Synthesized periphery 5. 3 X larger than bitcell array

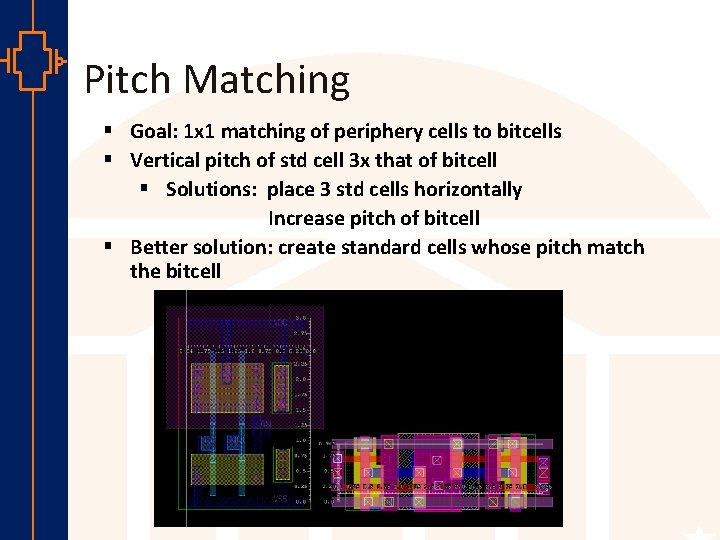

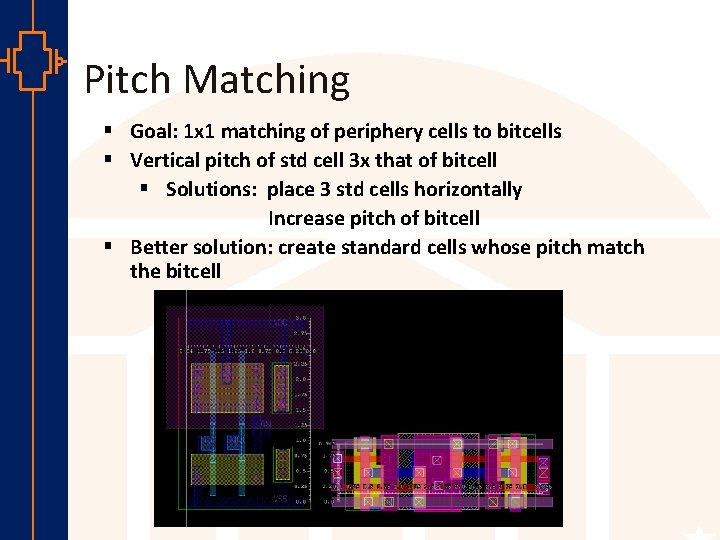

Pitch Matching § Goal: 1 x 1 matching of periphery cells to bitcells § Vertical pitch of std cell 3 x that of bitcell § Solutions: place 3 std cells horizontally Increase pitch of bitcell § Better solution: create standard cells whose pitch match the bitcell st Robu Low er Pow VLSI

Conclusions § Standard cell library cells are not suited for SRAM periphery § Periphery usually consumes on 20% of total area because it is pitch matched to the bitcells § Place and route tool could be useful for doing top level routing (assuming placement information could be easily passed to the tool) st Robu Low er Pow VLSI

Why I didn’t like Synopsys § No online forums for answering questions (like cadence has) st Robu Low er Pow VLSI § Nothing worked the first time § Spent 70% of my time debugging the tool, some problems could not be overcome § Tech support infrastructure not adequate (i. e. working tutorials, wiki FAQs, students with experience) § Conclusion: changing tools = huge start up cost

Questions? st Robu Low er Pow VLSI 23