Synopsys Tool 1 Contents Synopsys Synopsys Setup Synopsys

![Synopsys 환경 Setup(cont’d) �. synopsys_sge. setup 작성의 예 ………. [Symbol. Libraries] $SGE_ROOT/lib/IEEElib = Yes Synopsys 환경 Setup(cont’d) �. synopsys_sge. setup 작성의 예 ………. [Symbol. Libraries] $SGE_ROOT/lib/IEEElib = Yes](https://slidetodoc.com/presentation_image/103370fca6380966817e57c646ccdf80/image-7.jpg)

![Synopsys 환경 Setup(cont’d) �. synopsys_sge 2 vhdl. setup 작성의 예 [Defaults] net_type = std_logic Synopsys 환경 Setup(cont’d) �. synopsys_sge 2 vhdl. setup 작성의 예 [Defaults] net_type = std_logic](https://slidetodoc.com/presentation_image/103370fca6380966817e57c646ccdf80/image-8.jpg)

![Synopsys 환경 Setup(cont’d) �. synopsys_sge 2 vhdl. setup 작성의 예 ……………. . . [CLASS_Defaults] Synopsys 환경 Setup(cont’d) �. synopsys_sge 2 vhdl. setup 작성의 예 ……………. . . [CLASS_Defaults]](https://slidetodoc.com/presentation_image/103370fca6380966817e57c646ccdf80/image-9.jpg)

- Slides: 70

Synopsys Tool 사용법 및 실습 1

Contents � Synopsys - Synopsys 환경 Setup - Synopsys 사용법 - Synthesis Procedures 2

Synopsys 환경 Setup � Synopsys 사용을 위한 setup 환경 잡기 -. cshrc -. synopsys_dc. setup -. synopsys_vss. setup -. synopsys_sge 2 vhdl. setup � 이 파일들의 Default 는 $SYNOPSYS/admin/setup 디렉토리에서 볼 수 있음 3

Synopsys 환경 Setup(cont’d) �. cshrc (Synopsys환경변수) setenv SYNOPSYS /home/95. 5/synopsys setenv ARCH sparc. OS 5 source $SYNOPSYS/admin/install/sim/environ. csh set path = ($path $SYNOPSYS/$ARCH/syn/bin) set path = ($path $SYNOPSYS/$ARCH/sim/bin) set path = ($path $SYNOPSYS/$ARCH/sge/bin) set path = ($path $SYNOPSYS/$ARCH/ds/bin) set path = ($path $SYNOPSYS/iview 2/bin) 4

Synopsys 환경 Setup(cont’d) �. synopsys_dc. setup 파일(Default) search_path = {} + search_path link_library = {class. db}; target_library = {class. db}; symbol_library =class. sdb}; define_design_lib WORK -path. /work; designer = ”student” company = ”CNU IDEC" 5

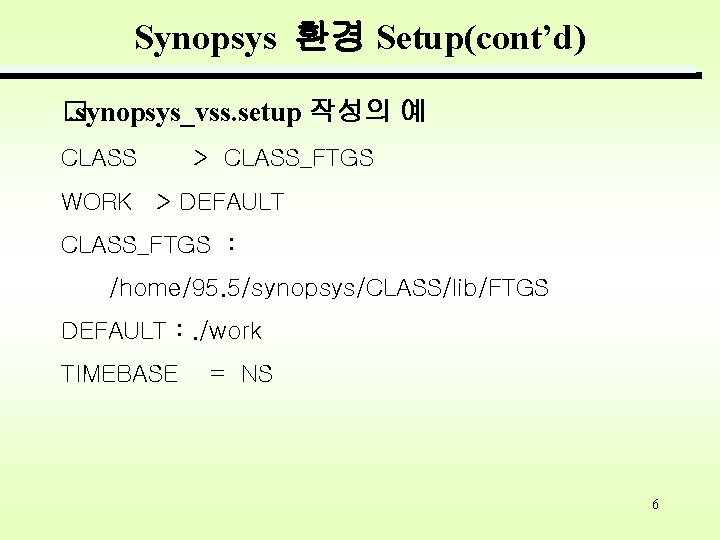

Synopsys 환경 Setup(cont’d) �. synopsys_vss. setup 작성의 예 CLASS > CLASS_FTGS WORK > DEFAULT CLASS_FTGS : /home/95. 5/synopsys/CLASS/lib/FTGS DEFAULT : . /work TIMEBASE = NS 6

![Synopsys 환경 Setupcontd synopsyssge setup 작성의 예 Symbol Libraries SGEROOTlibIEEElib Yes Synopsys 환경 Setup(cont’d) �. synopsys_sge. setup 작성의 예 ………. [Symbol. Libraries] $SGE_ROOT/lib/IEEElib = Yes](https://slidetodoc.com/presentation_image/103370fca6380966817e57c646ccdf80/image-7.jpg)

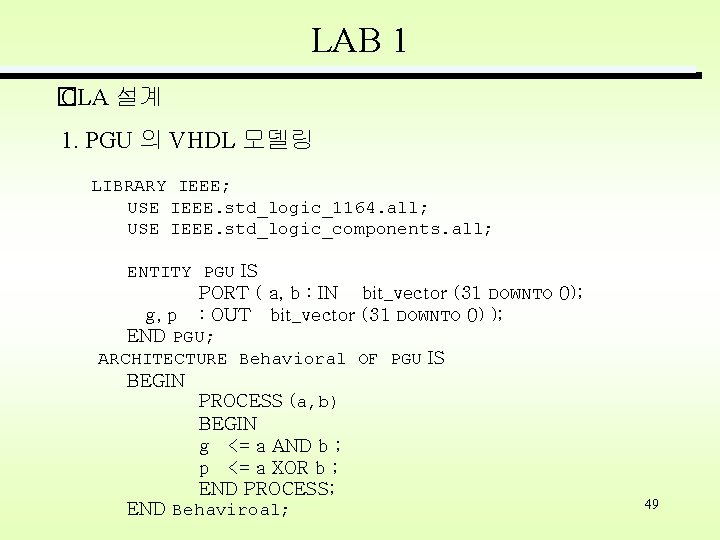

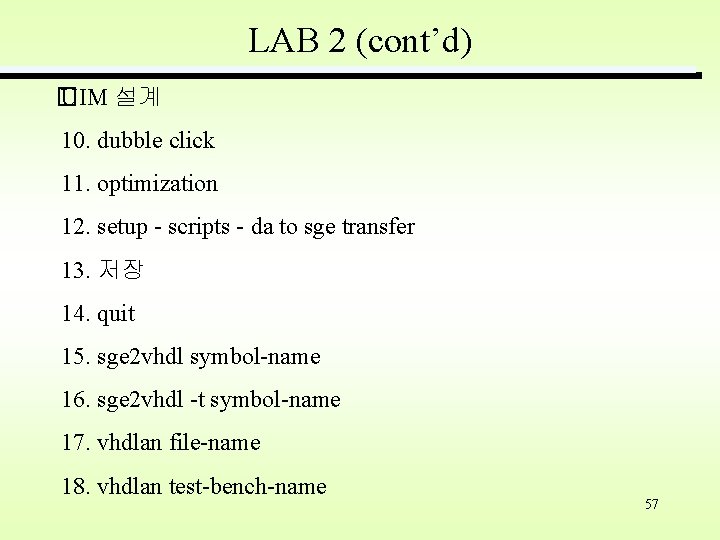

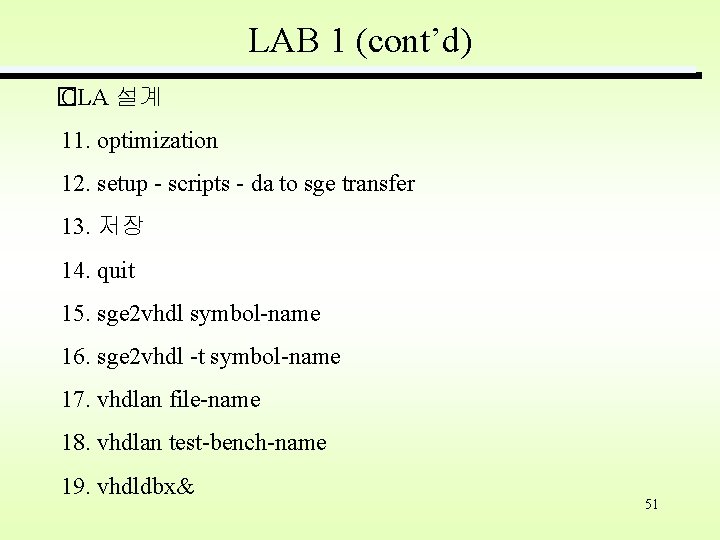

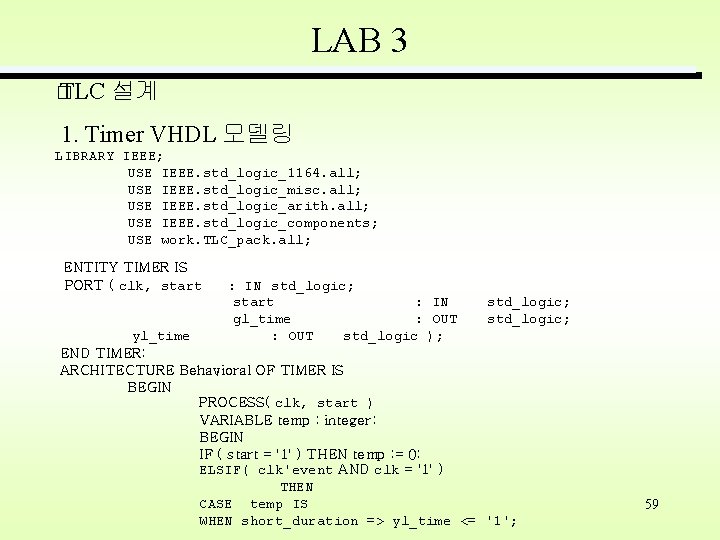

Synopsys 환경 Setup(cont’d) �. synopsys_sge. setup 작성의 예 ………. [Symbol. Libraries] $SGE_ROOT/lib/IEEElib = Yes $SGE_ROOT/lib/MVL 7 lib = No $SGE_ROOT/lib/verilib = No /home/95. 5/synopsys/CLASS/sym = Yes …………………. . 7

![Synopsys 환경 Setupcontd synopsyssge 2 vhdl setup 작성의 예 Defaults nettype stdlogic Synopsys 환경 Setup(cont’d) �. synopsys_sge 2 vhdl. setup 작성의 예 [Defaults] net_type = std_logic](https://slidetodoc.com/presentation_image/103370fca6380966817e57c646ccdf80/image-8.jpg)

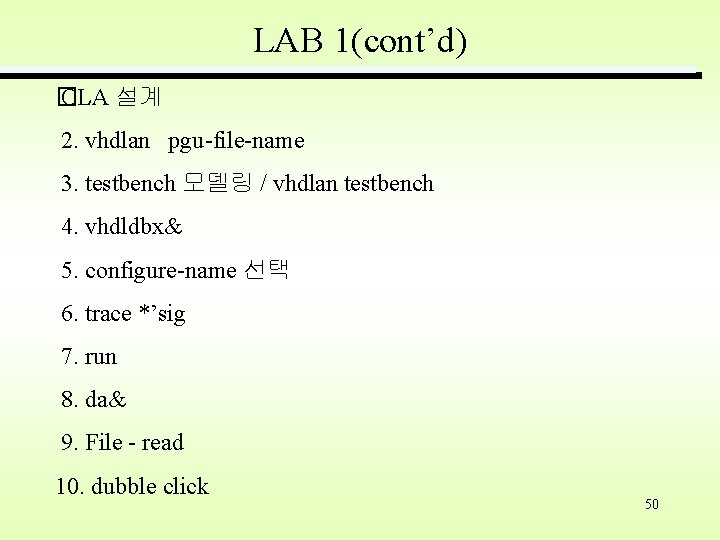

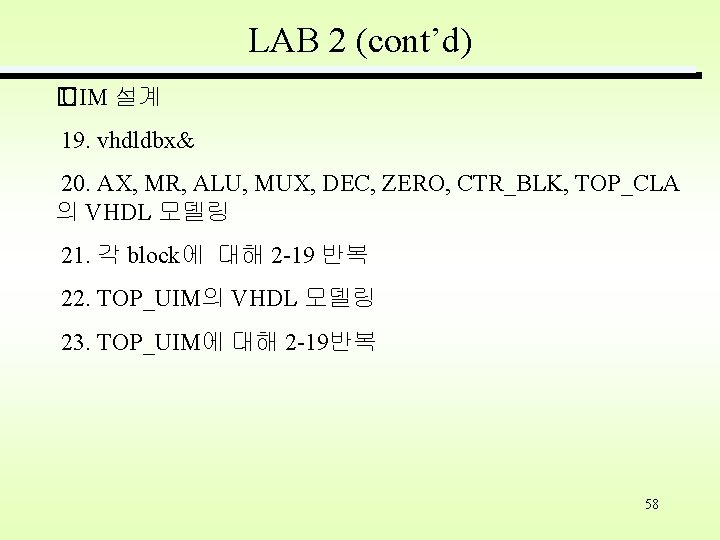

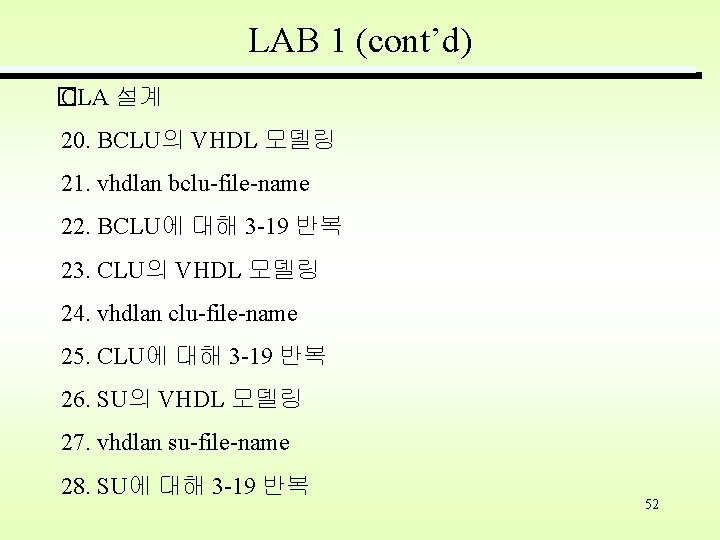

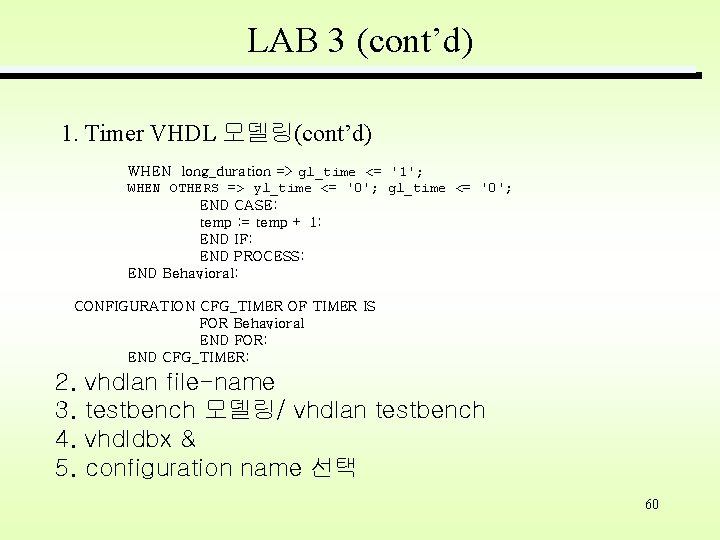

Synopsys 환경 Setup(cont’d) �. synopsys_sge 2 vhdl. setup 작성의 예 [Defaults] net_type = std_logic bus_type = std_logic_vector() work_lib = WORK model_lib = CLASS default_modellib_arch = FTGS use_lib_section = CLASS_Defaults default_sym_arch = BEHAVIORAL default_sch_arch = SCHEMATIC default_cfg = CFG_%E tb_entity = TB_FILE tb_arch = testbench tb_inst = UUT tb_cfg = CFG_TB_%E_%A 8

![Synopsys 환경 Setupcontd synopsyssge 2 vhdl setup 작성의 예 CLASSDefaults Synopsys 환경 Setup(cont’d) �. synopsys_sge 2 vhdl. setup 작성의 예 ……………. . . [CLASS_Defaults]](https://slidetodoc.com/presentation_image/103370fca6380966817e57c646ccdf80/image-9.jpg)

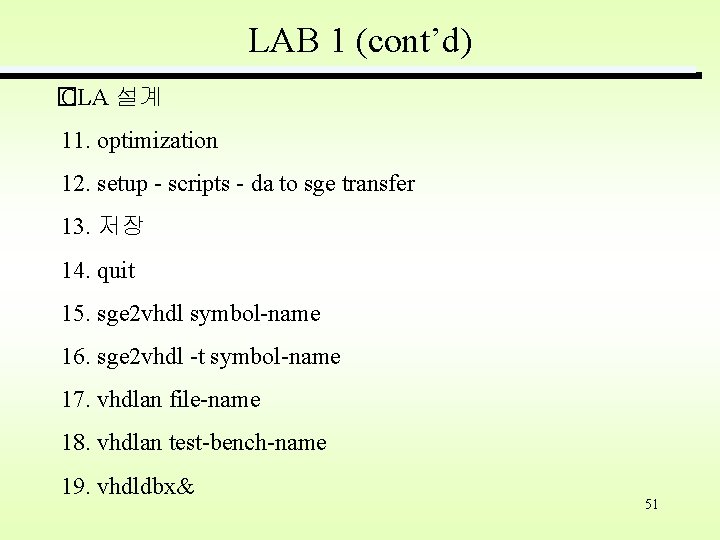

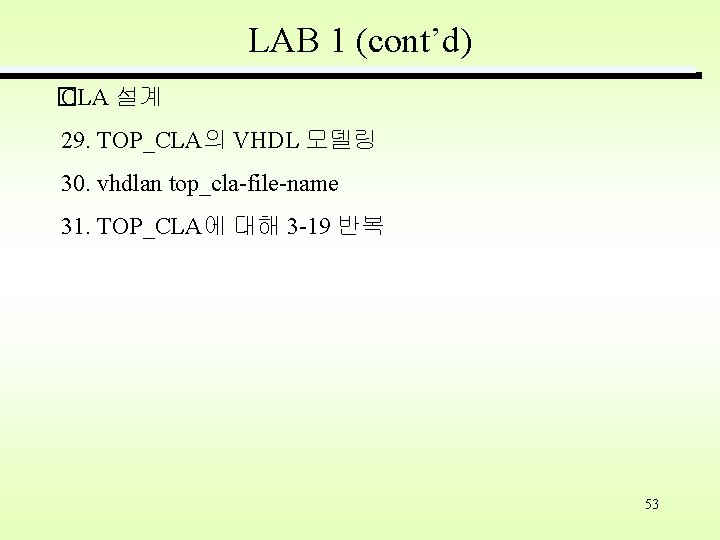

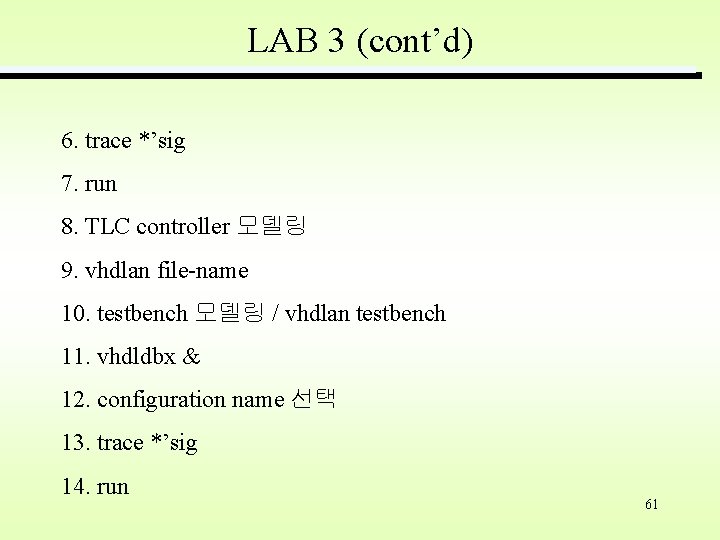

Synopsys 환경 Setup(cont’d) �. synopsys_sge 2 vhdl. setup 작성의 예 ……………. . . [CLASS_Defaults] library IEEE, CLASS; use IEEE. std_logic_1164. all; use CLASS. components. all; ……………. 9

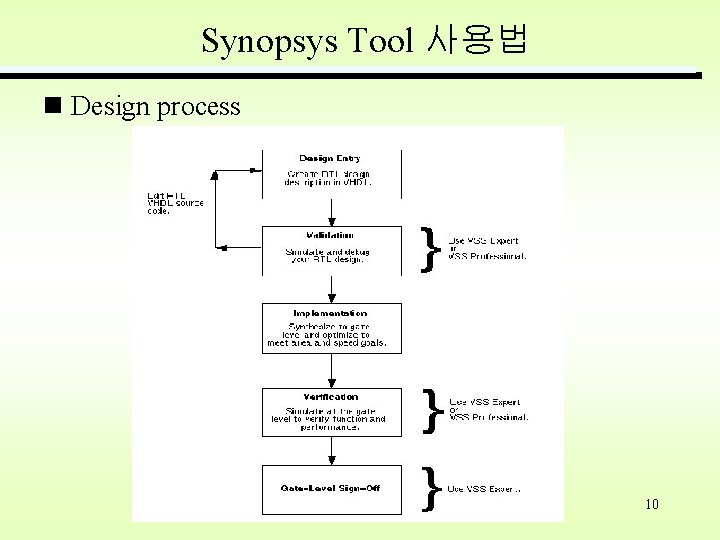

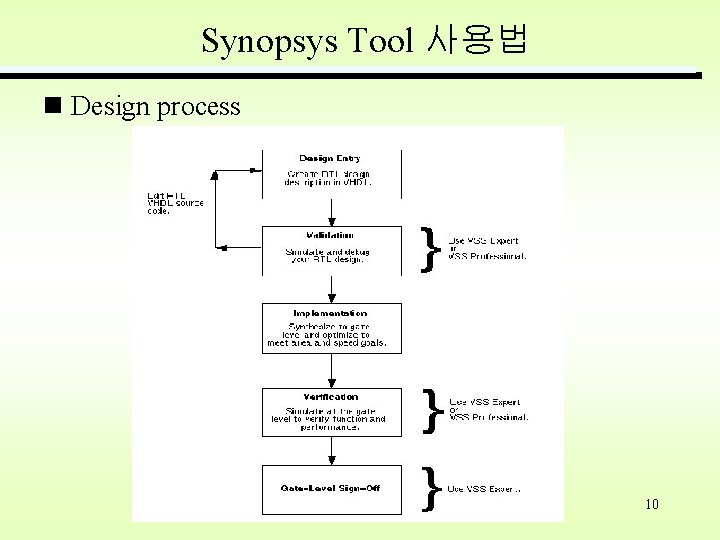

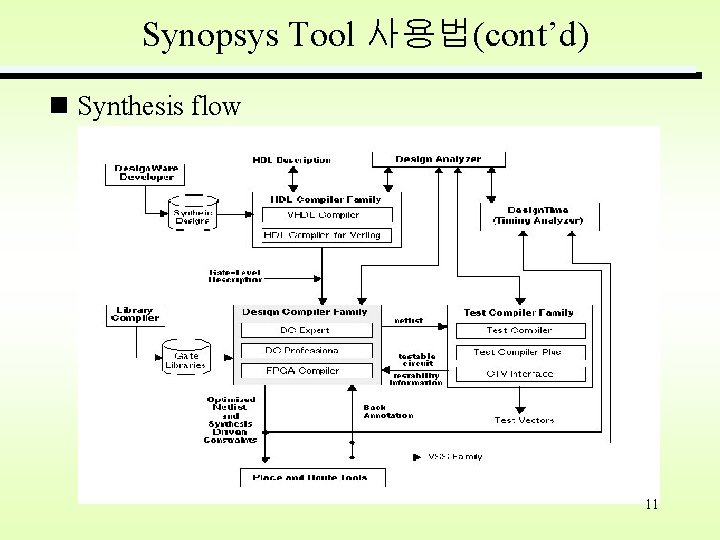

Synopsys Tool 사용법 Design process 10

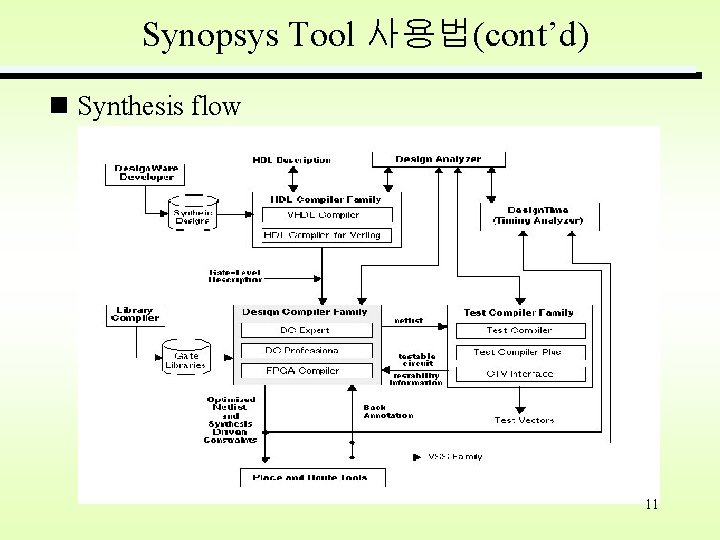

Synopsys Tool 사용법(cont’d) Synthesis flow 11

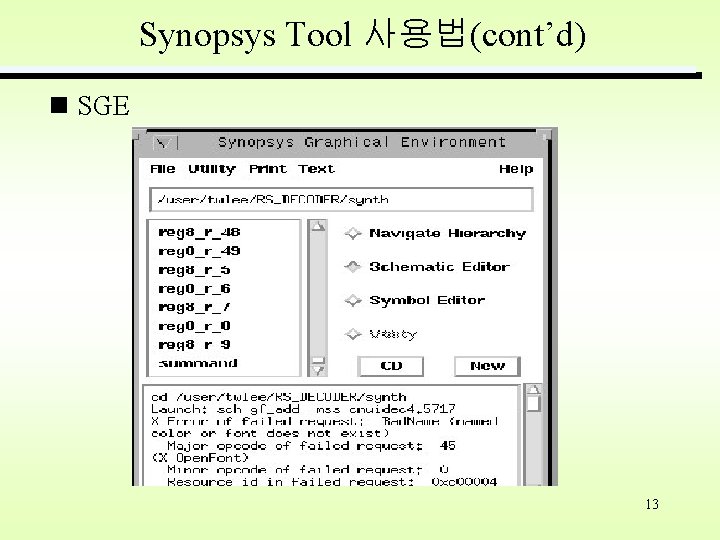

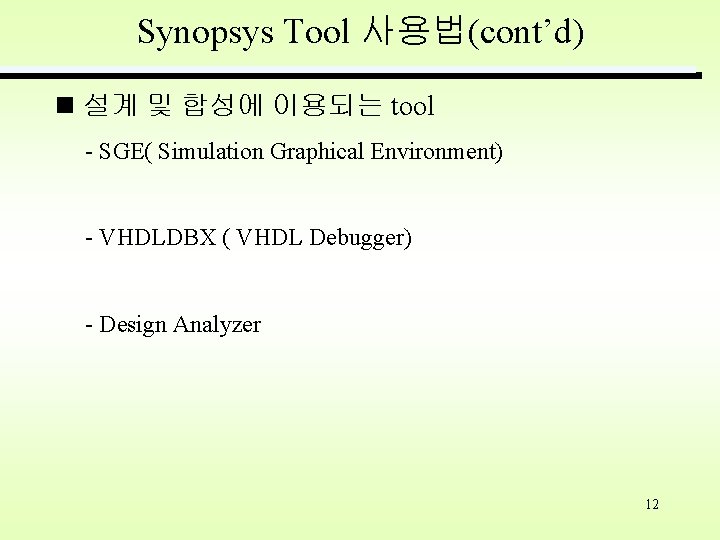

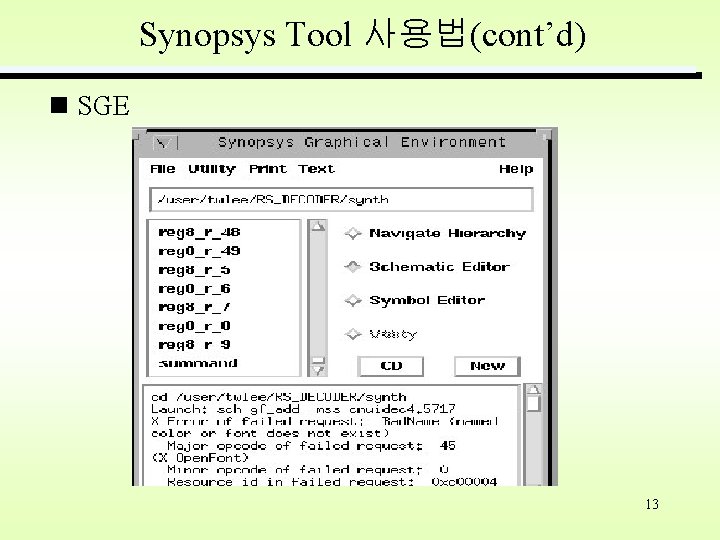

Synopsys Tool 사용법(cont’d) 설계 및 합성에 이용되는 tool - SGE( Simulation Graphical Environment) - VHDLDBX ( VHDL Debugger) - Design Analyzer 12

Synopsys Tool 사용법(cont’d) SGE 13

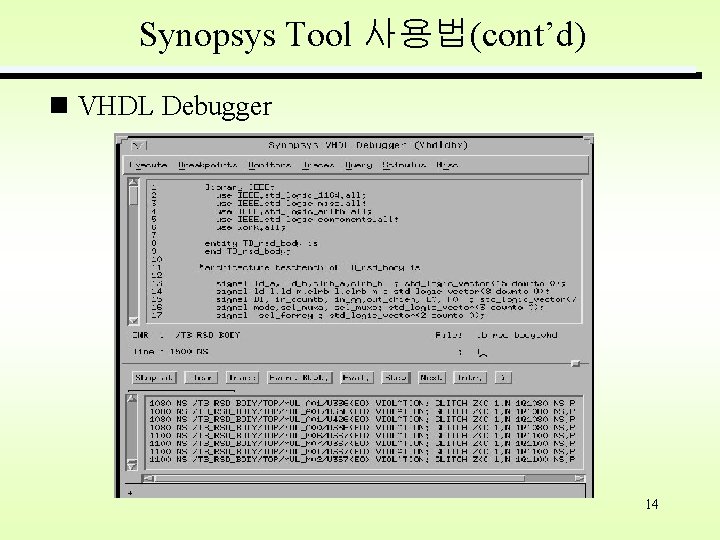

Synopsys Tool 사용법(cont’d) VHDL Debugger 14

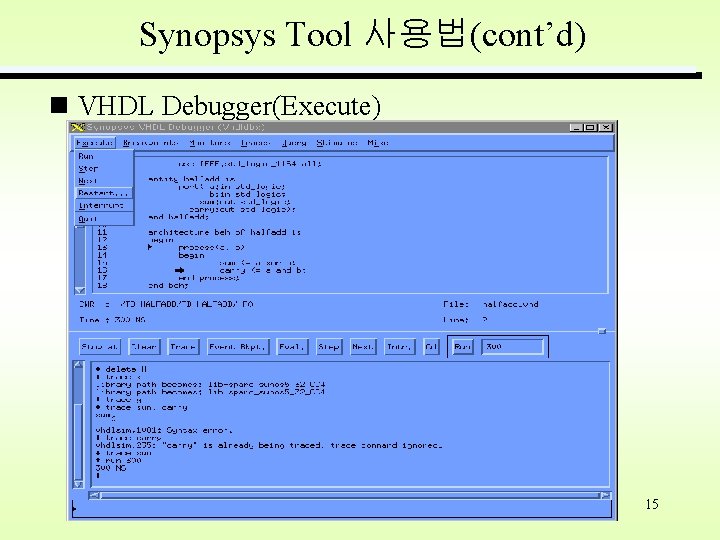

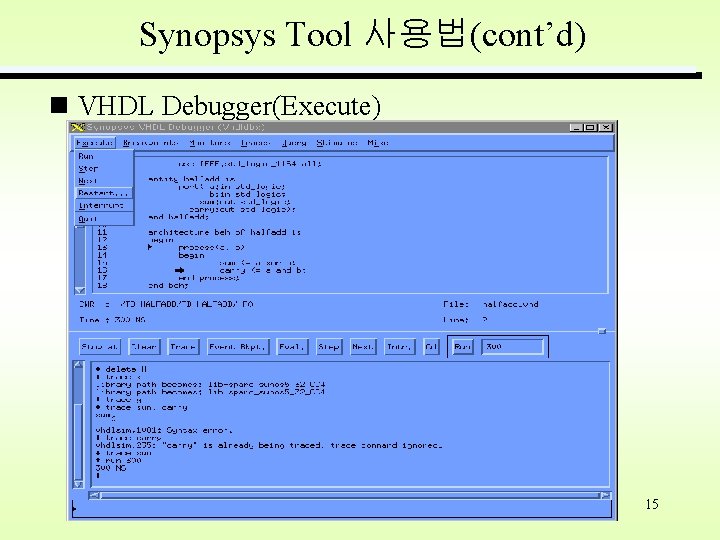

Synopsys Tool 사용법(cont’d) VHDL Debugger(Execute) 15

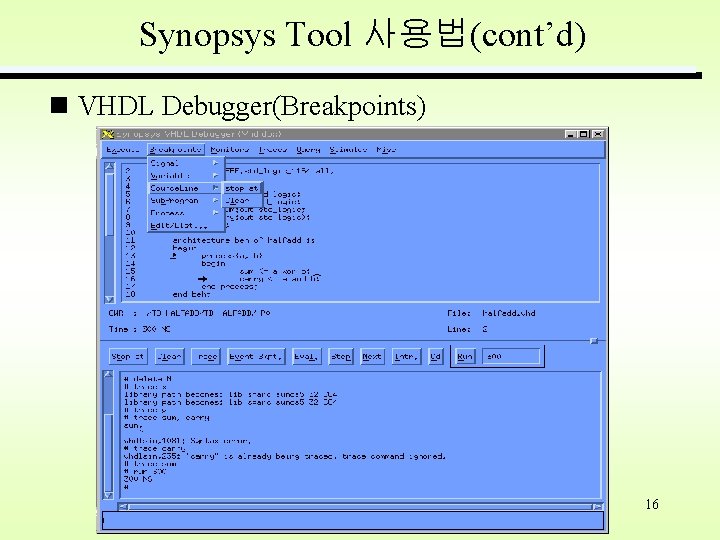

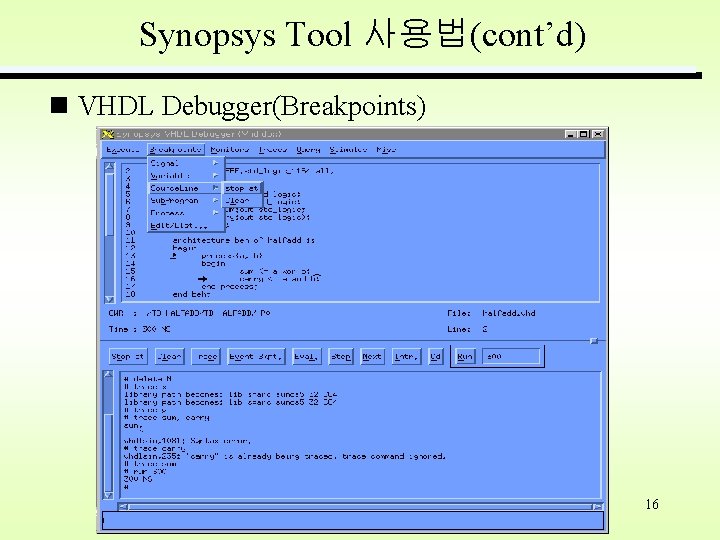

Synopsys Tool 사용법(cont’d) VHDL Debugger(Breakpoints) 16

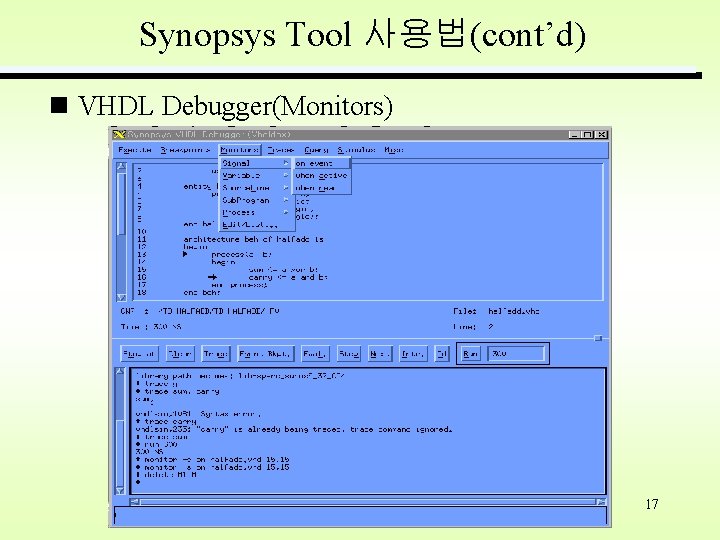

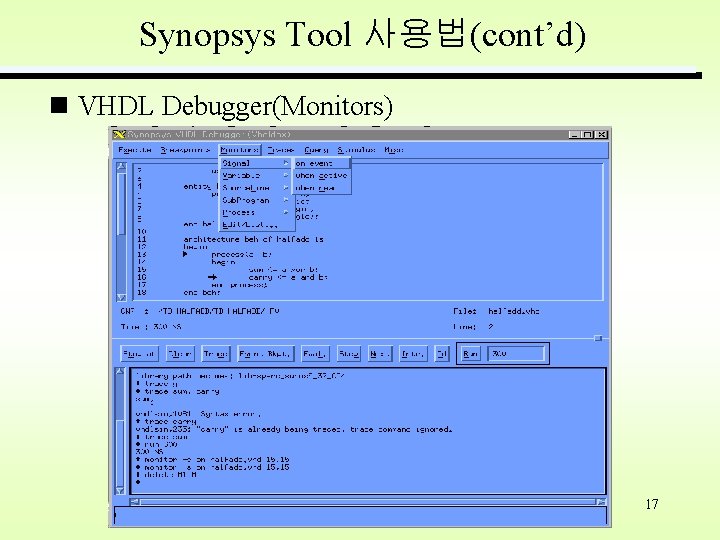

Synopsys Tool 사용법(cont’d) VHDL Debugger(Monitors) 17

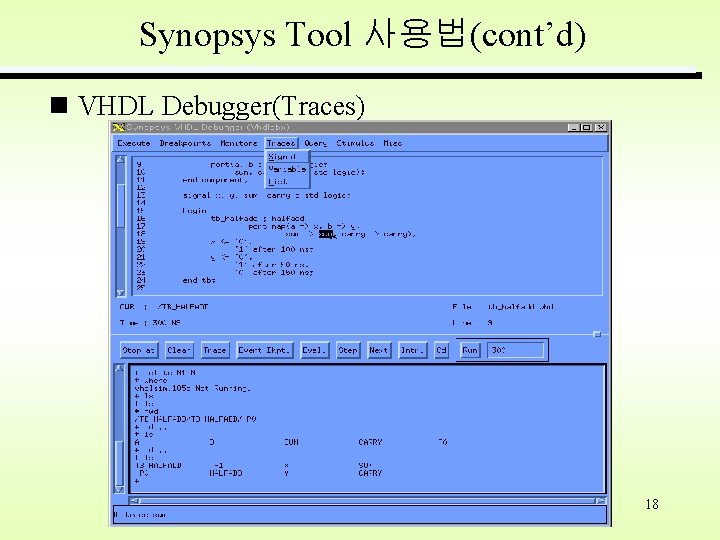

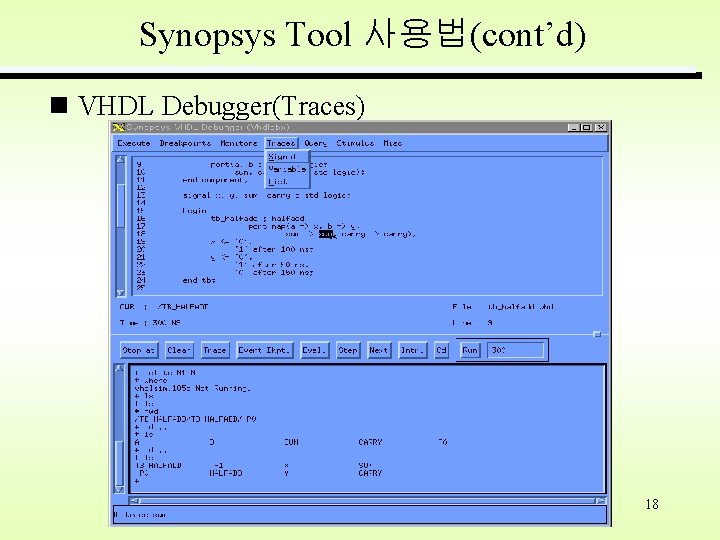

Synopsys Tool 사용법(cont’d) VHDL Debugger(Traces) 18

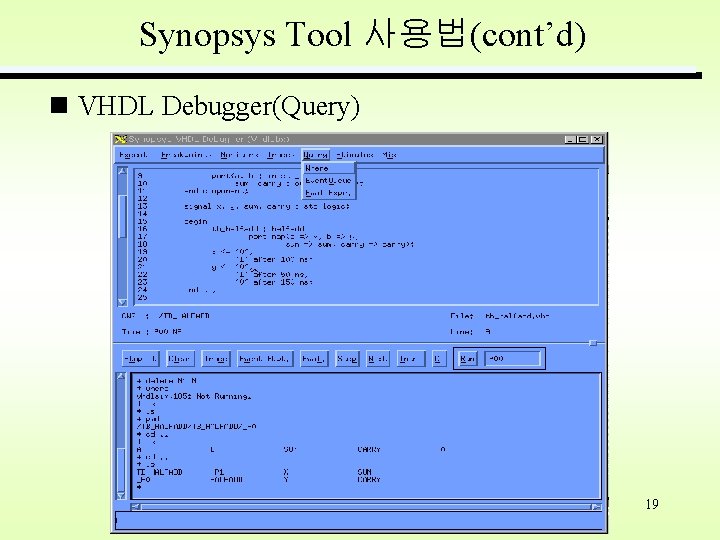

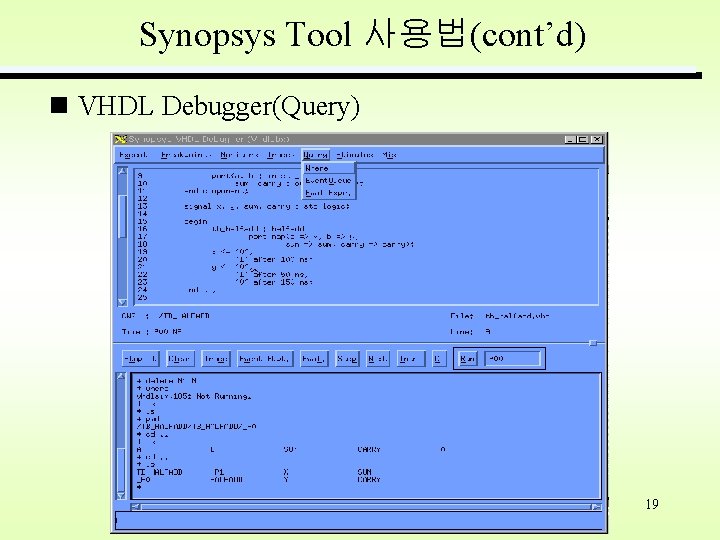

Synopsys Tool 사용법(cont’d) VHDL Debugger(Query) 19

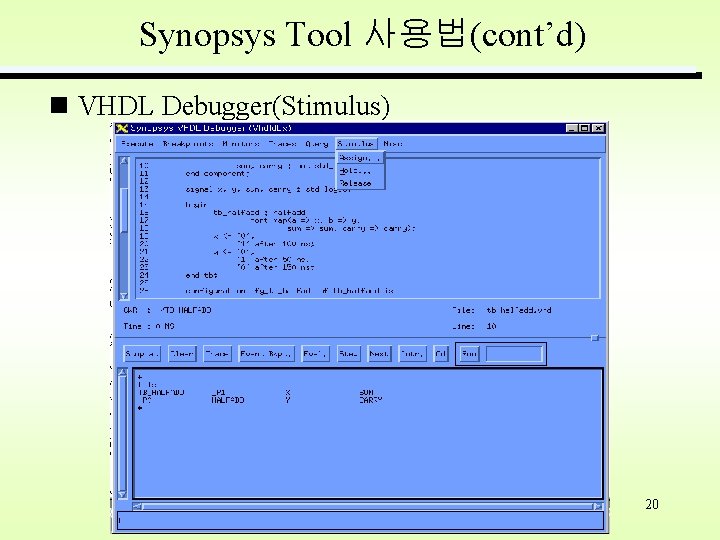

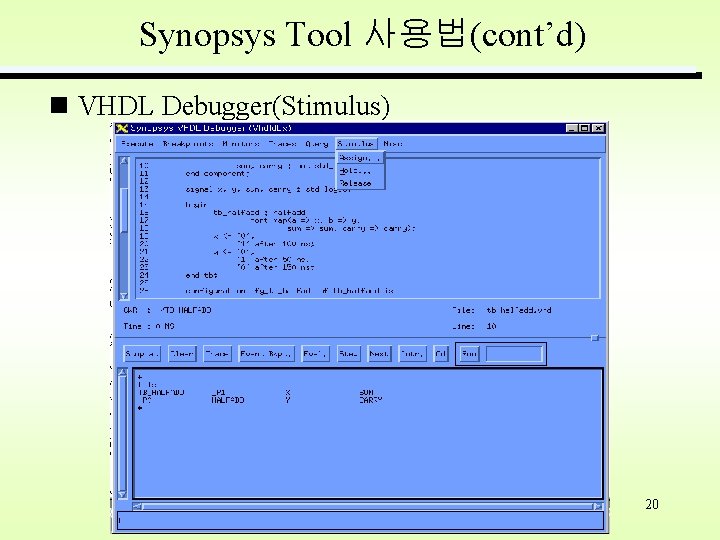

Synopsys Tool 사용법(cont’d) VHDL Debugger(Stimulus) 20

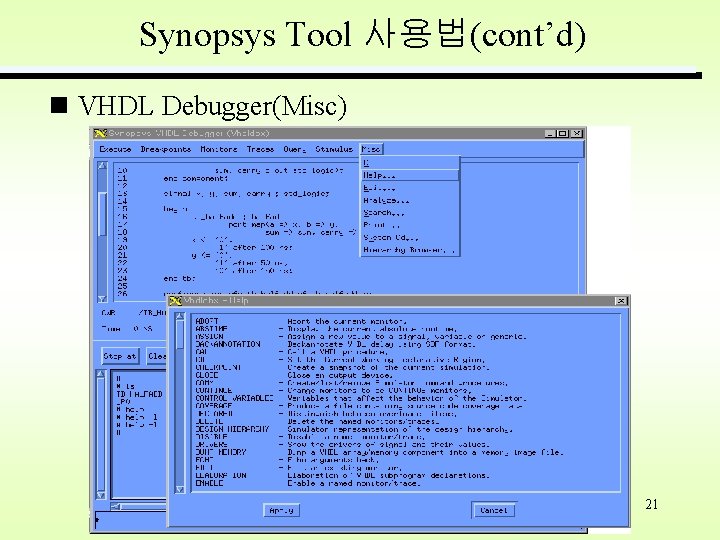

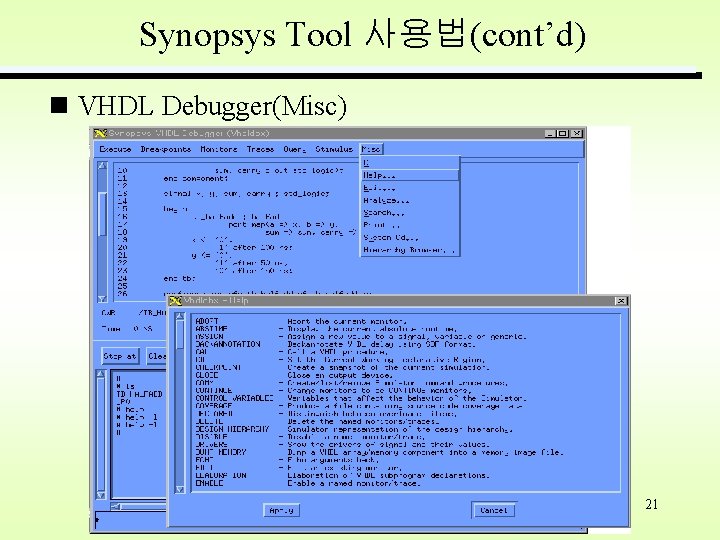

Synopsys Tool 사용법(cont’d) VHDL Debugger(Misc) 21

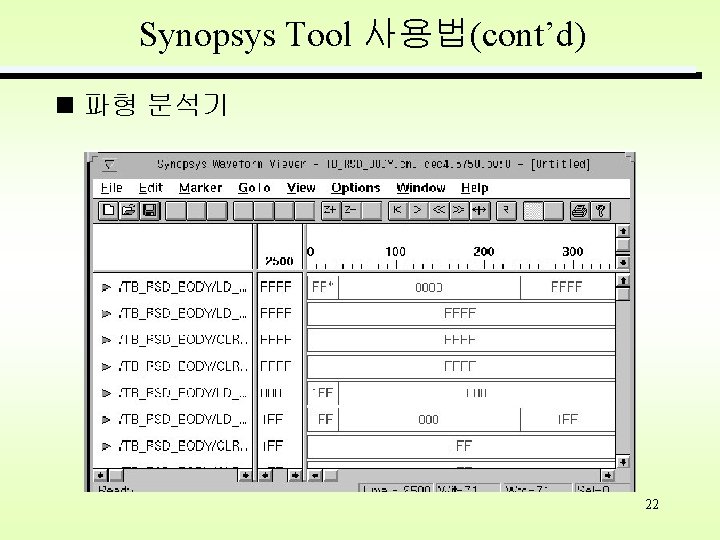

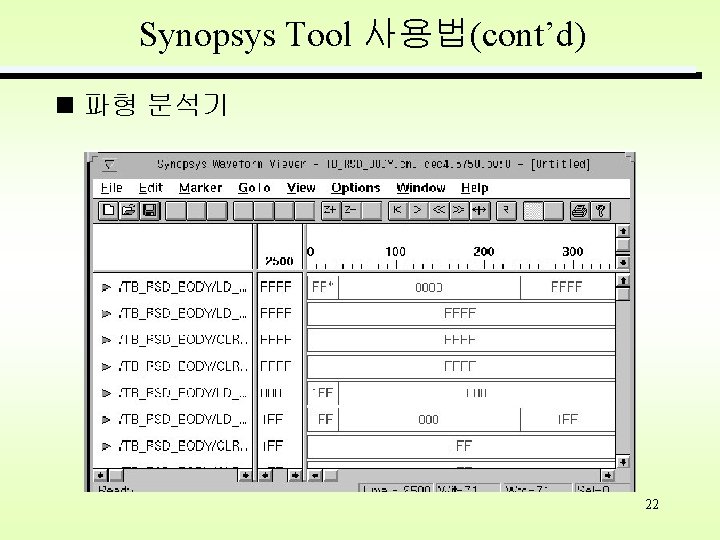

Synopsys Tool 사용법(cont’d) 파형 분석기 22

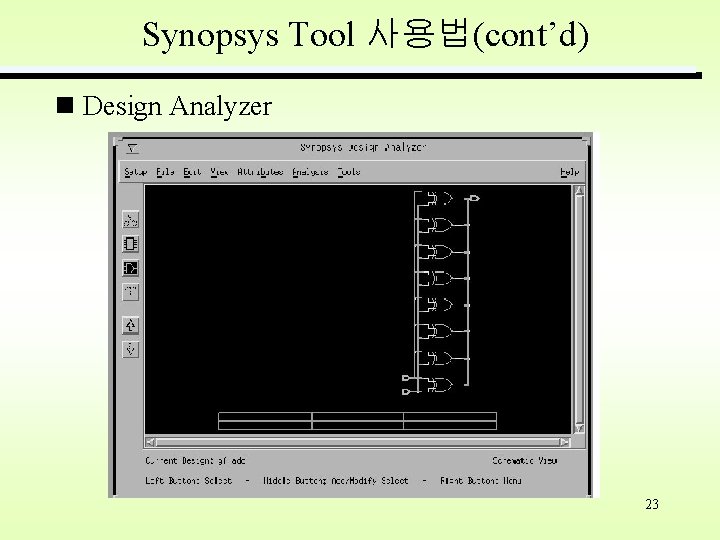

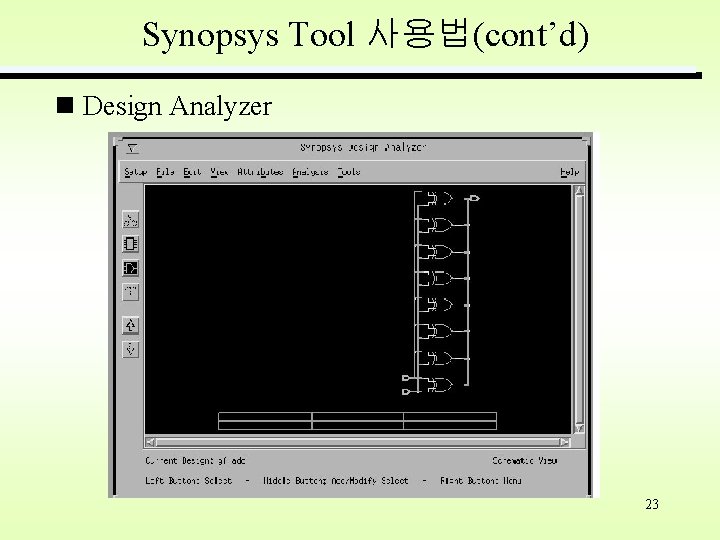

Synopsys Tool 사용법(cont’d) Design Analyzer 23

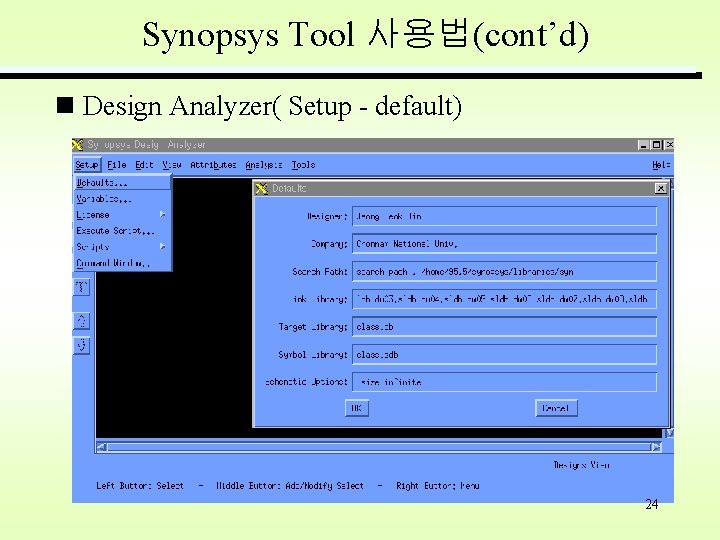

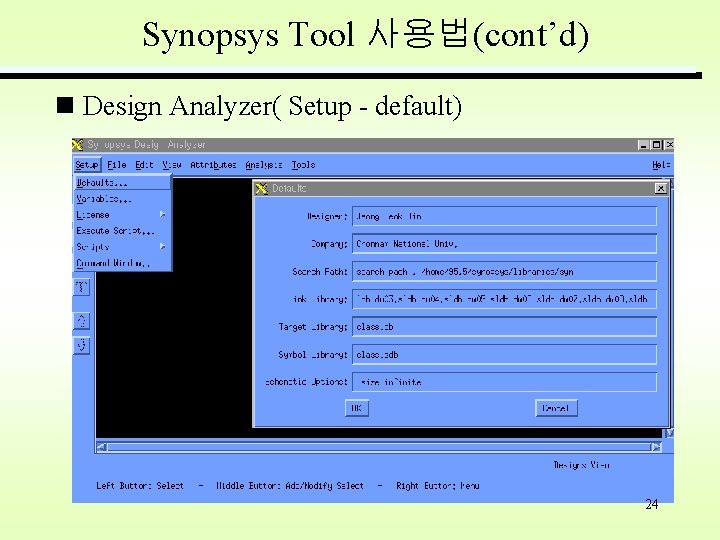

Synopsys Tool 사용법(cont’d) Design Analyzer( Setup - default) 24

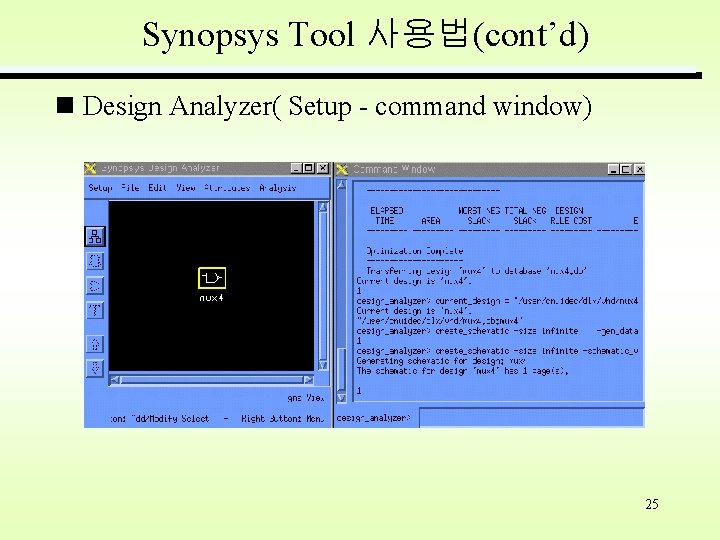

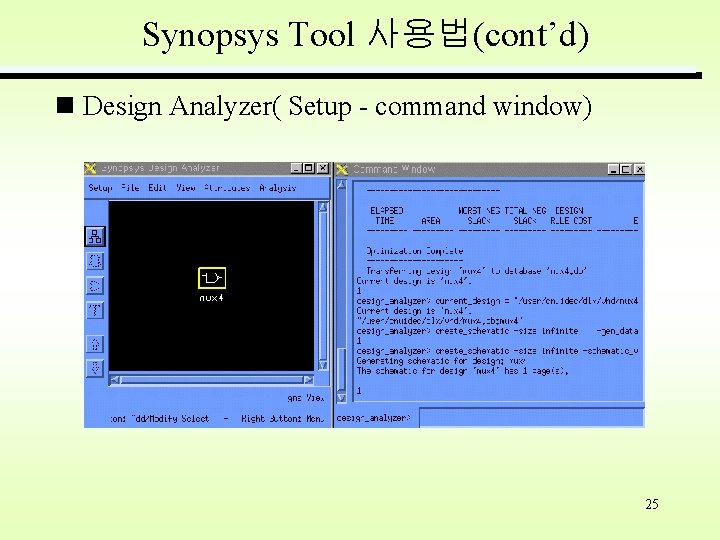

Synopsys Tool 사용법(cont’d) Design Analyzer( Setup - command window) 25

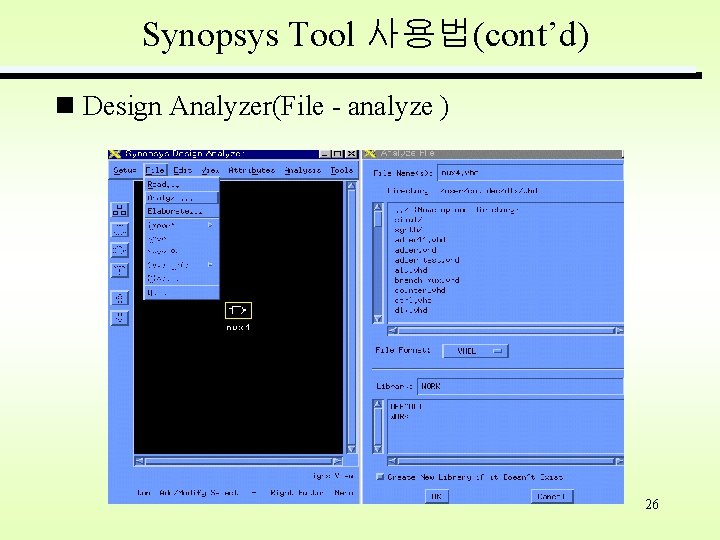

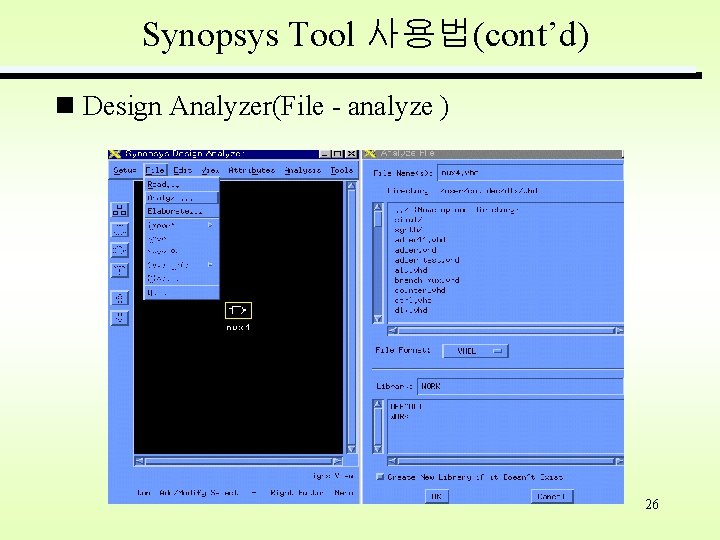

Synopsys Tool 사용법(cont’d) Design Analyzer(File - analyze ) 26

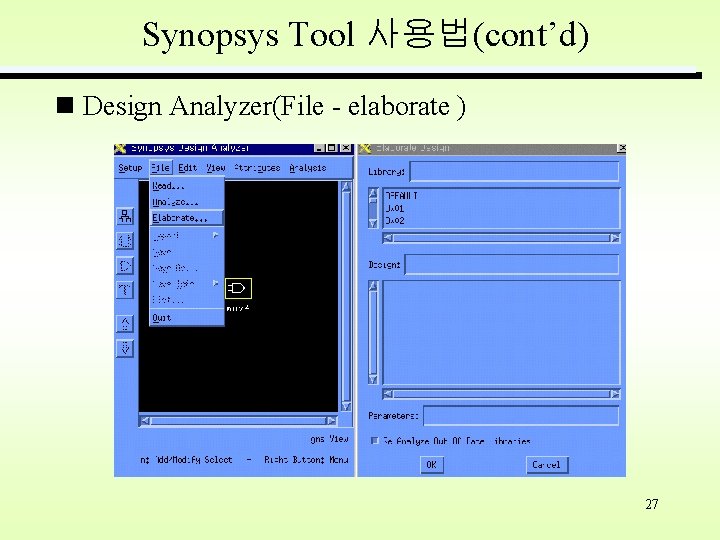

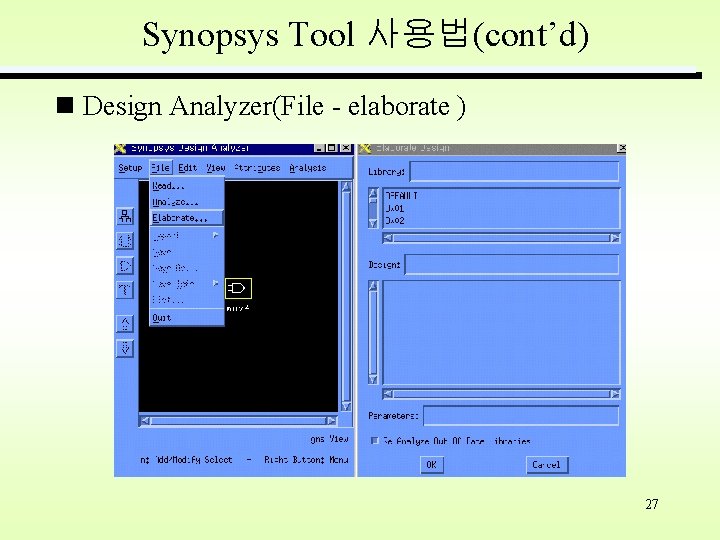

Synopsys Tool 사용법(cont’d) Design Analyzer(File - elaborate ) 27

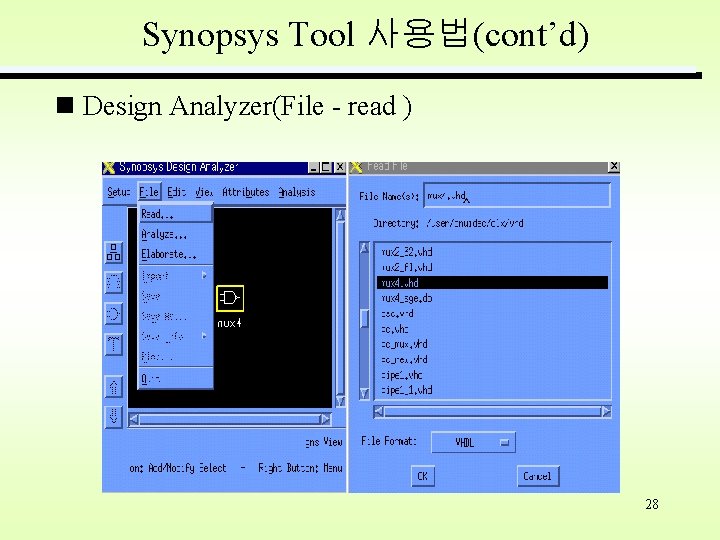

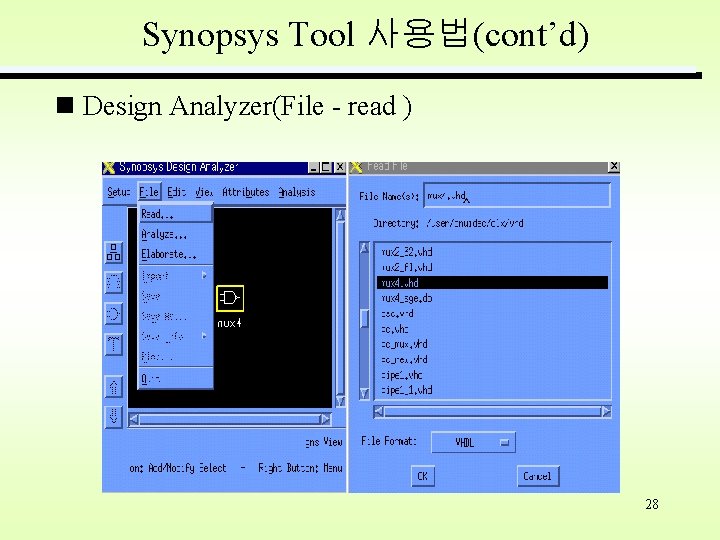

Synopsys Tool 사용법(cont’d) Design Analyzer(File - read ) 28

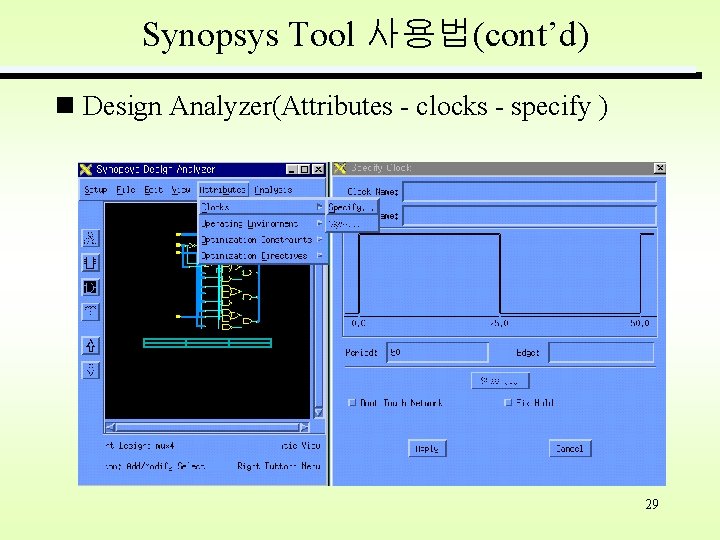

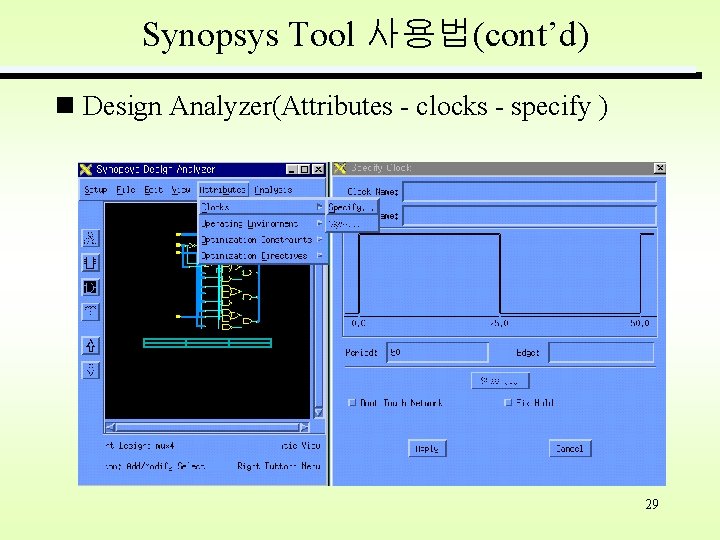

Synopsys Tool 사용법(cont’d) Design Analyzer(Attributes - clocks - specify ) 29

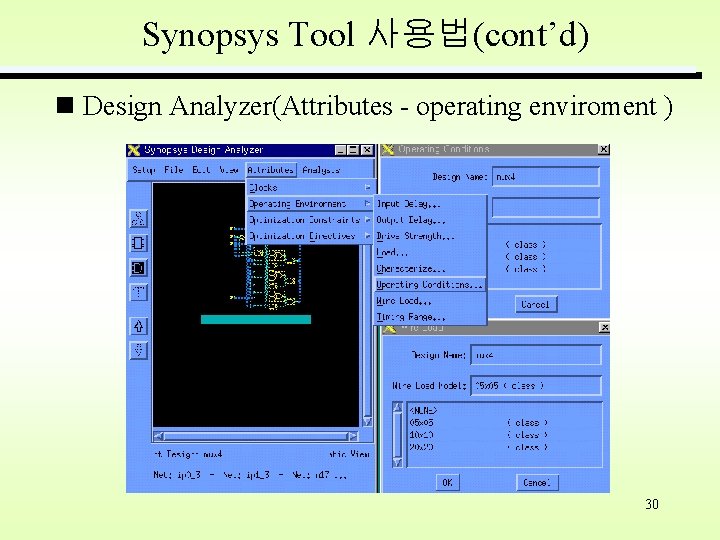

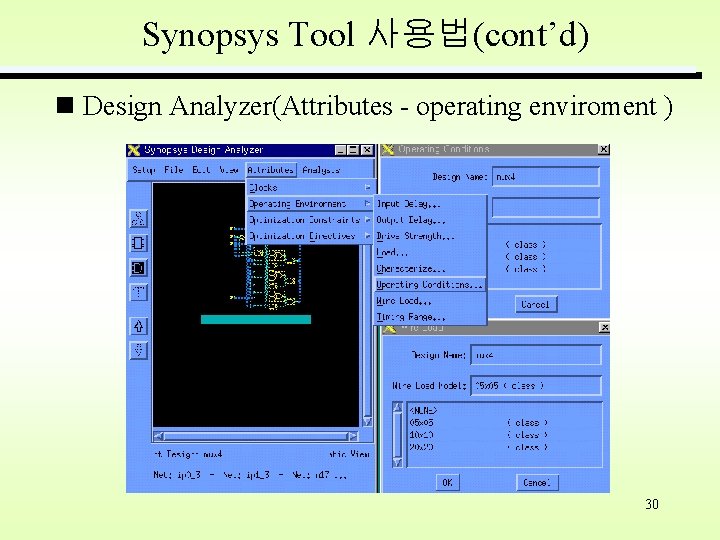

Synopsys Tool 사용법(cont’d) Design Analyzer(Attributes - operating enviroment ) 30

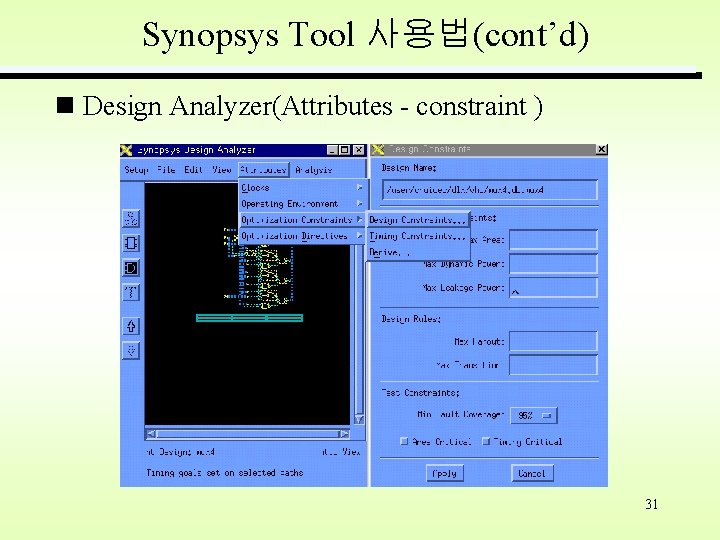

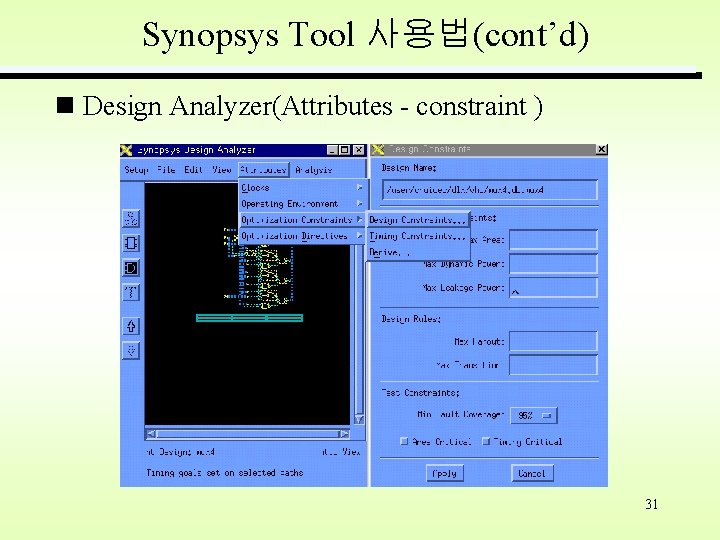

Synopsys Tool 사용법(cont’d) Design Analyzer(Attributes - constraint ) 31

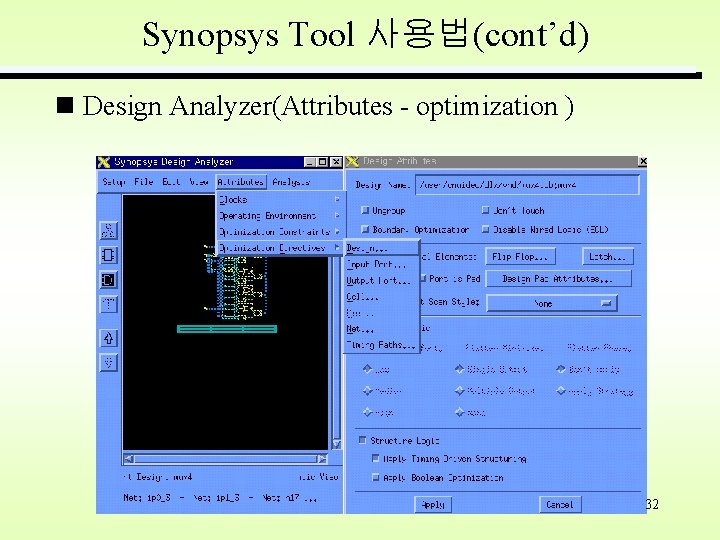

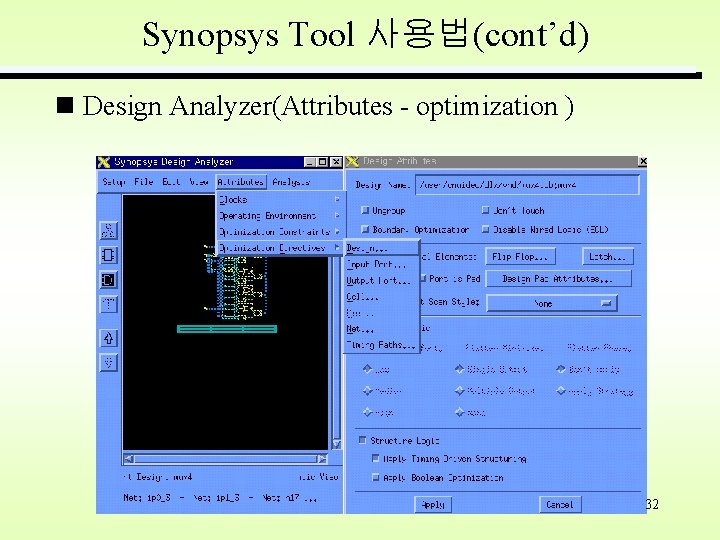

Synopsys Tool 사용법(cont’d) Design Analyzer(Attributes - optimization ) 32

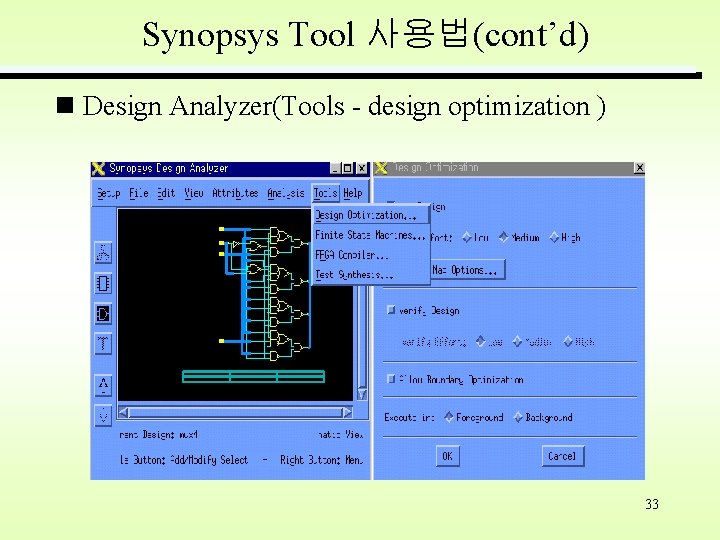

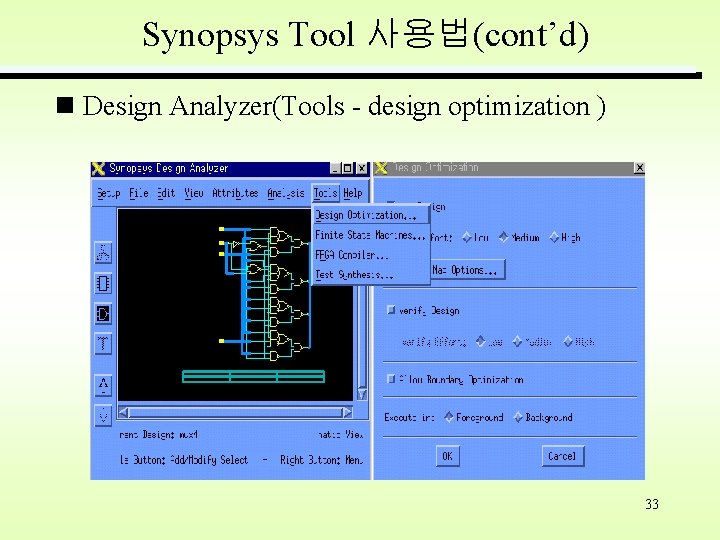

Synopsys Tool 사용법(cont’d) Design Analyzer(Tools - design optimization ) 33

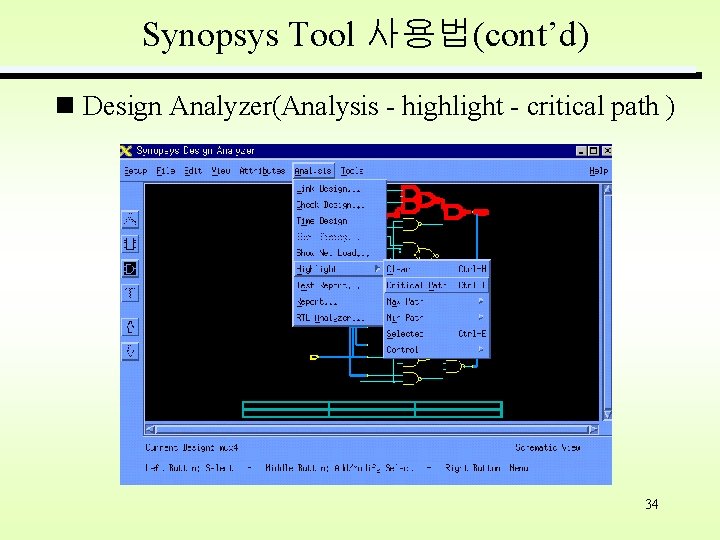

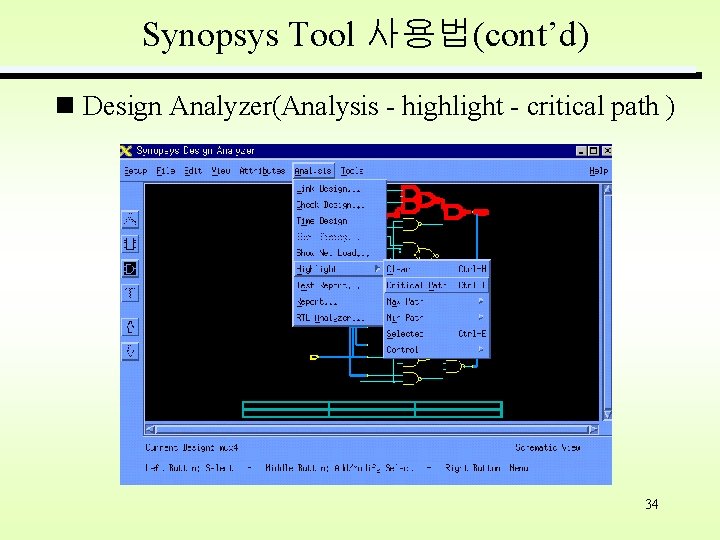

Synopsys Tool 사용법(cont’d) Design Analyzer(Analysis - highlight - critical path ) 34

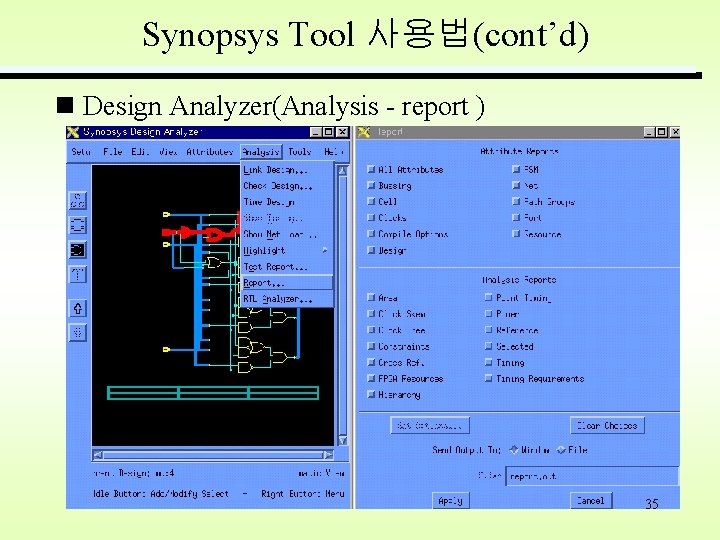

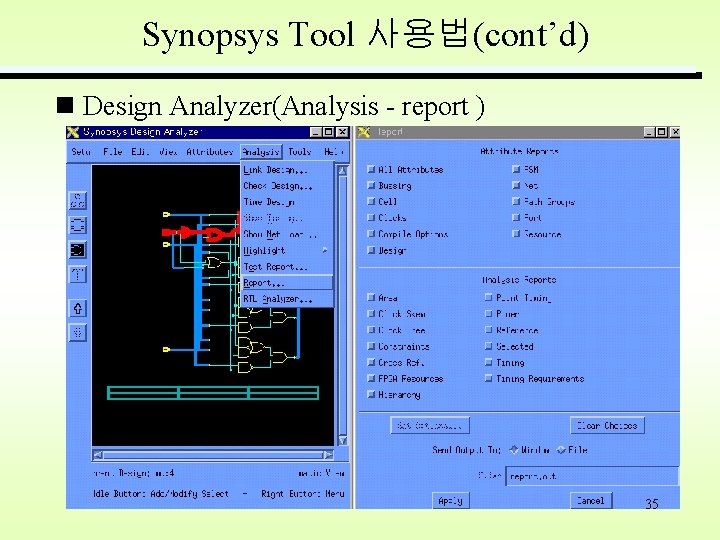

Synopsys Tool 사용법(cont’d) Design Analyzer(Analysis - report ) 35

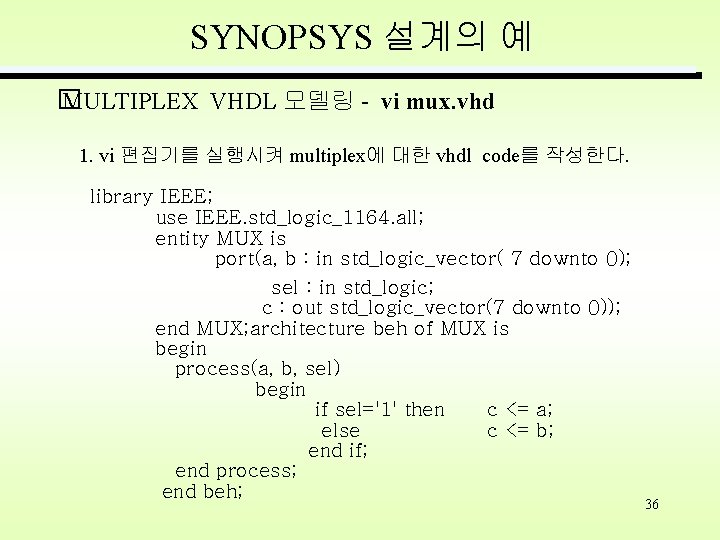

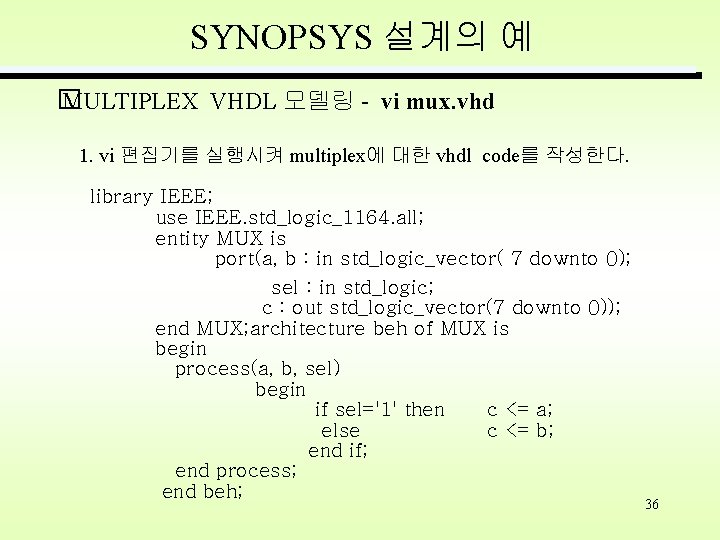

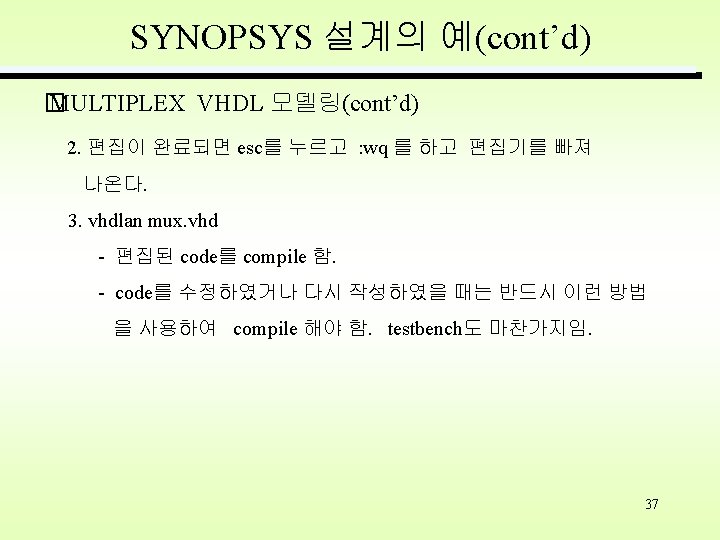

SYNOPSYS 설계의 예 � MULTIPLEX VHDL 모델링 - vi mux. vhd 1. vi 편집기를 실행시켜 multiplex에 대한 vhdl code를 작성한다. library IEEE; use IEEE. std_logic_1164. all; entity MUX is port(a, b : in std_logic_vector( 7 downto 0); sel : in std_logic; c : out std_logic_vector(7 downto 0)); end MUX; architecture beh of MUX is begin process(a, b, sel) begin if sel='1' then c <= a; else c <= b; end if; end process; end beh; 36

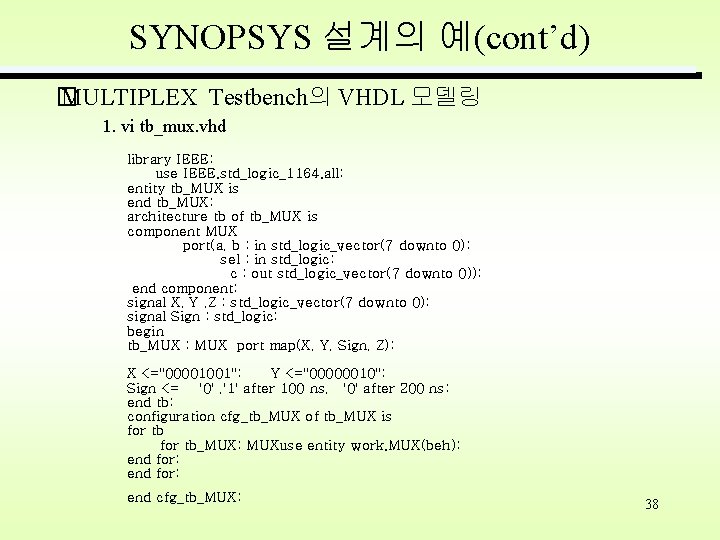

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX Testbench의 VHDL 모델링 1. vi tb_mux. vhd library IEEE; use IEEE. std_logic_1164. all; entity tb_MUX is end tb_MUX; architecture tb of tb_MUX is component MUX port(a, b : in std_logic_vector(7 downto 0); sel : in std_logic; c : out std_logic_vector(7 downto 0)); end component; signal X, Y , Z : std_logic_vector(7 downto 0); signal Sign : std_logic; begin tb_MUX : MUX port map(X, Y, Sign, Z); X <="00001001"; Y <="00000010"; Sign <= '0' , '1' after 100 ns, '0' after 200 ns; end tb; configuration cfg_tb_MUX of tb_MUX is for tb_MUX: MUXuse entity work. MUX(beh); end for; end cfg_tb_MUX; 38

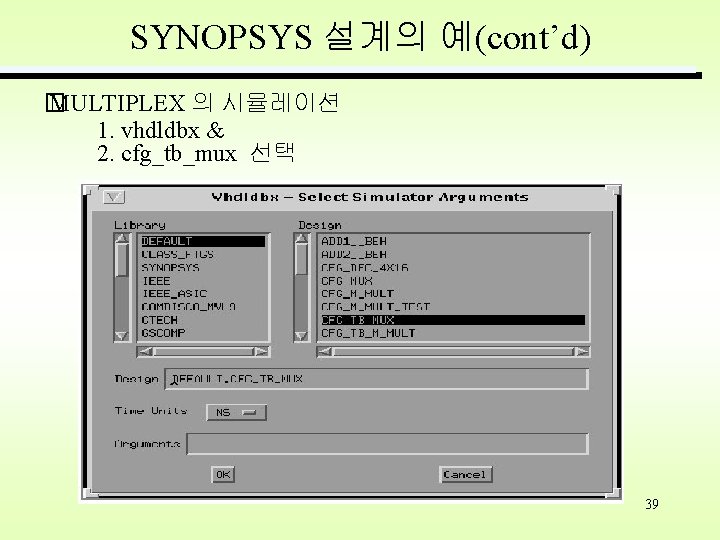

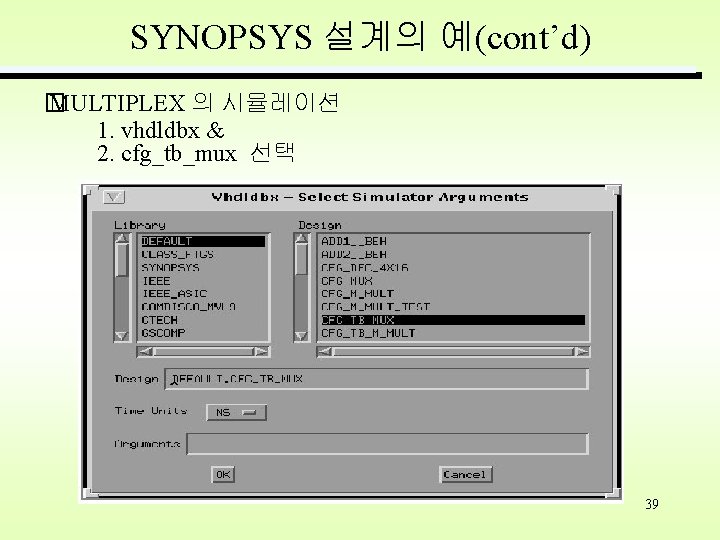

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 시뮬레이션 1. vhdldbx & 2. cfg_tb_mux 선택 39

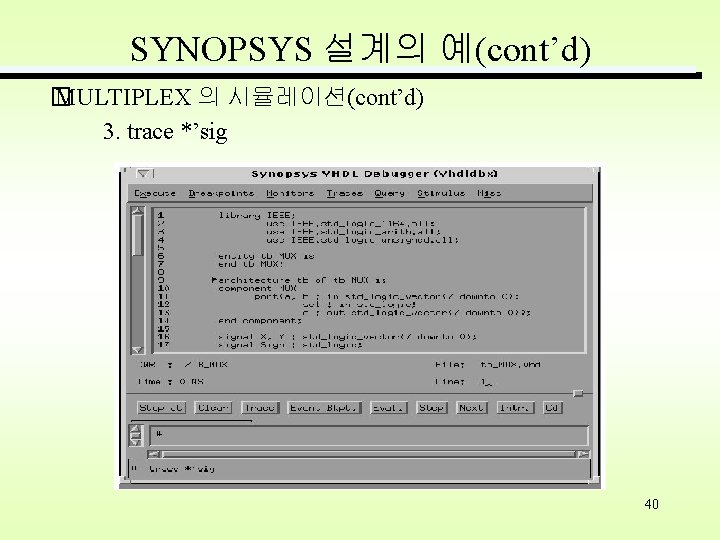

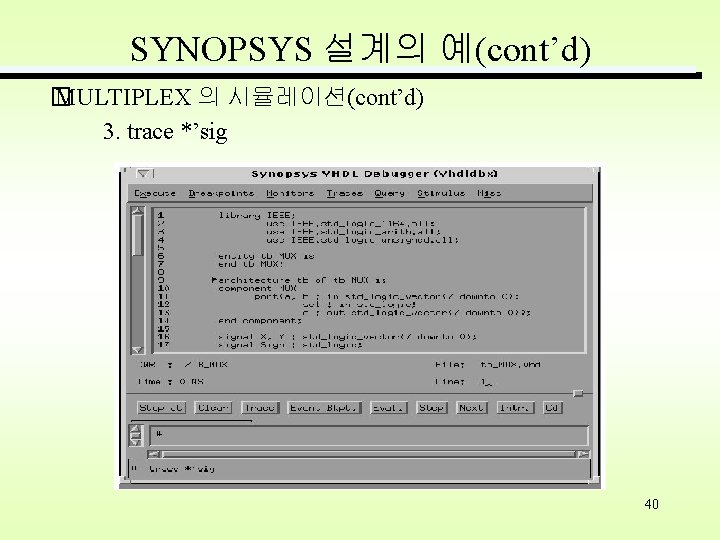

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 시뮬레이션(cont’d) 3. trace *’sig 40

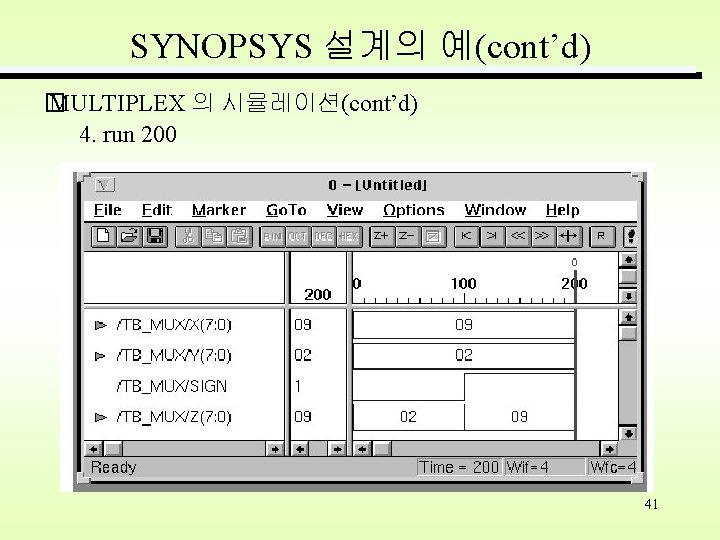

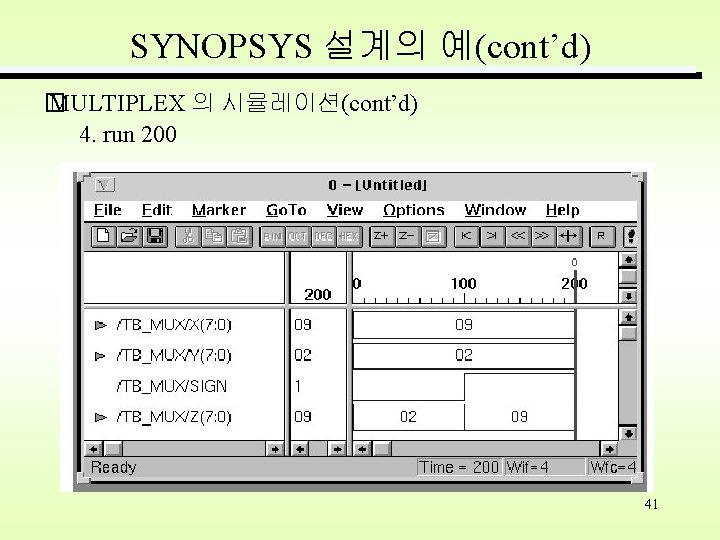

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 시뮬레이션(cont’d) 4. run 200 41

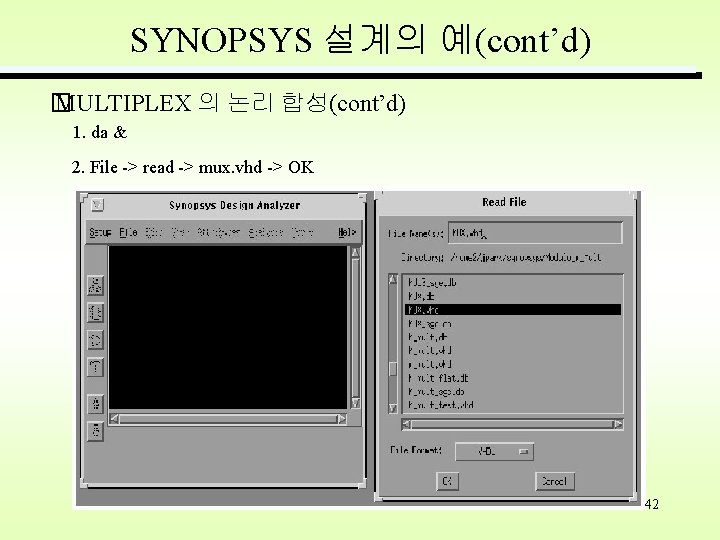

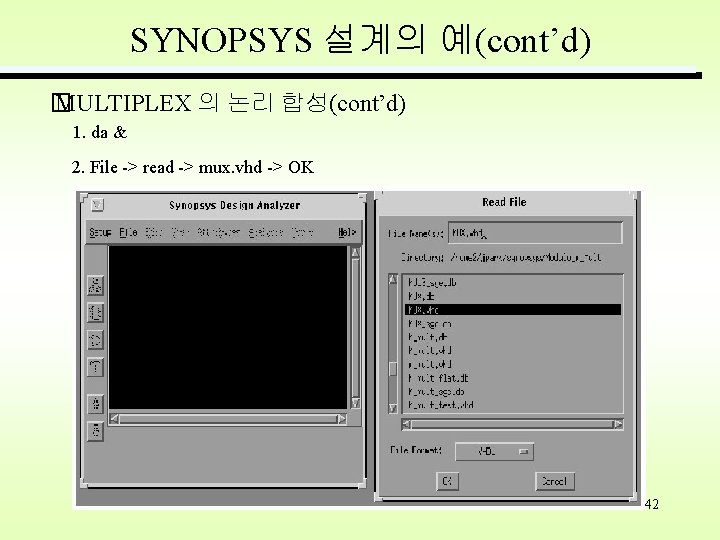

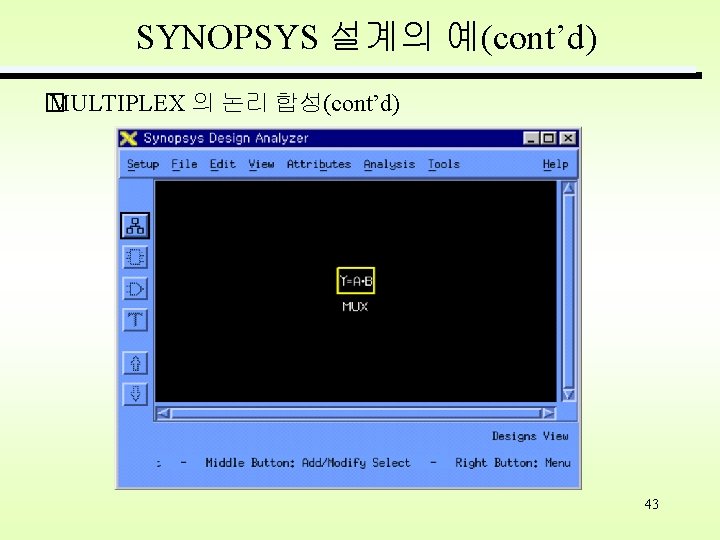

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 논리 합성(cont’d) 1. da & 2. File -> read -> mux. vhd -> OK 42

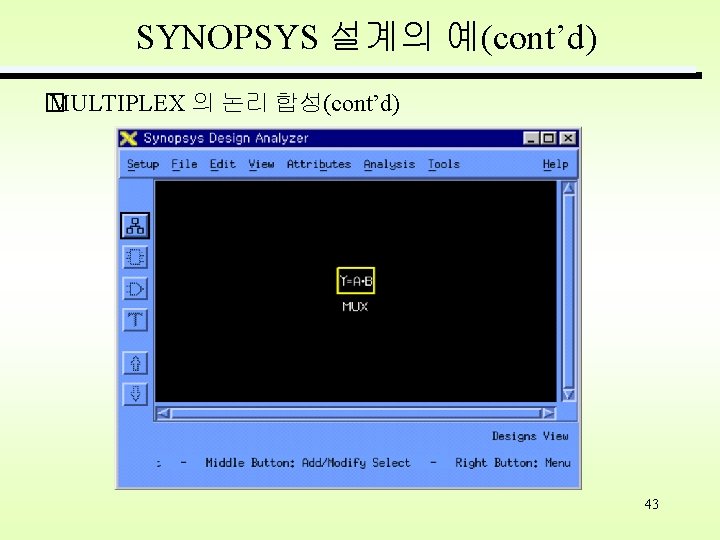

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 논리 합성(cont’d) 43

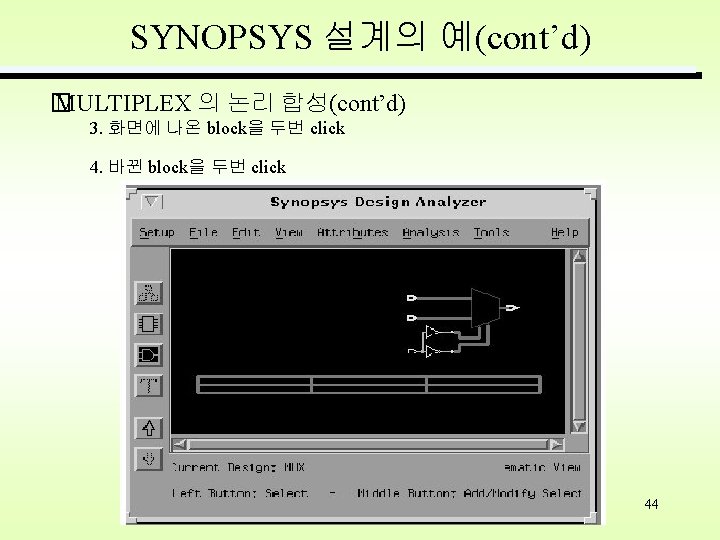

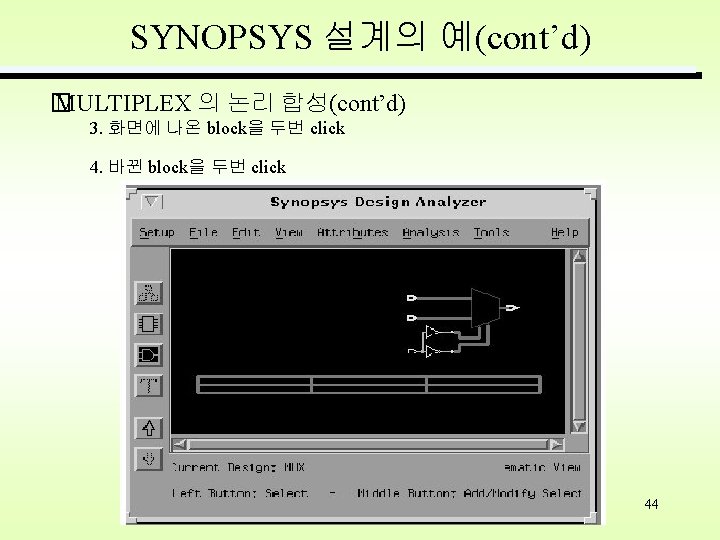

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 논리 합성(cont’d) 3. 화면에 나온 block을 두번 click 4. 바뀐 block을 두번 click 44

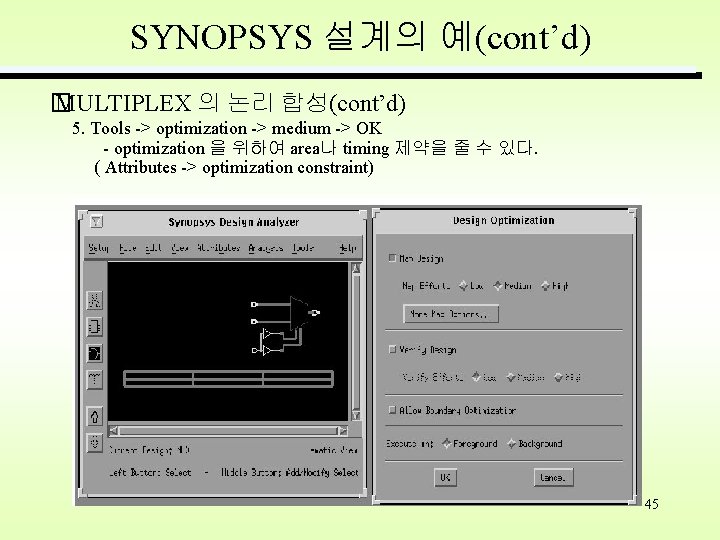

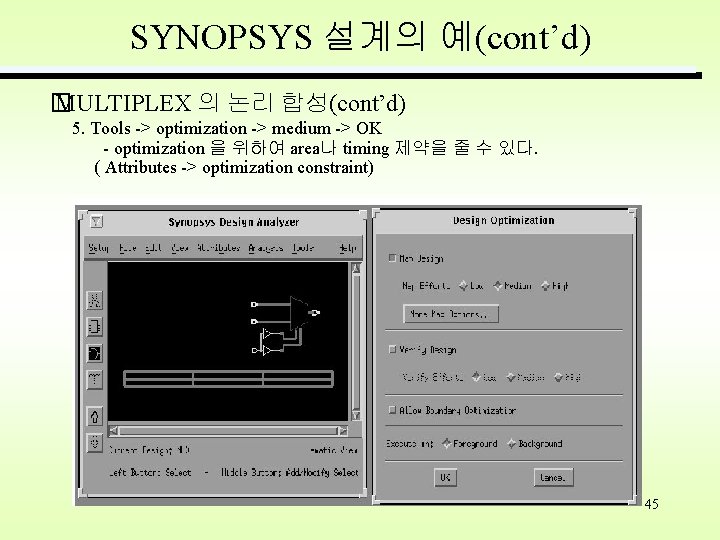

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 논리 합성(cont’d) 5. Tools -> optimization -> medium -> OK - optimization 을 위하여 area나 timing 제약을 줄 수 있다. ( Attributes -> optimization constraint) 45

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 논리 합성(cont’d) 46

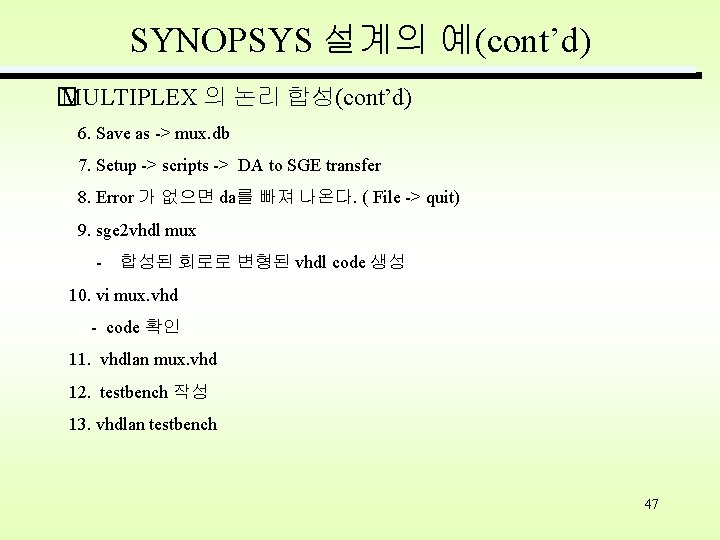

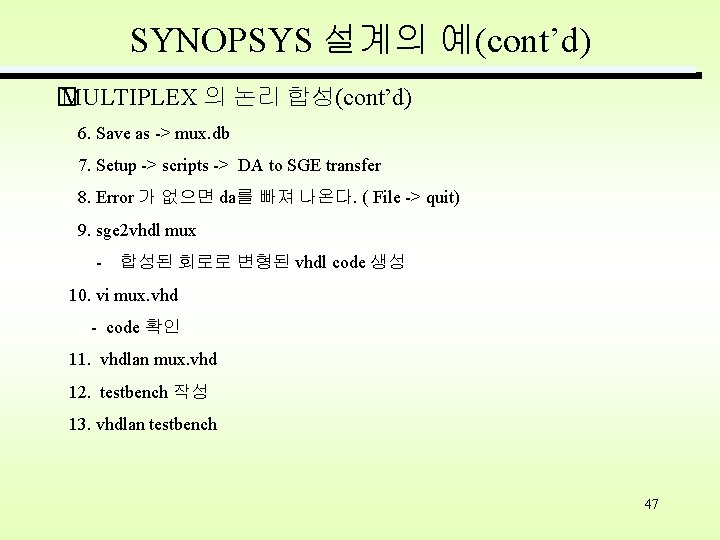

SYNOPSYS 설계의 예(cont’d) � MULTIPLEX 의 논리 합성(cont’d) 6. Save as -> mux. db 7. Setup -> scripts -> DA to SGE transfer 8. Error 가 없으면 da를 빠져 나온다. ( File -> quit) 9. sge 2 vhdl mux - 합성된 회로로 변형된 vhdl code 생성 10. vi mux. vhd - code 확인 11. vhdlan mux. vhd 12. testbench 작성 13. vhdlan testbench 47

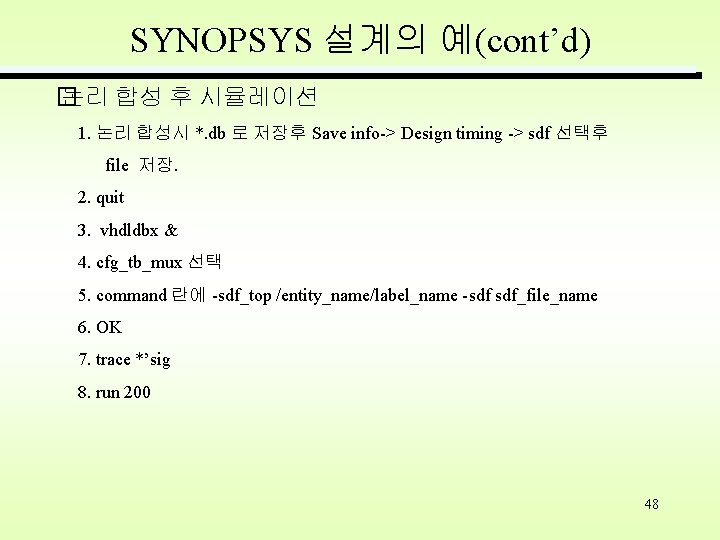

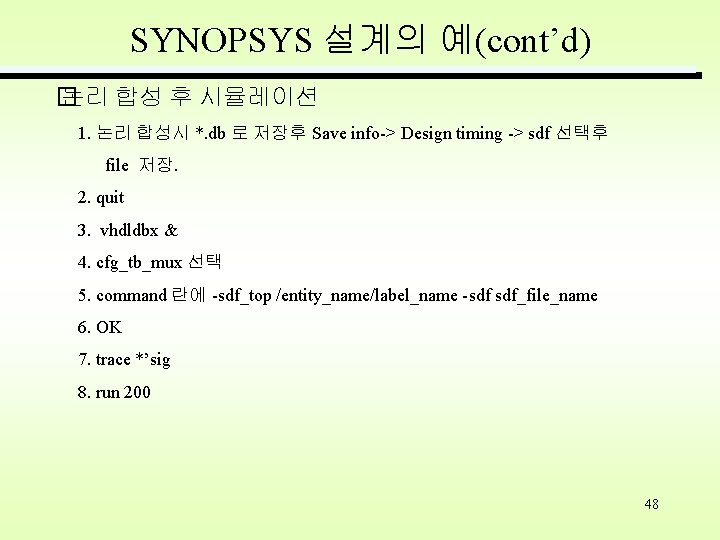

SYNOPSYS 설계의 예(cont’d) � 논리 합성 후 시뮬레이션 1. 논리 합성시 *. db 로 저장후 Save info-> Design timing -> sdf 선택후 file 저장. 2. quit 3. vhdldbx & 4. cfg_tb_mux 선택 5. command 란에 -sdf_top /entity_name/label_name -sdf sdf_file_name 6. OK 7. trace *’sig 8. run 200 48

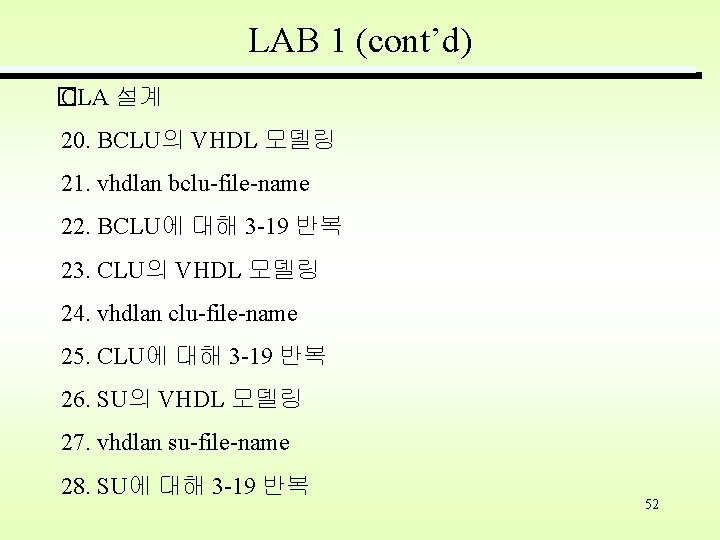

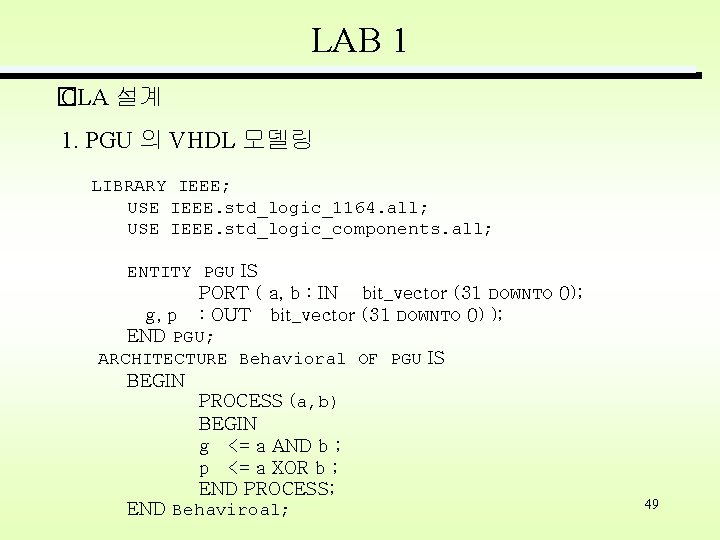

LAB 1 � CLA 설계 1. PGU 의 VHDL 모델링 LIBRARY IEEE; USE IEEE. std_logic_1164. all; USE IEEE. std_logic_components. all; ENTITY PGU IS PORT ( a, b : IN bit_vector (31 DOWNTO 0); g, p : OUT bit_vector (31 DOWNTO 0) ); END PGU; ARCHITECTURE Behavioral OF PGU IS BEGIN PROCESS (a, b) BEGIN g <= a AND b ; p <= a XOR b ; END PROCESS; END Behaviroal; 49

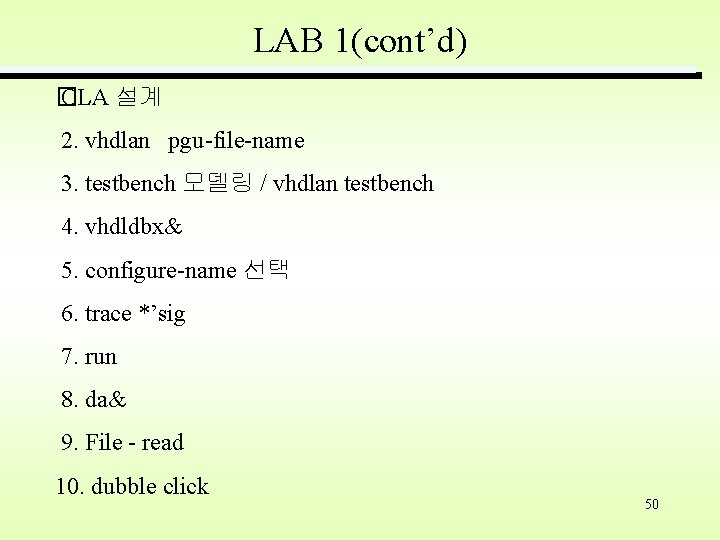

LAB 1(cont’d) � CLA 설계 2. vhdlan pgu-file-name 3. testbench 모델링 / vhdlan testbench 4. vhdldbx& 5. configure-name 선택 6. trace *’sig 7. run 8. da& 9. File - read 10. dubble click 50

LAB 1 (cont’d) � CLA 설계 11. optimization 12. setup - scripts - da to sge transfer 13. 저장 14. quit 15. sge 2 vhdl symbol-name 16. sge 2 vhdl -t symbol-name 17. vhdlan file-name 18. vhdlan test-bench-name 19. vhdldbx& 51

LAB 1 (cont’d) � CLA 설계 20. BCLU의 VHDL 모델링 21. vhdlan bclu-file-name 22. BCLU에 대해 3 -19 반복 23. CLU의 VHDL 모델링 24. vhdlan clu-file-name 25. CLU에 대해 3 -19 반복 26. SU의 VHDL 모델링 27. vhdlan su-file-name 28. SU에 대해 3 -19 반복 52

LAB 1 (cont’d) � CLA 설계 29. TOP_CLA의 VHDL 모델링 30. vhdlan top_cla-file-name 31. TOP_CLA에 대해 3 -19 반복 53

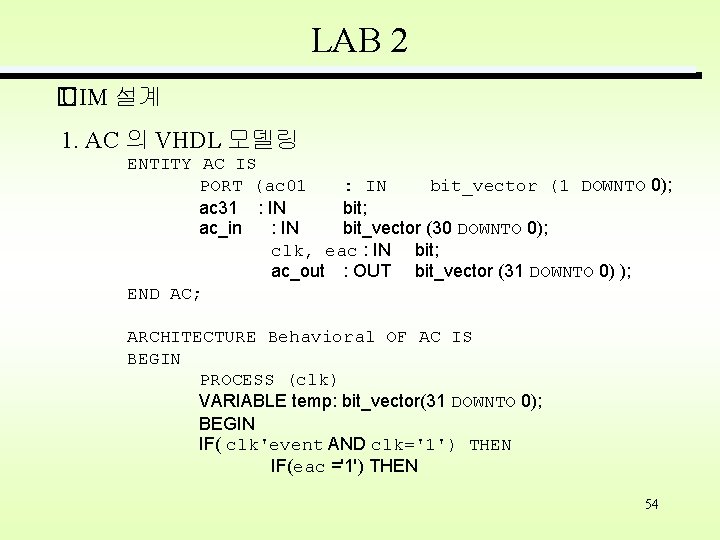

LAB 2 � UIM 설계 1. AC 의 VHDL 모델링 ENTITY AC IS PORT (ac 01 : IN bit_vector (1 DOWNTO 0); ac 31 : IN bit; ac_in : IN bit_vector (30 DOWNTO 0); clk, eac : IN bit; ac_out : OUT bit_vector (31 DOWNTO 0) ); END AC; ARCHITECTURE Behavioral OF AC IS BEGIN PROCESS (clk) VARIABLE temp: bit_vector(31 DOWNTO 0); BEGIN IF( clk'event AND clk='1') THEN IF(eac ='1') THEN 54

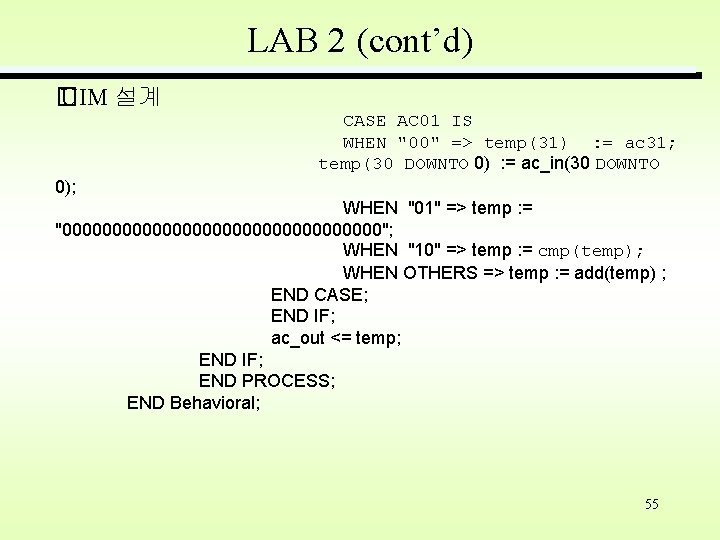

LAB 2 (cont’d) � UIM 설계 CASE AC 01 IS WHEN "00" => temp(31) : = ac 31; temp(30 DOWNTO 0) : = ac_in(30 DOWNTO 0); WHEN "01" => temp : = "0000000000000000"; WHEN "10" => temp : = cmp(temp); WHEN OTHERS => temp : = add(temp) ; END CASE; END IF; ac_out <= temp; END IF; END PROCESS; END Behavioral; 55

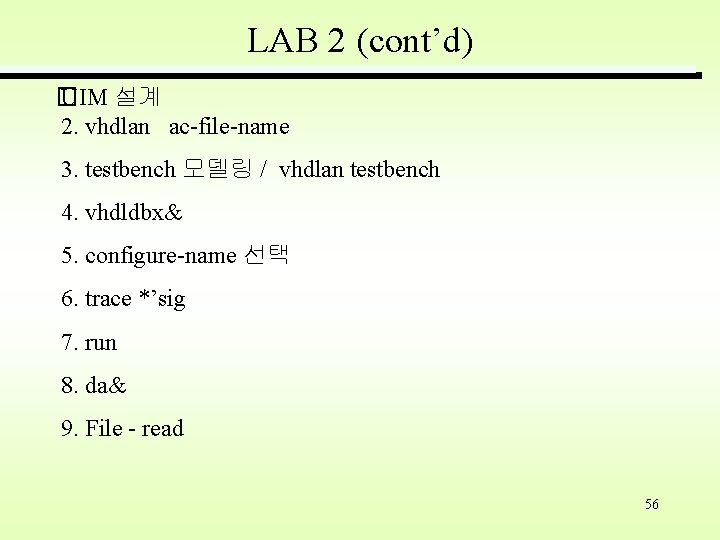

LAB 2 (cont’d) � UIM 설계 2. vhdlan ac-file-name 3. testbench 모델링 / vhdlan testbench 4. vhdldbx& 5. configure-name 선택 6. trace *’sig 7. run 8. da& 9. File - read 56

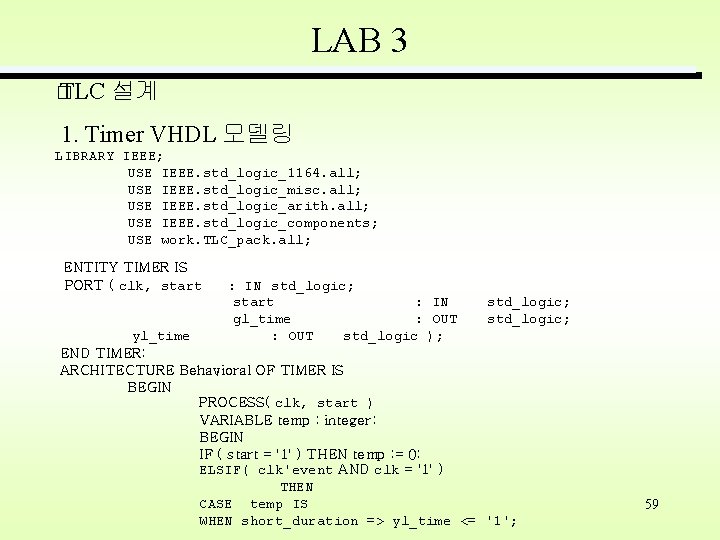

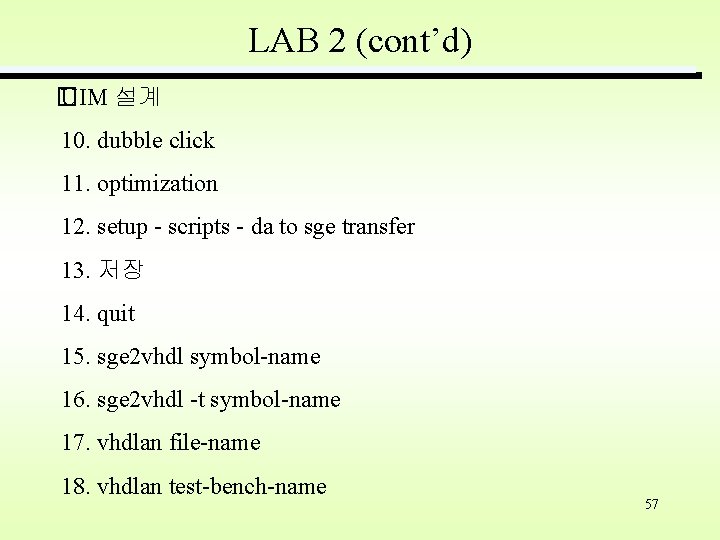

LAB 2 (cont’d) � UIM 설계 10. dubble click 11. optimization 12. setup - scripts - da to sge transfer 13. 저장 14. quit 15. sge 2 vhdl symbol-name 16. sge 2 vhdl -t symbol-name 17. vhdlan file-name 18. vhdlan test-bench-name 57

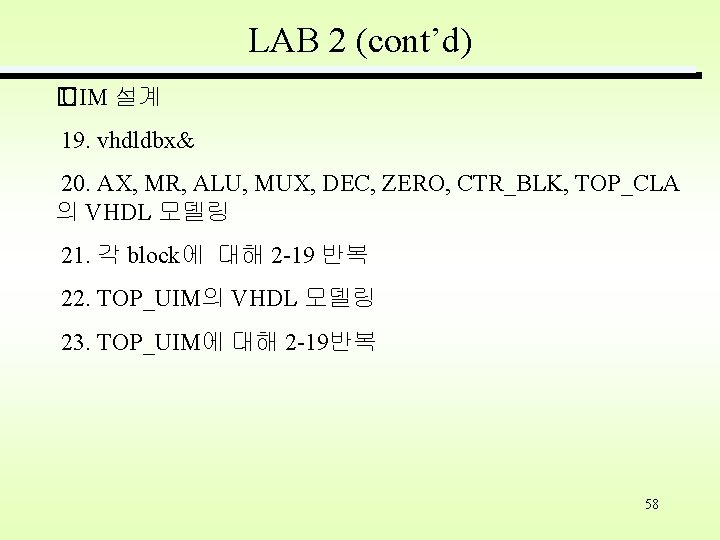

LAB 2 (cont’d) � UIM 설계 19. vhdldbx& 20. AX, MR, ALU, MUX, DEC, ZERO, CTR_BLK, TOP_CLA 의 VHDL 모델링 21. 각 block에 대해 2 -19 반복 22. TOP_UIM의 VHDL 모델링 23. TOP_UIM에 대해 2 -19반복 58

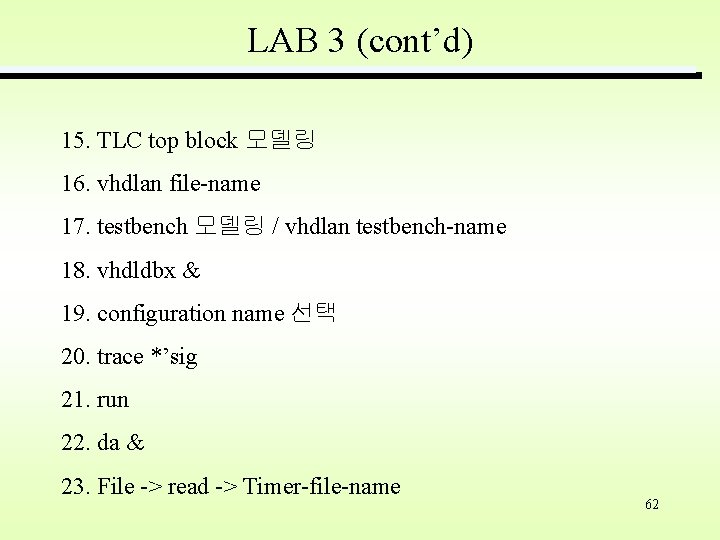

LAB 3 � TLC 설계 1. Timer VHDL 모델링 LIBRARY IEEE; USE IEEE. std_logic_1164. all; USE IEEE. std_logic_misc. all; USE IEEE. std_logic_arith. all; USE IEEE. std_logic_components; USE work. TLC_pack. all; ENTITY TIMER IS PORT ( clk, start : IN std_logic; start : IN gl_time : OUT std_logic ); std_logic; yl_time END TIMER; ARCHITECTURE Behavioral OF TIMER IS BEGIN PROCESS( clk, start ) VARIABLE temp : integer; BEGIN IF ( start = '1' ) THEN temp : = 0; ELSIF( clk'event AND clk = '1' ) THEN CASE temp IS WHEN short_duration => yl_time <= '1'; 59

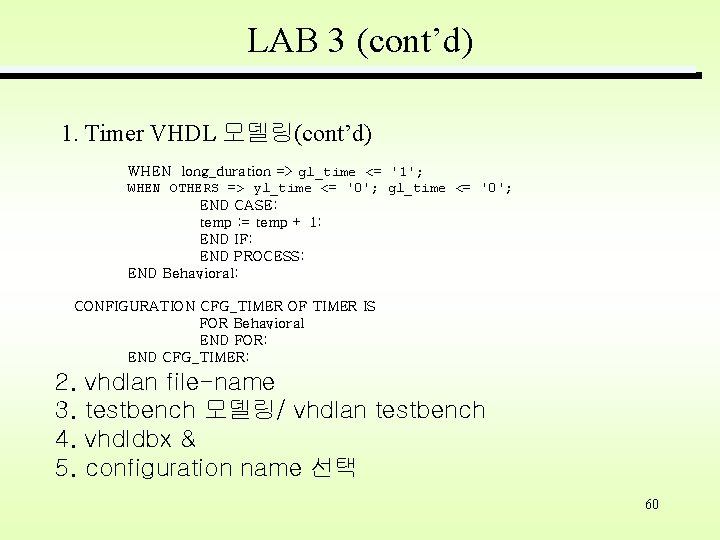

LAB 3 (cont’d) 1. Timer VHDL 모델링(cont’d) WHEN long_duration => gl_time <= '1'; WHEN OTHERS => yl_time <= '0'; gl_time <= '0'; END CASE; temp : = temp + 1; END IF; END PROCESS; END Behavioral; CONFIGURATION CFG_TIMER OF TIMER IS FOR Behavioral END FOR; END CFG_TIMER; 2. 3. 4. 5. vhdlan file-name testbench 모델링/ vhdlan testbench vhdldbx & configuration name 선택 60

LAB 3 (cont’d) 6. trace *’sig 7. run 8. TLC controller 모델링 9. vhdlan file-name 10. testbench 모델링 / vhdlan testbench 11. vhdldbx & 12. configuration name 선택 13. trace *’sig 14. run 61

LAB 3 (cont’d) 15. TLC top block 모델링 16. vhdlan file-name 17. testbench 모델링 / vhdlan testbench-name 18. vhdldbx & 19. configuration name 선택 20. trace *’sig 21. run 22. da & 23. File -> read -> Timer-file-name 62

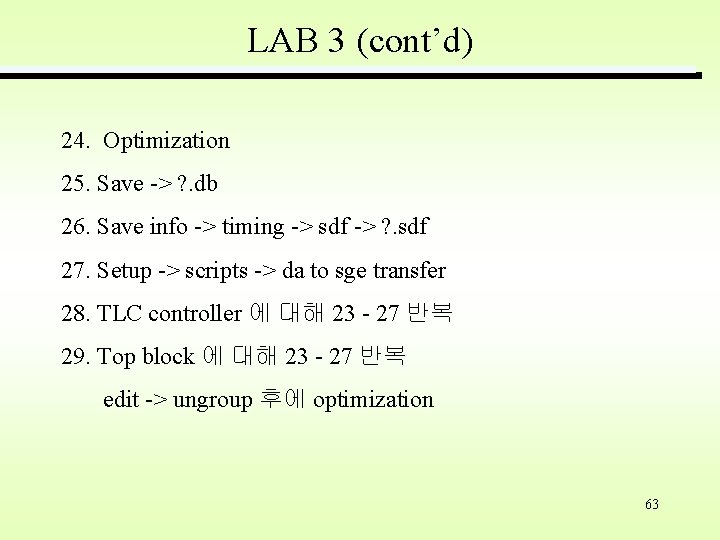

LAB 3 (cont’d) 24. Optimization 25. Save -> ? . db 26. Save info -> timing -> sdf -> ? . sdf 27. Setup -> scripts -> da to sge transfer 28. TLC controller 에 대해 23 - 27 반복 29. Top block 에 대해 23 - 27 반복 edit -> ungroup 후에 optimization 63

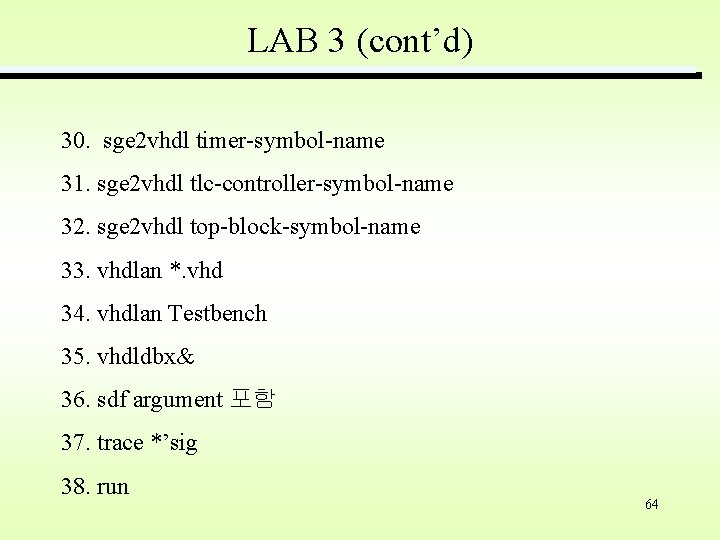

LAB 3 (cont’d) 30. sge 2 vhdl timer-symbol-name 31. sge 2 vhdl tlc-controller-symbol-name 32. sge 2 vhdl top-block-symbol-name 33. vhdlan *. vhd 34. vhdlan Testbench 35. vhdldbx& 36. sdf argument 포함 37. trace *’sig 38. run 64

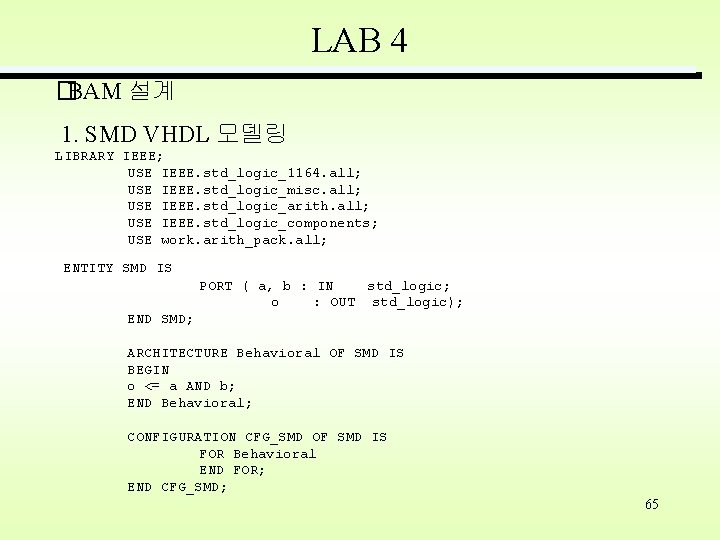

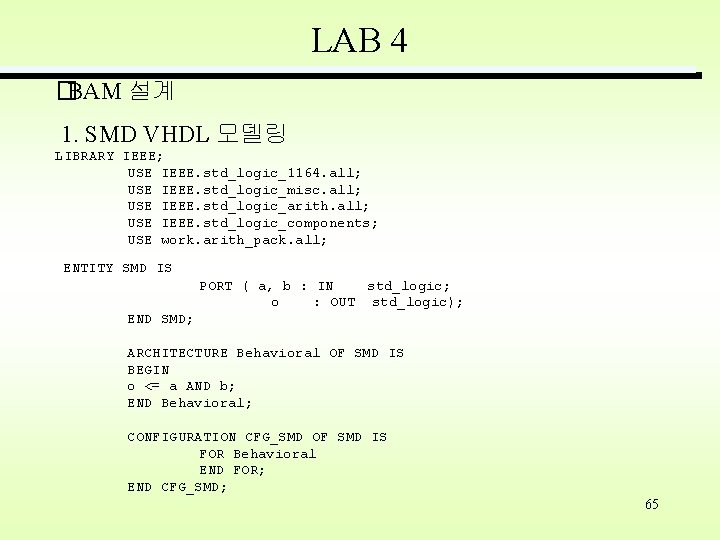

LAB 4 � BAM 설계 1. SMD VHDL 모델링 LIBRARY IEEE; USE IEEE. std_logic_1164. all; USE IEEE. std_logic_misc. all; USE IEEE. std_logic_arith. all; USE IEEE. std_logic_components; USE work. arith_pack. all; ENTITY SMD IS PORT ( a, b : IN std_logic; o : OUT std_logic); END SMD; ARCHITECTURE Behavioral OF SMD IS BEGIN o <= a AND b; END Behavioral; CONFIGURATION CFG_SMD OF SMD IS FOR Behavioral END FOR; END CFG_SMD; 65

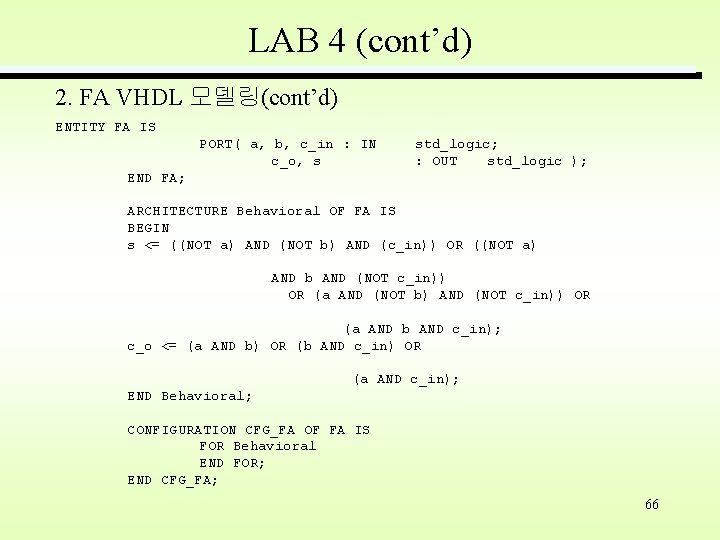

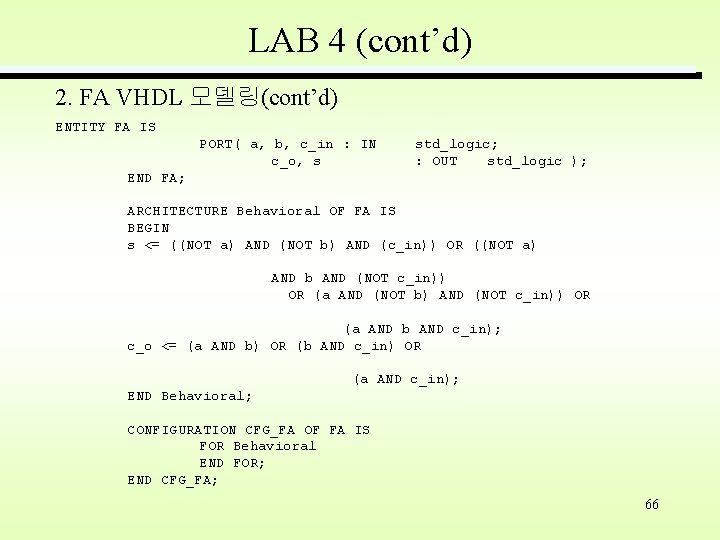

LAB 4 (cont’d) 2. FA VHDL 모델링(cont’d) ENTITY FA IS PORT( a, b, c_in : IN c_o, s std_logic; : OUT std_logic ); END FA; ARCHITECTURE Behavioral OF FA IS BEGIN s <= ((NOT a) AND (NOT b) AND (c_in)) OR ((NOT a) AND b AND (NOT c_in)) OR (a AND (NOT b) AND (NOT c_in)) OR (a AND b AND c_in); c_o <= (a AND b) OR (b AND c_in) OR (a AND c_in); END Behavioral; CONFIGURATION CFG_FA OF FA IS FOR Behavioral END FOR; END CFG_FA; 66

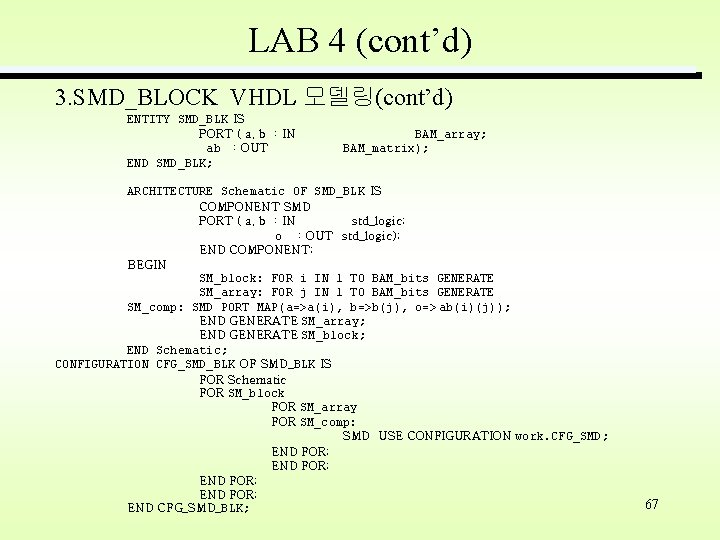

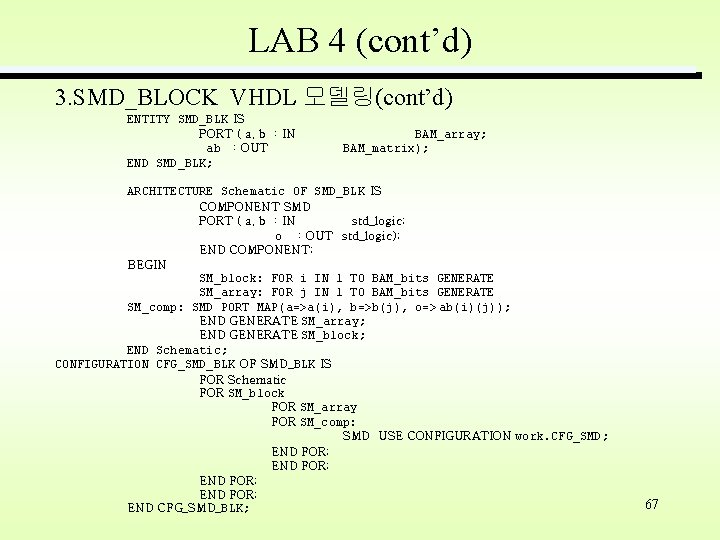

LAB 4 (cont’d) 3. SMD_BLOCK VHDL 모델링(cont’d) ENTITY SMD_BLK IS PORT ( a, b : IN ab : OUT END SMD_BLK; BAM_array; BAM_matrix); ARCHITECTURE Schematic OF SMD_BLK IS COMPONENT SMD PORT ( a, b : IN std_logic; o : OUT std_logic); END COMPONENT; BEGIN SM_block: FOR i IN 1 TO BAM_bits GENERATE SM_array: FOR j IN 1 TO BAM_bits GENERATE SM_comp: SMD PORT MAP(a=>a(i), b=>b(j), o=> ab(i)(j)); END GENERATE SM_array; END GENERATE SM_block; END Schematic; CONFIGURATION CFG_SMD_BLK OF SMD_BLK IS FOR Schematic FOR SM_block FOR SM_array FOR SM_comp: SMD USE CONFIGURATION work. CFG_SMD; END FOR; END CFG_SMD_BLK; 67

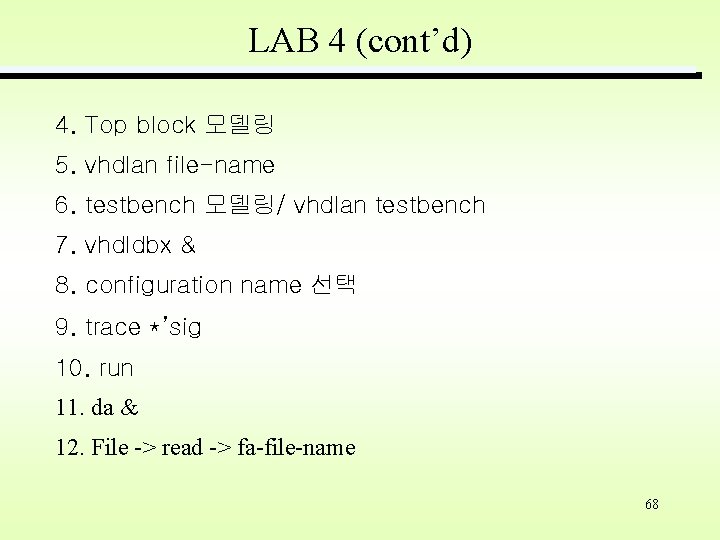

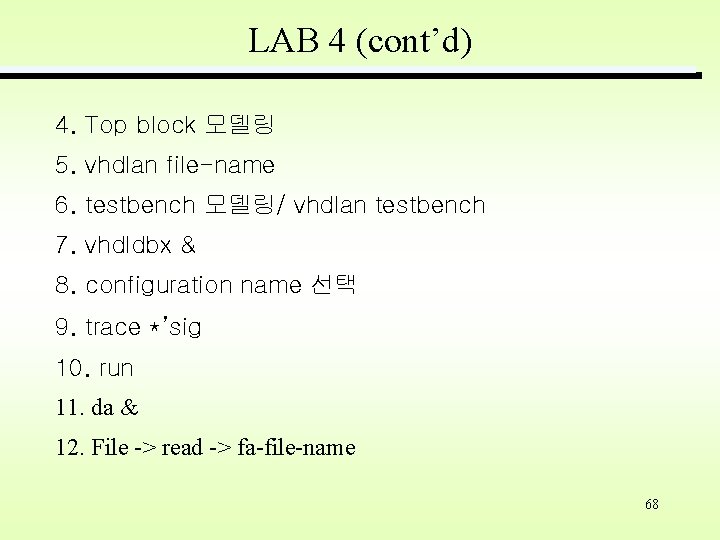

LAB 4 (cont’d) 4. Top block 모델링 5. vhdlan file-name 6. testbench 모델링/ vhdlan testbench 7. vhdldbx & 8. configuration name 선택 9. trace *’sig 10. run 11. da & 12. File -> read -> fa-file-name 68

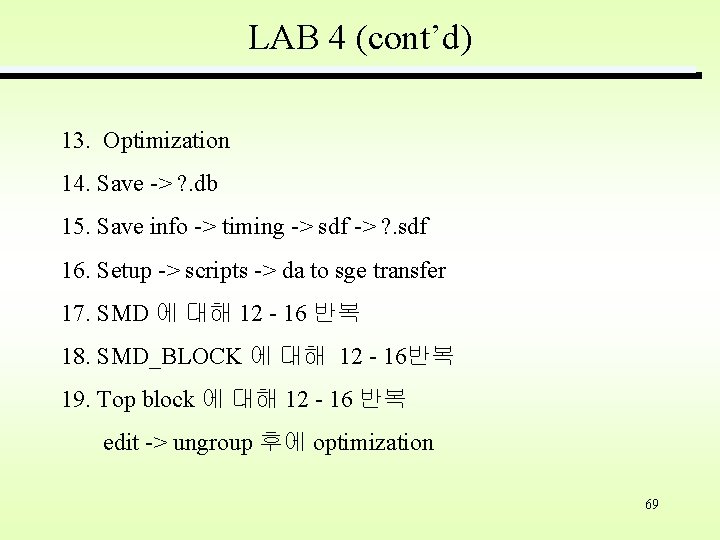

LAB 4 (cont’d) 13. Optimization 14. Save -> ? . db 15. Save info -> timing -> sdf -> ? . sdf 16. Setup -> scripts -> da to sge transfer 17. SMD 에 대해 12 - 16 반복 18. SMD_BLOCK 에 대해 12 - 16반복 19. Top block 에 대해 12 - 16 반복 edit -> ungroup 후에 optimization 69

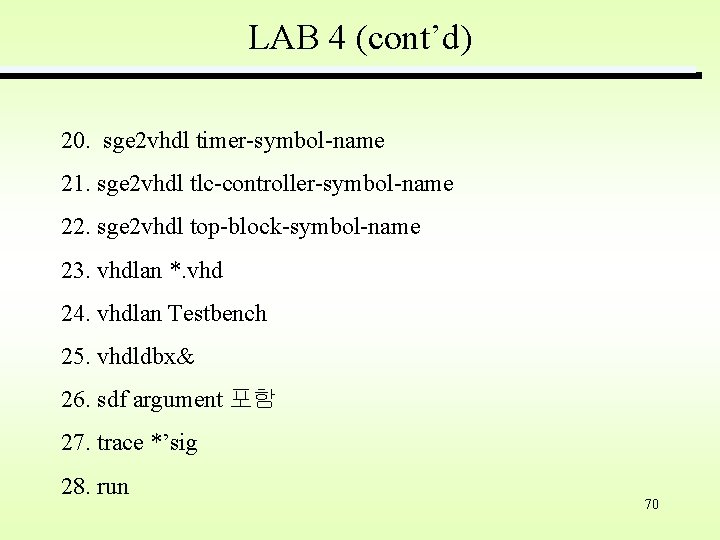

LAB 4 (cont’d) 20. sge 2 vhdl timer-symbol-name 21. sge 2 vhdl tlc-controller-symbol-name 22. sge 2 vhdl top-block-symbol-name 23. vhdlan *. vhd 24. vhdlan Testbench 25. vhdldbx& 26. sdf argument 포함 27. trace *’sig 28. run 70