Synopsys VIP User Guide Y C Chang Test

- Slides: 21

Synopsys VIP User Guide Y. C. Chang

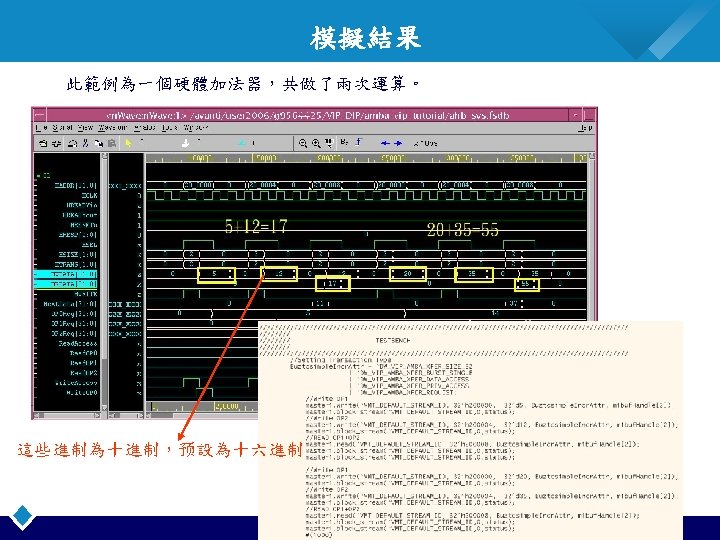

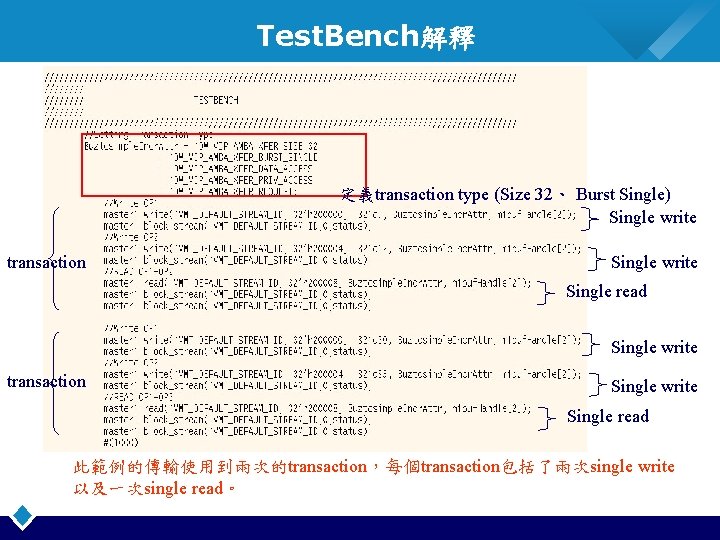

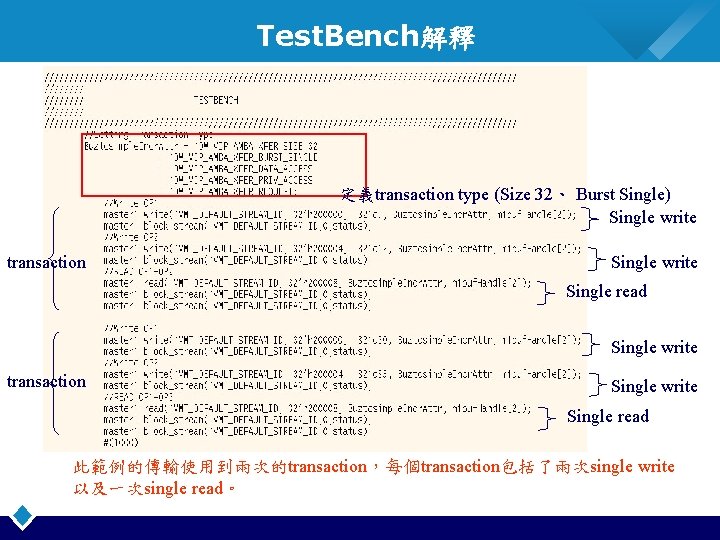

Test. Bench解釋 定義transaction type (Size 32、 Burst Single) Single write transaction Single write Single read 此範例的傳輸使用到兩次的transaction,每個transaction包括了兩次single write 以及一次single read。

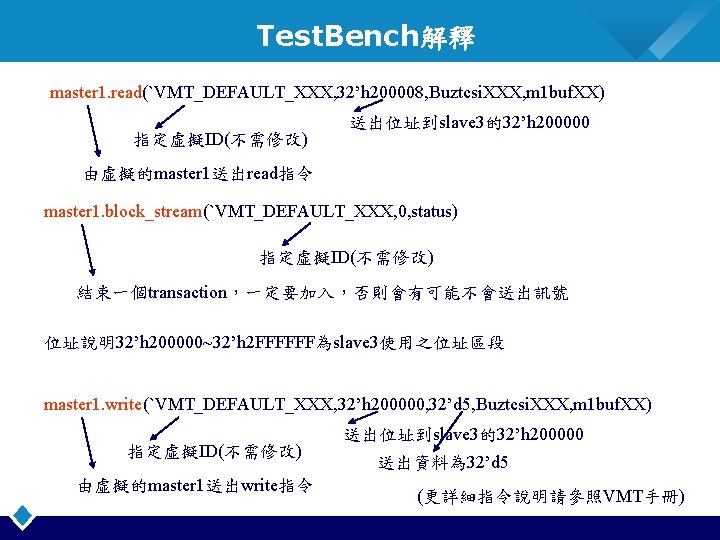

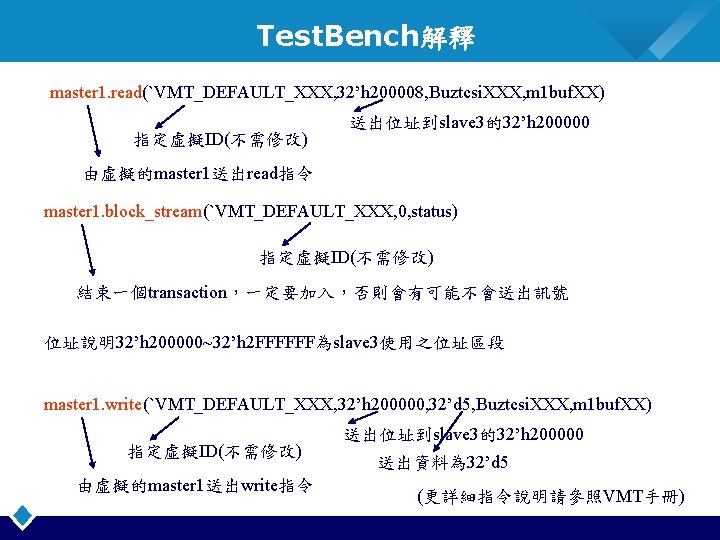

Test. Bench解釋 master 1. read(`VMT_DEFAULT_XXX, 32’h 200008, Buztcsi. XXX, m 1 buf. XX) 指定虛擬ID(不需修改) 送出位址到slave 3的32’h 200000 由虛擬的master 1送出read指令 master 1. block_stream(`VMT_DEFAULT_XXX, 0, status) 指定虛擬ID(不需修改) 結束一個transaction,一定要加入,否則會有可能不會送出訊號 位址說明32’h 200000~32’h 2 FFFFFF為slave 3使用之位址區段 master 1. write(`VMT_DEFAULT_XXX, 32’h 200000, 32’d 5, Buztcsi. XXX, m 1 buf. XX) 指定虛擬ID(不需修改) 由虛擬的master 1送出write指令 送出位址到slave 3的32’h 200000 送出資料為 32’d 5 (更詳細指令說明請參照VMT手冊)

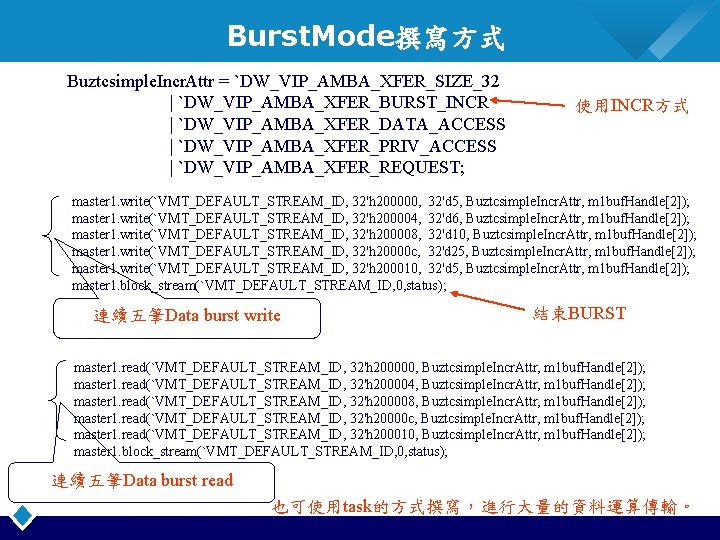

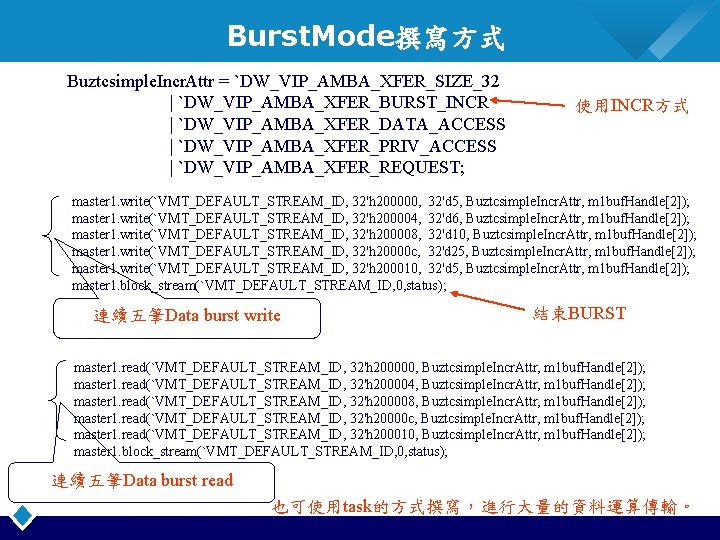

Burst. Mode撰寫方式 Buztcsimple. Incr. Attr = `DW_VIP_AMBA_XFER_SIZE_32 | `DW_VIP_AMBA_XFER_BURST_INCR | `DW_VIP_AMBA_XFER_DATA_ACCESS | `DW_VIP_AMBA_XFER_PRIV_ACCESS | `DW_VIP_AMBA_XFER_REQUEST; 使用INCR方式 master 1. write(`VMT_DEFAULT_STREAM_ID, 32'h 200000, 32'd 5, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. write(`VMT_DEFAULT_STREAM_ID, 32'h 200004, 32'd 6, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. write(`VMT_DEFAULT_STREAM_ID, 32'h 200008, 32'd 10, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. write(`VMT_DEFAULT_STREAM_ID, 32'h 20000 c, 32'd 25, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. write(`VMT_DEFAULT_STREAM_ID, 32'h 200010, 32'd 5, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. block_stream(`VMT_DEFAULT_STREAM_ID, 0, status); 連續五筆Data burst write 結束BURST master 1. read(`VMT_DEFAULT_STREAM_ID, 32'h 200000, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. read(`VMT_DEFAULT_STREAM_ID, 32'h 200004, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. read(`VMT_DEFAULT_STREAM_ID, 32'h 200008, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. read(`VMT_DEFAULT_STREAM_ID, 32'h 20000 c, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. read(`VMT_DEFAULT_STREAM_ID, 32'h 200010, Buztcsimple. Incr. Attr, m 1 buf. Handle[2]); master 1. block_stream(`VMT_DEFAULT_STREAM_ID, 0, status); 連續五筆Data burst read 也可使用task的方式撰寫,進行大量的資料運算傳輸。

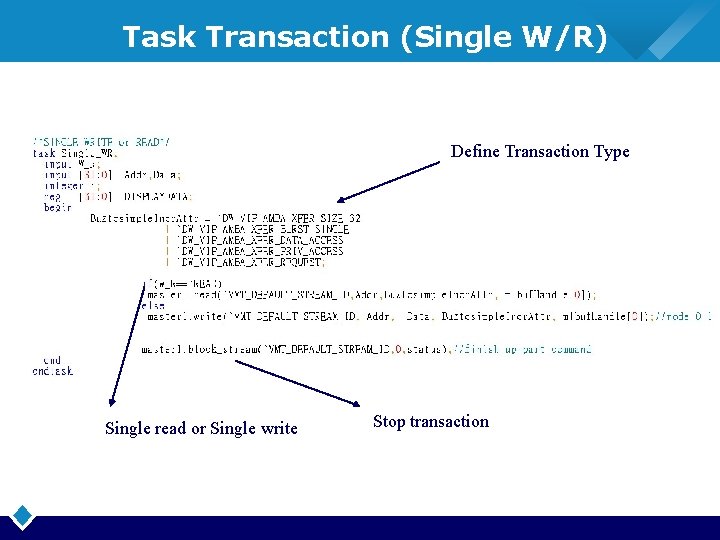

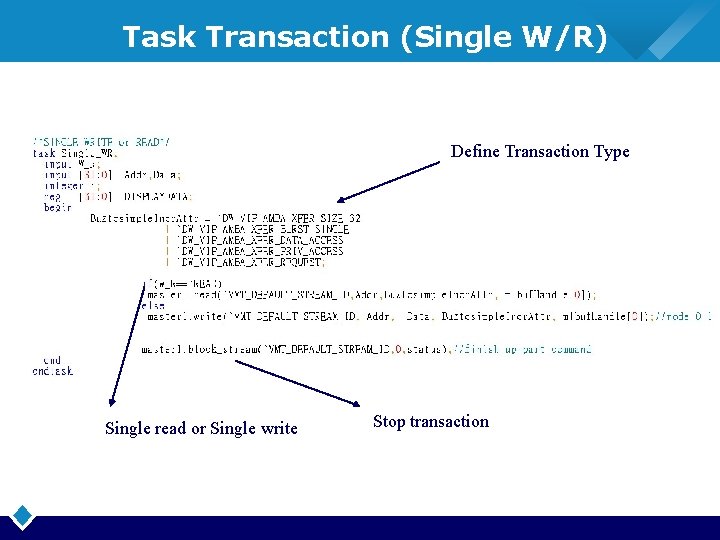

Task Transaction (Single W/R) Define Transaction Type Single read or Single write Stop transaction

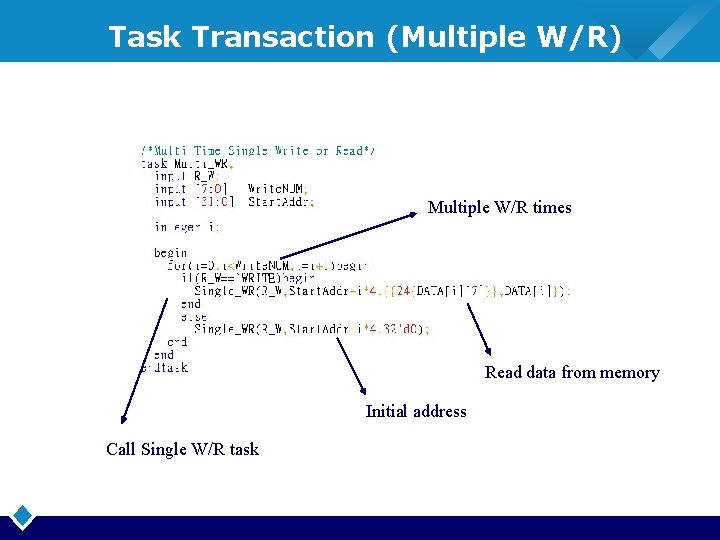

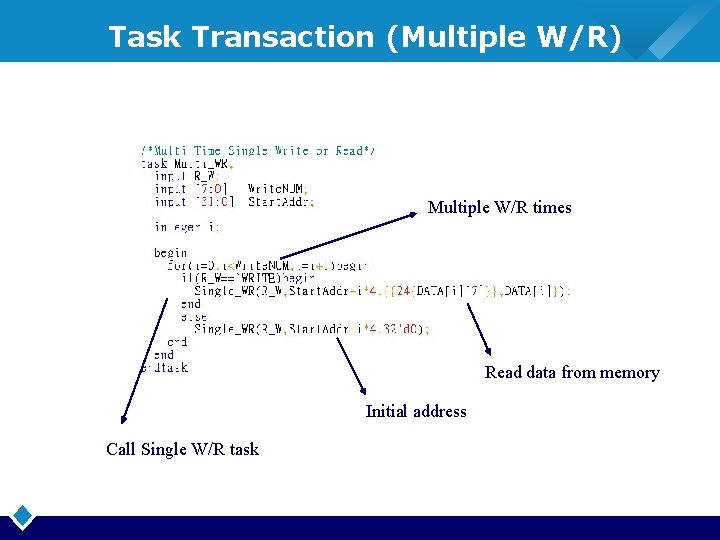

Task Transaction (Multiple W/R) Multiple W/R times Read data from memory Initial address Call Single W/R task

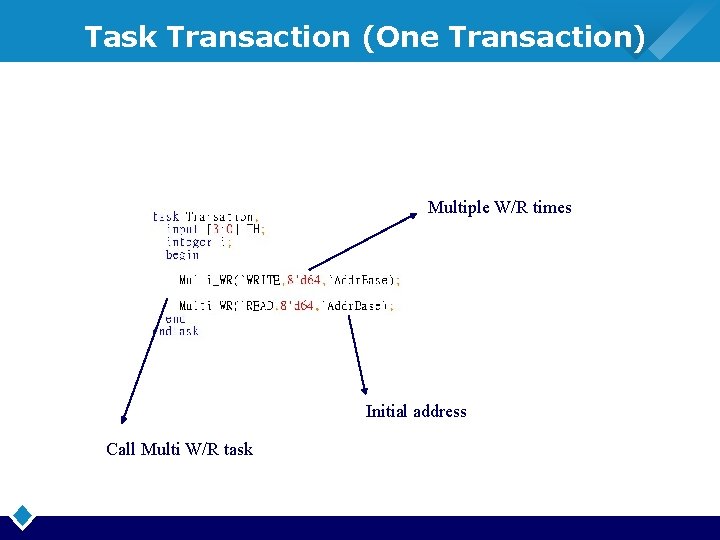

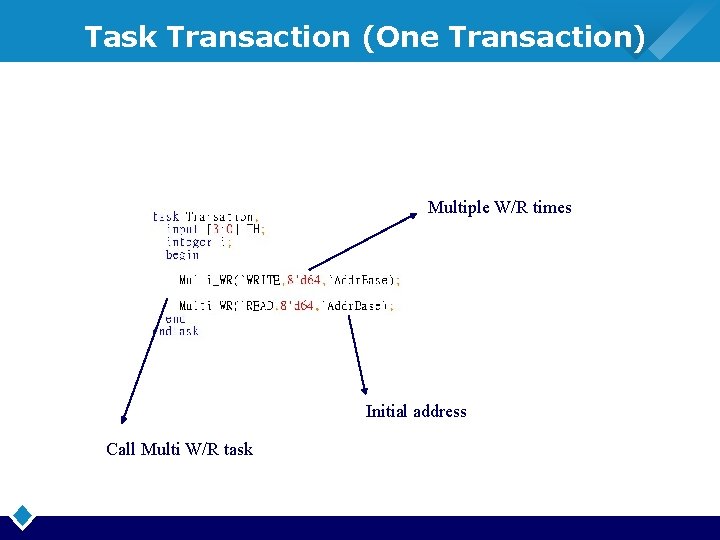

Task Transaction (One Transaction) Multiple W/R times Initial address Call Multi W/R task

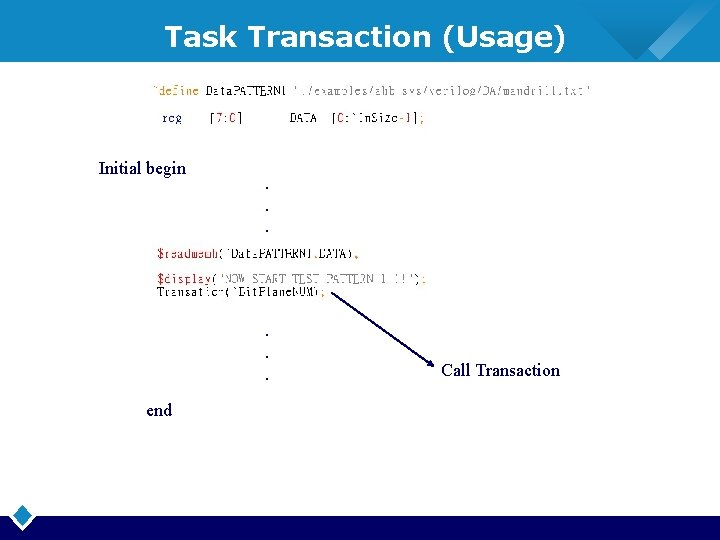

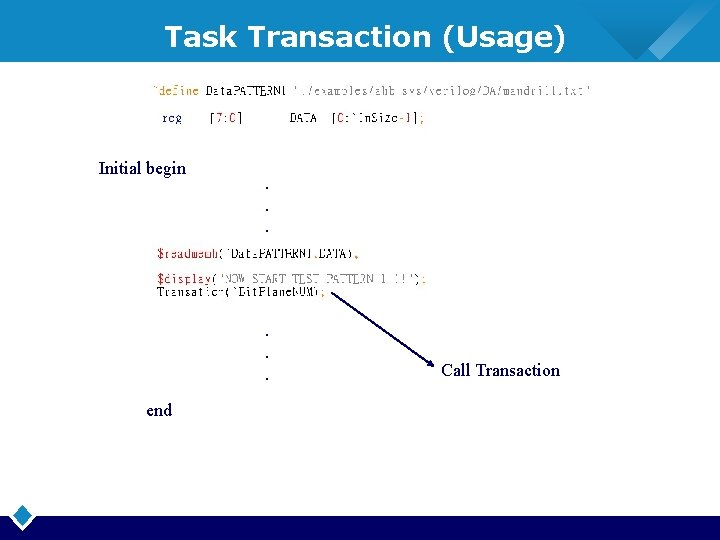

Task Transaction (Usage) Initial begin . . . end Call Transaction

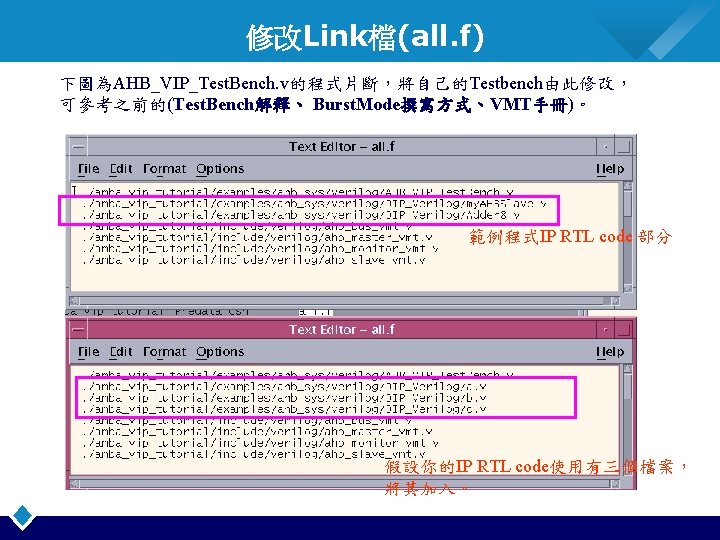

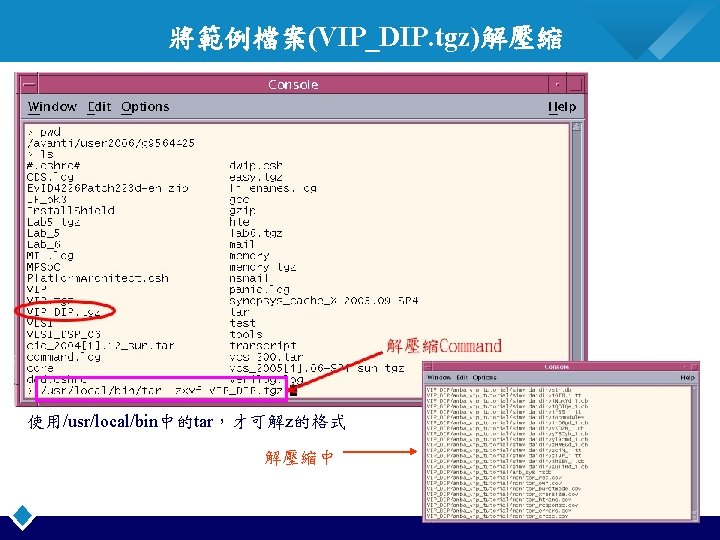

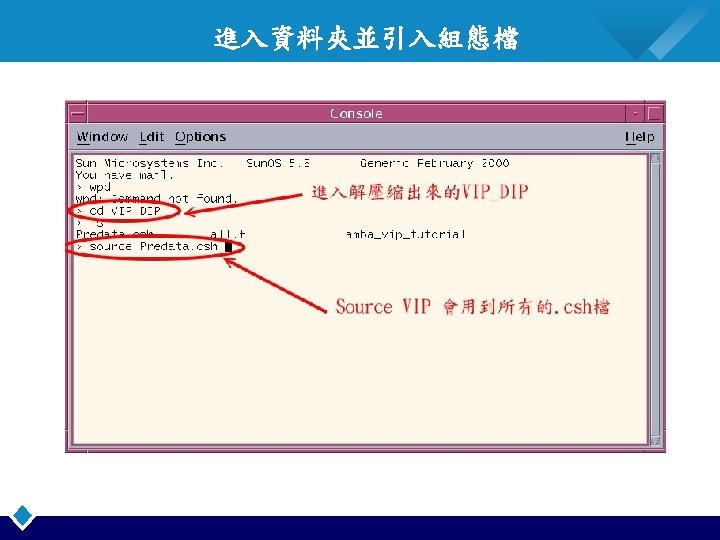

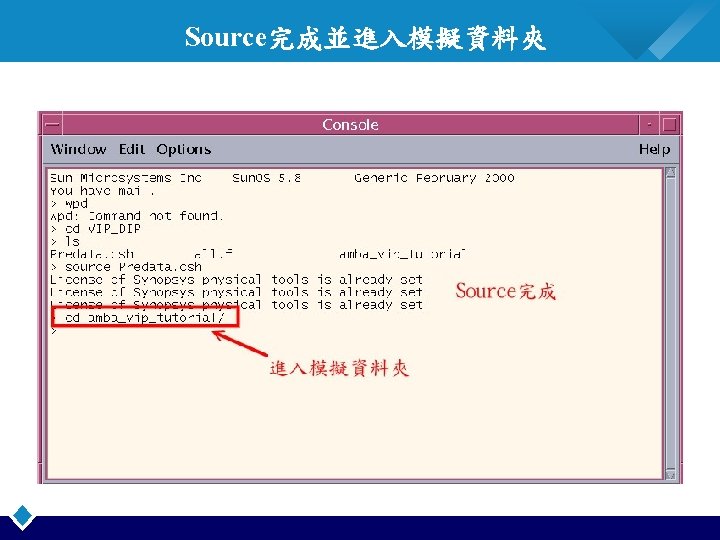

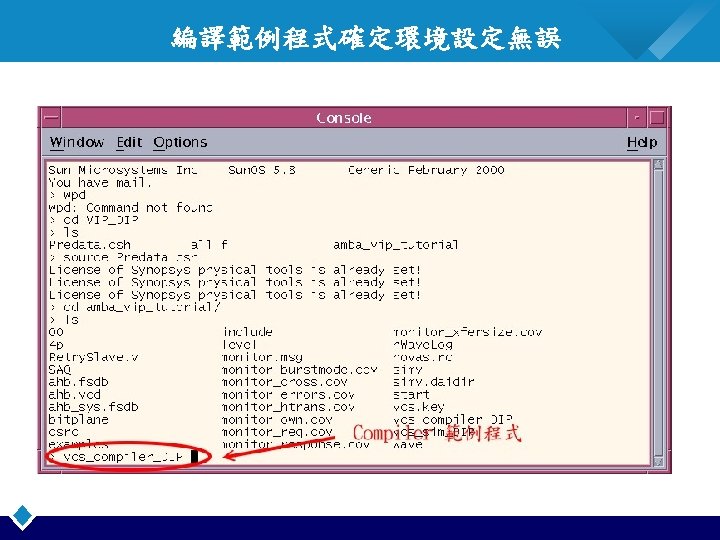

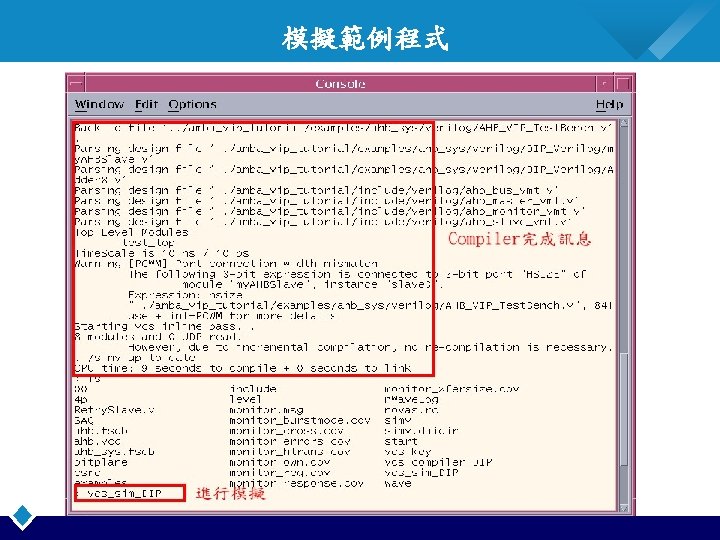

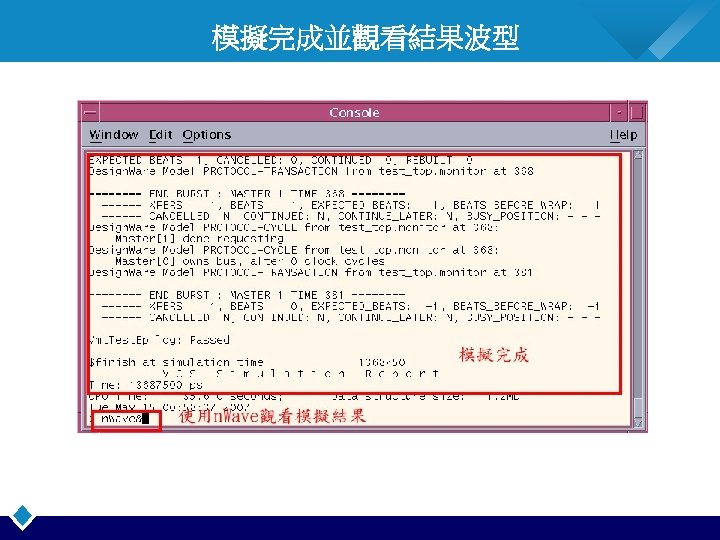

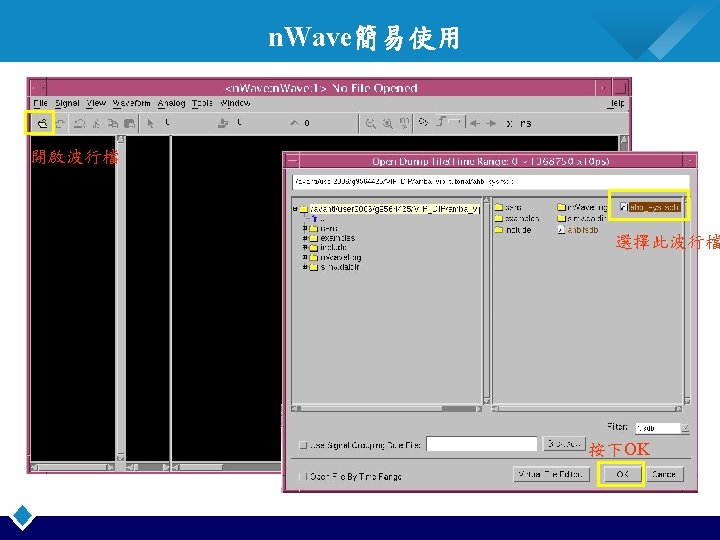

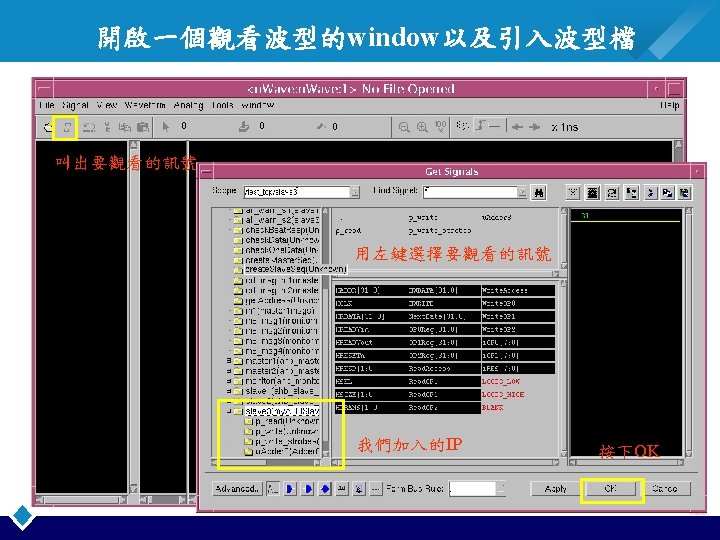

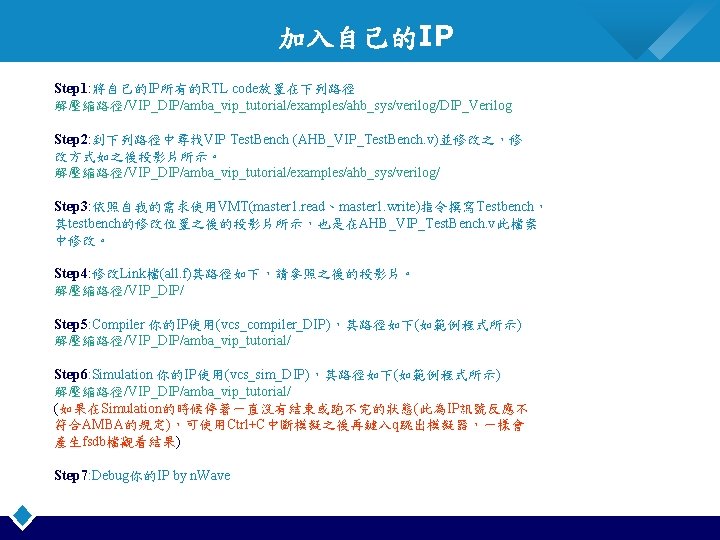

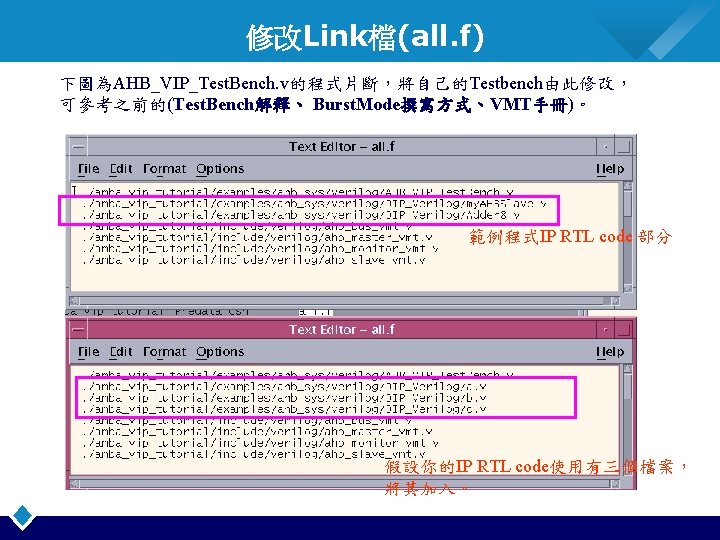

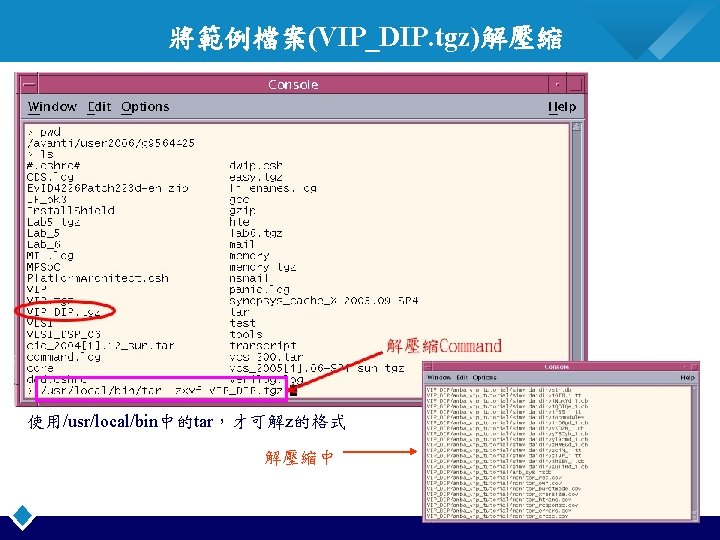

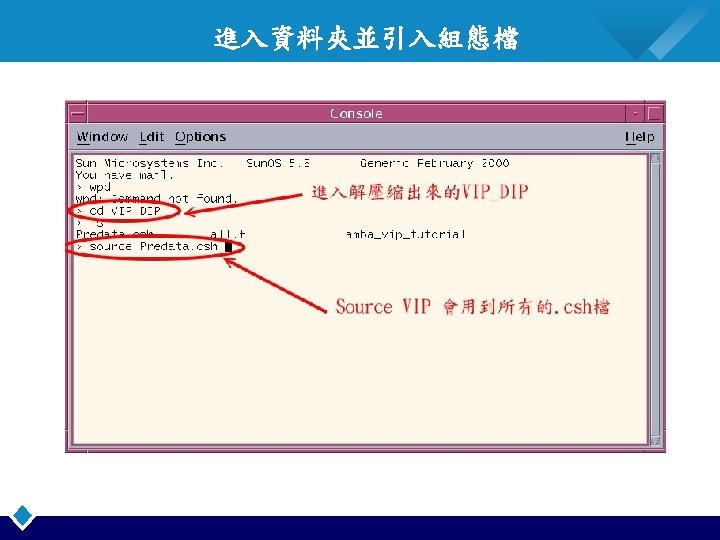

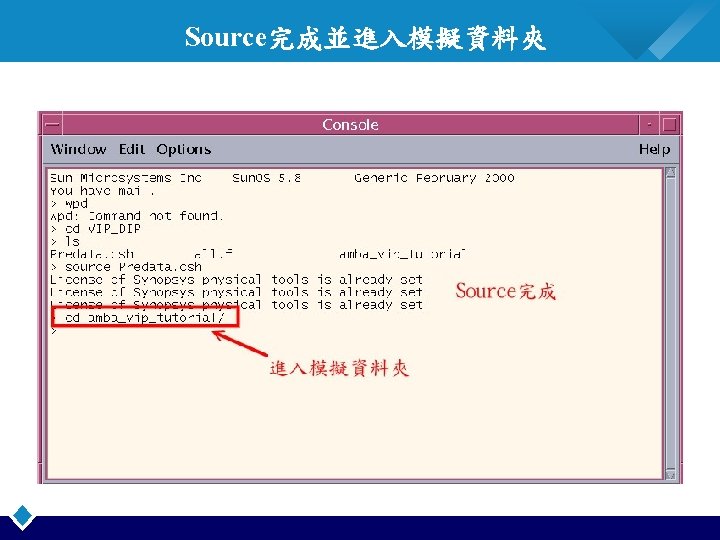

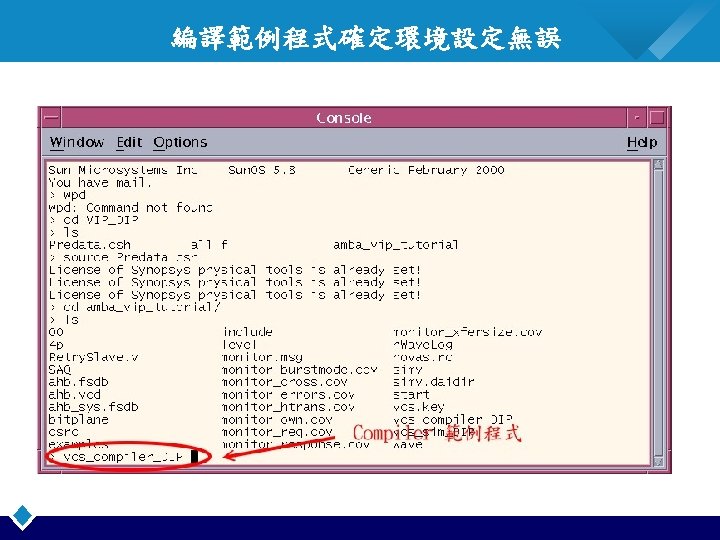

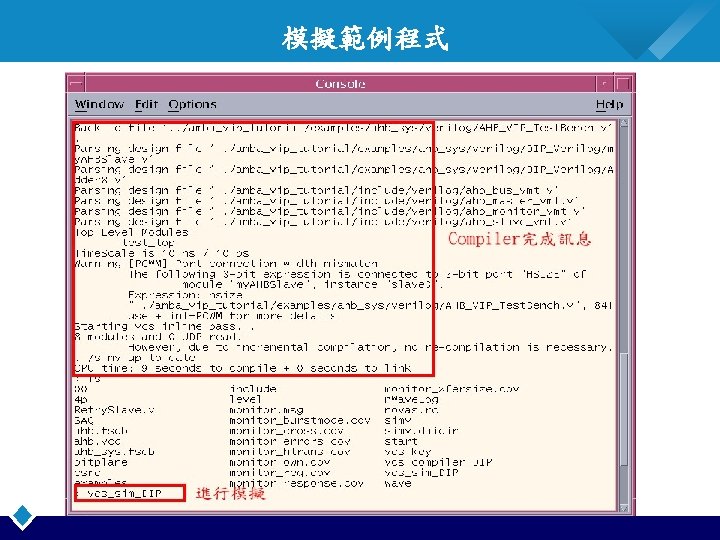

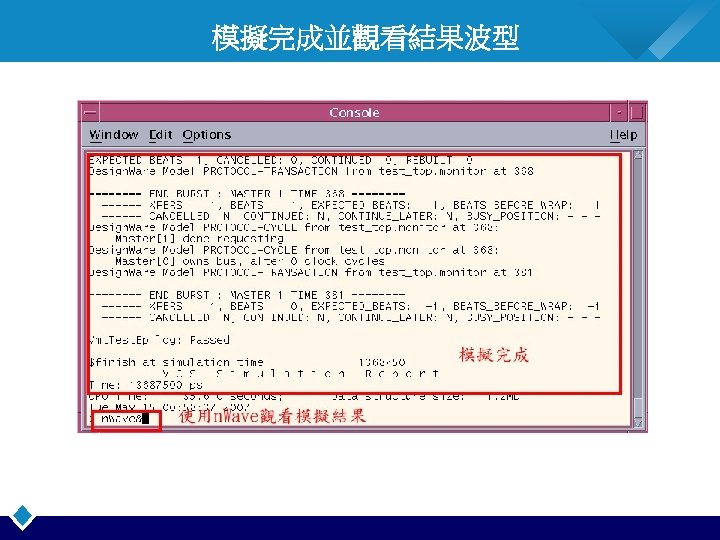

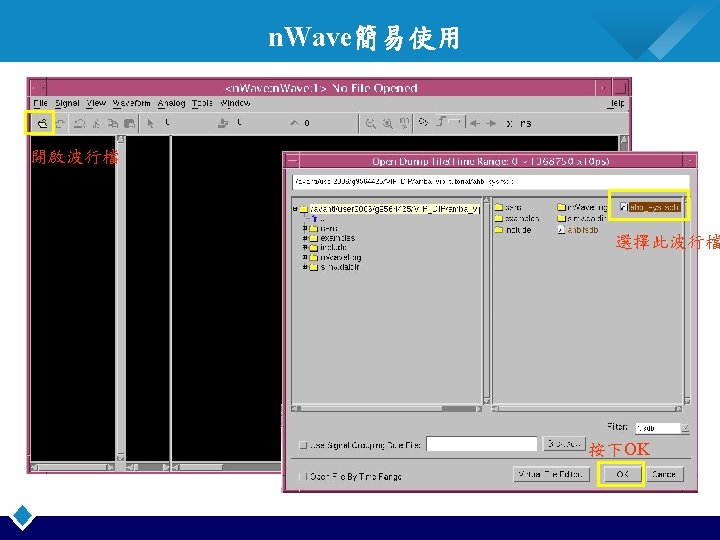

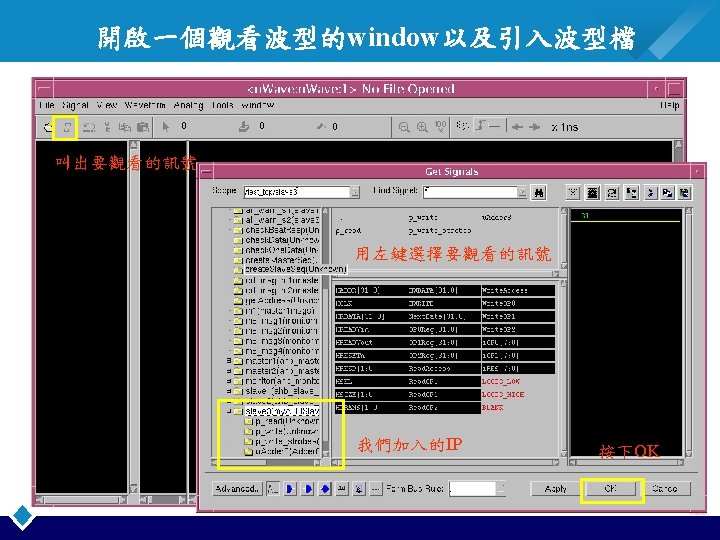

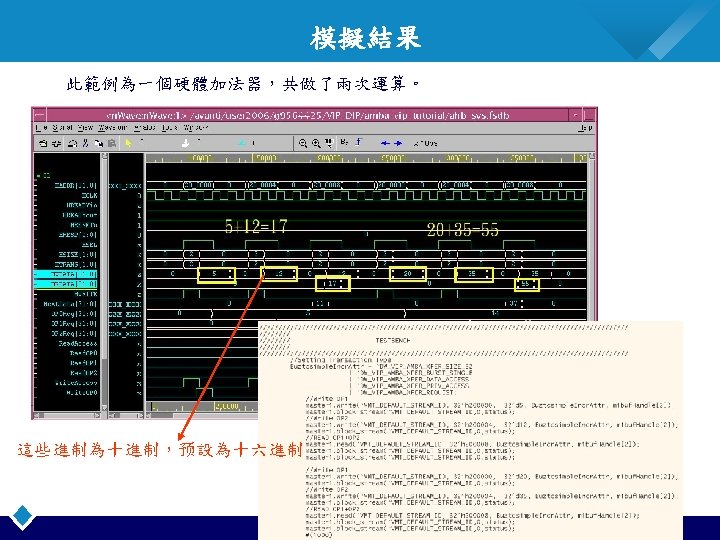

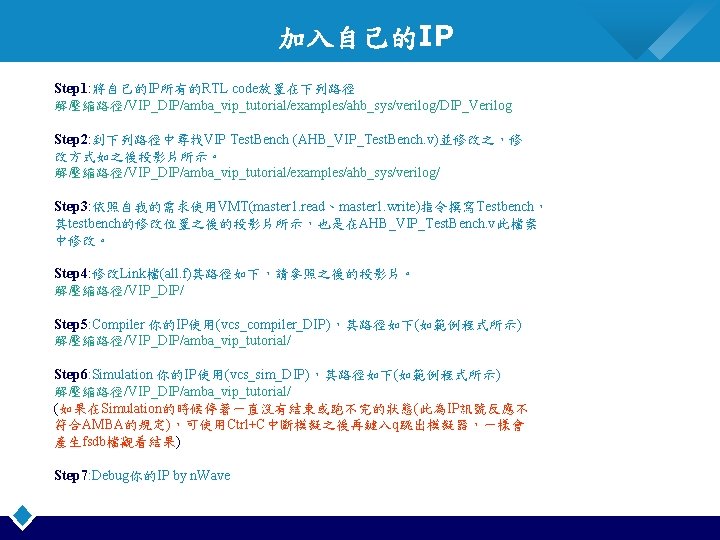

加入自己的IP Step 1: 將自己的IP所有的RTL code放置在下列路徑 解壓縮路徑/VIP_DIP/amba_vip_tutorial/examples/ahb_sys/verilog/DIP_Verilog Step 2: 到下列路徑中尋找VIP Test. Bench (AHB_VIP_Test. Bench. v)並修改之,修 改方式如之後投影片所示。 解壓縮路徑/VIP_DIP/amba_vip_tutorial/examples/ahb_sys/verilog/ Step 3: 依照自我的需求使用VMT(master 1. read、master 1. write)指令撰寫Testbench, 其testbench的修改位置之後的投影片所示,也是在AHB_VIP_Test. Bench. v此檔案 中修改。 Step 4: 修改Link檔(all. f)其路徑如下,請參照之後的投影片。 解壓縮路徑/VIP_DIP/ Step 5: Compiler 你的IP使用(vcs_compiler_DIP),其路徑如下(如範例程式所示) 解壓縮路徑/VIP_DIP/amba_vip_tutorial/ Step 6: Simulation 你的IP使用(vcs_sim_DIP),其路徑如下(如範例程式所示) 解壓縮路徑/VIP_DIP/amba_vip_tutorial/ (如果在Simulation的時候停著一直沒有結束或跑不完的狀態(此為IP訊號反應不 符合AMBA的規定),可使用Ctrl+C中斷模擬之後再鍵入q跳出模擬器,一樣會 產生fsdb檔觀看結果) Step 7: Debug你的IP by n. Wave

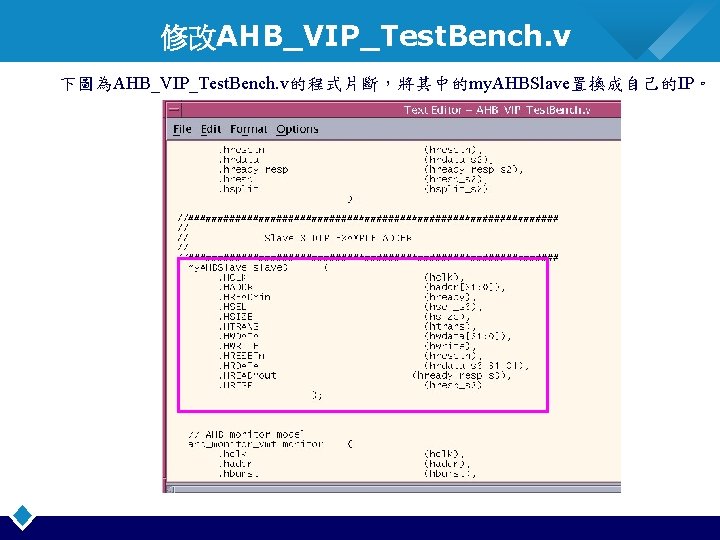

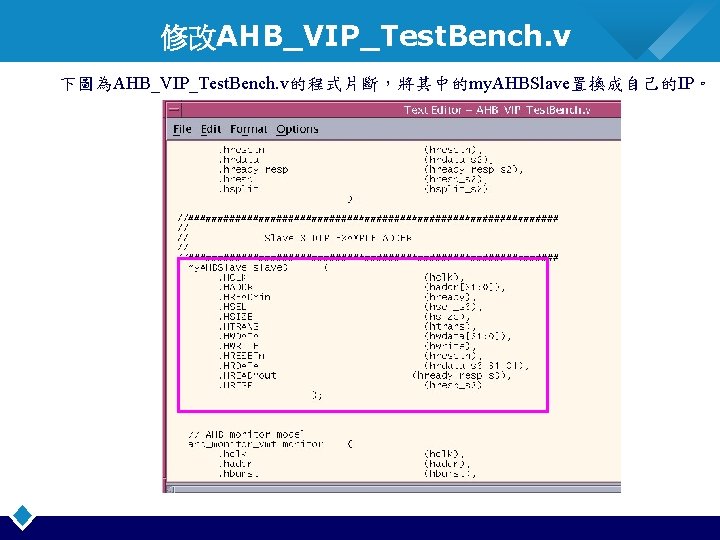

修改AHB_VIP_Test. Bench. v 下圖為AHB_VIP_Test. Bench. v的程式片斷,將其中的my. AHBSlave置換成自己的IP。

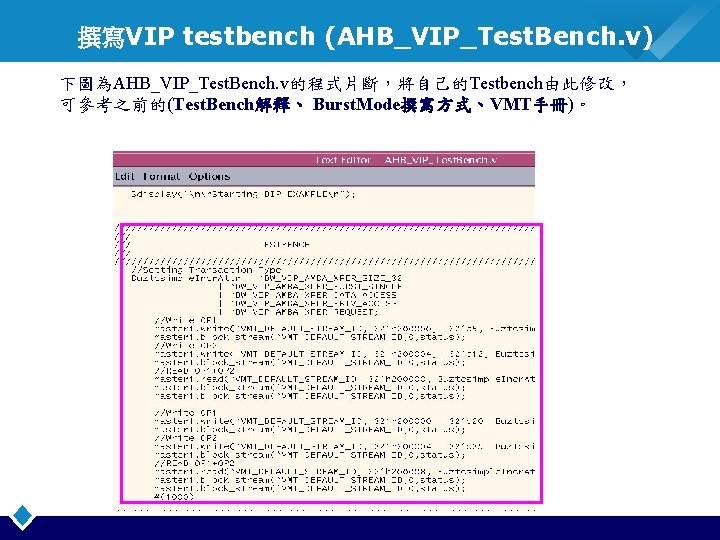

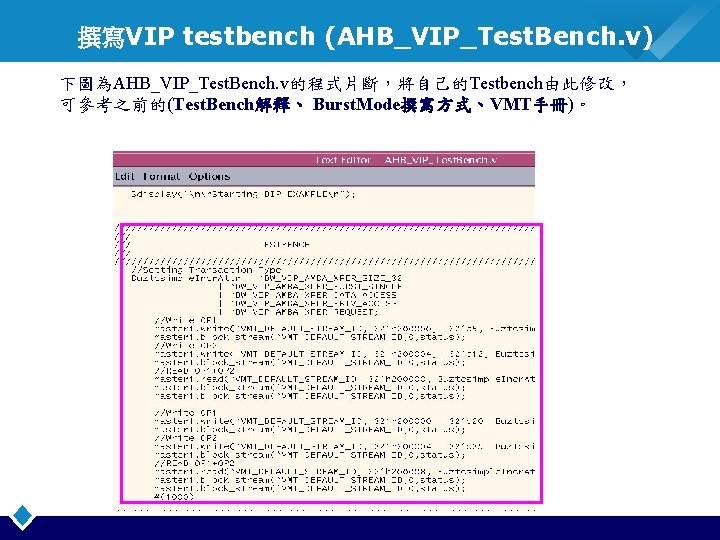

撰寫VIP testbench (AHB_VIP_Test. Bench. v) 下圖為AHB_VIP_Test. Bench. v的程式片斷,將自己的Testbench由此修改, 可參考之前的(Test. Bench解釋、 Burst. Mode撰寫方式、VMT手冊)。