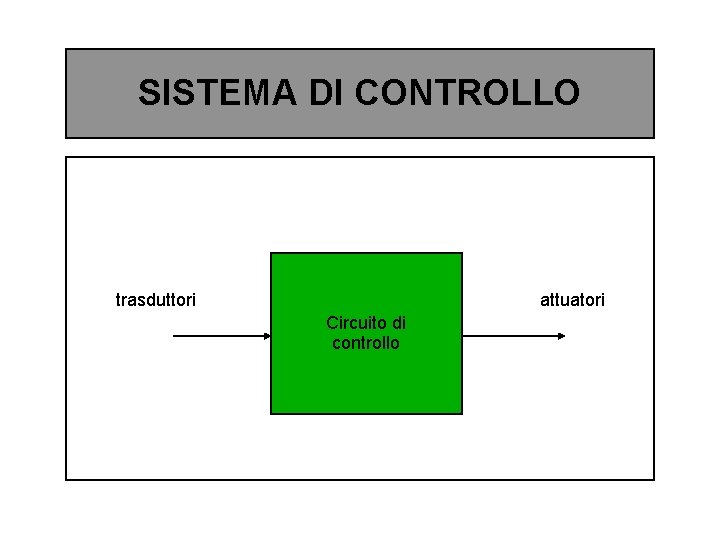

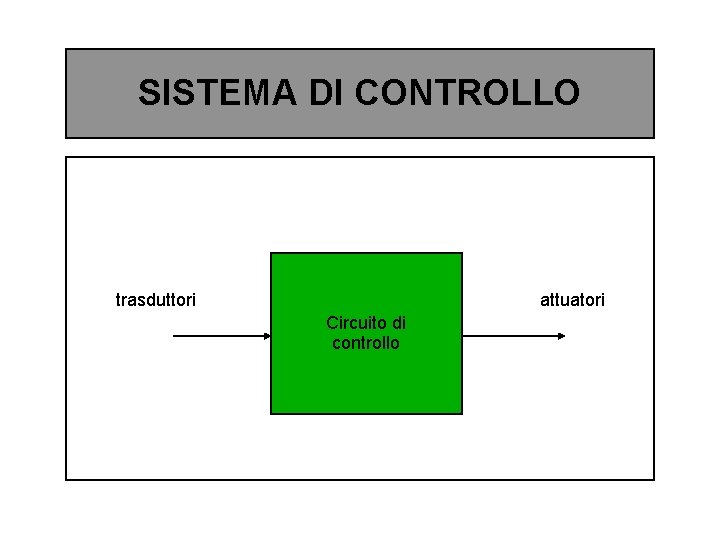

SISTEMA DI CONTROLLO trasduttori attuatori Circuito di controllo

- Slides: 54

SISTEMA DI CONTROLLO trasduttori attuatori Circuito di controllo

SEGNALE DIGITALE E ANALOGICO • SEGNALE DI TIPO ANALOGICO l'informazione è contenuta nei valori istantanei del segnale • SEGNALE DI TIPO DIGITALE l'informazione è di tipo binario e quindi caratterizzata da una banda discreta di valori

DISPOSITIVI IN LOGICA CABLATA UN PROBLEMA DI TIPO LOGICO PUO' ESSERE RISOLTO : • UTILIZZANDO COMPONENTI DIGITALI DI TIPO COMBINATORIO O SEQUENZIALE TRA LORO OPPORTUNAMENTE COLLEGATI (LOGICA CABLATA)

DISPOSITIVI IN LOGICA PROGRAMMATA UN PROBLEMA DI TIPO LOGICO PUO' ESSERE RISOLTO : • RICORRENDO A DISPOSITIVI CHE VENGONO OPPORTUNAMENTE PROGRAMMATI PER SVOLGERE QUELLA DETERMINATA FUNZIONE (LOGICA PROGRAMMATA)

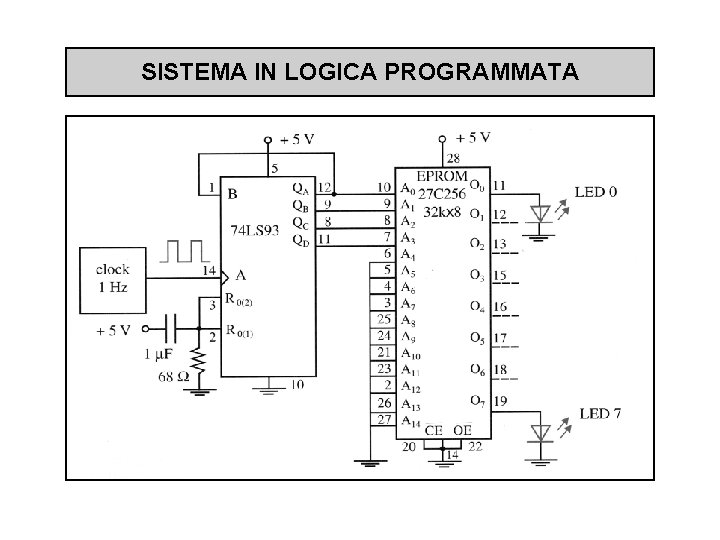

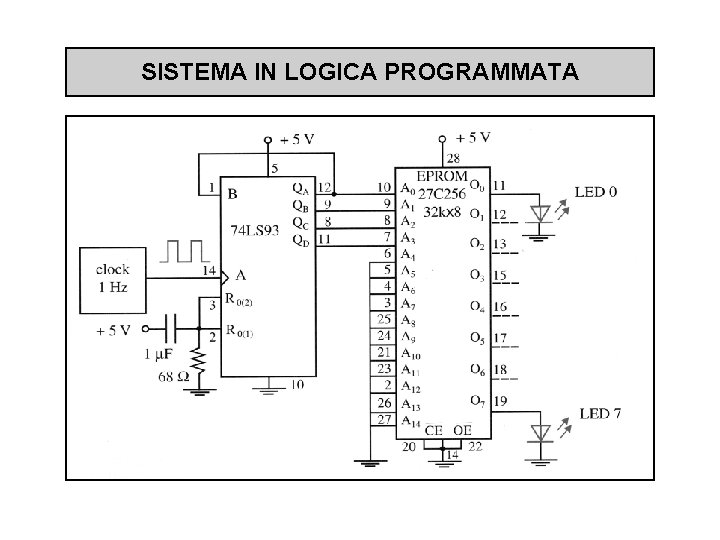

SISTEMA IN LOGICA PROGRAMMATA

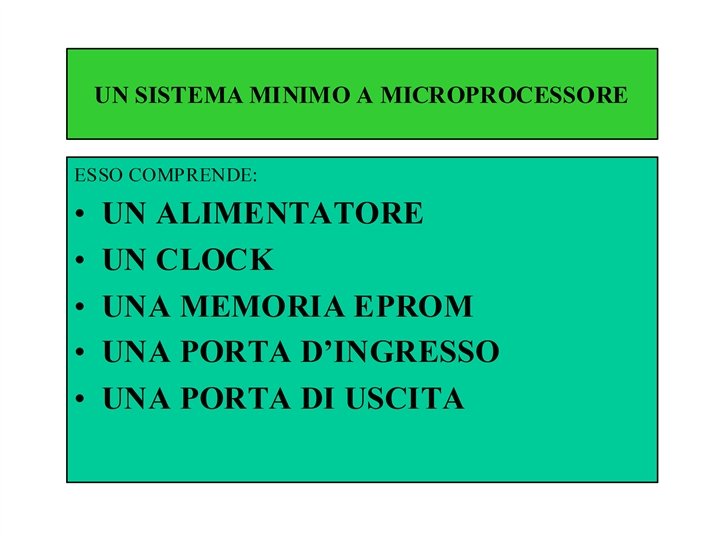

CONSIDERAZIONI IL SISTEMA COMPRENDE: • UN GENERATORE DI CLOCK • UN CONTATORE • UNA EPROM PROGRAMMATA

PRINCIPIO DI FUNZIONAMENTO • NELLA EPROM VENGONO MEMORIZZATI I BIT CORRISPONDENTI ALLO STATO DEI LED CHE SI VUOLE ACCENDERE • IL CONTATORE PUNTA ALLE PRIME 16 LOCAZIONI DI MEMORIA CIASCUNA DI 8 BIT • VENGONO INDIRIZZATE CELLE CONSEGUENTI GRAZIE AL SEGNALE DI CLOCK APPLICATO AL CONTATORE • MODIFICANDO IL CONTENUTO DELLA EPROM (IL SOFTWARE) CAMBIERA’ LA SEQUENZA DI ACCENSIONE DEI LED E QUESTO SENZA MODIFICARE L’HARDWARE

MICROPROCESSORE : campi di appicazione • ELETTRONICA DI CONSUMO – CALCOLATRICI, OROLOGI, VIDEOGIOCHI, APP. FOTOGRAFICHE • INDUSTRIA – COMPUTER, ROBOTICA , TELEFONIA, CONTROLLO PROCESSI, MACCHINE A CONTROLLO NUMERICO • STRUMENTAZIONE – STRUM. LABORATORIO, ELETTROMEDICALI, SISTEMI PUNTAMENTO D'ARMA E SICUREZZA • COMMERCIO – FOTOCOPIATRICI, FAX, TERMINALI RETI, APP. BANCARIE, DISTRIBUTORI AUTOMATICI

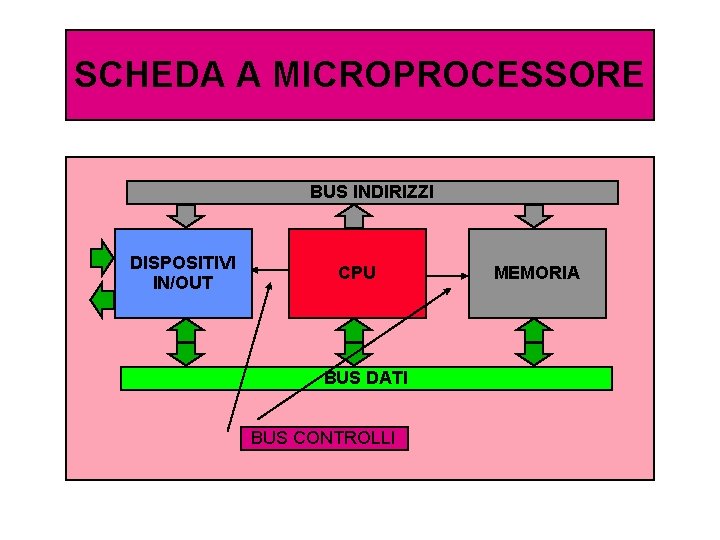

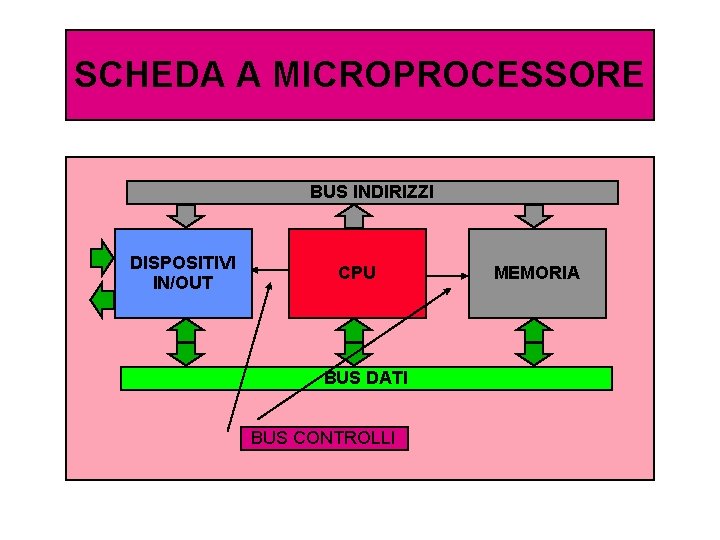

SCHEDA A MICROPROCESSORE BUS INDIRIZZI DISPOSITIVI IN/OUT CPU BUS DATI BUS CONTROLLI MEMORIA

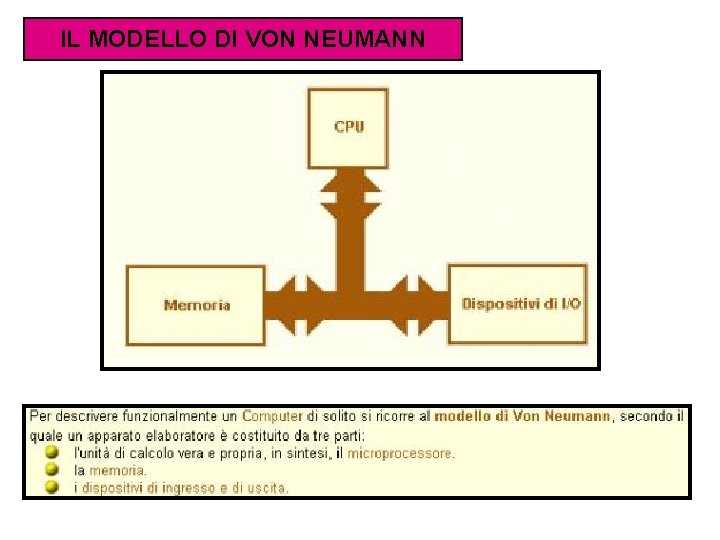

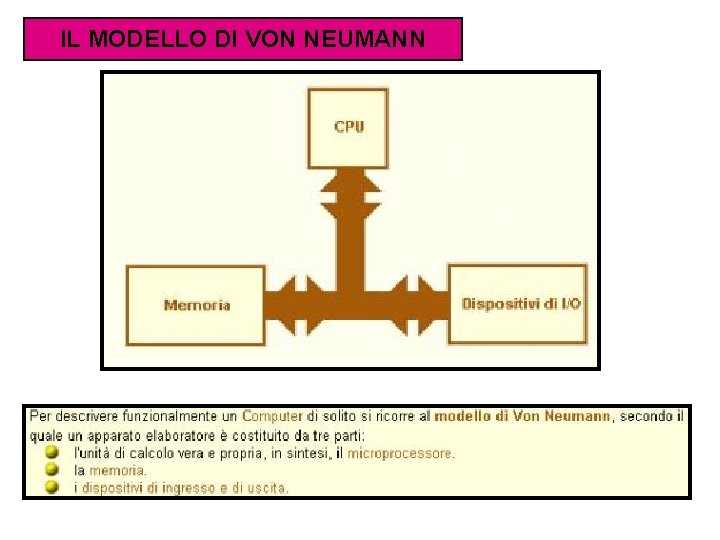

IL MODELLO DI VON NEUMANN

LA STRUTTURA A BUS IL COMPUTER E’ CARATTERIZZATO DALLA PRESENZA DI TRE TIPI DI BUS: • IL BUS DATI • IL BUS INDIRIZZI • IL BUS CONTROLLI

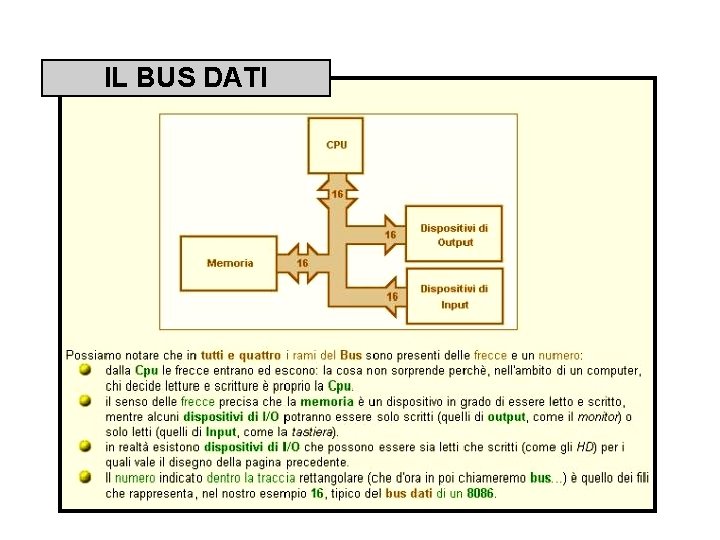

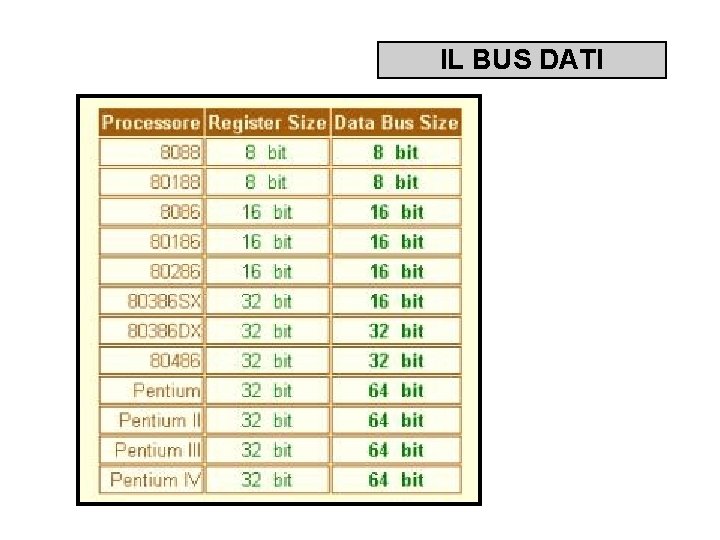

MICROPROCESSORE: IL BUS DATI • attraverso il bus dati scorrono le informazioni che possono essere dati da processare o istruzioni di programma.

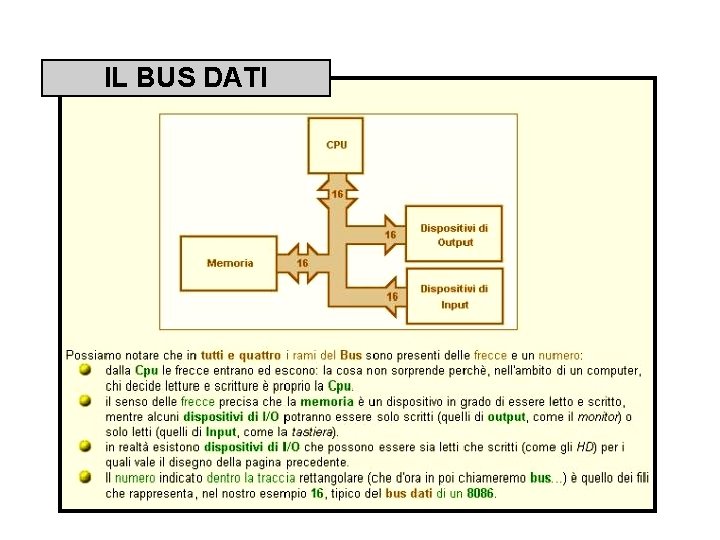

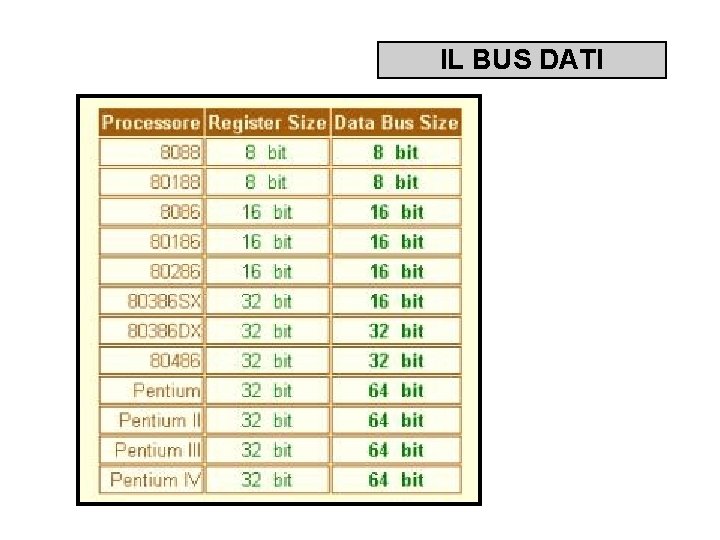

IL BUS DATI

IL BUS DATI

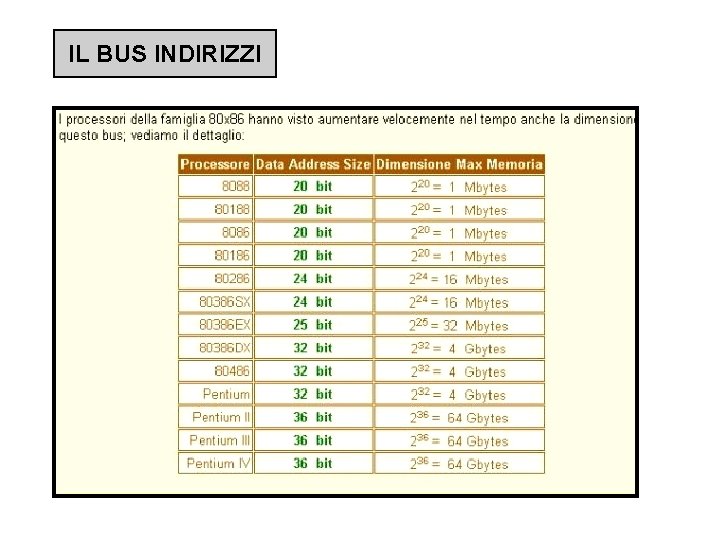

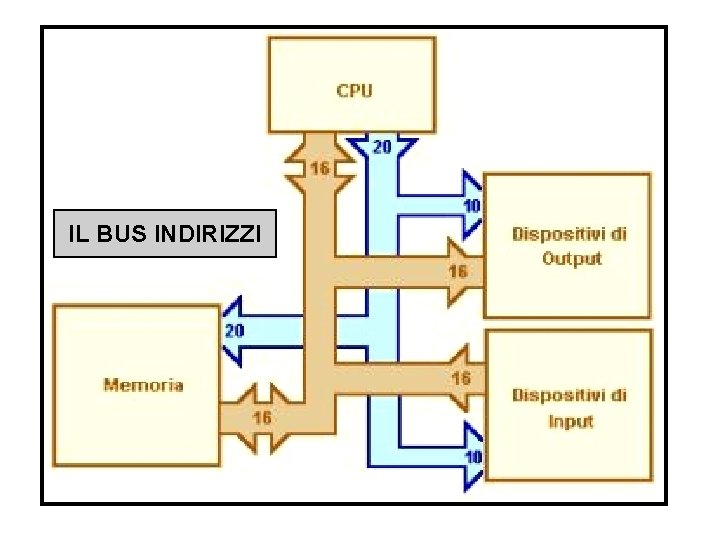

MICROPROCESSORE: IL BUS INDIRIZZI • è un collegamento unidirezionale dal microprocessore alle altre unità del sistema che permette la comunicazione dal o verso il micro.

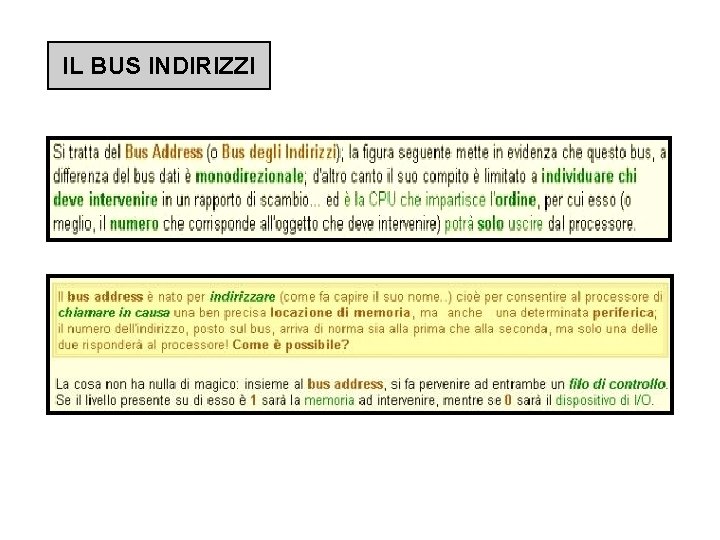

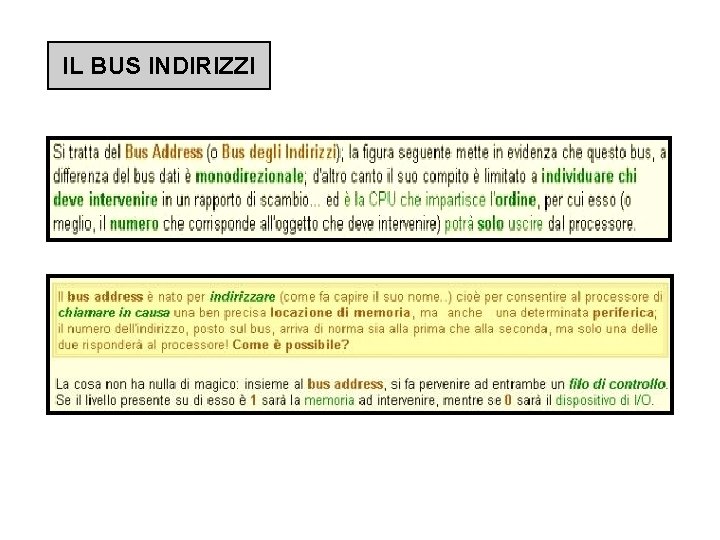

IL BUS INDIRIZZI

IL BUS INDIRIZZI

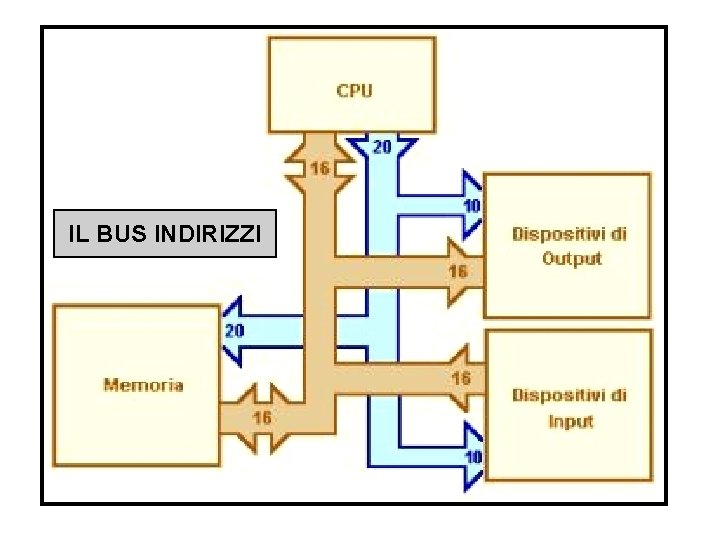

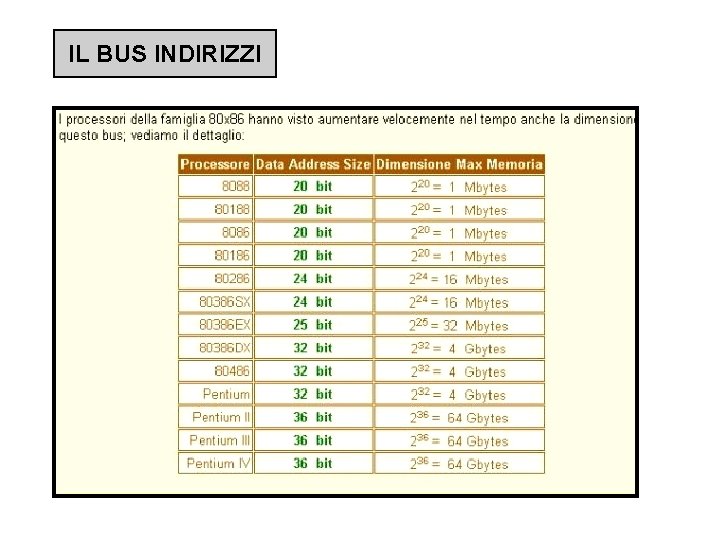

IL BUS INDIRIZZI

MICROPROCESSORE: IL BUS CONTROLLI • è l'insieme di conduttori che collegano i vari blocchi che compongono il microprocessore e permettono di controllare la funzionalità di ciascun blocco

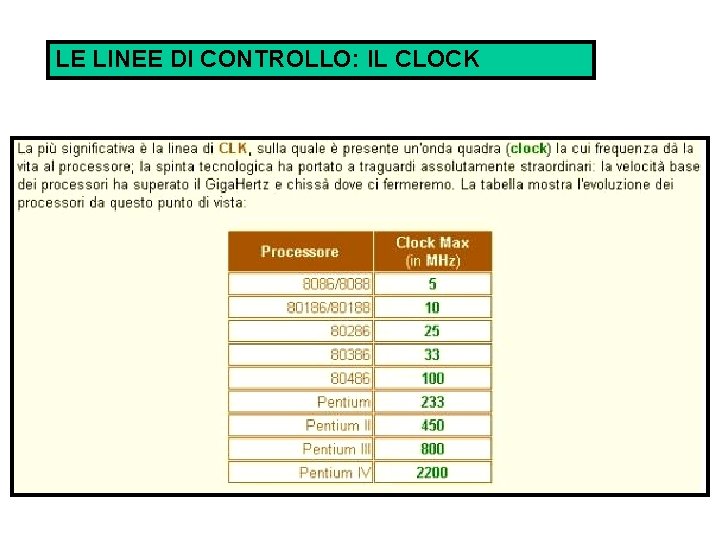

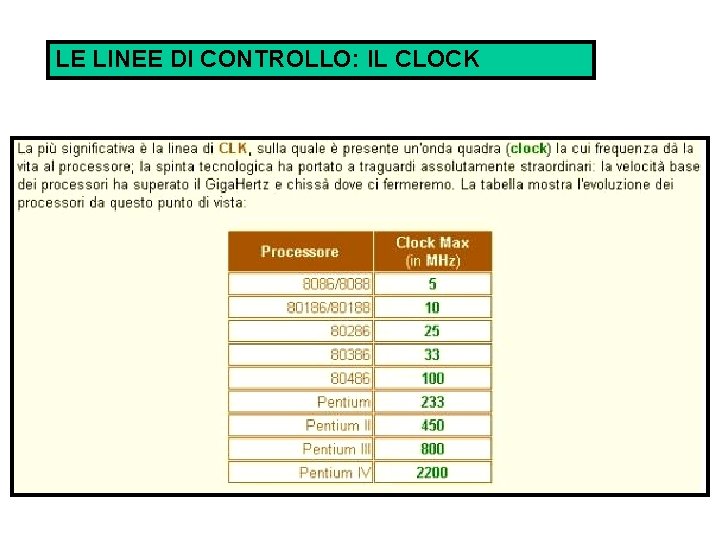

LE LINEE DI CONTROLLO: IL CLOCK

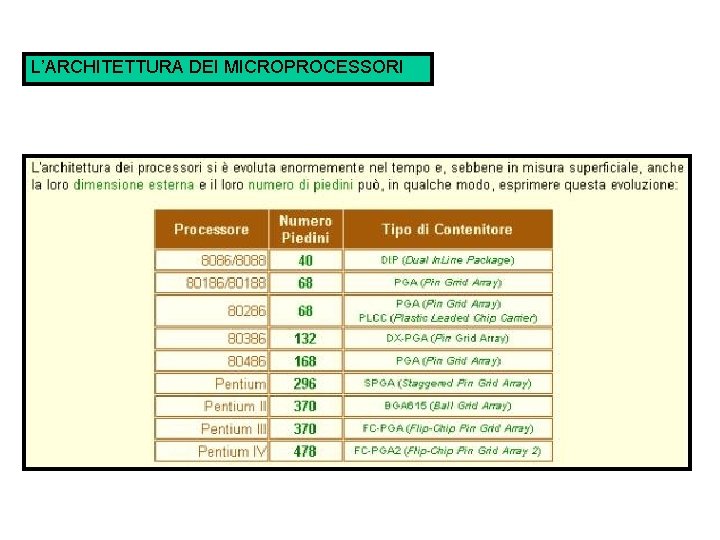

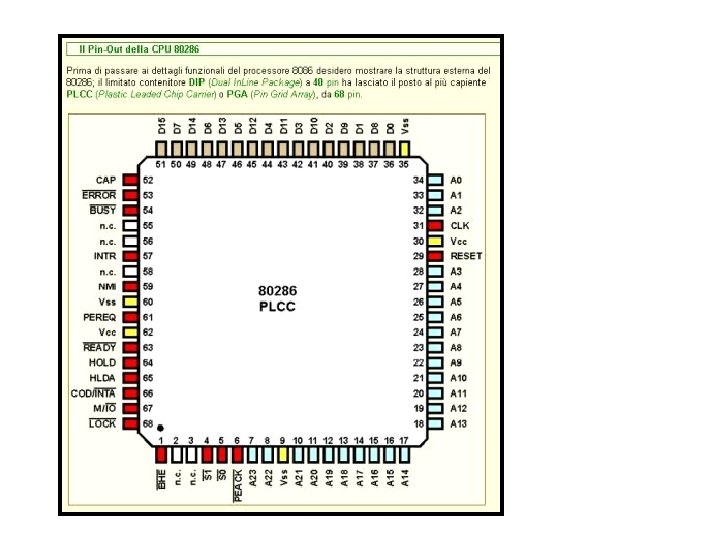

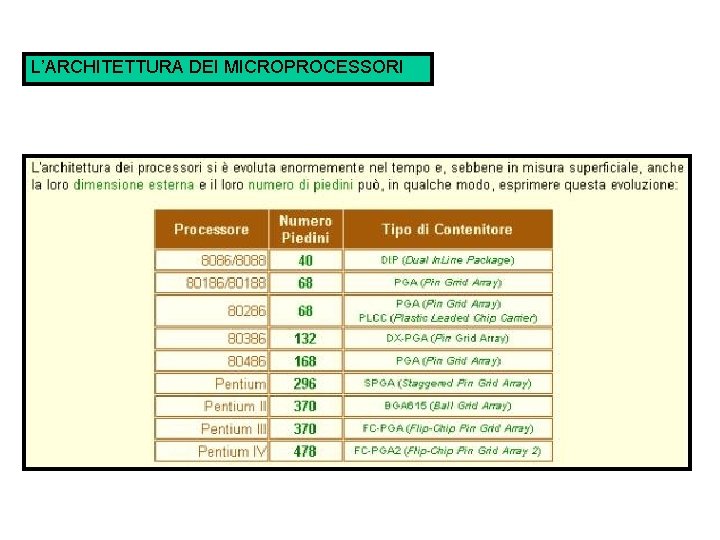

L’ARCHITETTURA DEI MICROPROCESSORI

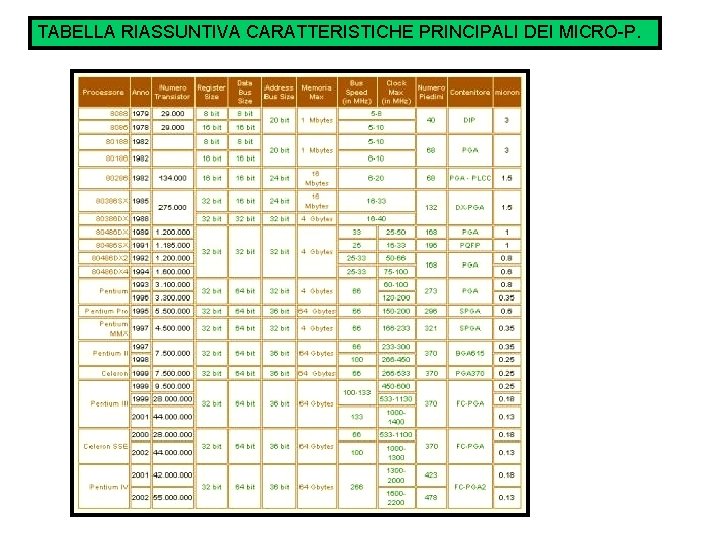

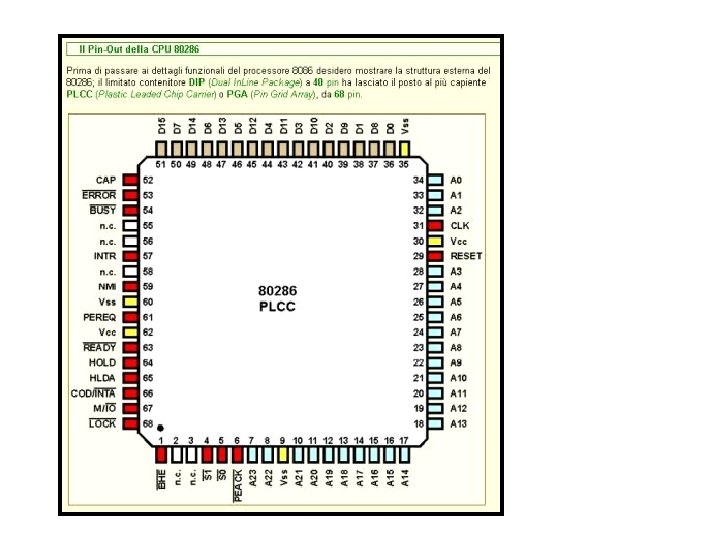

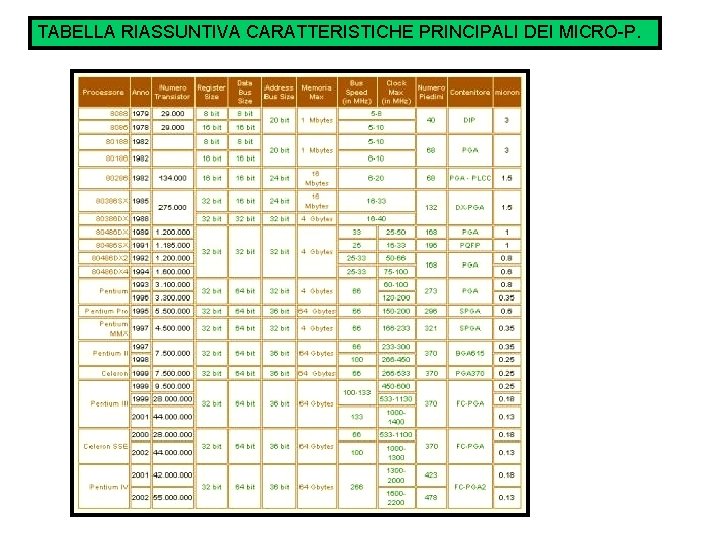

TABELLA RIASSUNTIVA CARATTERISTICHE PRINCIPALI DEI MICRO-P.

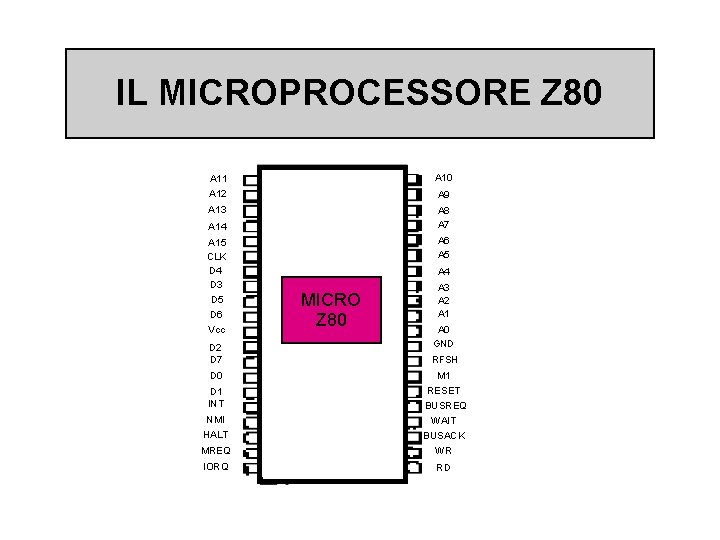

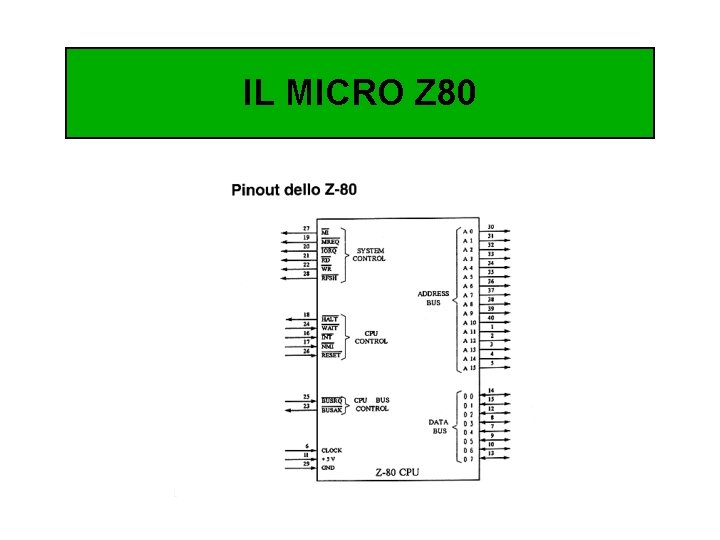

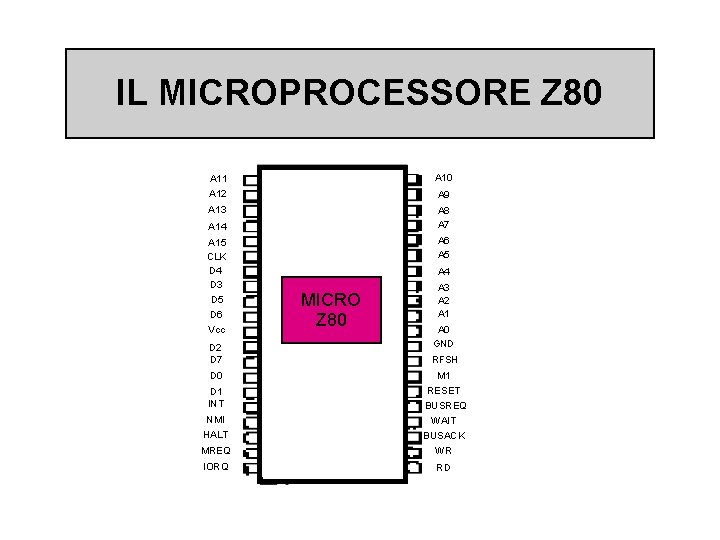

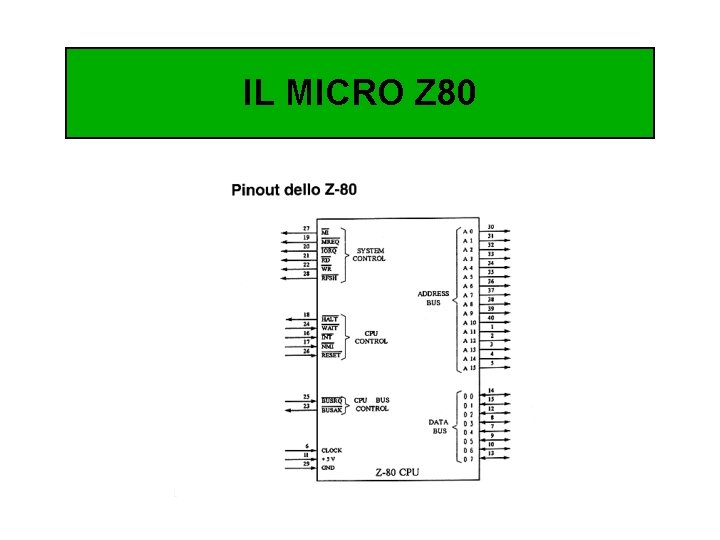

IL MICROPROCESSORE Z 80 A 11 A 12 A 13 A 9 A 8 A 9 A 14 A 7 A 15 CLK D 4 D 3 D 5 D 6 Vcc A 6 A 5 D 2 D 7 D 0 A 4 MICRO Z 80 A 3 A 2 A 1 A 0 GND RFSH MREQ M 1 RESET BUSREQ WAIT BUSACK WR IORQ RD D 1 INT NMI HALT

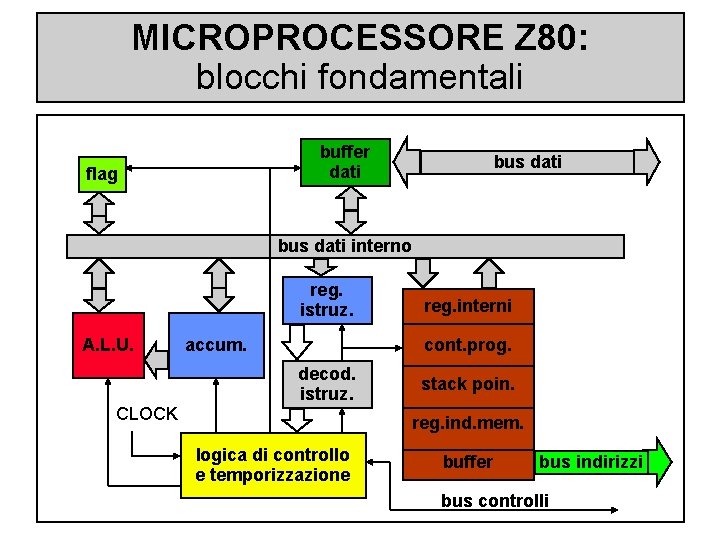

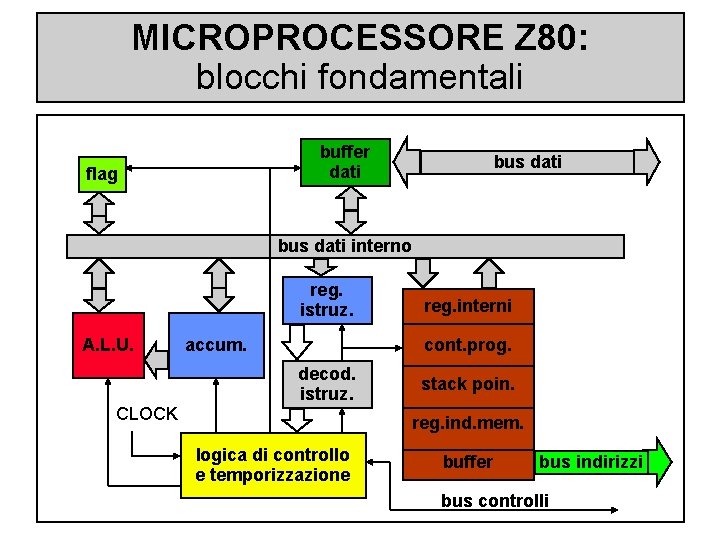

MICROPROCESSORE Z 80: blocchi fondamentali buffer dati flag bus dati interno reg. istruz. A. L. U. accum. reg. interni cont. prog. decod. istruz. CLOCK stack poin. reg. ind. mem. logica di controllo e temporizzazione buffer bus indirizzi bus controlli

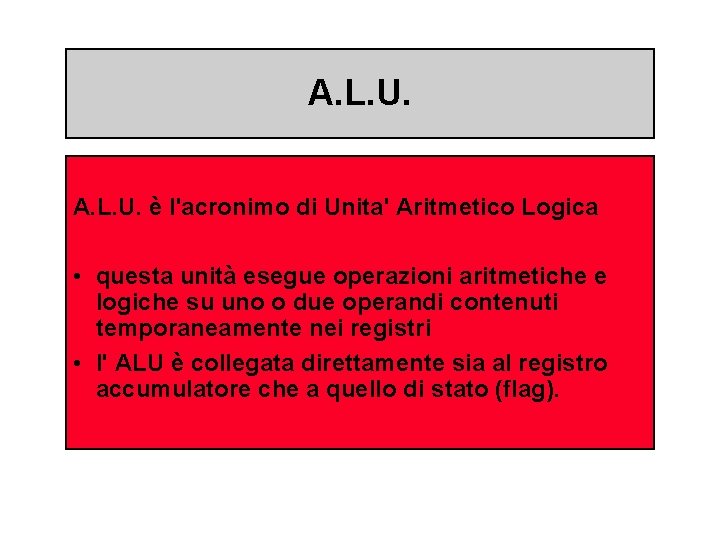

A. L. U. è l'acronimo di Unita' Aritmetico Logica • questa unità esegue operazioni aritmetiche e logiche su uno o due operandi contenuti temporaneamente nei registri • l' ALU è collegata direttamente sia al registro accumulatore che a quello di stato (flag).

REGISTRI • Un registro è costituito da un insieme di flip-flop dove è possibile memorizzare temporaneamente un dato. • i registri più importanti sono: l'accumulatore, quello di stato, il contatore programma, il registro istruzioni, quello di indirizzi di memoria , lo stack pointer e i registri di uso generale. • Ciascun registro ha una capacità di 8 o 16 bit.

LOGICA DI CONTROLLO • Tale blocco permette a tutte le parti del micro di lavorare nella corretta sequenza temporale. • La funzione principale è quella di decodificare ciascuna istruzione di programma ed emettere i segnali di controllo per eseguire tale istruzione. • Da essa dipartono tutti i segnali del bus di controllo interno ed esterno.

IL MICRO Z 80

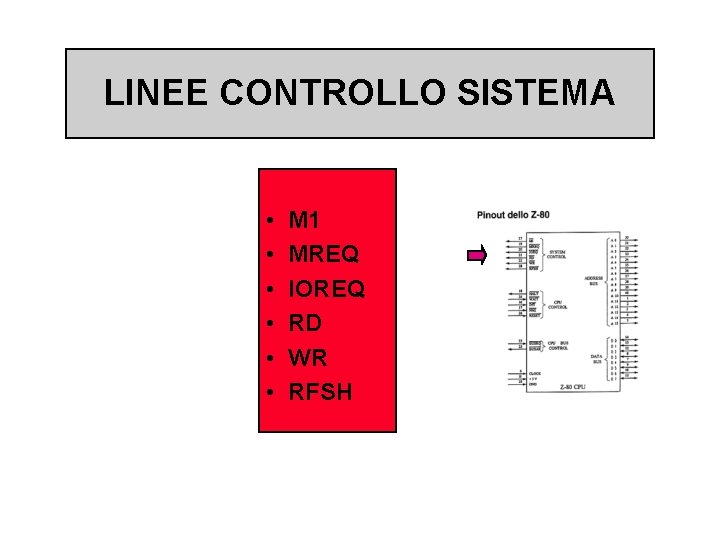

LINEE CONTROLLO SISTEMA • • • M 1 MREQ IOREQ RD WR RFSH

LINEE CONTROLLO CPU • • • HALT WAIT NMI INT RESET

LINEE CONTROLLO BUS • BUSREQ • BUSACK

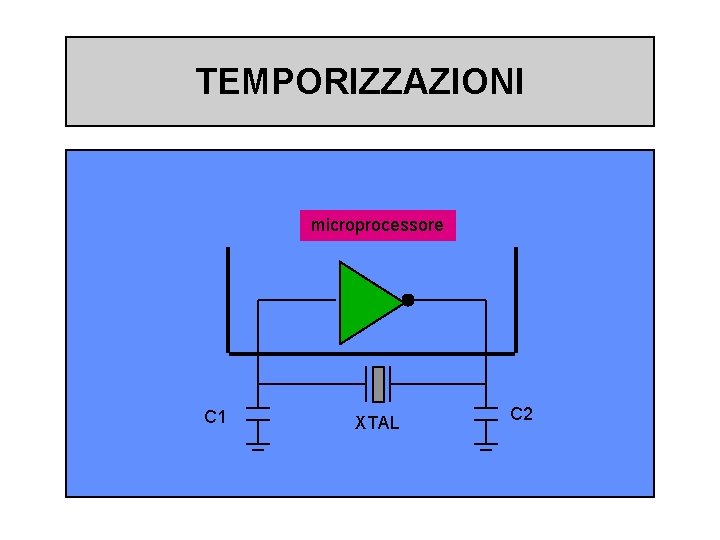

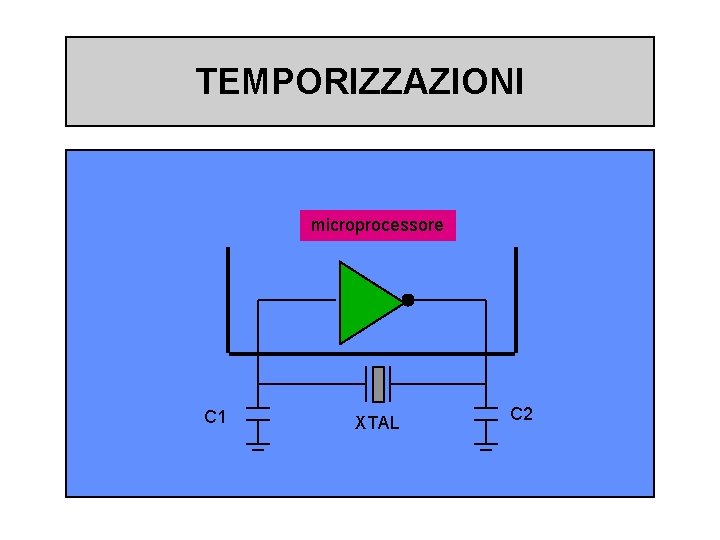

TEMPORIZZAZIONI microprocessore C 1 XTAL C 2

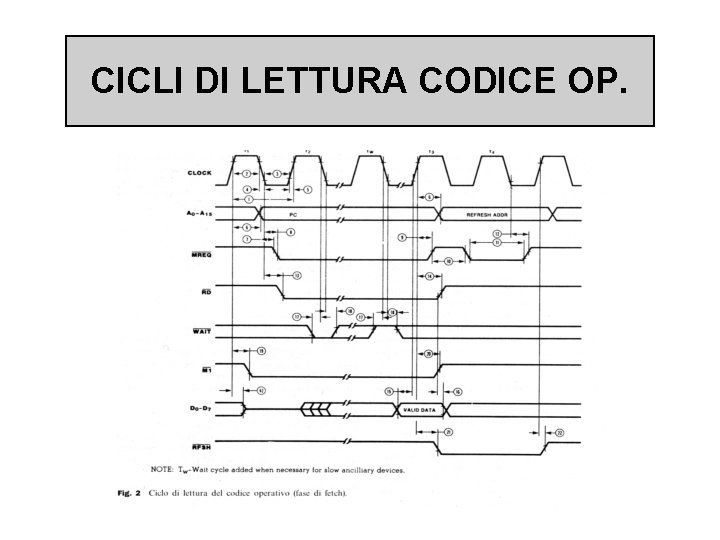

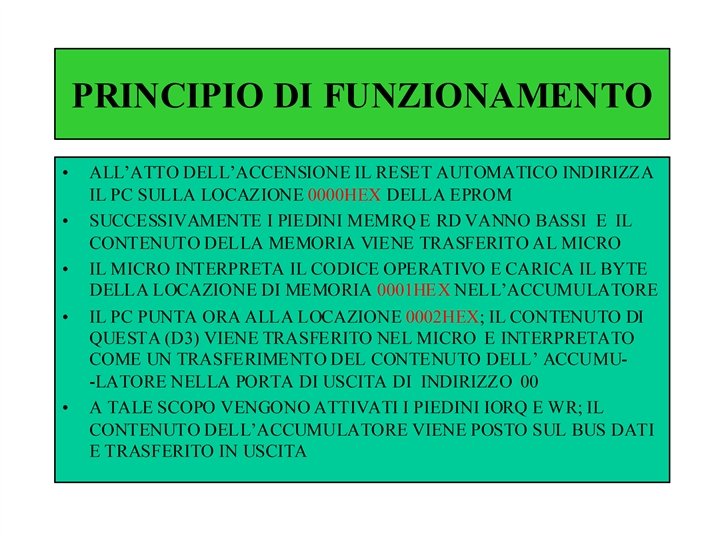

TEMPORIZZAZIONI • L' ESECUZIONE DI UNA ISTRUZIONE PREVEDE DUE FASI: – FASE DI FETCH – FASE DI EXECUTE • IL CICLO DI ISTRUZIONE E' COSTITUITO DA UNA SEQUENZA DI PASSI DETTA CICLO MACCHINA

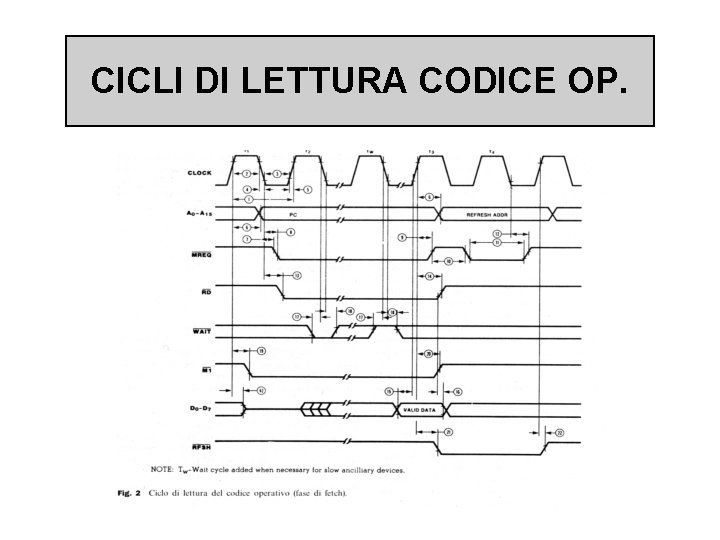

CICLI DI LETTURA CODICE OP.

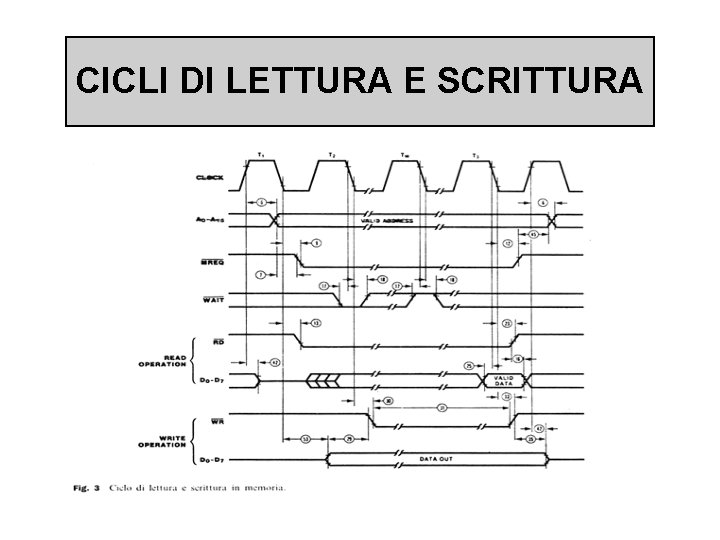

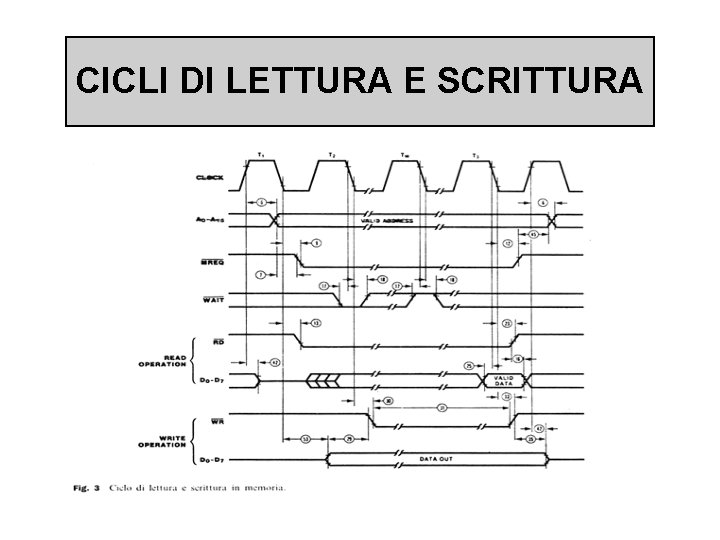

CICLI DI LETTURA E SCRITTURA

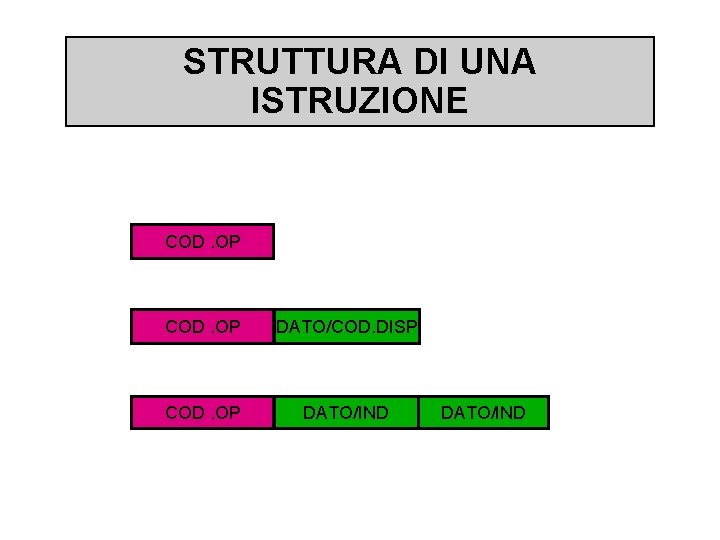

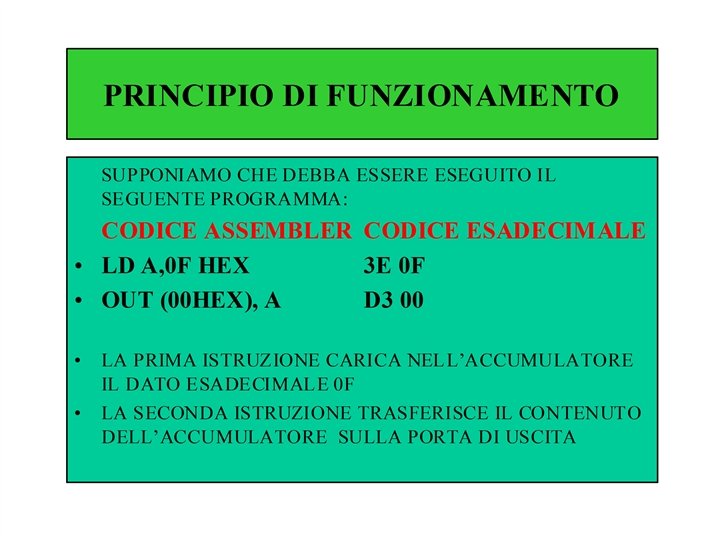

MICROPROCESSORE : set di istruzioni • UNA ISTRUZIONE E' COSTITUITA DA UN GRUPPO DI CARATTERI CHE DETERMINANO UNA SPECIFICA OPERAZIONE. • CIASCUNA ISTRUZIONE PUO' ESPRESSA IN VARIE FORME : ESSERE – IN CODICE MACCHINA (codice oggetto) – IN CODICE ASSEMBLER (codice sorgente)

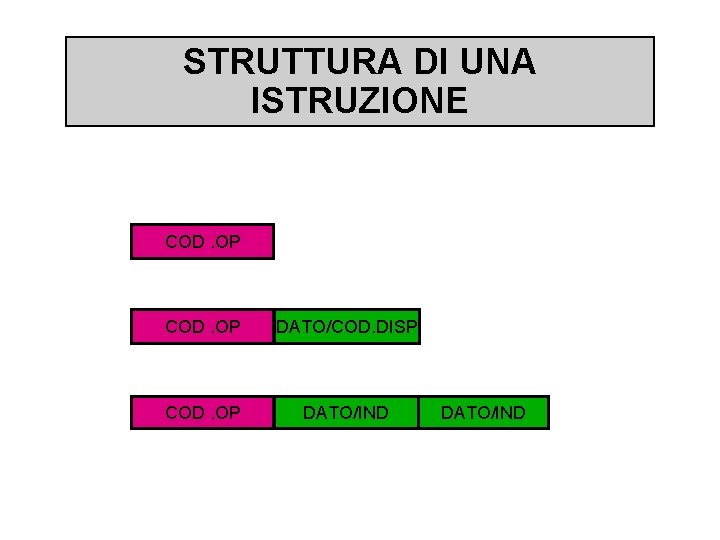

STRUTTURA DI UNA ISTRUZIONE COD. OP DATO/COD. DISP COD. OP DATO/IND

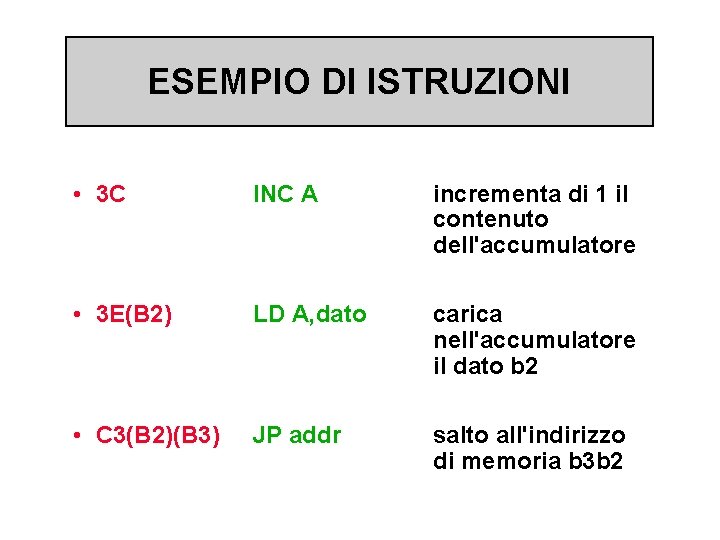

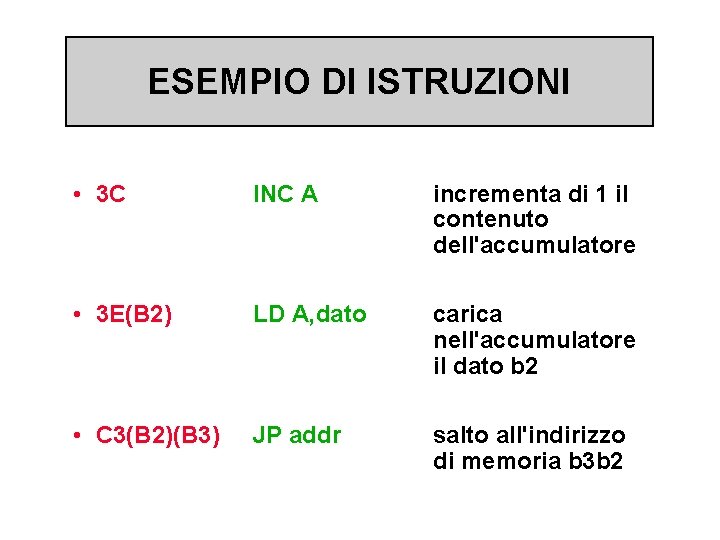

ESEMPIO DI ISTRUZIONI • 3 C INC A incrementa di 1 il contenuto dell'accumulatore • 3 E(B 2) LD A, dato carica nell'accumulatore il dato b 2 • C 3(B 2)(B 3) JP addr salto all'indirizzo di memoria b 3 b 2

MICROPROCESSORE : istruzioni fondamentali • TRASFERIMENTO DATI • ARITMETICO- LOGICHE • SALTO CHIAMATA E RITORNO • MANIPOLAZIONE DEI BIT • ROTAZIONE E SCORRIMENTO • DI I/O E CONTROLLO MACCHINA

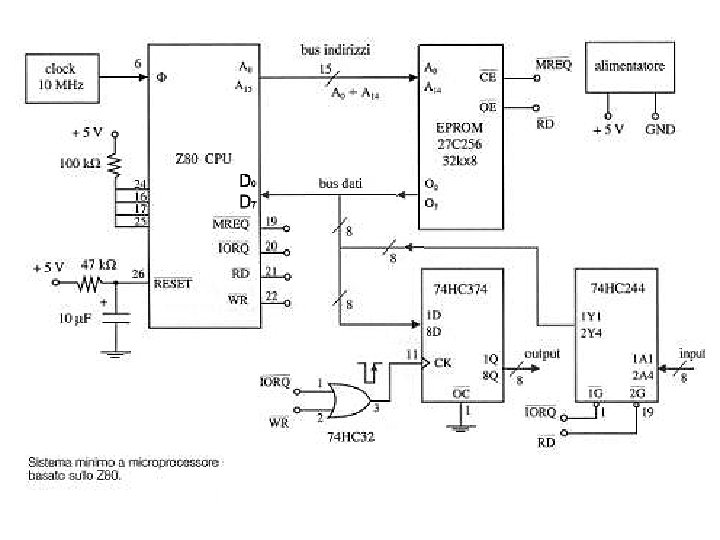

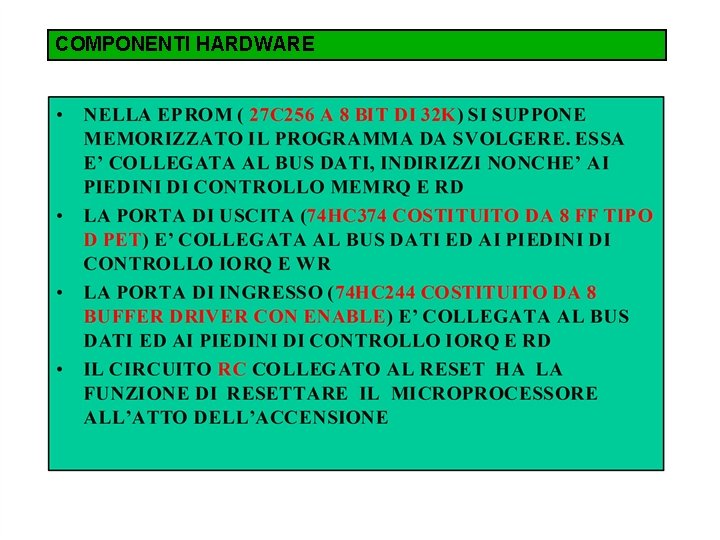

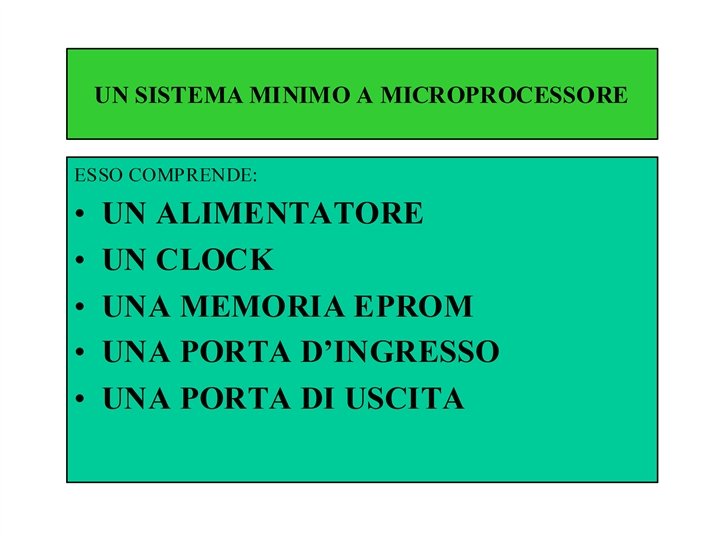

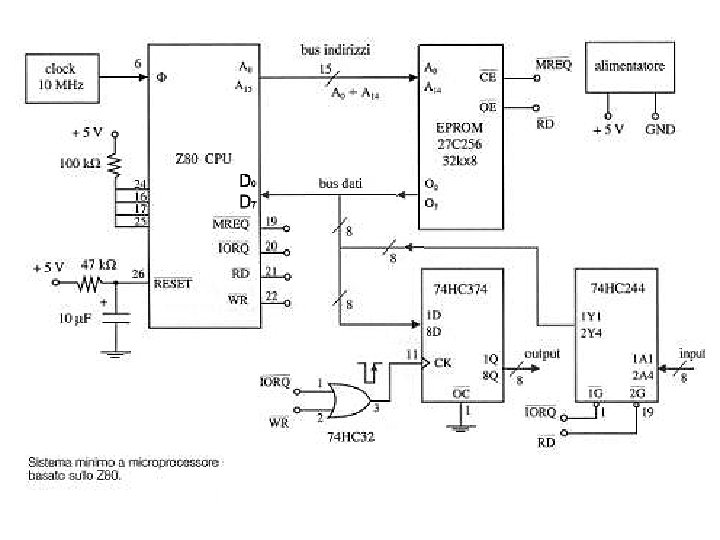

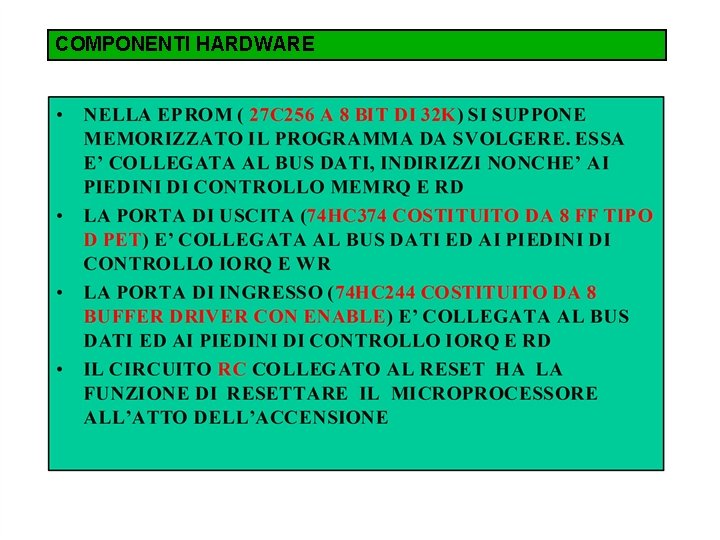

COMPONENTI HARDWARE

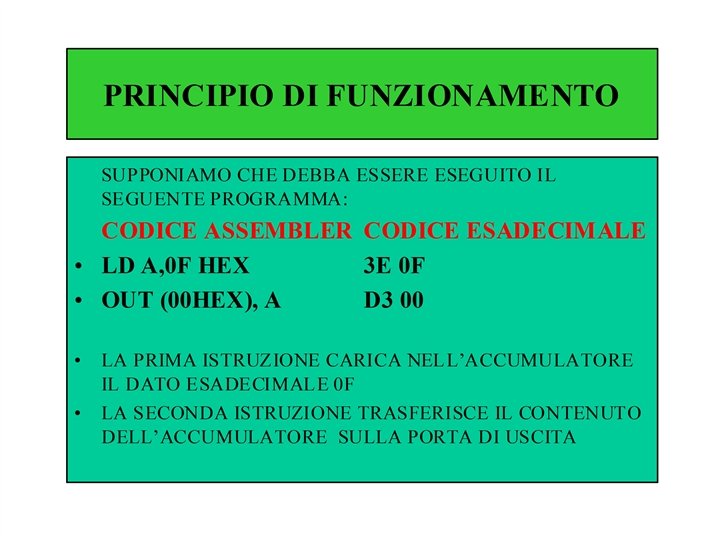

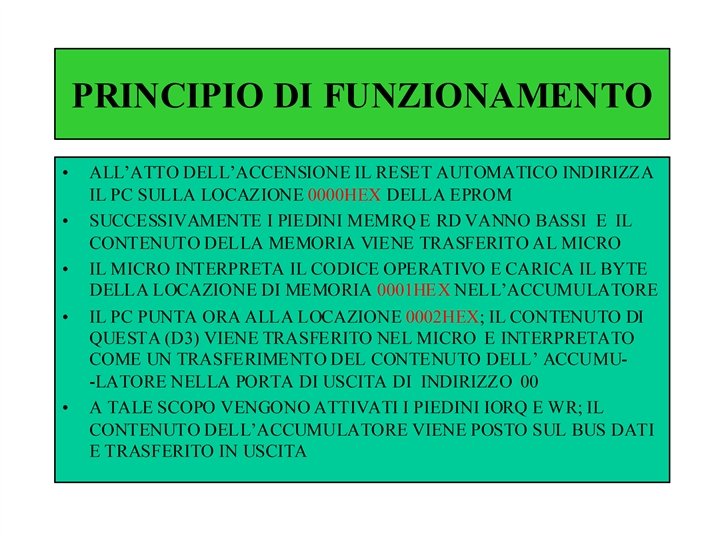

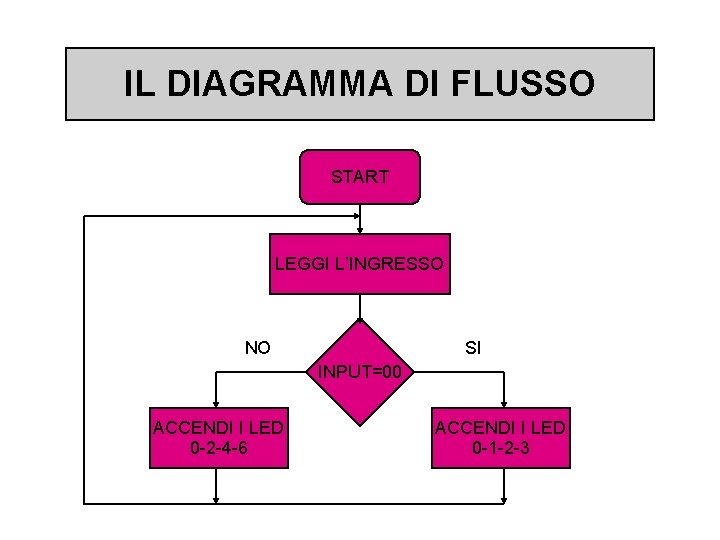

PROGRAMMA DI I/O NOTE: • QUANDO SI ESEGUE UN PROGRAMMA CONVIENE INIZIALMENTE TRACCIARE IL DIAGRAMMA DI FLUSSO CHE RIASSUME LE OPERAZIONI LOGICHE BISOGNA SVOLGERE • SUCCESSIVAMENTE SI TRASCRIVE IL PROGRAMMA ASSEMBLER E OVE NECESSARIO QUELLO IN CODICE MACCHINA

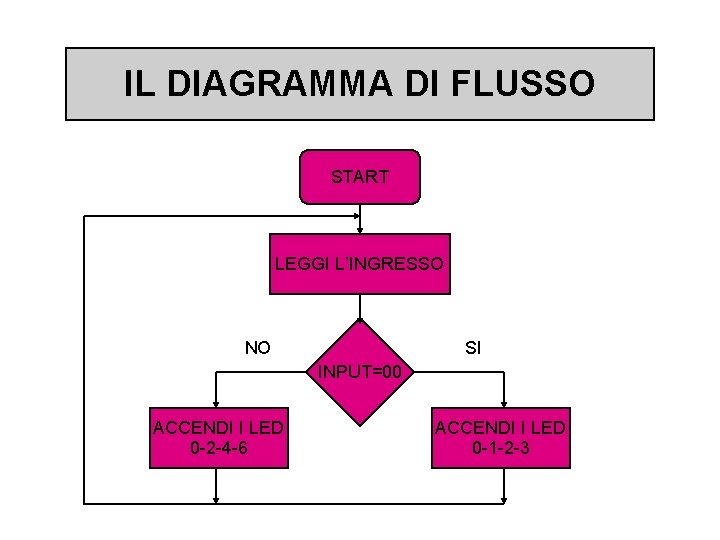

IL DIAGRAMMA DI FLUSSO START LEGGI L’INGRESSO NO SI INPUT=00 ACCENDI I LED 0 -2 -4 -6 ACCENDI I LED 0 -1 -2 -3

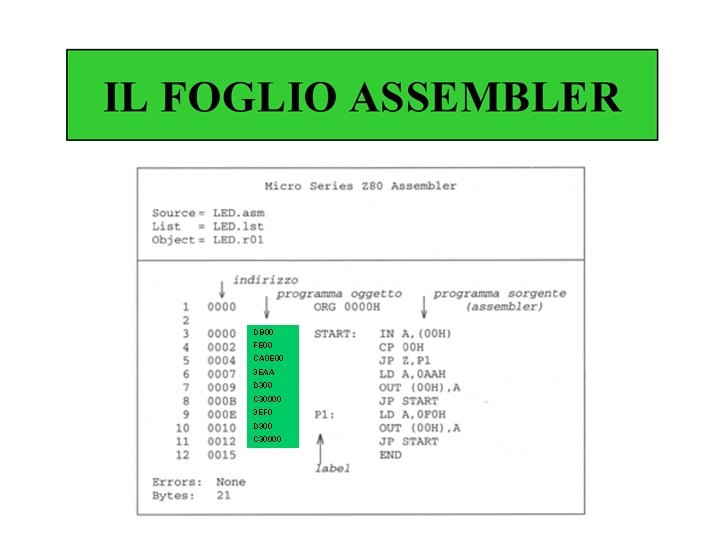

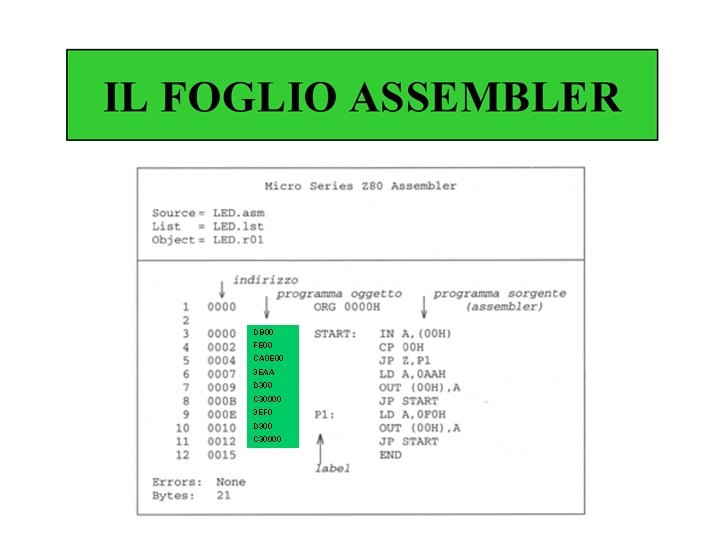

DB 00 FE 00 CA 0 E 00 3 EAA D 300 C 30000 3 EF 0 D 300 C 30000

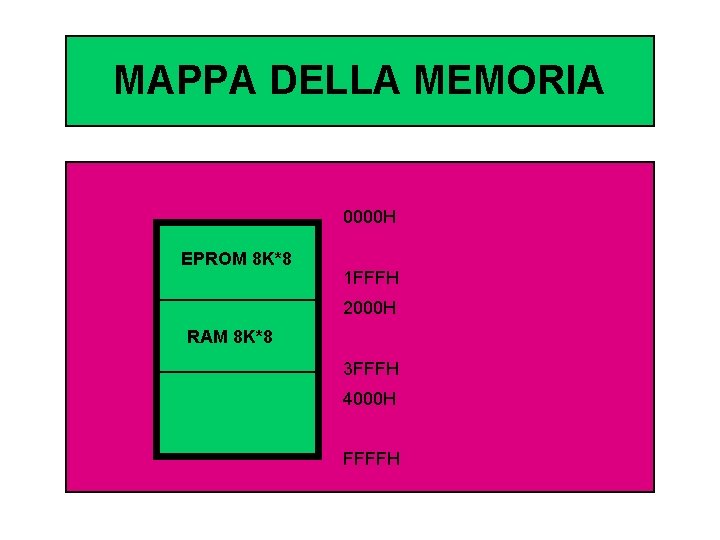

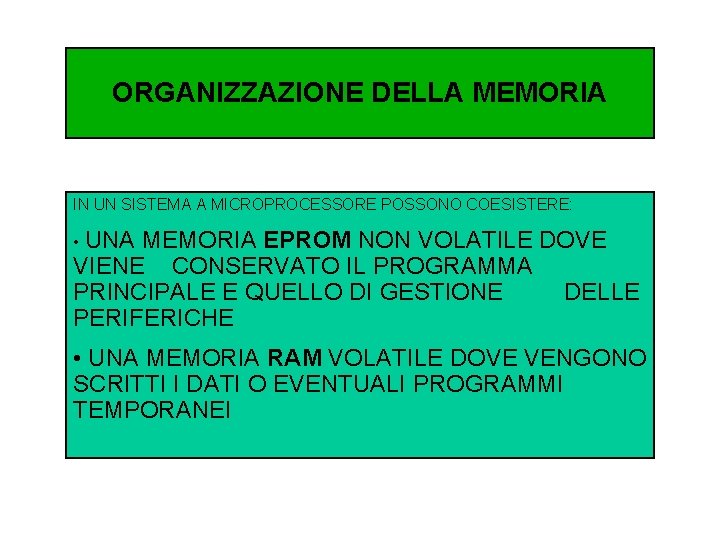

ORGANIZZAZIONE DELLA MEMORIA IN UN SISTEMA A MICROPROCESSORE POSSONO COESISTERE: • UNA MEMORIA EPROM NON VOLATILE DOVE VIENE CONSERVATO IL PROGRAMMA PRINCIPALE E QUELLO DI GESTIONE DELLE PERIFERICHE • UNA MEMORIA RAM VOLATILE DOVE VENGONO SCRITTI I DATI O EVENTUALI PROGRAMMI TEMPORANEI

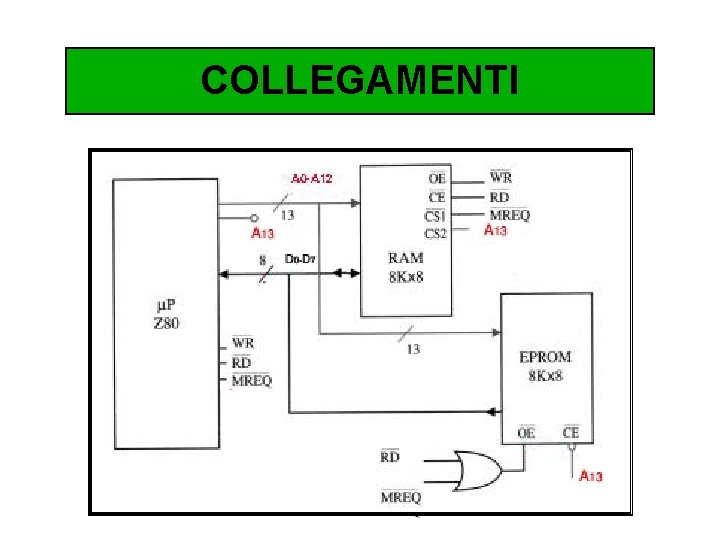

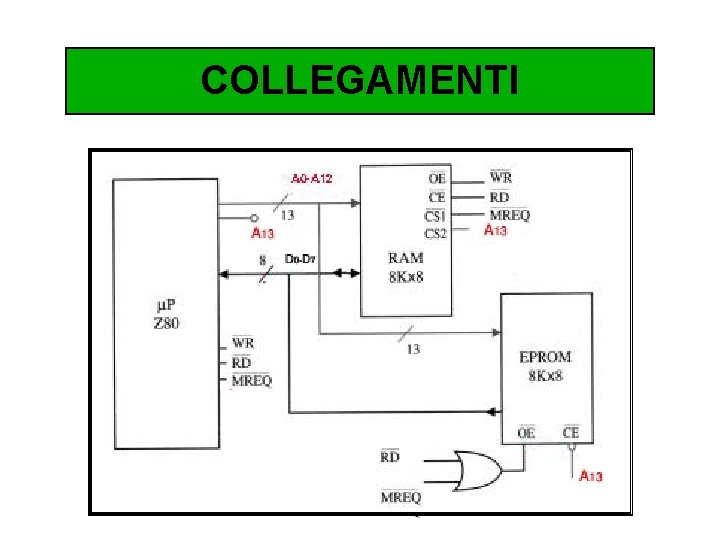

COLLEGAMENTI A 0 -A 12 A 13 D 0 -D 7 A 13

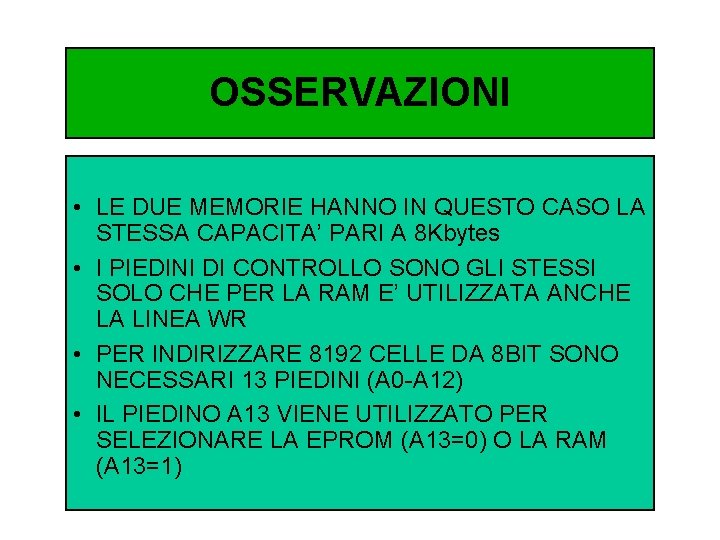

OSSERVAZIONI • LE DUE MEMORIE HANNO IN QUESTO CASO LA STESSA CAPACITA’ PARI A 8 Kbytes • I PIEDINI DI CONTROLLO SONO GLI STESSI SOLO CHE PER LA RAM E’ UTILIZZATA ANCHE LA LINEA WR • PER INDIRIZZARE 8192 CELLE DA 8 BIT SONO NECESSARI 13 PIEDINI (A 0 -A 12) • IL PIEDINO A 13 VIENE UTILIZZATO PER SELEZIONARE LA EPROM (A 13=0) O LA RAM (A 13=1)

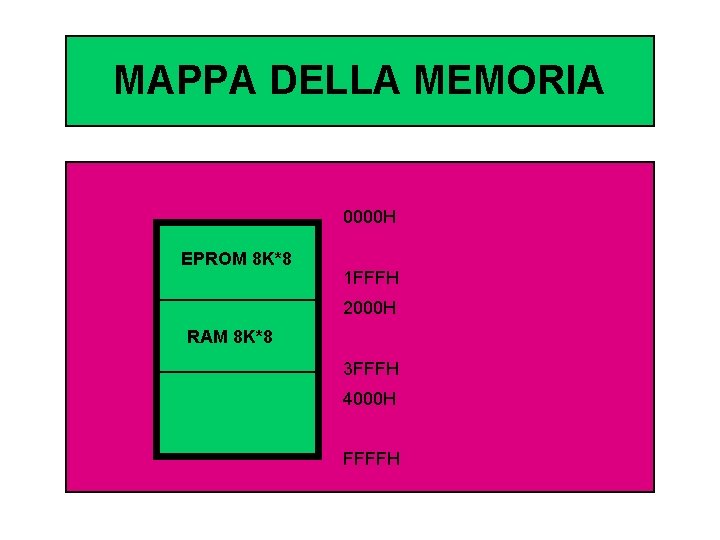

INDIRIZZI IN QUESTO MODO : • ALLA EPROM COMPETONO GLI INDIRIZZI DI CELLA COMPRESI TRA 0000 H-1 FFFH • ALLA RAM COMPETONO GLI INDIRIZZI DI CELLA COMPRESI TRA 2000 H-3 FFFH

MAPPA DELLA MEMORIA 0000 H EPROM 8 K*8 1 FFFH 2000 H RAM 8 K*8 3 FFFH 4000 H FFFFH