Overview of Microprocessors Lecturer Sri Parameswaran Notes by

Overview of Microprocessors Lecturer: Sri Parameswaran Notes by : Annie Guo Week 3 1

Lecture overview l l l Introduction to microprocessors Instruction set architecture Typical commercial microprocessors Week 3 2

Microprocessors l l A microprocessor is a CPU on a single chip. If a microprocessor, its associated support circuitry, memory and peripheral I/O components are implemented on a single chip, it is a microcontroller. l We use AVR microcontroller as the example in our course study Week 3 3

Microprocessor types l Microprocessors can be characterized based on l the word size l l Instruction set structure l l RISC (Reduced Instruction Set Computer), CISC (Complex Instruction Set Computer) Functions l l 8 bit, 16 bit, 32 bit, etc. processors General purpose, special purpose such image processing, floating point calculations And more … Week 3 4

Typical microprocessors l Most commonly used l 68 K l l x 86 l l l Advanced RISC Machine Power. PC l l Microprocessor without interlocked pipeline stages ARM l l Intel MIPS l l Intel IA-64 l l Motorola Apple-IBM-Motorola alliance Atmel AVR A brief summary will be given later Week 3 5

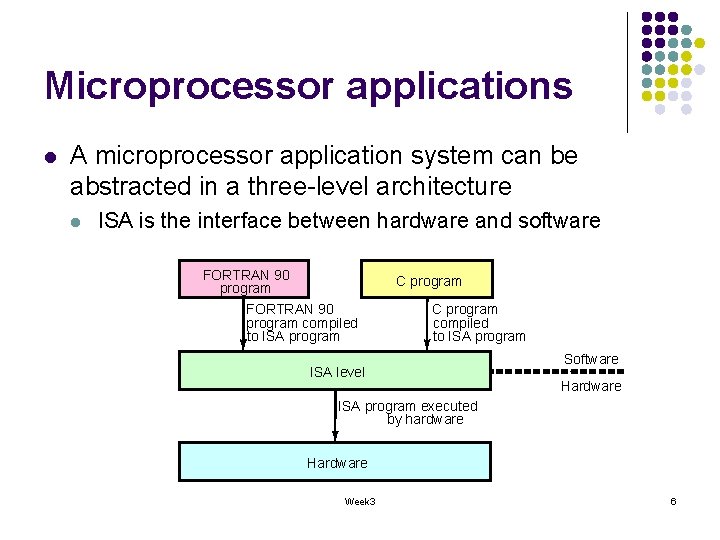

Microprocessor applications l A microprocessor application system can be abstracted in a three-level architecture l ISA is the interface between hardware and software FORTRAN 90 program C program FORTRAN 90 program compiled to ISA program C program compiled to ISA program ISA level Software Hardware ISA program executed by hardware Hardware Week 3 6

ISA l l l Stands for Instruction Set Architecture Provides functional specifications for software programmers to use/program hardware to perform certain tasks Provides the functional requirements for hardware designers so that their hardware design (called micro-architectures) can execute software programs. Week 3 7

What makes an ISA l ISA specifies all aspects of a computer architecture visible to a programmer l Basic l Instructions § § l l Instruction format Addressing modes Native data types Registers Memory models advanced l Interrupt handling § Week 3 To be covered in the later lectures 8

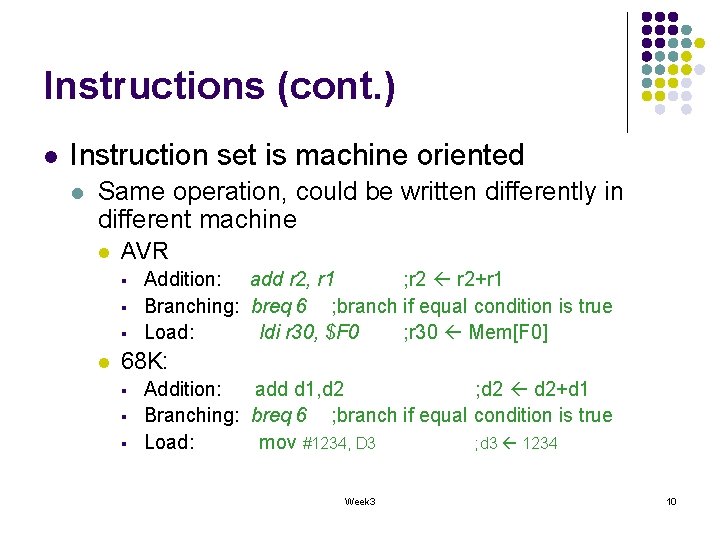

Instructions l This is the key part of an ISA l l specifies the basic operations available to a programmer Example: l l Arithmetic instructions Instruction set is machine oriented l Different machine, different instruction set l For example § 68 K has more comprehensive instruction set than ARM Week 3 9

Instructions (cont. ) l Instruction set is machine oriented l Same operation, could be written differently in different machine l AVR § § § l Addition: add r 2, r 1 ; r 2+r 1 Branching: breq 6 ; branch if equal condition is true Load: ldi r 30, $F 0 ; r 30 Mem[F 0] 68 K: § § § Addition: add d 1, d 2 ; d 2+d 1 Branching: breq 6 ; branch if equal condition is true Load: mov #1234, D 3 ; d 3 1234 Week 3 10

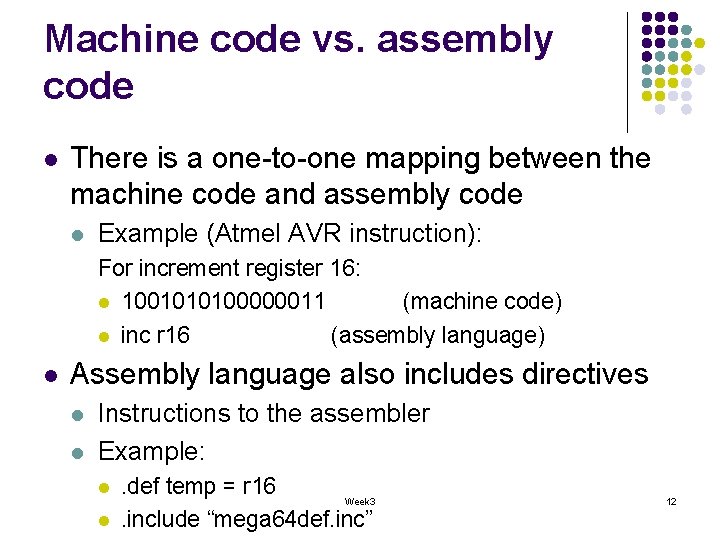

Instructions (cont. ) l Instructions can be written in two languages l Machine language l l l made of binary digits Used by machines Assembly language l l l a textual representation of machine language Easier to understand than machine language Used by human beings Week 3 11

Machine code vs. assembly code l There is a one-to-one mapping between the machine code and assembly code l Example (Atmel AVR instruction): For increment register 16: l 1001010100000011 (machine code) l inc r 16 (assembly language) l Assembly language also includes directives l l Instructions to the assembler Example: l l . def temp = r 16 Week 3. include “mega 64 def. inc” 12

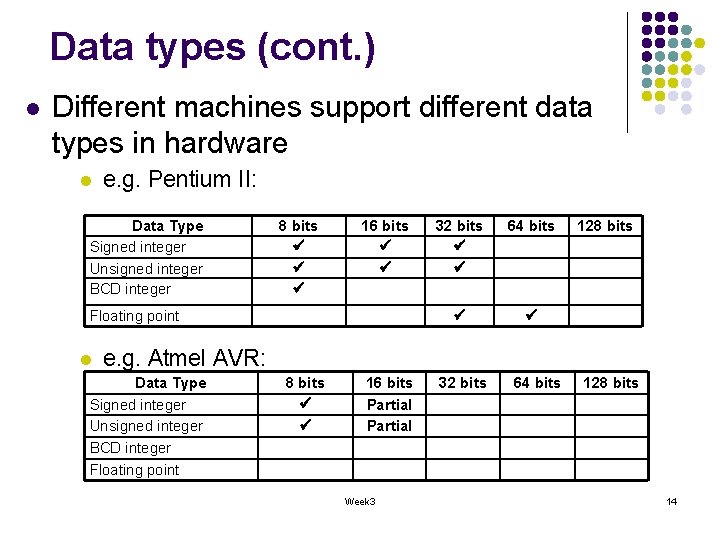

Data types l l The basic capability of using different classes of values. Typical data types l Numbers l Integers of different lengths (8, 16, 32, 64 bits) § § l Floating point numbers, e. g. 32 bits (single precision) or 64 bits (double precision) § l Available in some processors such as Power. PC BCD (binary coded decimal) numbers § l Possibly signed or unsigned Commonly available Available in some processors, such as 68 K Non-numeric l l Boolean Characters Week 3 13

Data types (cont. ) l Different machines support different data types in hardware l e. g. Pentium II: Data Type Signed integer Unsigned integer BCD integer 8 bits 16 bits Floating point l 32 bits 64 bits 128 bits e. g. Atmel AVR: Data Type Signed integer Unsigned integer BCD integer Floating point 8 bits 16 bits Partial Week 3 32 bits 64 bits 128 bits 14

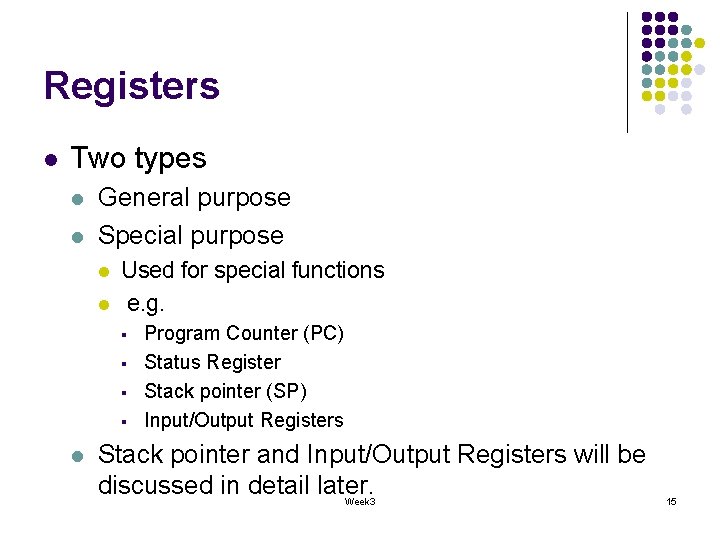

Registers l Two types l l General purpose Special purpose l l Used for special functions e. g. § § l Program Counter (PC) Status Register Stack pointer (SP) Input/Output Registers Stack pointer and Input/Output Registers will be discussed in detail later. Week 3 15

General Purpose Registers l A set of registers in the machine l l l Used for storing temporary data/results For example l In (68 K) instruction add d 3, d 5, operands are stored in general registers d 3 and d 5, and the result are stored in d 5. Can be structured differently in different machines l For example l Separated general purpose registers for data and address § l 68 K Different numbers registers and different size of each registers § § 32 32 -bit in MIPS 16 32 -bit in ARM Week 3 16

Program counter l Special register l l Can be of different size l l For storing memory address of currently executed instruction E. g. 16 bit, 32 bit Can be auto-incremented l l By the instruction word size Gives rise the name “counter” Week 3 17

Status register l l Contains a number of bits with each bit associated with CPU operations Typical status bits l l l V: Overflow C: Carry Z: Zero N: Negative Used for controlling program execution flow Week 3 18

Memory models l l Data processed by CPU is usually large and cannot be held in the registers at the same time. Both data and program code need to be stored in memory. Memory model is related to how memory is used to store data Issues l l Addressable unit size Address spaces Endianness Alignment Week 3 19

Addressable unit size l l l Memory has units, each of which has an address Most common unit size is 8 bits (1 byte) Modern processors have multiple-byte unit l For example: l l 32 -bit instruction memory in MIPs 16 -bit Instruction memory in AVR Week 3 20

Address spaces l The range of addresses a processor can access. l The address space can be one or more than one in a processor. For example l Princeton architecture or Von Neumann architecture § l A single linear address space for both instructions and data memory Harvard architecture § Separate address spaces for instructions and data memories Week 3 21

Address spaces (cont. ) l Address space is not necessarily just for memories l l E. g, all general purpose registers and I/O registers can be accessed through memory addresses in AVR Address space is limited by the width of the address bus. l The bus width: the number of bits the address is represented Week 3 22

Endianness l Memory objects are basic entities that can be accessed as a function of the address and the length l l E. g. bytes, words, longwords For large objects (>byte), there are two ordering conventions l Little endian – little end (least significant byte) stored first (at lowest address) l l Intel microprocessors (Pentium etc) Big endian – big end stored first l SPARC, Motorola microprocessors Week 3 23

Endianness (cont. ) l Most CPUs produced since ~1992 are “bi-endian” (support both) l l some switchable at boot time others at run time (i. e. can change dynamically) Week 3 24

Big Endian & Little Endian l Example: 0 x 12345678—a long word of 4 bytes. It is stored in the memory at address 0 x 00000100 l l big endian: little endian: Address 0 x 00000100 0 x 00000101 0 x 00000102 0 x 00000103 data 12 34 56 78 Address 0 x 00000100 0 x 00000101 0 x 00000102 0 x 00000103 Week 3 data 78 56 34 12 25

Alignment l l Often multiple bytes can be fetched from memory Alignment specifies how the (beginning) address of a multiple-byte data is determined. l data must be aligned in some way. For example l l l 4 -byte words starting at addresses 0, 4, 8, … 8 -byte words starting at addresses 0, 8, 16, … Alignment makes memory data accessing more efficient Week 3 26

Example l A hardware design that has data fetched from memory every 4 bytes l Fetching an unaligned data (as shown) means to access memory twice. Week 3 27

Instruction format l Is a definition l l how instructions are represented in binary code Instructions typically consist of l Opcode (Operation Code) l l Operands l l defines the operation (e. g. addition) what’s being operated on Instructions typically have 0, 1, 2 or 3 operands Week 3 28

Instruction format examples Op. Code Opd 1 Op. Code Opd 2 Op. Code Opd 1 Week 3 Opd 2 Opd 3 29

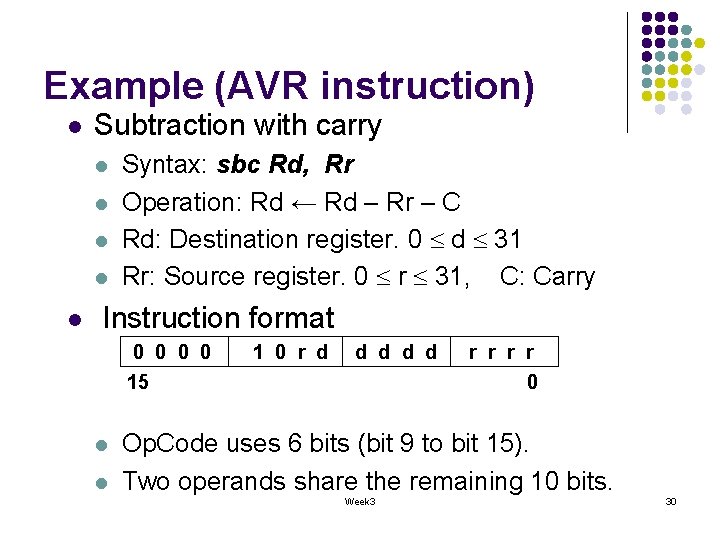

Example (AVR instruction) l Subtraction with carry l l l Syntax: sbc Rd, Rr Operation: Rd ← Rd – Rr – C Rd: Destination register. 0 d 31 Rr: Source register. 0 r 31, C: Carry Instruction format 0 0 15 l l 1 0 r d d d r r 0 Op. Code uses 6 bits (bit 9 to bit 15). Two operands share the remaining 10 bits. Week 3 30

Instruction lengths l l The number of bits an instruction has For some machines – instructions all have the same length l l E. g. MIPS machines For other machines – instructions can have different lengths l E. g. M 68 K machine Week 3 31

Instruction encoding l Operation Encoding l l 2 n operations needs at least n bits Operand Encoding l Depends on the addressing modes and access space. l l For example: An operand in direct register addressing mode requires at most 3 bits if the number of registers it can be stored is 8. With a fixed instruction length, more encoding of operations means less available bits for encoding operands l Week 3 Tradeoffs should be concerned 32

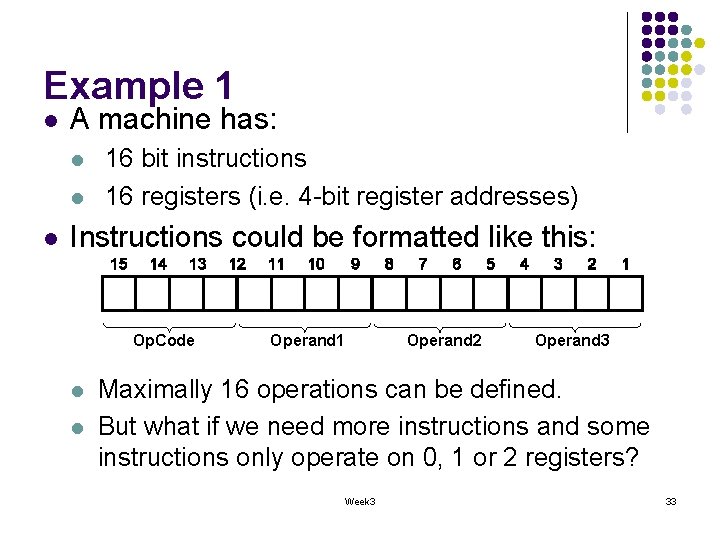

Example 1 l A machine has: l l l 16 bit instructions 16 registers (i. e. 4 -bit register addresses) Instructions could be formatted like this: Op. Code l l Operand 1 Operand 2 Operand 3 Maximally 16 operations can be defined. But what if we need more instructions and some instructions only operate on 0, 1 or 2 registers? Week 3 33

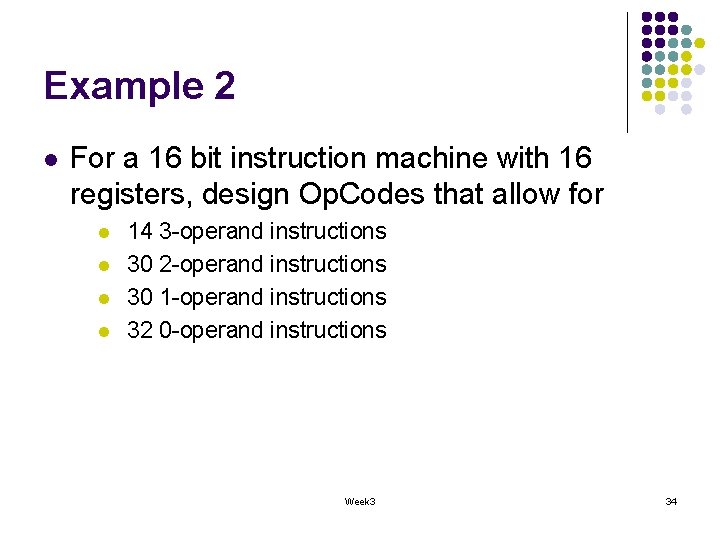

Example 2 l For a 16 bit instruction machine with 16 registers, design Op. Codes that allow for l l 14 3 -operand instructions 30 2 -operand instructions 30 1 -operand instructions 32 0 -operand instructions Week 3 34

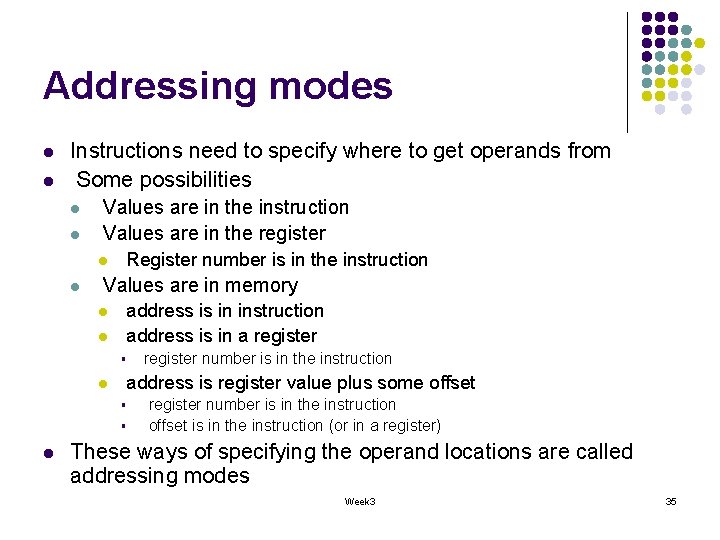

Addressing modes l l Instructions need to specify where to get operands from Some possibilities l l Values are in the instruction Values are in the register l l Register number is in the instruction Values are in memory l l address is in instruction address is in a register § l address is register value plus some offset § § l register number is in the instruction offset is in the instruction (or in a register) These ways of specifying the operand locations are called addressing modes Week 3 35

Immediate Addressing l The operand is from the instruction itself l l I. e the operand is immediately available from the instruction For example, in 68 K addw l l #99, d 7 Perform d 7 99 + d 7; value 99 comes from the instruction d 7 is a register Week 3 36

Register Direct Addressing l l Data from a register and the register number is directly given by the instruction For example, in 68 K addw l l d 0, d 7 Perform d 7 + d 0; add value in d 0 to value in d 7 and store result to d 7 d 0 and d 7 are registers Week 3 37

Memory direct addressing l l l The data is from memory, the memory address is directly given by the instruction We use notion: (addr) to represent memory value with a given address, addr For example, in 68 K addw l 0 x 123 A, d 7 Perform d 7 + (0 x 123 A); add value in memory location 0 x 123 A to register d 7 Week 3 38

Memory Register Indirect Addressing l l The data is from memory, the memory address is given by a register and the register number is directly given by the instruction For example, in 68 K addw l (a 0), d 7 Perform d 7 + (a 0); add value in memory with the address stored in register a 0, to register d 7 l For example, if a 0 = 100 and (100) = 123, then this adds 123 to d 7 Week 3 39

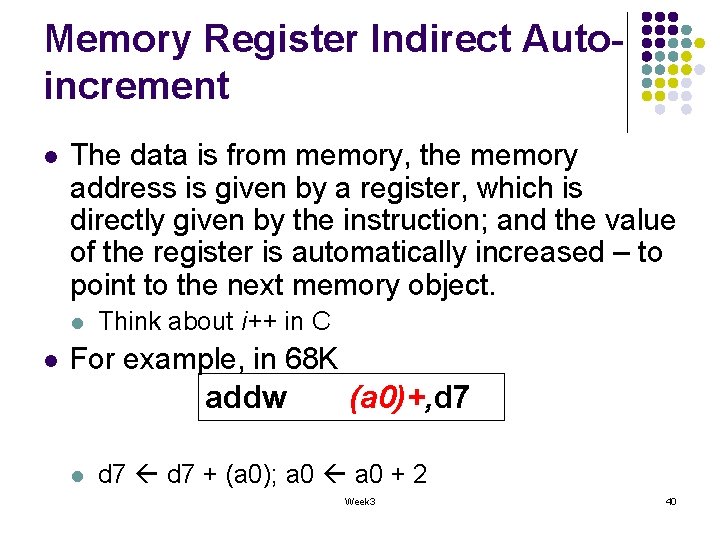

Memory Register Indirect Autoincrement l The data is from memory, the memory address is given by a register, which is directly given by the instruction; and the value of the register is automatically increased – to point to the next memory object. l l Think about i++ in C For example, in 68 K addw l (a 0)+, d 7 + (a 0); a 0 + 2 Week 3 40

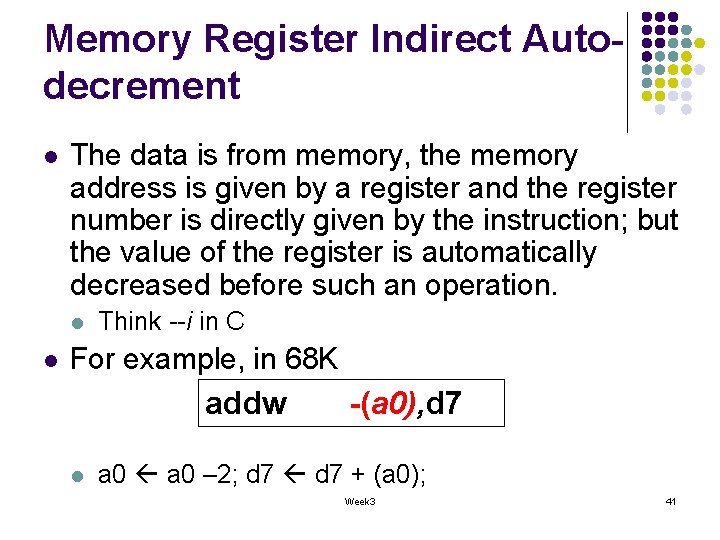

Memory Register Indirect Autodecrement l The data is from memory, the memory address is given by a register and the register number is directly given by the instruction; but the value of the register is automatically decreased before such an operation. l l Think --i in C For example, in 68 K addw l -(a 0), d 7 a 0 – 2; d 7 + (a 0); Week 3 41

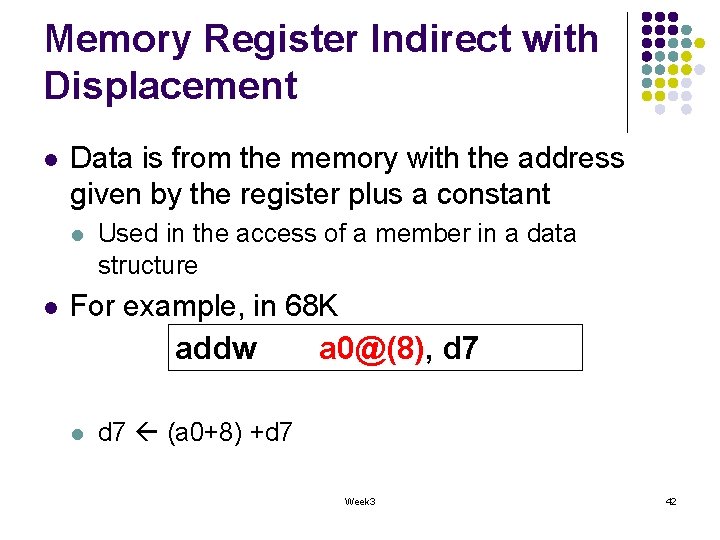

Memory Register Indirect with Displacement l Data is from the memory with the address given by the register plus a constant l l Used in the access of a member in a data structure For example, in 68 K addw l a 0@(8), d 7 (a 0+8) +d 7 Week 3 42

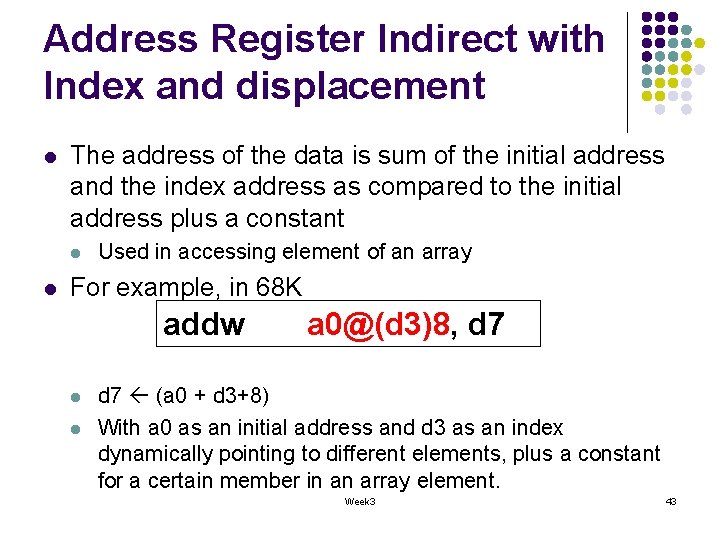

Address Register Indirect with Index and displacement l The address of the data is sum of the initial address and the index address as compared to the initial address plus a constant l l Used in accessing element of an array For example, in 68 K addw l l a 0@(d 3)8, d 7 (a 0 + d 3+8) With a 0 as an initial address and d 3 as an index dynamically pointing to different elements, plus a constant for a certain member in an array element. Week 3 43

RISC l RICS stands for reduced instruction set computer l Smaller and simpler set of instructions l l Smaller: small number of instructions in the instruction set Simpler: instruction encoding is simple § l Such as fixed instruction length All instructions take about the same amount of time to execute Week 3 44

CISC l CISC stands for complex instruction set computer l Each instructions can execute several low-level operations l l l Such operations of load memory, arithmetic and store memory in one instructions Required complicated hardware support All instructions take different amount of time to execute Week 3 45

Recall: Typical processors l Most commonly implemented in hardware l l l l 68 K l Motorola x 86 l Intel IA-64 l Intel MIPS l Microprocessor without interlocked pipeline stages ARM l Advanced RISC Machine Power. PC l Apple-IBM-Motorola alliance Week 3 Atmel AVR 46

X 86 l CISC architecture l l l 16 bit 32 -bit 64 -bit Words are stored in the little endian order Allow unaligned memory access. Current x 86 -processors employs a few “extra” decoding steps to (during execution) split (most) x 86 instructions into smaller pieces (micro-instructions) which are then readily executed by a RISC-like micro-architecture. Application areas (dominant) l Desktop, portable computer, small servers Week 3 47

68 K l CISC processor l l l Early generation, hybrid 8/16/32 bit chip (8 -bit bus) Late generation, fully 32 -bit Separate data registers and address registers Big endian Area applications l l Early used in for calculators, control systems, desktop computers Later used in microcontroller/embedded microprocessors. Week 3 48

MIPS l RISC processor l l l A large family designs with different configurations Deep pipeline (>=5 stages) With additional features l l Clean instruction set Could be booted either big-endian or little-endian Many application areas, including embedded systems The design of the MIPS CPU family, together with SPARC, another early RISC architecture, greatly influenced later RISC designs Week 3 49

ARM l 32 -bit RISC processor l l l Three-address architecture No support for misaligned memory accesses 16 x 32 bit register file Fixed opcode width of 32 bit to ease decoding and pipelining, at the cost of decreased code density Mostly single-cycle execution With additional features l Conditional execution of most instructions § § l reducing branch overhead and compensating for the lack of a branch predictor Powerful indexed addressing modes Power saving Week 3 50

Power. PC l l Superscalar RISC 32 -bit, 64 -bit implementation With both big-endian and little endian modes, can switch from one mode to the other at runtime. Intended for high performance PC, for highend machines Week 3 51

Reading Material l Chap. 2 in Microcontrollers and Microcomputers. Week 3 52

Questions 1. Given an address bus width in a processor as 16 -bit, determine the maximal address space. 2. Assume a memory address is 0 x. FFFF, how many locations this address can represent if the related computer is? I) a Harvard machine II) a Von Neumann machine Week 3 53

- Slides: 53