Introduction to MetalOxideSemiconductor Field Effect Transistors MOSFETs Chapter

- Slides: 37

Introduction to Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) Chapter 7, Anderson and Anderson

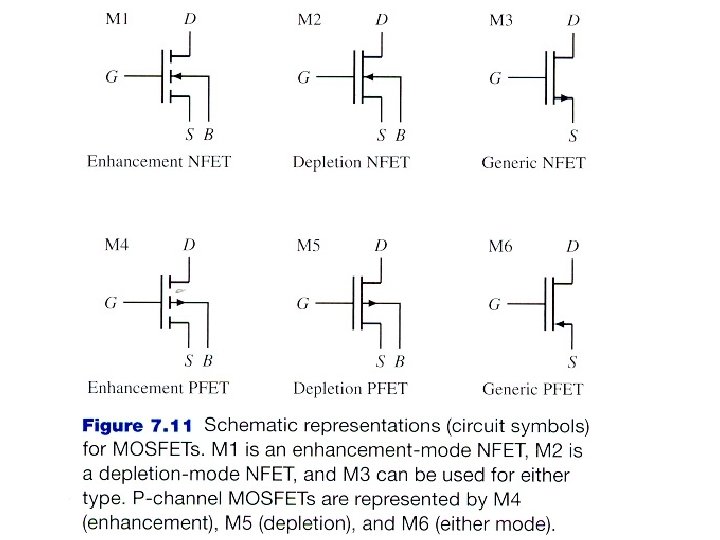

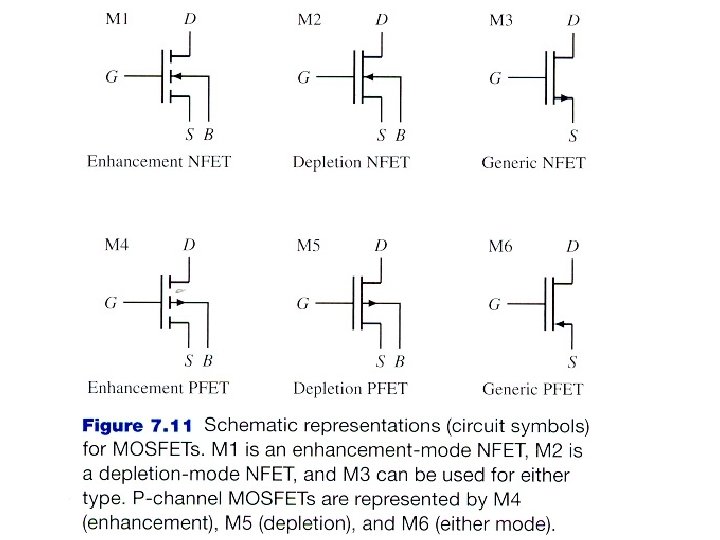

MOSFET • • History Structure Review Future Threshold Voltage I-V Characteristics Modifications to I-V: – – – • • • Depletion layer correction (Sup. 3) Mobility, Vsat Short Channel Effects Channel Length Modulation Channel Quantum Effects MOSFET Scaling and Current Topics (Literature + Sup. 3) Subthreshold Behavior Damage and Temperature (Sup. 3) Spice (Sup. 3) HFET, MESFET, JFET, DRAM, CCD (Some in Sup. 3)

MOSFET History (Very Short!) • First Patents: – 1935 • Variable Capacitor Proposed: – 1959 • Silicon MOS: – 1960 • Clean PMOS, NMOS: – Late 1960 s, big growth! • CCDs: – 1970 s, Bell Labs • Switch to CMOS: – 1980 s

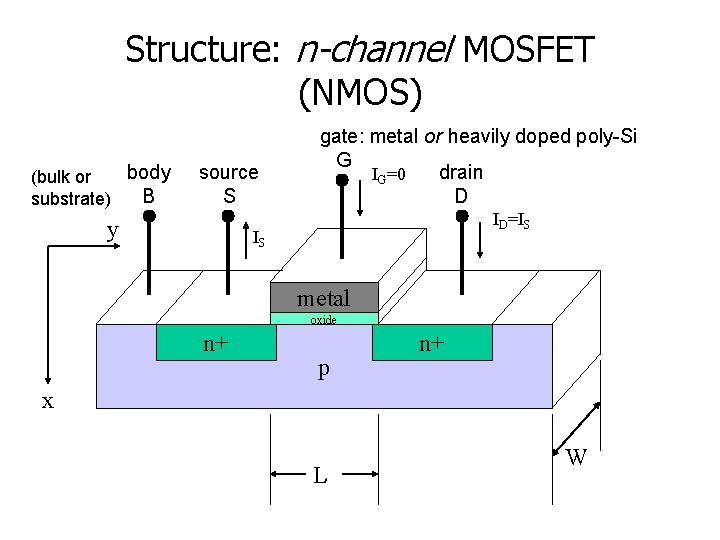

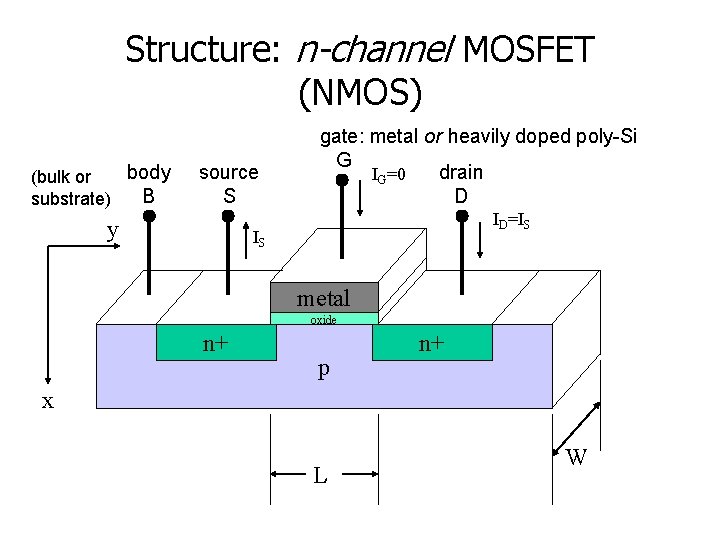

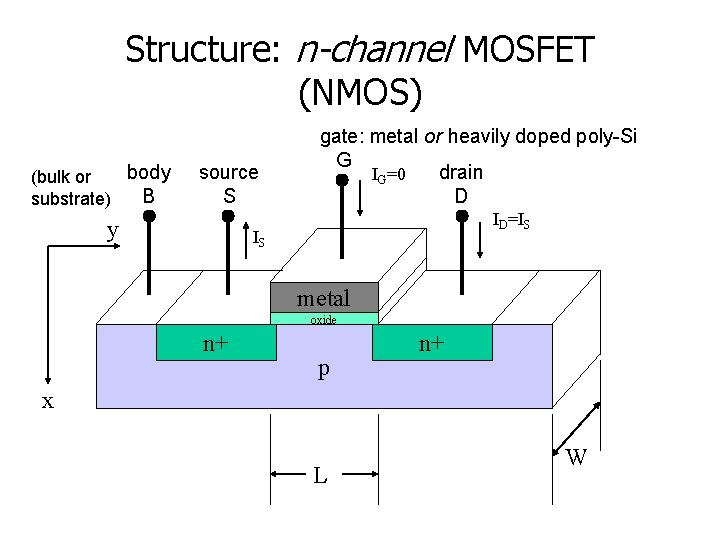

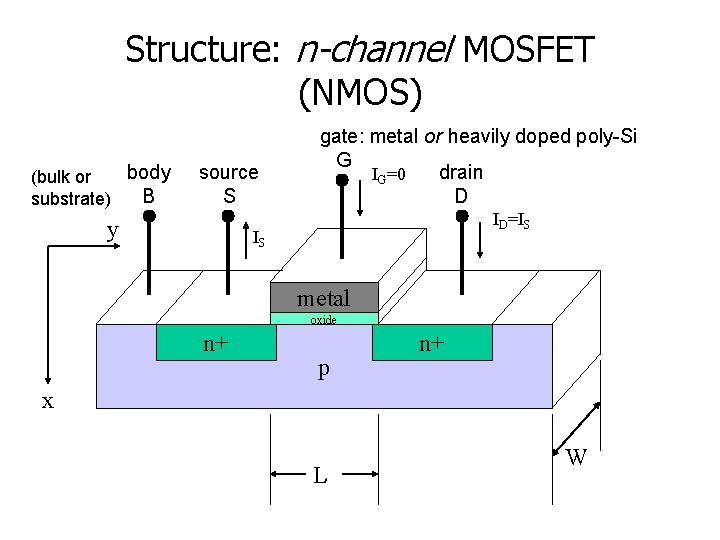

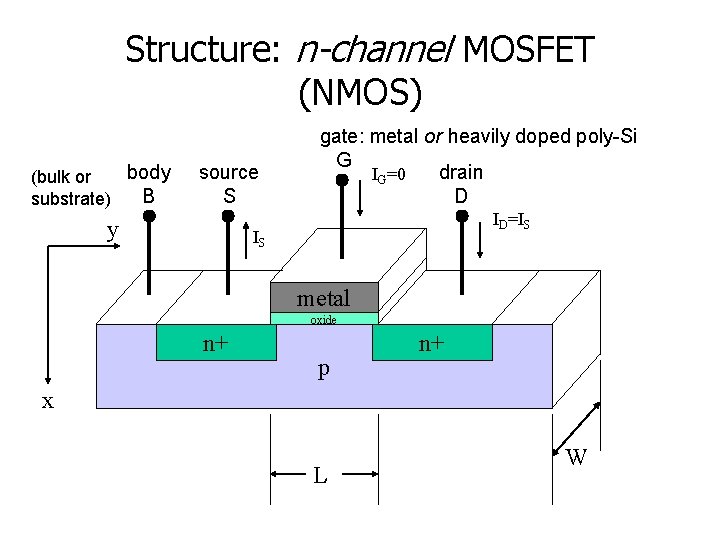

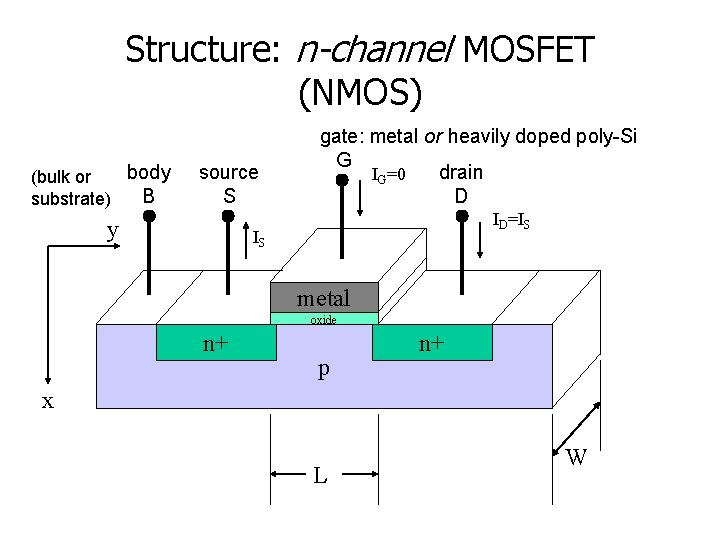

Structure: n-channel MOSFET (NMOS) body (bulk or B substrate) source S y gate: metal or heavily doped poly-Si G drain IG=0 D ID=IS IS metal oxide n+ p n+ x L W

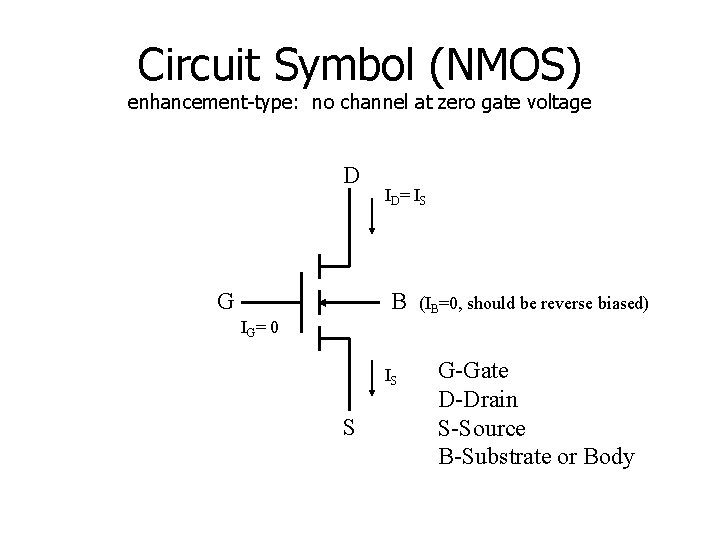

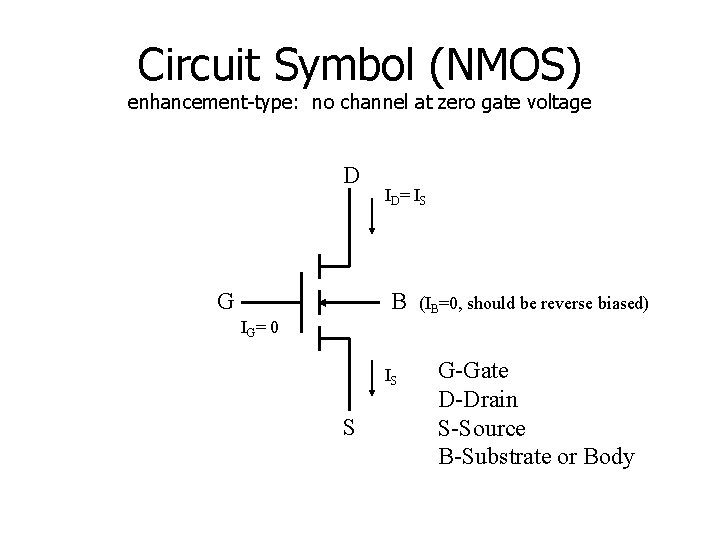

Circuit Symbol (NMOS) enhancement-type: no channel at zero gate voltage D G ID = I S B (IB=0, should be reverse biased) IG = 0 IS S G-Gate D-Drain S-Source B-Substrate or Body

Structure: n-channel MOSFET (NMOS) body (bulk or B substrate) source S y gate: metal or heavily doped poly-Si G drain IG=0 D ID=IS IS metal oxide n+ p n+ x L W

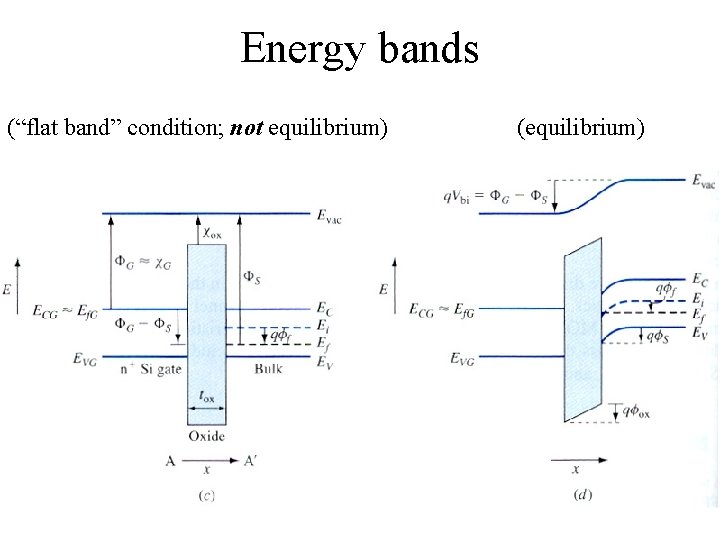

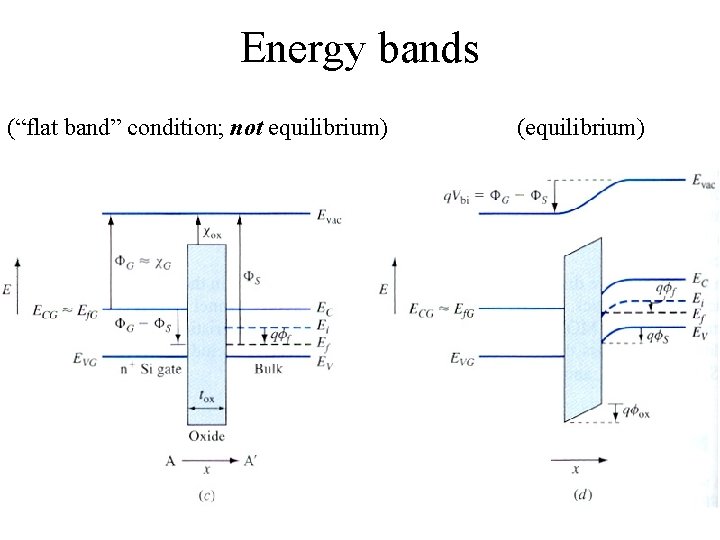

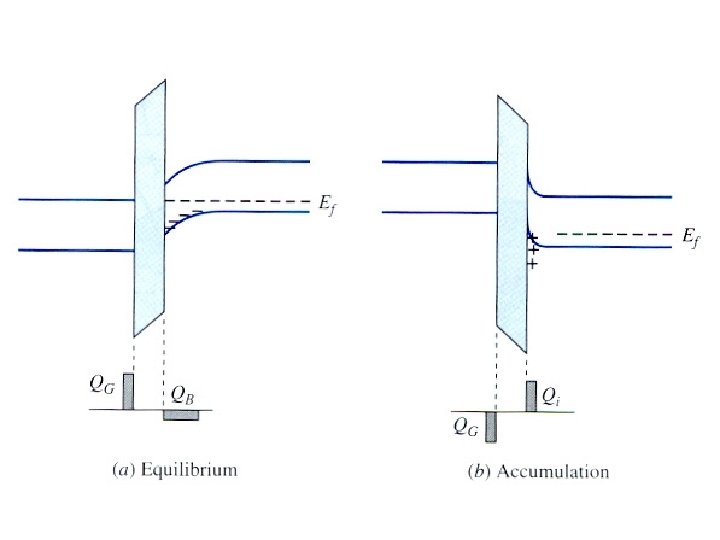

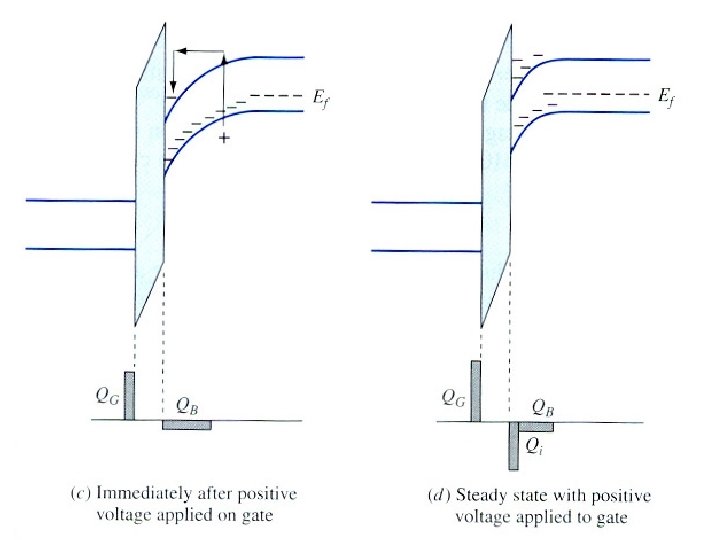

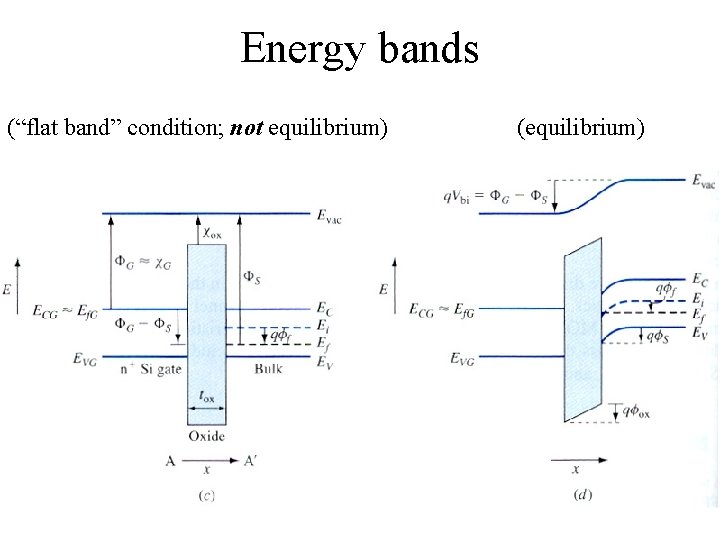

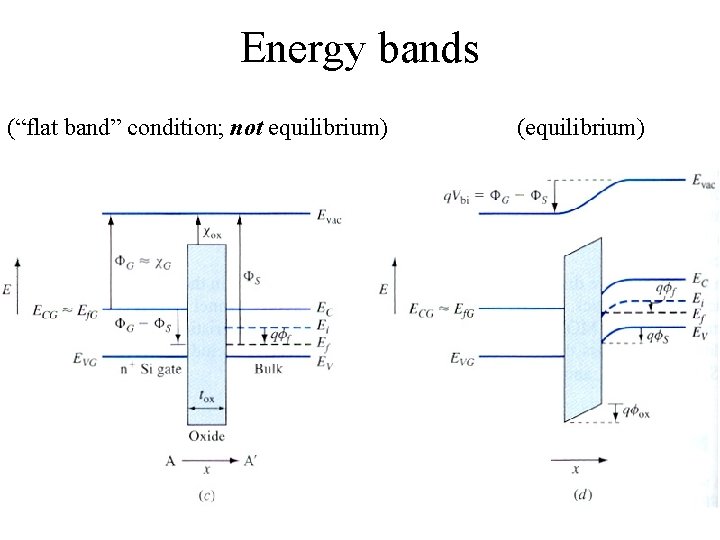

Energy bands (“flat band” condition; not equilibrium) (equilibrium)

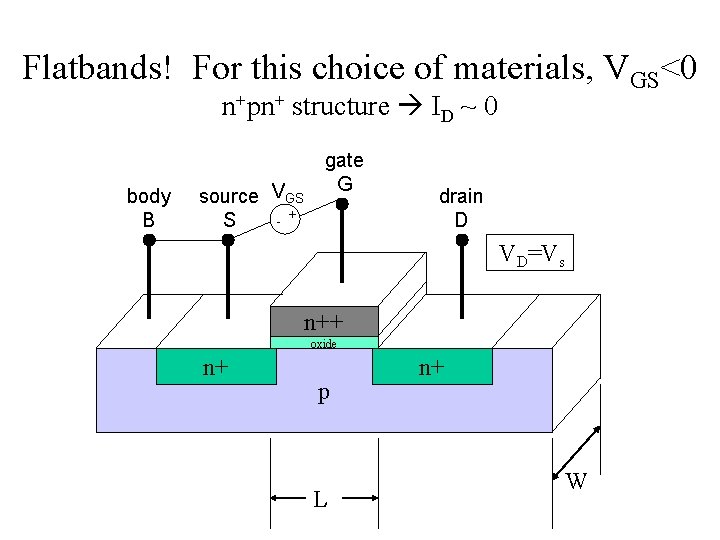

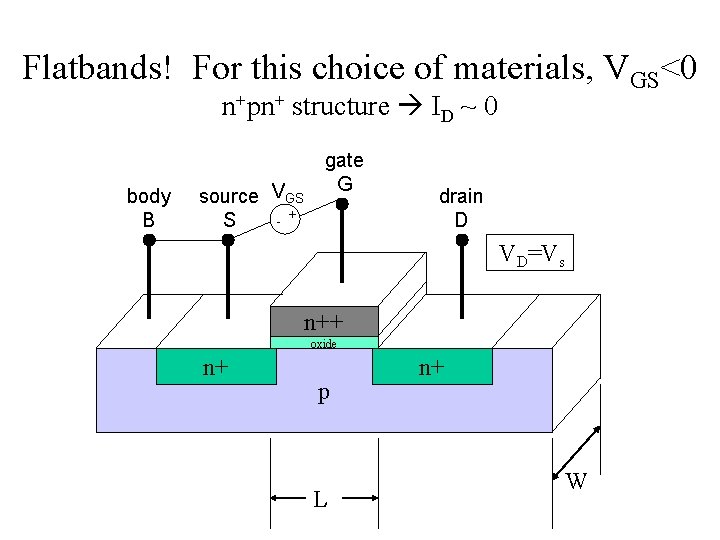

Flatbands! For this choice of materials, VGS<0 n+pn+ structure ID ~ 0 body B source VGS - + S gate G drain D VD=Vs n++ oxide n+ p L n+ W

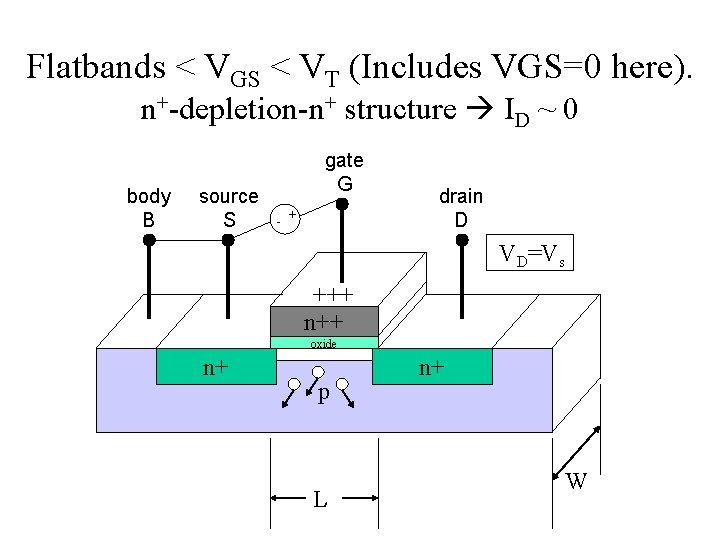

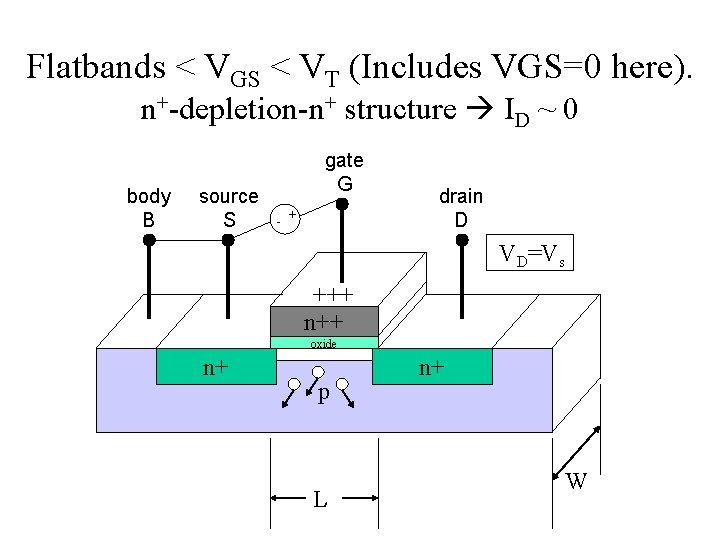

Flatbands < VGS < VT (Includes VGS=0 here). n+-depletion-n+ structure ID ~ 0 body B source S gate G - + drain D VD=Vs +++ n++ oxide n+ p L n+ W

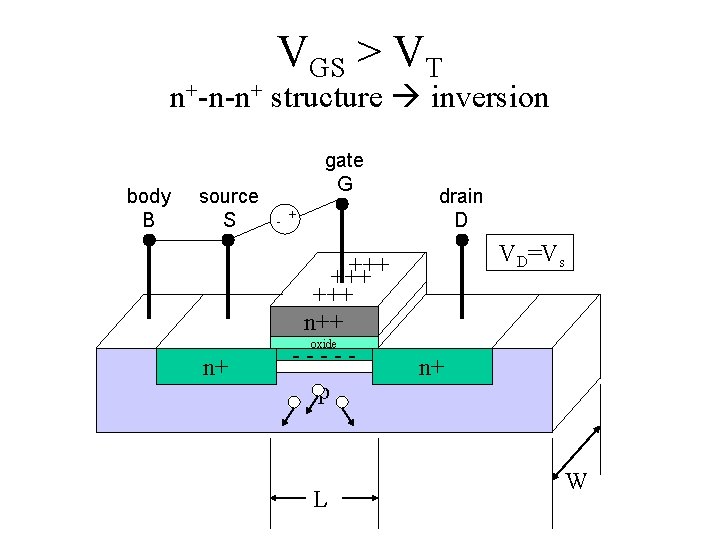

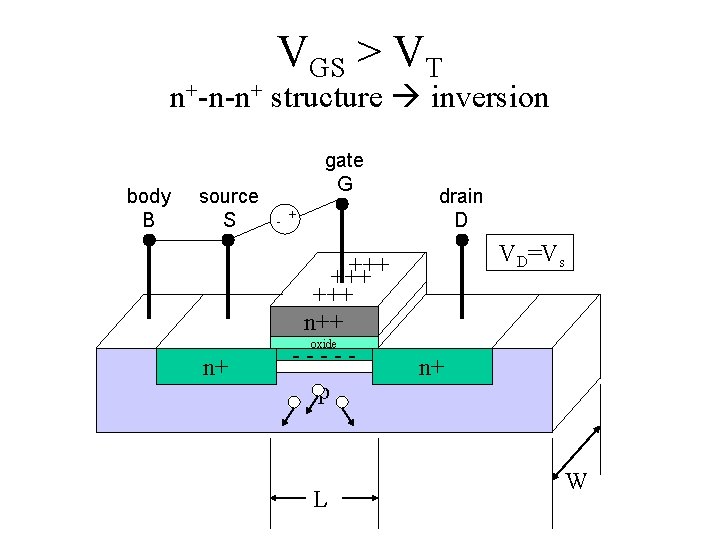

VGS > VT n+-n-n+ structure inversion body B source S n+ gate G - + +++ +++ n++ oxide ----p L drain D VD=Vs n+ W

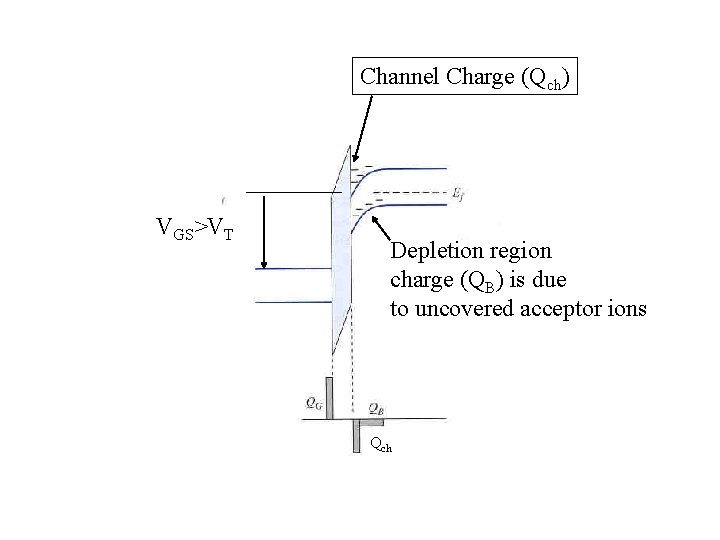

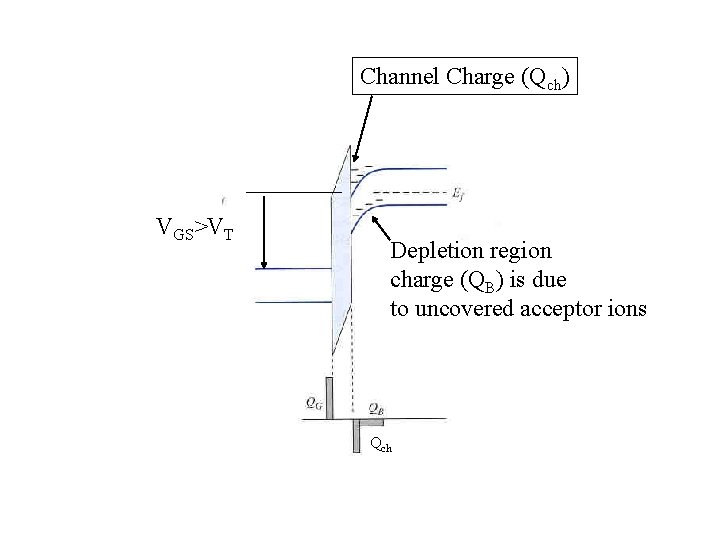

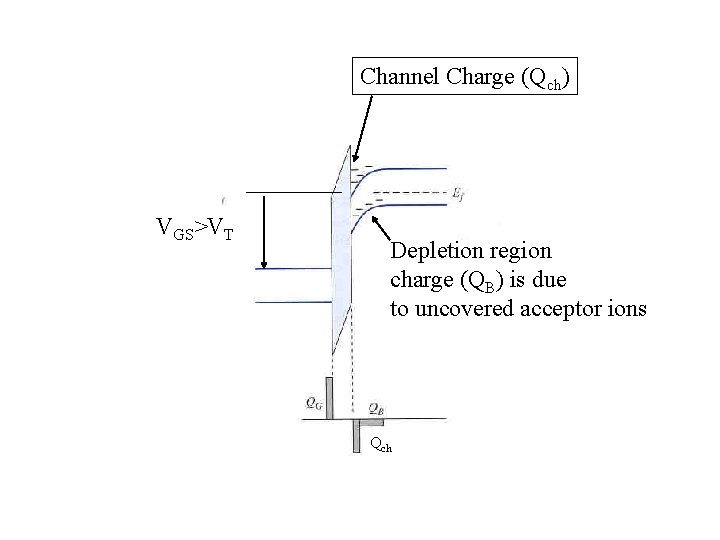

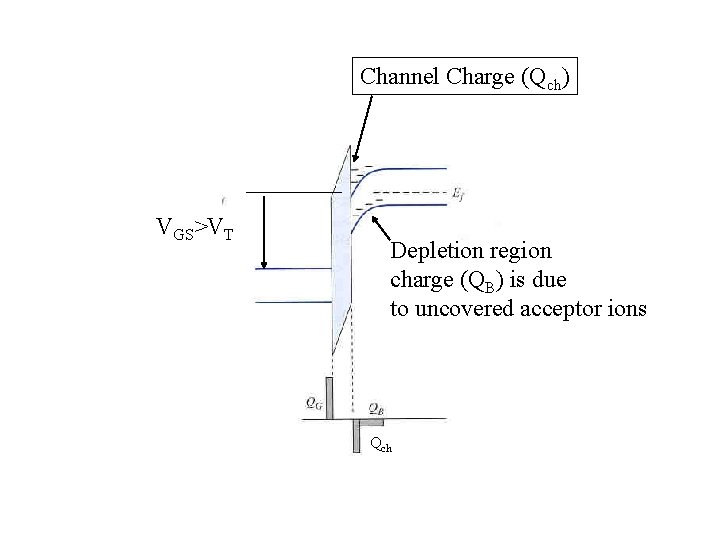

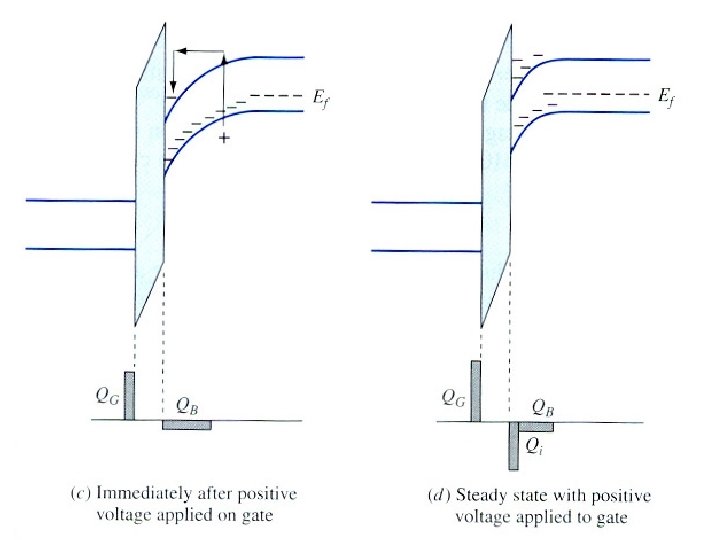

Channel Charge (Qch) VGS>VT Depletion region charge (QB) is due to uncovered acceptor ions Qch

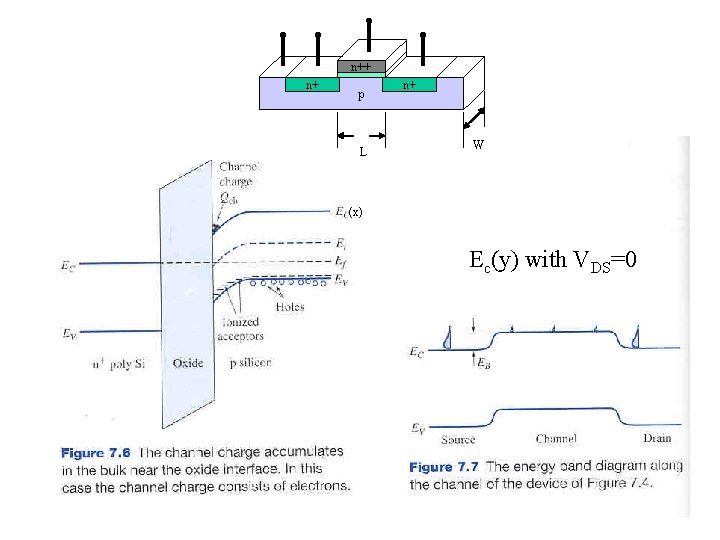

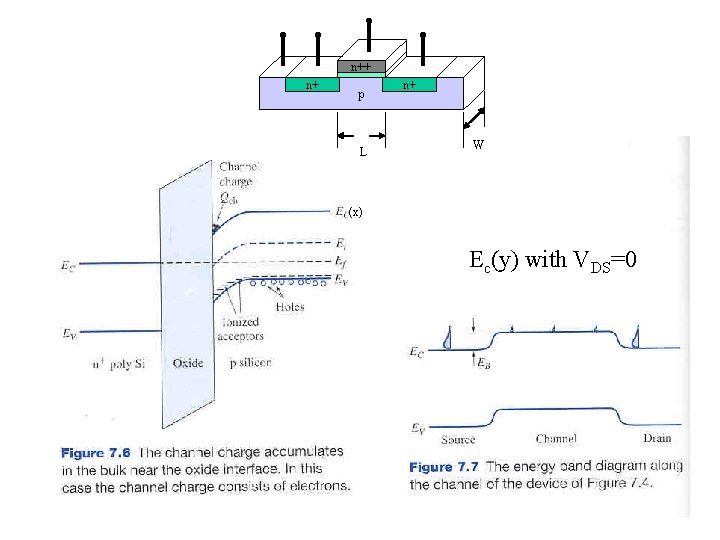

n++ n+ p L n+ W (x) Ec(y) with VDS=0

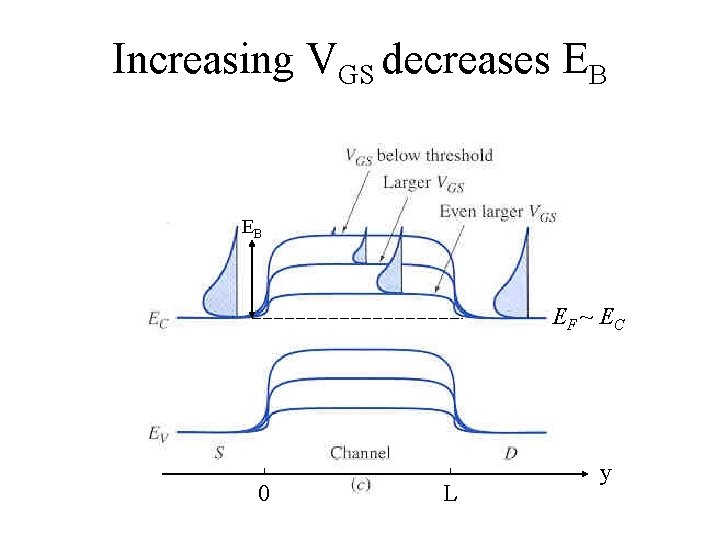

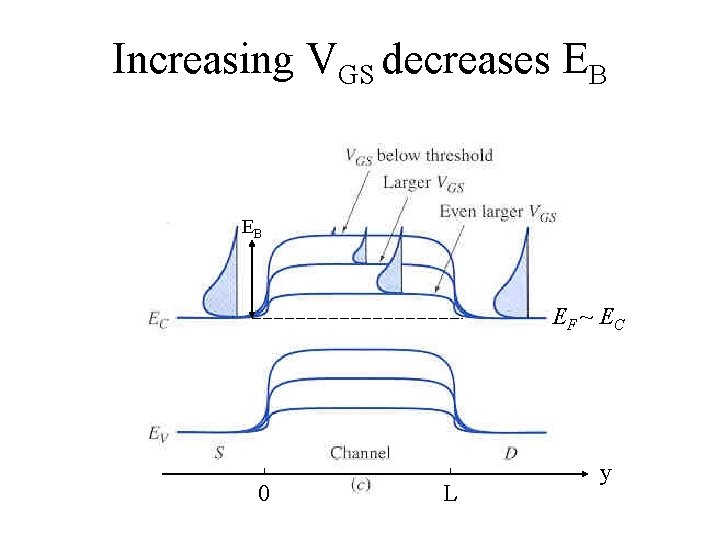

Increasing VGS decreases EB EB EF ~ EC 0 L y

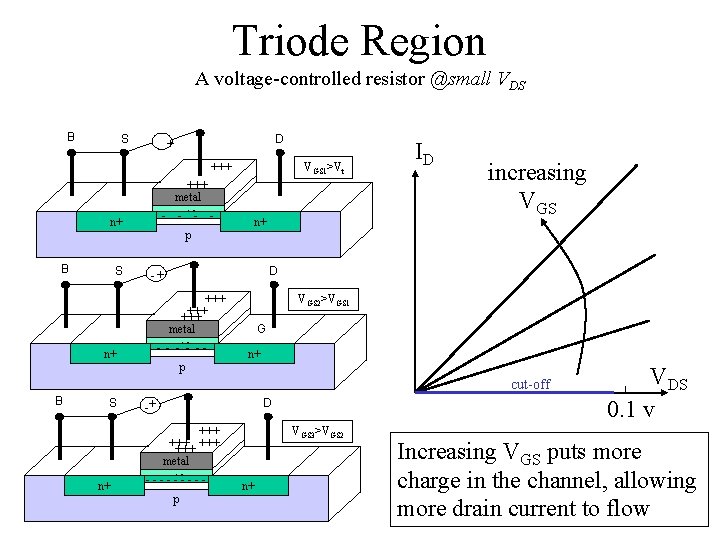

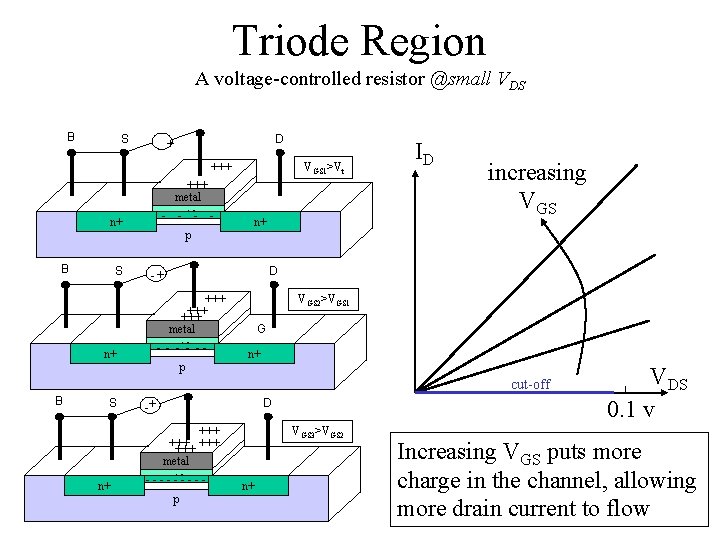

Triode Region A voltage-controlled resistor @small VDS B S D - + +++ metal - oxide - - - n+ B S p VGS 1>Vt n+ increasing VGS D -+ +++ +++ metal - -oxide - - -- n+ ID p VGS 2>VGS 1 G n+ cut-off B S n+ D -+ +++ +++ metal - - -oxide -----p VGS 3>VGS 2 n+ VDS 0. 1 v Increasing VGS puts more charge in the channel, allowing more drain current to flow

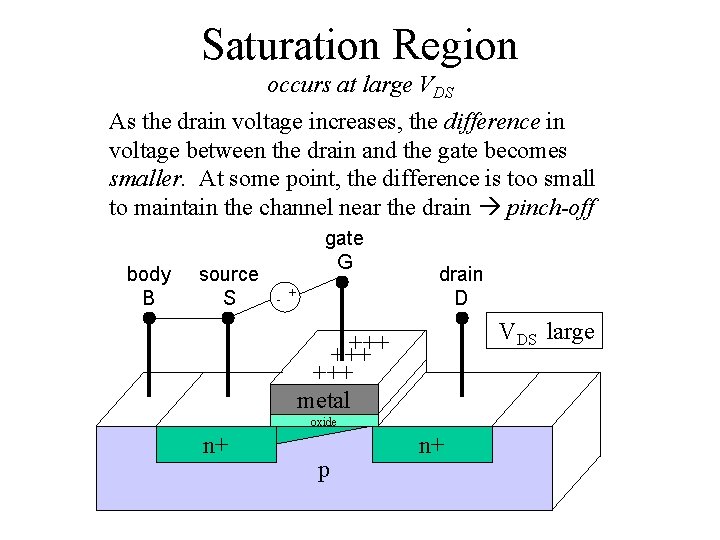

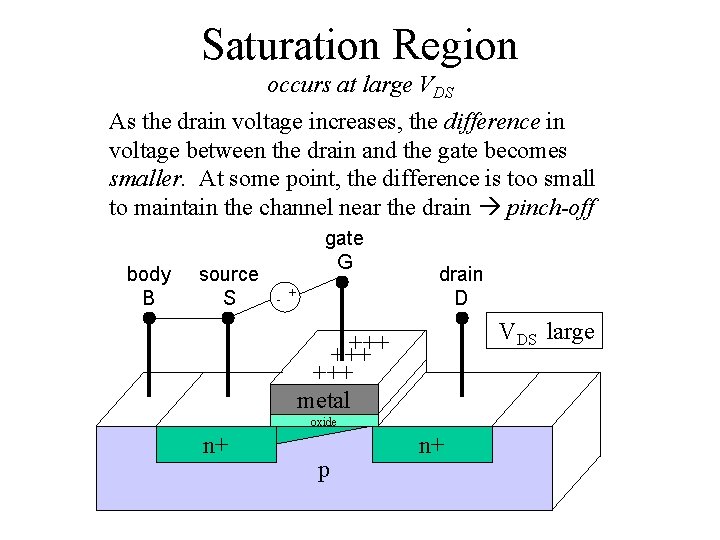

Saturation Region occurs at large VDS As the drain voltage increases, the difference in voltage between the drain and the gate becomes smaller. At some point, the difference is too small to maintain the channel near the drain pinch-off body B source S gate G - + drain D VDS large +++ +++ metal oxide n+ p n+

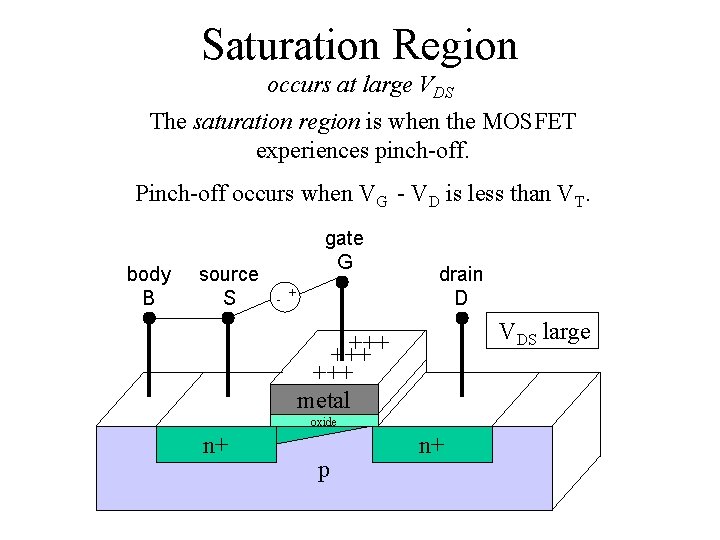

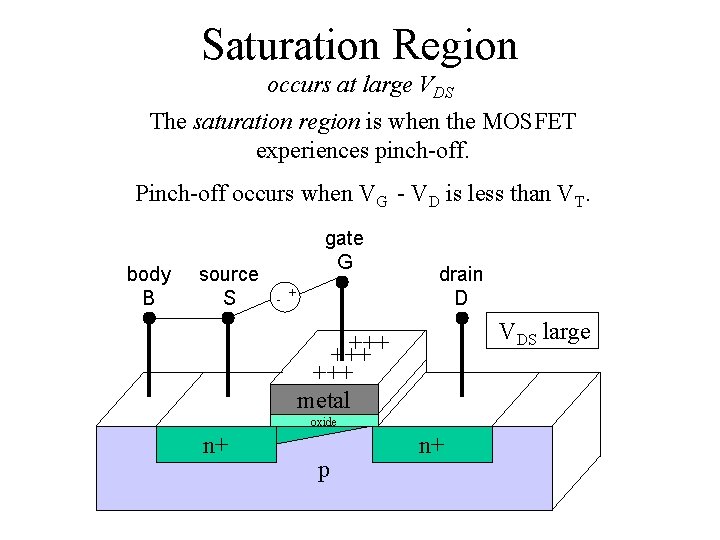

Saturation Region occurs at large VDS The saturation region is when the MOSFET experiences pinch-off. Pinch-off occurs when VG - VD is less than VT. body B source S gate G - + drain D VDS large +++ +++ metal oxide n+ p n+

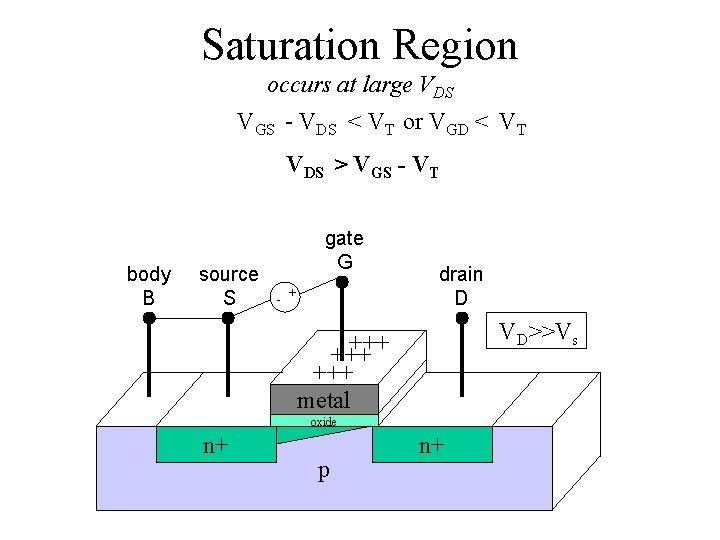

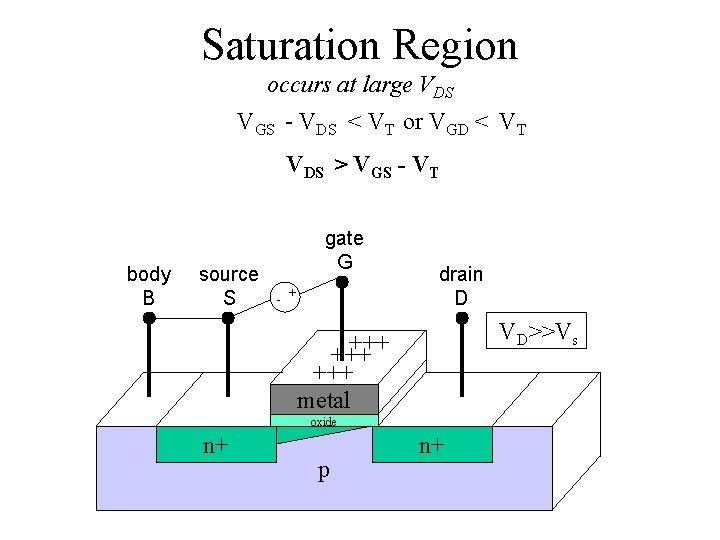

Saturation Region occurs at large VDS VGS - VDS < VT or VGD < VT VDS > VGS - VT body B source S gate G - + drain D VD>>Vs +++ +++ metal oxide n+ p n+

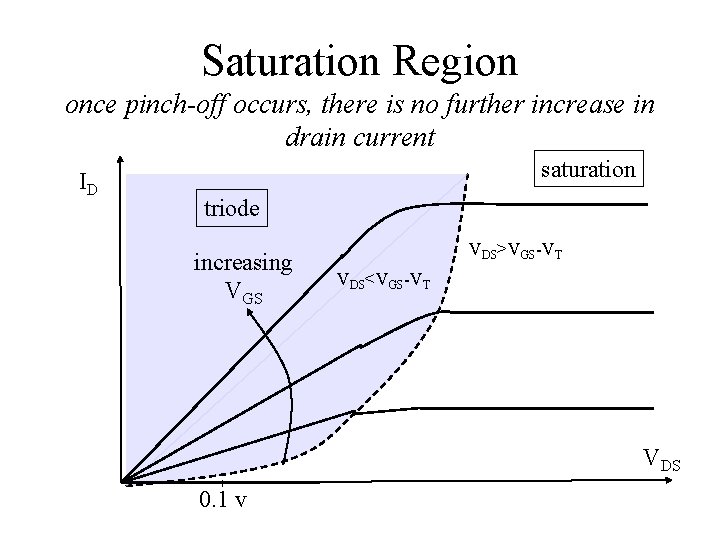

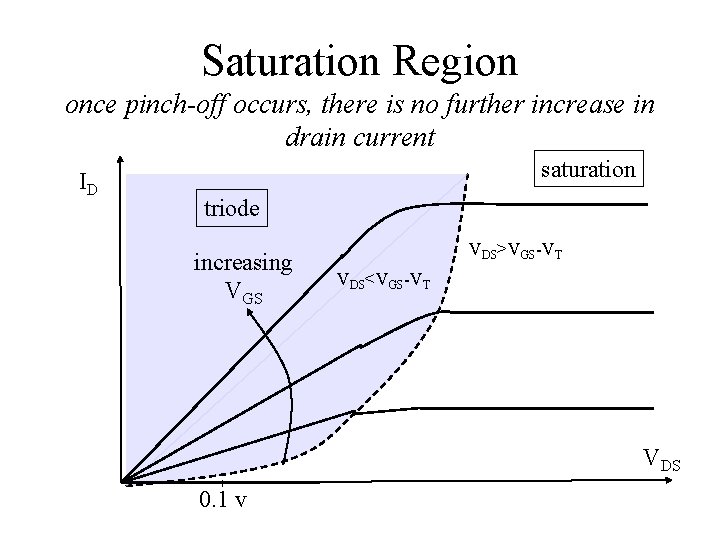

Saturation Region once pinch-off occurs, there is no further increase in drain current ID saturation triode increasing VGS VDS>VGS-VT VDS<VGS-VT VDS 0. 1 v

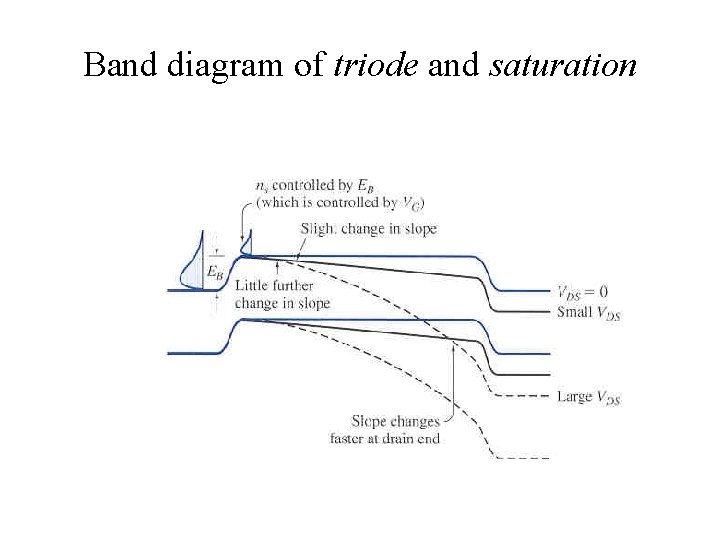

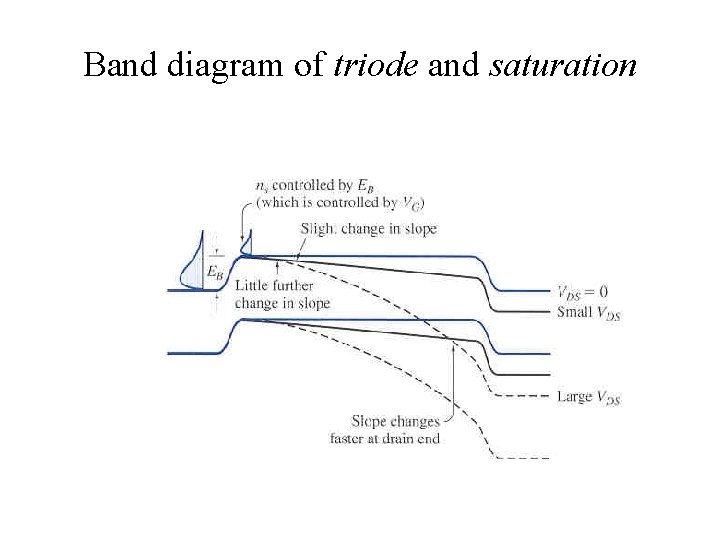

Band diagram of triode and saturation

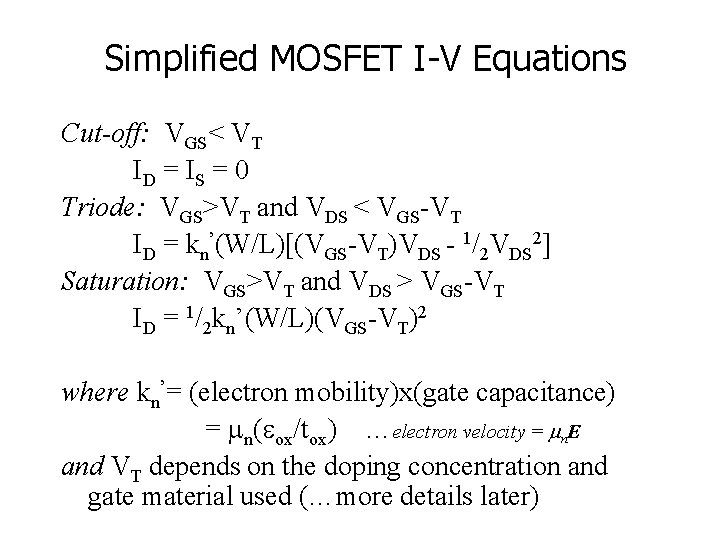

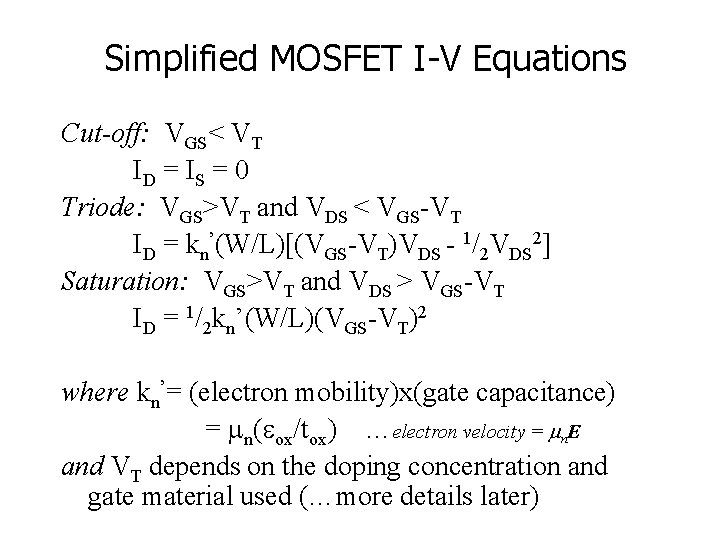

Simplified MOSFET I-V Equations Cut-off: VGS< VT ID = I S = 0 Triode: VGS>VT and VDS < VGS-VT ID = kn’(W/L)[(VGS-VT)VDS - 1/2 VDS 2] Saturation: VGS>VT and VDS > VGS-VT ID = 1/2 kn’(W/L)(VGS-VT)2 where kn’= (electron mobility)x(gate capacitance) = mn(eox/tox) …electron velocity = mn. E and VT depends on the doping concentration and gate material used (…more details later)

Structure: n-channel MOSFET (NMOS) body (bulk or B substrate) source S y gate: metal or heavily doped poly-Si G drain IG=0 D ID=IS IS metal oxide n+ p n+ x L W

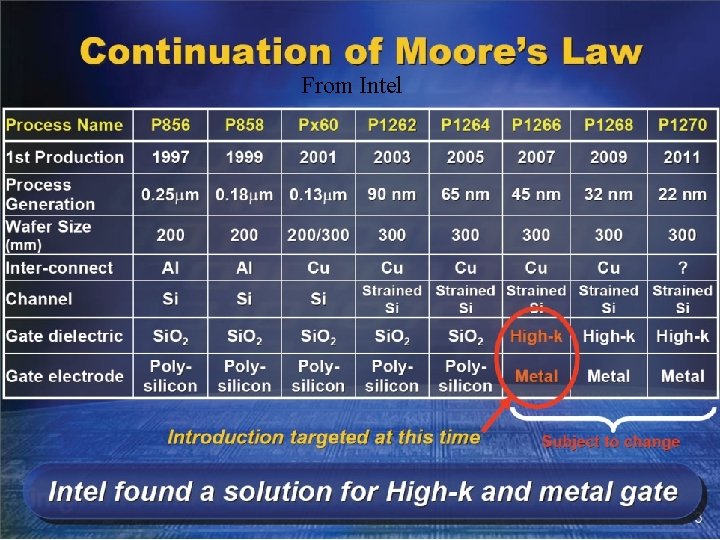

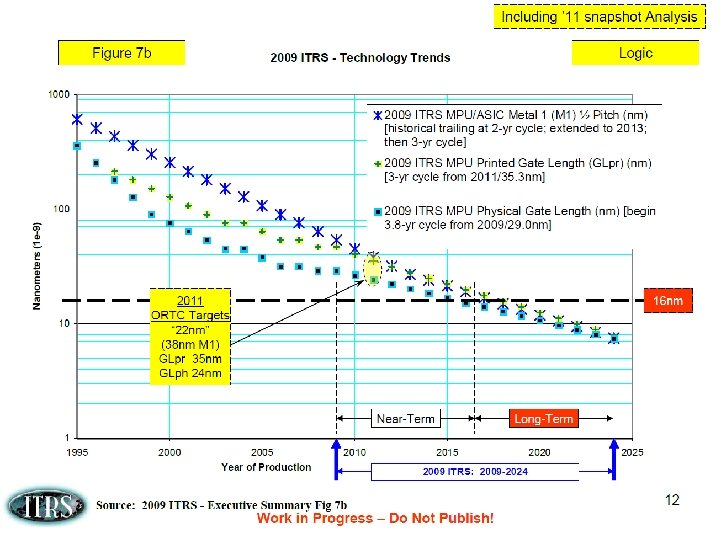

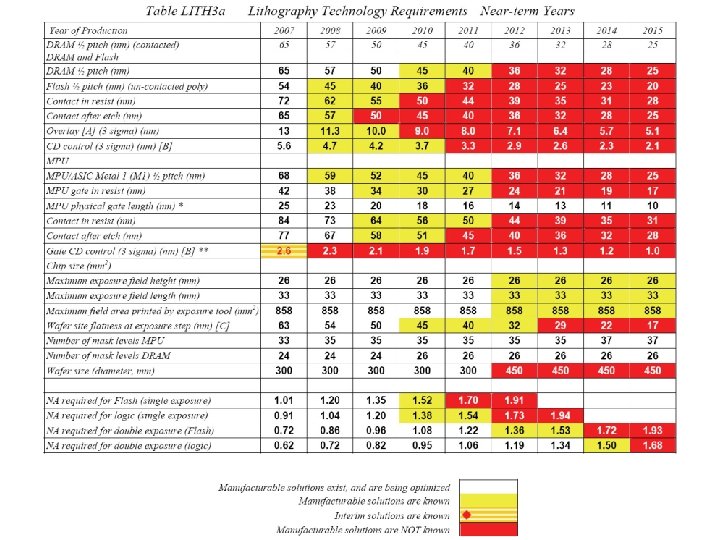

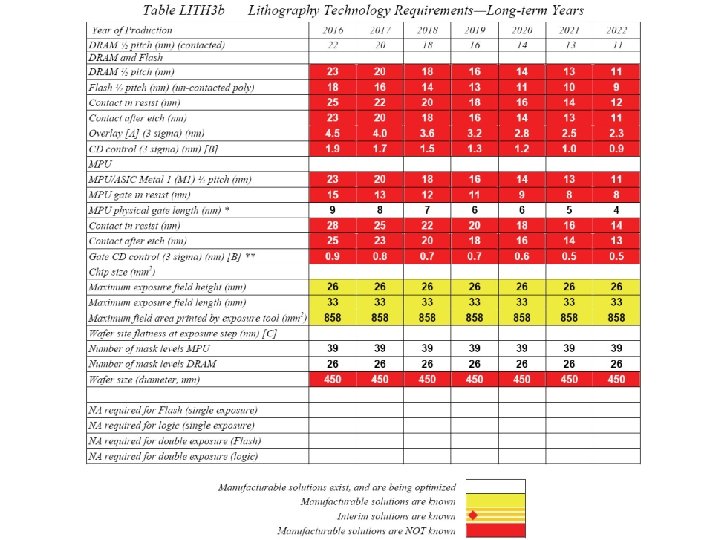

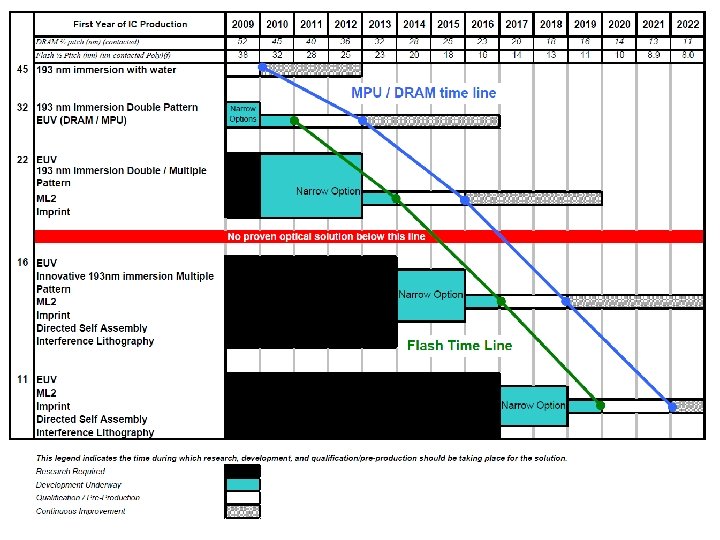

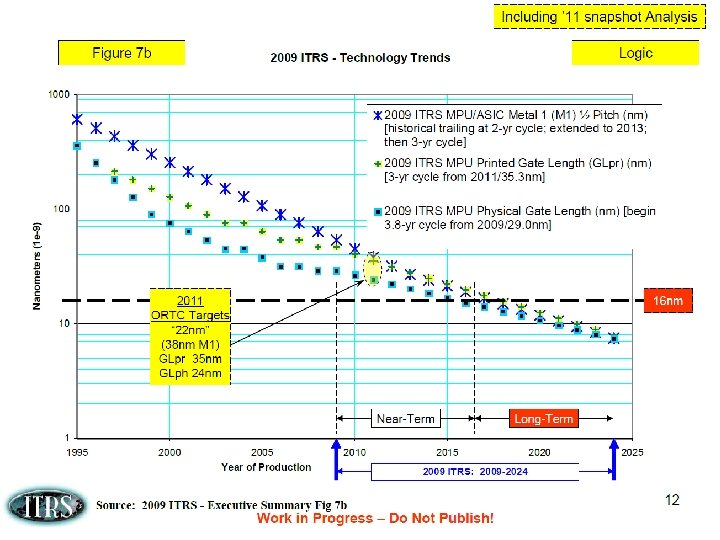

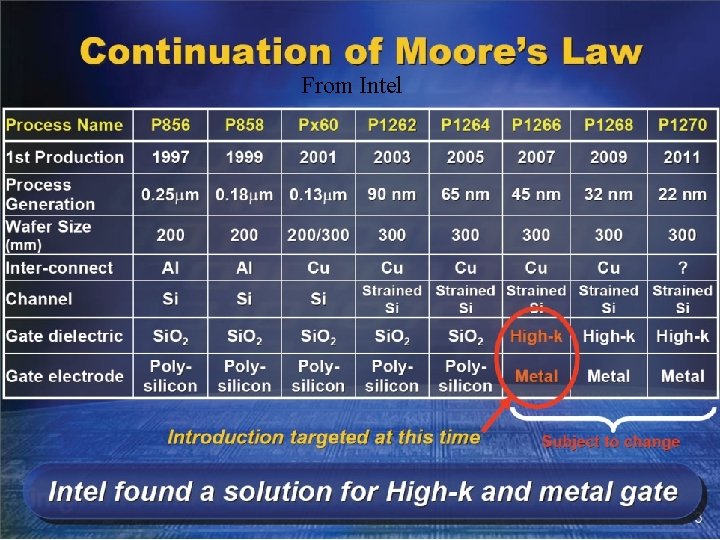

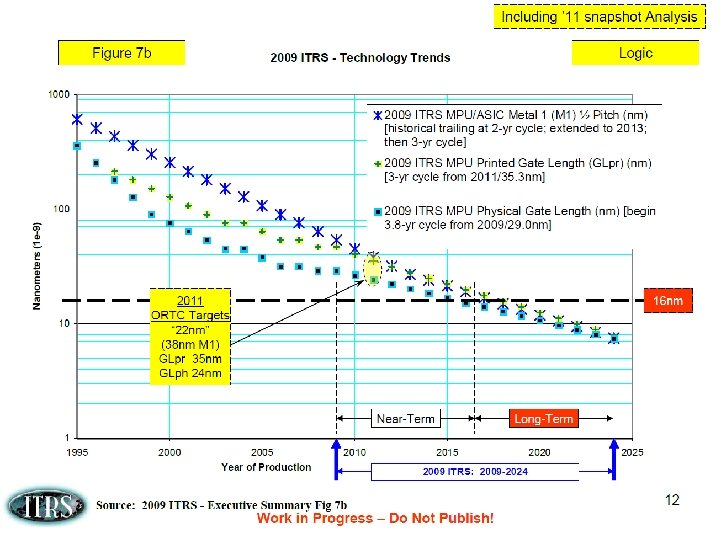

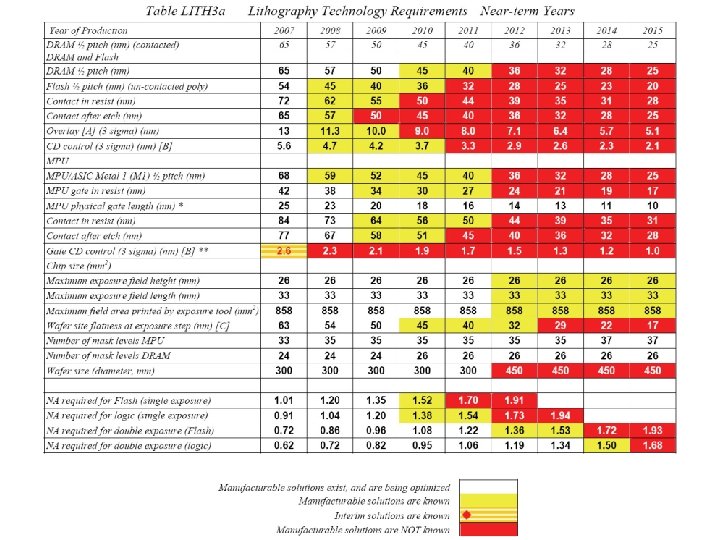

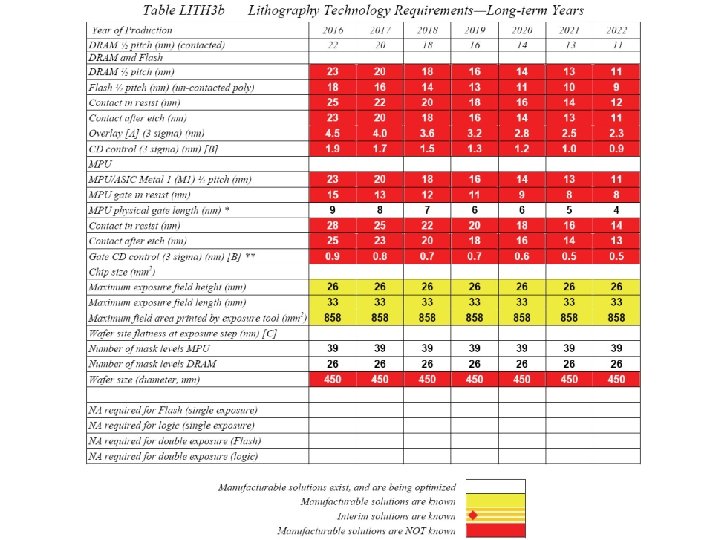

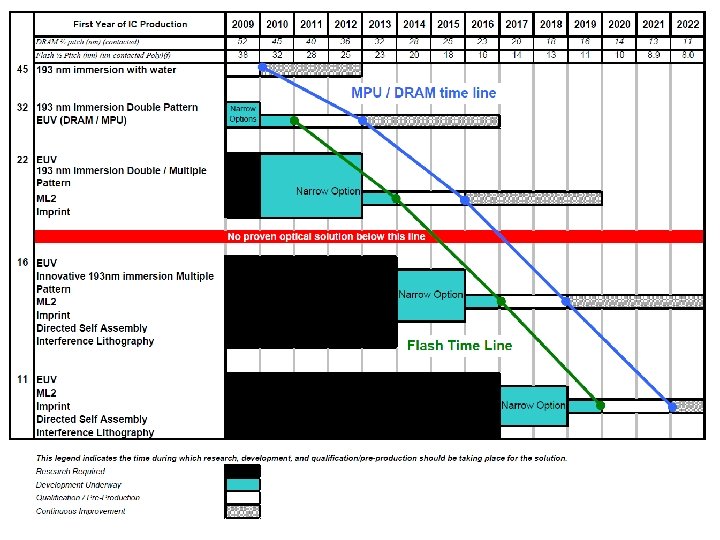

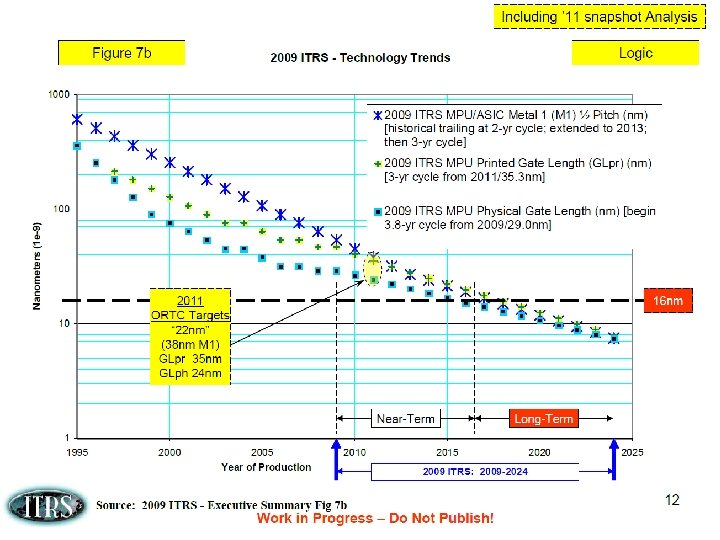

MOSFET Future (One Part of) • International Technology Roadmap for Semiconductors, 2008 update. • Look at size, manufacturing technique.

From Intel

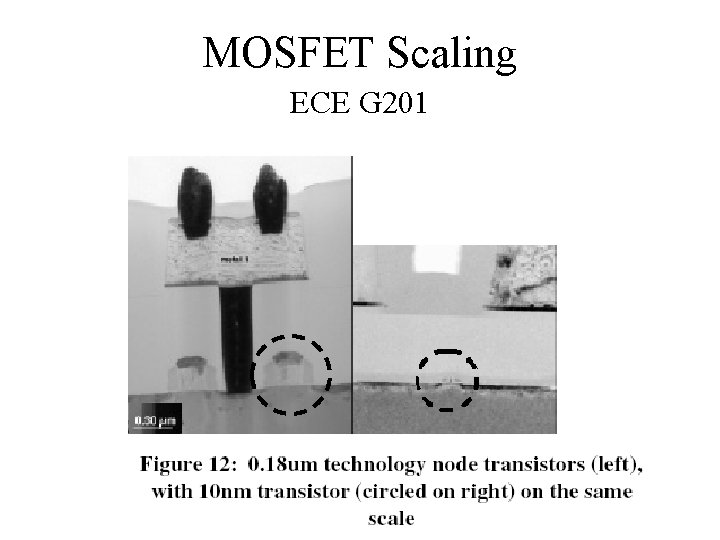

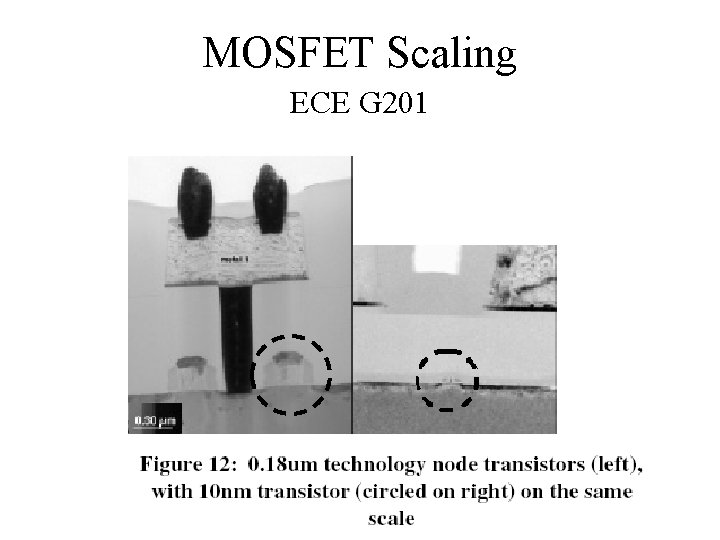

MOSFET Scaling ECE G 201

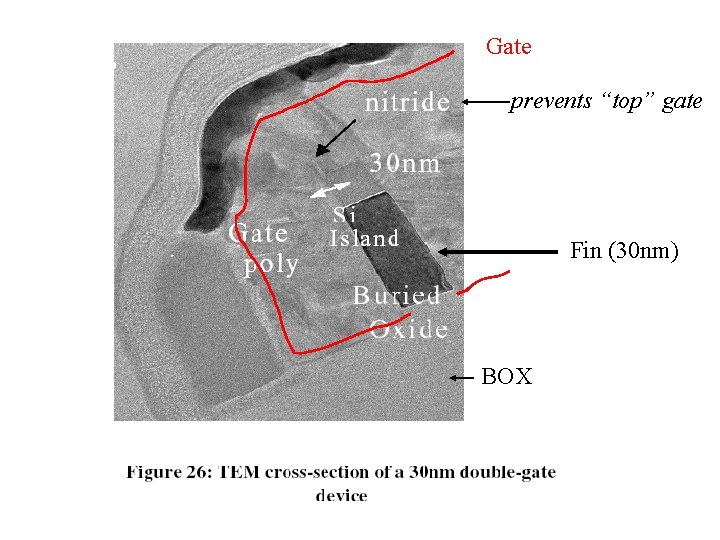

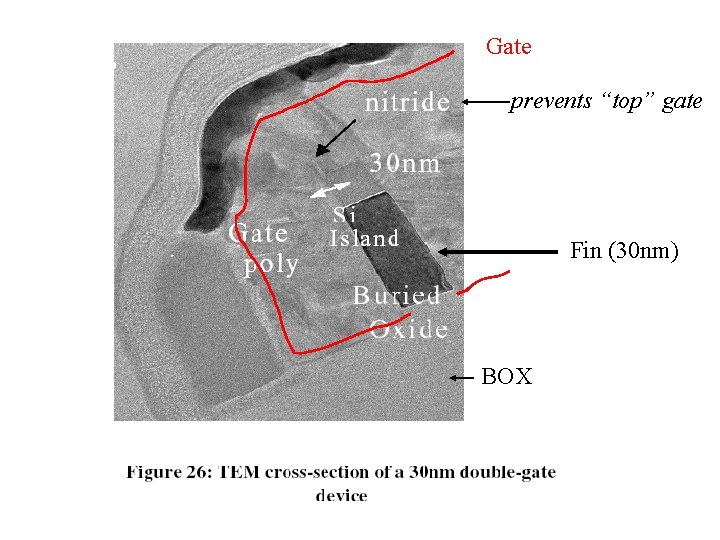

Gate prevents “top” gate Fin (30 nm) BOX

Energy bands (“flat band” condition; not equilibrium) (equilibrium)

Channel Charge (Qch) VGS>VT Depletion region charge (QB) is due to uncovered acceptor ions Qch

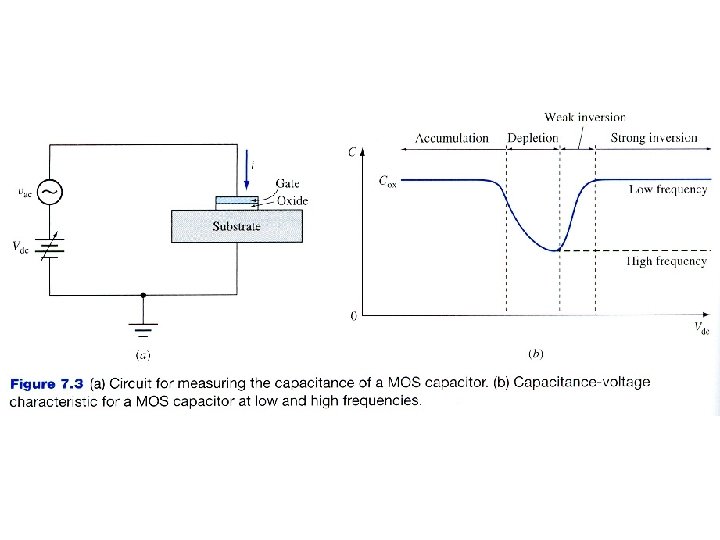

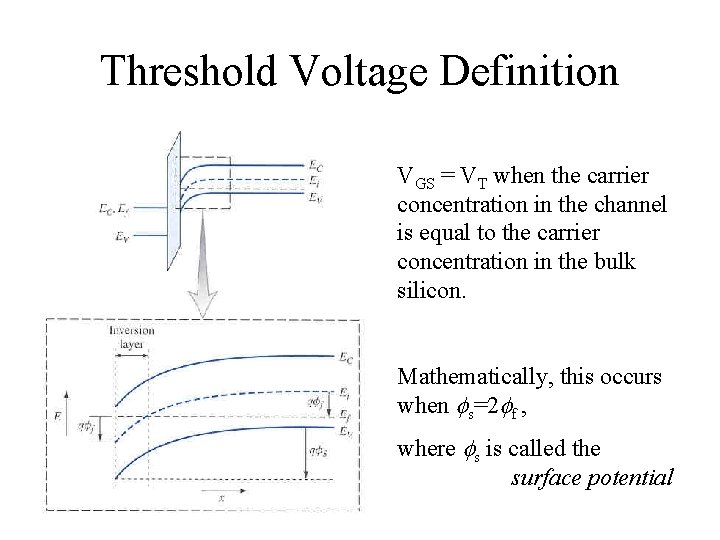

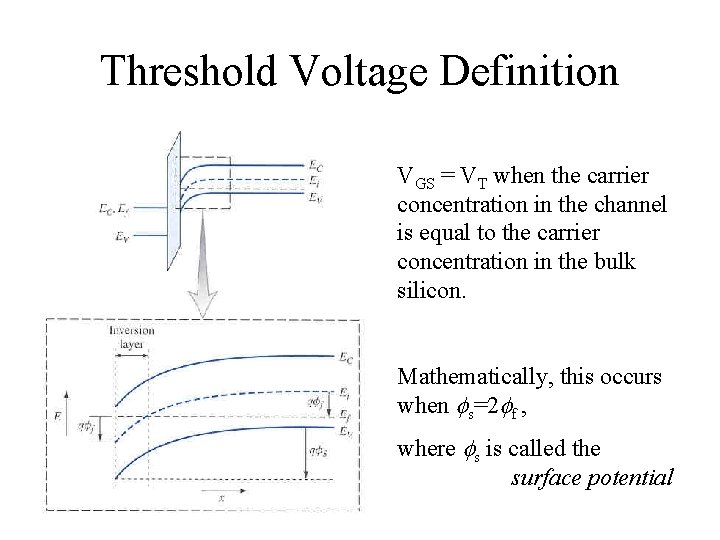

Threshold Voltage Definition VGS = VT when the carrier concentration in the channel is equal to the carrier concentration in the bulk silicon. Mathematically, this occurs when fs=2 ff , where fs is called the surface potential