Informationsteknologi Todays class n Instruction set architecture Friday

- Slides: 53

Informationsteknologi Today’s class n Instruction set architecture Friday, November 16, 2007 Computer Architecture I - Class 11 1

Informationsteknologi Instruction Set Design The instruction set architecture (ISA) level is between the high-level languages and the hardware n When new hardware architecture comes along … n ® Need to maintain backward compatibility ® Can add new features to exploit new hardware capabilities Friday, November 16, 2007 Computer Architecture I - Class 11 2

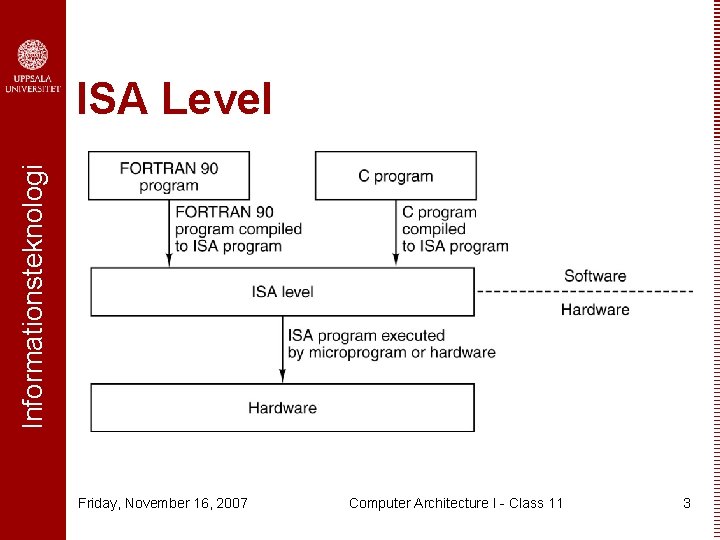

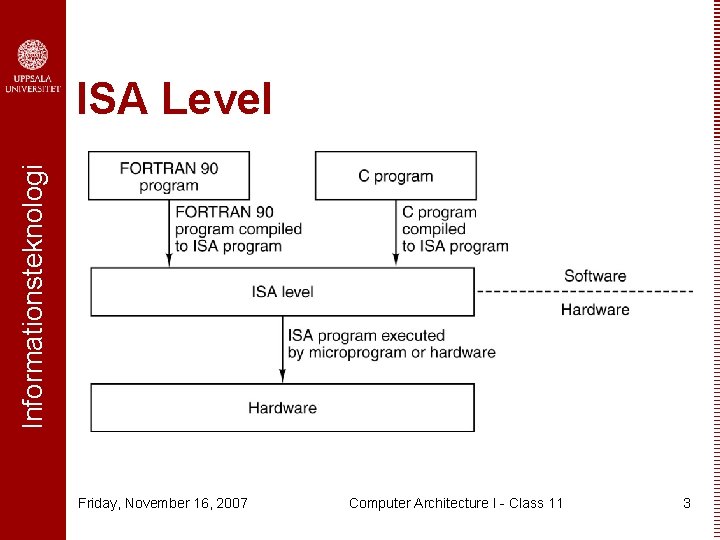

Informationsteknologi ISA Level Friday, November 16, 2007 Computer Architecture I - Class 11 3

Informationsteknologi Properties of the ISA Level n n n In principle, the ISA level is defined by how the machine appears to a machine language programmer In modern times, this is refined to say that ISAlevel code is what a compiler outputs Compiler writer needs to know: Memory model ® What registers are available ® What data types are available ® What instructions are available ® Friday, November 16, 2007 Computer Architecture I - Class 11 4

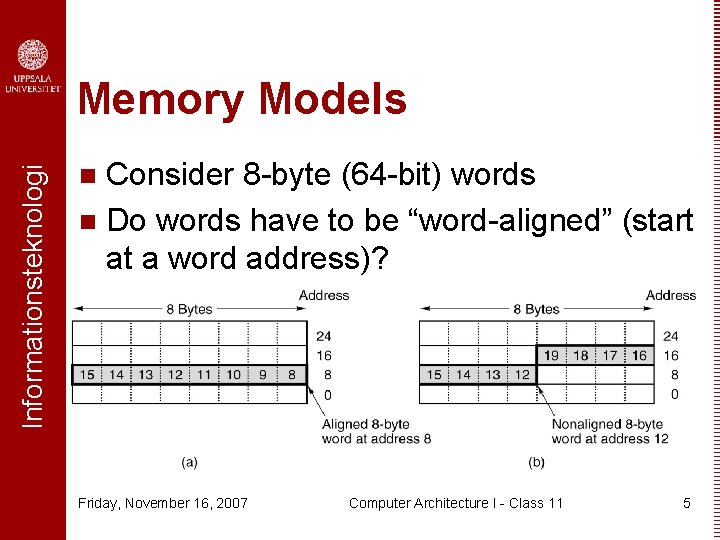

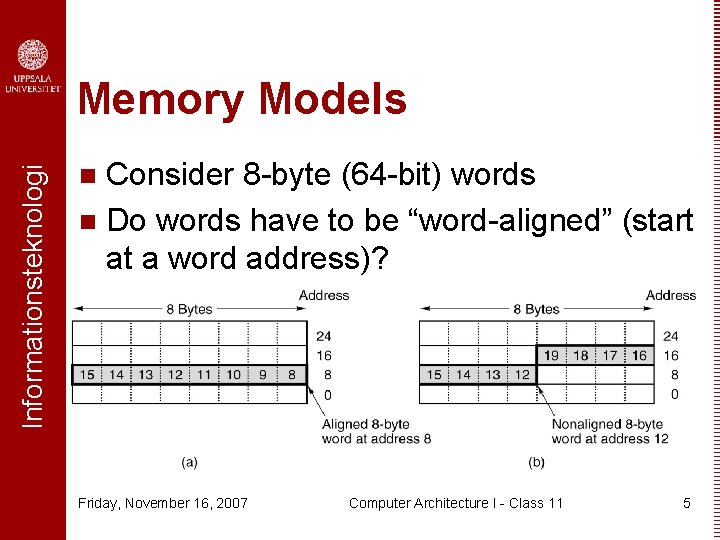

Informationsteknologi Memory Models Consider 8 -byte (64 -bit) words n Do words have to be “word-aligned” (start at a word address)? n Friday, November 16, 2007 Computer Architecture I - Class 11 5

Informationsteknologi Instruction and Data Spaces Most machines have a single linear address space at the ISA level n However, a few machines have separate address spaces for instructions and data n ® Effectively doubles memory! ® All writes go to data space, protecting instructions from being overwritten Friday, November 16, 2007 Computer Architecture I - Class 11 6

Informationsteknologi Registers n Special purpose Program counter ® Stack pointer ® Program status word ® n General purpose Hold key local variables and intermediate results of calculations ® RISC machines usually have at least 32 ® Trend in new CPU designs is to have even more ® Friday, November 16, 2007 Computer Architecture I - Class 11 7

Informationsteknologi Instructions LOAD and STORE instructions – move data between memory and registers n MOVE instructions – move data among the registers n Arithmetic instructions n Boolean instructions n Comparing data items and branching on the results n Friday, November 16, 2007 Computer Architecture I - Class 11 8

Informationsteknologi Pentium 4 n Three operating modes Real mode – all features added since the 8088 are turned off (effectively behaves like a simple 8088; if a program does something wrong whole machine crashes) ® Virtual 8086 mode – makes it possible to run old 8088 programs in a protected way (if a program crashes, the OS is notified instead of the machine crashing) ® Protected mode – actually behaves like a Pentium 4! ® Friday, November 16, 2007 Computer Architecture I - Class 11 9

Informationsteknologi Pentium 4 n Address space ® 16, 384 segments ® Each segment has 232 addresses (4 GB) ® Most operating systems, including Unix and Windows, support only one segment ® Every byte has its own address ® Words are 32 bits long, and low-endian Friday, November 16, 2007 Computer Architecture I - Class 11 10

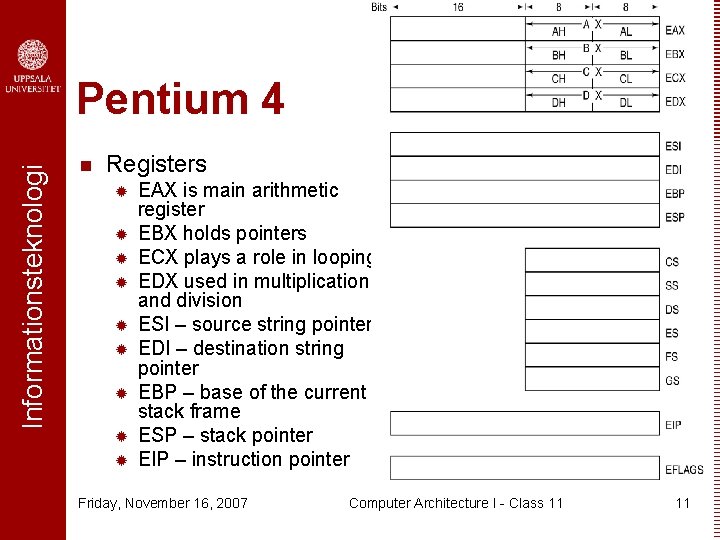

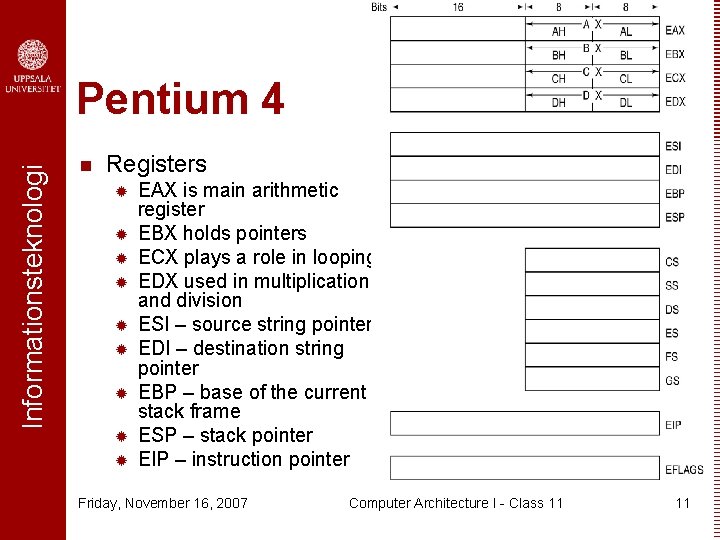

Informationsteknologi Pentium 4 n Registers ® ® ® ® ® EAX is main arithmetic register EBX holds pointers ECX plays a role in looping EDX used in multiplication and division ESI – source string pointer EDI – destination string pointer EBP – base of the current stack frame ESP – stack pointer EIP – instruction pointer Friday, November 16, 2007 Computer Architecture I - Class 11 11

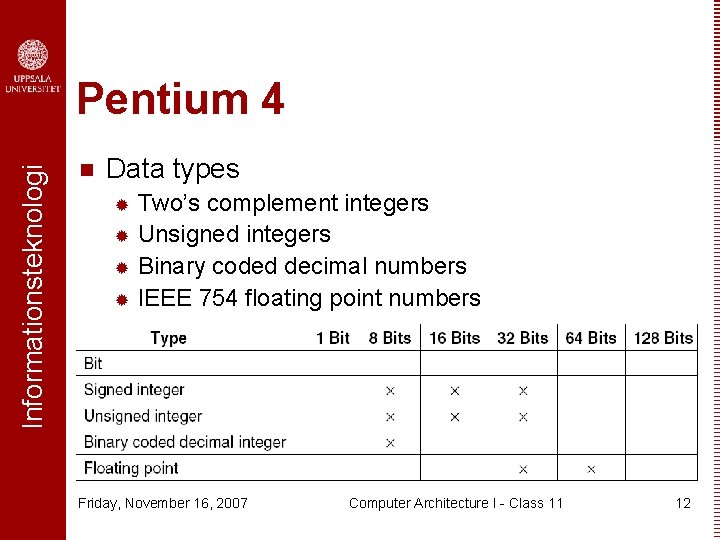

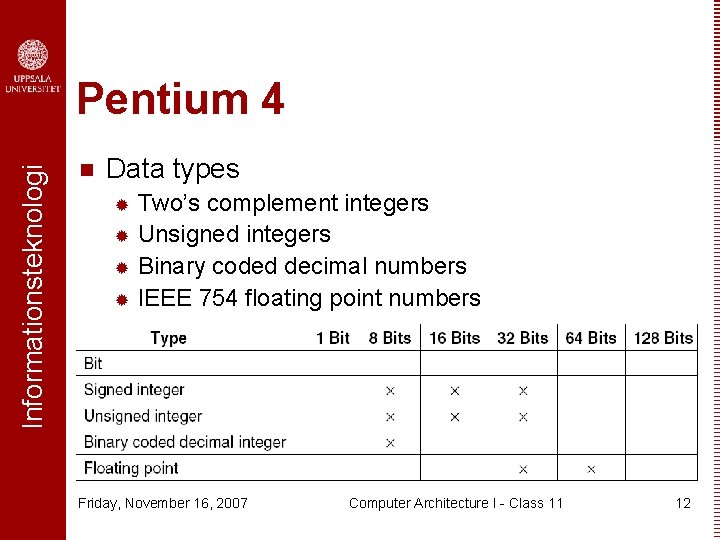

Informationsteknologi Pentium 4 n Data types Two’s complement integers ® Unsigned integers ® Binary coded decimal numbers ® IEEE 754 floating point numbers ® Friday, November 16, 2007 Computer Architecture I - Class 11 12

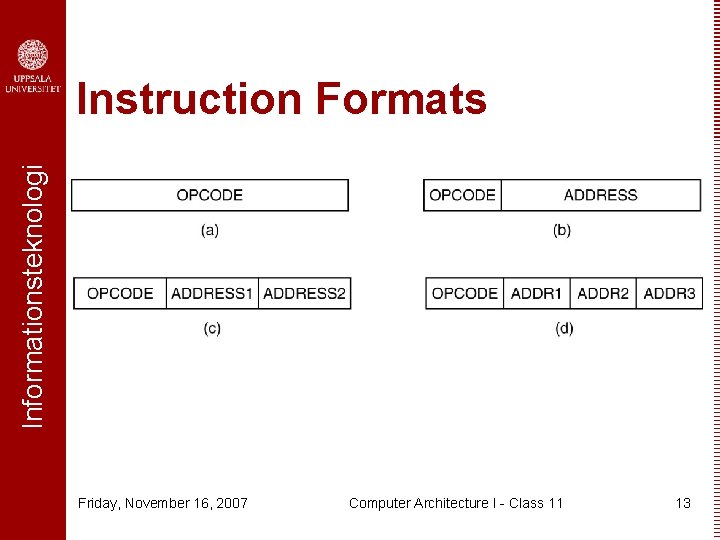

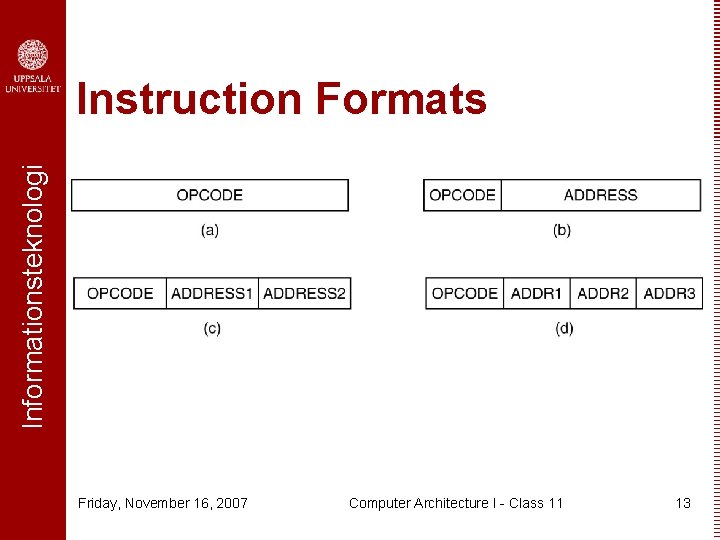

Informationsteknologi Instruction Formats Friday, November 16, 2007 Computer Architecture I - Class 11 13

Informationsteknologi Design Criteria Short instructions are better than long ones n Sufficient room in the instruction format to express all the operations desired n Number of bits in the address field n Friday, November 16, 2007 Computer Architecture I - Class 11 14

Informationsteknologi Examples n Consider an (n + k) bit instruction that has a kbit opcode and a single n-bit address Allows for 2 k different operations ® Allows for 2 n addressable memory cells ® n Could alternatively have: ® k-1 bit opcode and n+1 bit address § Half as many instructions but twice the addressable memory ® k+1 bit opcode and n-1 bit address § Twice as many instructions but half the addressable memory Friday, November 16, 2007 Computer Architecture I - Class 11 15

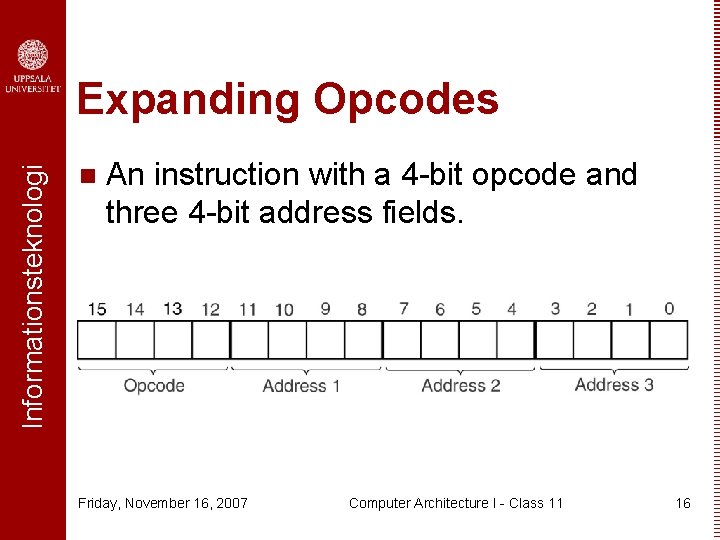

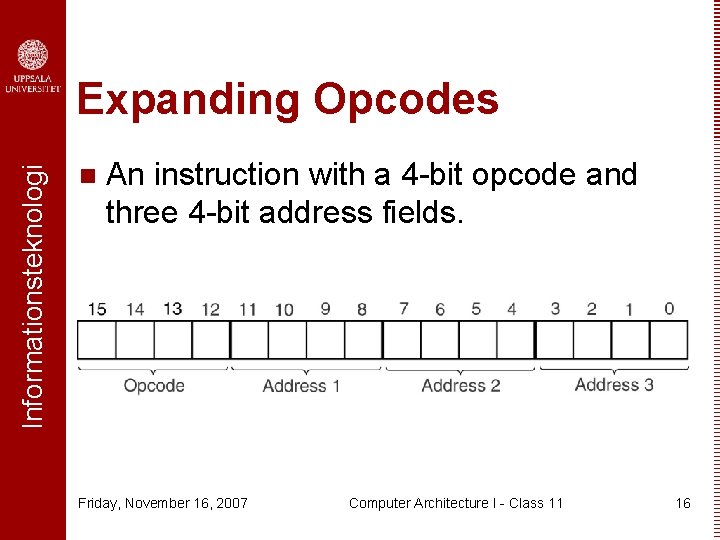

Informationsteknologi Expanding Opcodes n An instruction with a 4 -bit opcode and three 4 -bit address fields. Friday, November 16, 2007 Computer Architecture I - Class 11 16

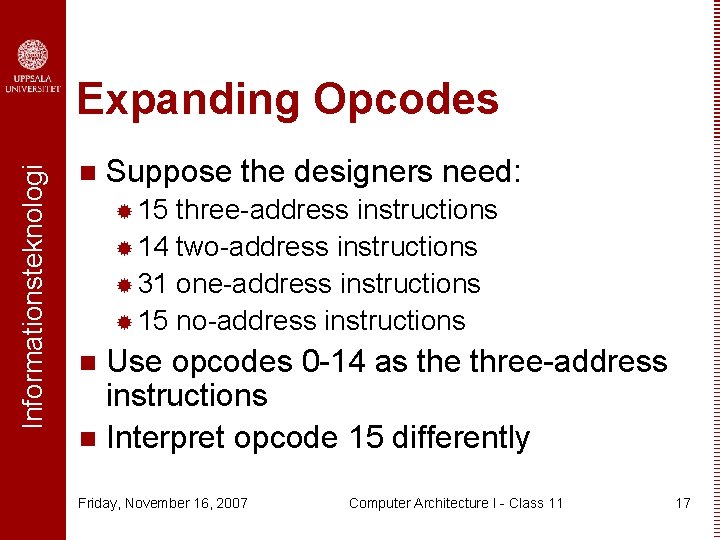

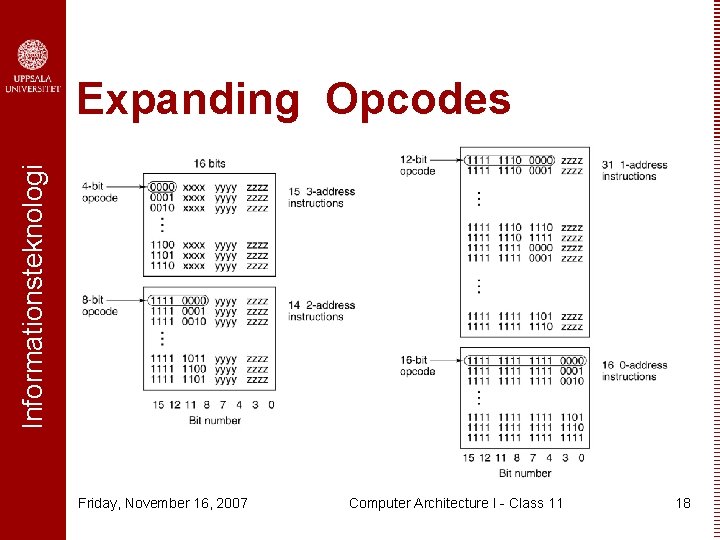

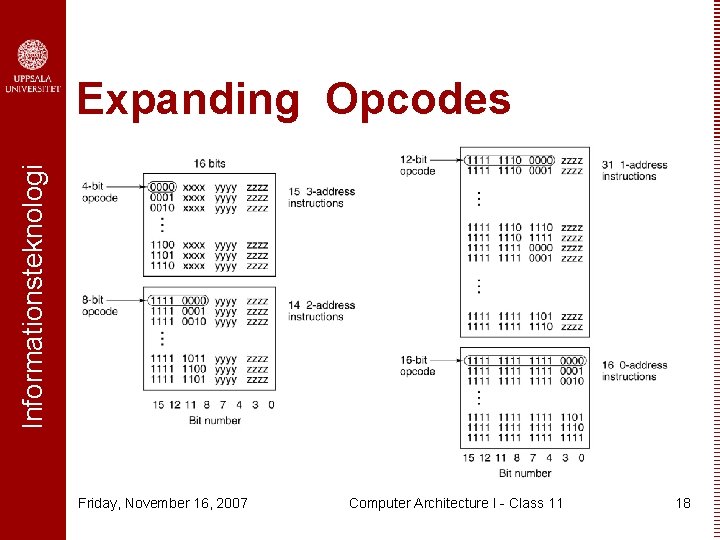

Informationsteknologi Expanding Opcodes n Suppose the designers need: ® 15 three-address instructions ® 14 two-address instructions ® 31 one-address instructions ® 15 no-address instructions Use opcodes 0 -14 as the three-address instructions n Interpret opcode 15 differently n Friday, November 16, 2007 Computer Architecture I - Class 11 17

Informationsteknologi Expanding Opcodes Friday, November 16, 2007 Computer Architecture I - Class 11 18

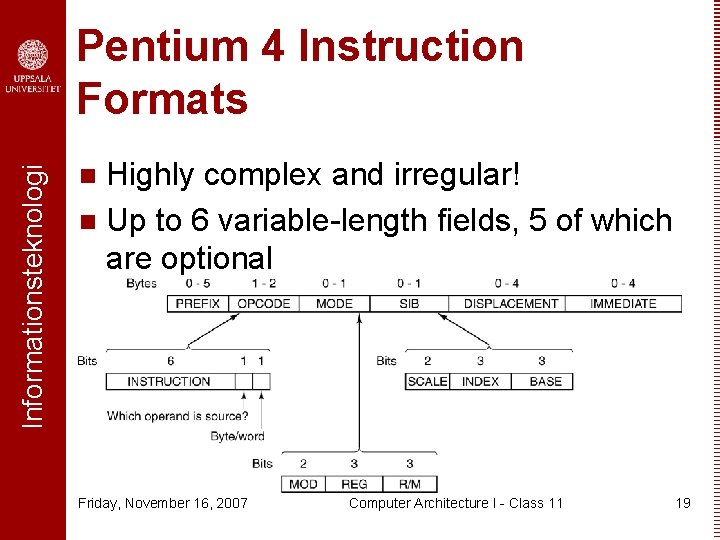

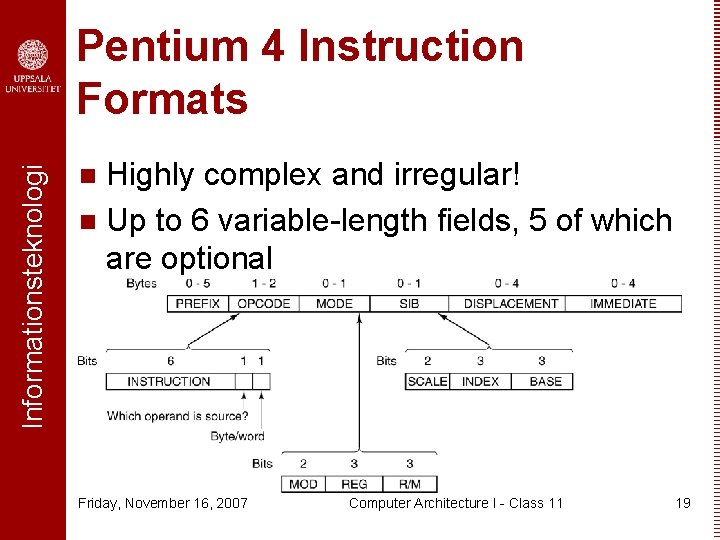

Informationsteknologi Pentium 4 Instruction Formats Highly complex and irregular! n Up to 6 variable-length fields, 5 of which are optional n Friday, November 16, 2007 Computer Architecture I - Class 11 19

Informationsteknologi Addressing Modes How to specify where an operand for an instruction is located n How the bits of an address field in an instruction are interpreted n Friday, November 16, 2007 Computer Architecture I - Class 11 20

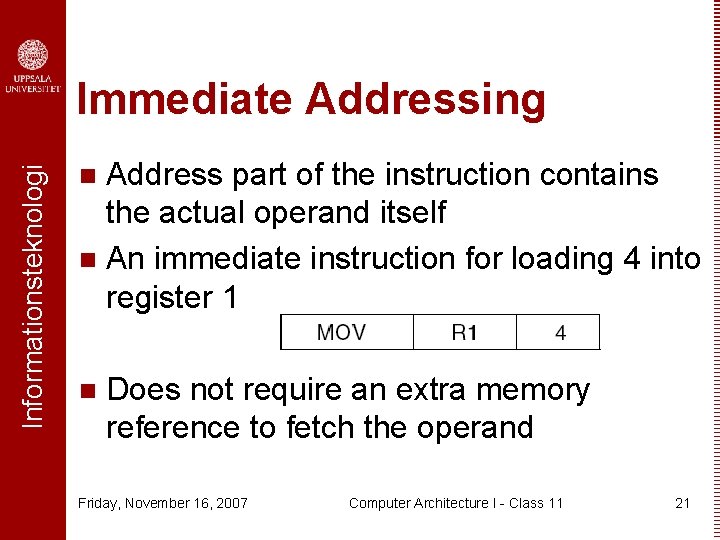

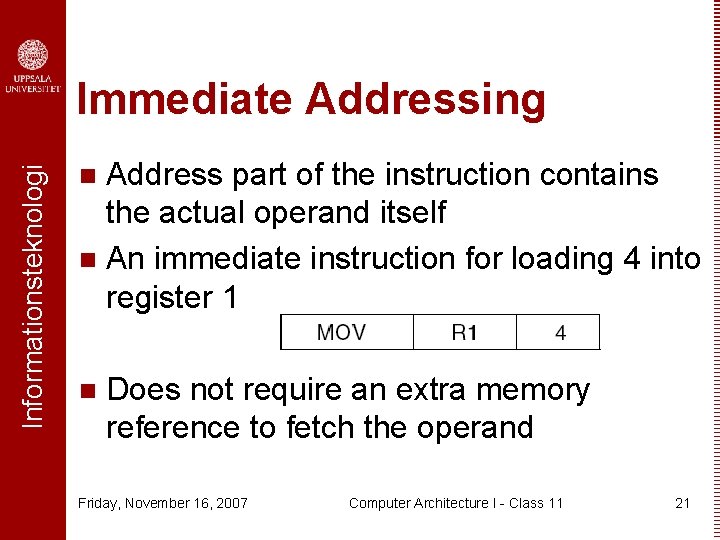

Informationsteknologi Immediate Addressing Address part of the instruction contains the actual operand itself n An immediate instruction for loading 4 into register 1 n n Does not require an extra memory reference to fetch the operand Friday, November 16, 2007 Computer Architecture I - Class 11 21

Informationsteknologi Direct Addressing Instruction specifies full address of the operand n Instruction will always access the same memory location n Useful for accessing global variables n Friday, November 16, 2007 Computer Architecture I - Class 11 22

Informationsteknologi Register Addressing Specifies a register for the operand n Most common addressing mode on computers n Friday, November 16, 2007 Computer Architecture I - Class 11 23

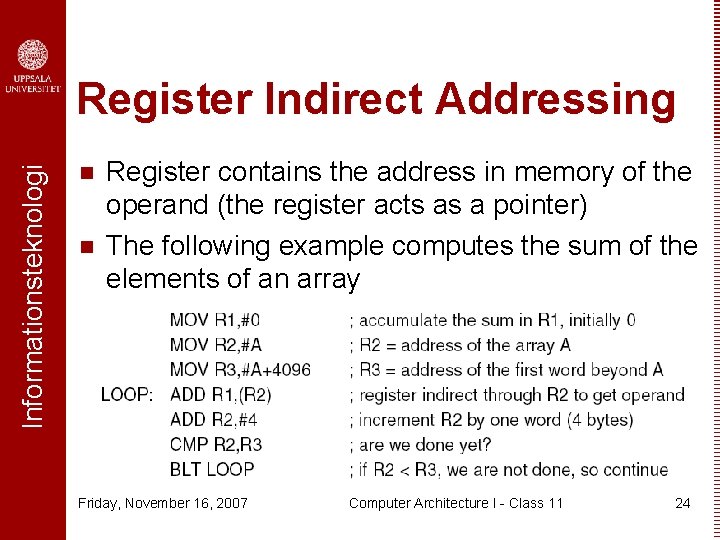

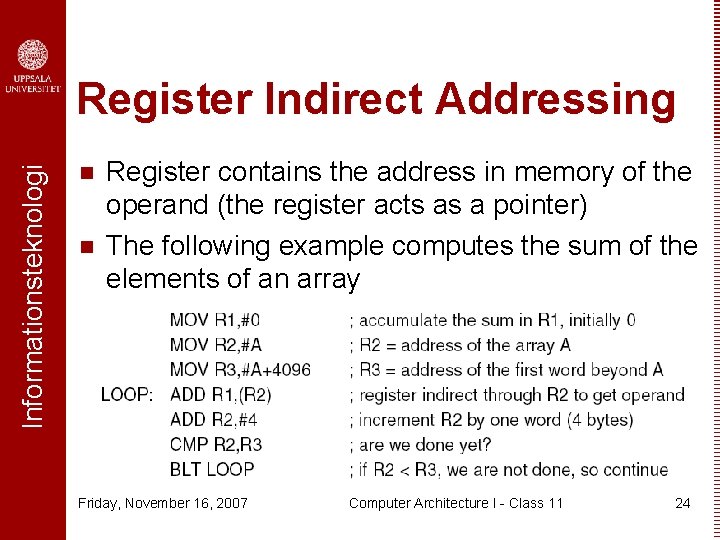

Informationsteknologi Register Indirect Addressing n n Register contains the address in memory of the operand (the register acts as a pointer) The following example computes the sum of the elements of an array Friday, November 16, 2007 Computer Architecture I - Class 11 24

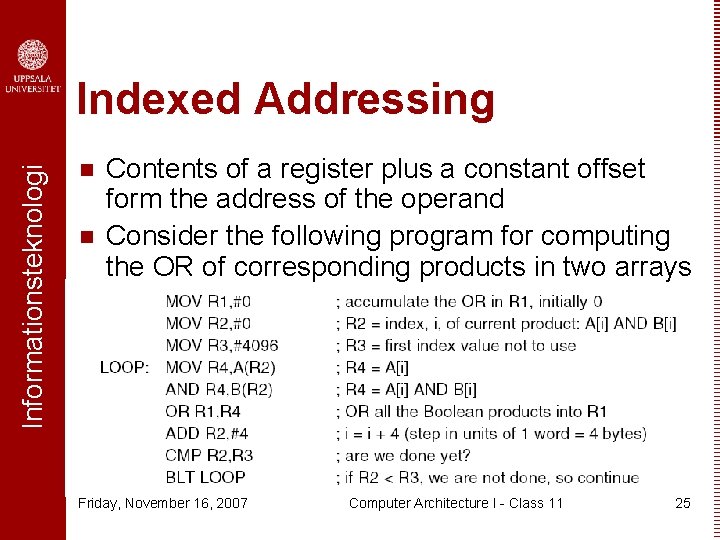

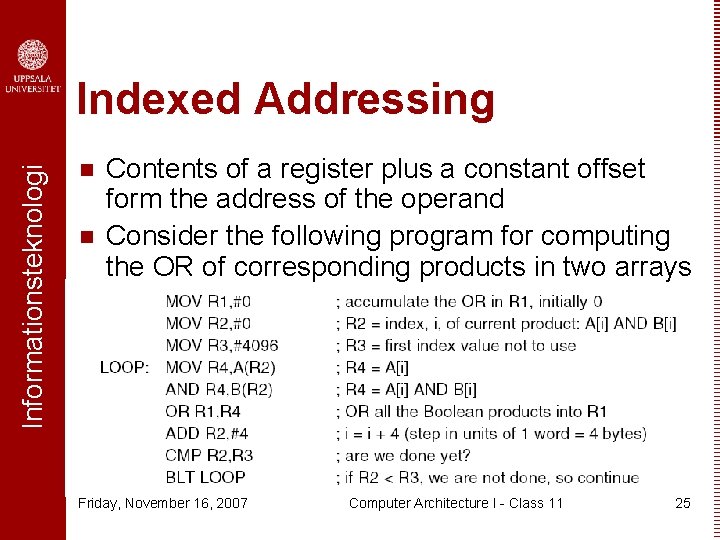

Informationsteknologi Indexed Addressing n n Contents of a register plus a constant offset form the address of the operand Consider the following program for computing the OR of corresponding products in two arrays Friday, November 16, 2007 Computer Architecture I - Class 11 25

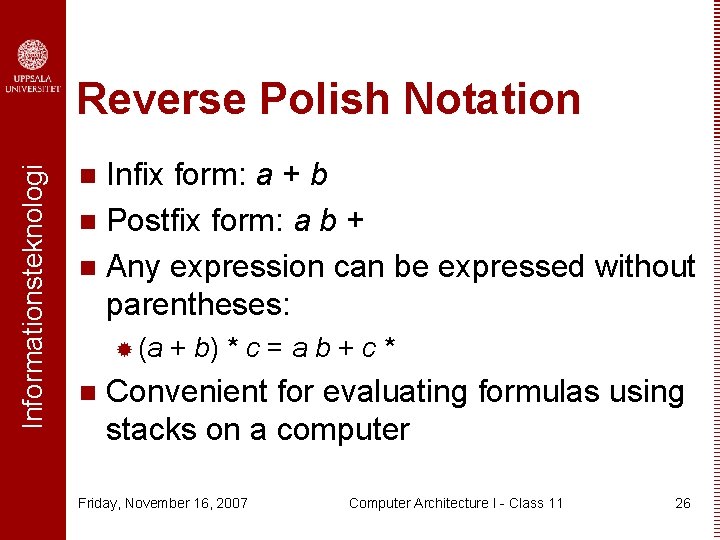

Informationsteknologi Reverse Polish Notation Infix form: a + b n Postfix form: a b + n Any expression can be expressed without parentheses: n ® (a n + b) * c = a b + c * Convenient for evaluating formulas using stacks on a computer Friday, November 16, 2007 Computer Architecture I - Class 11 26

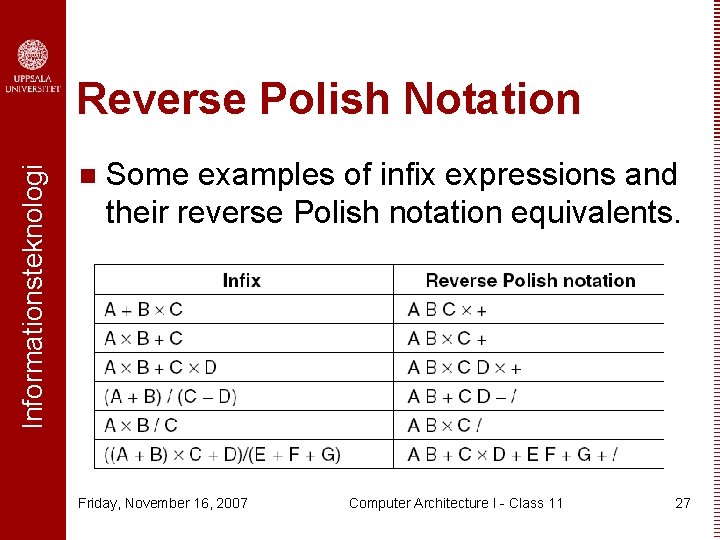

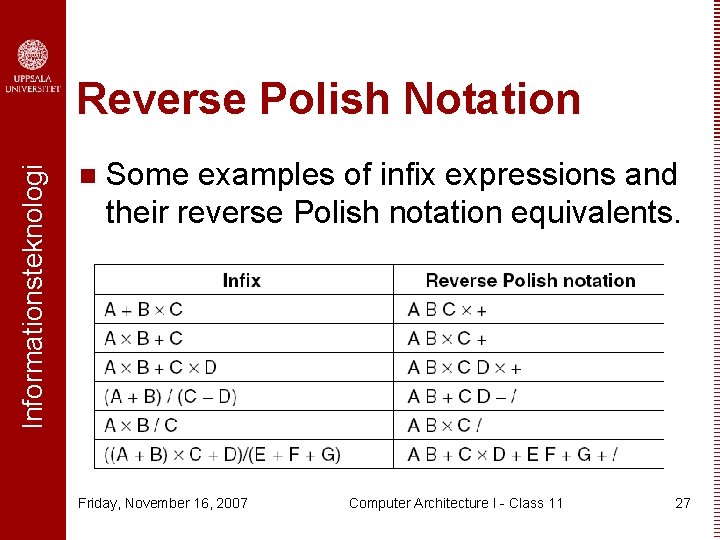

Informationsteknologi Reverse Polish Notation n Some examples of infix expressions and their reverse Polish notation equivalents. Friday, November 16, 2007 Computer Architecture I - Class 11 27

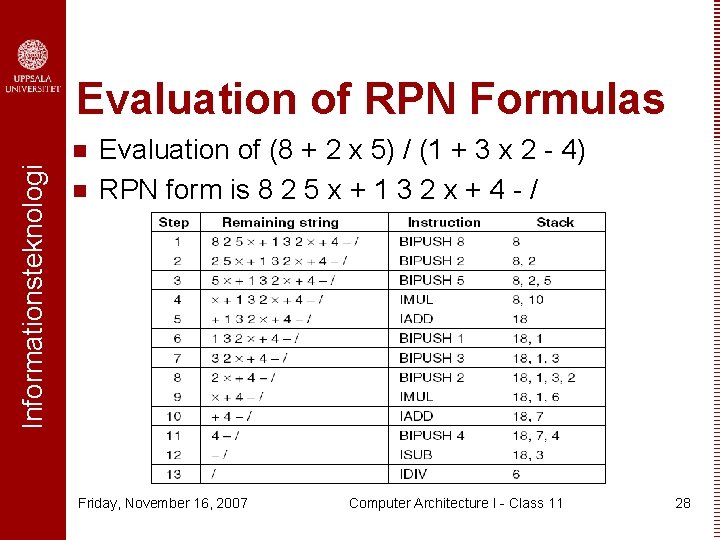

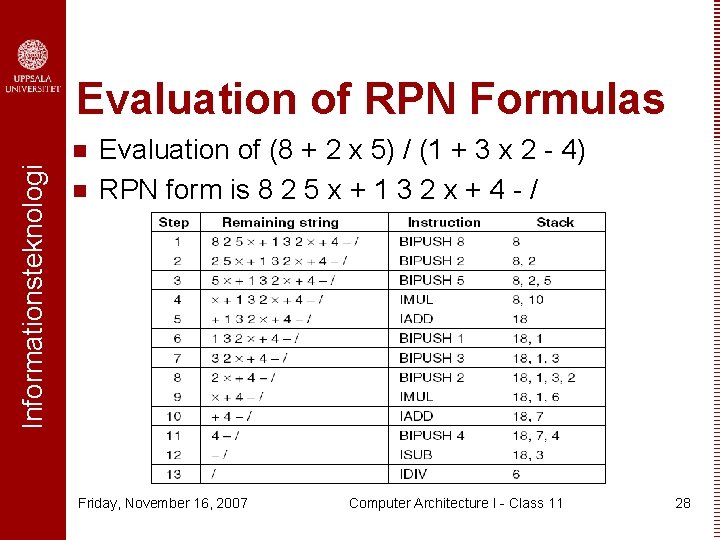

Evaluation of RPN Formulas Informationsteknologi n n Evaluation of (8 + 2 x 5) / (1 + 3 x 2 - 4) RPN form is 8 2 5 x + 1 3 2 x + 4 - / Friday, November 16, 2007 Computer Architecture I - Class 11 28

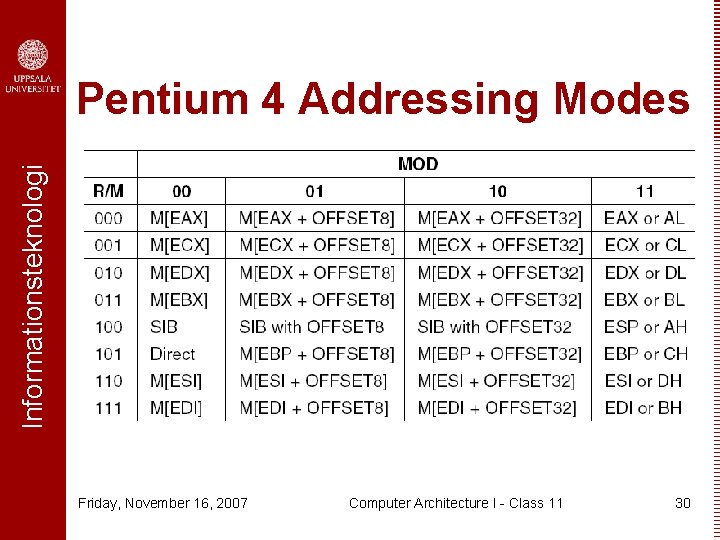

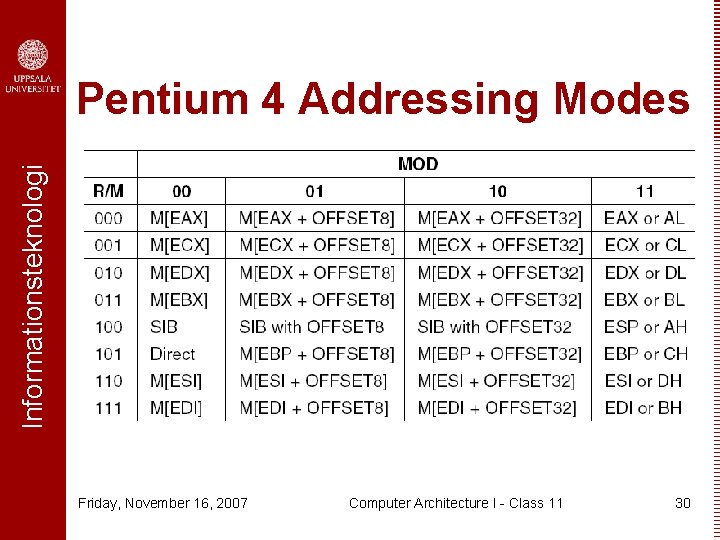

Informationsteknologi Pentium 4 Addressing Modes Highly irregular n Depends on which operating mode you are in (16 -bit or 32 -bit) n Not all modes apply to all instructions n Not all registers can be used in all modes n Compiler writer’s nightmare! n Friday, November 16, 2007 Computer Architecture I - Class 11 29

Informationsteknologi Pentium 4 Addressing Modes Friday, November 16, 2007 Computer Architecture I - Class 11 30

Informationsteknologi Data Movement Instructions n n Copying data is the most fundamental of all operations Four possibilities: Register to register ® Register to memory ® Memory to register ® Memory to memory ® n n May have one general instruction to cover all cases, or separate instructions for each case Need to indicate how much data to copy Friday, November 16, 2007 Computer Architecture I - Class 11 31

Informationsteknologi Dyadic Operations Combine two operands to produce a result n Arithmetic instructions n Boolean instructions n Friday, November 16, 2007 Computer Architecture I - Class 11 32

Informationsteknologi Monadic Operations Have one operand produce one result n Shift and rotate instructions n CLR, INC, NEG n Friday, November 16, 2007 Computer Architecture I - Class 11 33

Informationsteknologi Comparisons and Conditional Branches Common operation is a comparison to 0 n Use bits in the PSW, such as C, N, Z n Friday, November 16, 2007 Computer Architecture I - Class 11 34

Informationsteknologi Other Instructions Procedure calls n Loop control n Friday, November 16, 2007 Computer Architecture I - Class 11 35

Informationsteknologi Programmed Input/Output Single input instruction and single output instruction n Selects an I/O device and a single character is transferred n CPU must execute an explicit sequence of instructions for each and every character read or written n Friday, November 16, 2007 Computer Architecture I - Class 11 36

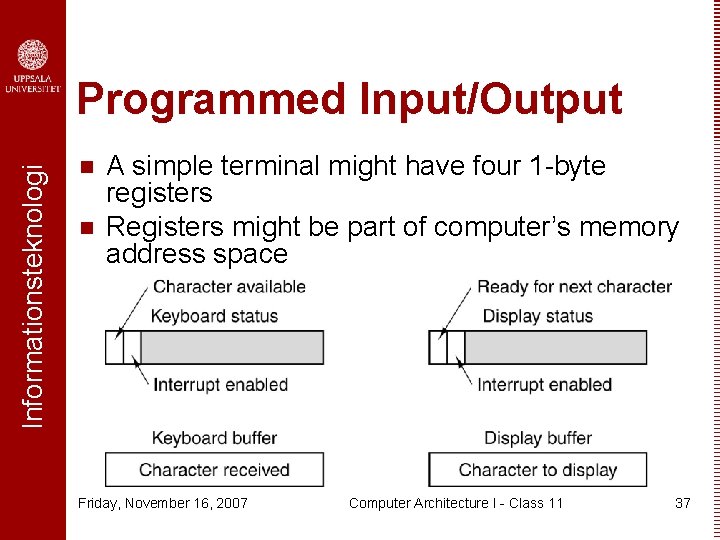

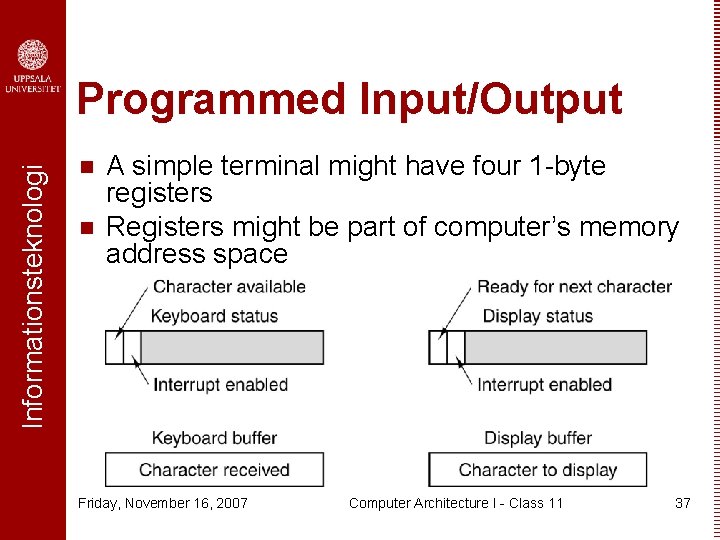

Informationsteknologi Programmed Input/Output n n A simple terminal might have four 1 -byte registers Registers might be part of computer’s memory address space Friday, November 16, 2007 Computer Architecture I - Class 11 37

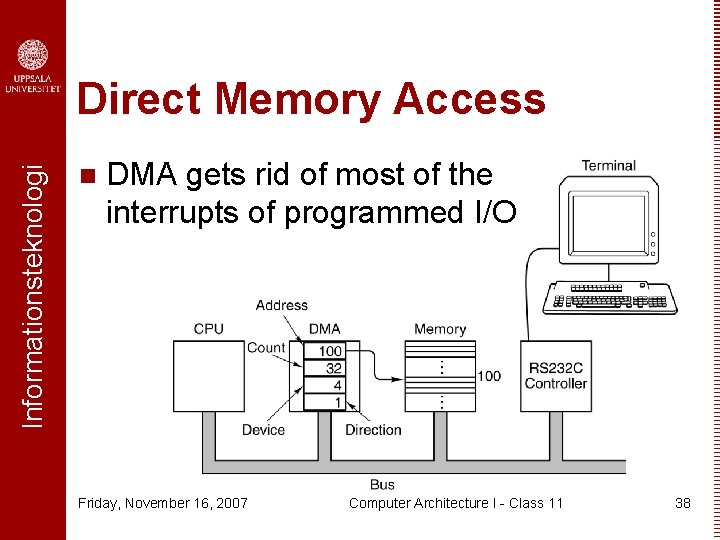

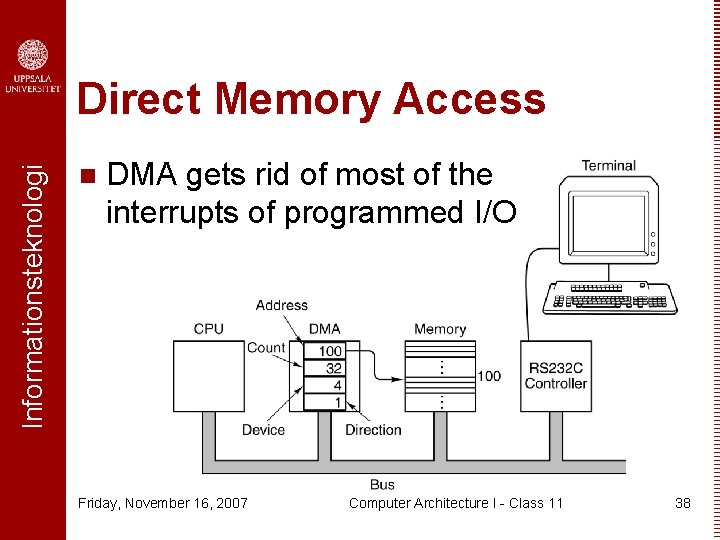

Informationsteknologi Direct Memory Access n DMA gets rid of most of the interrupts of programmed I/O Friday, November 16, 2007 Computer Architecture I - Class 11 38

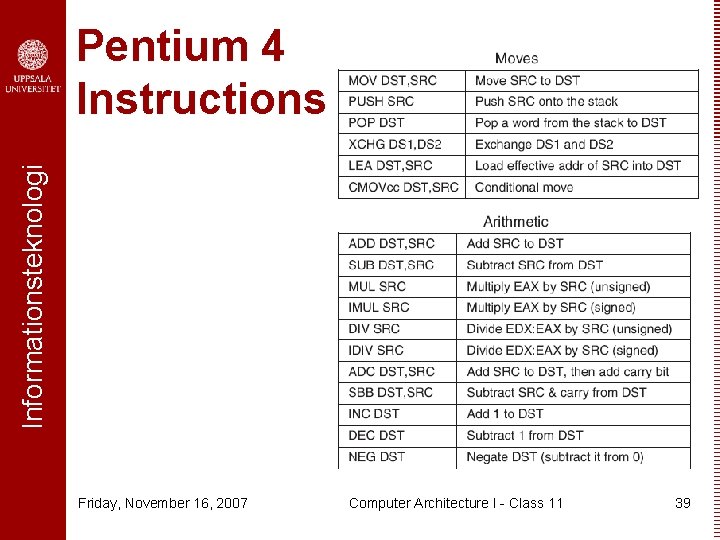

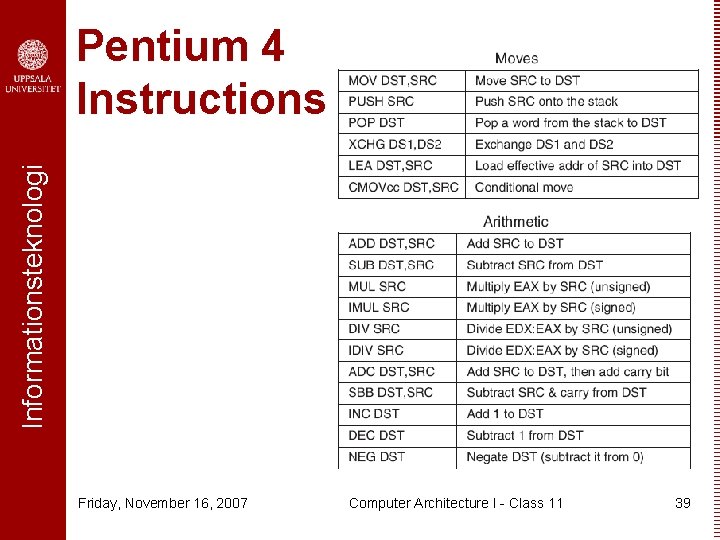

Informationsteknologi Pentium 4 Instructions Friday, November 16, 2007 Computer Architecture I - Class 11 39

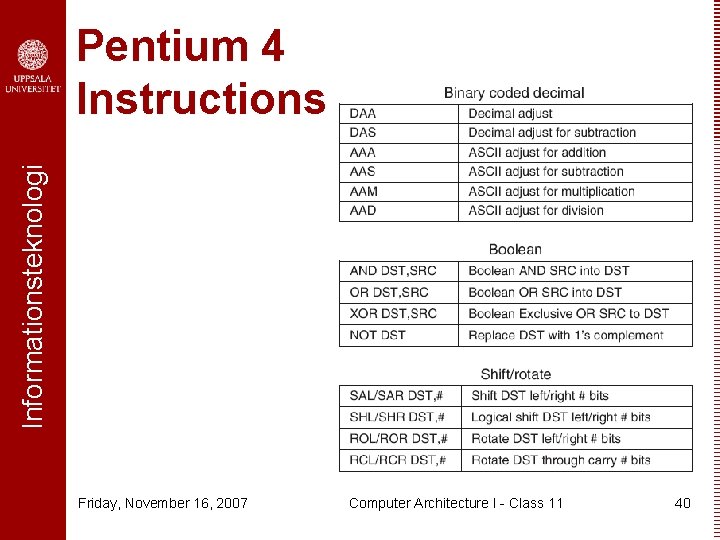

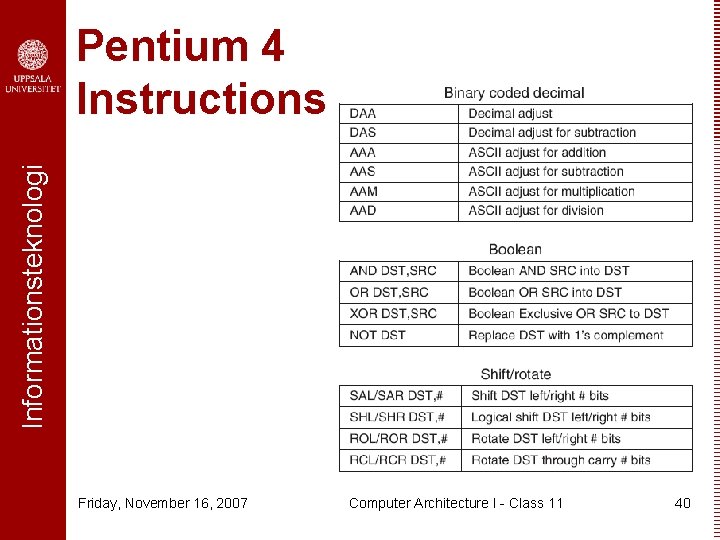

Informationsteknologi Pentium 4 Instructions Friday, November 16, 2007 Computer Architecture I - Class 11 40

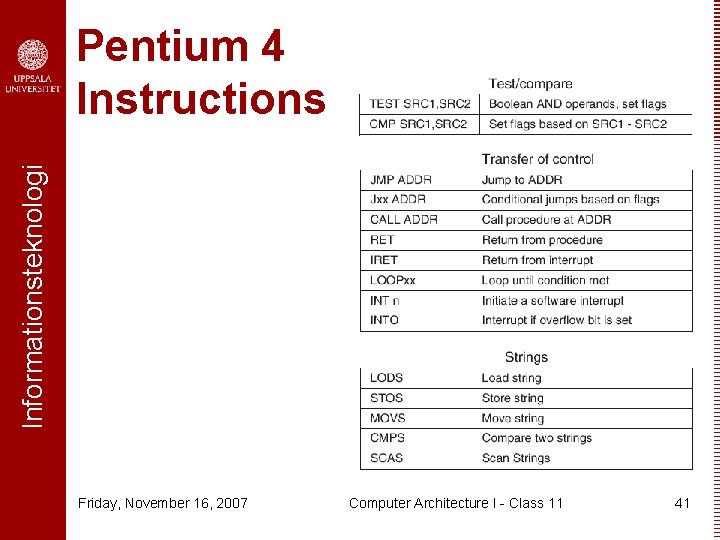

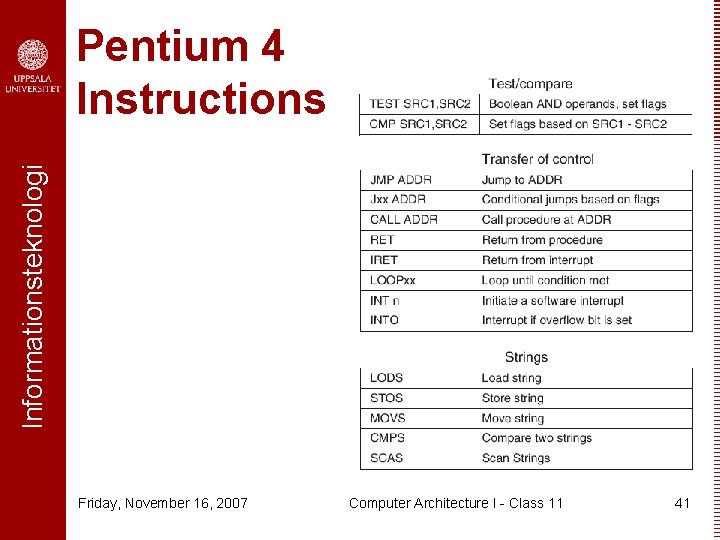

Informationsteknologi Pentium 4 Instructions Friday, November 16, 2007 Computer Architecture I - Class 11 41

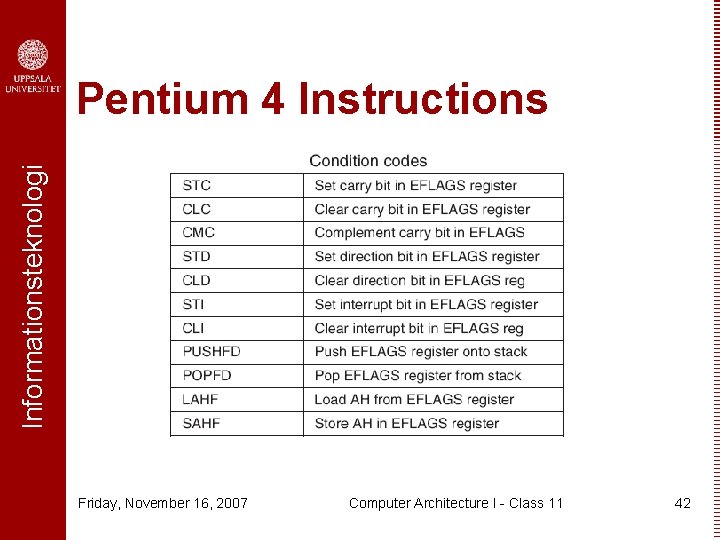

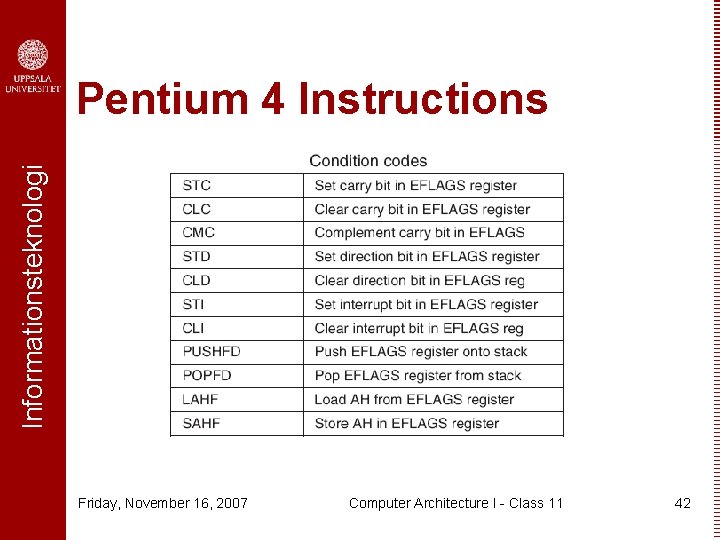

Informationsteknologi Pentium 4 Instructions Friday, November 16, 2007 Computer Architecture I - Class 11 42

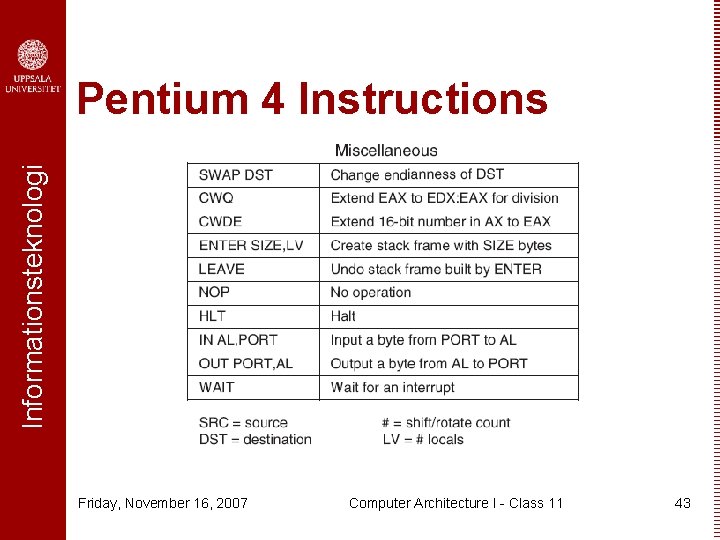

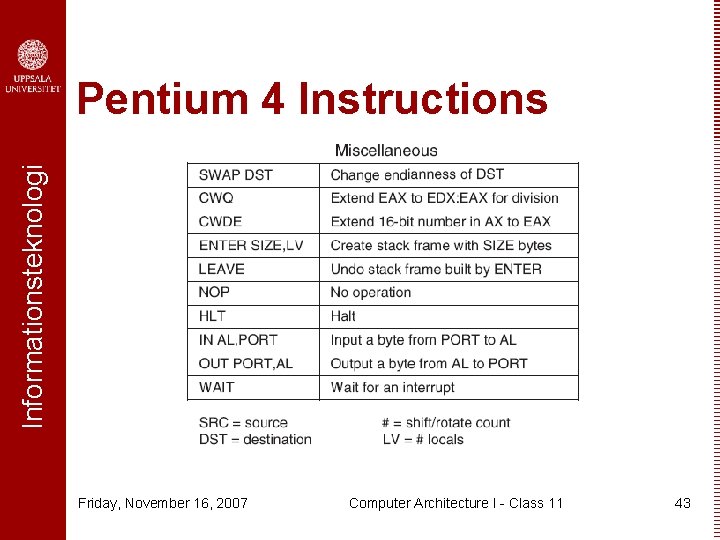

Informationsteknologi Pentium 4 Instructions Friday, November 16, 2007 Computer Architecture I - Class 11 43

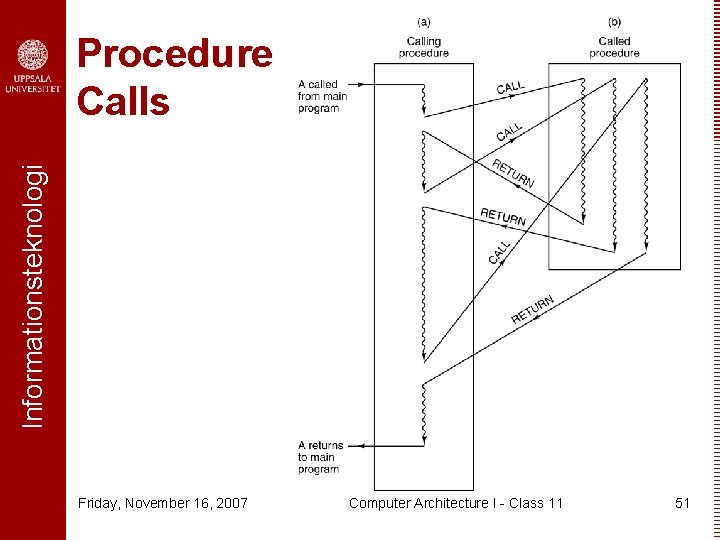

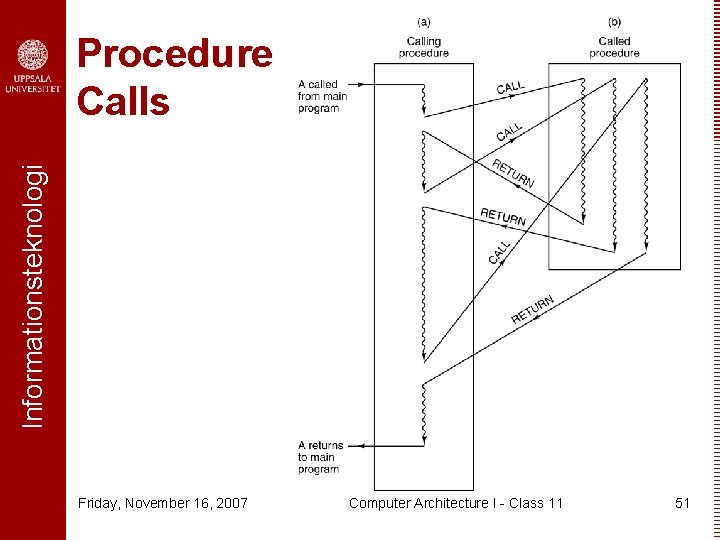

Informationsteknologi Flow of Control Most statements execute sequentially n Branches alter statement flow n Procedures also alter statement flow, but unlike branches, control is returned to the statement after the procedure call once the procedure is finished n Recursive procedures are procedures that call themselves n Friday, November 16, 2007 Computer Architecture I - Class 11 44

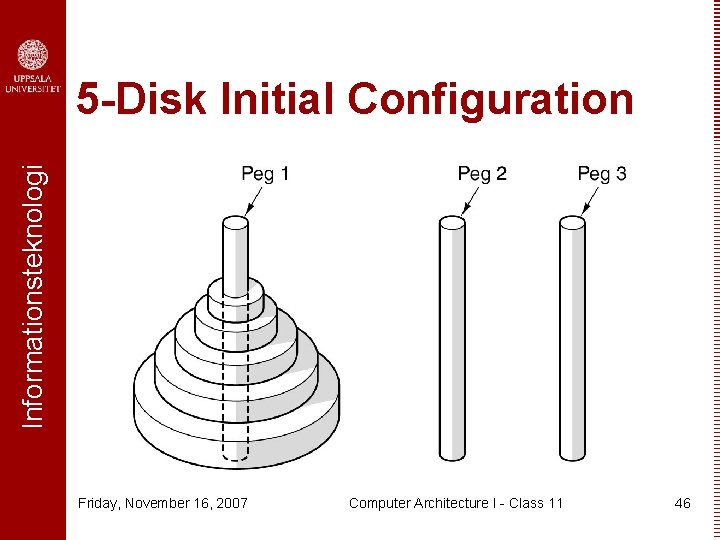

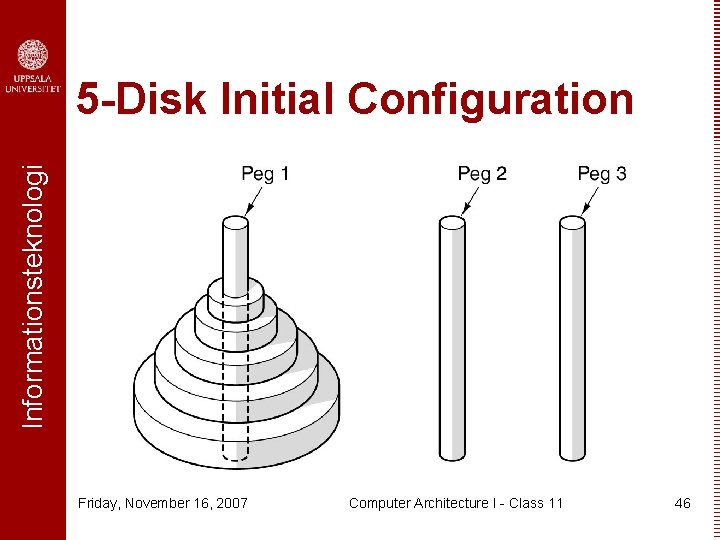

Informationsteknologi The Towers of Hanoi n n n An ancient problem with a simple recursive solution In a certain monastery in Hanoi there are 3 gold pegs Around the first peg are 64 gold disks, each disk slightly smaller in diameter than the disk below it The monks have to move the disks to the third peg, one disk at a time, but at no time may a larger disk sit on top of a smaller one It is said that when they finish the world will come to an end Friday, November 16, 2007 Computer Architecture I - Class 11 45

Informationsteknologi 5 -Disk Initial Configuration Friday, November 16, 2007 Computer Architecture I - Class 11 46

Informationsteknologi Solution Outline First move n-1 disks from peg 1 to peg 2 n Now move 1 disk from peg 1 to peg 3 n Then move the n-1 disks from peg 2 to peg 3 n Friday, November 16, 2007 Computer Architecture I - Class 11 47

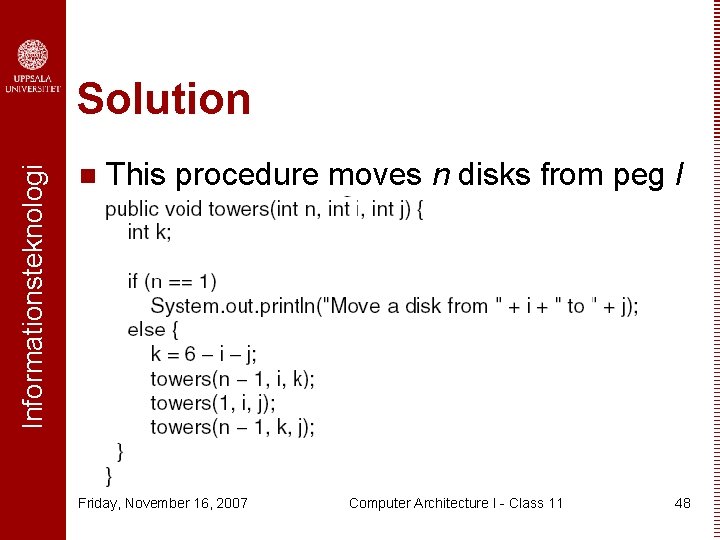

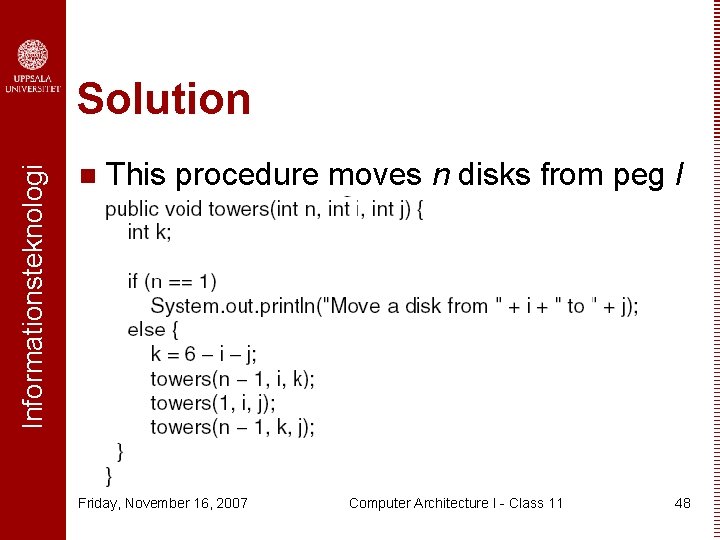

Informationsteknologi Solution n This procedure moves n disks from peg I to peg j. Friday, November 16, 2007 Computer Architecture I - Class 11 48

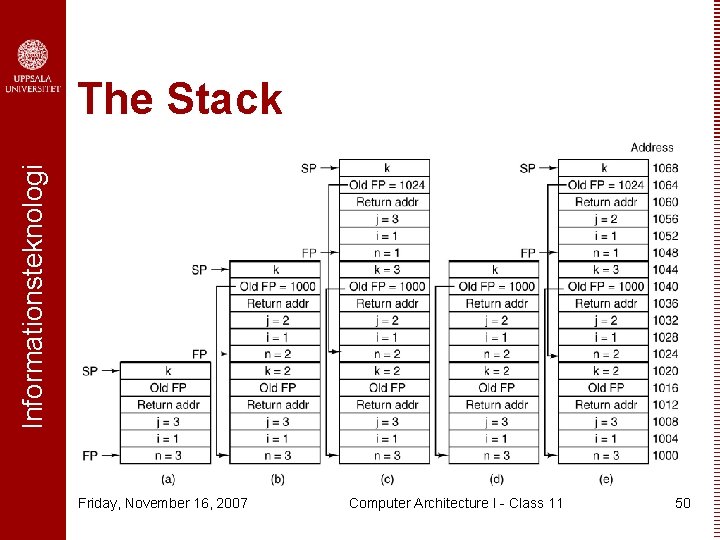

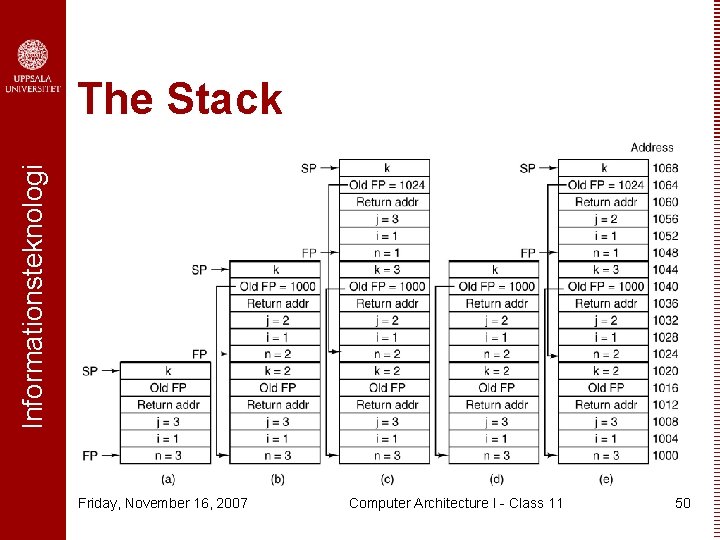

Informationsteknologi The Stack Need a stack to store the parameters and local variables for each invocation of a recursive procedure n Do not want to confuse values of these variables in different invocations n Friday, November 16, 2007 Computer Architecture I - Class 11 49

Informationsteknologi The Stack Friday, November 16, 2007 Computer Architecture I - Class 11 50

Informationsteknologi Procedure Calls Friday, November 16, 2007 Computer Architecture I - Class 11 51

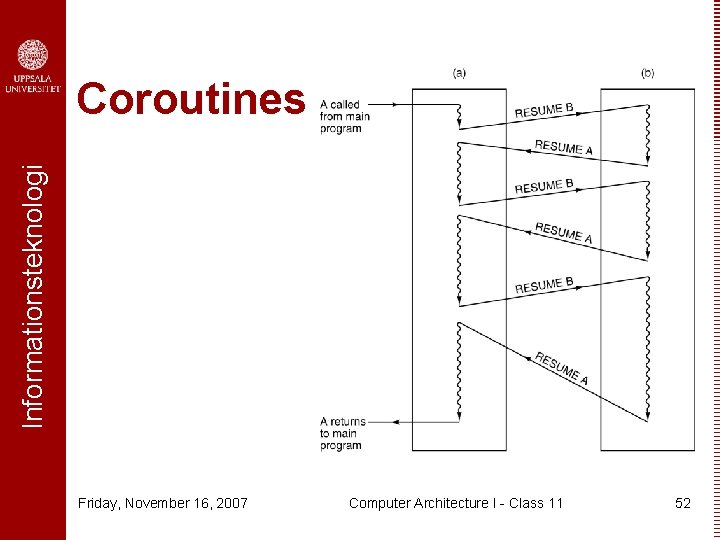

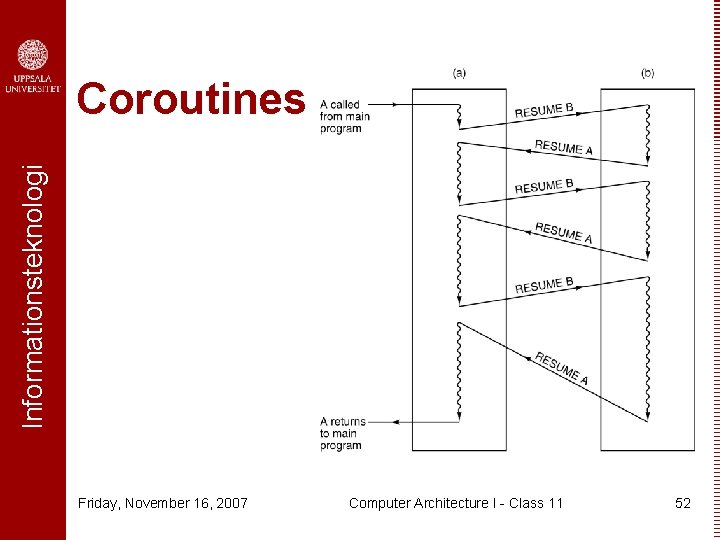

Informationsteknologi Coroutines Friday, November 16, 2007 Computer Architecture I - Class 11 52

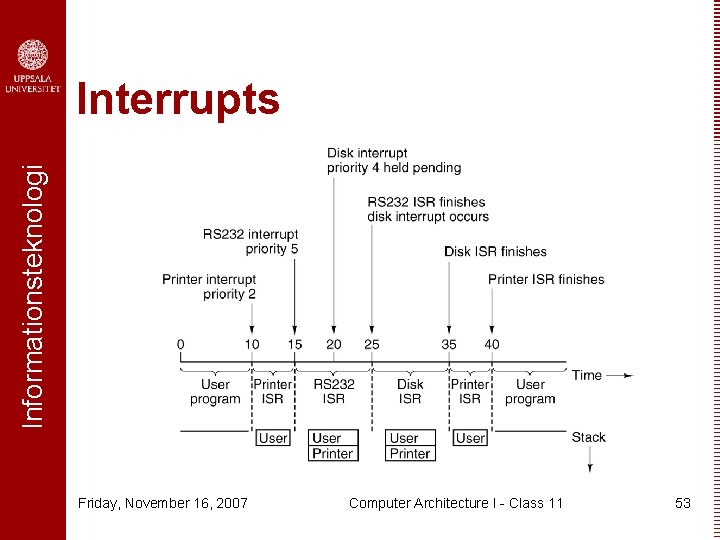

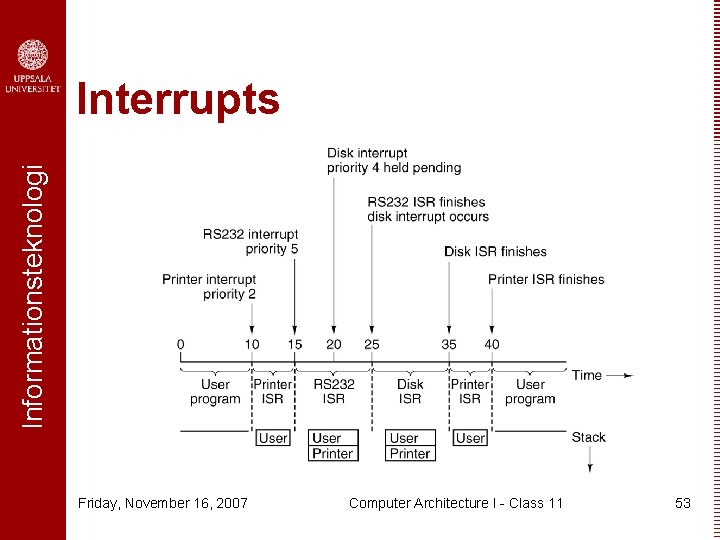

Informationsteknologi Interrupts Friday, November 16, 2007 Computer Architecture I - Class 11 53