x 86s instruction sets 1 Instruction Set Classification

![MOV Example o o o o MOV AX, 1000 h MOV [100 h], AX MOV Example o o o o MOV AX, 1000 h MOV [100 h], AX](https://slidetodoc.com/presentation_image/47487d34f2a05ca201f04cd16ab1f776/image-6.jpg)

![What is the result of… o o MOV [100 h] , 10 h Address What is the result of… o o MOV [100 h] , 10 h Address](https://slidetodoc.com/presentation_image/47487d34f2a05ca201f04cd16ab1f776/image-11.jpg)

- Slides: 52

x 86’s instruction sets 1

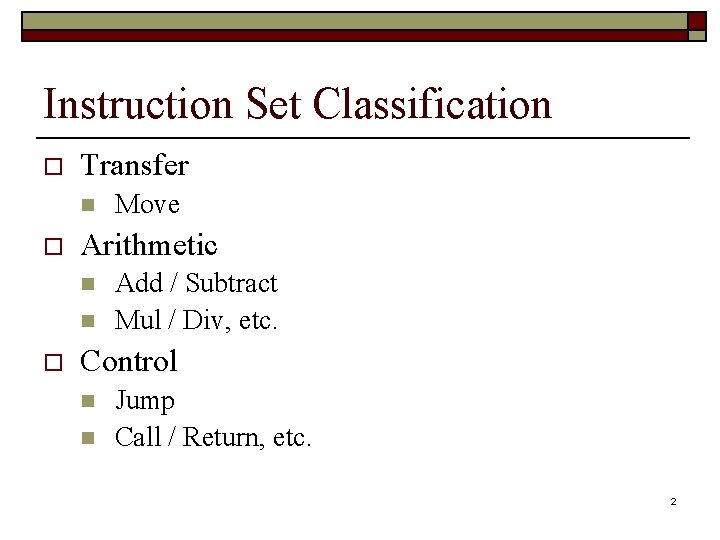

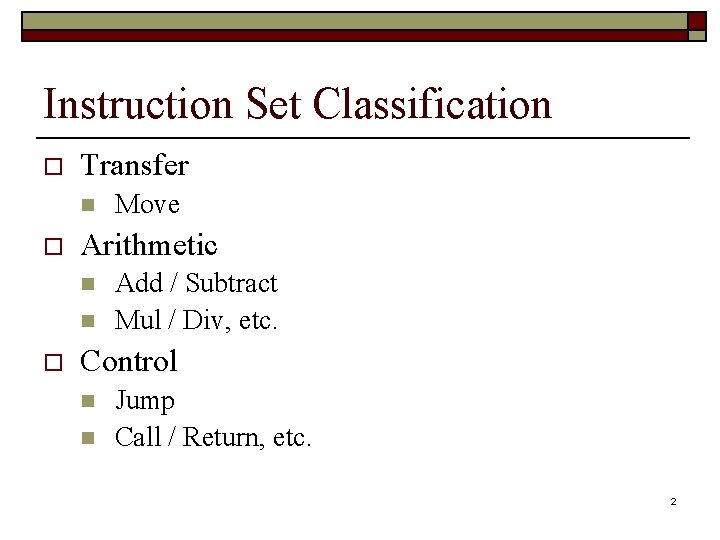

Instruction Set Classification o Transfer n o Arithmetic n n o Move Add / Subtract Mul / Div, etc. Control n n Jump Call / Return, etc. 2

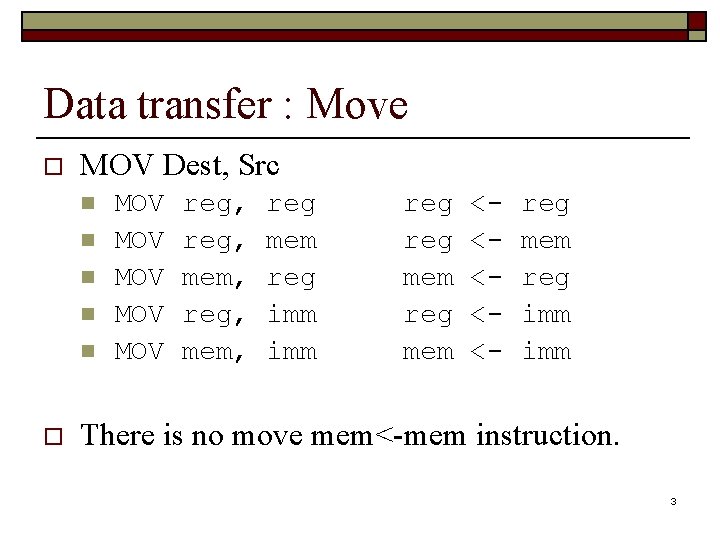

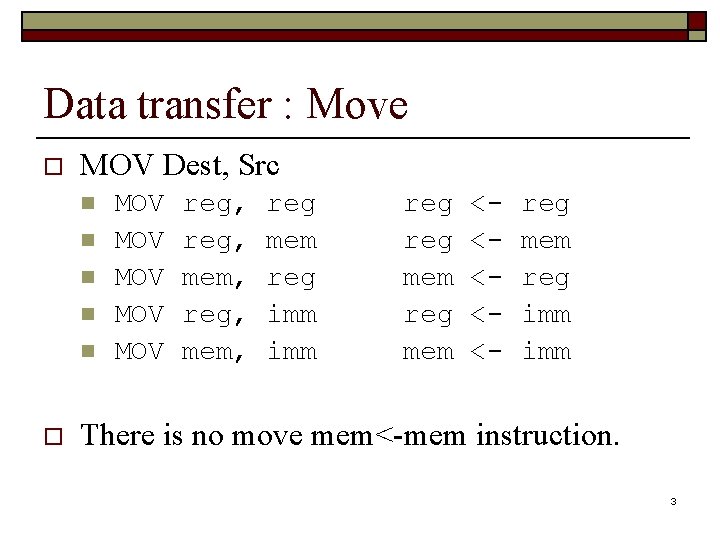

Data transfer : Move o MOV Dest, Src n n n o MOV MOV MOV reg, mem, reg mem reg imm reg mem <<<<<- reg mem reg imm There is no move mem<-mem instruction. 3

Move limitation o o o Both operand must be in the same size. There is no instruction to put immediate value directly to segment register. Have to use accumulator (AX) to accomplish this. To put immediate value directly to memory, we have to specify its size. (Byte/Word PTR( 4

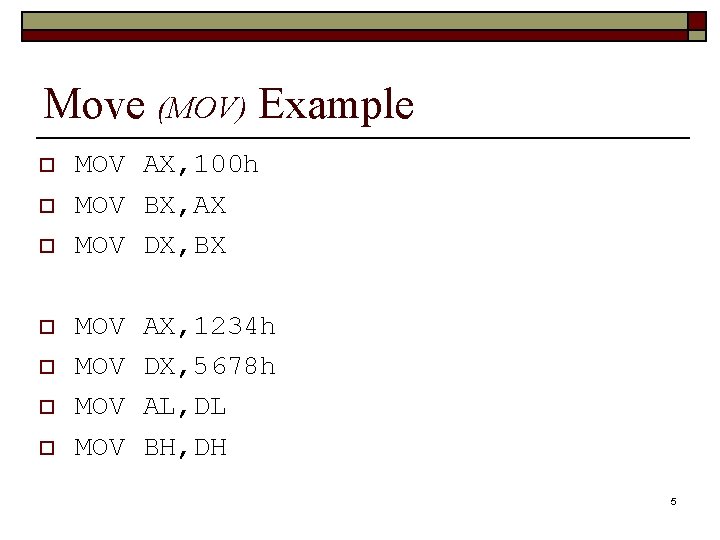

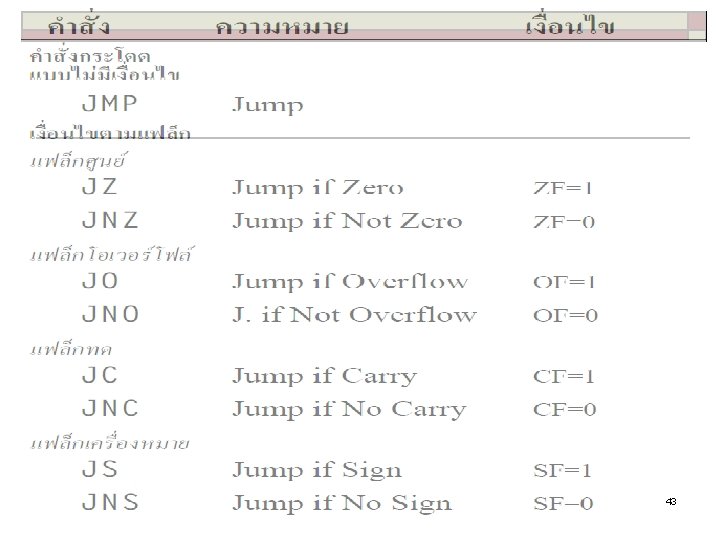

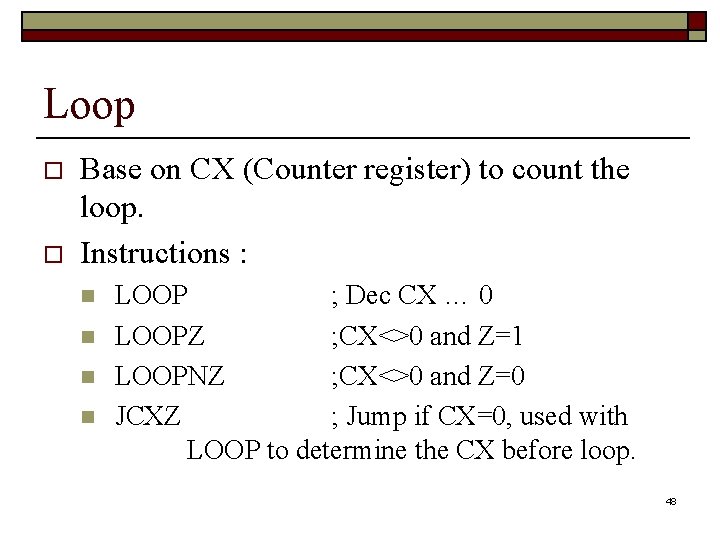

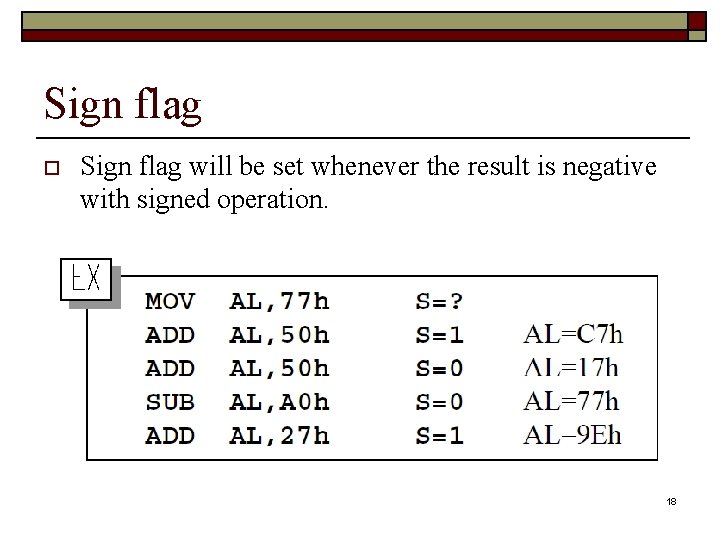

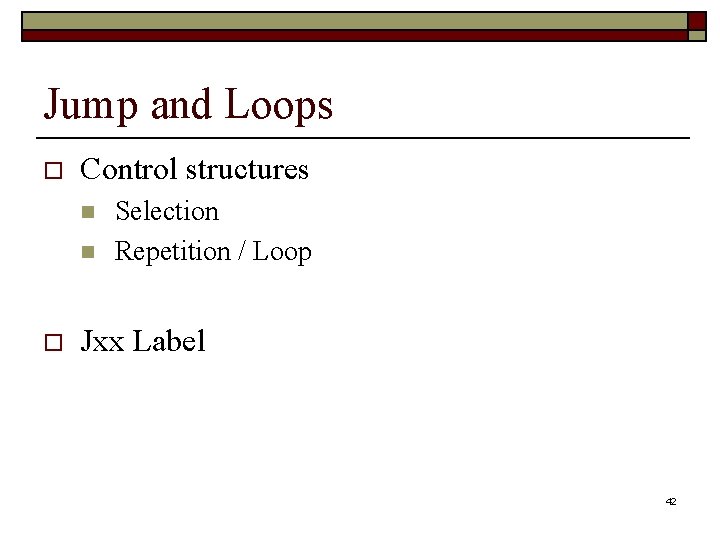

Move (MOV) Example o o o o MOV AX, 100 h MOV BX, AX MOV DX, BX MOV MOV AX, 1234 h DX, 5678 h AL, DL BH, DH 5

![MOV Example o o o o MOV AX 1000 h MOV 100 h AX MOV Example o o o o MOV AX, 1000 h MOV [100 h], AX](https://slidetodoc.com/presentation_image/47487d34f2a05ca201f04cd16ab1f776/image-6.jpg)

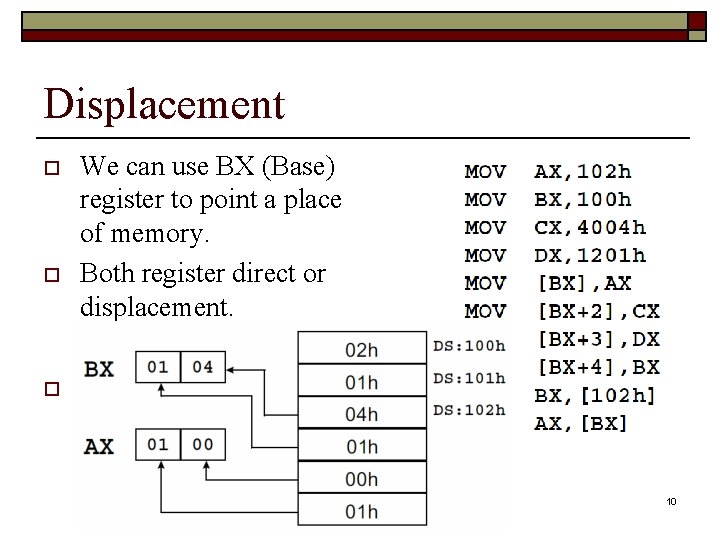

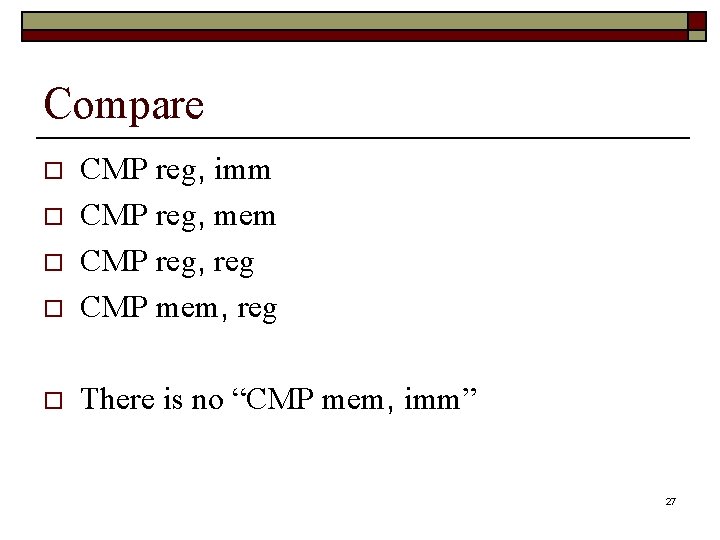

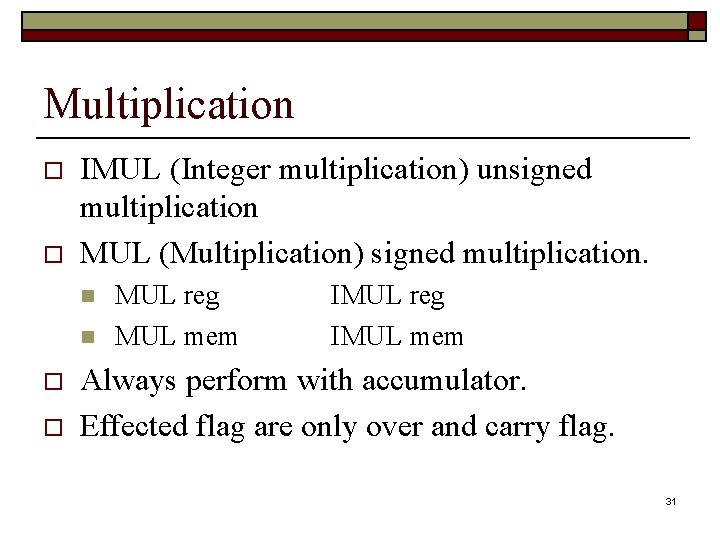

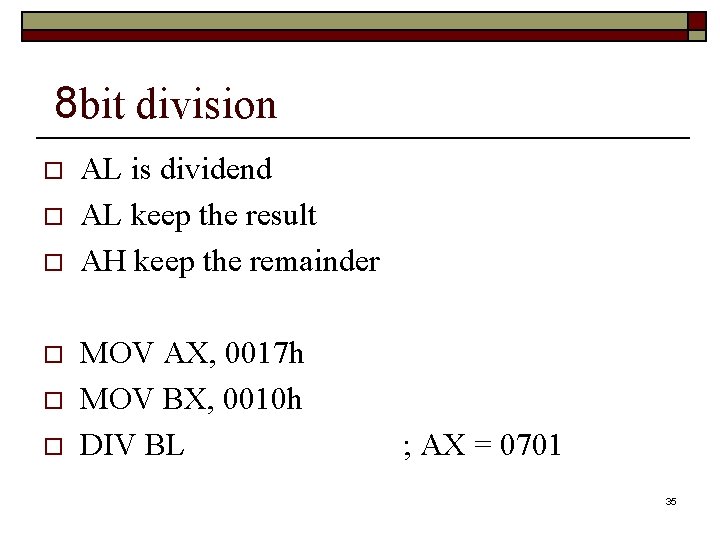

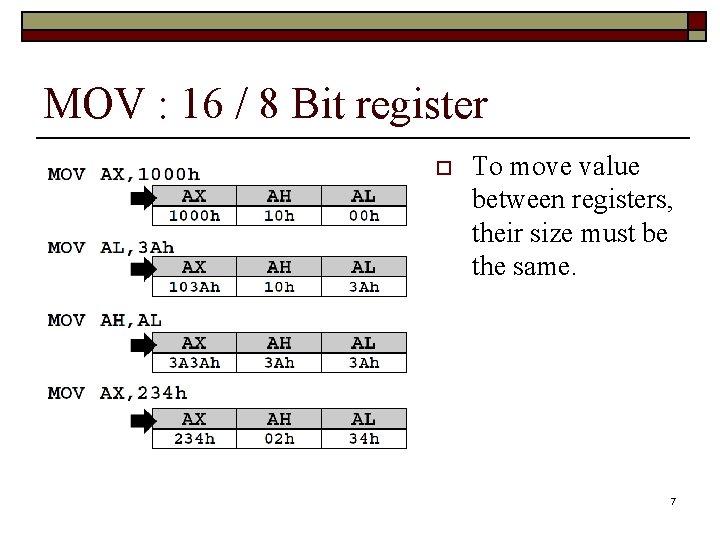

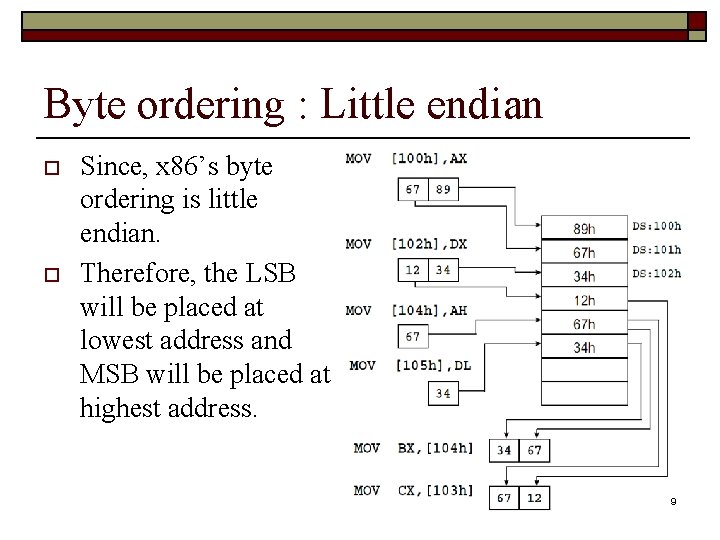

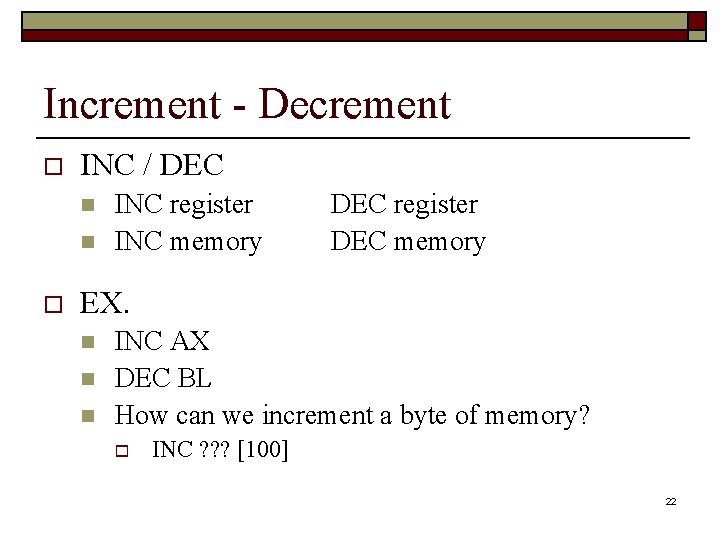

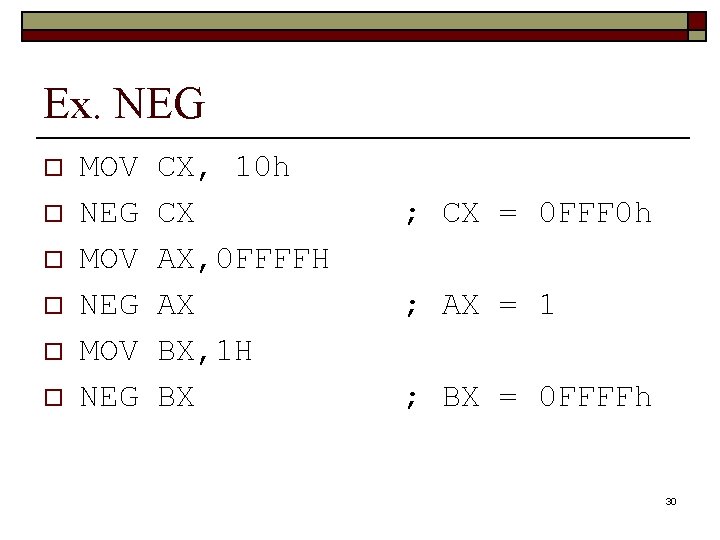

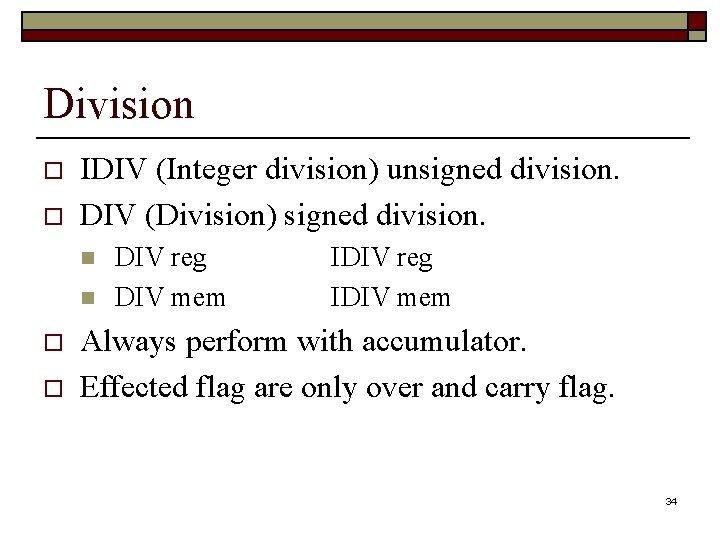

MOV Example o o o o MOV AX, 1000 h MOV [100 h], AX MOV BX, [100 h] MOV BYTE PTR [200 h], 10 h MOV WORD PTR [300 h], 10 h MOV AX, 2300 h MOV DS, AX 6

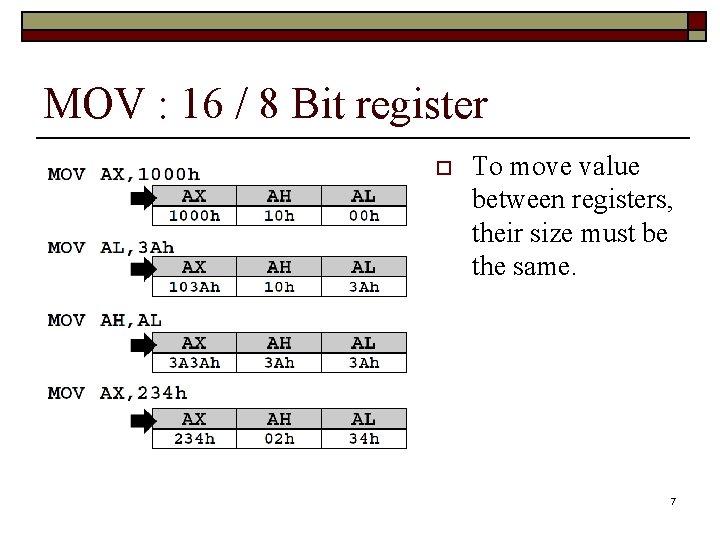

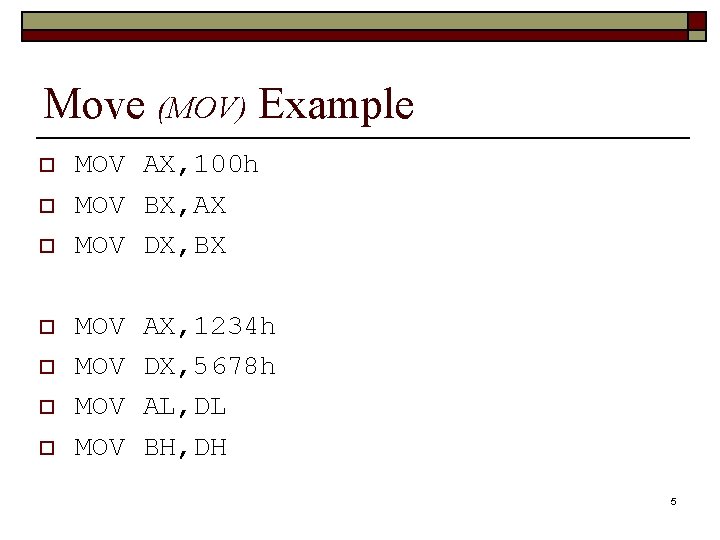

MOV : 16 / 8 Bit register o To move value between registers, their size must be the same. 7

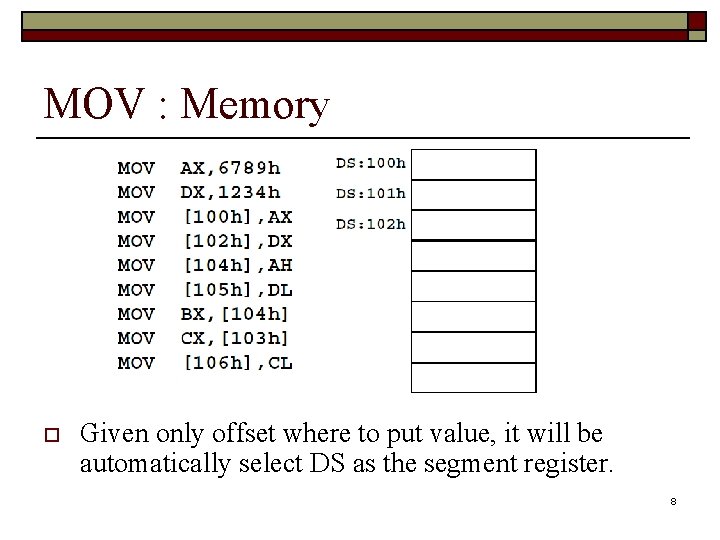

MOV : Memory o Given only offset where to put value, it will be automatically select DS as the segment register. 8

Byte ordering : Little endian o o Since, x 86’s byte ordering is little endian. Therefore, the LSB will be placed at lowest address and MSB will be placed at highest address. 9

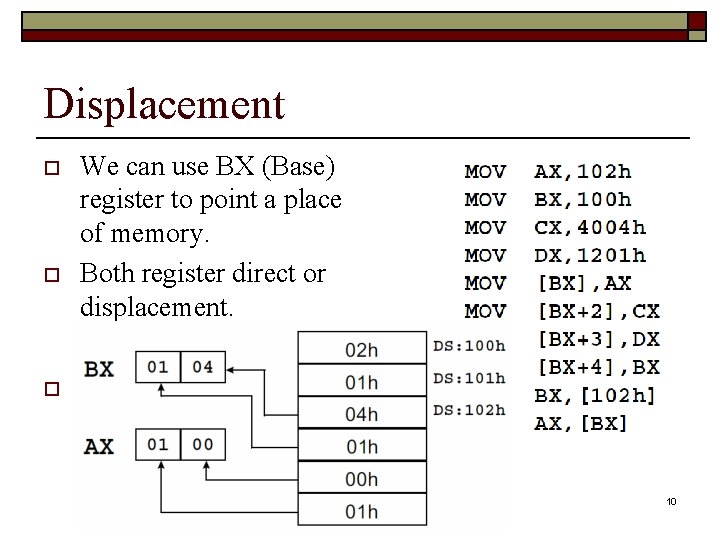

Displacement o o o We can use BX (Base) register to point a place of memory. Both register direct or displacement. AX = ? 10

![What is the result of o o MOV 100 h 10 h Address What is the result of… o o MOV [100 h] , 10 h Address](https://slidetodoc.com/presentation_image/47487d34f2a05ca201f04cd16ab1f776/image-11.jpg)

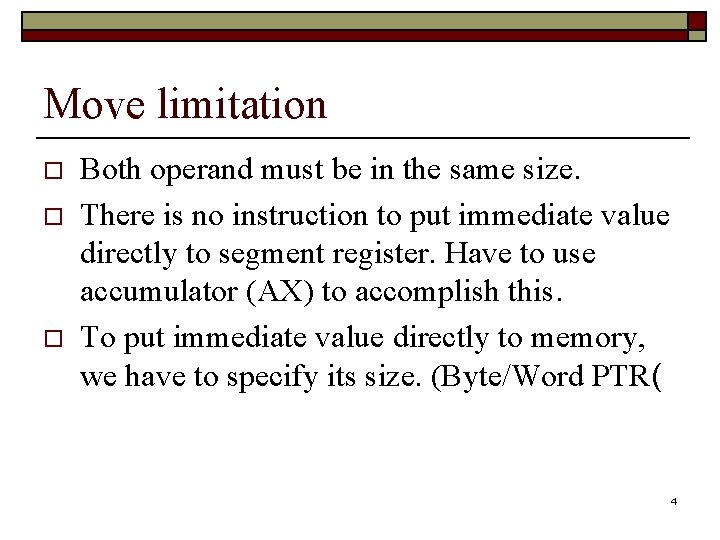

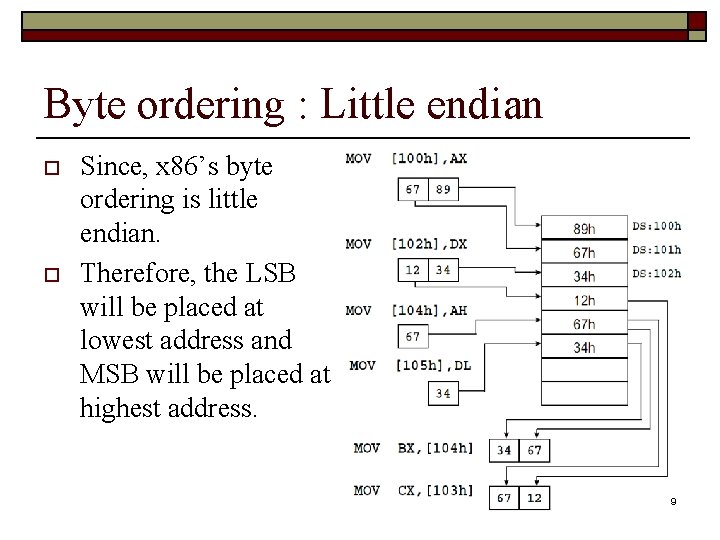

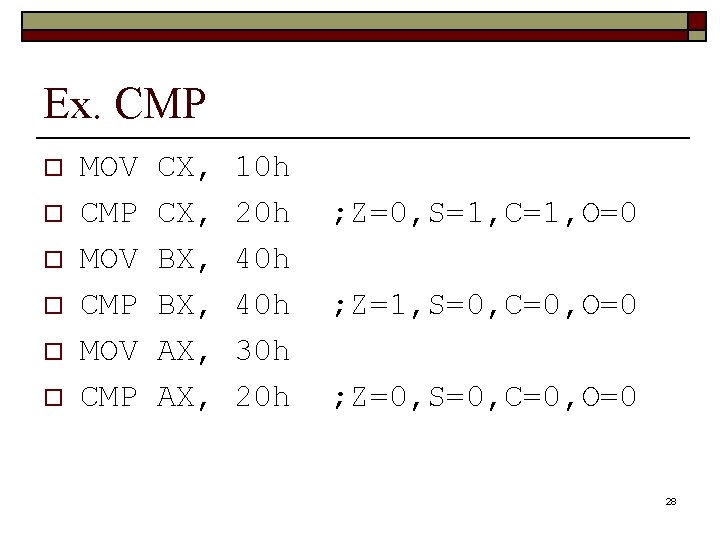

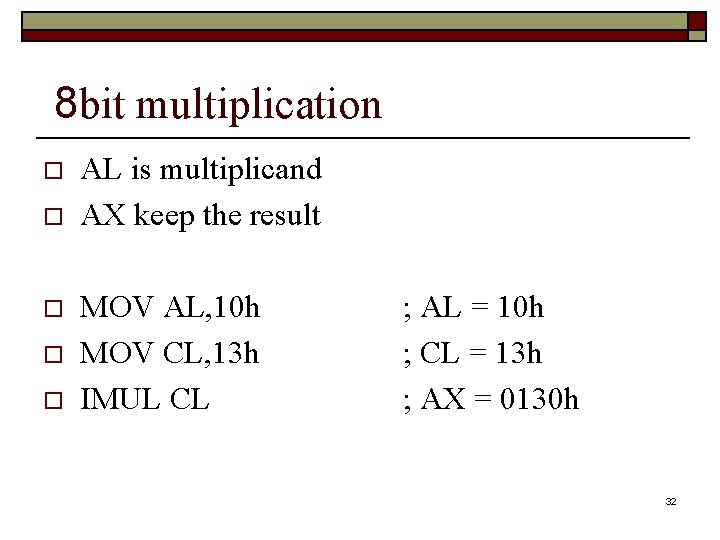

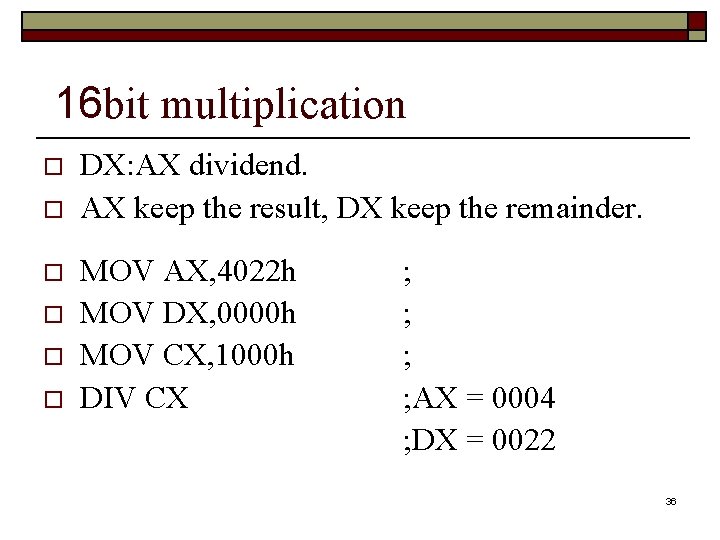

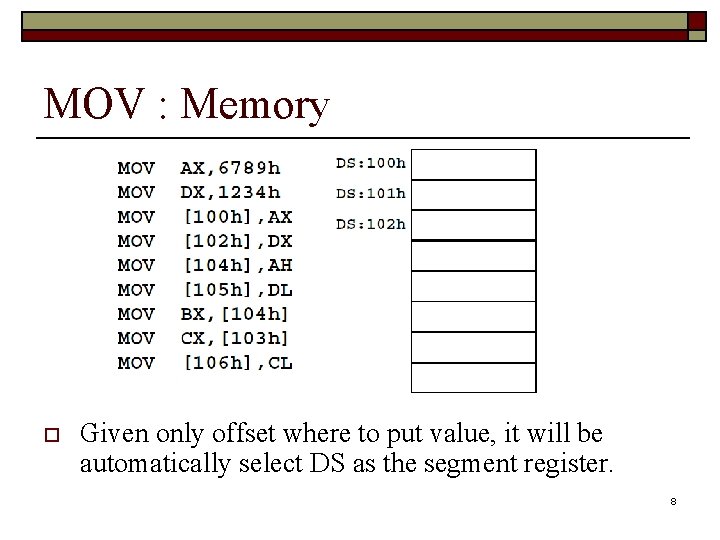

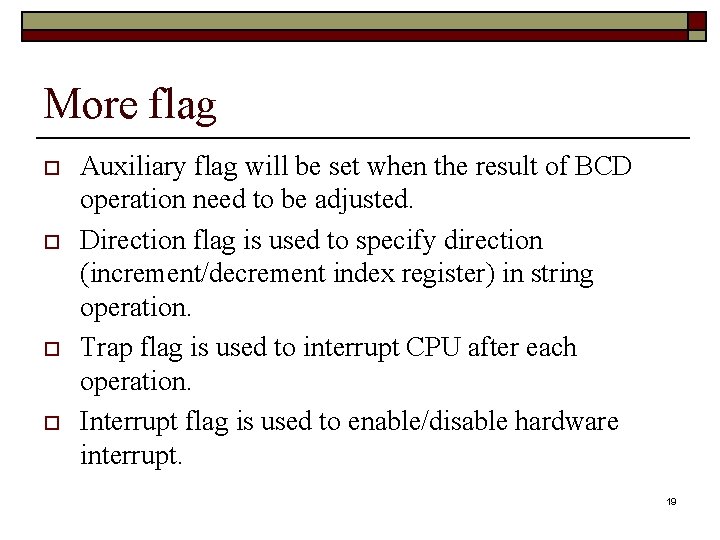

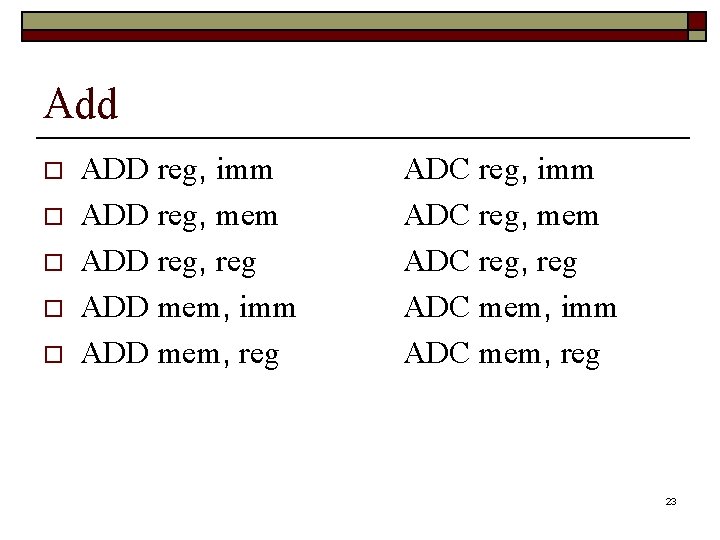

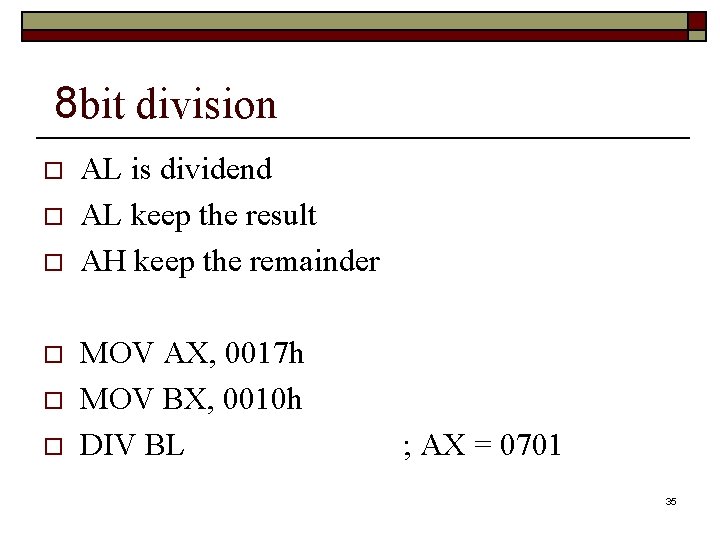

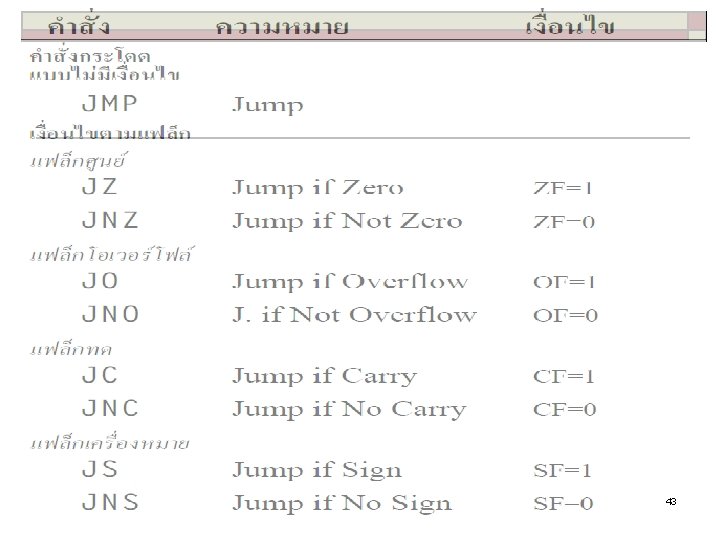

What is the result of… o o MOV [100 h] , 10 h Address 100 = 10 h What about address 101? Word or Byte? n n o MOV WORD PTR [100 h], 10 h MOV BYTE PTR [100 h], 10 h What about MOV [100 h], AX ? 11

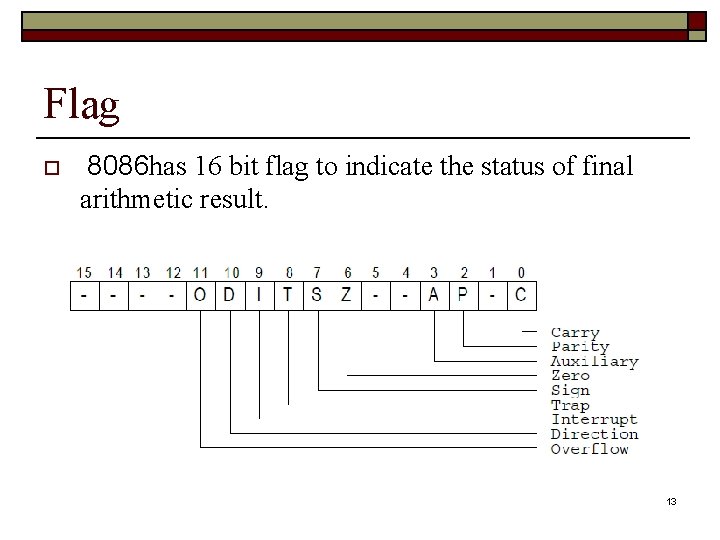

Status Register (Flag( 12

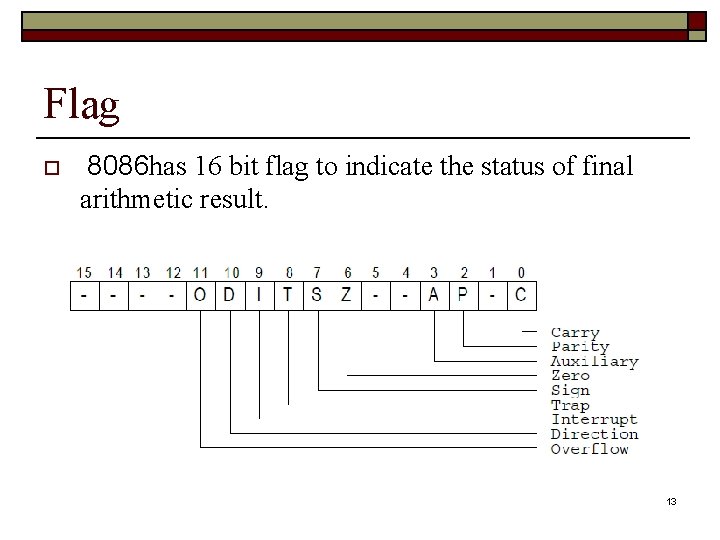

Flag o 8086 has 16 bit flag to indicate the status of final arithmetic result. 13

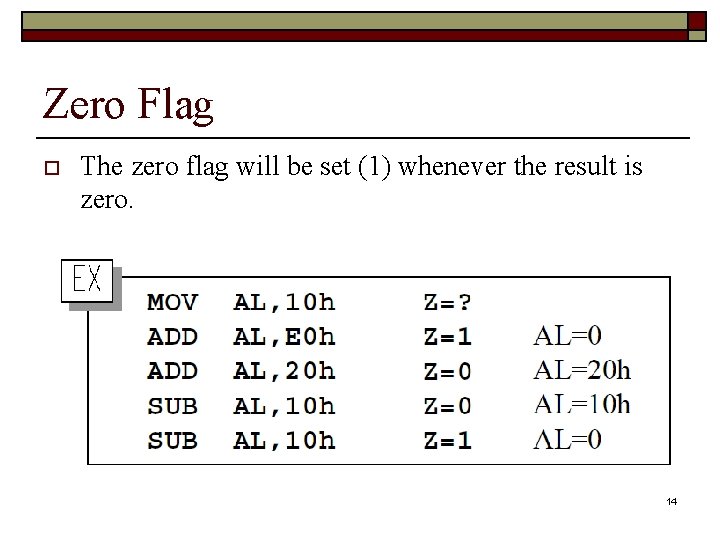

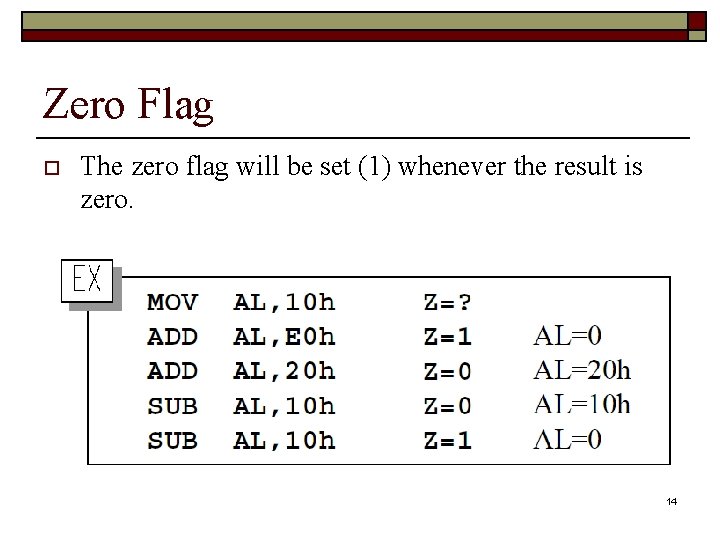

Zero Flag o The zero flag will be set (1) whenever the result is zero. 14

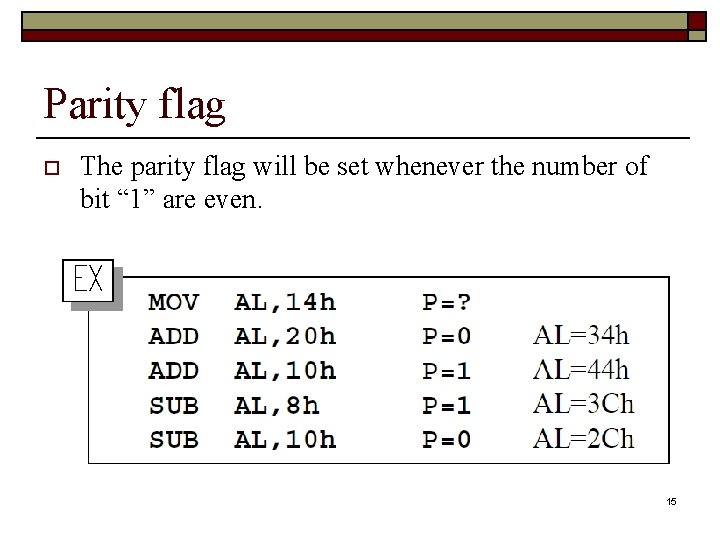

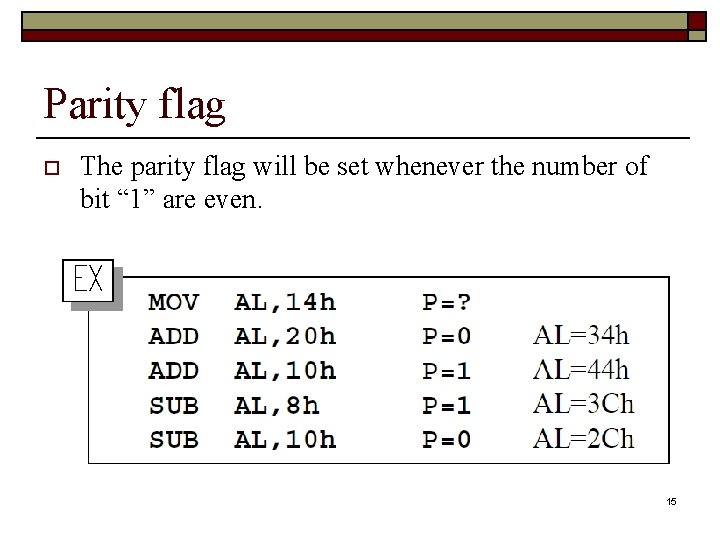

Parity flag o The parity flag will be set whenever the number of bit “ 1” are even. 15

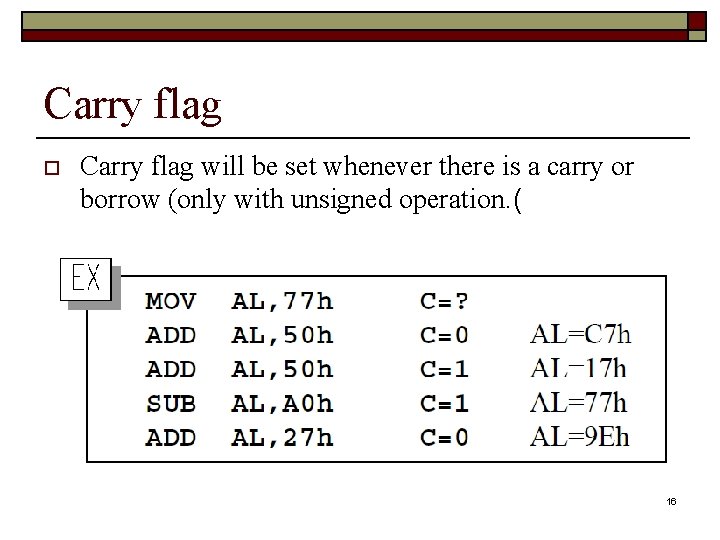

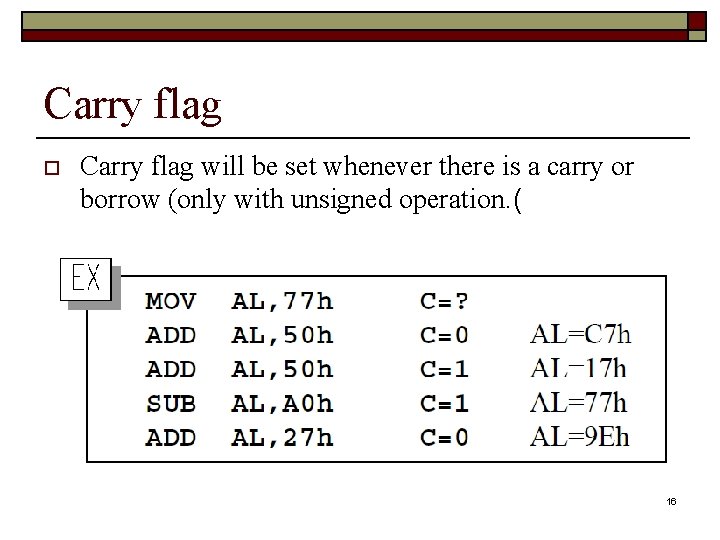

Carry flag o Carry flag will be set whenever there is a carry or borrow (only with unsigned operation. ( 16

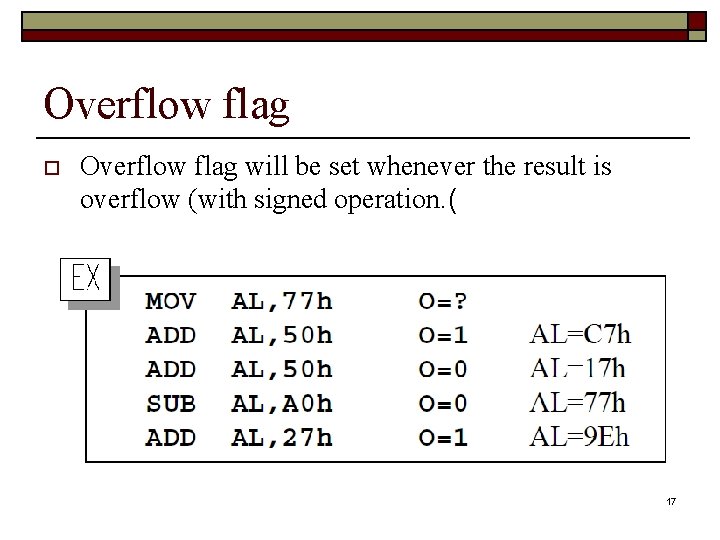

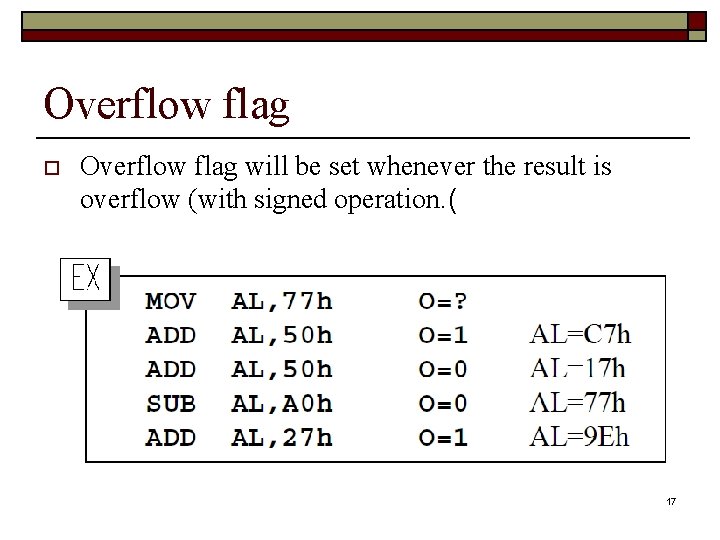

Overflow flag o Overflow flag will be set whenever the result is overflow (with signed operation. ( 17

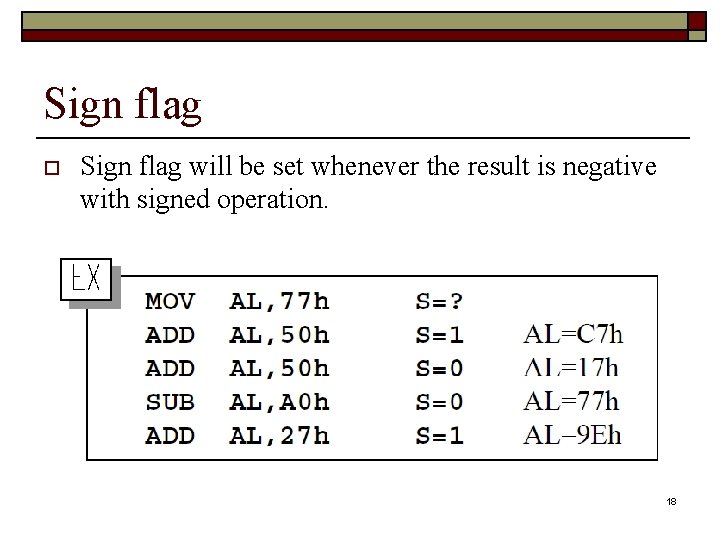

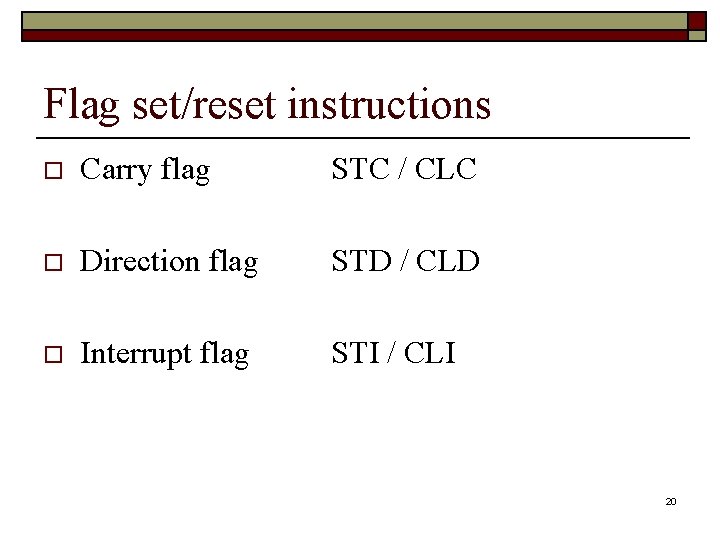

Sign flag o Sign flag will be set whenever the result is negative with signed operation. 18

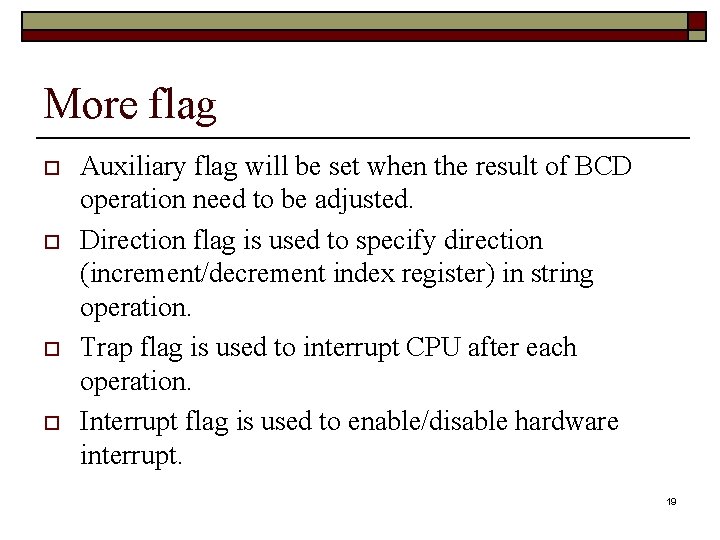

More flag o o Auxiliary flag will be set when the result of BCD operation need to be adjusted. Direction flag is used to specify direction (increment/decrement index register) in string operation. Trap flag is used to interrupt CPU after each operation. Interrupt flag is used to enable/disable hardware interrupt. 19

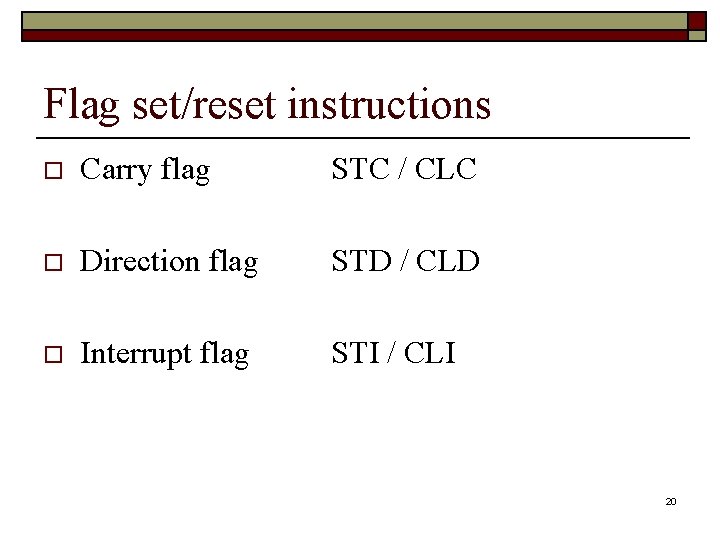

Flag set/reset instructions o Carry flag STC / CLC o Direction flag STD / CLD o Interrupt flag STI / CLI 20

Arithmetic instructions 21

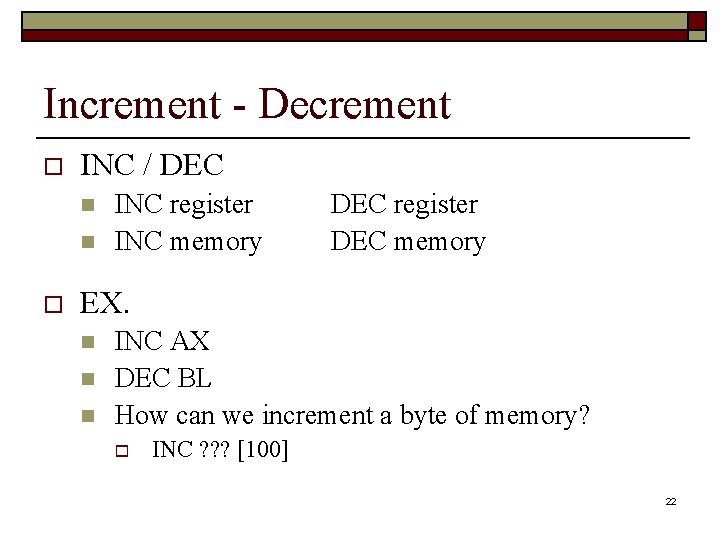

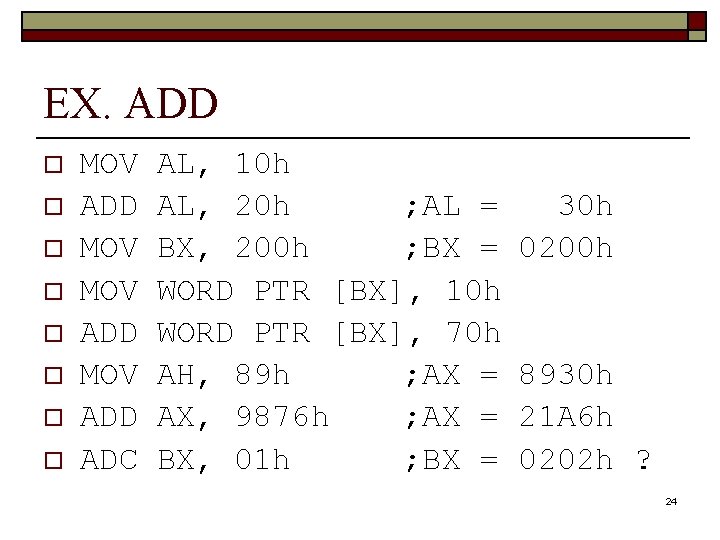

Increment - Decrement o INC / DEC n n o INC register INC memory DEC register DEC memory EX. n n n INC AX DEC BL How can we increment a byte of memory? o INC ? ? ? [100] 22

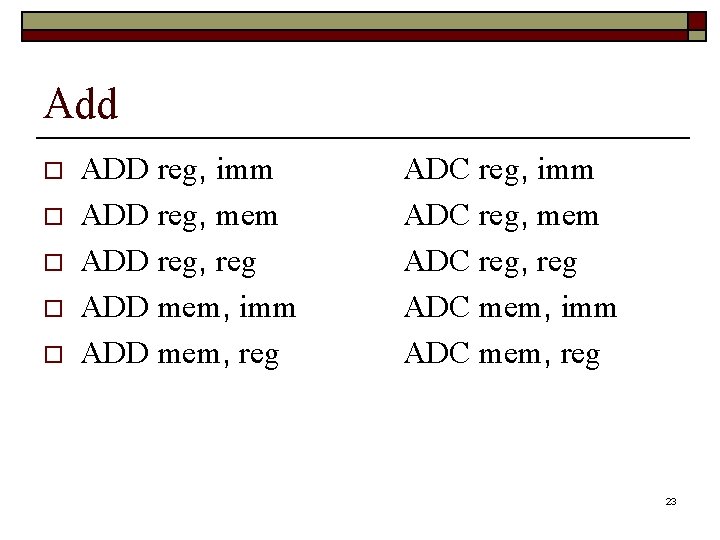

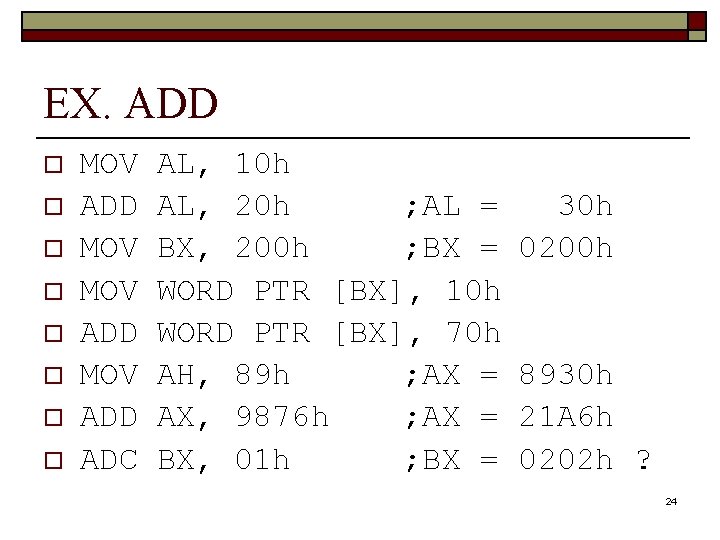

Add o o o ADD reg, imm ADD reg, mem ADD reg, reg ADD mem, imm ADD mem, reg ADC reg, imm ADC reg, mem ADC reg, reg ADC mem, imm ADC mem, reg 23

EX. ADD o o o o MOV ADD ADC AL, 10 h AL, 20 h ; AL = BX, 200 h ; BX = WORD PTR [BX], 10 h WORD PTR [BX], 70 h AH, 89 h ; AX = AX, 9876 h ; AX = BX, 01 h ; BX = 30 h 0200 h 8930 h 21 A 6 h 0202 h ? 24

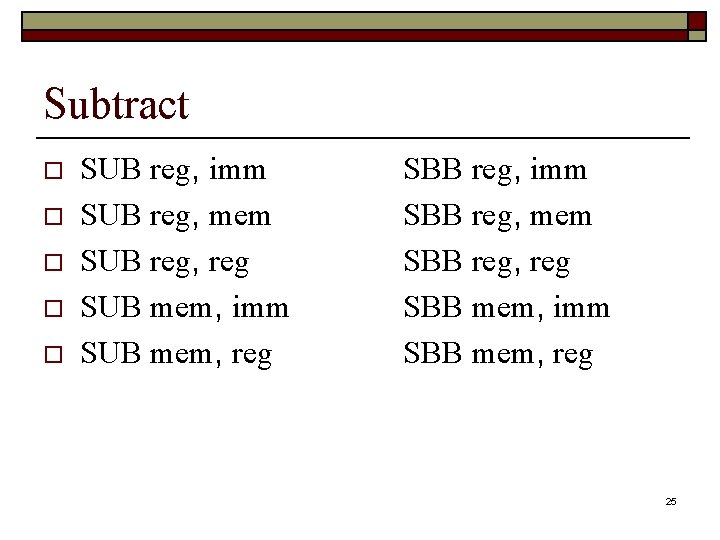

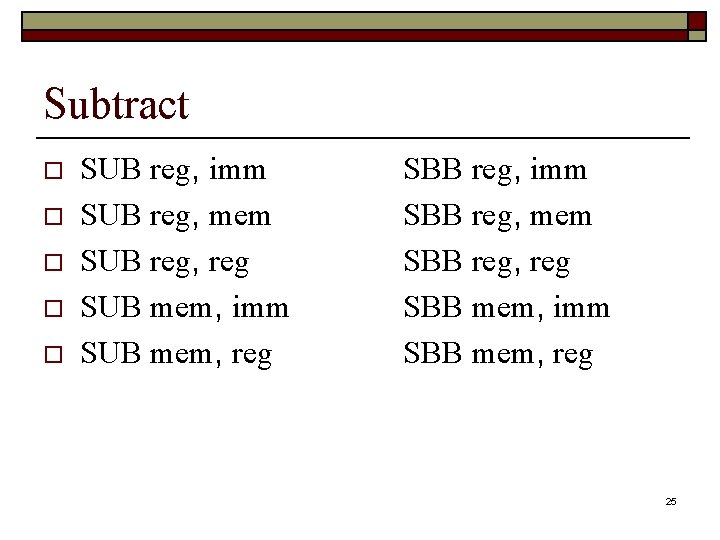

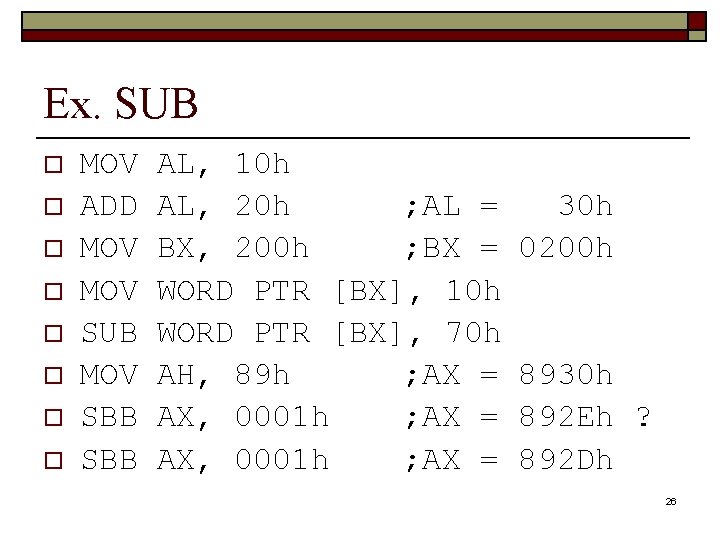

Subtract o o o SUB reg, imm SUB reg, mem SUB reg, reg SUB mem, imm SUB mem, reg SBB reg, imm SBB reg, mem SBB reg, reg SBB mem, imm SBB mem, reg 25

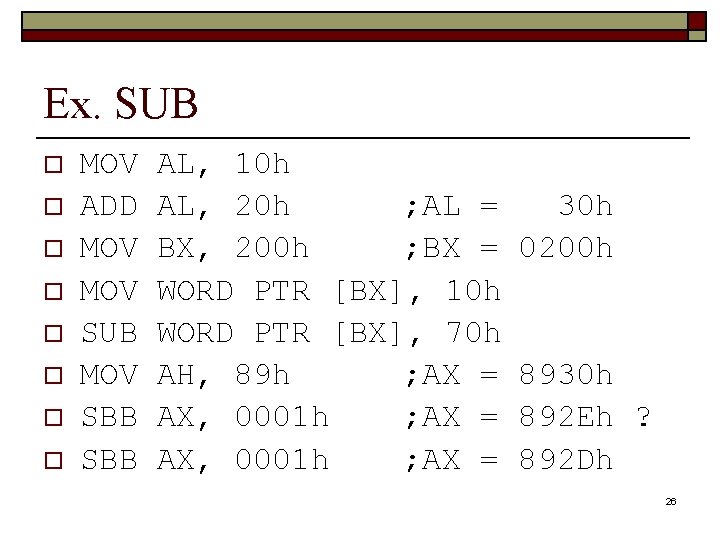

Ex. SUB o o o o MOV ADD MOV SUB MOV SBB AL, 10 h AL, 20 h ; AL = BX, 200 h ; BX = WORD PTR [BX], 10 h WORD PTR [BX], 70 h AH, 89 h ; AX = AX, 0001 h ; AX = 30 h 0200 h 8930 h 892 Eh ? 892 Dh 26

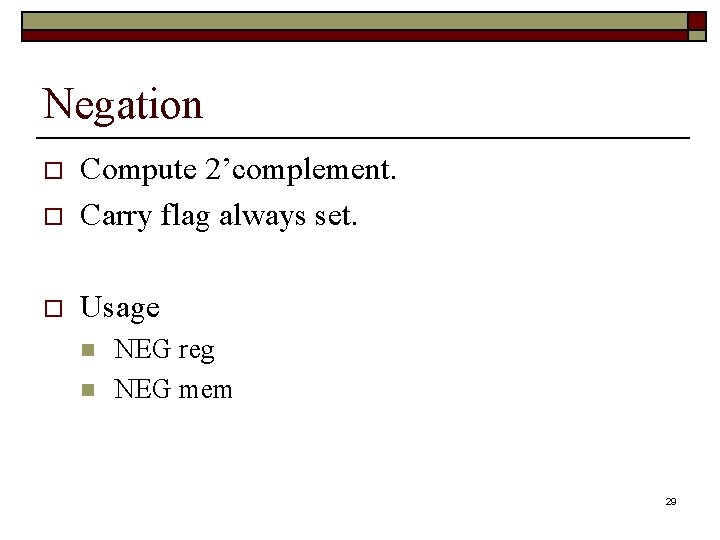

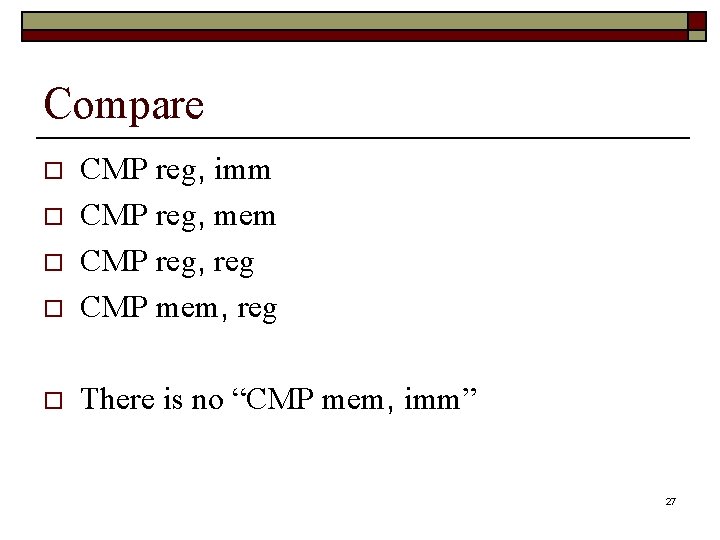

Compare o CMP reg, imm CMP reg, mem CMP reg, reg CMP mem, reg o There is no “CMP mem, imm” o o o 27

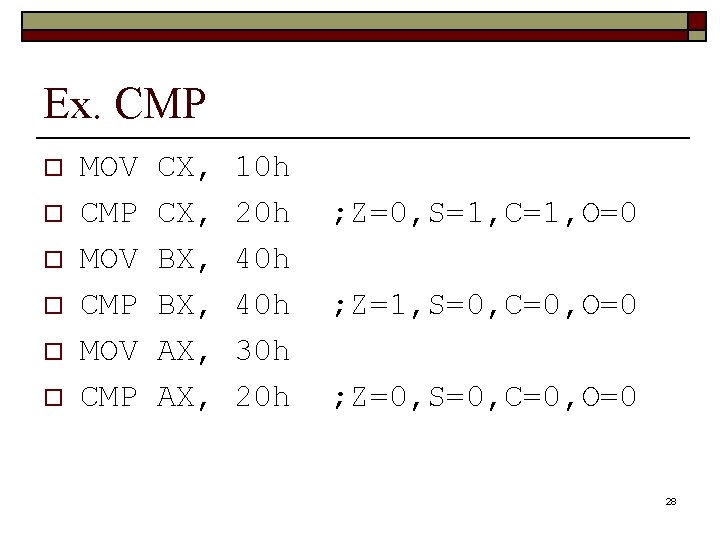

Ex. CMP o o o MOV CMP CX, BX, AX, 10 h 20 h 40 h 30 h 20 h ; Z=0, S=1, C=1, O=0 ; Z=1, S=0, C=0, O=0 ; Z=0, S=0, C=0, O=0 28

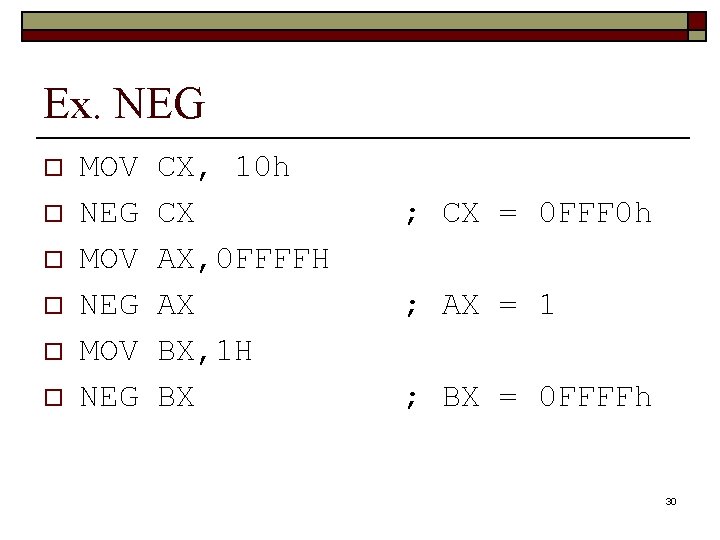

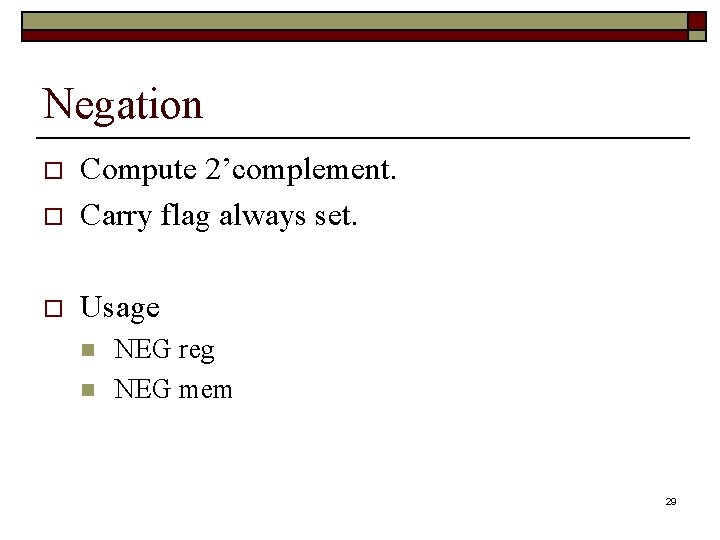

Negation o Compute 2’complement. Carry flag always set. o Usage o n n NEG reg NEG mem 29

Ex. NEG o o o MOV NEG CX, 10 h CX AX, 0 FFFFH AX BX, 1 H BX ; CX = 0 FFF 0 h ; AX = 1 ; BX = 0 FFFFh 30

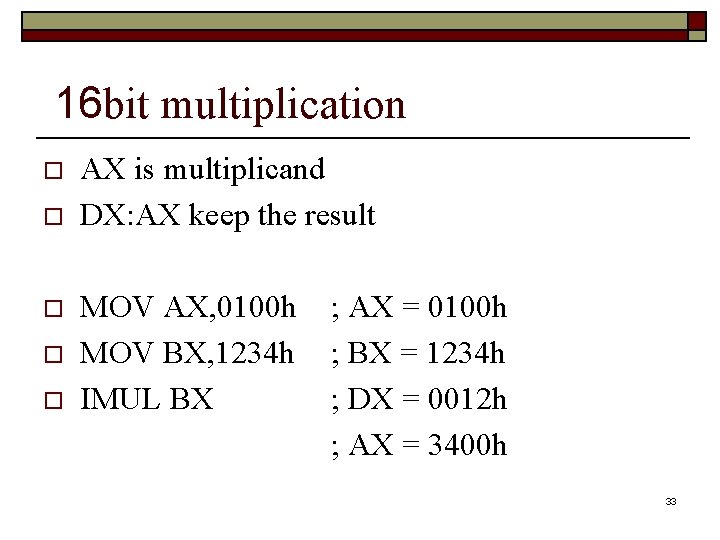

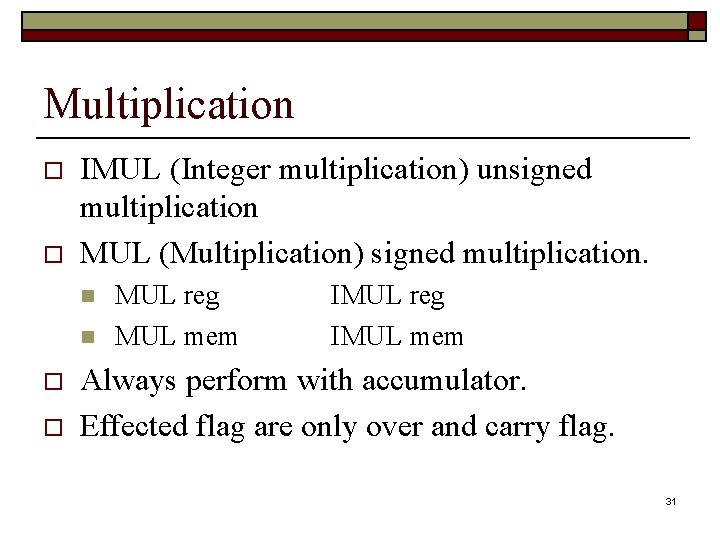

Multiplication o o IMUL (Integer multiplication) unsigned multiplication MUL (Multiplication) signed multiplication. n n o o MUL reg MUL mem IMUL reg IMUL mem Always perform with accumulator. Effected flag are only over and carry flag. 31

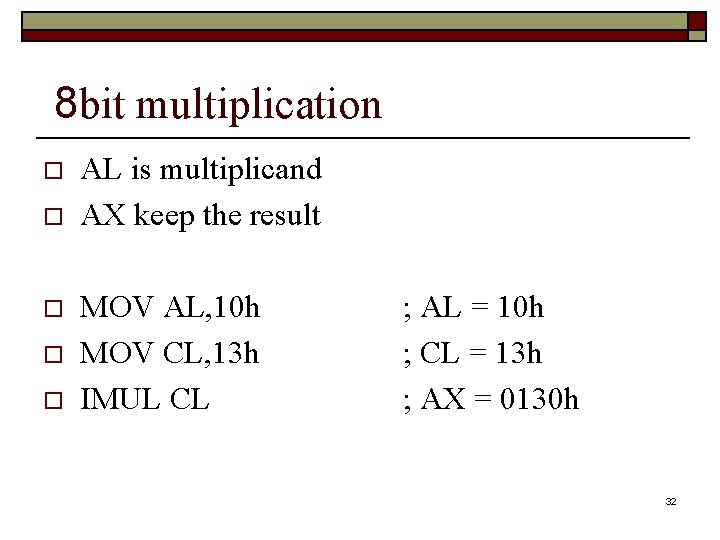

8 bit multiplication o o o AL is multiplicand AX keep the result MOV AL, 10 h MOV CL, 13 h IMUL CL ; AL = 10 h ; CL = 13 h ; AX = 0130 h 32

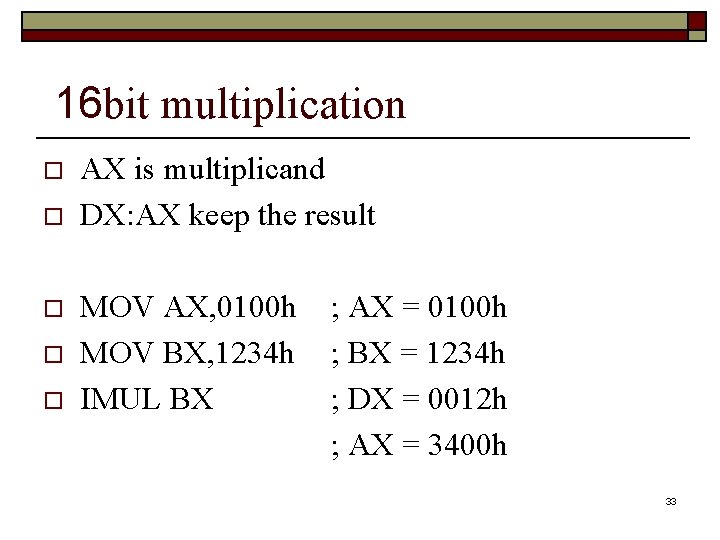

16 bit multiplication o o o AX is multiplicand DX: AX keep the result MOV AX, 0100 h MOV BX, 1234 h IMUL BX ; AX = 0100 h ; BX = 1234 h ; DX = 0012 h ; AX = 3400 h 33

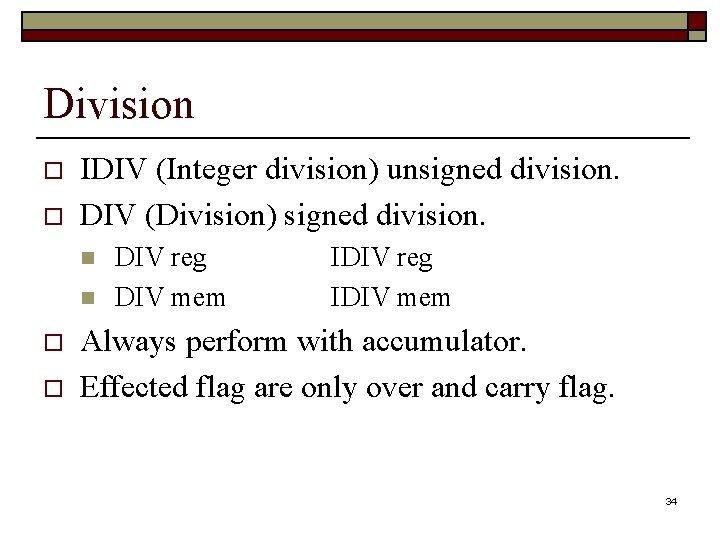

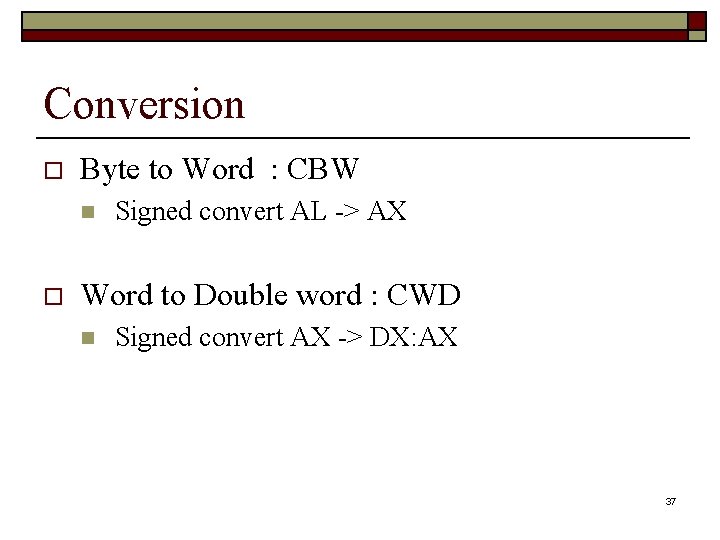

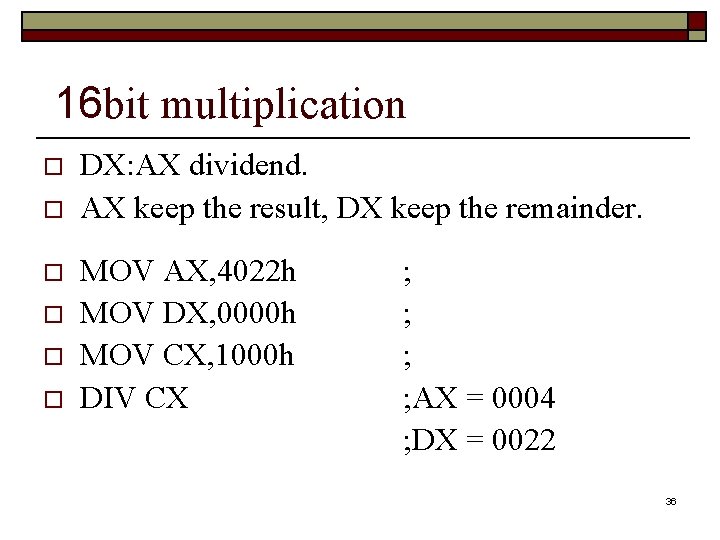

Division o o IDIV (Integer division) unsigned division. DIV (Division) signed division. n n o o DIV reg DIV mem IDIV reg IDIV mem Always perform with accumulator. Effected flag are only over and carry flag. 34

8 bit division o o o AL is dividend AL keep the result AH keep the remainder MOV AX, 0017 h MOV BX, 0010 h DIV BL ; AX = 0701 35

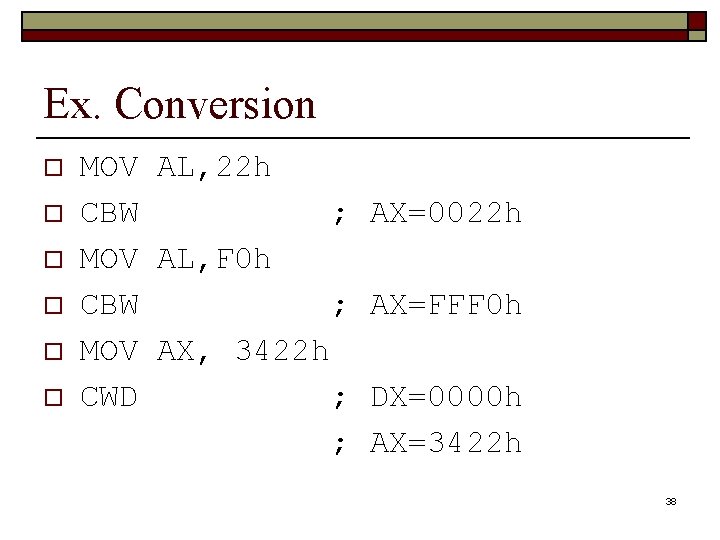

16 bit multiplication o o o DX: AX dividend. AX keep the result, DX keep the remainder. MOV AX, 4022 h MOV DX, 0000 h MOV CX, 1000 h DIV CX ; ; AX = 0004 ; DX = 0022 36

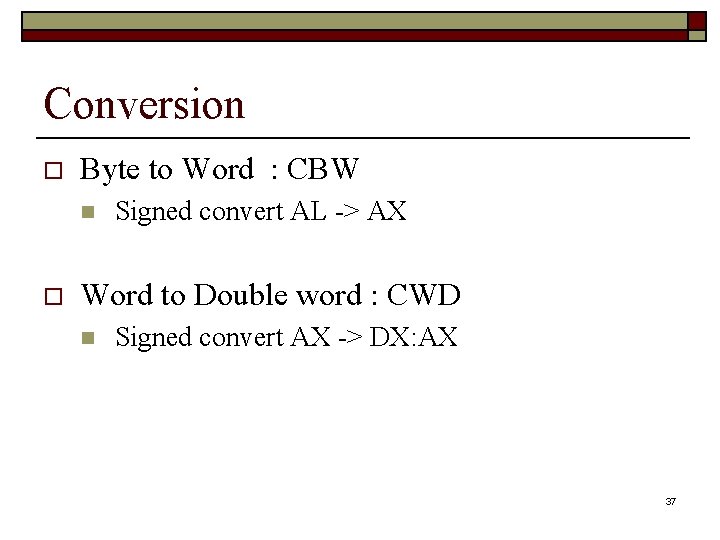

Conversion o Byte to Word : CBW n o Signed convert AL -> AX Word to Double word : CWD n Signed convert AX -> DX: AX 37

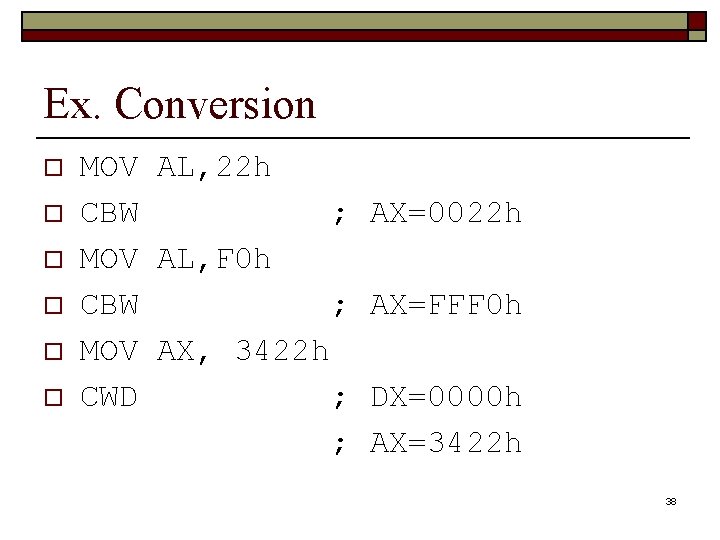

Ex. Conversion o o o MOV AL, 22 h CBW ; MOV AL, F 0 h CBW ; MOV AX, 3422 h CWD ; ; AX=0022 h AX=FFF 0 h DX=0000 h AX=3422 h 38

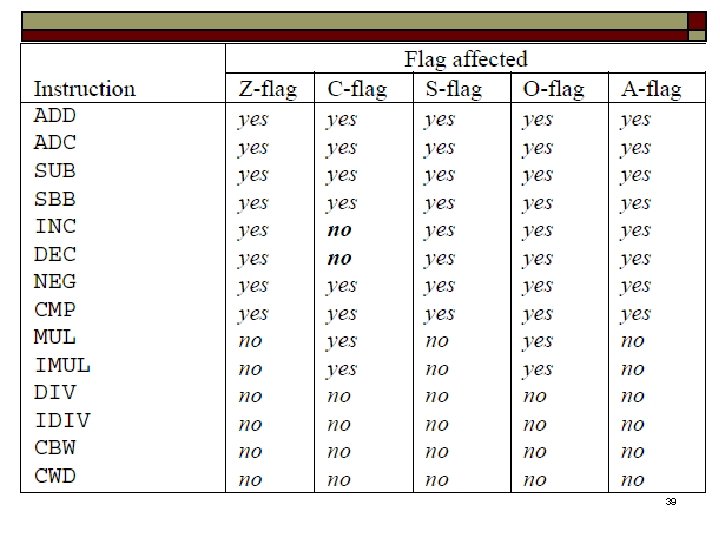

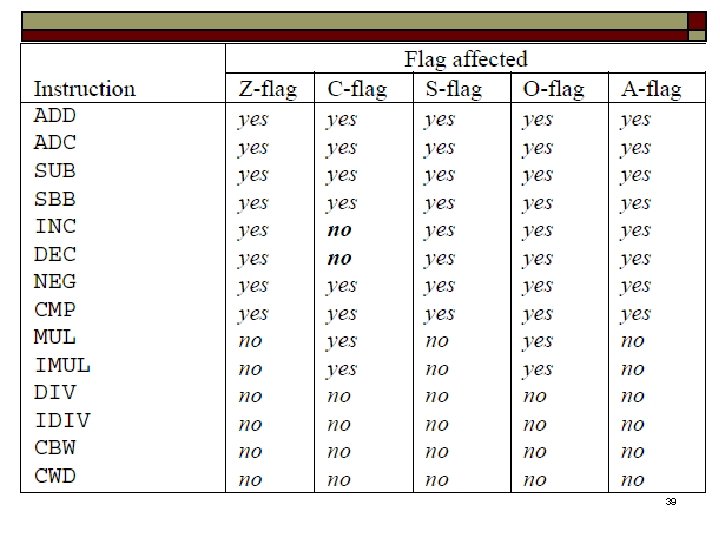

39

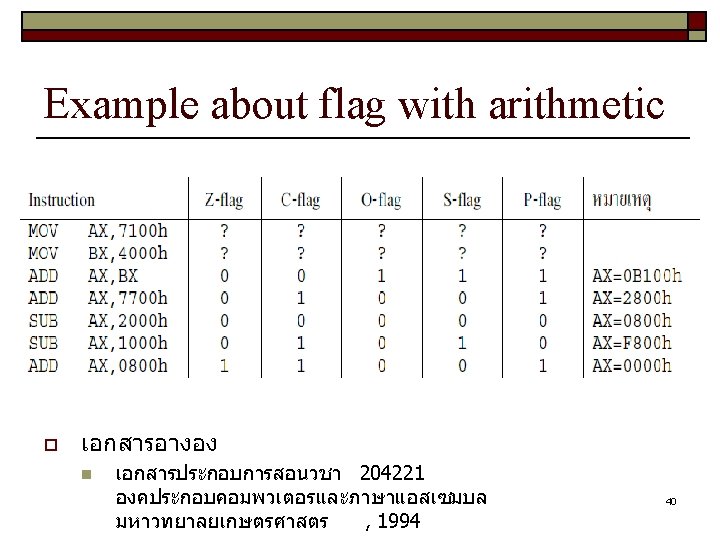

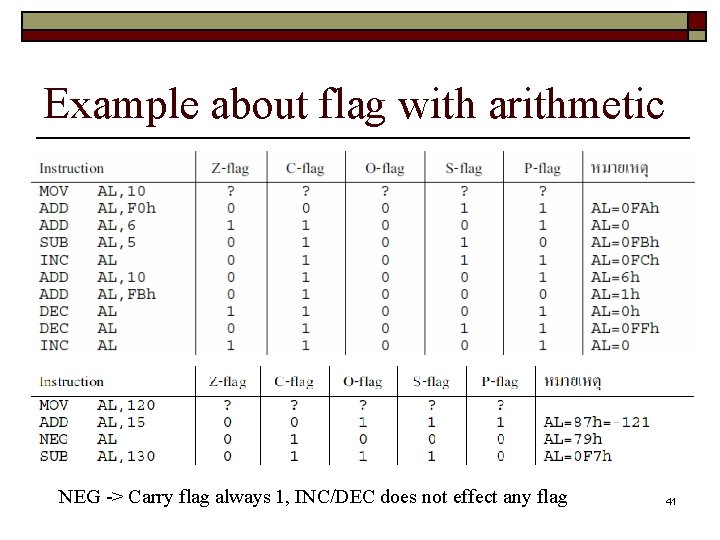

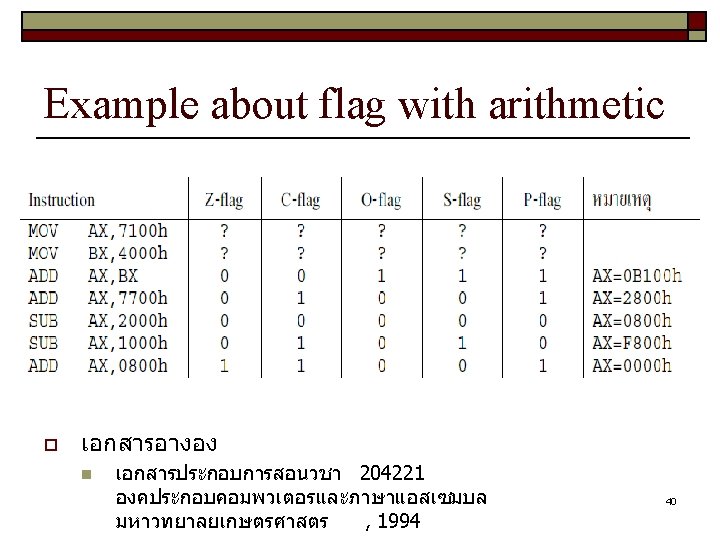

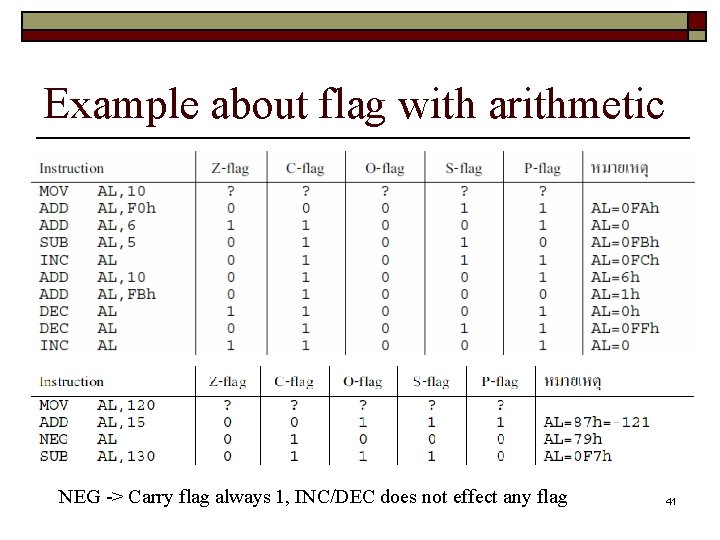

Example about flag with arithmetic NEG -> Carry flag always 1, INC/DEC does not effect any flag 41

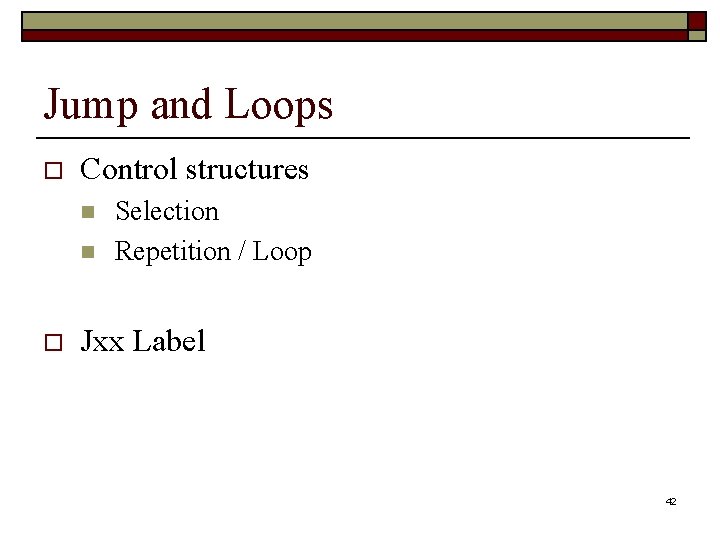

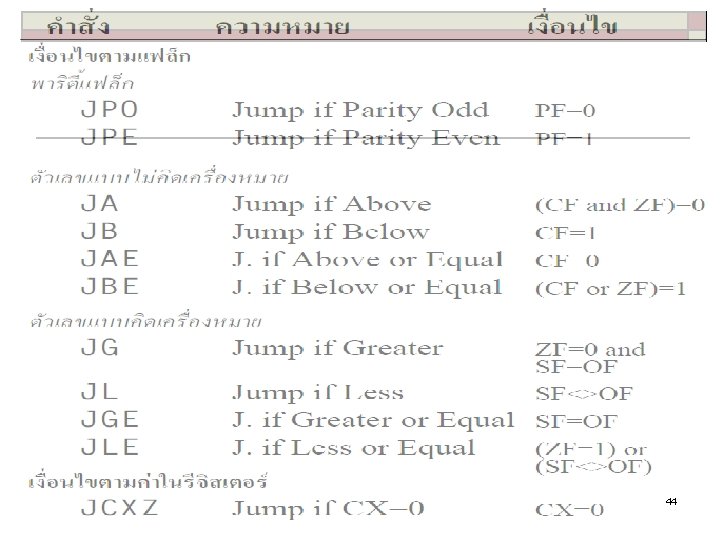

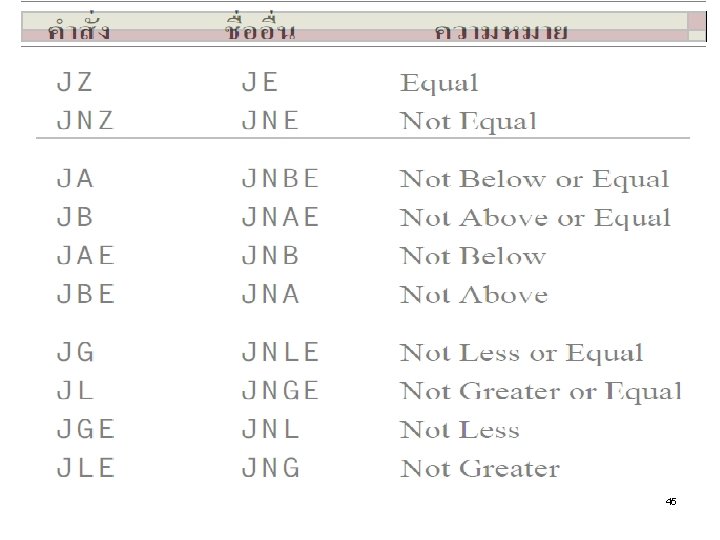

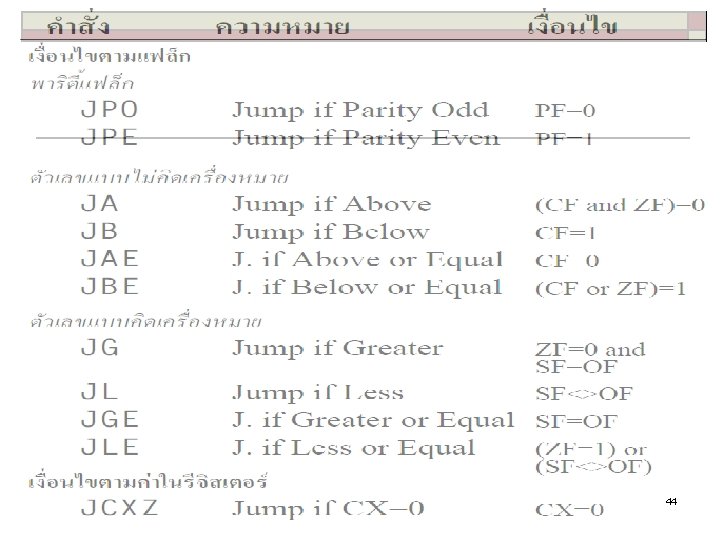

Jump and Loops o Control structures n n o Selection Repetition / Loop Jxx Label 42

43

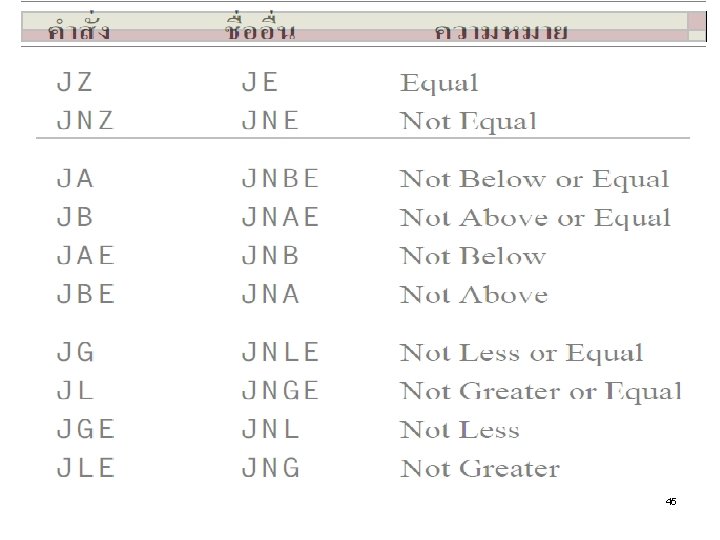

44

45

If ah=10, if ah>=10 46

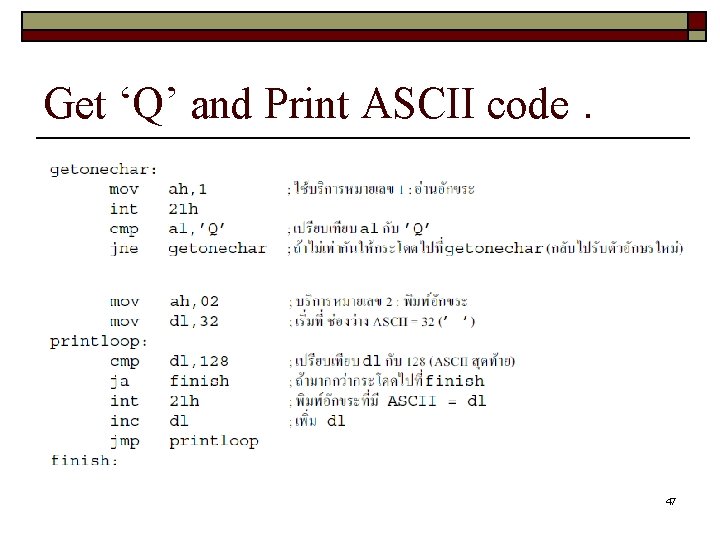

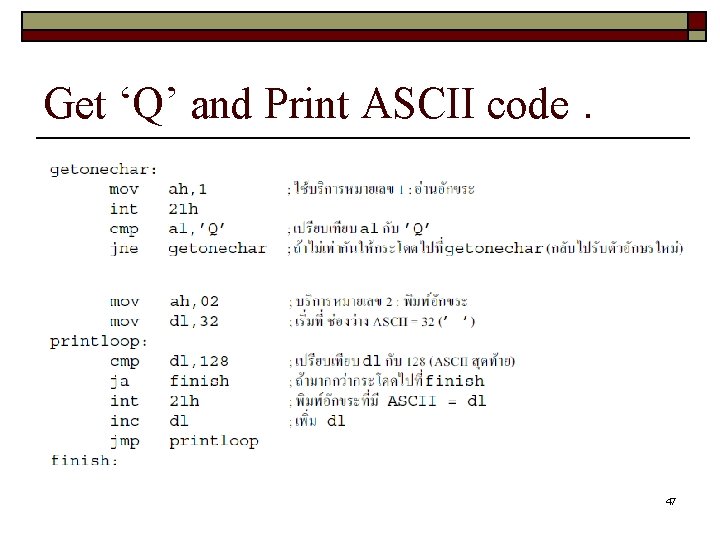

Get ‘Q’ and Print ASCII code. 47

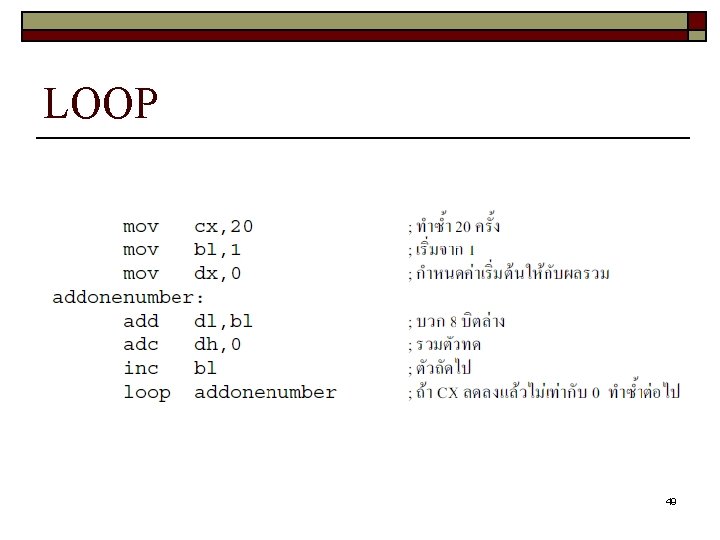

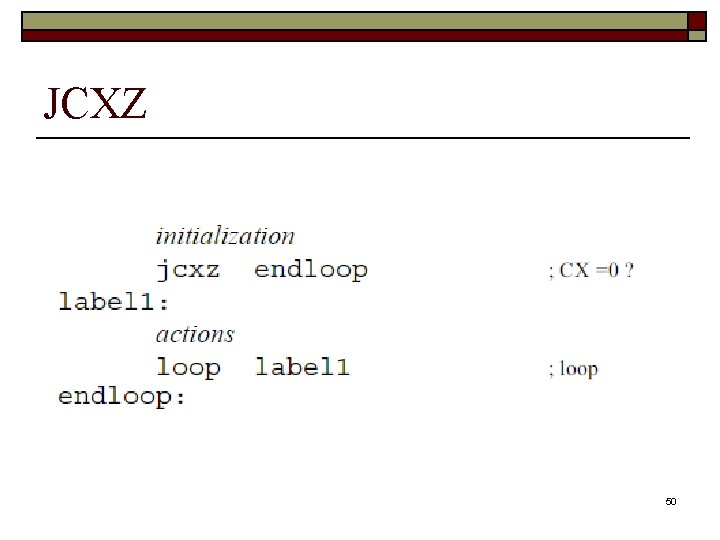

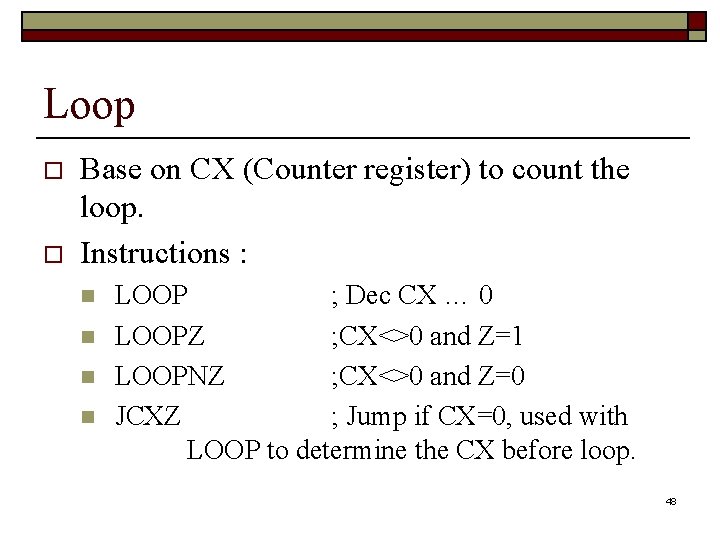

Loop o o Base on CX (Counter register) to count the loop. Instructions : n n LOOP ; Dec CX … 0 LOOPZ ; CX<>0 and Z=1 LOOPNZ ; CX<>0 and Z=0 JCXZ ; Jump if CX=0, used with LOOP to determine the CX before loop. 48

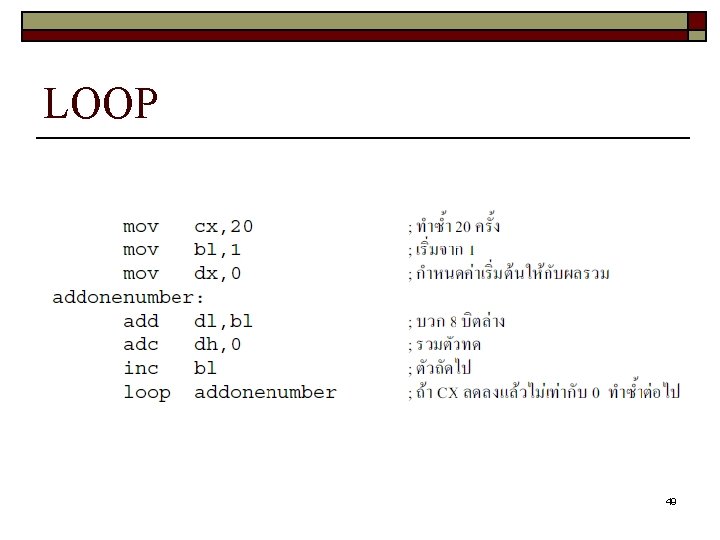

LOOP 49

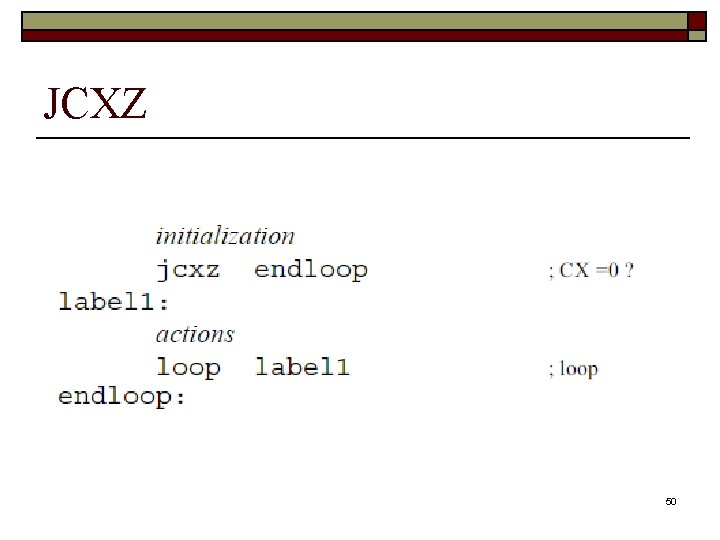

JCXZ 50

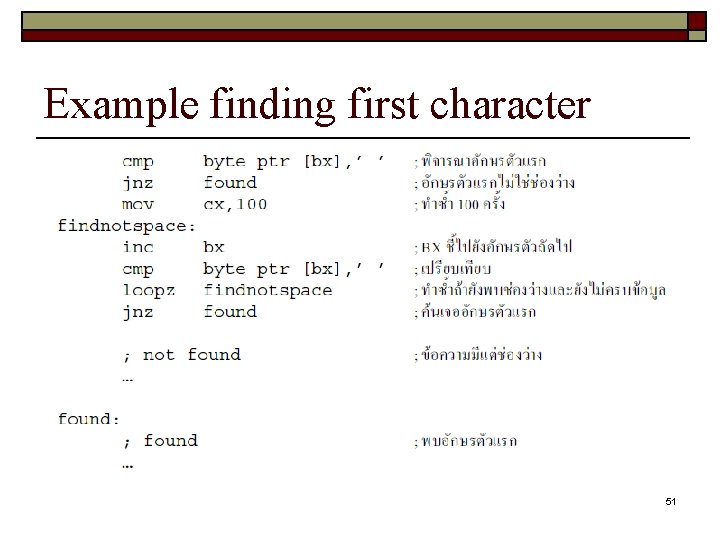

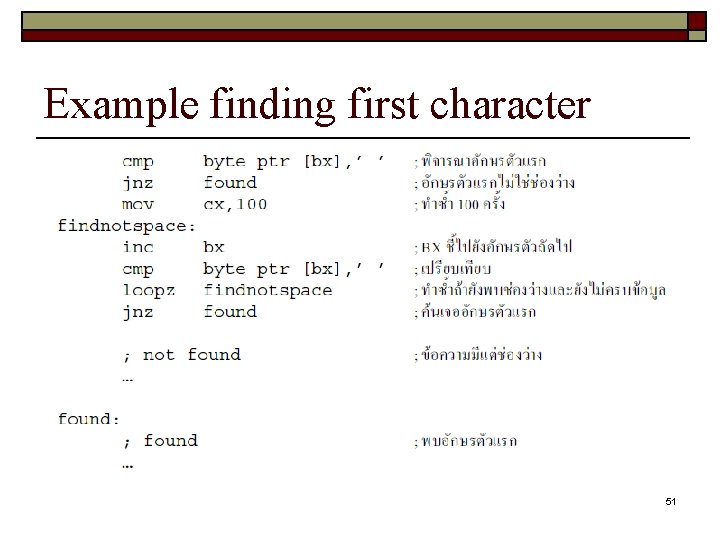

Example finding first character 51

That’s all. 52