AVR CPU Core 8 bit AVR Instruction Set

AVR CPU Core & 8 bit AVR Instruction Set

안철수 KAIST 석좌교수 "개발자가 성공하는 길" 개발자가 성공하는 길 http: //www. devmento. co. kr/devmain/ucc/ucc_detail. j sp? cate_code=ADAFAA&data. Seq=76&main_id=SUCC 1 W 001 incoming Lab.

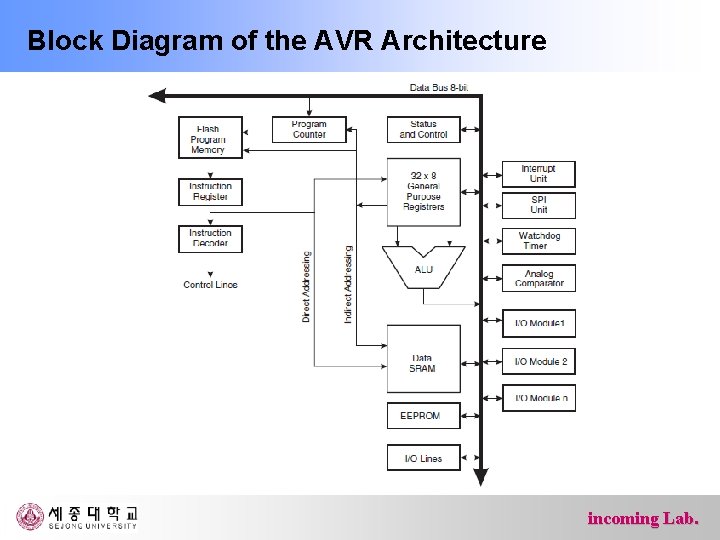

Block Diagram of the AVR Architecture incoming Lab.

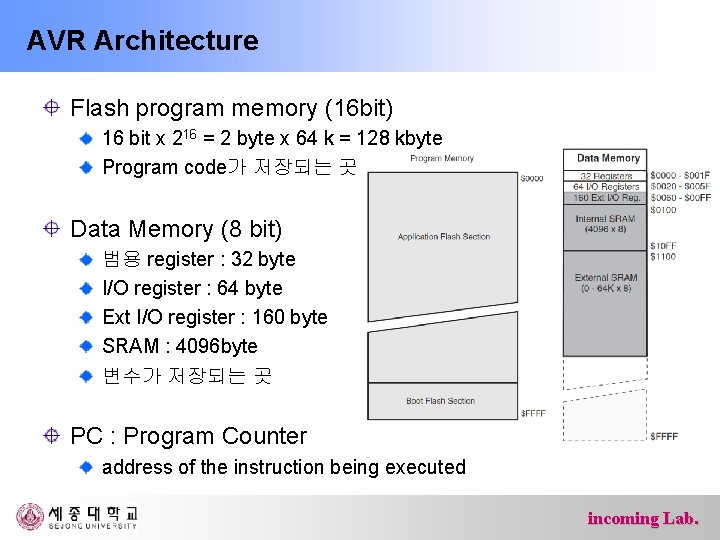

AVR Architecture Flash program memory (16 bit) 16 bit x 216 = 2 byte x 64 k = 128 kbyte Program code가 저장되는 곳 Data Memory (8 bit) 범용 register : 32 byte I/O register : 64 byte Ext I/O register : 160 byte SRAM : 4096 byte 변수가 저장되는 곳 PC : Program Counter address of the instruction being executed incoming Lab.

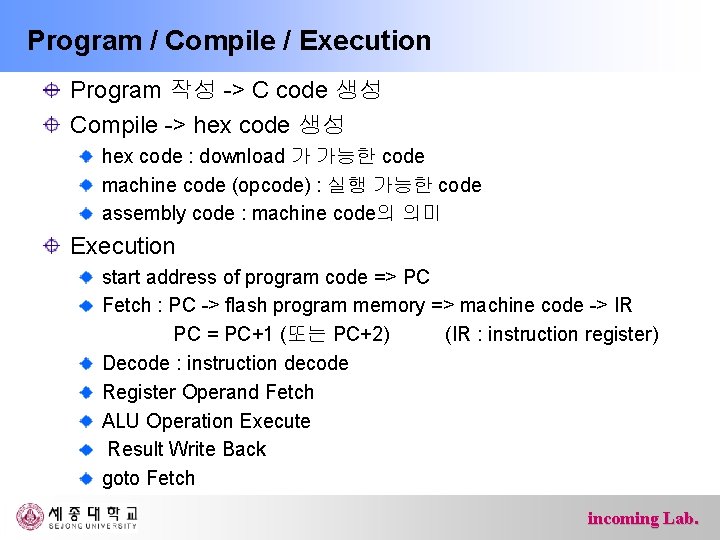

Program / Compile / Execution Program 작성 -> C code 생성 Compile -> hex code 생성 hex code : download 가 가능한 code machine code (opcode) : 실행 가능한 code assembly code : machine code의 의미 Execution start address of program code => PC Fetch : PC -> flash program memory => machine code -> IR PC = PC+1 (또는 PC+2) (IR : instruction register) Decode : instruction decode Register Operand Fetch ALU Operation Execute Result Write Back goto Fetch incoming Lab.

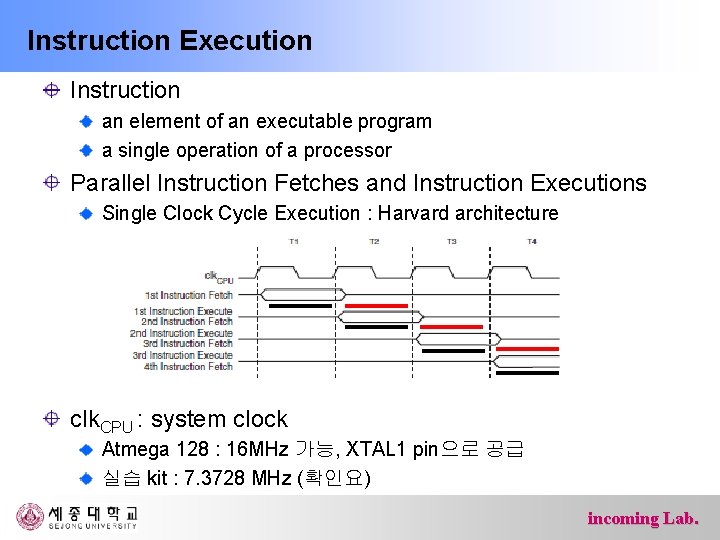

Instruction Execution Instruction an element of an executable program a single operation of a processor Parallel Instruction Fetches and Instruction Executions Single Clock Cycle Execution : Harvard architecture clk. CPU : system clock Atmega 128 : 16 MHz 가능, XTAL 1 pin으로 공급 실습 kit : 7. 3728 MHz (확인요) incoming Lab.

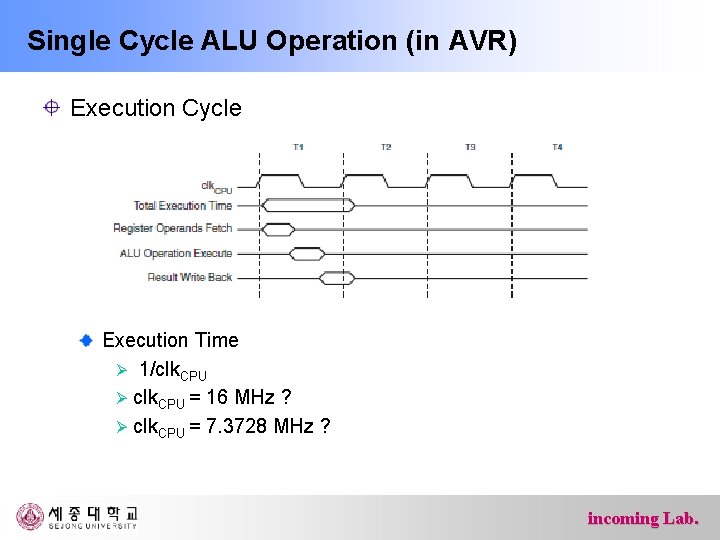

Single Cycle ALU Operation (in AVR) Execution Cycle Execution Time Ø 1/clk. CPU Ø clk. CPU = 16 MHz ? Ø clk. CPU = 7. 3728 MHz ? incoming Lab.

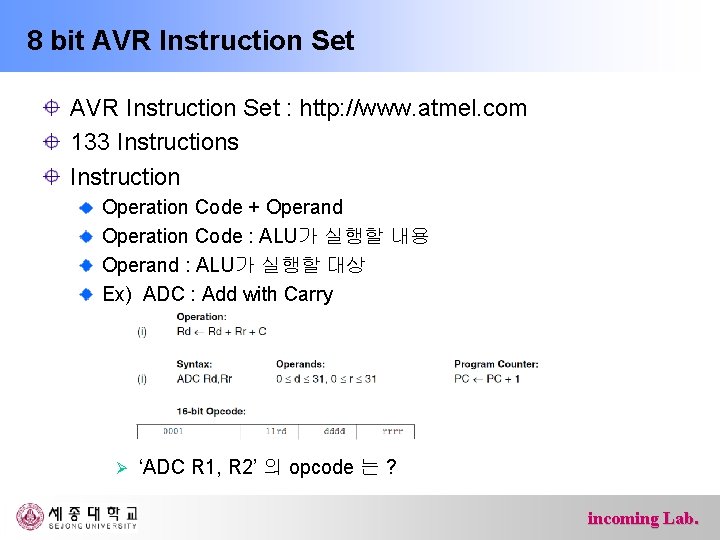

8 bit AVR Instruction Set : http: //www. atmel. com 133 Instructions Instruction Operation Code + Operand Operation Code : ALU가 실행할 내용 Operand : ALU가 실행할 대상 Ex) ADC : Add with Carry Ø ‘ADC R 1, R 2’ 의 opcode 는 ? incoming Lab.

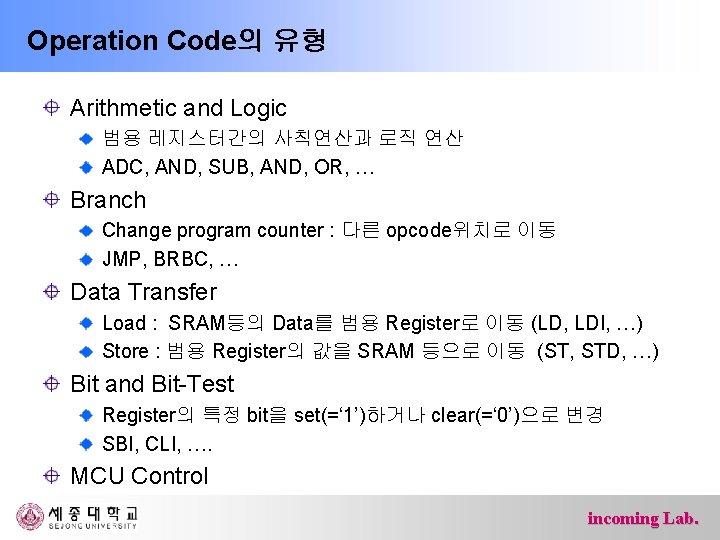

Operation Code의 유형 Arithmetic and Logic 범용 레지스터간의 사칙연산과 로직 연산 ADC, AND, SUB, AND, OR, … Branch Change program counter : 다른 opcode위치로 이동 JMP, BRBC, … Data Transfer Load : SRAM등의 Data를 범용 Register로 이동 (LD, LDI, …) Store : 범용 Register의 값을 SRAM 등으로 이동 (ST, STD, …) Bit and Bit-Test Register의 특정 bit을 set(=‘ 1’)하거나 clear(=‘ 0’)으로 변경 SBI, CLI, …. MCU Control incoming Lab.

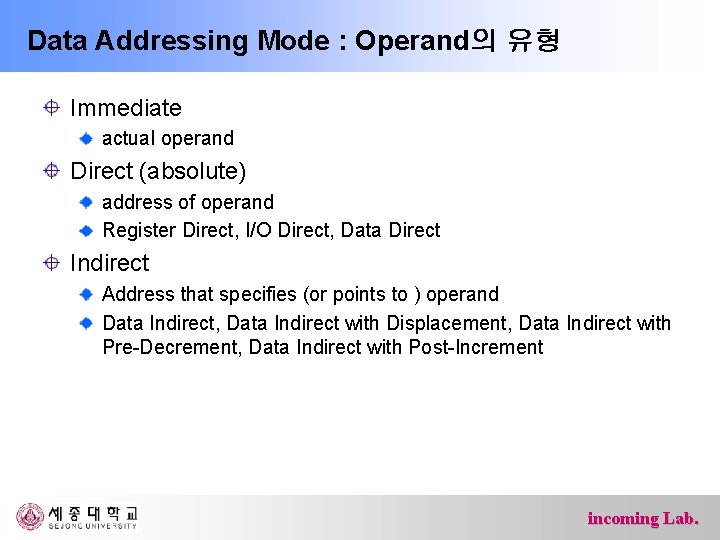

Data Addressing Mode : Operand의 유형 Immediate actual operand Direct (absolute) address of operand Register Direct, I/O Direct, Data Direct Indirect Address that specifies (or points to ) operand Data Indirect, Data Indirect with Displacement, Data Indirect with Pre-Decrement, Data Indirect with Post-Increment incoming Lab.

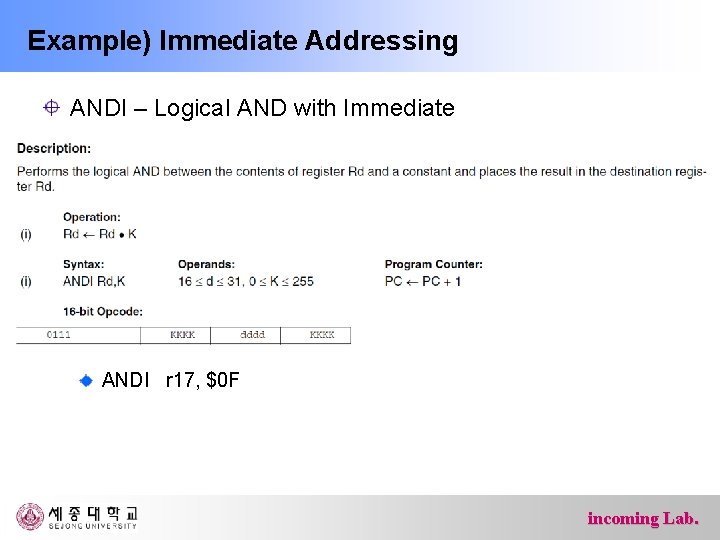

Example) Immediate Addressing ANDI – Logical AND with Immediate ANDI r 17, $0 F incoming Lab.

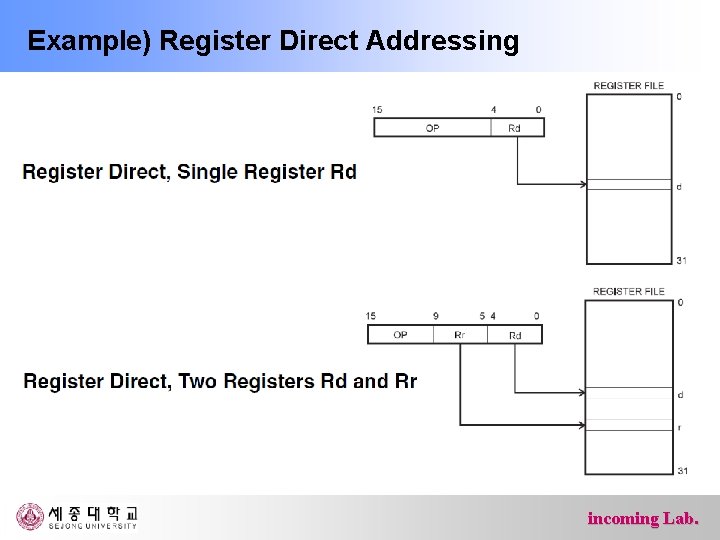

Example) Register Direct Addressing incoming Lab.

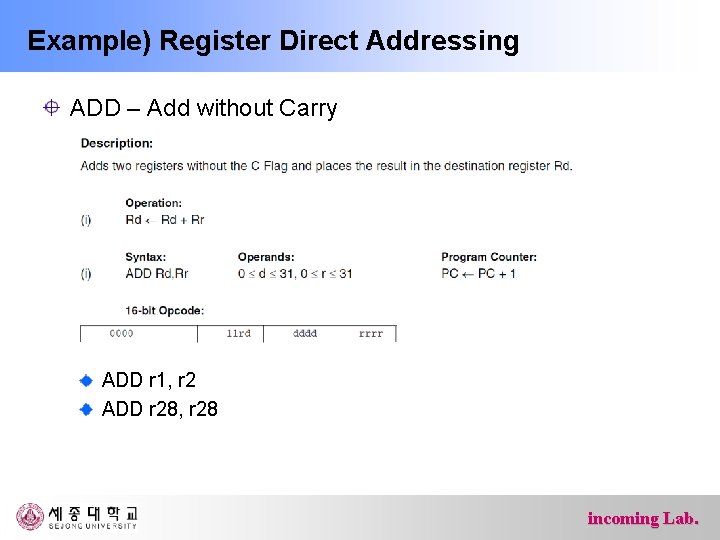

Example) Register Direct Addressing ADD – Add without Carry ADD r 1, r 2 ADD r 28, r 28 incoming Lab.

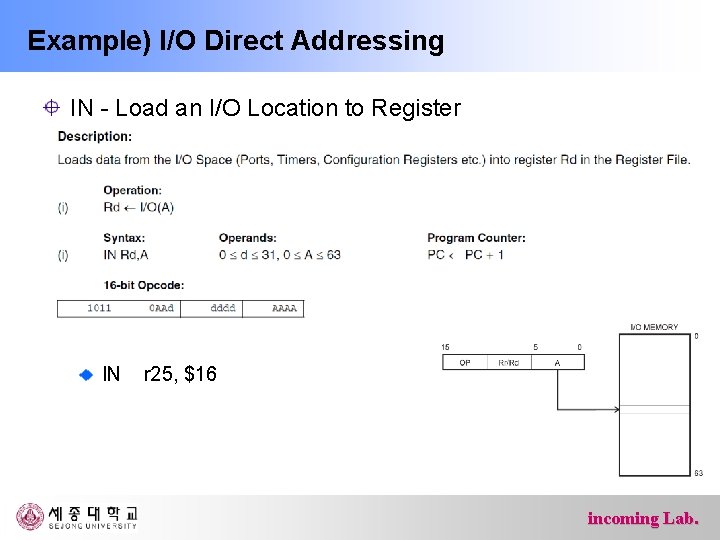

Example) I/O Direct Addressing IN - Load an I/O Location to Register IN r 25, $16 incoming Lab.

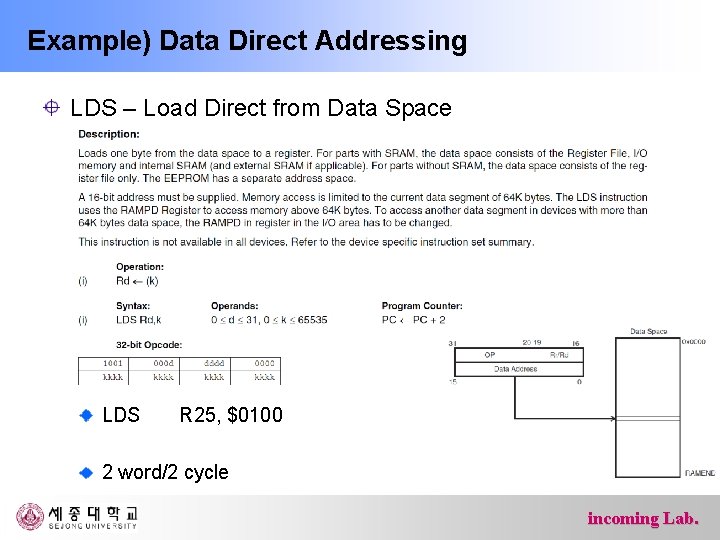

Example) Data Direct Addressing LDS – Load Direct from Data Space LDS R 25, $0100 2 word/2 cycle incoming Lab.

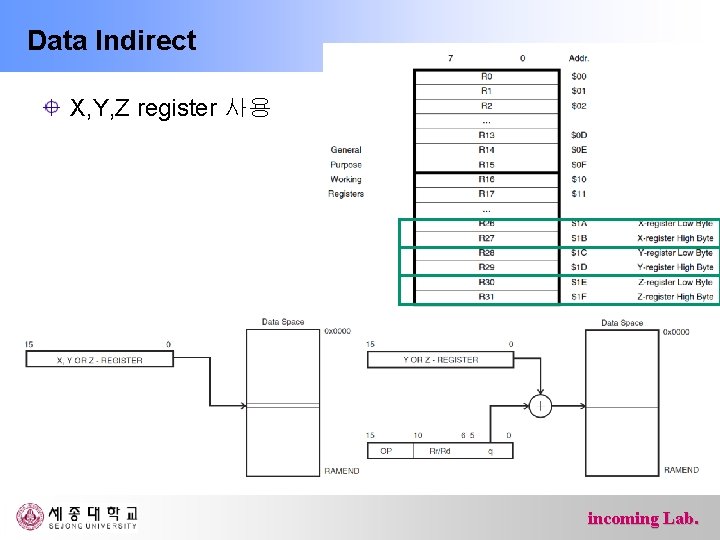

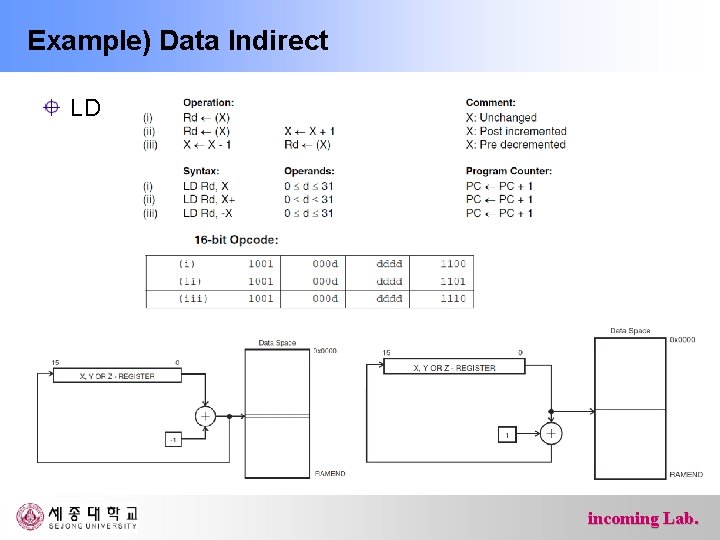

Data Indirect X, Y, Z register 사용 incoming Lab.

Example) Data Indirect LD incoming Lab.

Example) Data Indirect CLR R 27 LDI R 26, $60 LD R 0, X+ LD R 1, X LDI R 26, $63 LD R 2, X LD R 3, –X incoming Lab.

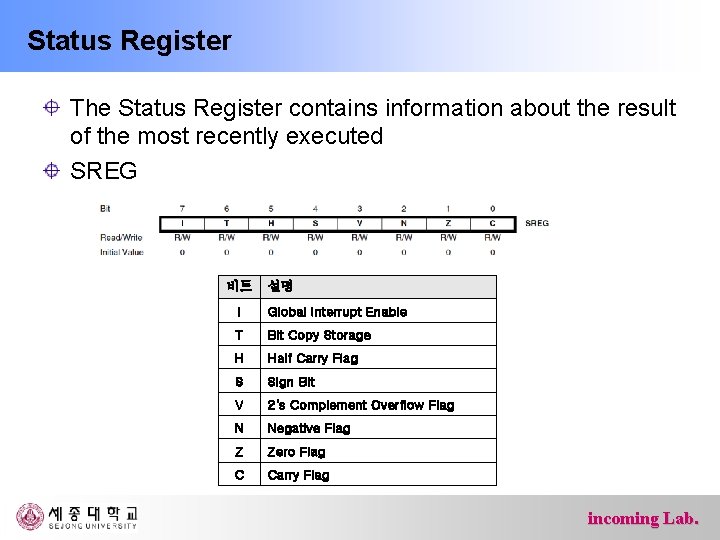

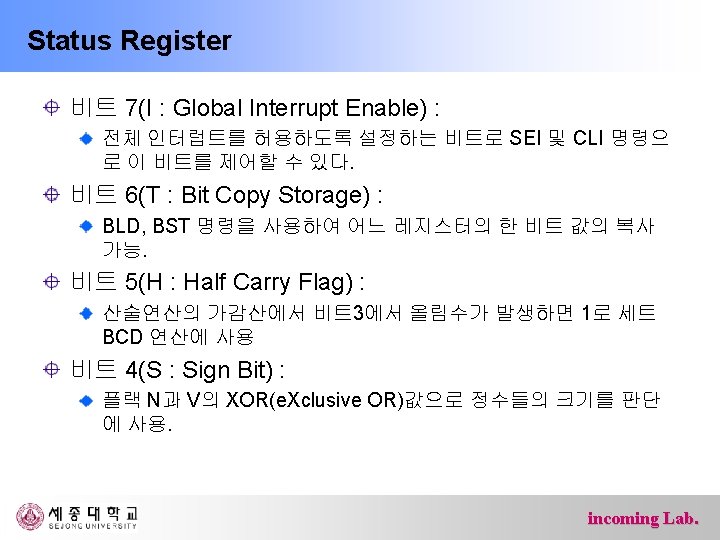

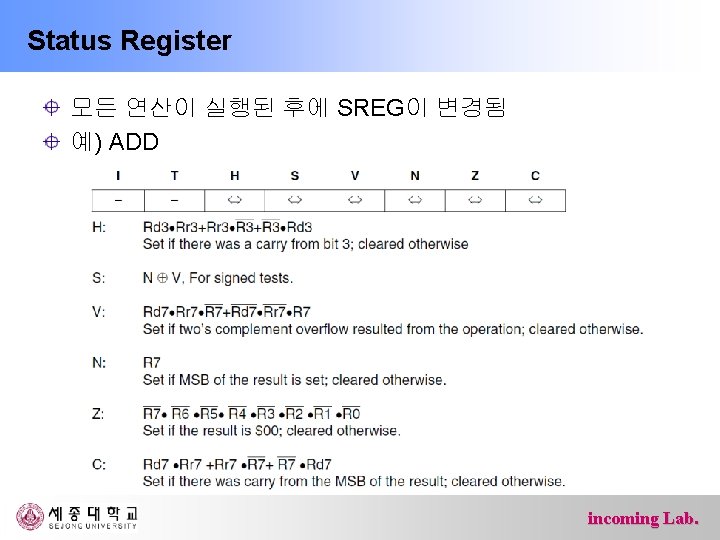

Status Register The Status Register contains information about the result of the most recently executed SREG 비트 설명 I Global Interrupt Enable T Bit Copy Storage H Half Carry Flag S Sign Bit V 2's Complement Overflow Flag N Negative Flag Z Zero Flag C Carry Flag incoming Lab.

Status Register 모든 연산이 실행된 후에 SREG이 변경됨 예) ADD incoming Lab.

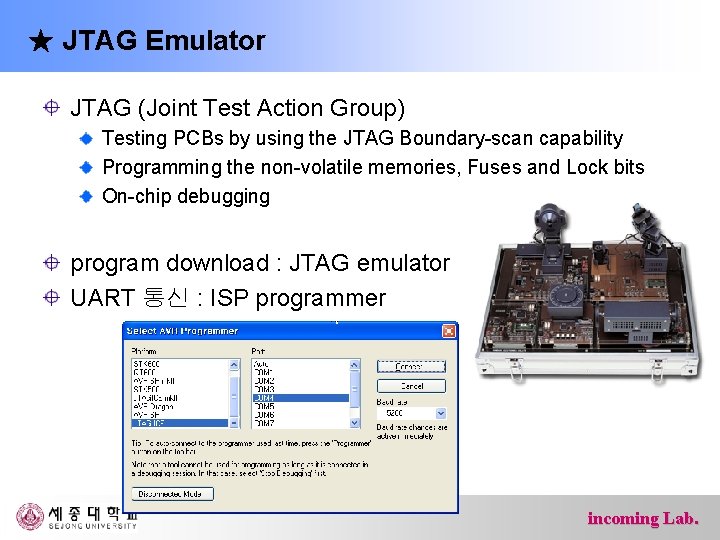

★ JTAG Emulator JTAG (Joint Test Action Group) Testing PCBs by using the JTAG Boundary-scan capability Programming the non-volatile memories, Fuses and Lock bits On-chip debugging program download : JTAG emulator UART 통신 : ISP programmer incoming Lab.

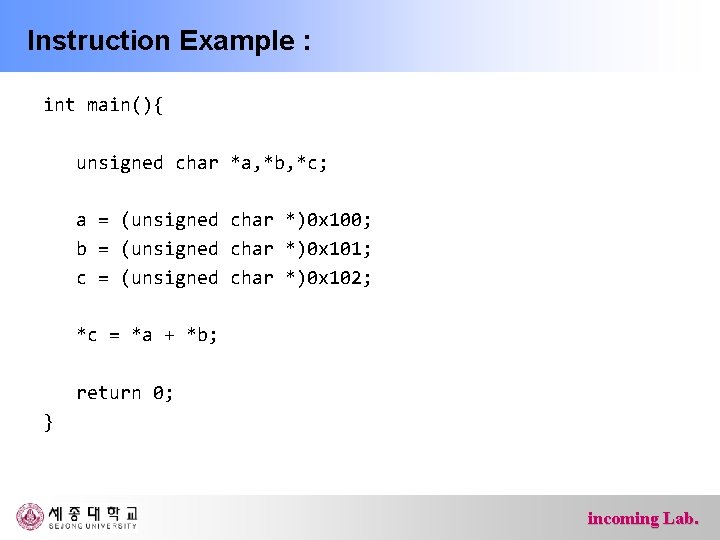

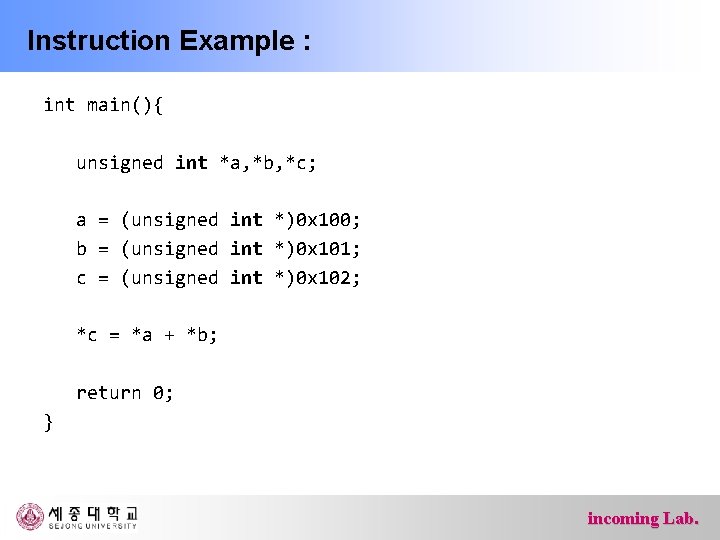

Instruction Example : int main(){ unsigned char *a, *b, *c; a = (unsigned char *)0 x 100; b = (unsigned char *)0 x 101; c = (unsigned char *)0 x 102; *c = *a + *b; return 0; } incoming Lab.

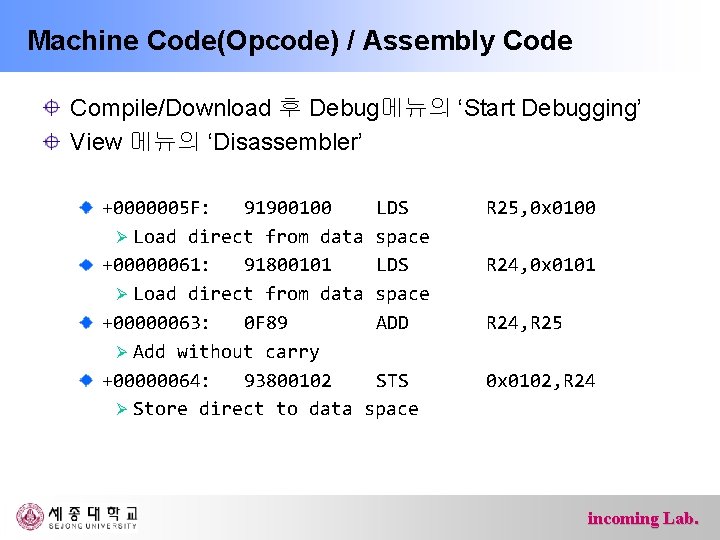

Machine Code(Opcode) / Assembly Code Compile/Download 후 Debug메뉴의 ‘Start Debugging’ View 메뉴의 ‘Disassembler’ +0000005 F: 91900100 LDS Ø Load direct from data space +00000061: 91800101 LDS Ø Load direct from data space +00000063: 0 F 89 ADD Ø Add without carry +00000064: 93800102 STS Ø Store direct to data space R 25, 0 x 0100 R 24, 0 x 0101 R 24, R 25 0 x 0102, R 24 incoming Lab.

Instruction Example : int main(){ unsigned int *a, *b, *c; a = (unsigned int *)0 x 100; b = (unsigned int *)0 x 101; c = (unsigned int *)0 x 102; *c = *a + *b; return 0; } incoming Lab.

Machine Code(Opcode) / Assembly Code Program address Opcode Assembly Code incoming Lab.

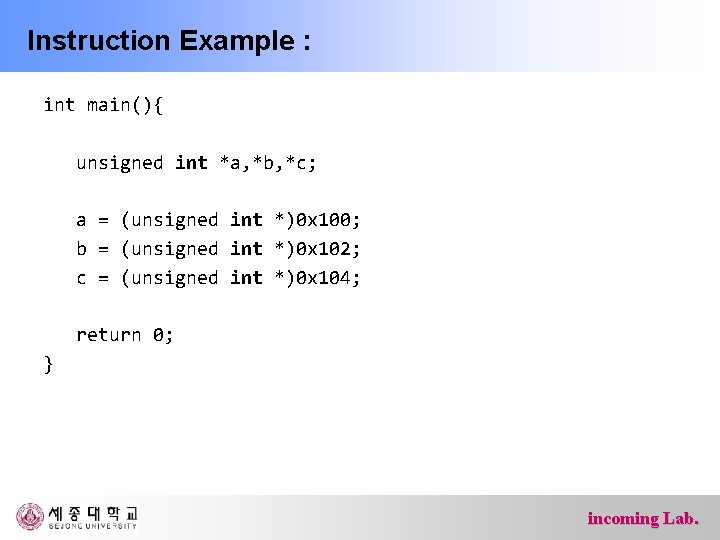

Instruction Example : int main(){ unsigned int *a, *b, *c; a = (unsigned int *)0 x 100; b = (unsigned int *)0 x 102; c = (unsigned int *)0 x 104; return 0; } incoming Lab.

Machine Code(Opcode) / Assembly Code Program address Opcode Assembly Code incoming Lab.

HEX File Compile 결과물의 하나 Project directory 아래 “default” 폴더 Intel Hex Format : 10000 C 9446000 C 945 D 0013 : 10000 C 945 D 00 EC : 100020000 C 945 D 00 DC : 100030000 C 945 D 00 CC : 100040000 C 945 D 00 BC : 100050000 C 945 D 00 AC : 100060000 C 945 D 009 C : 100070000 C 945 D 008 C : 100080000 C 945 D 0011241 FBE 67 … incoming Lab.

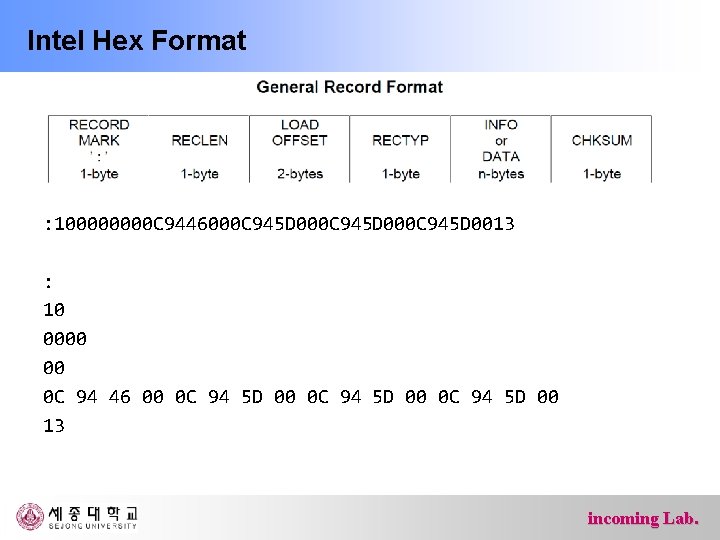

Intel Hex Format : 10000 C 9446000 C 945 D 0013 : 10 0000 00 0 C 94 46 00 0 C 94 5 D 00 13 incoming Lab.

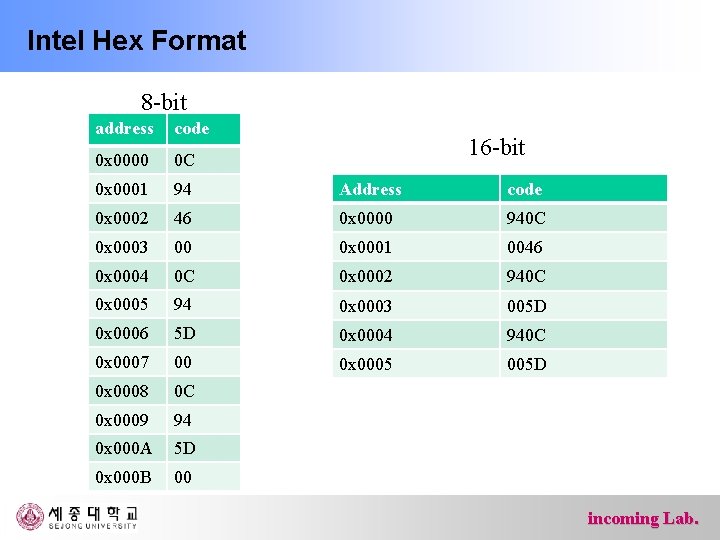

Intel Hex Format 8 -bit address code 0 x 0000 0 C 0 x 0001 94 Address code 0 x 0002 46 0 x 0000 940 C 0 x 0003 00 0 x 0001 0046 0 x 0004 0 C 0 x 0002 940 C 0 x 0005 94 0 x 0003 005 D 0 x 0006 5 D 0 x 0004 940 C 0 x 0007 00 0 x 0005 005 D 0 x 0008 0 C 0 x 0009 94 0 x 000 A 5 D 0 x 000 B 00 16 -bit incoming Lab.

- Slides: 32