Informationsteknologi Todays class n Microarchitecture Saturday October 20

Informationsteknologi Today’s class n Microarchitecture Saturday, October 20, 2007 Computer Architecture I - Class 9 1

Informationsteknologi Data Path n n The part of the CPU containing the ALU, its inputs, and its outputs This is an example data path for the IJVM microarchitecture developed in your text Saturday, October 20, 2007 Computer Architecture I - Class 9 2

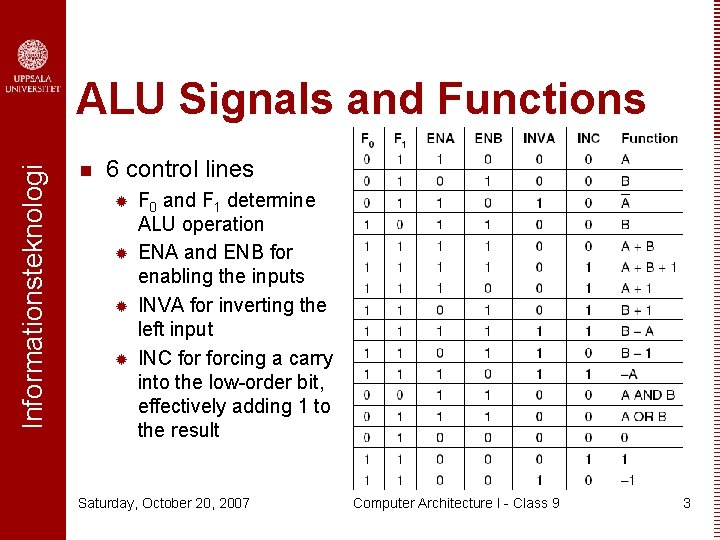

Informationsteknologi ALU Signals and Functions n 6 control lines ® ® F 0 and F 1 determine ALU operation ENA and ENB for enabling the inputs INVA for inverting the left input INC forcing a carry into the low-order bit, effectively adding 1 to the result Saturday, October 20, 2007 Computer Architecture I - Class 9 3

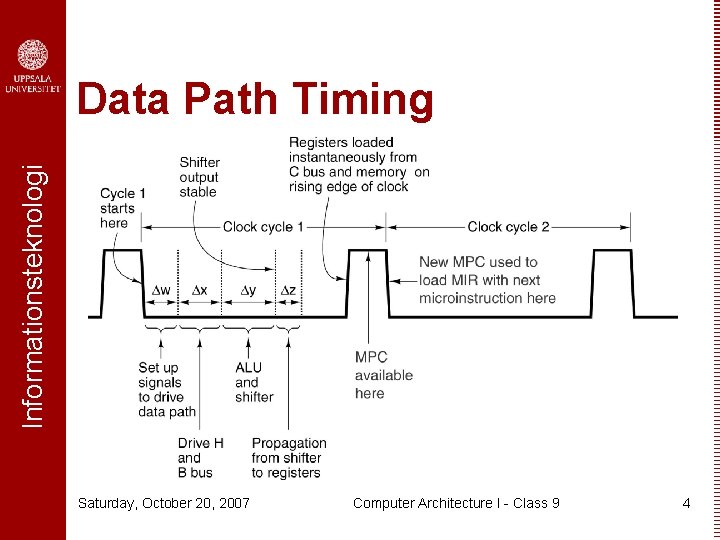

Informationsteknologi Data Path Timing Saturday, October 20, 2007 Computer Architecture I - Class 9 4

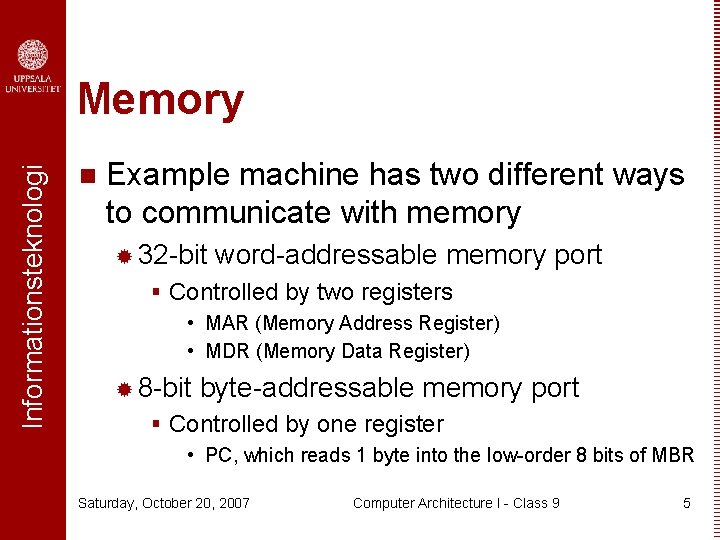

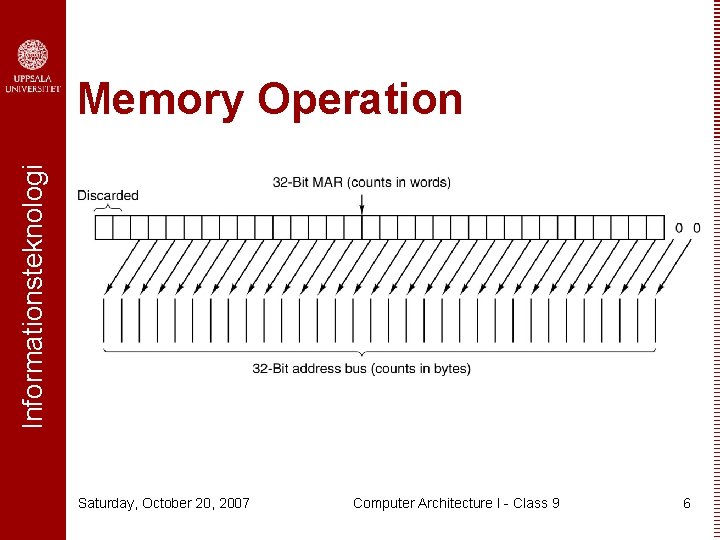

Informationsteknologi Memory n Example machine has two different ways to communicate with memory ® 32 -bit word-addressable memory port § Controlled by two registers • MAR (Memory Address Register) • MDR (Memory Data Register) ® 8 -bit byte-addressable memory port § Controlled by one register • PC, which reads 1 byte into the low-order 8 bits of MBR Saturday, October 20, 2007 Computer Architecture I - Class 9 5

Informationsteknologi Memory Operation Saturday, October 20, 2007 Computer Architecture I - Class 9 6

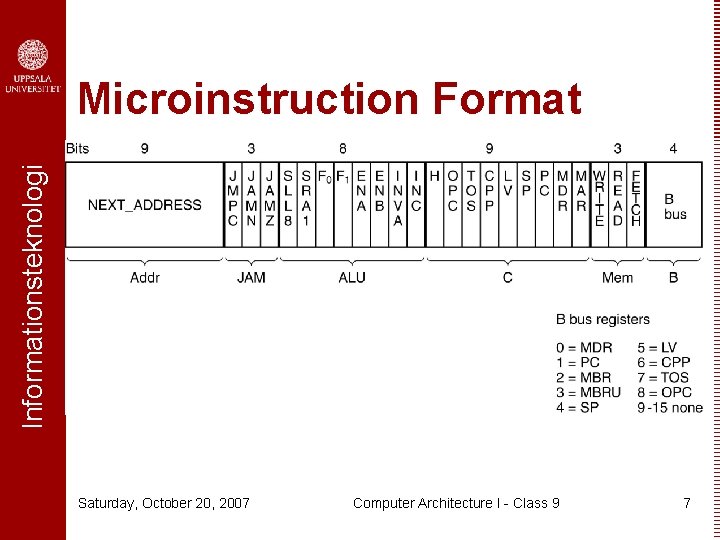

Informationsteknologi Microinstruction Format Saturday, October 20, 2007 Computer Architecture I - Class 9 7

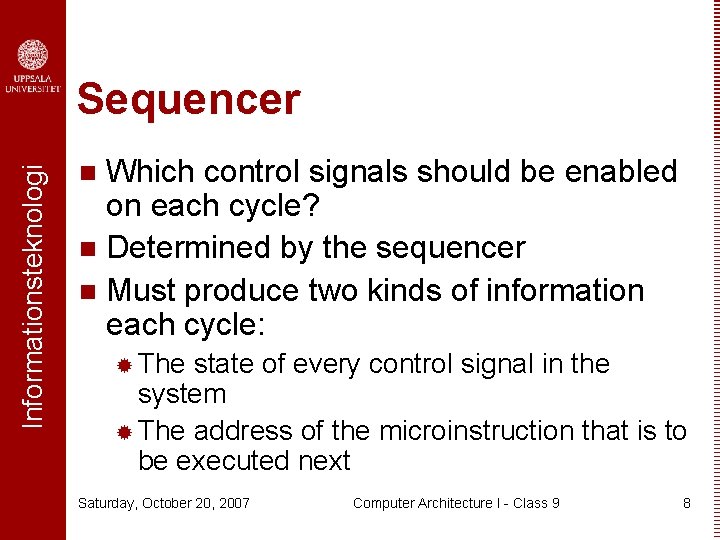

Informationsteknologi Sequencer Which control signals should be enabled on each cycle? n Determined by the sequencer n Must produce two kinds of information each cycle: n ® The state of every control signal in the system ® The address of the microinstruction that is to be executed next Saturday, October 20, 2007 Computer Architecture I - Class 9 8

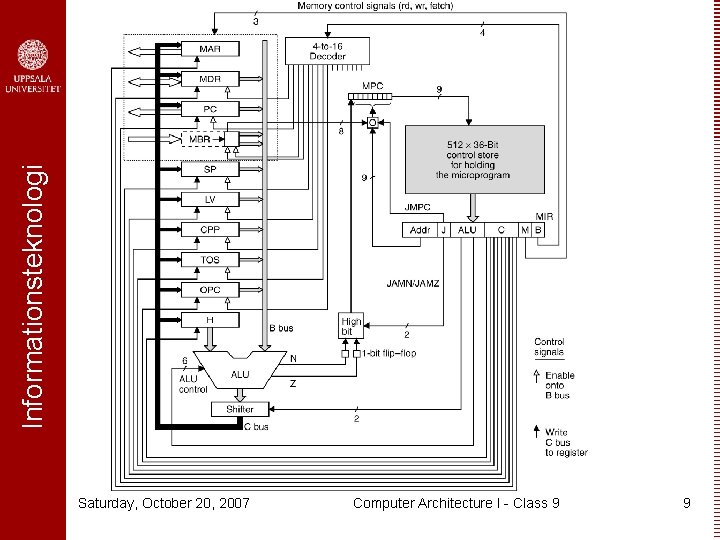

Informationsteknologi Saturday, October 20, 2007 Computer Architecture I - Class 9 9

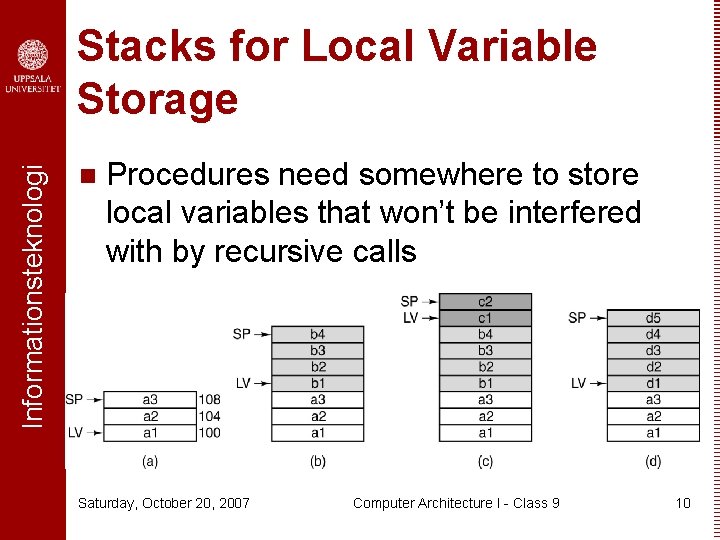

Informationsteknologi Stacks for Local Variable Storage n Procedures need somewhere to store local variables that won’t be interfered with by recursive calls Saturday, October 20, 2007 Computer Architecture I - Class 9 10

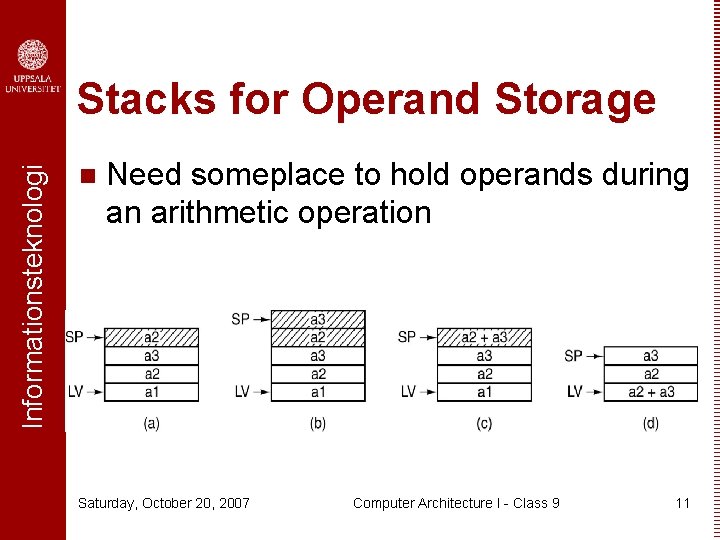

Informationsteknologi Stacks for Operand Storage n Need someplace to hold operands during an arithmetic operation Saturday, October 20, 2007 Computer Architecture I - Class 9 11

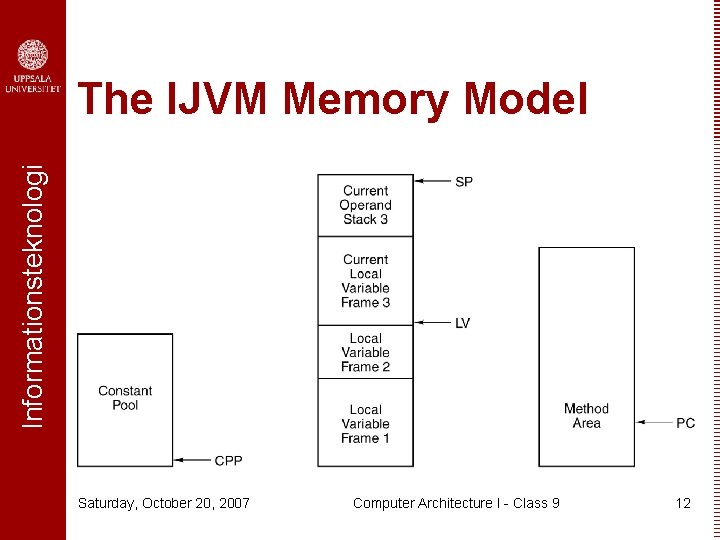

Informationsteknologi The IJVM Memory Model Saturday, October 20, 2007 Computer Architecture I - Class 9 12

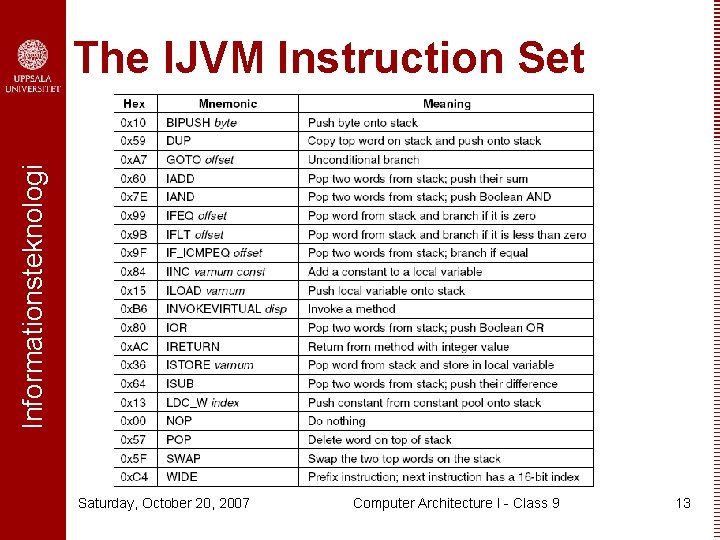

Informationsteknologi The IJVM Instruction Set Saturday, October 20, 2007 Computer Architecture I - Class 9 13

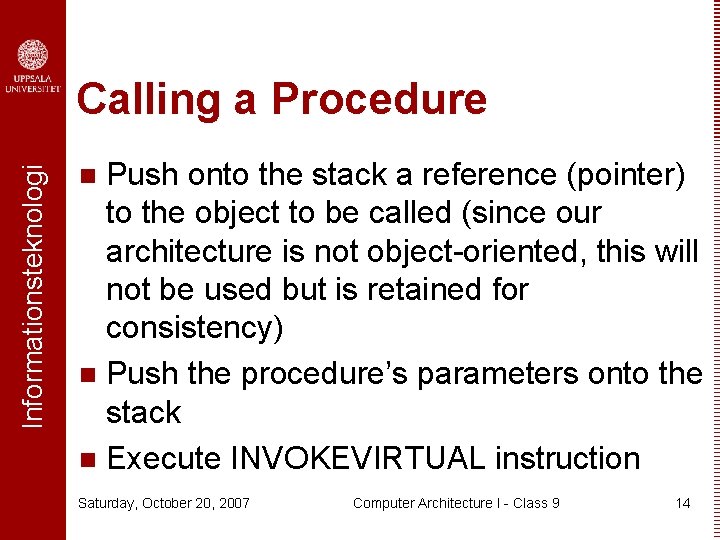

Informationsteknologi Calling a Procedure Push onto the stack a reference (pointer) to the object to be called (since our architecture is not object-oriented, this will not be used but is retained for consistency) n Push the procedure’s parameters onto the stack n Execute INVOKEVIRTUAL instruction n Saturday, October 20, 2007 Computer Architecture I - Class 9 14

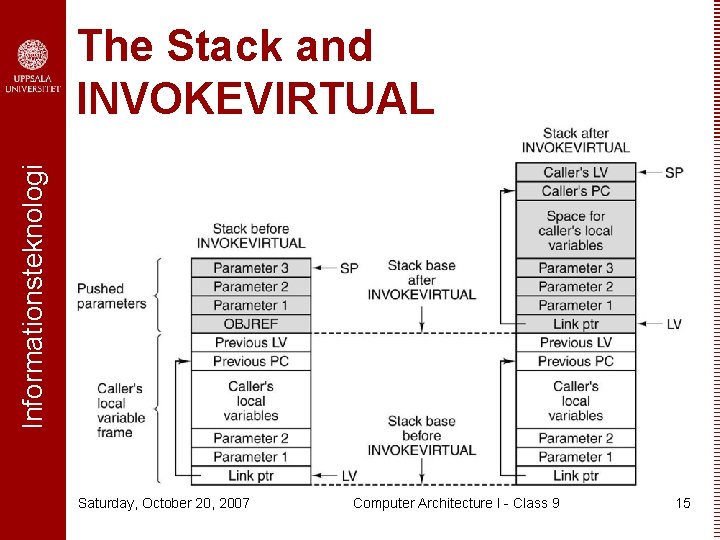

Informationsteknologi The Stack and INVOKEVIRTUAL Saturday, October 20, 2007 Computer Architecture I - Class 9 15

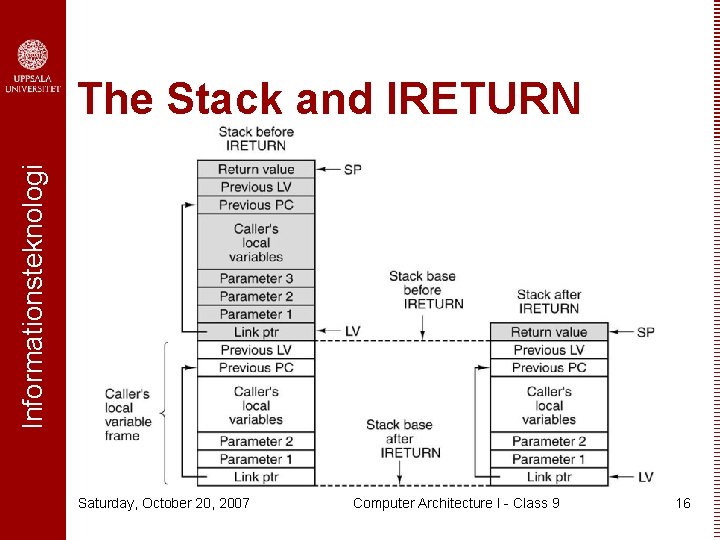

Informationsteknologi The Stack and IRETURN Saturday, October 20, 2007 Computer Architecture I - Class 9 16

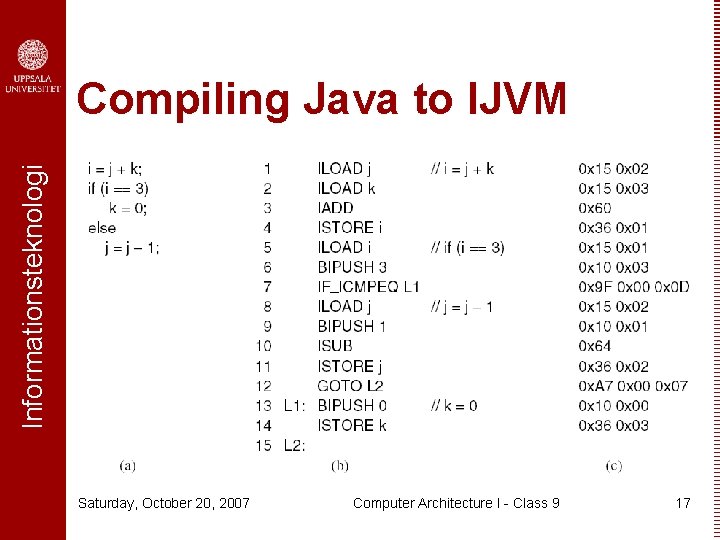

Informationsteknologi Compiling Java to IJVM Saturday, October 20, 2007 Computer Architecture I - Class 9 17

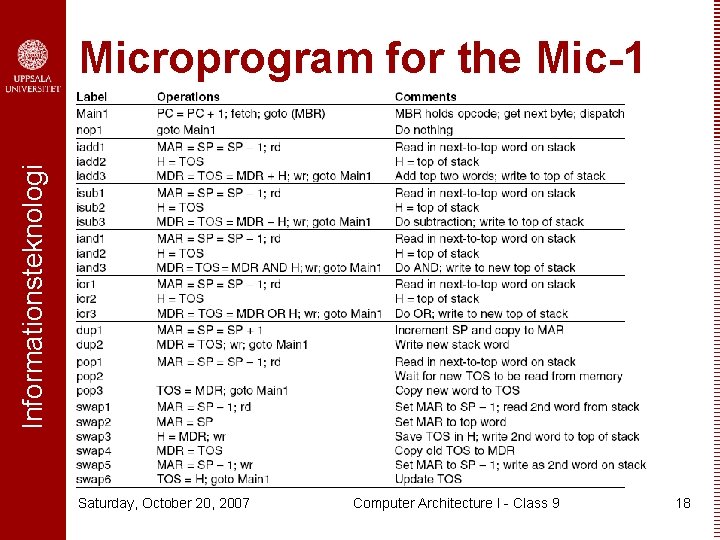

Informationsteknologi Microprogram for the Mic-1 Saturday, October 20, 2007 Computer Architecture I - Class 9 18

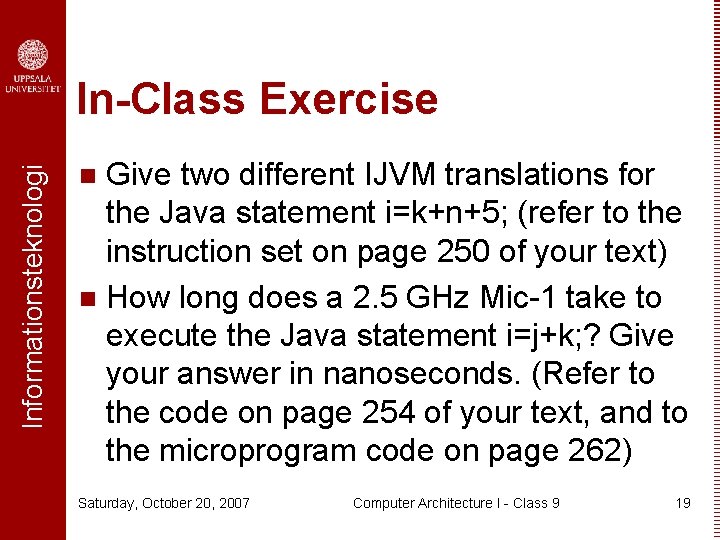

Informationsteknologi In-Class Exercise Give two different IJVM translations for the Java statement i=k+n+5; (refer to the instruction set on page 250 of your text) n How long does a 2. 5 GHz Mic-1 take to execute the Java statement i=j+k; ? Give your answer in nanoseconds. (Refer to the code on page 254 of your text, and to the microprogram code on page 262) n Saturday, October 20, 2007 Computer Architecture I - Class 9 19

Informationsteknologi Increasing Speed of Execution Reduce the number of clock cycles needed to execute an instruction n Simplify the organization so that the clock cycle can be shorter n Overlap the execution of instructions n Saturday, October 20, 2007 Computer Architecture I - Class 9 20

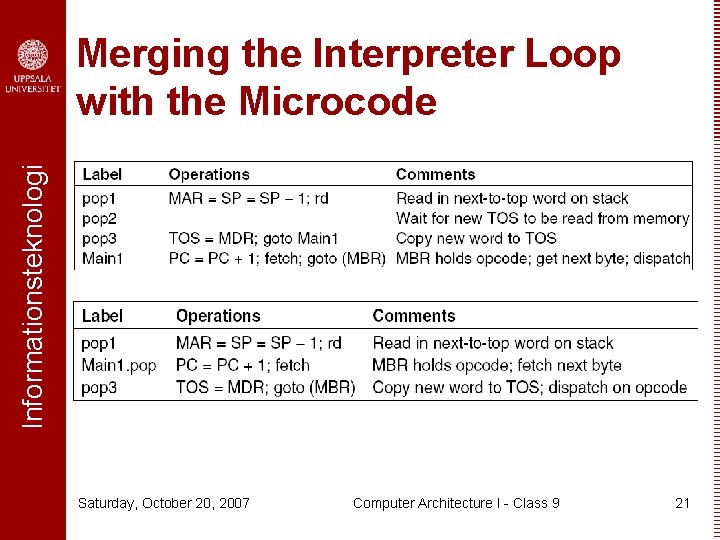

Informationsteknologi Merging the Interpreter Loop with the Microcode Saturday, October 20, 2007 Computer Architecture I - Class 9 21

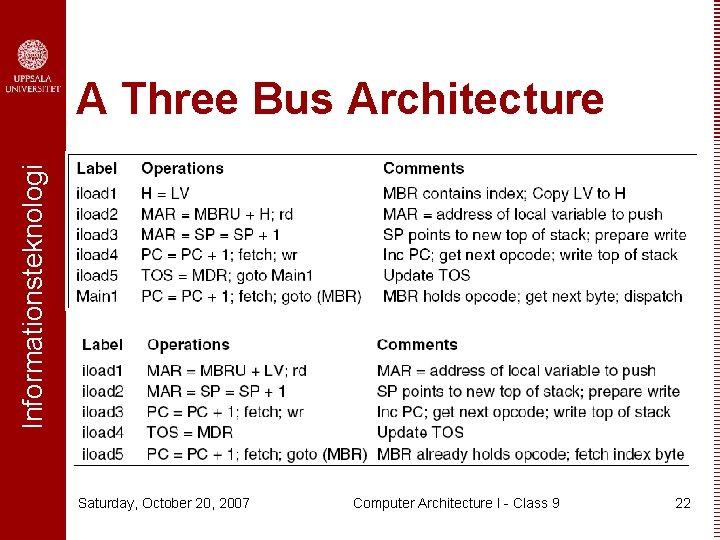

Informationsteknologi A Three Bus Architecture Saturday, October 20, 2007 Computer Architecture I - Class 9 22

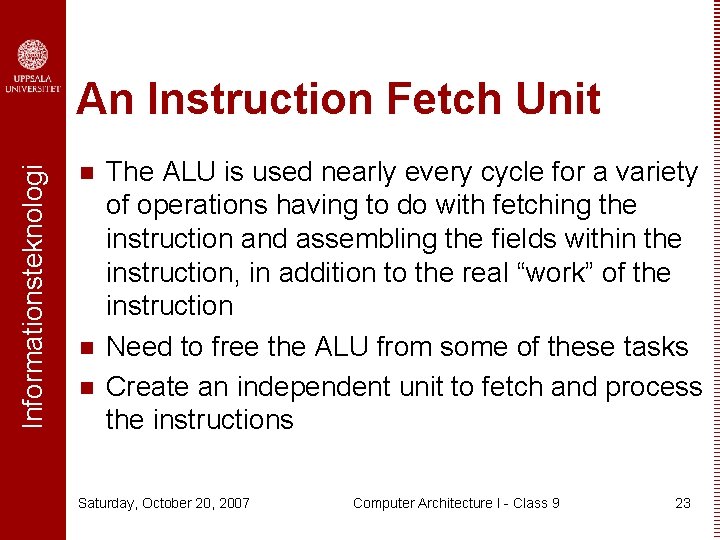

Informationsteknologi An Instruction Fetch Unit n n n The ALU is used nearly every cycle for a variety of operations having to do with fetching the instruction and assembling the fields within the instruction, in addition to the real “work” of the instruction Need to free the ALU from some of these tasks Create an independent unit to fetch and process the instructions Saturday, October 20, 2007 Computer Architecture I - Class 9 23

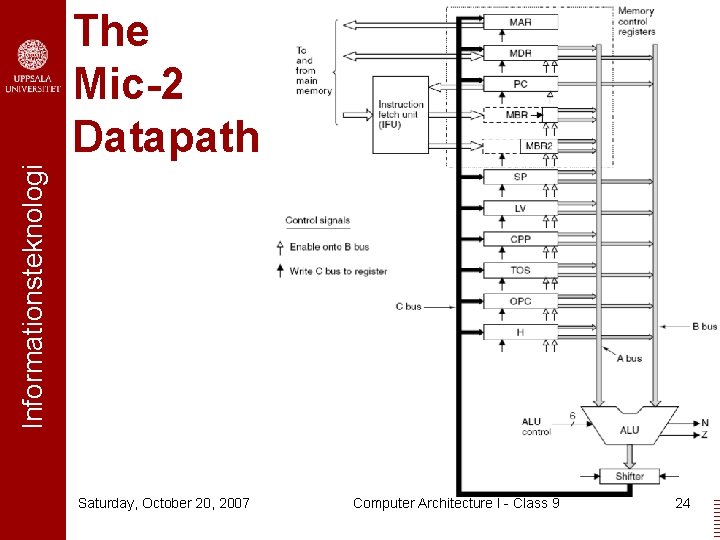

Informationsteknologi The Mic-2 Datapath Saturday, October 20, 2007 Computer Architecture I - Class 9 24

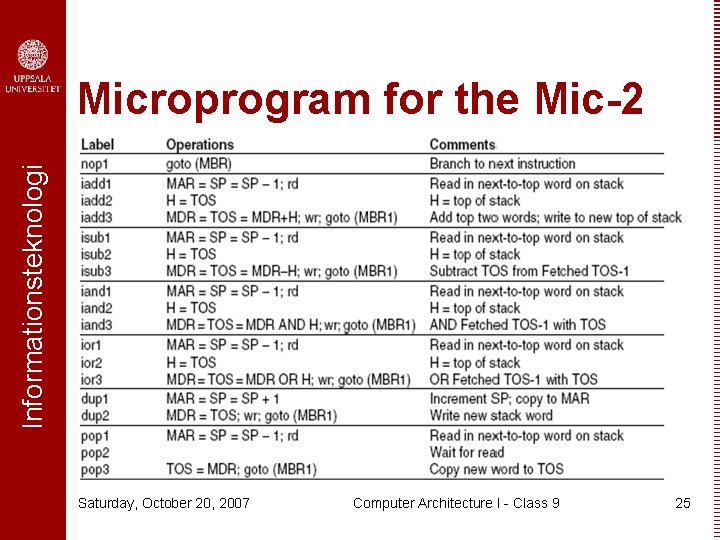

Informationsteknologi Microprogram for the Mic-2 Saturday, October 20, 2007 Computer Architecture I - Class 9 25

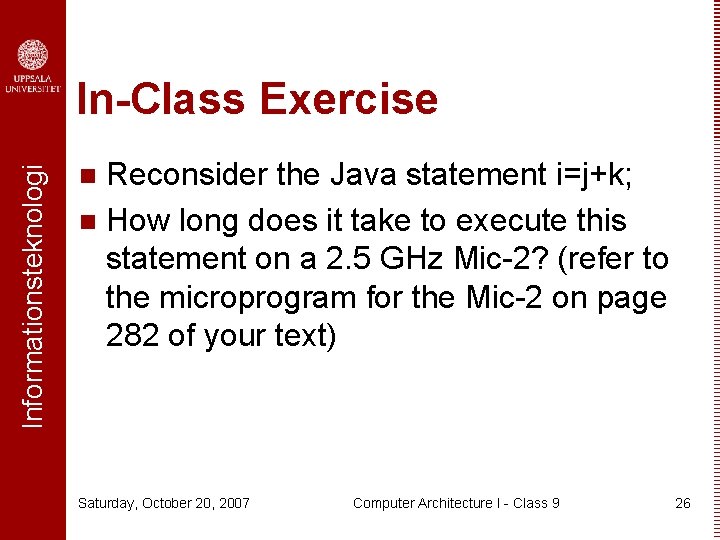

Informationsteknologi In-Class Exercise Reconsider the Java statement i=j+k; n How long does it take to execute this statement on a 2. 5 GHz Mic-2? (refer to the microprogram for the Mic-2 on page 282 of your text) n Saturday, October 20, 2007 Computer Architecture I - Class 9 26

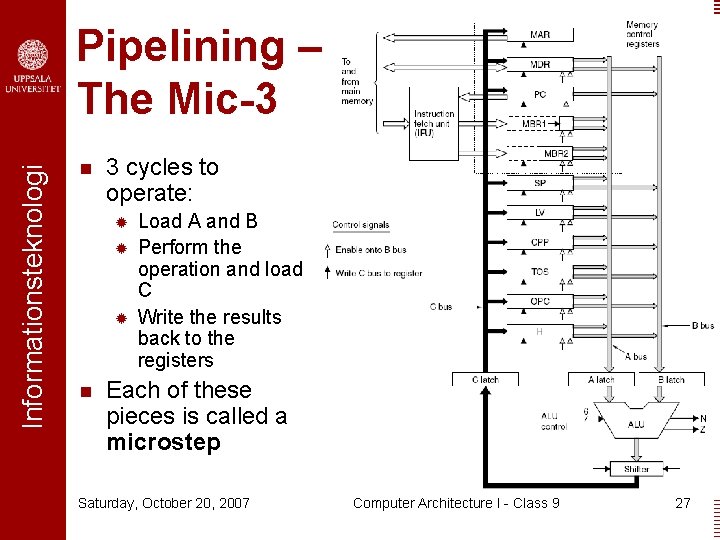

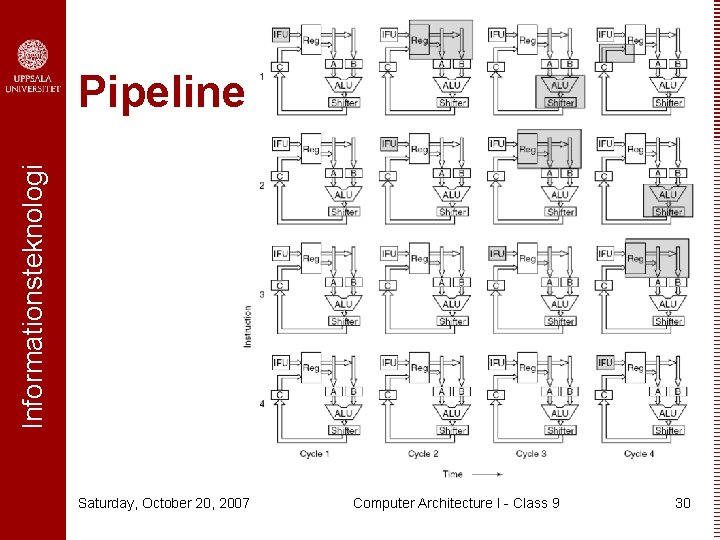

Informationsteknologi Pipelining – The Mic-3 n 3 cycles to operate: ® ® ® n Load A and B Perform the operation and load C Write the results back to the registers Each of these pieces is called a microstep Saturday, October 20, 2007 Computer Architecture I - Class 9 27

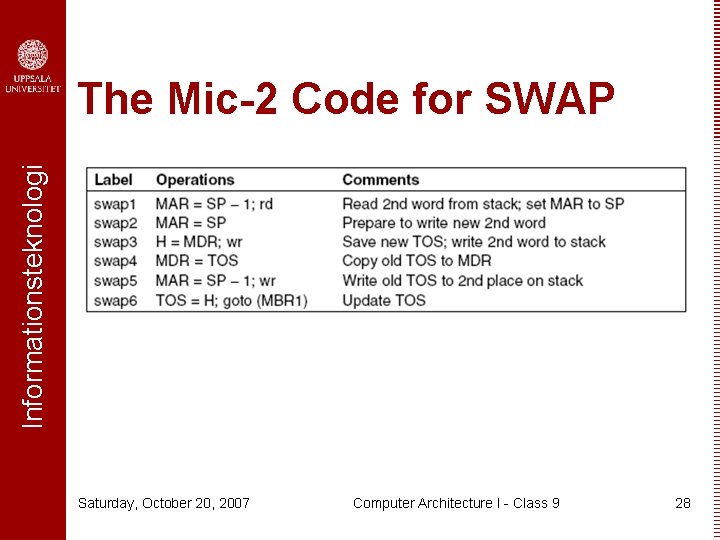

Informationsteknologi The Mic-2 Code for SWAP Saturday, October 20, 2007 Computer Architecture I - Class 9 28

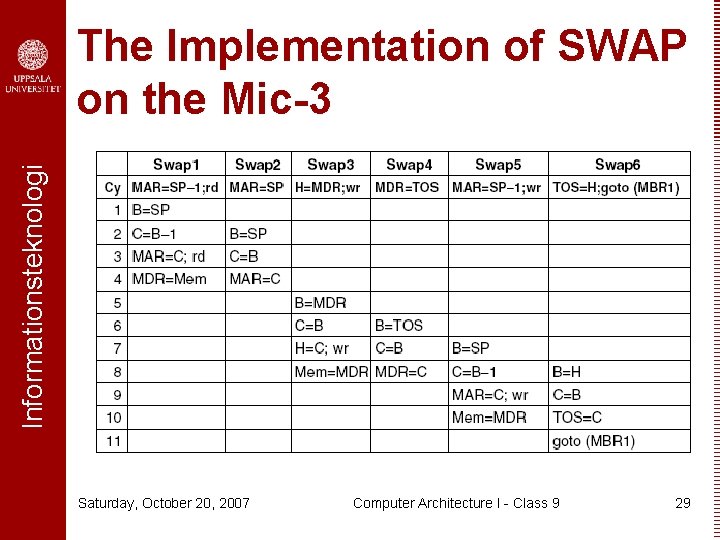

Informationsteknologi The Implementation of SWAP on the Mic-3 Saturday, October 20, 2007 Computer Architecture I - Class 9 29

Informationsteknologi Pipeline Saturday, October 20, 2007 Computer Architecture I - Class 9 30

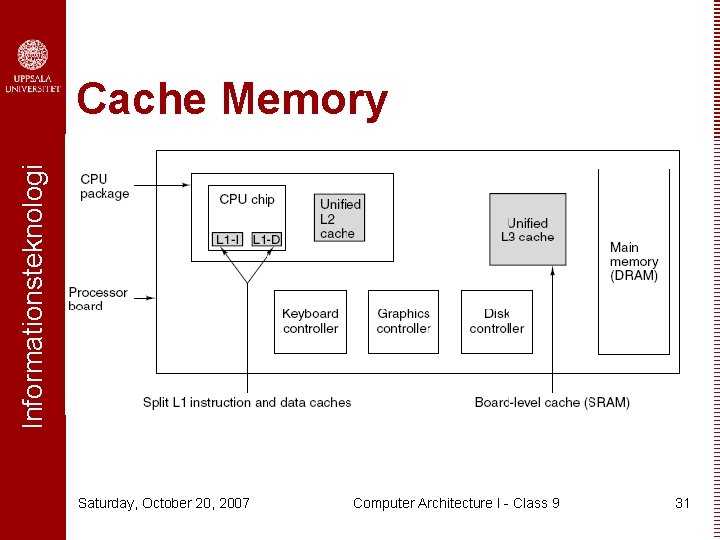

Informationsteknologi Cache Memory A system with three levels of cache. Saturday, October 20, 2007 Computer Architecture I - Class 9 31

Informationsteknologi Cache Model Main memory is divided up into fixed-size blocks called cache lines n A cache line consists of 4 to 64 consecutive bytes n Lines are numbered consecutively starting at 0 n Saturday, October 20, 2007 Computer Architecture I - Class 9 32

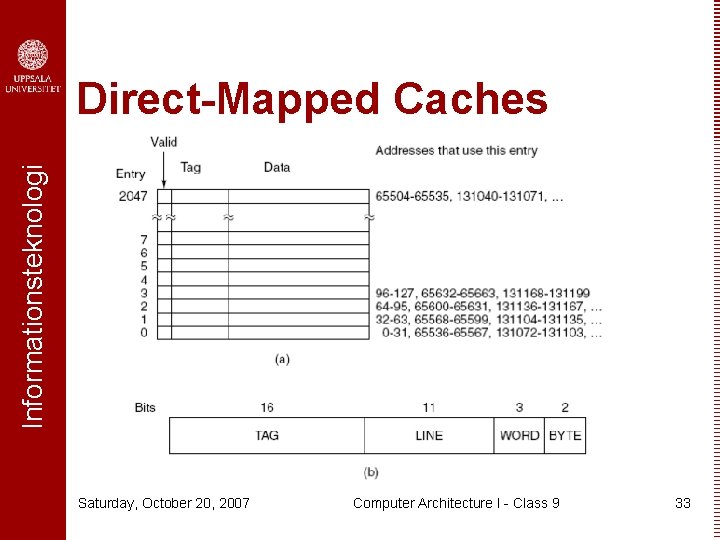

Informationsteknologi Direct-Mapped Caches Saturday, October 20, 2007 Computer Architecture I - Class 9 33

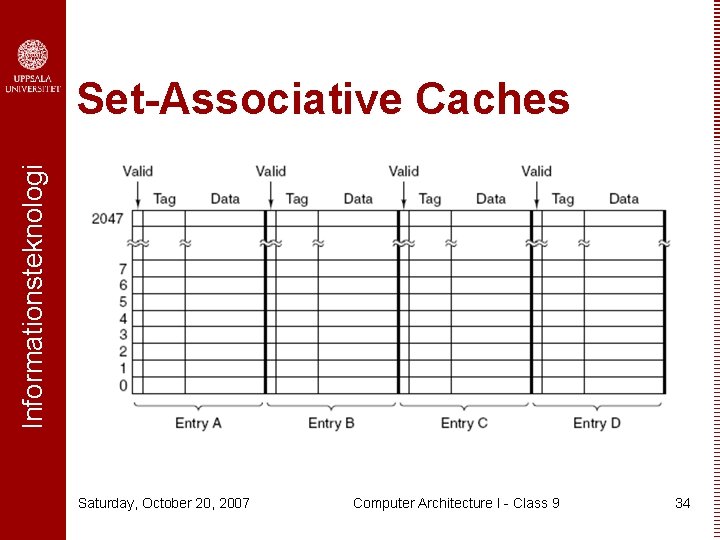

Informationsteknologi Set-Associative Caches Saturday, October 20, 2007 Computer Architecture I - Class 9 34

- Slides: 34