Chap 4 5 LC3 Computer LC3 Instructions Chap

![Branch Instruction BR [0000 nzp PCoffset 9] • Branch specifies one or more condition Branch Instruction BR [0000 nzp PCoffset 9] • Branch specifies one or more condition](https://slidetodoc.com/presentation_image_h/2ea41151b1545b18cbf402c5730d7548/image-20.jpg)

![Jump Instruction JMP Base. R [1100 000 Base. R 000000] • Jump is an Jump Instruction JMP Base. R [1100 000 Base. R 000000] • Jump is an](https://slidetodoc.com/presentation_image_h/2ea41151b1545b18cbf402c5730d7548/image-22.jpg)

- Slides: 25

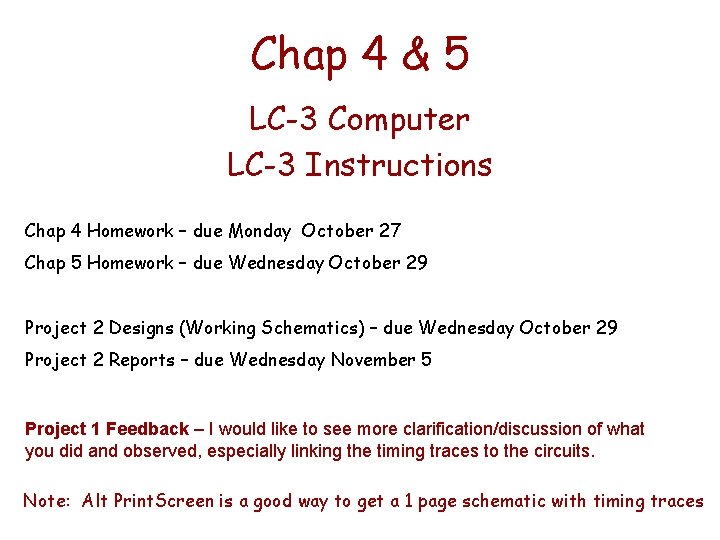

Chap 4 & 5 LC-3 Computer LC-3 Instructions Chap 4 Homework – due Monday October 27 Chap 5 Homework – due Wednesday October 29 Project 2 Designs (Working Schematics) – due Wednesday October 29 Project 2 Reports – due Wednesday November 5 Project 1 Feedback – I would like to see more clarification/discussion of what you did and observed, especially linking the timing traces to the circuits. Note: Alt Print. Screen is a good way to get a 1 page schematic with timing traces

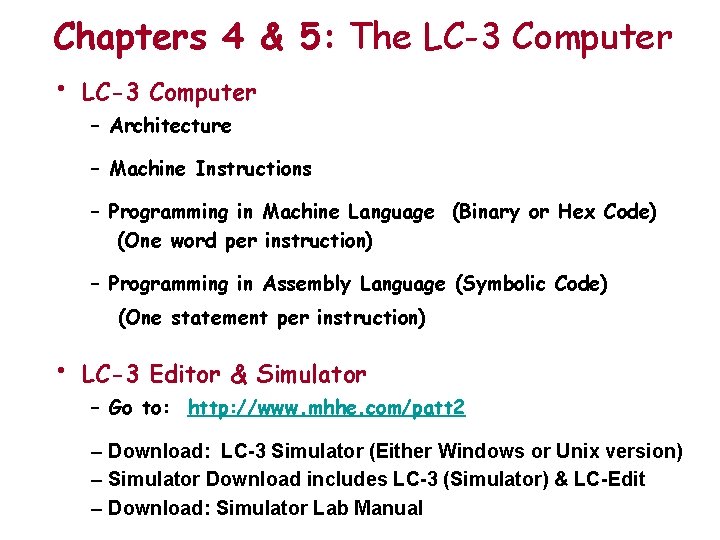

Chapters 4 & 5: The LC-3 Computer • LC-3 Computer – Architecture – Machine Instructions – Programming in Machine Language (Binary or Hex Code) (One word per instruction) – Programming in Assembly Language (Symbolic Code) (One statement per instruction) • LC-3 Editor & Simulator – Go to: http: //www. mhhe. com/patt 2 – Download: LC-3 Simulator (Either Windows or Unix version) – Simulator Download includes LC-3 (Simulator) & LC-Edit – Download: Simulator Lab Manual

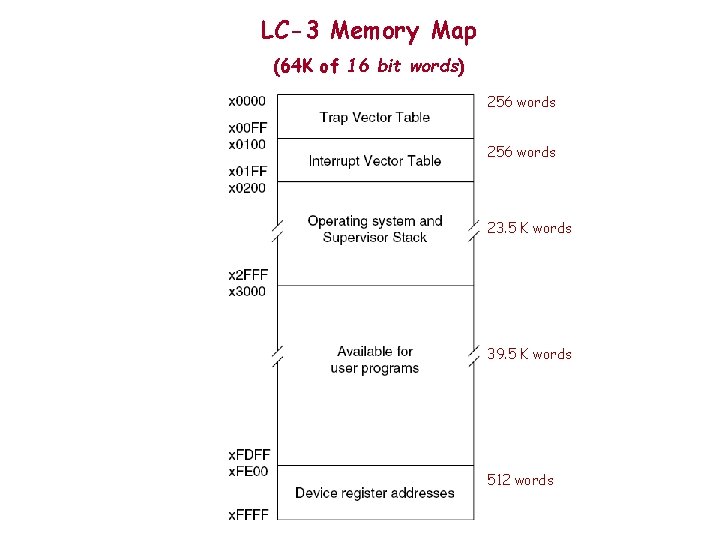

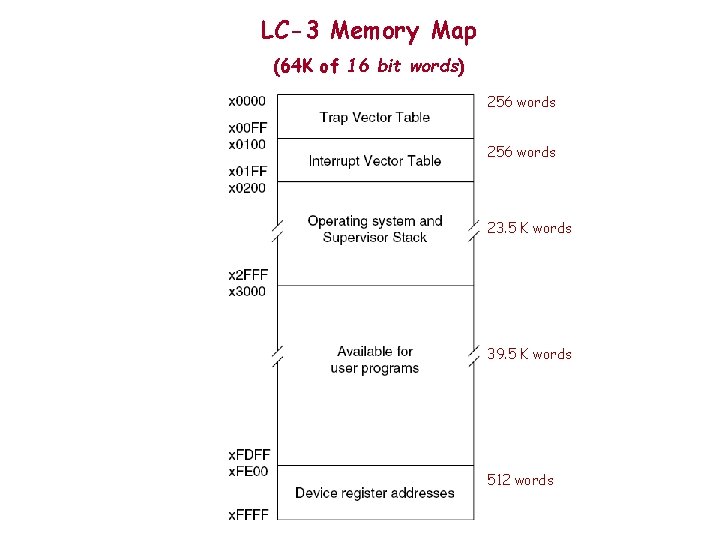

LC-3 Memory Map (64 K of 16 bit words) 256 words 23. 5 K words 39. 5 K words 512 words

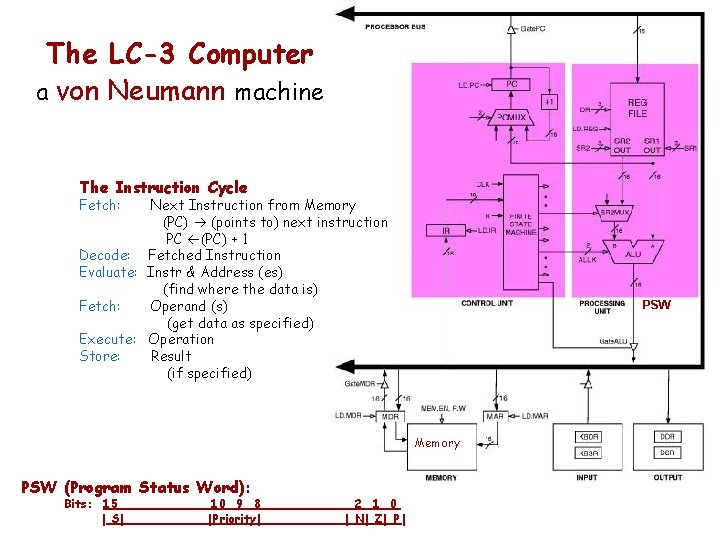

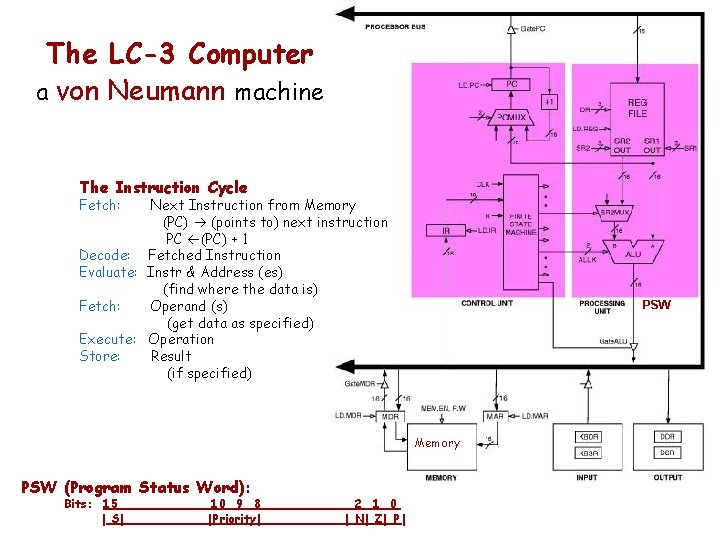

The LC-3 Computer a von Neumann machine The Instruction Cycle Fetch: Next Instruction from Memory (PC) (points to) next instruction PC (PC) + 1 Decode: Fetched Instruction Evaluate: Instr & Address (es) (find where the data is) Fetch: Operand (s) (get data as specified) Execute: Operation Store: Result (if specified) PSW Memory PSW (Program Status Word): Bits: 15 | S| 10 9 8 |Priority| 2 1 0 | N| Z| P |

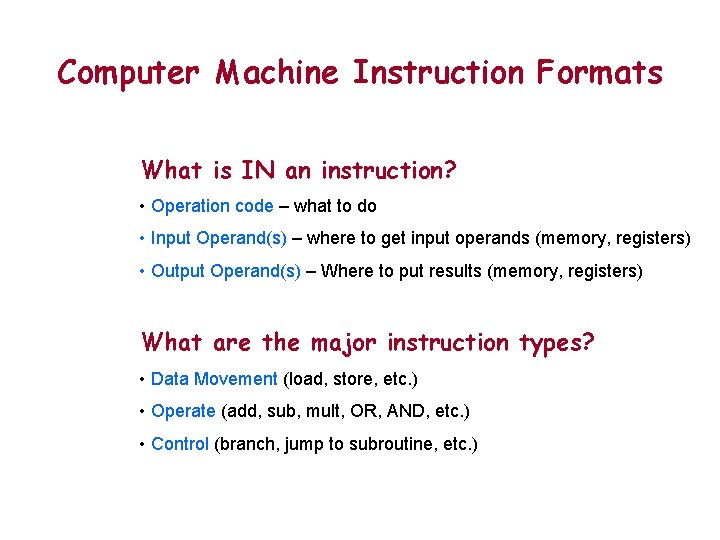

Computer Machine Instruction Formats What is IN an instruction? • Operation code – what to do • Input Operand(s) – where to get input operands (memory, registers) • Output Operand(s) – Where to put results (memory, registers) What are the major instruction types? • Data Movement (load, store, etc. ) • Operate (add, sub, mult, OR, AND, etc. ) • Control (branch, jump to subroutine, etc. )

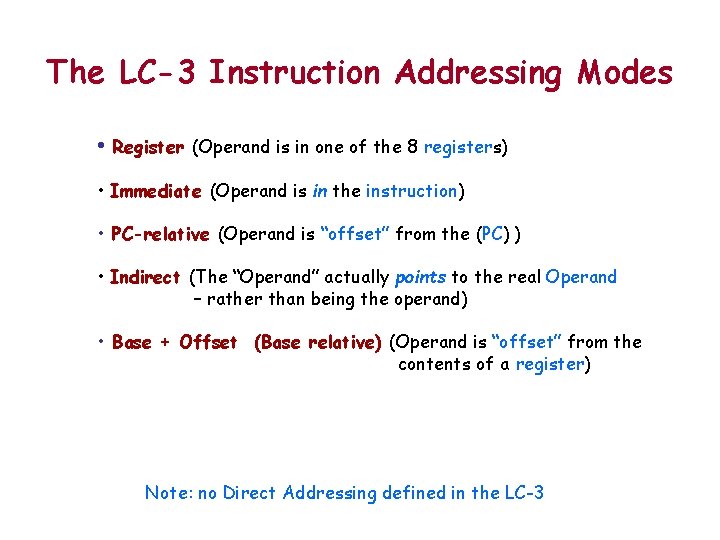

The LC-3 Instruction Addressing Modes • Register (Operand is in one of the 8 registers) • Immediate (Operand is in the instruction) • PC-relative (Operand is “offset” from the (PC) ) • Indirect (The “Operand” actually points to the real Operand – rather than being the operand) • Base + Offset (Base relative) (Operand is “offset” from the contents of a register) Note: no Direct Addressing defined in the LC-3

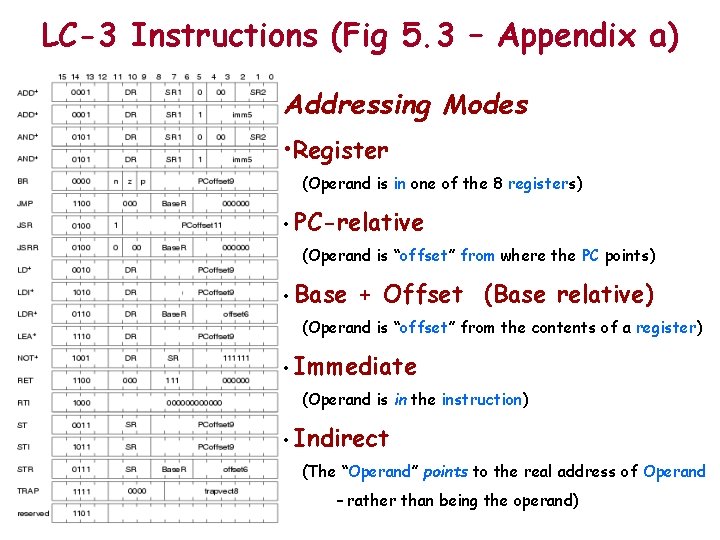

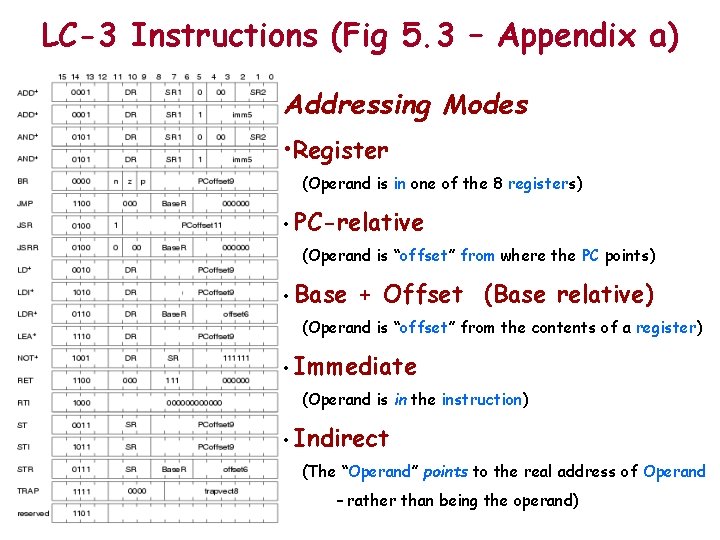

LC-3 Instructions (Fig 5. 3 – Appendix a) Addressing Modes • Register (Operand is in one of the 8 registers) • PC-relative (Operand is “offset” from where the PC points) • Base + Offset (Base relative) (Operand is “offset” from the contents of a register) • Immediate (Operand is in the instruction) • Indirect (The “Operand” points to the real address of Operand – rather than being the operand)

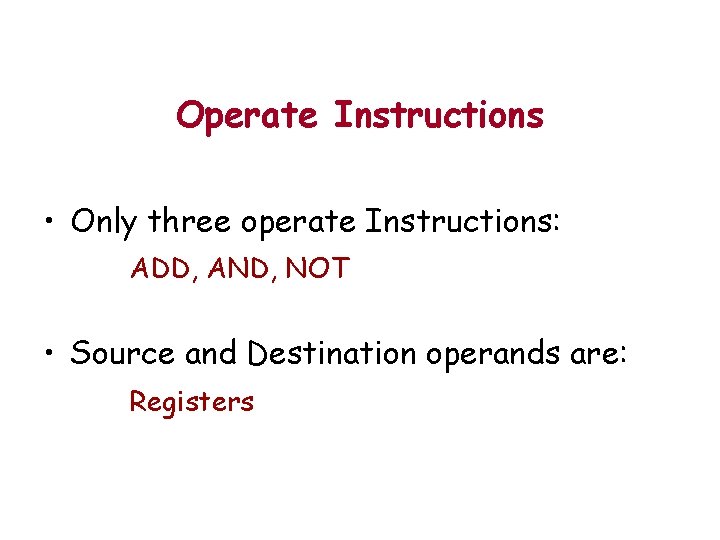

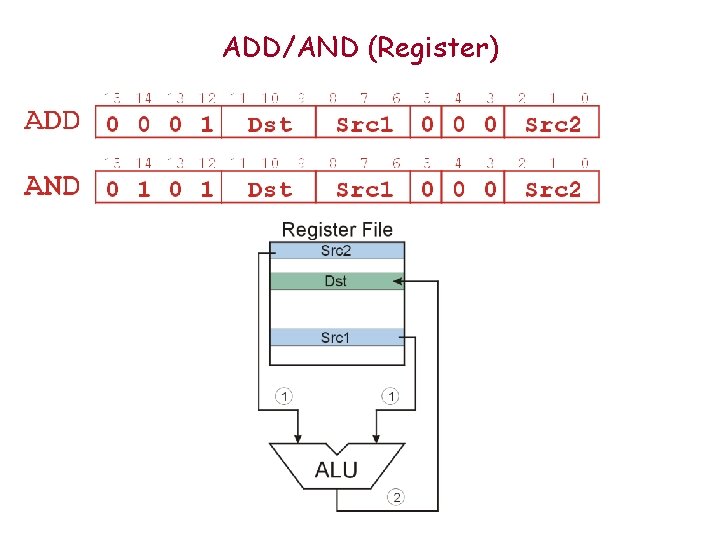

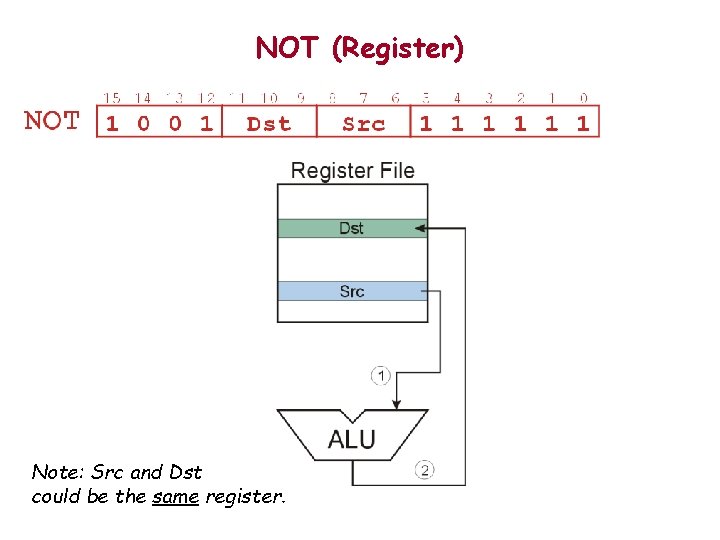

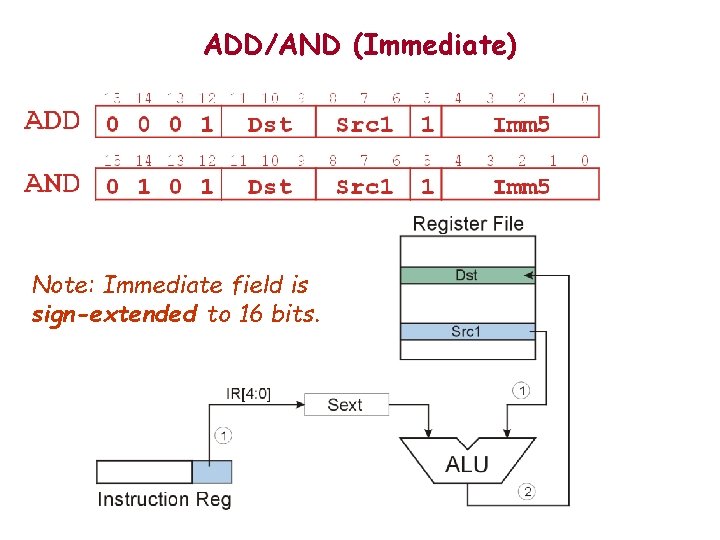

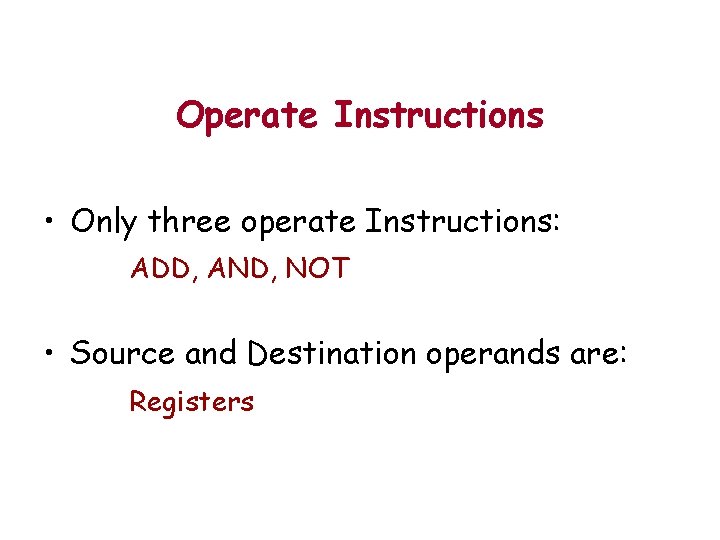

Operate Instructions • Only three operate Instructions: ADD, AND, NOT • Source and Destination operands are: Registers

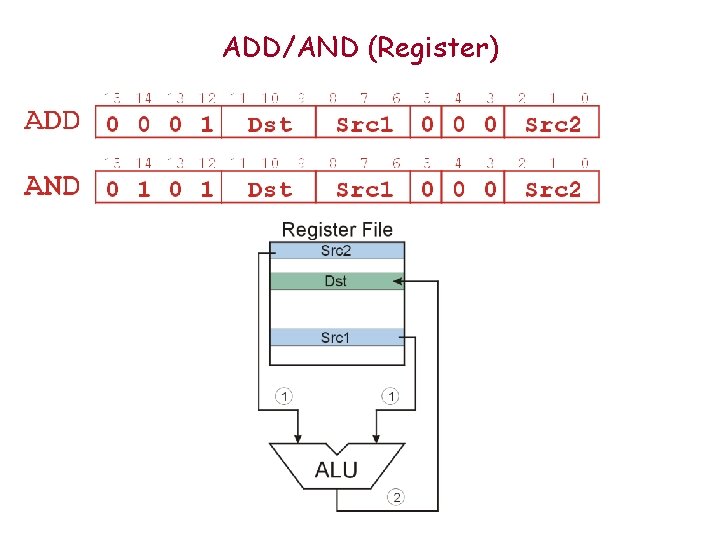

ADD/AND (Register)

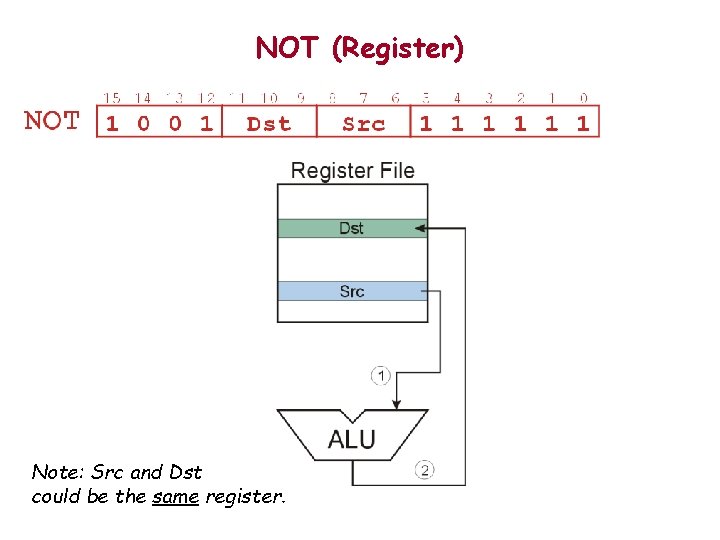

NOT (Register) Note: Src and Dst could be the same register.

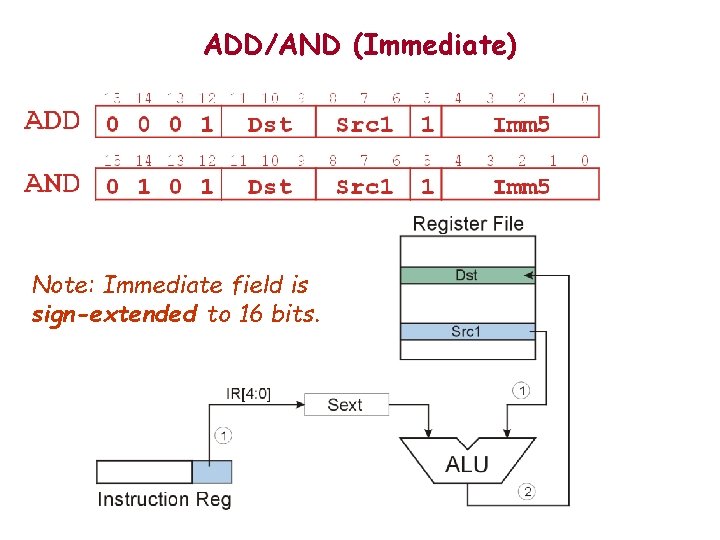

ADD/AND (Immediate) Note: Immediate field is sign-extended to 16 bits.

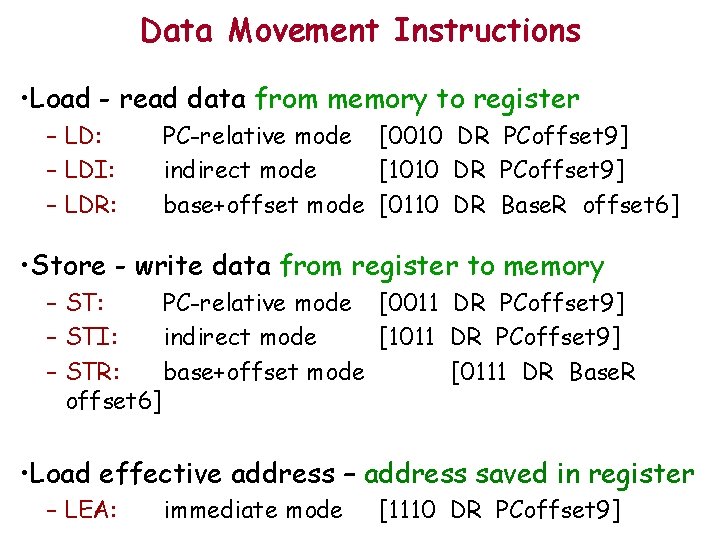

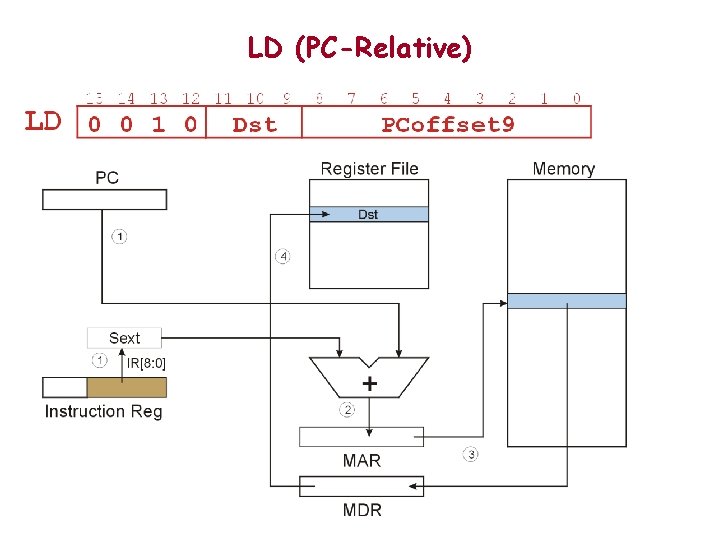

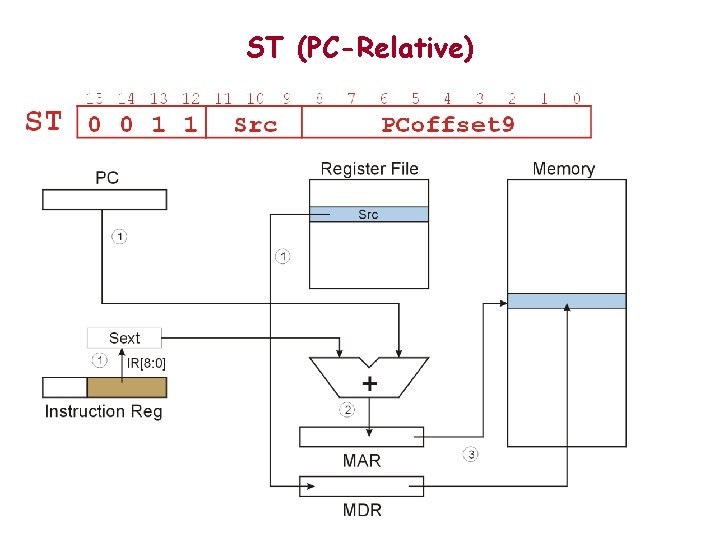

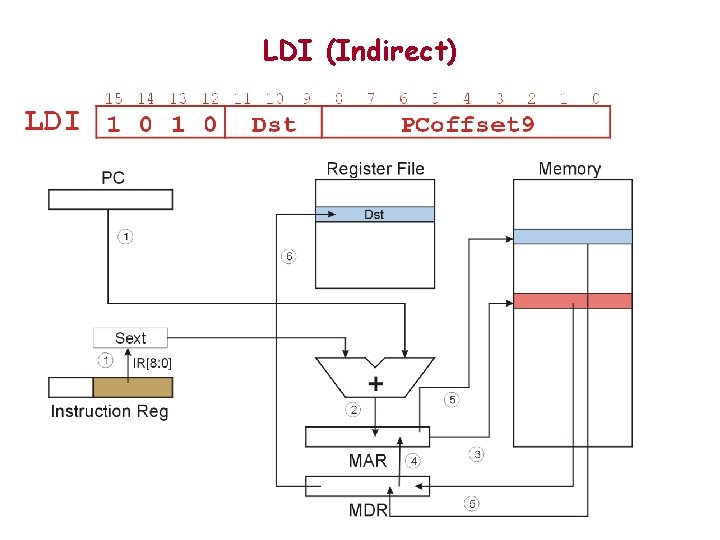

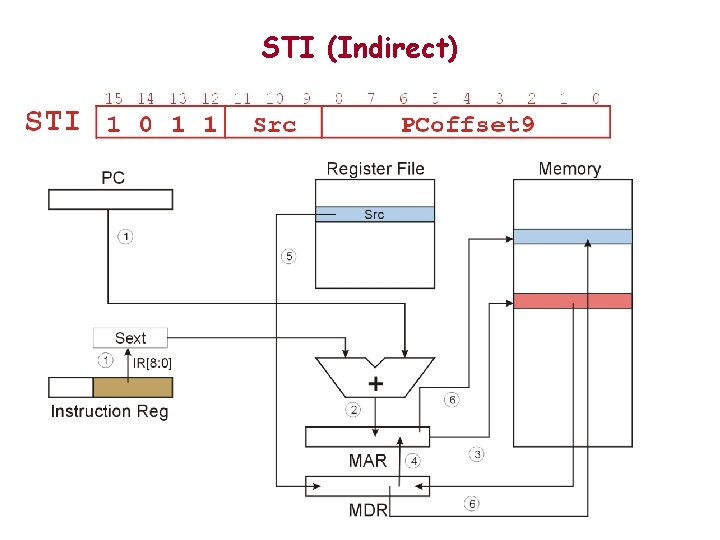

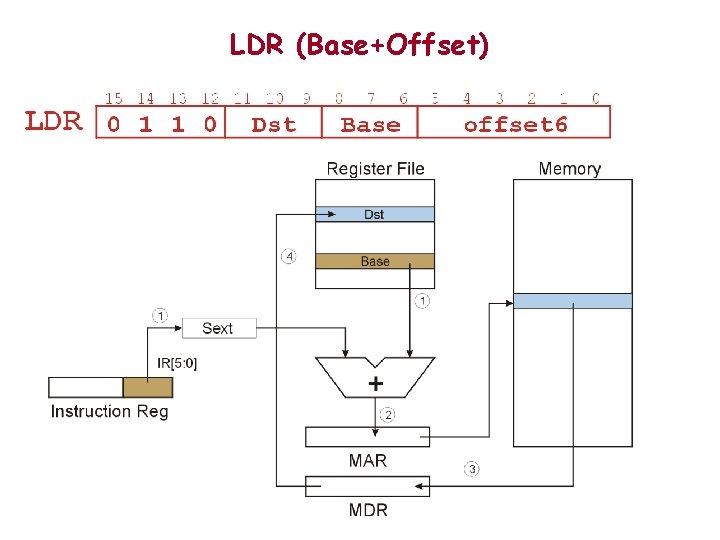

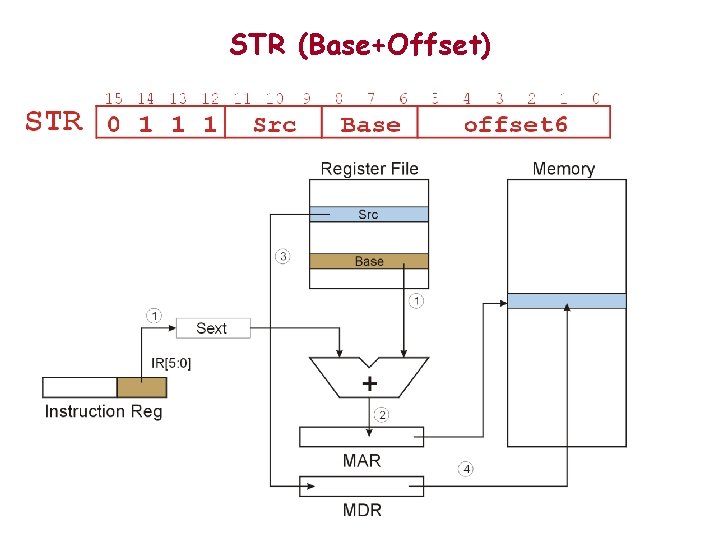

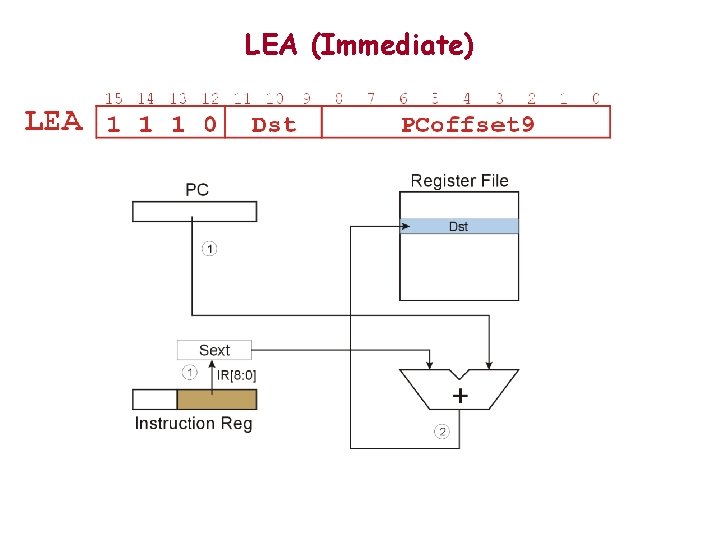

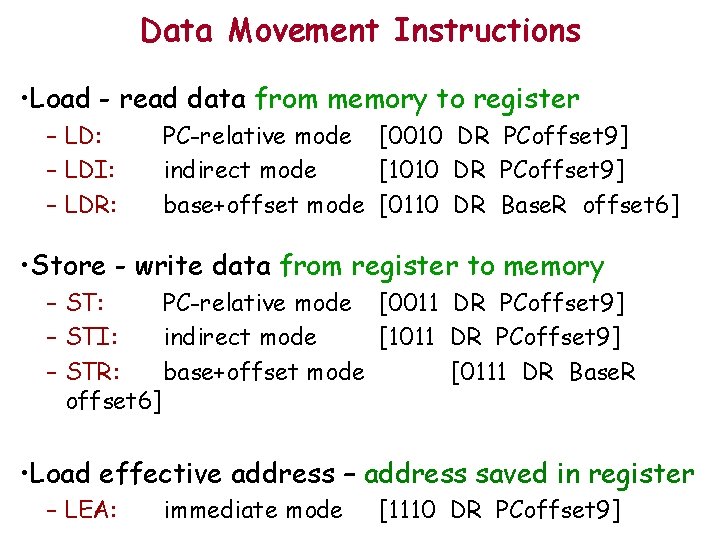

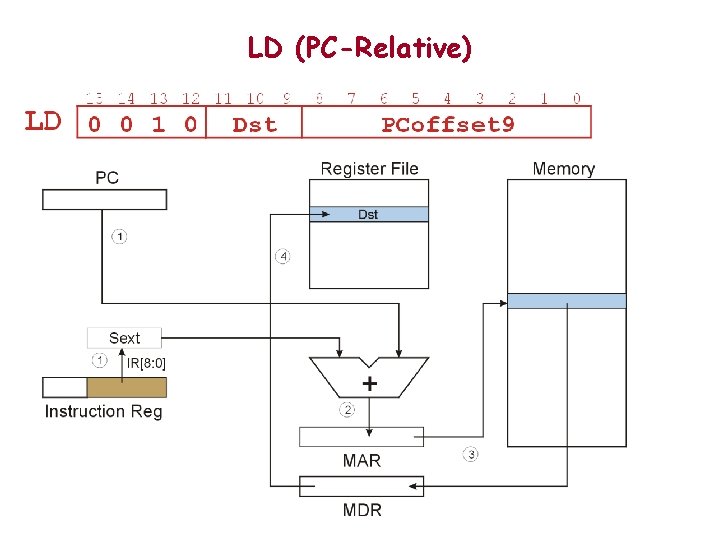

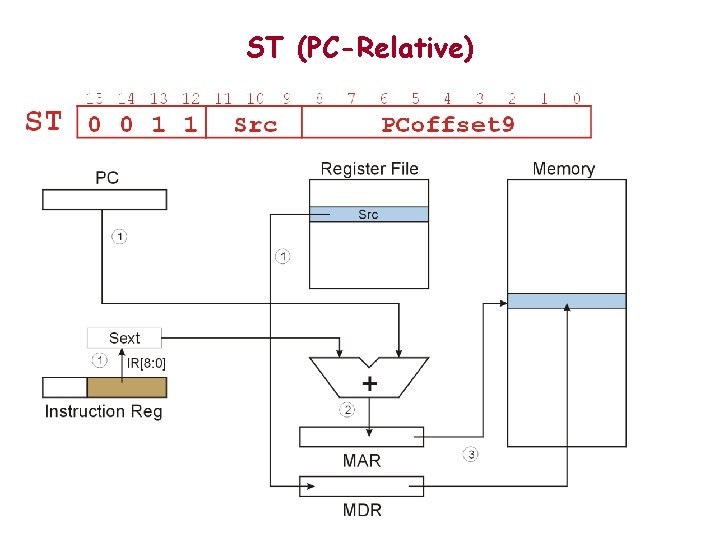

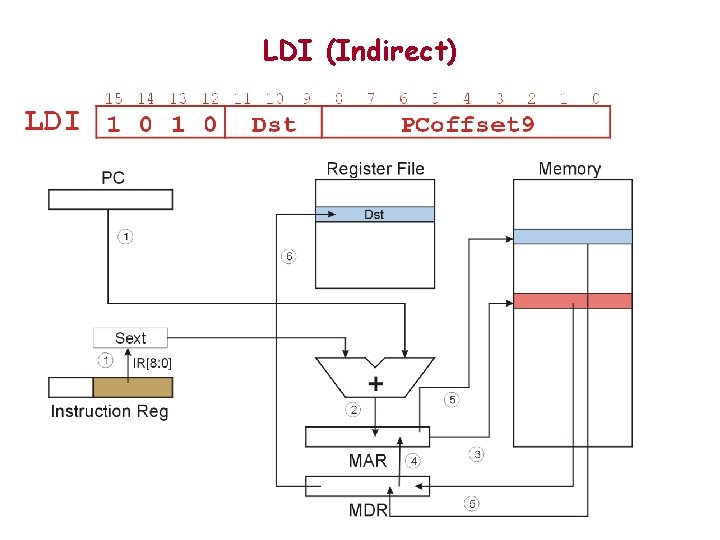

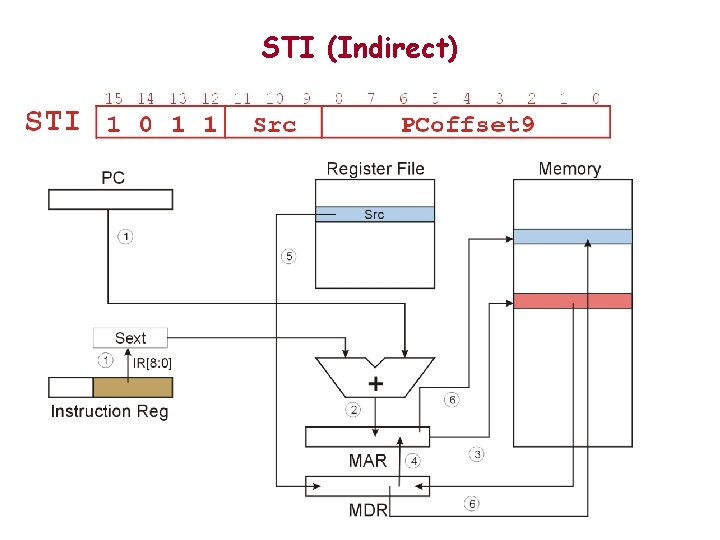

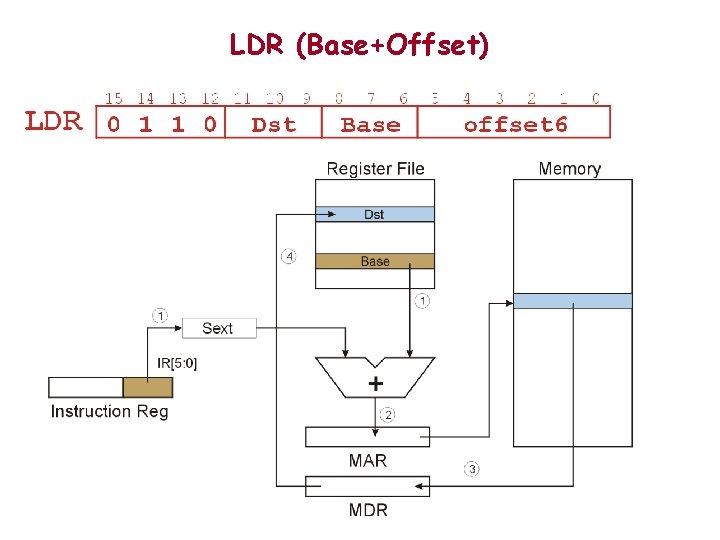

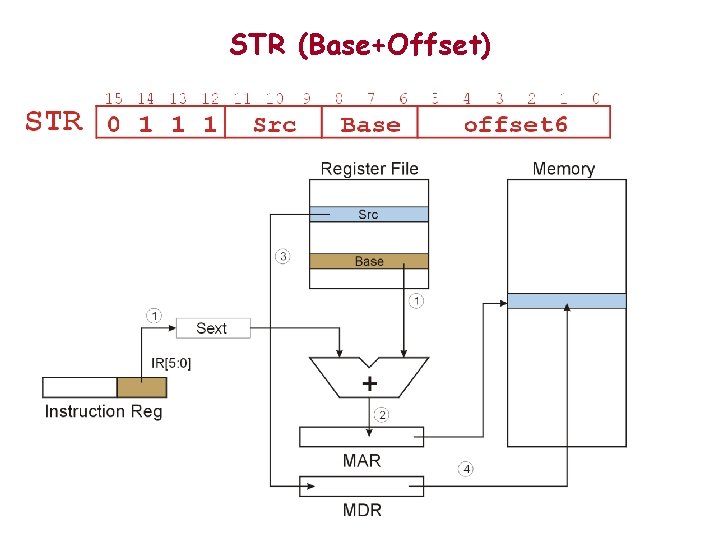

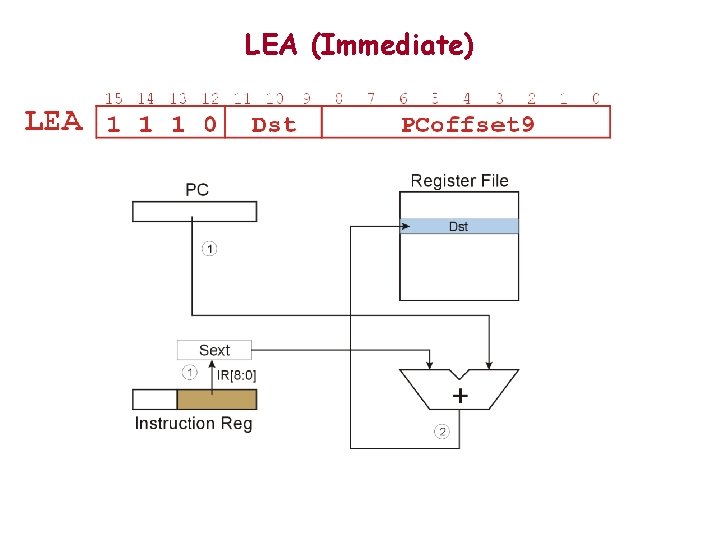

Data Movement Instructions • Load - read data from memory to register – LD: – LDI: – LDR: PC-relative mode [0010 DR PCoffset 9] indirect mode [1010 DR PCoffset 9] base+offset mode [0110 DR Base. R offset 6] • Store - write data from register to memory – ST: PC-relative mode [0011 DR PCoffset 9] – STI: indirect mode [1011 DR PCoffset 9] – STR: base+offset mode [0111 DR Base. R offset 6] • Load effective address – address saved in register – LEA: immediate mode [1110 DR PCoffset 9]

LD (PC-Relative)

ST (PC-Relative)

LDI (Indirect)

STI (Indirect)

LDR (Base+Offset)

STR (Base+Offset)

LEA (Immediate)

![Branch Instruction BR 0000 nzp PCoffset 9 Branch specifies one or more condition Branch Instruction BR [0000 nzp PCoffset 9] • Branch specifies one or more condition](https://slidetodoc.com/presentation_image_h/2ea41151b1545b18cbf402c5730d7548/image-20.jpg)

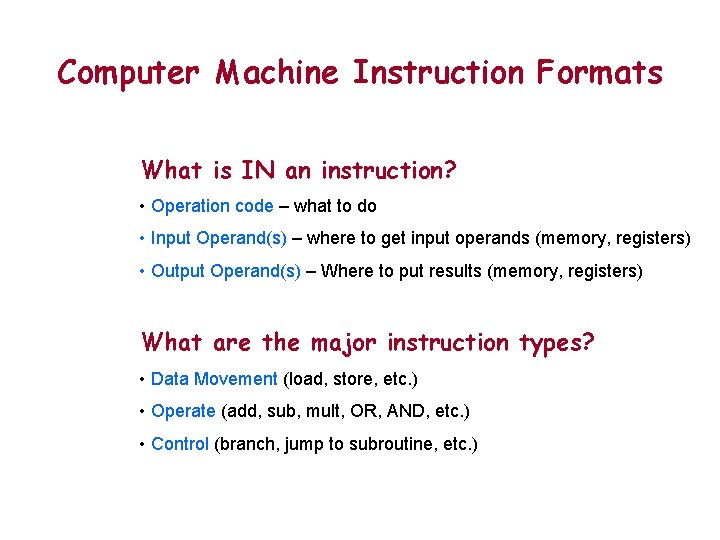

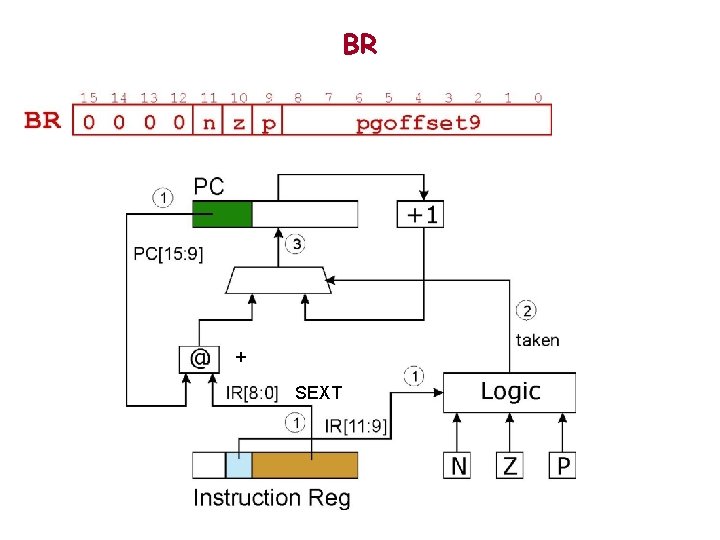

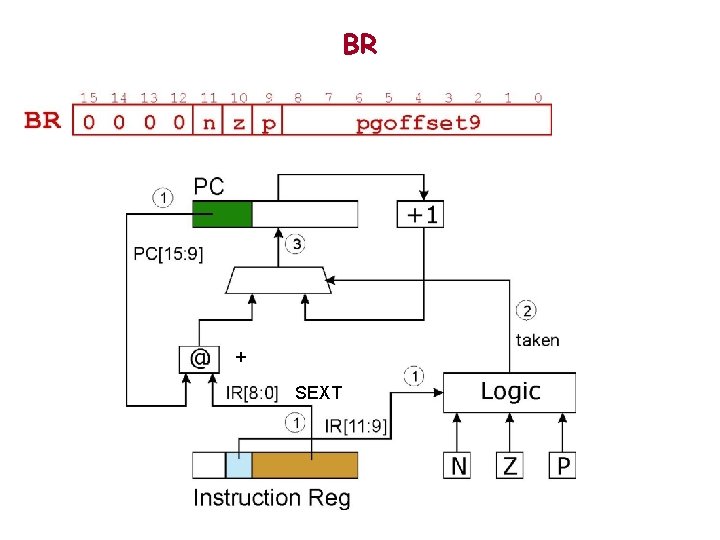

Branch Instruction BR [0000 nzp PCoffset 9] • Branch specifies one or more condition codes Program Status Word (PSW): Bits: 15 | S| 10 9 8 |Priority| 2 1 0 |N|Z|P| • If the set bit is specified, the branch is taken: – PC is set to the address specified in the instruction - Target address is made by adding SEXT(IR[8: 0]) to the PC • If the branch is not taken: - the next sequential instruction (PC) is executed.

BR + SEXT

![Jump Instruction JMP Base R 1100 000 Base R 000000 Jump is an Jump Instruction JMP Base. R [1100 000 Base. R 000000] • Jump is an](https://slidetodoc.com/presentation_image_h/2ea41151b1545b18cbf402c5730d7548/image-22.jpg)

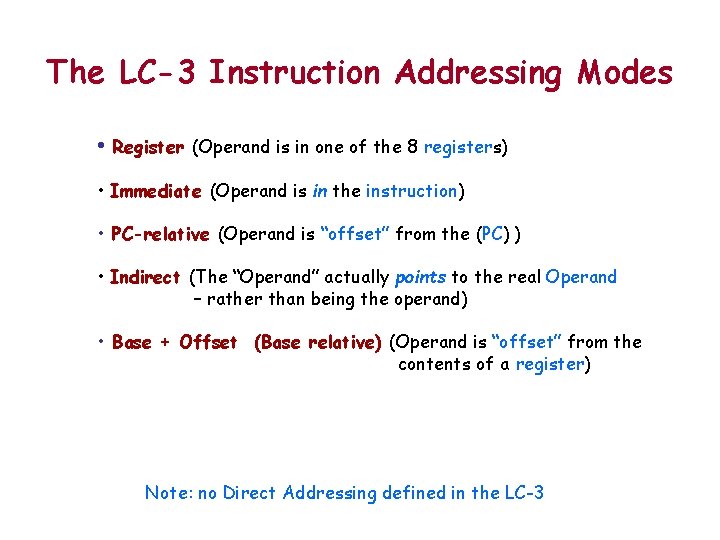

Jump Instruction JMP Base. R [1100 000 Base. R 000000] • Jump is an unconditional branch -- always taken. • Base. R – Address is contents of the register – Allows any target address.

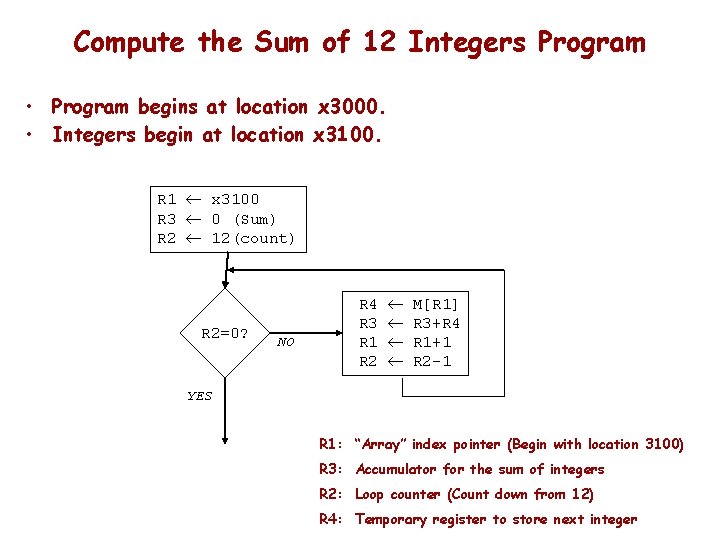

Example LC-3 Program • Write a program to add 12 integers and store the result in a Register.

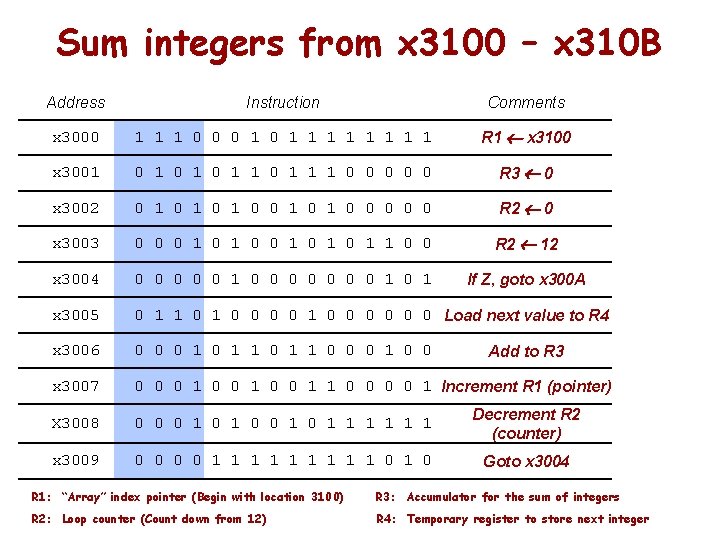

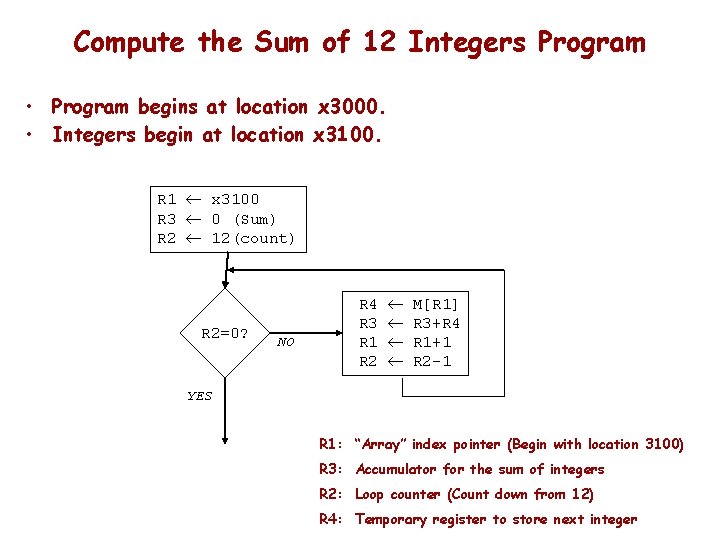

Compute the Sum of 12 Integers Program • Program begins at location x 3000. • Integers begin at location x 3100. R 1 x 3100 R 3 0 (Sum) R 2 12(count) R 2=0? NO R 4 R 3 R 1 R 2 M[R 1] R 3+R 4 R 1+1 R 2 -1 YES R 1: “Array” index pointer (Begin with location 3100) R 3: Accumulator for the sum of integers R 2: Loop counter (Count down from 12) R 4: Temporary register to store next integer

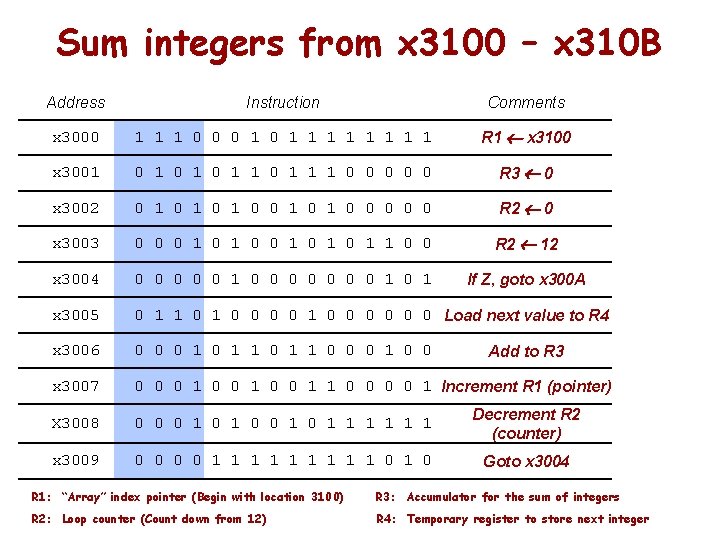

Sum integers from x 3100 – x 310 B Address Instruction Comments x 3000 1 1 1 0 0 0 1 1 1 1 1 R 1 x 3100 x 3001 0 1 0 1 1 1 0 0 0 R 3 0 x 3002 0 1 0 1 0 1 0 0 0 R 2 0 x 3003 0 0 0 1 0 1 0 1 1 0 0 R 2 12 x 3004 0 0 0 1 0 0 0 0 1 If Z, goto x 300 A x 3005 0 1 1 0 0 0 0 1 0 0 0 Load next value to R 4 x 3006 0 0 0 1 1 0 0 0 1 0 0 x 3007 0 0 0 1 1 0 0 1 Increment R 1 (pointer) X 3008 0 0 0 1 0 1 1 1 1 Decrement R 2 (counter) x 3009 0 0 1 1 1 1 1 0 Goto x 3004 Add to R 3 R 1: “Array” index pointer (Begin with location 3100) R 3: Accumulator for the sum of integers R 2: Loop counter (Count down from 12) R 4: Temporary register to store next integer