Chapter 5 The LC3 Computer Architecture Memory Map

![Branch Instruction BR • [0000 nzp PCoffset 9] Branch specifies one or more condition Branch Instruction BR • [0000 nzp PCoffset 9] Branch specifies one or more condition](https://slidetodoc.com/presentation_image_h2/bc3ae8221f6261f1215e455fb2d4eceb/image-12.jpg)

![Jump Instruction JMP Base. R [1100 000 Base. R 000000] • Jump is an Jump Instruction JMP Base. R [1100 000 Base. R 000000] • Jump is an](https://slidetodoc.com/presentation_image_h2/bc3ae8221f6261f1215e455fb2d4eceb/image-14.jpg)

- Slides: 23

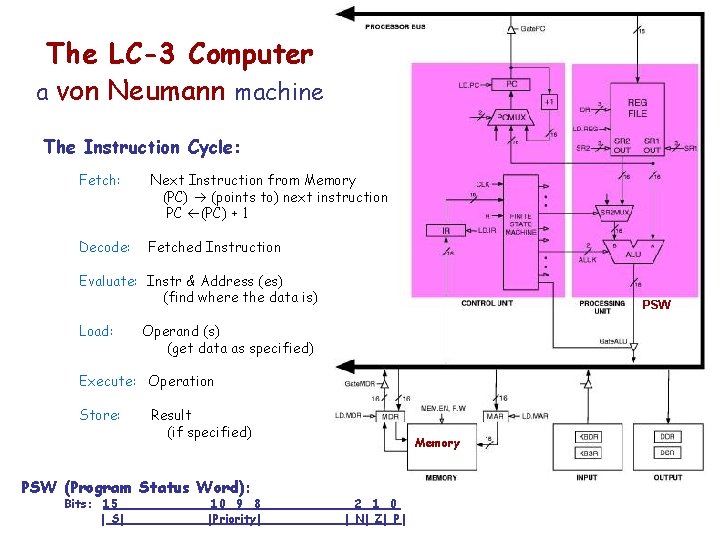

Chapter 5 The LC-3 Computer – Architecture – Memory Map – Instruction Set Architecture (ISA) • Machine Instructions • Address Modes • Instructions - Operate - Data Move - Control – Programming in Machine Code

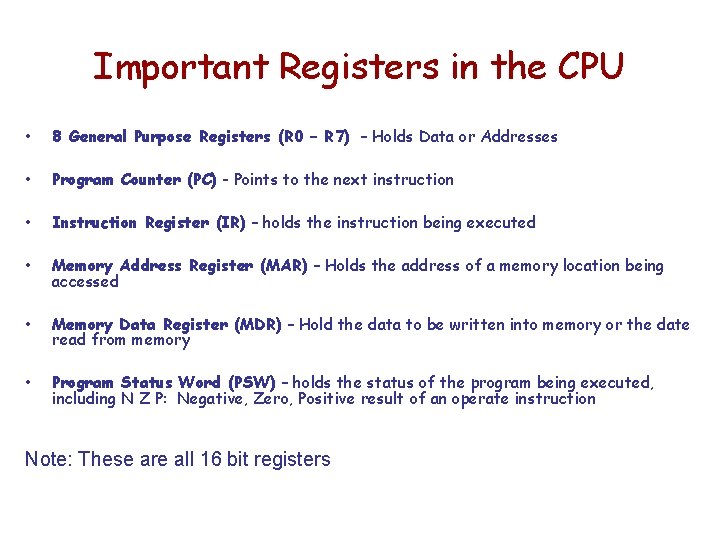

The LC-3 Computer a von Neumann machine The Instruction Cycle: Fetch: Next Instruction from Memory (PC) (points to) next instruction PC (PC) + 1 Decode: Fetched Instruction Evaluate: Instr & Address (es) (find where the data is) Load: PSW Operand (s) (get data as specified) Execute: Operation Store: Result (if specified) PSW (Program Status Word): Bits: 15 | S| 10 9 8 |Priority| Memory 2 1 0 | N| Z| P |

Important Registers in the CPU • 8 General Purpose Registers (R 0 – R 7) – Holds Data or Addresses • Program Counter (PC) - Points to the next instruction • Instruction Register (IR) – holds the instruction being executed • Memory Address Register (MAR) – Holds the address of a memory location being accessed • Memory Data Register (MDR) – Hold the data to be written into memory or the date read from memory • Program Status Word (PSW) – holds the status of the program being executed, including N Z P: Negative, Zero, Positive result of an operate instruction Note: These are all 16 bit registers

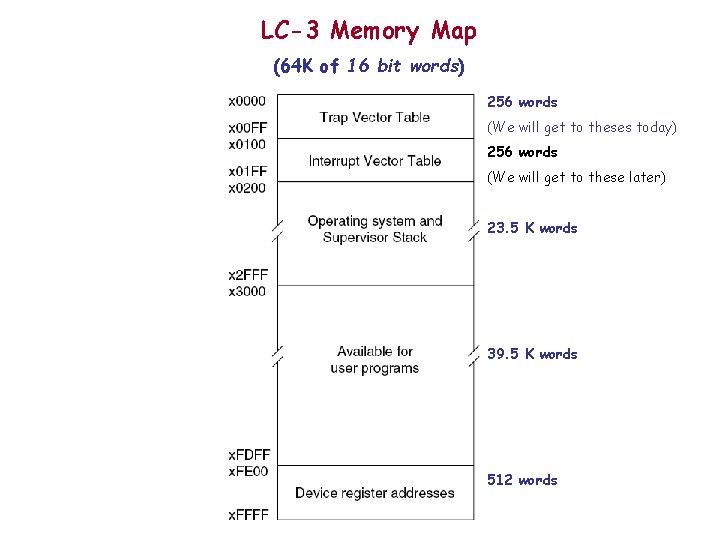

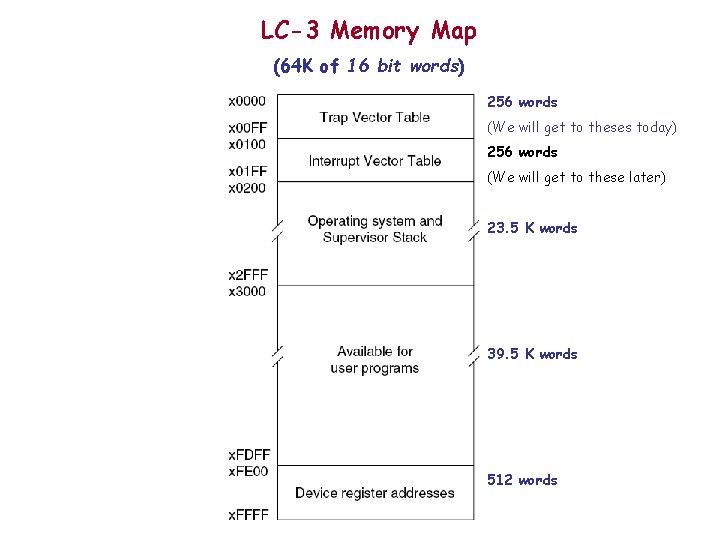

LC-3 Memory Map (64 K of 16 bit words) 256 words (We will get to theses today) 256 words (We will get to these later) 23. 5 K words 39. 5 K words 512 words

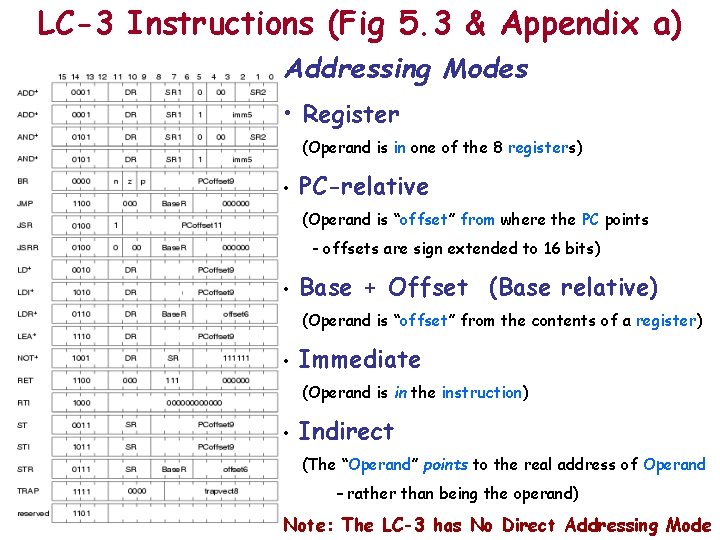

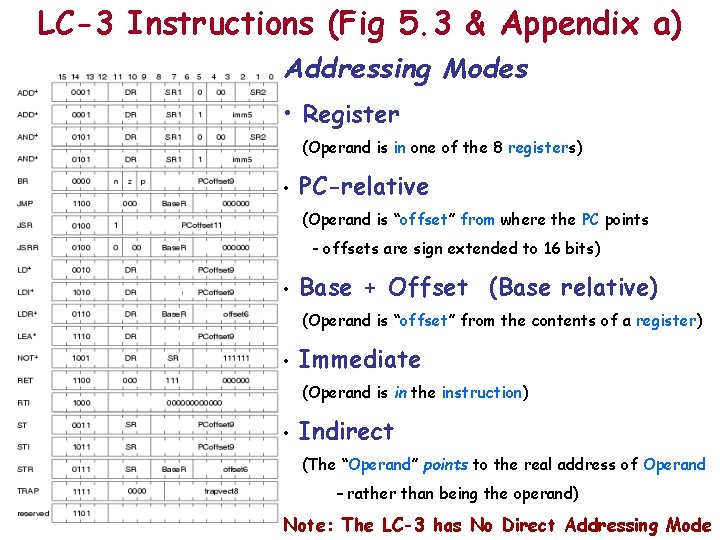

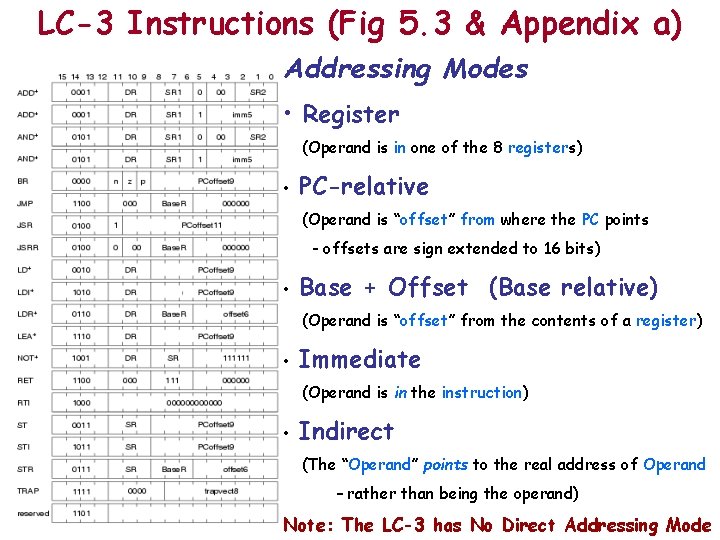

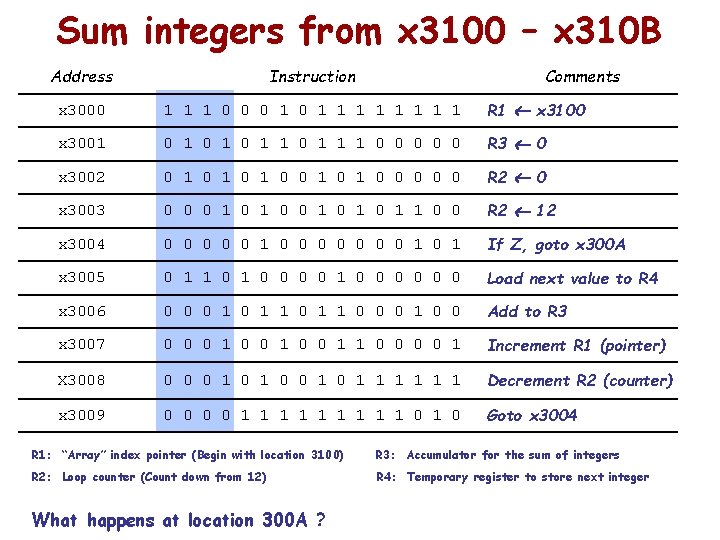

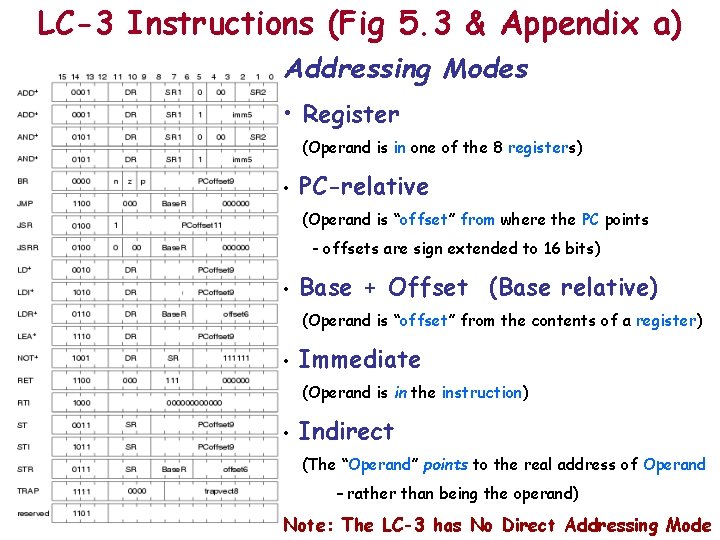

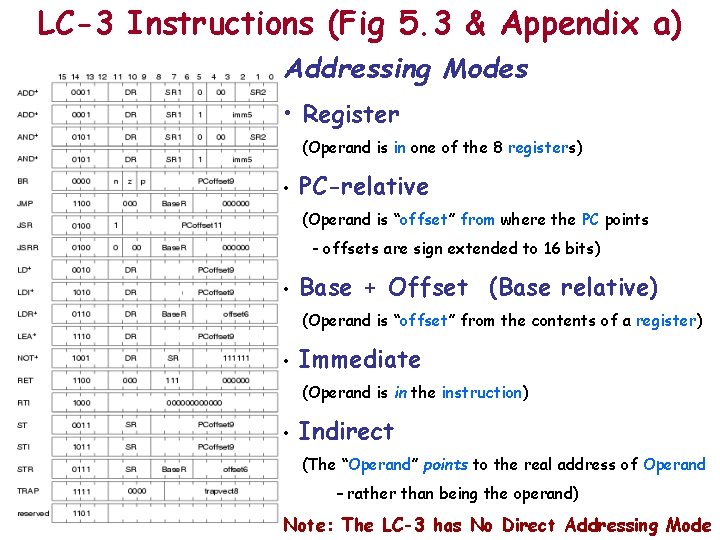

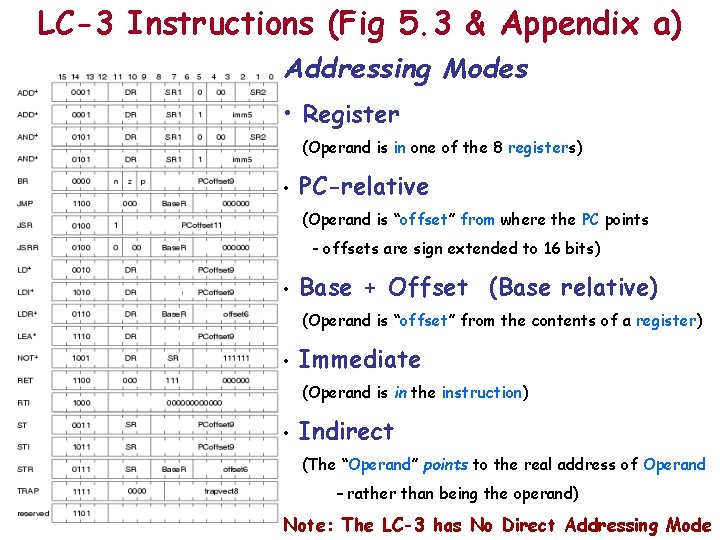

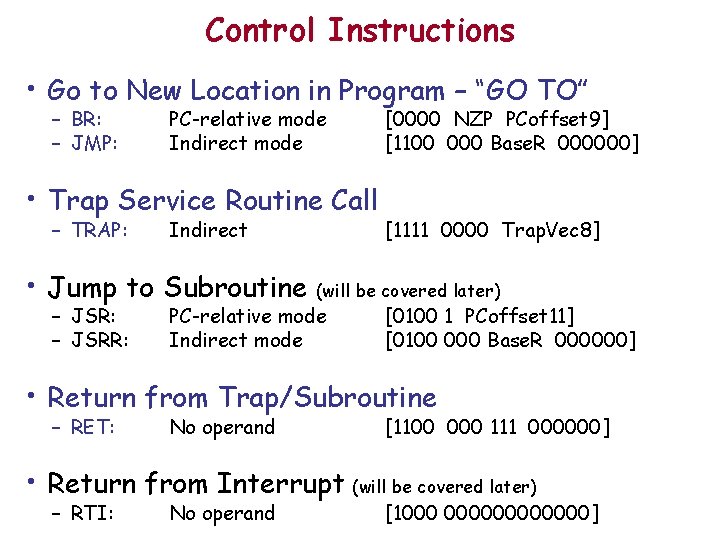

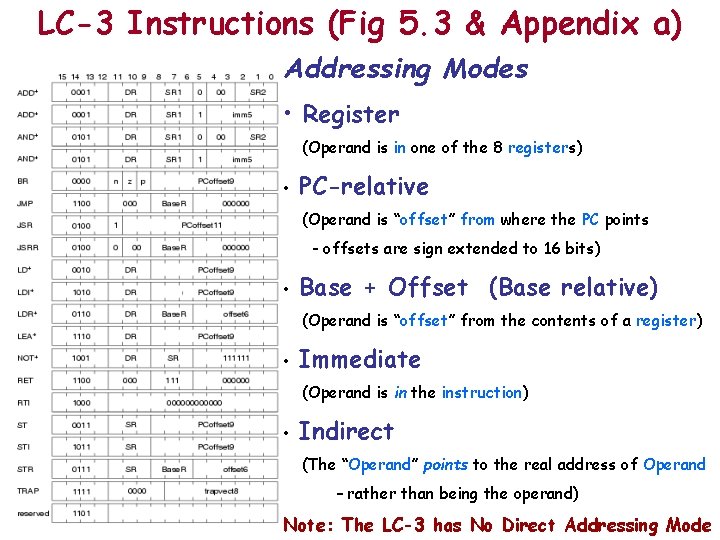

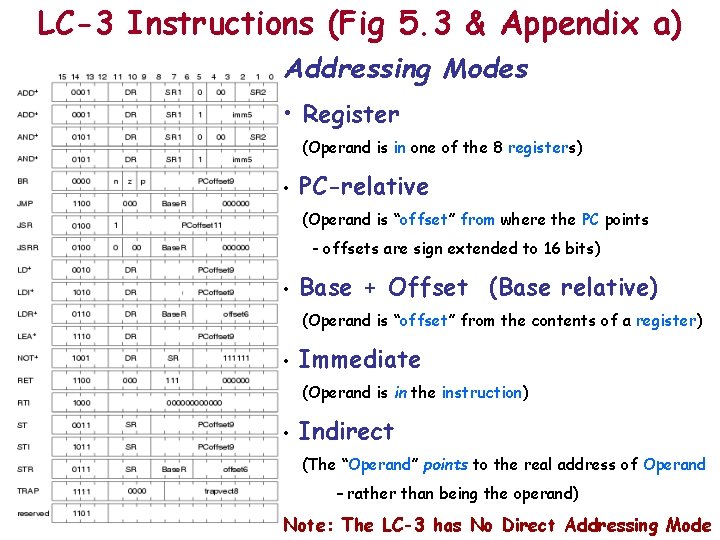

LC-3 Instructions (Fig 5. 3 & Appendix a) Addressing Modes • Register (Operand is in one of the 8 registers) • PC-relative (Operand is “offset” from where the PC points - offsets are sign extended to 16 bits) • Base + Offset (Base relative) (Operand is “offset” from the contents of a register) • Immediate (Operand is in the instruction) • Indirect (The “Operand” points to the real address of Operand – rather than being the operand) Note: The LC-3 has No Direct Addressing Mode

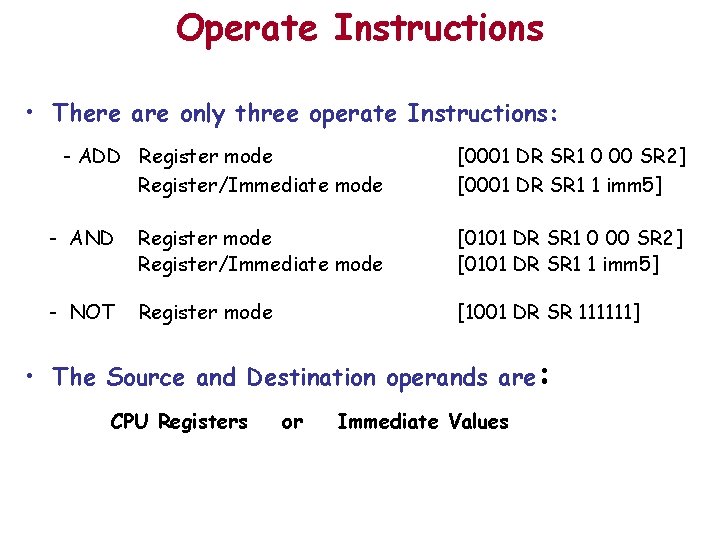

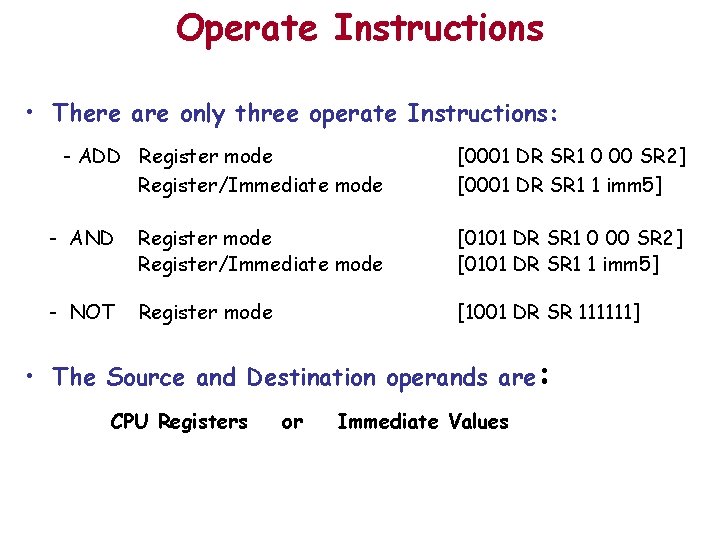

Operate Instructions • There are only three operate Instructions: - ADD Register mode Register/Immediate mode [0001 DR SR 1 0 00 SR 2] [0001 DR SR 1 1 imm 5] - AND Register mode Register/Immediate mode [0101 DR SR 1 0 00 SR 2] [0101 DR SR 1 1 imm 5] - NOT Register mode [1001 DR SR 111111] • The Source and Destination operands are: CPU Registers or Immediate Values

LC-3 Instructions (Fig 5. 3 & Appendix a) Addressing Modes • Register (Operand is in one of the 8 registers) • PC-relative (Operand is “offset” from where the PC points - offsets are sign extended to 16 bits) • Base + Offset (Base relative) (Operand is “offset” from the contents of a register) • Immediate (Operand is in the instruction) • Indirect (The “Operand” points to the real address of Operand – rather than being the operand) Note: The LC-3 has No Direct Addressing Mode

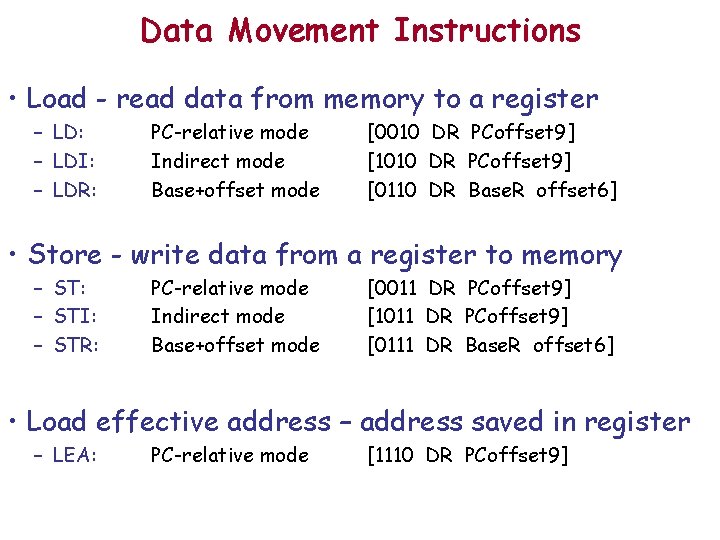

Data Movement Instructions • Load - read data from memory to a register – LD: – LDI: – LDR: PC-relative mode Indirect mode Base+offset mode [0010 DR PCoffset 9] [1010 DR PCoffset 9] [0110 DR Base. R offset 6] • Store - write data from a register to memory – ST: – STI: – STR: PC-relative mode Indirect mode Base+offset mode [0011 DR PCoffset 9] [1011 DR PCoffset 9] [0111 DR Base. R offset 6] • Load effective address – address saved in register – LEA: PC-relative mode [1110 DR PCoffset 9]

LC-3 Instructions (Fig 5. 3 & Appendix a) Addressing Modes • Register (Operand is in one of the 8 registers) • PC-relative (Operand is “offset” from where the PC points - offsets are sign extended to 16 bits) • Base + Offset (Base relative) (Operand is “offset” from the contents of a register) • Immediate (Operand is in the instruction) • Indirect (The “Operand” points to the real address of Operand – rather than being the operand) Note: The LC-3 has No Direct Addressing Mode

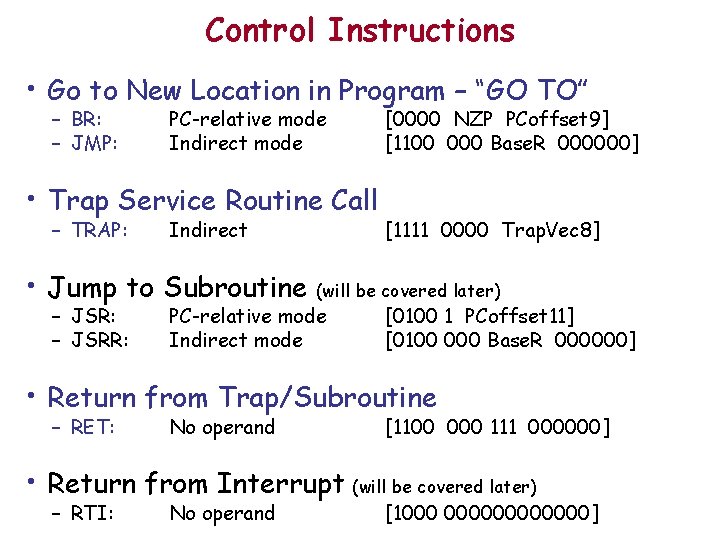

Control Instructions • Go to New Location in Program – “GO TO” – BR: – JMP: PC-relative mode Indirect mode • Trap Service Routine Call – TRAP: Indirect [0000 NZP PCoffset 9] [1100 000 Base. R 000000] [1111 0000 Trap. Vec 8] • Jump to Subroutine (will be covered later) – JSR: – JSRR: PC-relative mode Indirect mode [0100 1 PCoffset 11] [0100 000 Base. R 000000] • Return from Trap/Subroutine – RET: No operand [1100 000 111 000000] • Return from Interrupt (will be covered later) – RTI: No operand [1000 000000]

LC-3 Instructions (Fig 5. 3 & Appendix a) Addressing Modes • Register (Operand is in one of the 8 registers) • PC-relative (Operand is “offset” from where the PC points - offsets are sign extended to 16 bits) • Base + Offset (Base relative) (Operand is “offset” from the contents of a register) • Immediate (Operand is in the instruction) • Indirect (The “Operand” points to the real address of Operand – rather than being the operand) Note: The LC-3 has No Direct Addressing Mode

![Branch Instruction BR 0000 nzp PCoffset 9 Branch specifies one or more condition Branch Instruction BR • [0000 nzp PCoffset 9] Branch specifies one or more condition](https://slidetodoc.com/presentation_image_h2/bc3ae8221f6261f1215e455fb2d4eceb/image-12.jpg)

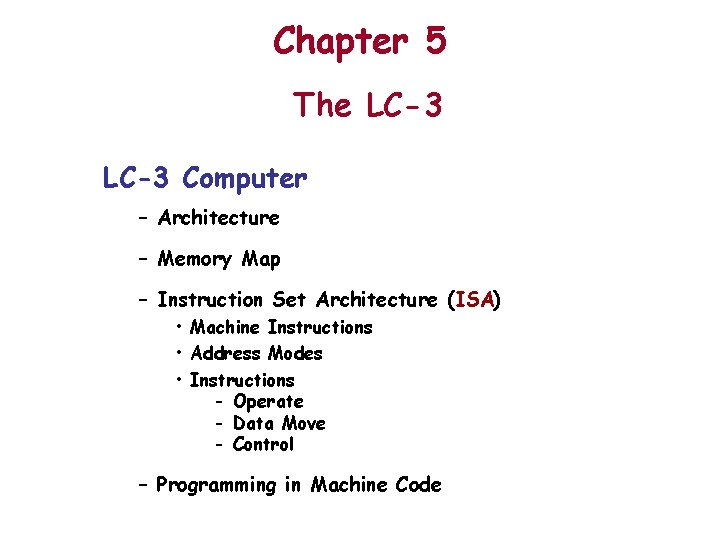

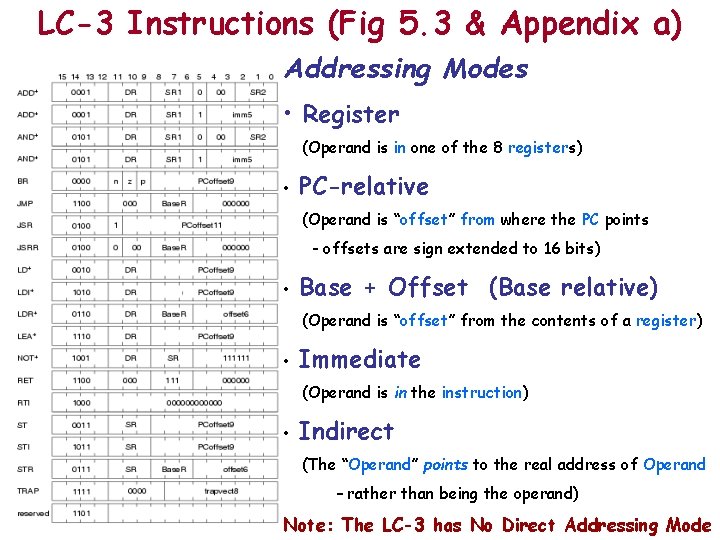

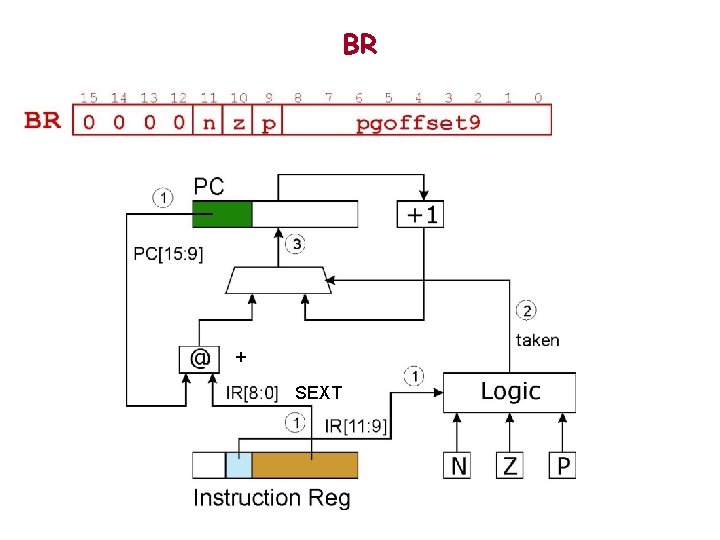

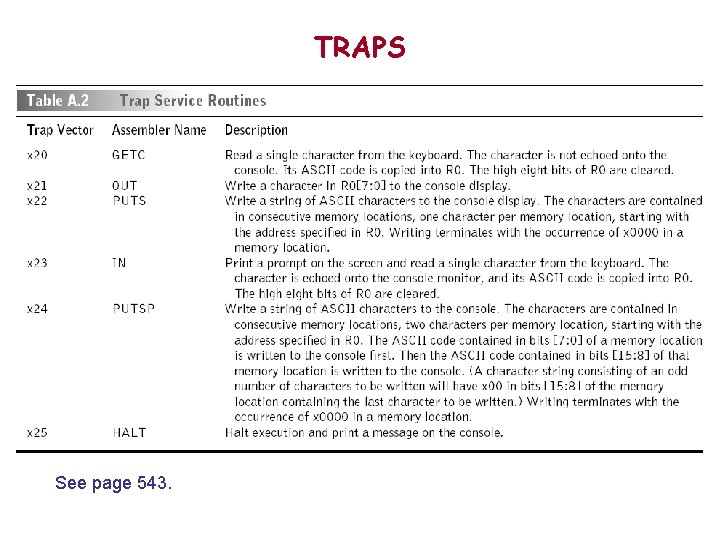

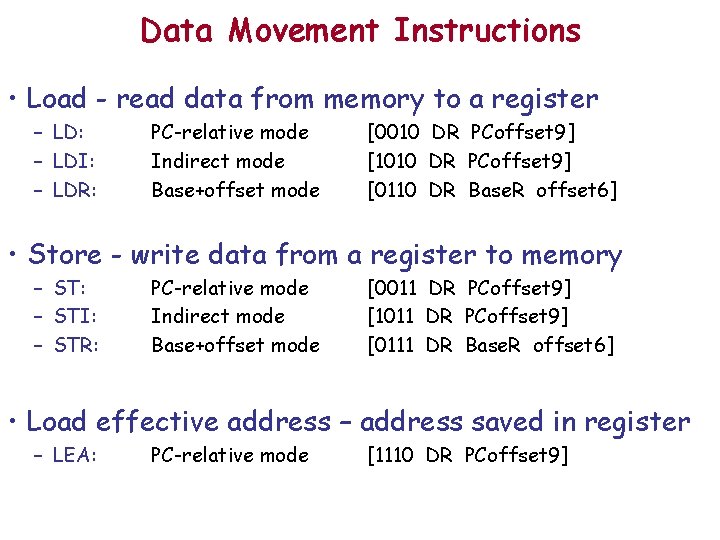

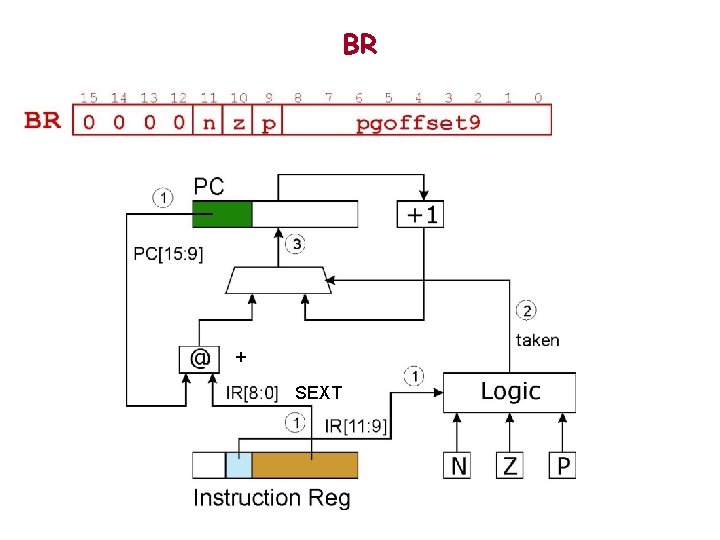

Branch Instruction BR • [0000 nzp PCoffset 9] Branch specifies one or more condition codes Program Status Word (PSW): Bits: • 15 | S| 10 9 8 |Priority| 2 1 0 |N|Z|P | If the specified bit(s) is (are) set, the branch is taken: – PC is set to the address specified in the instruction - Target (new PC) address is computed by: adding SEXT(IR[8: 0]) to the PC contents • If the branch is not taken: - the next sequential instruction is executed (presently pointed to by the PC).

BR + SEXT

![Jump Instruction JMP Base R 1100 000 Base R 000000 Jump is an Jump Instruction JMP Base. R [1100 000 Base. R 000000] • Jump is an](https://slidetodoc.com/presentation_image_h2/bc3ae8221f6261f1215e455fb2d4eceb/image-14.jpg)

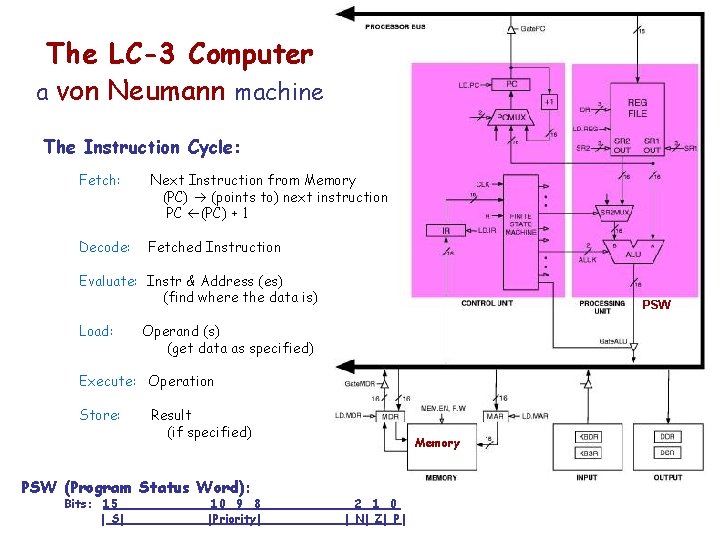

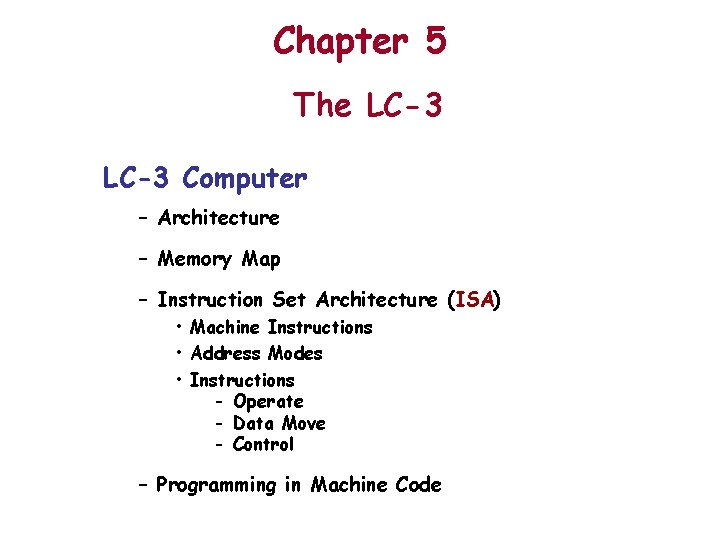

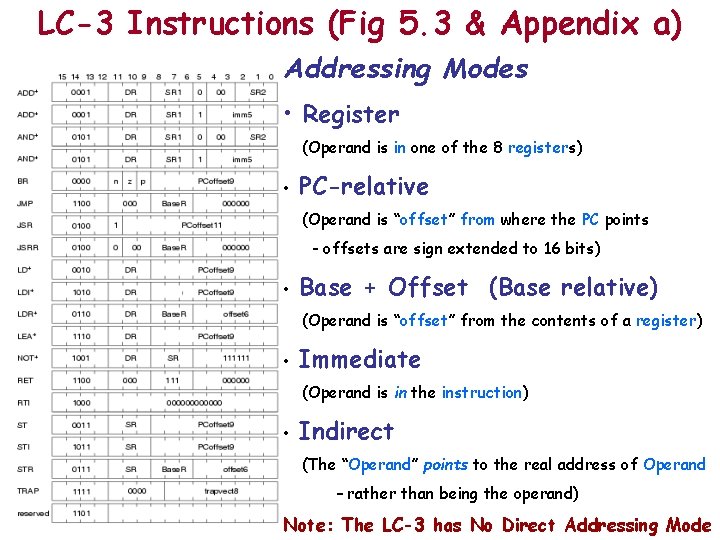

Jump Instruction JMP Base. R [1100 000 Base. R 000000] • Jump is an unconditional branch -- always taken. • Base. R – New PC contents (an Address) is the contents of the Base register – Allows any target address !

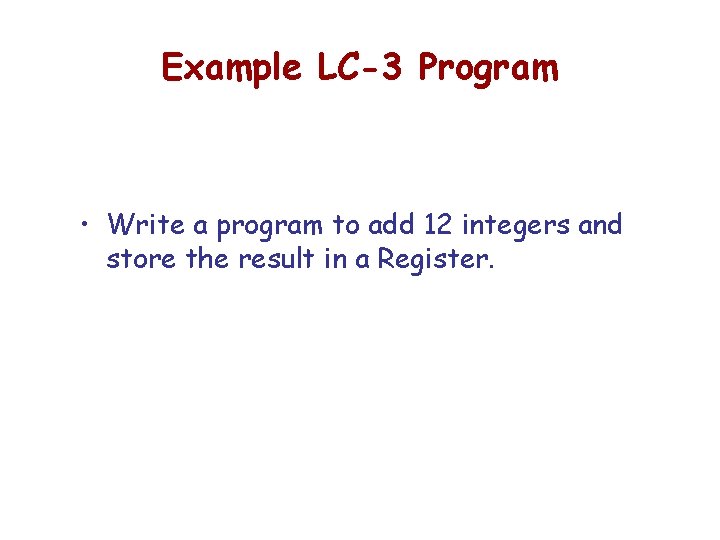

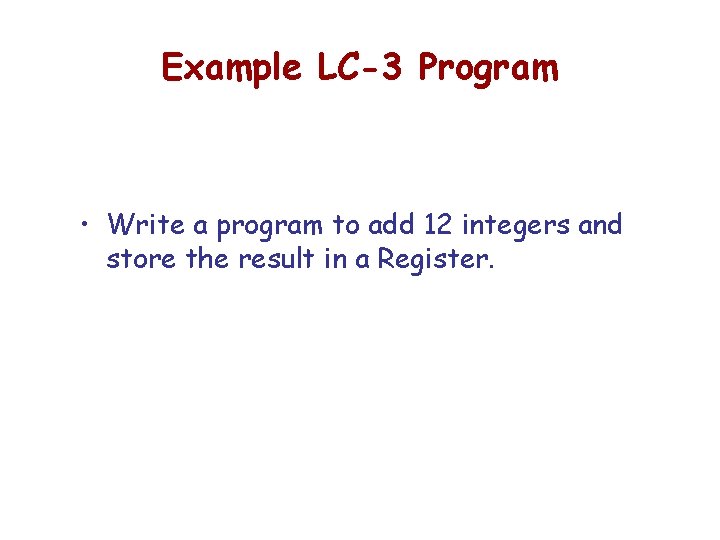

Example LC-3 Program • Write a program to add 12 integers and store the result in a Register.

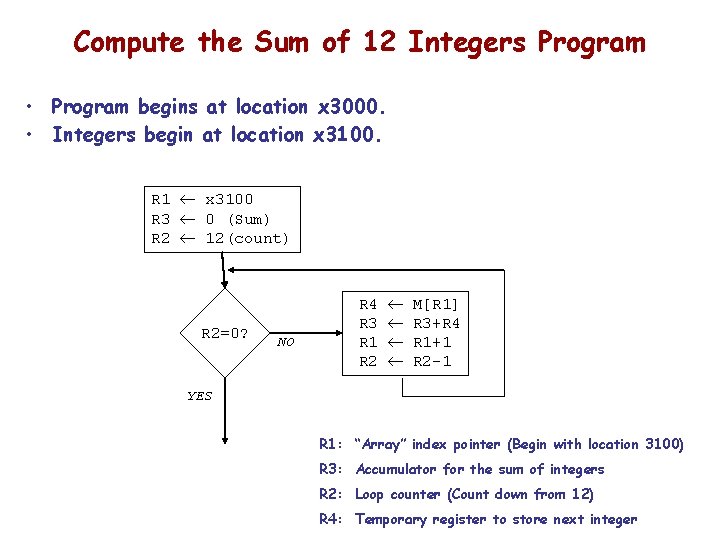

Compute the Sum of 12 Integers Program • Program begins at location x 3000. • Integers begin at location x 3100. R 1 x 3100 R 3 0 (Sum) R 2 12(count) R 2=0? NO R 4 R 3 R 1 R 2 M[R 1] R 3+R 4 R 1+1 R 2 -1 YES R 1: “Array” index pointer (Begin with location 3100) R 3: Accumulator for the sum of integers R 2: Loop counter (Count down from 12) R 4: Temporary register to store next integer

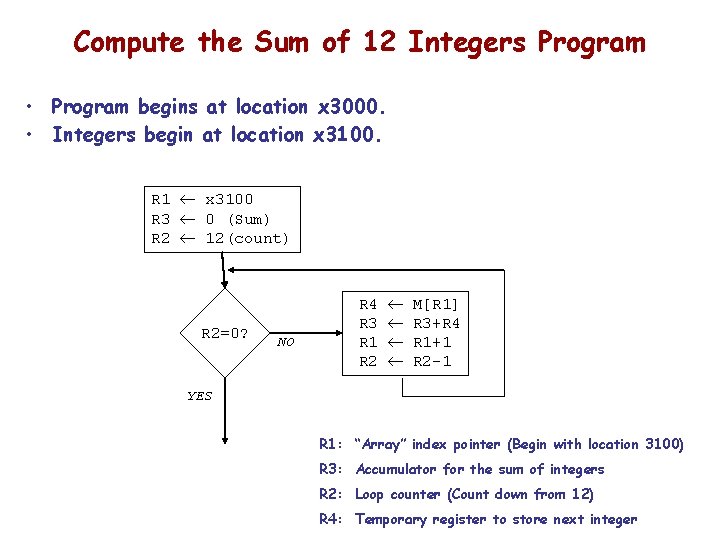

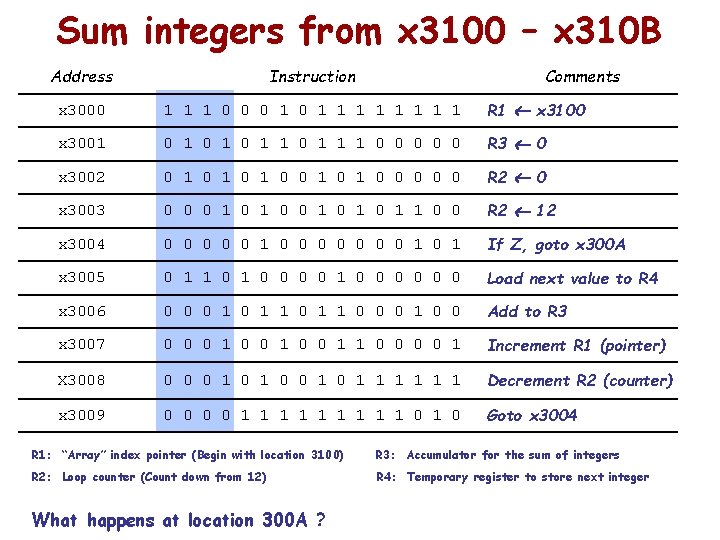

Sum integers from x 3100 – x 310 B Address Instruction Comments x 3000 1 1 1 0 0 0 1 1 1 1 1 R 1 x 3100 x 3001 0 1 0 1 1 1 0 0 0 R 3 0 x 3002 0 1 0 1 0 1 0 0 0 R 2 0 x 3003 0 0 0 1 0 1 0 1 1 0 0 R 2 12 x 3004 0 0 0 1 0 0 0 0 1 If Z, goto x 300 A x 3005 0 1 1 0 0 0 0 1 0 0 0 Load next value to R 4 x 3006 0 0 0 1 1 0 0 0 1 0 0 Add to R 3 x 3007 0 0 0 1 1 0 0 1 Increment R 1 (pointer) X 3008 0 0 0 1 0 1 1 1 1 Decrement R 2 (counter) x 3009 0 0 1 1 1 1 1 0 Goto x 3004 R 1: “Array” index pointer (Begin with location 3100) R 3: Accumulator for the sum of integers R 2: Loop counter (Count down from 12) R 4: Temporary register to store next integer What happens at location 300 A ?

LC-3 Instructions (Fig 5. 3 & Appendix a) Addressing Modes • Register (Operand is in one of the 8 registers) • PC-relative (Operand is “offset” from where the PC points - offsets are sign extended to 16 bits) • Base + Offset (Base relative) (Operand is “offset” from the contents of a register) • Immediate (Operand is in the instruction) • Indirect (The “Operand” points to the real address of Operand – rather than being the operand) Note: The LC-3 has No Direct Addressing Mode

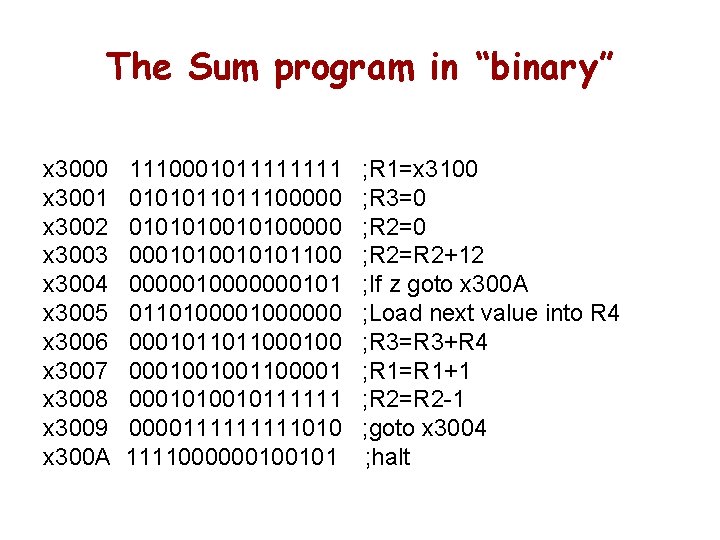

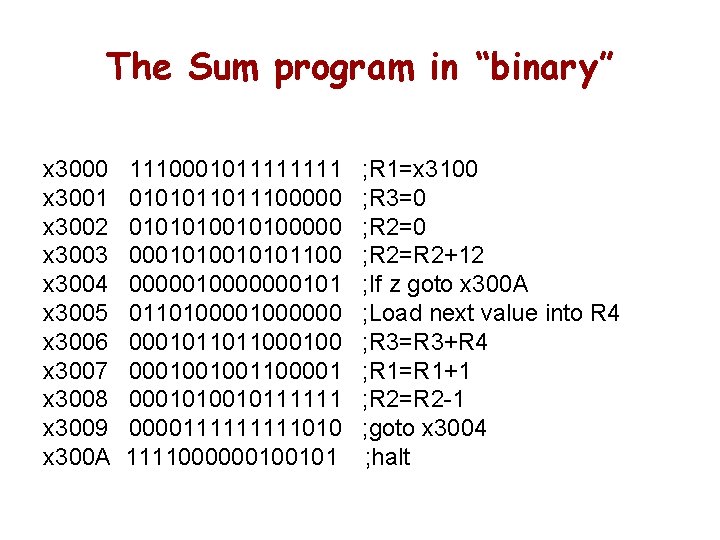

The Sum program in “binary” x 3000 x 3001 x 3002 x 3003 x 3004 x 3005 x 3006 x 3007 x 3008 x 3009 x 300 A 111000101111 0101011011100000 01010100000 00010101100 0000010000000101 01101000000 000101101100010010011000010111111 000011111010 1111000000100101 ; R 1=x 3100 ; R 3=0 ; R 2=R 2+12 ; If z goto x 300 A ; Load next value into R 4 ; R 3=R 3+R 4 ; R 1=R 1+1 ; R 2=R 2 -1 ; goto x 3004 ; halt

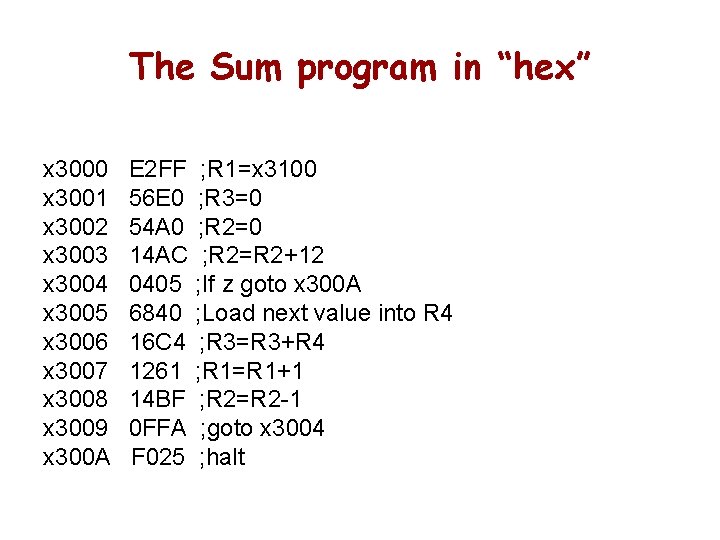

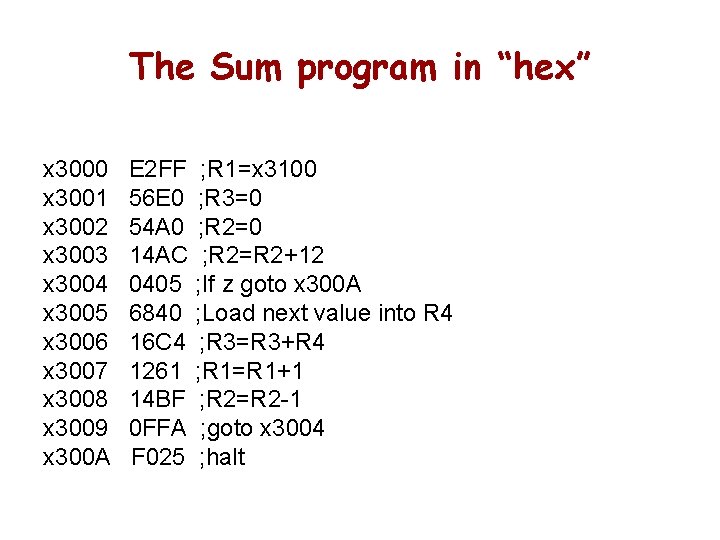

The Sum program in “hex” x 3000 x 3001 x 3002 x 3003 x 3004 x 3005 x 3006 x 3007 x 3008 x 3009 x 300 A E 2 FF ; R 1=x 3100 56 E 0 ; R 3=0 54 A 0 ; R 2=0 14 AC ; R 2=R 2+12 0405 ; If z goto x 300 A 6840 ; Load next value into R 4 16 C 4 ; R 3=R 3+R 4 1261 ; R 1=R 1+1 14 BF ; R 2=R 2 -1 0 FFA ; goto x 3004 F 025 ; halt

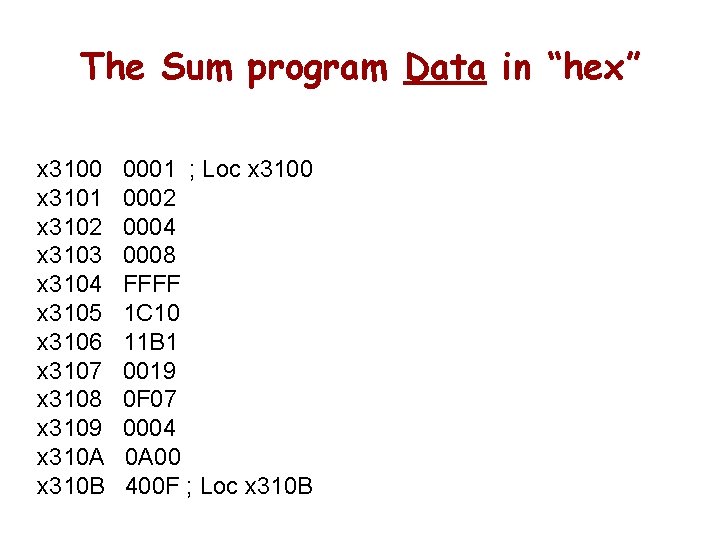

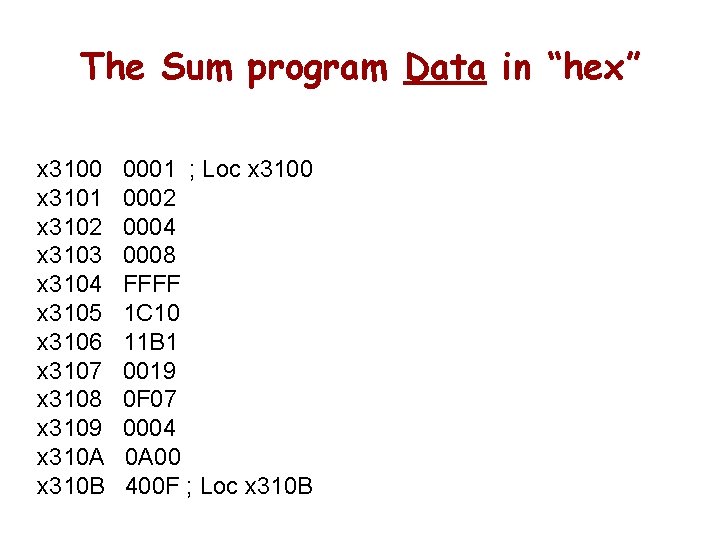

The Sum program Data in “hex” x 3100 x 3101 x 3102 x 3103 x 3104 x 3105 x 3106 x 3107 x 3108 x 3109 x 310 A x 310 B 0001 ; Loc x 3100 0002 0004 0008 FFFF 1 C 10 11 B 1 0019 0 F 07 0004 0 A 00 400 F ; Loc x 310 B

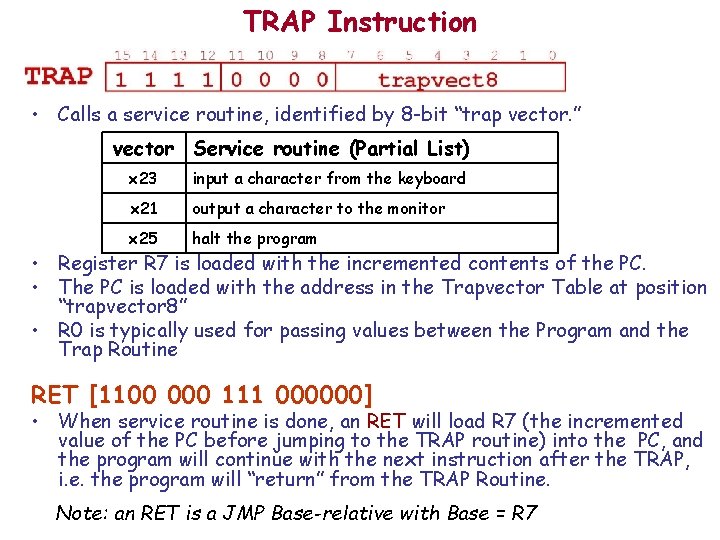

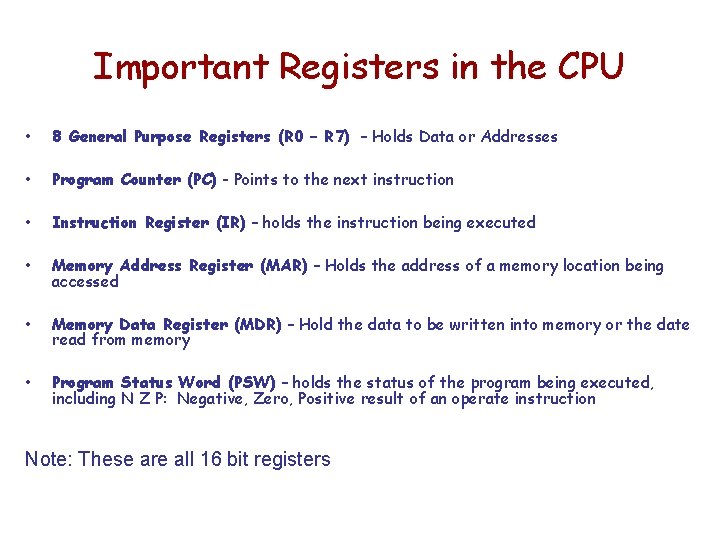

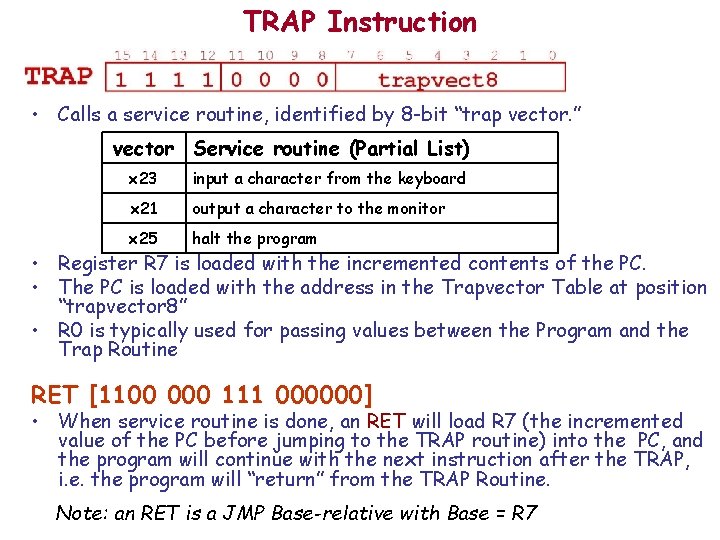

TRAP Instruction • Calls a service routine, identified by 8 -bit “trap vector. ” vector Service routine (Partial List) x 23 input a character from the keyboard x 21 output a character to the monitor x 25 halt the program • Register R 7 is loaded with the incremented contents of the PC. • The PC is loaded with the address in the Trapvector Table at position “trapvector 8” • R 0 is typically used for passing values between the Program and the Trap Routine RET [1100 000 111 000000] • When service routine is done, an RET will load R 7 (the incremented value of the PC before jumping to the TRAP routine) into the PC, and the program will continue with the next instruction after the TRAP, i. e. the program will “return” from the TRAP Routine. Note: an RET is a JMP Base-relative with Base = R 7

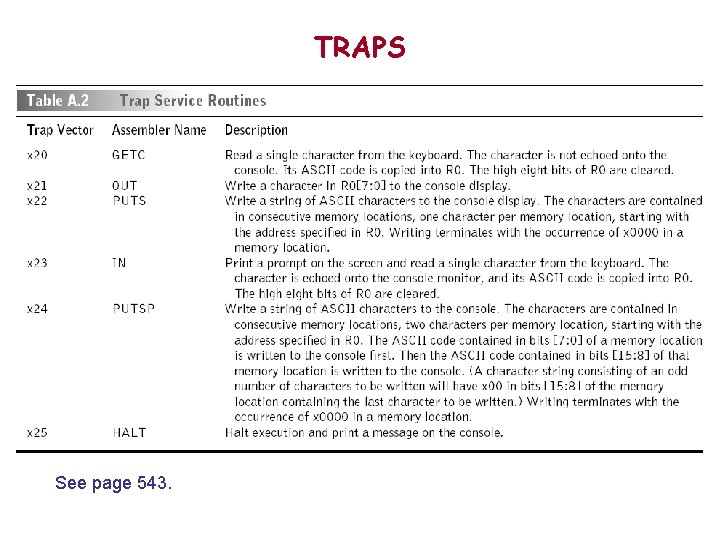

TRAPS See page 543.